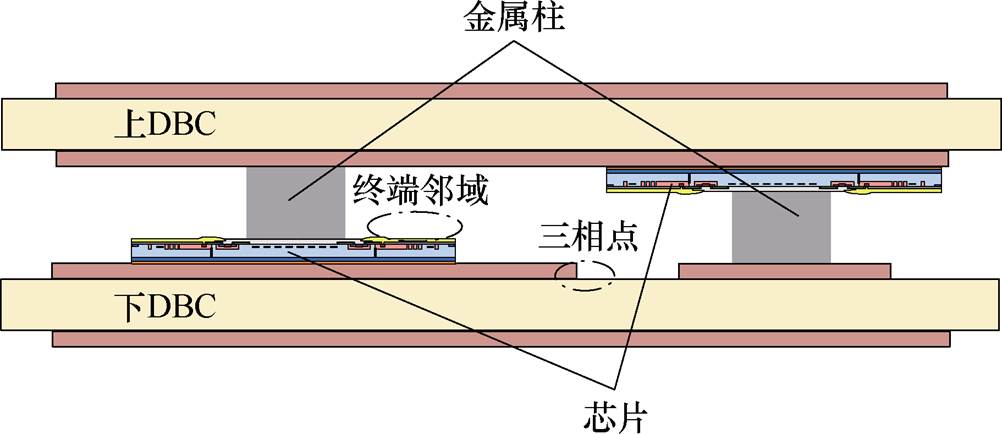

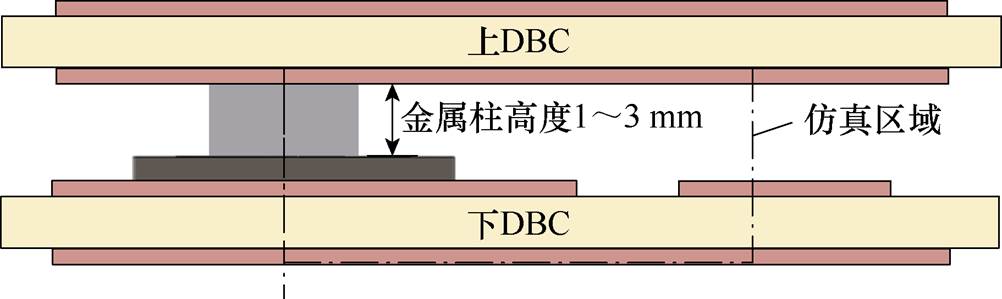

图1 高压SiC MOSFET模块中电场应力集中区域

Fig.1 Electric field stress concentration area in high-voltage silicon carbide MOSFET module

摘要 针对10 kV及以上电压等级碳化硅金属氧化物场效应晶体管(SiC MOSFET)器件封装的高电场应力、高寄生参数和新材料新结构带来的热可靠性问题,该文提出一种15 kV/10 A双面碳化硅功率模块的封装设计方案,解决了芯片终端邻域电场集中与寄生电感过高的技术难题。通过半导体仿真软件(TCAD)建立电场仿真模型,提出采用热膨胀系数匹配的自研高分子粘结剂固定聚酰亚胺绝缘框架,覆盖高电场强度区域,并通过温度循环测试验证其热机械可靠性。实验表明,模块在12 kV直流电压下无局部放电现象,动态测试显示其几乎无电压过冲,在10 kV母线电压下的动态测试中,开关速度达217 kV/ms(开通)与58 kV/ms(关断),总开关损耗仅为9.29 mJ,支持50 kHz高频工况。该研究为高压碳化硅功率模块提供了低寄生参数、高绝缘可靠性的封装方案,可以应用于脉冲功率与高频电能转换领域。

关键词:15 kV SiC MOSFET 芯片终端邻域 粘结剂 双脉冲测试

SiC MOSFET为代表的宽禁带半导体器件,正在成为学术和工业界的研究重点,尤其是在高压(电压等级大于6.5 kV)、高频应用上。与传统的高压硅绝缘栅双极型晶体管(Silicon Insulated Gate Bipolar Transistor, Si IGBT)模块相比,其应用范围更广,可用在分布式发电系统、医疗电源、船舶电力系统、固态变压器等领域[1-3]。

高压SiC MOSFET的高压、高频特性既是优点也对应用提出了挑战。现在已经存在的15 kV SiC MOSFET和20 kV SiC IGBT芯片,因封装技术的限制,阻碍了其大规模使用。在高压功率模块封装技术上主要是基于绝缘措施导致的电、热耦合问题[1, 4]:

(1)模块内电场集中引起的绝缘问题。随着芯片电压的提高,模块内电场不均匀程度加剧,电场集中处会发生局部放电(Partial Discharge, PD),对绝缘材料造成永久性损伤[4],使模块失效。高压碳化硅模块内部主要有两个电场集中点:一是在直接覆铜板(Direct Bond Copper, DBC)的铜层、陶瓷和灌封硅凝胶的结合点(又称三结合点、三相点)附近;二是在芯片终端外围区域又称芯片终端邻域(chip neighborhood)。为了缓释三相点电场,国内外学者提出了很多方案[5-9],这些方案均对三相点的电场集中有缓释作用。但目前对芯片终端邻域的电场分布和绝缘方案的研究则相对较少。

针对高压器件的芯片终端邻域电场分布的研究主要集中在高压IGBT上,以压接器件为主。传统的关于芯片终端绝缘问题的研究以芯片内部为主,未包含芯片终端邻域部分[10]。文献[11-15]均分析了目前高压IGBT器件在芯片终端邻域区域的电场分布,提出这是一个区别于三相点的新的电场集中区域。文献[13]指出了目前高压压接器件子单元内芯片终端外的氮气气隙是器件内电场集中点,并提出采用硅凝胶灌封的方案。文献[15]通过在场环截止区域增加电极的方法缓释了芯片终端邻域的电场强度。文献[16]的研究对象是高压SiC MOSFET器件,针对芯片邻域的电场集中提出了终端涂覆高分子聚合物绝缘方案,该聚合物可以承受极高电场强度,起到保护灌封硅凝胶的作用,但是该方案针对的是6.5 kV器件,缺乏更高电压等级器件的应用。

(2)高寄生电感问题。在传统的高压器件设计中,出于增大绝缘距离的设计,DBC铜间距较大,使得键合线长度增大,极大地提高了器件的寄生电感。因此,需要考虑基于压接、双面焊接(烧结)等方式的互联方案。压接互联方案主要用于高压Si基芯片的封装中,目前的高压SiC MOSFET芯片结构不适用于压接互联;双面焊接(烧结)的方案在文献[6]被提出,然而,这种基于金属柱的互联方案对于高压SiC MOSFET芯片终端电场分布的影响仍然欠缺文献说明。

(3)新结构的热、机械可靠性问题。目前提出的基于材料创新的绝缘结构的报道由于引入了新材料[7-8, 14],因此可能带来长期服役下的脱落、老化问题,导致绝缘效果下降。因此引入新材料的绝缘方案需要进一步论证。

综上所述,对高压SiC MOSFET采用双面封装形式,虽然可以减小模块寄生参数,但仍有芯片终端邻域绝缘与可靠性等问题亟待解决。目前,已经有数家国内外企业单位研制出6.5 kV及以上电压等级的高压SiC MOSFET功率模块。2011年,美国Wolfspeed公司最先发布了一款10 kV/120 A功率模块[17]。该模块采用引线键合的方式进行互联,采用硅凝胶灌封的形式绝缘。但由于该互联方式回路寄生电感较大,影响了模块的运行性能。随后该公司进行了多次迭代,减小了模块体积和寄生电感,但由于芯片终端邻域进行特殊绝缘设计,实际使用中极易发生绝缘损坏[18]。弗吉尼亚理工大学开发出了一种高密度、无键合线的10 kV SiC MOSFET功率模块[4]。该模块采用双面烧结的方式互联,并利用去耦电容和中点钳位的方式进行电磁干扰(Electro- magnetic Interference, EMI)和绝缘设计。这样的设计极大地减小了模块的共模电容、回路寄生电感和模块基板的局部放电起始电压(Partial Discharge Inception Voltage, PDIV)。然而,该方案未对芯片终端邻域的绝缘结构进行特殊设计,其使用集成电容进行中点钳位来提高绝缘的设计限制了模块功率密度的提高,且使得模块无法实现双面冷却。

国内方面,中国电子科技集团55研究所[19]、华中科技大学[20]、西安交通大学[16]等高校和科研机构均发布过6.5 kV及以上的高压SiC MOSFET功率模块。文献[21]提出了一款15 kV SiC MOSFET的单管封装模块,是国内首次提出,但集成度有待提高,动态测试电压较低。文献[22]提出了一款10 kV高压SiC 功率模块,采用级联结构,测试电压高达10 kV。然而,该结构引入的寄生电感极大,引起了高达2 kV的电压振荡。总之,国内针对高压SiC MOSFET封装的研究与国外有一定差距,亟需一款高工作电压、低寄生参数、高绝缘可靠性的封装方案。

综上所述,本文基于国产15 kV SiC MOSFET芯片,提出了自研高绝缘高可靠粘合剂粘接聚酰亚胺框架的芯片终端邻域绝缘方案,以此为基础封装出了一款双面焊接结构的、15 kV/10 A半桥功率模块。首先,采用TCAD仿真软件建立了15 kV芯片终端邻域电场分布模型,得到电场分布规律。其次,根据模型计算规律设计了芯片邻域的高可靠性绝缘结构,提出采用自研粘接材料粘接绝缘框架的绝缘方案,并通过热测试和机械测试说明了粘接可靠性。然后,展示了模块详细封装过程。最后,实现了模块的局部放电实验,并且展示了模块在6、8和10 kV的直流母线电压下的双脉冲测试结果。

采用金属垫块的双面互联结构取代键合线互联结构的模块通常在寄生参数上具有优势[23]。与键合线互联结构相比,通流路径由水平回路转化为垂直回路,大幅降低了功率回路寄生电感。在器件运行过程中,回路寄生电感会引起电压过冲,减小设计余量,影响器件寿命,而这种结构下,由互联结构引入的寄生电感可以被减小到较低水平(通常小于5 nH)。然而,15 kV等级高压SiC MOSFET芯片在源极金属垫块互联结构下芯片邻域电场分布仍不明晰,成为制约该种类芯片双面互联应用的条件之一。高压SiC MOSFET是否可以采用双面结构封装问题的关键在于确定该结构下芯片终端邻域的电场分布情况。

本研究首先分析模块绝缘失效机理,确定模块内电场分布集中区域,然后确定采用何种绝缘设计。

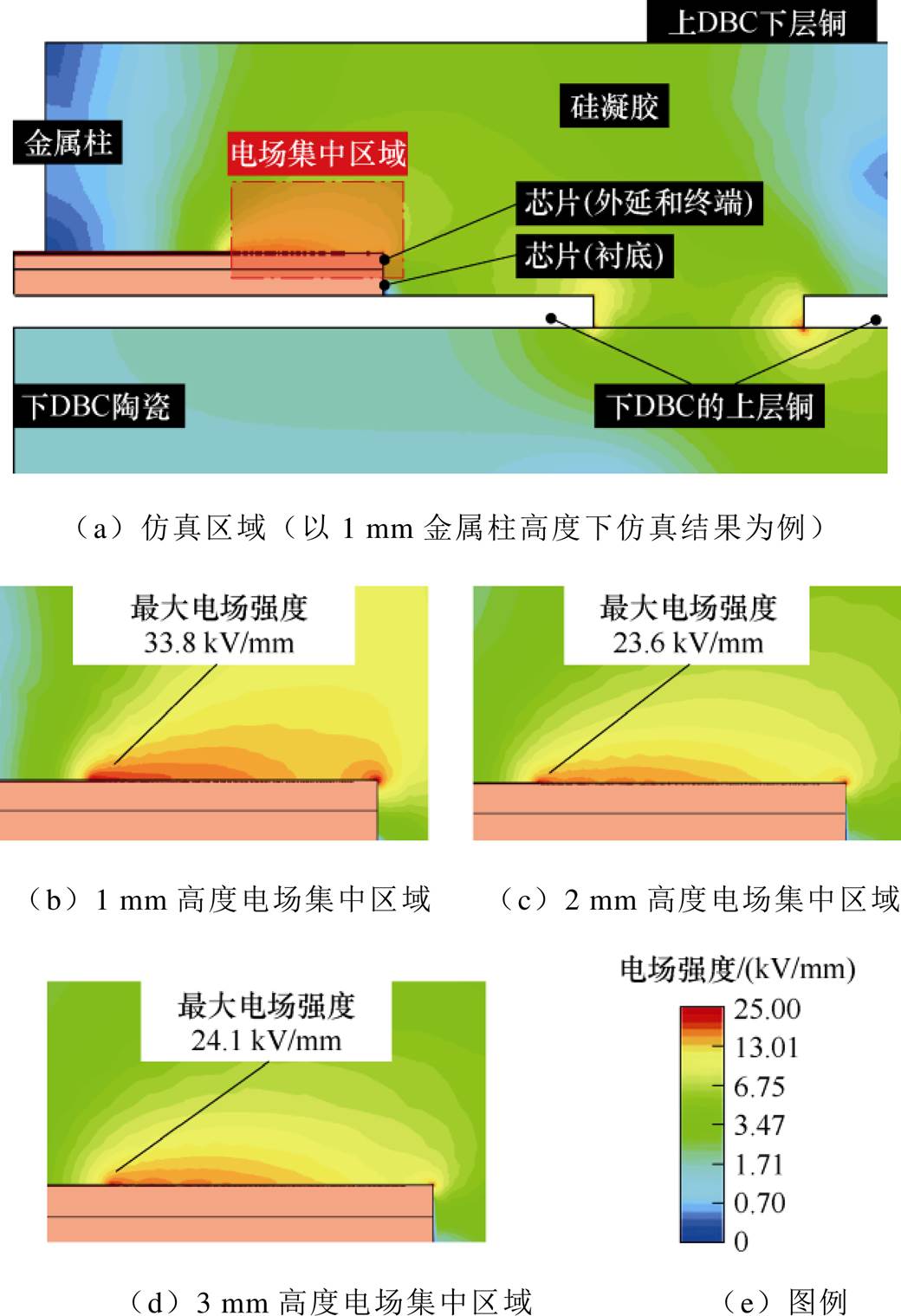

高压功率模块在工作时,绝缘失效通常发生在电场应力集中的点,如引言所述,在模块中有两个点的电场应力较为集中。一是所谓的三相点区域;二是在芯片终端邻域。高压SiC MOSFET模块中电场应力集中区域如图1所示。

图1 高压SiC MOSFET模块中电场应力集中区域

Fig.1 Electric field stress concentration area in high-voltage silicon carbide MOSFET module

在模块的三相点上,失效机制通常是DBC上层铜皮之间在陶瓷层表面的绝缘贯通击穿。针对这样的失效机制,已经有较多研究来缓和这个点的电场分布。例如,下层铜浮地[24]、改变DBC结构[5]、下层铜不直接接地[6]、采用非线性材料涂覆[9]等方案。这些方案都能有效改善该处的电场强度集中,但不是本文论述的重点,不再赘述,根据文献[24]中提供的方案对三相点的绝缘进行设计。

针对芯片终端邻域的电场研究主要在6.5 kV的器件上,其邻域电场分布不仅与芯片终端结构相关,还与芯片互联方式有关。文献[16]提出10 kV SiC MOSFET由于终端结构的设计,在芯片终端邻域处有较大电场强度。文献[25]提出键合线的存在会增大键合线下方芯片终端邻域处的电场强度。然而,目前对于SiC MOSFET的芯片终端邻域建模集中于键合线互联器件,且芯片电压偏低。因此,目前仍然缺乏15 kV器件的仿真模型和芯片终端邻域绝缘方案,需对该区域的电场分布进行重点研究。

获得芯片邻域电场分布需要在仿真模型中同时包含芯片结构和封装结构。芯片结构并不能用简单的两块平行焊盘与中间所夹的SiC介质来建模[13],需要建立亚芯片结构模型。同时,将这个亚芯片结构模型与封装结构进行联合仿真。

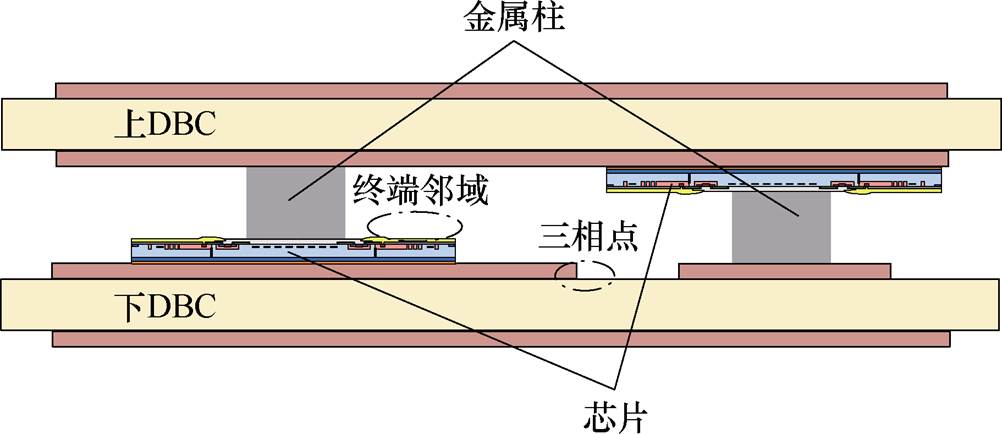

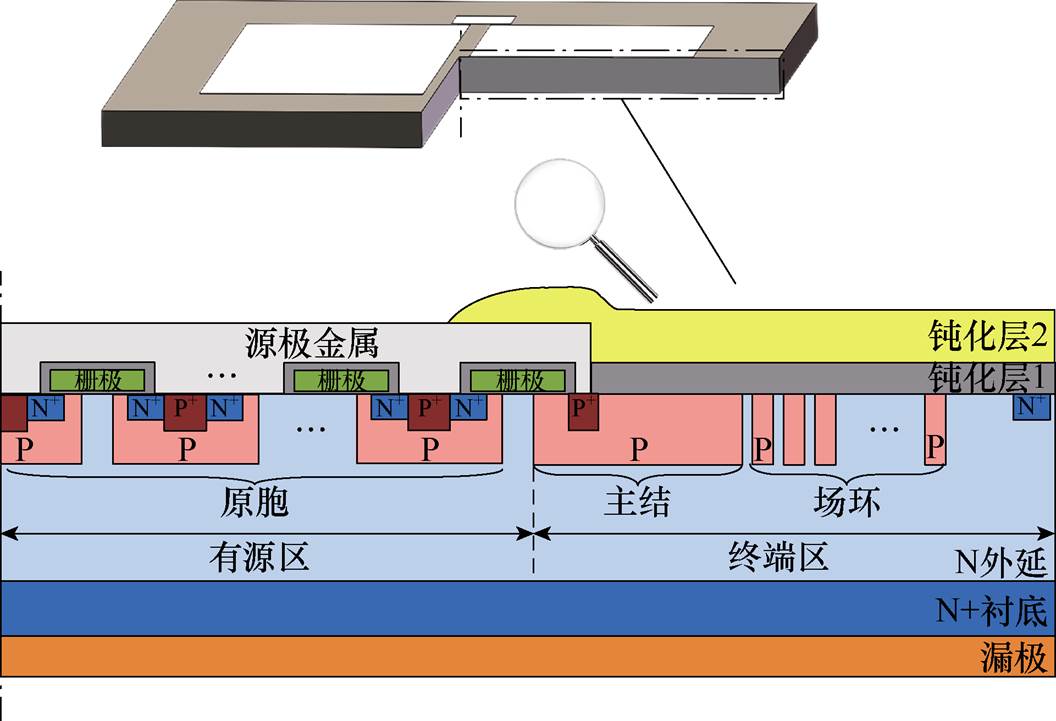

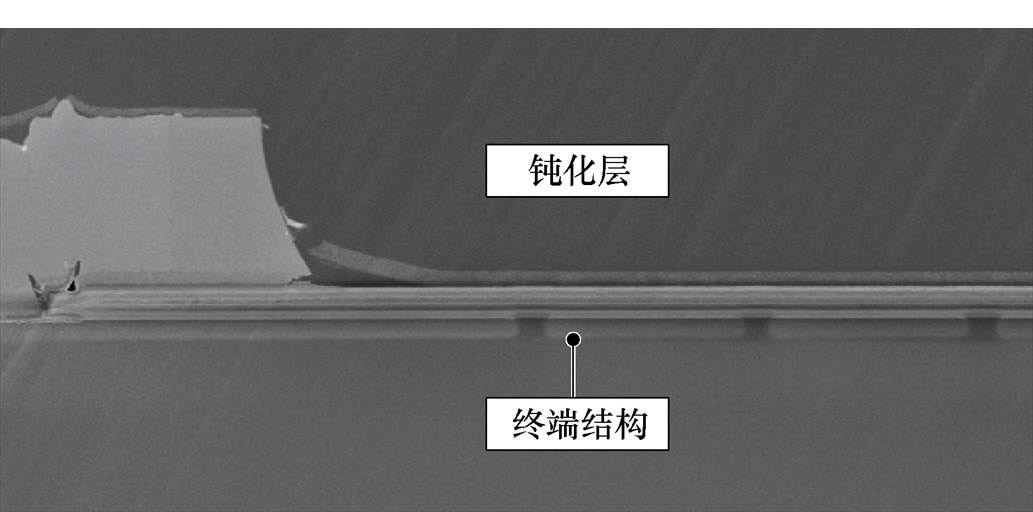

一个高压SiC MOSFET芯片的内部结构如图2所示。图2为剖面图,可以分为两个部分:有源区和终端区。有源区由原胞组成,每个原胞的源极和栅极通过芯片相关结构设计在芯片表面形成焊盘,是芯片有效的工作部分;终端区分布在芯片边缘,由场环等结构组成,场环是承压结构,防止芯片关闭时漏极和源极的击穿故障。

在本文仿真模型中,通过向供应商询问以及文献[21, 26-27]可以获得芯片的原胞结构和掺杂浓度,芯片的终端结构(场环宽度、深度、间距等数据)由聚焦离子束电镜(Focused Ion Beam, FIB)观察获得,SiC MOSFET终端观察如图3所示,建立包含芯片内部结构的器件模型。由于器件承压过程涉及载流子的分布变化,因此传统的有限元仿真软件(如AnsysEM)无法获得准确结果。因此,选用半导体器件专用仿真软件TCAD模拟工具进行仿真。

图2 SiC MOSFET内部结构

Fig.2 Internal structure of silicon carbide MOSFET

图3 SiC MOSFET终端观察

Fig.3 Observation of SiC MOSFET terminal

考虑到建立一个三维模型将大大增加复杂性和模拟时间,通常是基于二维模型对半导体器件结构进行模拟。而本文选择构建一个准三维模型,包括DBC、芯片结构、互联介质(金属柱)、封装材料,并选择具有代表性的横截面进行二维TCAD模拟仿真,仿真截面设置如图4所示,基于国产15 kV SiC MOSFET芯片进行仿真,该芯片采用条形原胞结构,为了简化仿真步骤,采用平行于原胞长边方向进行横截,得到最终的仿真模型。

图4 仿真截面设置

Fig.4 Simulation section settings

在芯片终端模型中,N+衬底厚度为250 mm,N外延厚度为150 mm,钝化层1(二氧化硅)厚度为0.6 mm,钝化层2(聚酰亚胺)厚度为6 mm,源极金属厚度为5 mm。

封装结构模型中,金属垫块与终端的距离设置为0.5 mm,垫块的高度从1~3 mm变化。模型示意图如图4所示。DBC的铜厚为300 mm,陶瓷厚度为1 mm,芯片边缘距离DBC铜边缘的距离为1 mm,下DBC上层铜间距为2 mm。模型中封装材料(硅凝胶)的介电常数设置为2.8 F/m。

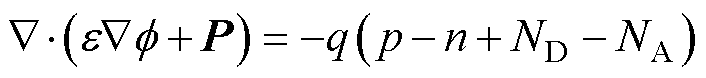

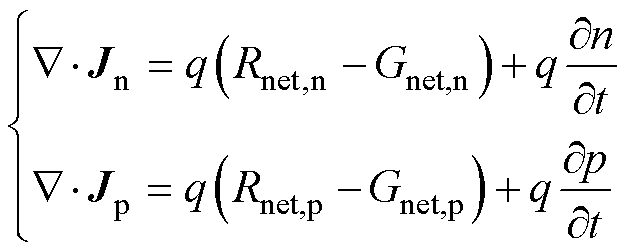

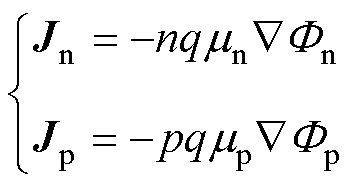

给予芯片漏极12 kV的高压激励,将芯片源极置0 V。设置求解物理方程为泊松方程、电子和空穴的漂移扩散方程,分别表示为

(1)

(1)

(2)

(2)

(3)

(3)

式中,e为相对介电常数;f为静电势;P为极化强度;Jn、Jp分别为电子和空穴电流密度;q为电子电荷量。电子浓度n和空穴浓度p可以通过能带模型和态密度模型得到;ND和NA分别为施主掺杂浓度和受主掺杂浓度;Rnet,n、Rnet,p、Gnet,n、Gnet,p分别为电子的复合率、空穴的复合率、电子的生成率、空穴的生成率,这4个物理参数需要通过载流子的产生和复合模型来确定,包括碰撞电离模型和肖克利-里德-霍尔(Shockley-Read-Hall, SRH)模型;mn和mp分别为电子和空穴的迁移率;Fn和Fp分别为电子和空穴的准费米势。对于SiC器件,还需要特别考虑不完全电离模型:SiC的带隙很宽,因此掺杂的杂质不能完全电离,特别是对于本文提到的器件中使用的铝掺杂,由于铝的电离能较高,不完全电离的比例相对较高,因此需要在模拟设置中依照文献[28]加入不完全电离模型。

为了降低仿真网格数目、提高仿真效率,采用“remove”指令近似认为金属材料表面均为等势面。仿真结果中金属材料均为白色,不显示电场分布。

边界条件默认为对称边界,由于仿真空间足够大,可以减小边界条件对仿真结果的影响。

双面互联结构下芯片邻域电场分布如图5所示。图5b~图5d显示了垫块高度1、2、3 mm的芯片终端邻域电场分布情况。可以看出,随着垫块高度的上升,芯片邻域的最大电场强度会从33.8 kV/mm下降到24.1 kV/mm。同时,电场强度不会随着垫块高度的提升无限制下降,高度超过2 mm的时候,电场强度下降速度开始放缓,但即使高度上升到3 mm,其最大电场强度仍然高于20 kV/mm。因此,高压SiC MOSFET器件采用金属柱进行双面互联,需要采用特殊结构对芯片终端邻域实施绝缘设计。

图5 双面互联结构下芯片邻域电场分布

Fig.5 Electric field distribution in the chip neighborhood under the double side structure

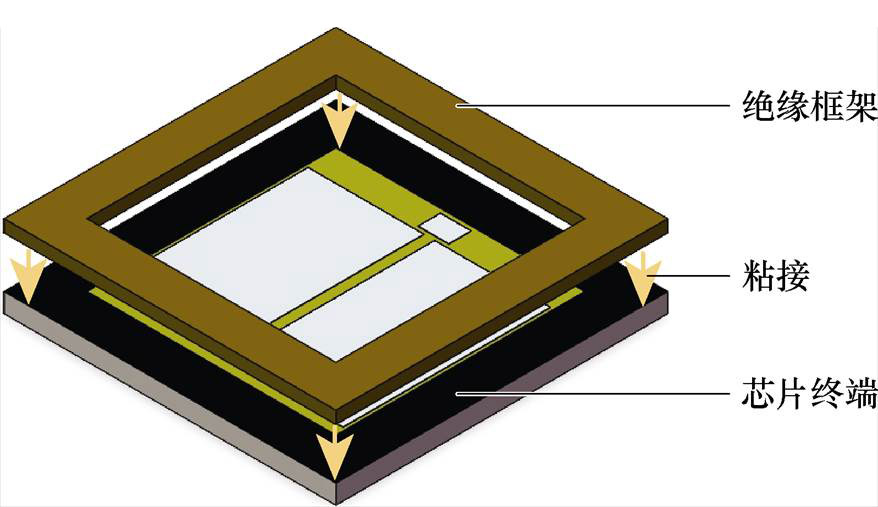

根据第1节中的仿真结果,芯片终端邻域有着高度30~60 mm的高电场强度区域,因此,需使用较厚的绝缘结构对高电场强度区域进行覆盖,保证硅凝胶尽可能承受更低的电场强度。因此,本文提出采用与芯片终端平面形状一致,高度为300 mm的聚酰亚胺绝缘框架覆盖高电场强度区域,通过粘接的方式粘接在芯片终端上方,芯片绝缘框架如图6所示。聚酰亚胺是一种高介电强度绝缘材料,其介电强度在100~300 kV/mm,可以承受终端邻域的高电场强度。为了绝缘框架与芯片终端紧密连接,需要调配合适的粘结材料,使得框架与终端进行互联。该粘结材料需要高绝缘性、与芯片匹配的热膨胀系数以及一定的连接强度。

图6 芯片绝缘框架

Fig.6 Chip insulation frame

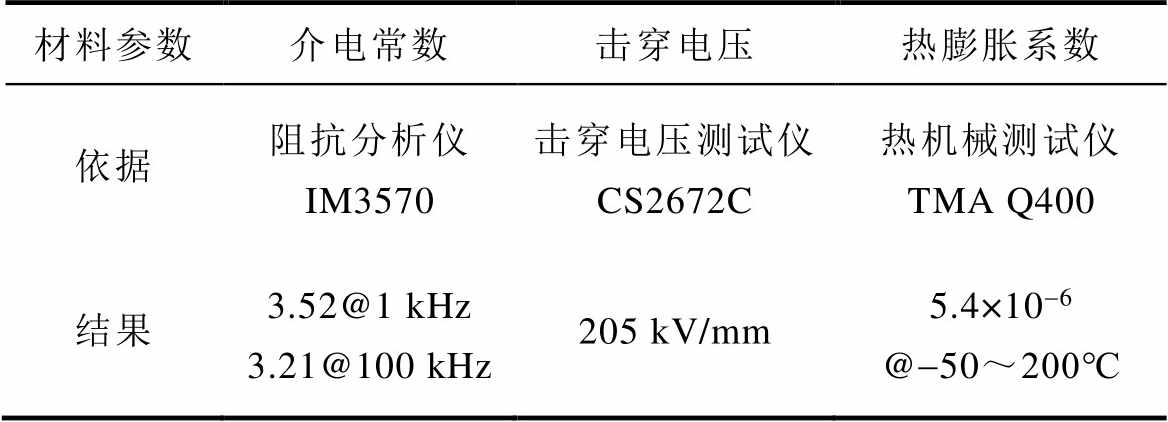

本文提出一种自制的基于高分子聚合物结构的粘结材料。该材料的单体会在极性溶液中发生聚合,生成胶状前体溶液。该溶液具有较好的粘合性能,可以将聚酰亚胺绝缘框架与终端层粘结起来。经过高温固化后,绝缘框架会与芯片终端紧密互联。表1显示了该粘结剂的热学性能与介电性能。可见,其较高的击穿电压可以保证粘结剂不被高电场强度击穿;而其在较大的温域内与SiC热膨胀系数(4.4× 10-6)较接近,可以保证运行过程中较低的热应力。

表1 该粘结剂的热学性能与介电性能(固化后)

Tab.1 The thermal and dielectric properties of the adhesive (after cured)

材料参数介电常数击穿电压热膨胀系数 依据阻抗分析仪IM3570击穿电压测试仪CS2672C热机械测试仪TMA Q400 结果3.52@1 kHz 3.21@100 kHz205 kV/mm5.4×10-6 @-50~200℃

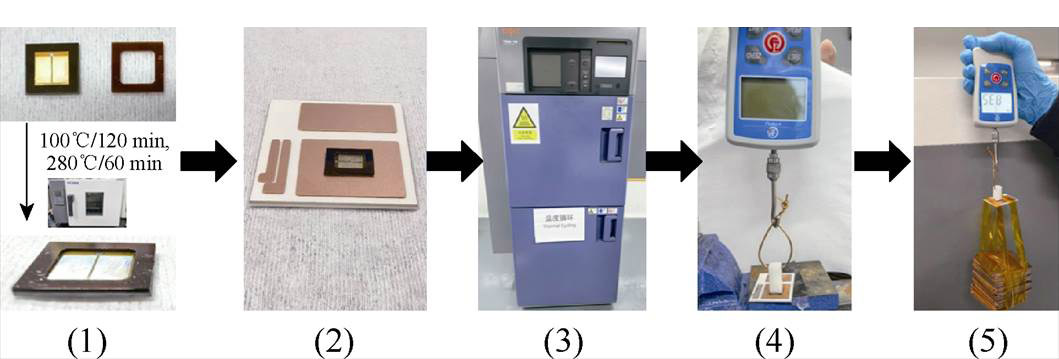

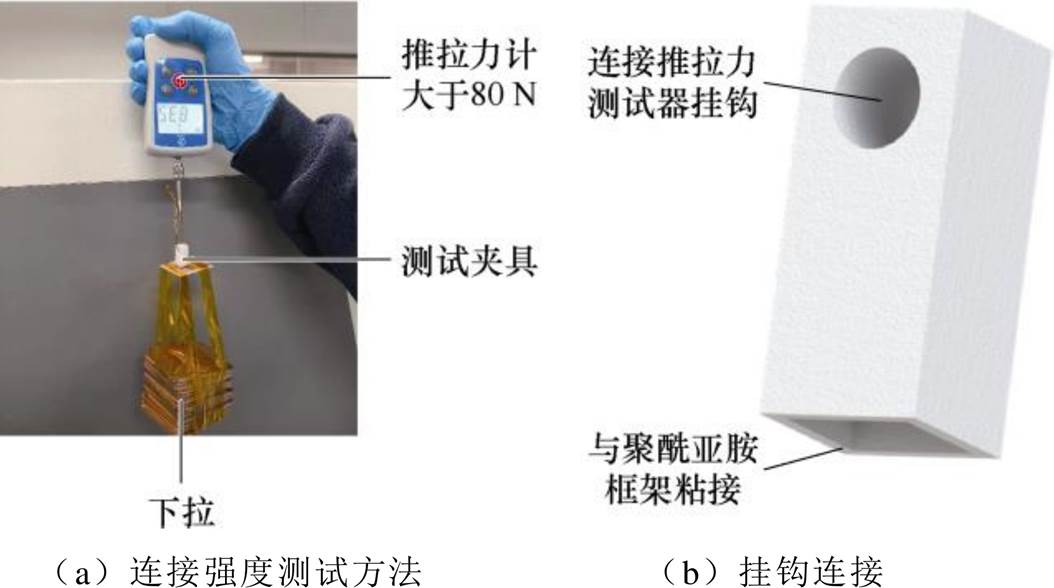

本文采用以下方法进行热测试和机械可靠性测试。首先将预制聚酰亚胺框架与芯片终端采用所提粘合剂进行粘连,然后将芯片放入温度冲击仪器中进行-70~200℃/(10 min)的温度冲击实。经过1 000次循环以后取出,采用推拉力测试仪对框架和芯片终端的粘连强度进行测量。热测试和机械可靠性测试的测试步骤如图7所示。

图7 热测试和机械可靠性测试的测试步骤

Fig.7 Test procedures for thermal testing and mechanical reliability testing

(1)将芯片与聚酰亚胺框架采用所提粘合剂进行粘连,按照最高280℃的温度曲线固化。

(2)将芯片与任意一DBC基板采用高温焊料进行焊接,便于直接施加拉力。

(3)固化完成后,放入温度冲击仪器中进行-70~200℃的温度冲击实验,这两个温度点分别保持10 min,即40 min进行一次循环,温度的切换几乎是瞬时的。设置循环数量为1 000次。

(4)设计了一个为了与推拉力测试挂钩相连的连接器如图8所示。图8b中,连接器一端被推拉力测试仪的挂钩穿过,另一端通过502强力胶水与聚酰亚胺框架的上表面粘接。涂胶水的时候需要确保胶水不会溢出框架。

(5)待胶水干透,将DBC上挂上重物以便保证竖直向下。同时,打开推拉力测试仪,设置为显示最大拉力值的模式。保持推拉力测试仪静止的同时通过重物缓慢下拉,直到将芯片与绝缘框架拉开为止,记录推拉力测试仪的数值,如图8a所示。

图8 连接强度测试方法与挂钩连接器

Fig.8 Connection strength test method and hook connector

本文制作了两种样品进行热测试和机械可靠性测试。结果显示,两个样品通过推拉力测试仪测试得到的连接力均大于80 N,连接强度大于3 MPa,该连接强度满足封装需求。

根据1.3节中的仿真结果可知,所用的绝缘框架高度为300 mm,远可以覆盖仿真中的电场强度集中位置。因此,可以在采用金属柱互联的情况下配合绝缘框架作为绝缘设计。然而,实际的15 kV高压SiC MOSFET芯片的栅极焊盘面积较小,用金属柱互联工艺难以控制,采用键合线互联较为稳妥。同时,对比键合线数量较多的芯片,较少键合线数量的芯片绝缘可靠性更高[24]。因此,考虑在采用绝缘框架的基础上,在源极采用金属柱互联,栅极采用键合线互联,能够在现有工艺水平的情况下,达到最佳的绝缘设计。

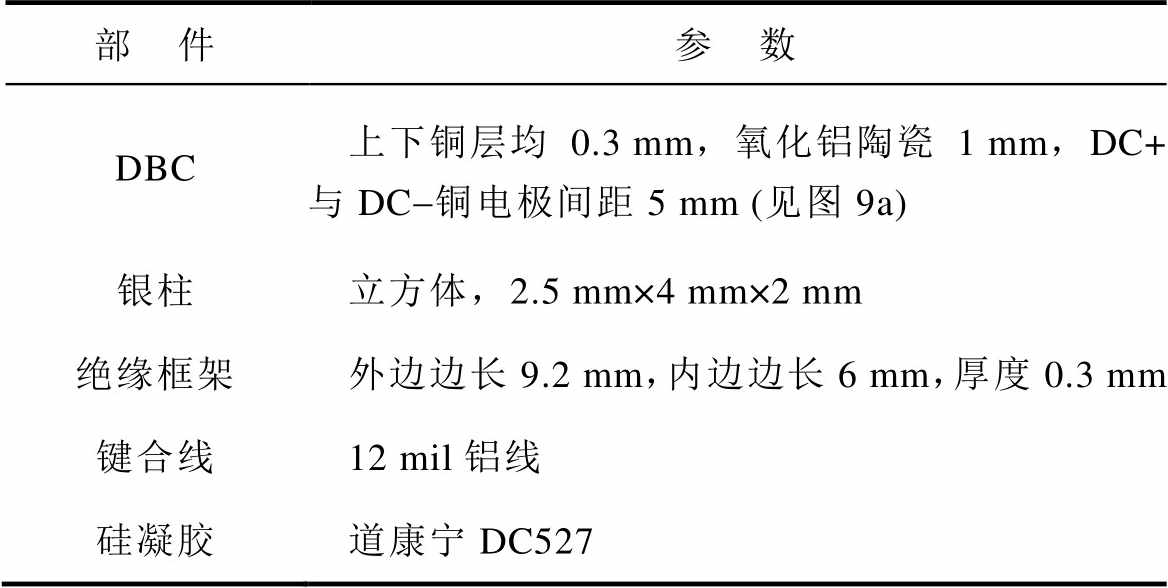

本文采用芯片上、下交错构成半桥拓扑的双面封装结构,上、下桥臂各1个芯片,采用DBC作为电气互联材料。考虑到较低的杨氏模量与较好的焊接性能,本文采用纯银作为导电金属柱;芯片在粘结上绝缘框架后,通过高温焊接材料与DBC、银柱互联;功率端子和信号端子采用纯铜材质,通过超声波焊接机与DBC互联;在焊接完成后,将其安装进对应的塑料壳体中,并填充硅凝胶。15 kV/10 A高压SiC MOSFET模块封装过程如图9所示,DBC、银柱、绝缘框架、键合线、硅凝胶的参数见表2。

图9 15 kV/10 A高压SiC MOSFET模块封装过程

Fig.9 Packaging process of 15 kV/10 A high-voltage silicon carbide MOSFET module

表2 封装参数

Tab.2 Encapsulation parameters

部 件参 数 DBC上下铜层均0.3 mm,氧化铝陶瓷1 mm,DC+与DC-铜电极间距5 mm (见图9a) 银柱立方体,2.5 mm×4 mm×2 mm 绝缘框架外边边长9.2 mm,内边边长6 mm,厚度0.3 mm 键合线12 mil铝线 硅凝胶道康宁DC527

对于本文所提的15 kV/10 A高压SiC MOSFET模块,封装过程总共包含以下四步:

(1)将绝缘框架采用本文提出的粘结材料粘结在芯片终端位置,放入温箱中在最高280℃的真空气氛下固化粘结剂。

(2)将芯片、银柱、DBC焊接在一起,并用超声波焊接机连接端子,最后完成栅极和开尔文源极的铝线键合。

(3)双DBC对焊,并且安装进塑料壳体的对应位置。

(4)灌封硅凝胶,经过100℃固化2 h。

本节中,模块在DC+与AC、AC与DC-两端子间的局部放电测试中被展示;模块的寄生电感通过AnsysQ3D仿真得到;通过在直流母线电压6、8和10 kV条件下的双脉冲实验,得到了模块的动态特性。

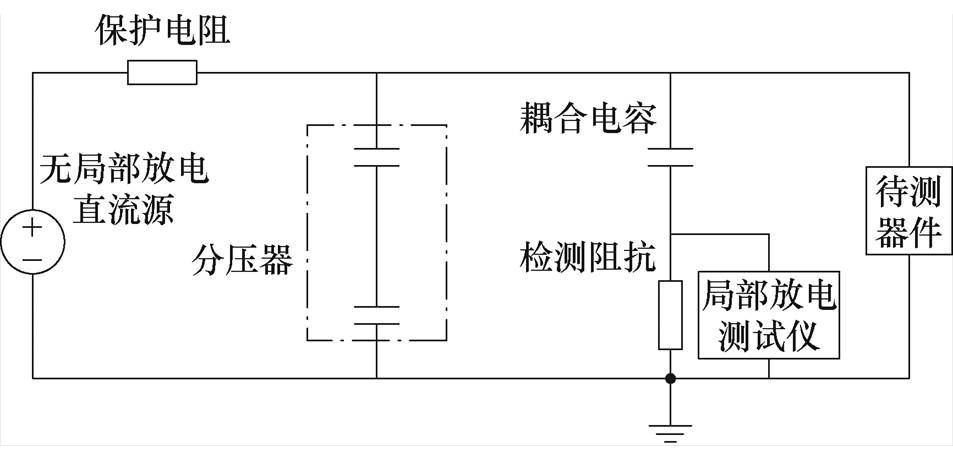

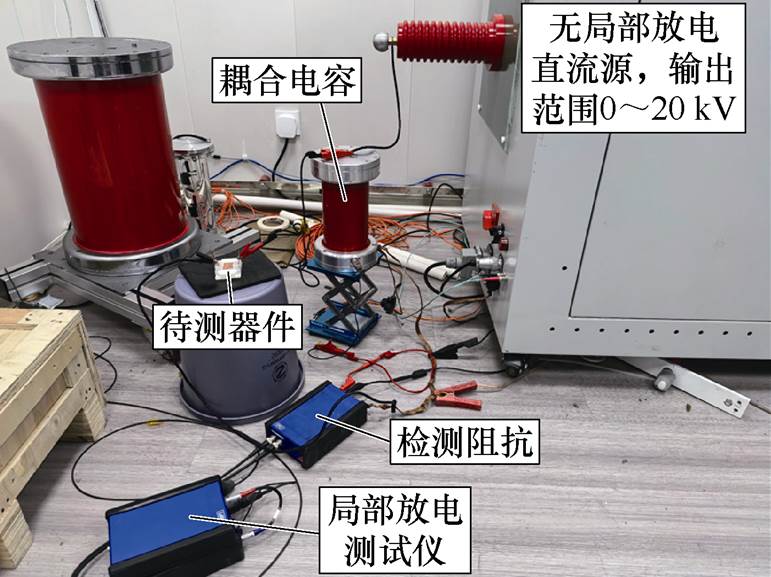

在完成封装后,对该模块进行局部放电测试。由于该芯片在接近15 kV的阻断电压下漏电流显著提升,这对测量造成较大干扰,考虑到后续双脉冲实验的需求,同时由于芯片无反向阻断电压能力,因此适当降低测试电压,设定局部放电激励电压为12 kV直流,直流测试系统接线如图10所示。

图10 直流局部放电测试系统

Fig.10 DC PD test system

模块上、下桥臂信号端子均短路,同时分别在DC+与AC、AC与DC-上加上12 kV直流电压。测试流程依据标准IEC 60270[29]。测试台架如图11所示。

图11 直流局部放电测试台架

Fig.11 DC PD test bench

经测试,DC+与AC、AC与DC-两端在12 kV直流电压激励下,10 min以内局部放电量超过10 pC和20 pC脉冲的次数,均在10个脉冲以内。局部放电实验证实了该芯片终端邻域绝缘结构和模块封装结构绝缘可靠性。

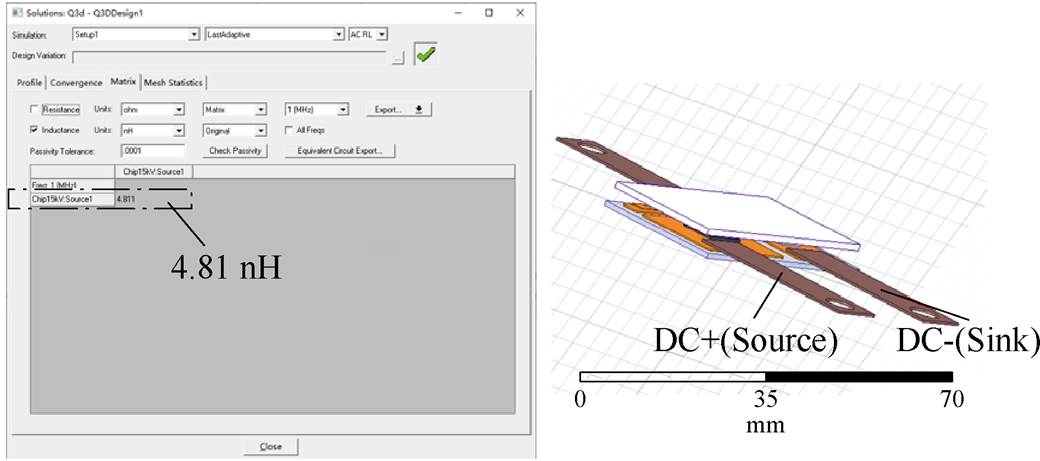

将该双面结构使用AnsysQ3D进行寄生电感提取,如图12所示,得到在1 MHz的激励源下,模块回路寄生电感为4.81 nH(含端子),较键合线互联结构有着显著的低寄生参数优势。

图12 AnsysQ3D提取寄生电感

Fig.12 AnsysQ3D extracts parasitic inductance

4.3.1 测试条件与设备选择

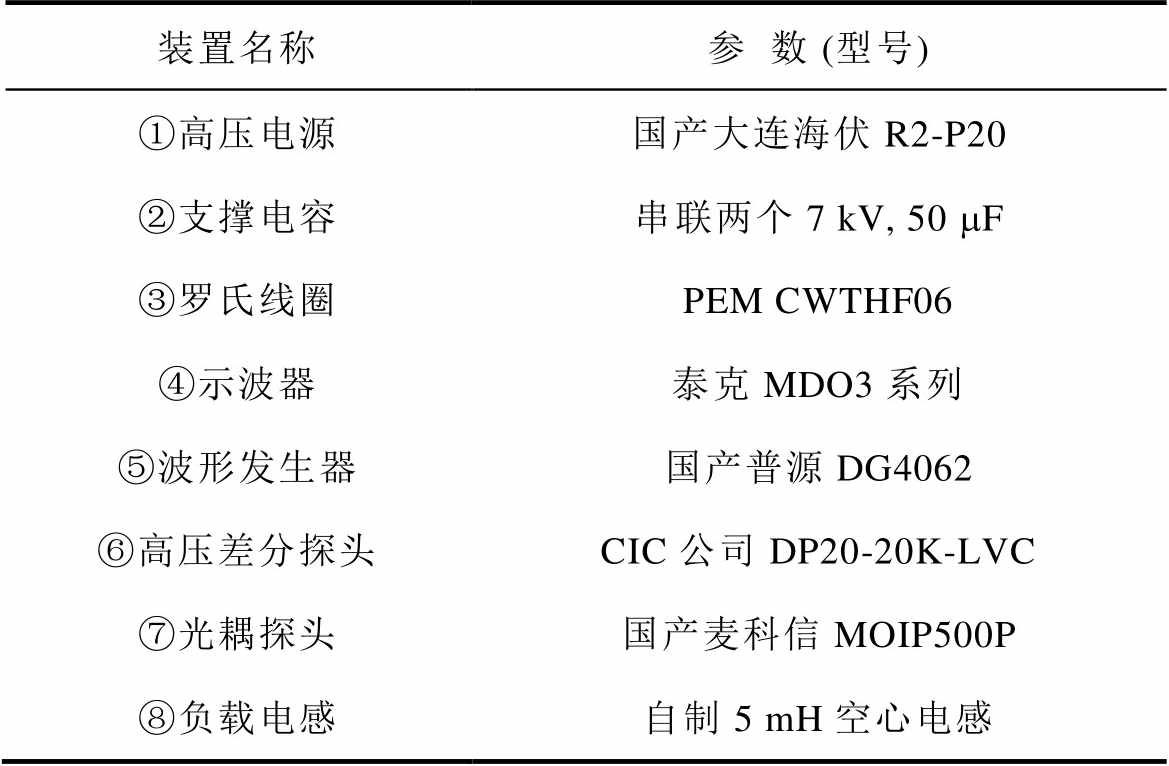

考虑到模块有较高的dV/dt,因此需要尽可能地减少测试过程中对地的耦合。本文中模块采用6、8和10 kV三个等级的直流母线电压进行测试,自制5 mH低寄生电容的空心电感作为负载,量程为20 kV的高压差分探头测量漏源电压,光耦探头测量栅极电压,采用罗氏线圈测量回路电流,这些测量设备均与大地隔离。双脉冲测试的测试参数与装备型号见表3。整体测试台架如图13所示。

表3 双脉冲测试的测试参数与装备型号

Tab.3 Test parameters and equipment model for double-pulse test

装置名称参数 (型号) ①高压电源国产大连海伏R2-P20 ②支撑电容串联两个7 kV, 50 mF ③罗氏线圈PEM CWTHF06 ④示波器泰克MDO3系列 ⑤波形发生器国产普源DG4062 ⑥高压差分探头CIC公司DP20-20K-LVC ⑦光耦探头国产麦科信MOIP500P ⑧负载电感自制5 mH空心电感

图13 双脉冲测试台架一览

Fig.13 Overview of dual-pulse test bench

4.3.2 双脉冲测试结果

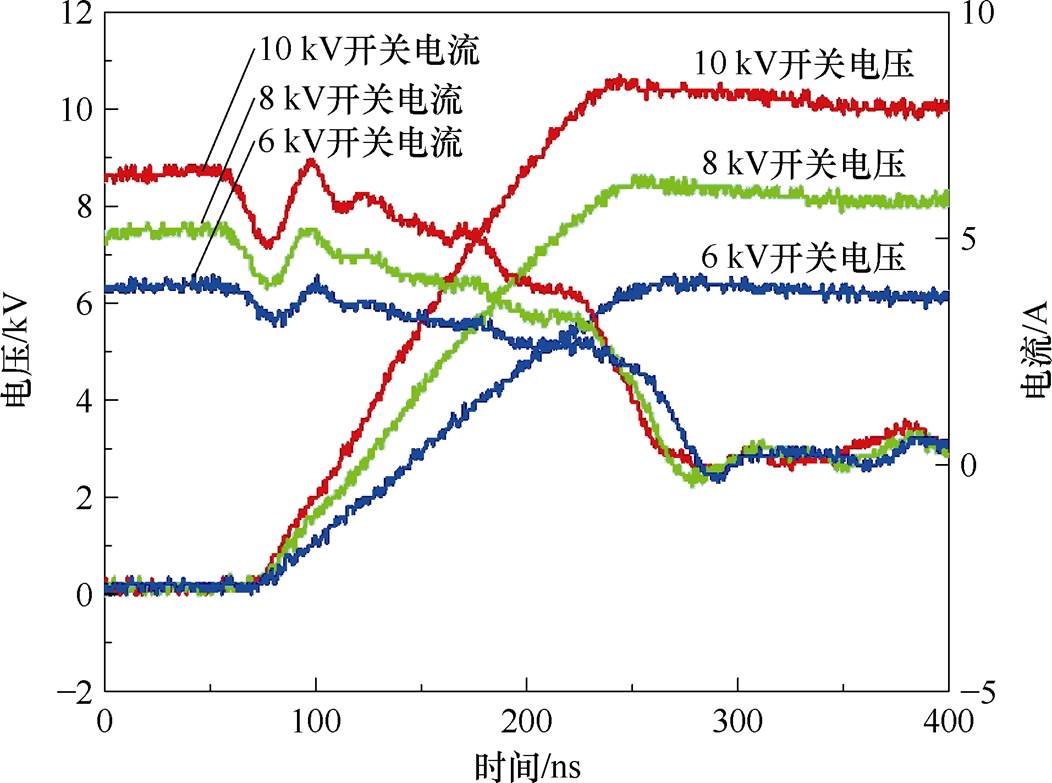

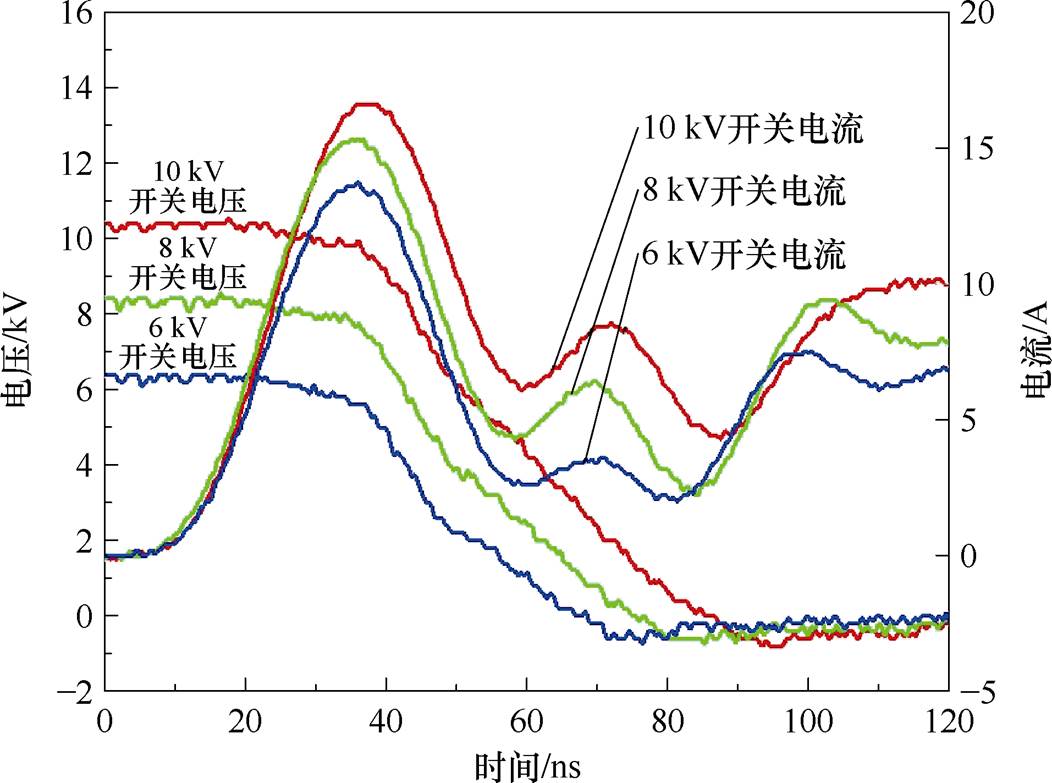

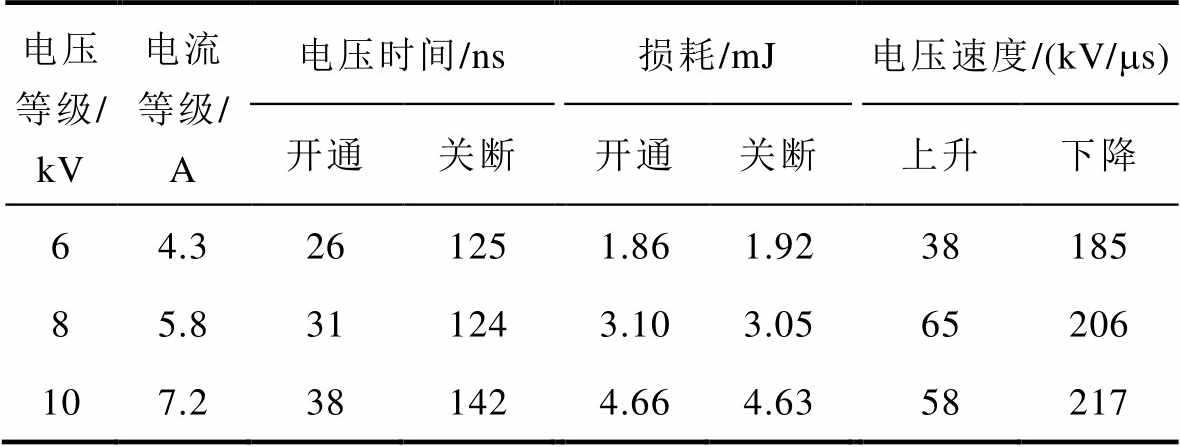

图14和图15分别为该模块在第一次关断和第二次开通的双脉冲图像。表4显示了不同电压、电流等级下模块的开关特性。其中,电压开通(关断)时间定义为90%(10%)~10%(90%)母线电压的时间,电压上升(下降)速度定义为10%(90%)~90%(10%)母线电压的电压变化率。开通损耗定义为10%导通电流到5%母线电压之间的模块损耗,关断损耗定义为10%母线电压到2%导通电流之间模块的损耗。

图14 第一次关断波形

Fig.14 The first time turn-off waveforms

图15 第二次开通波形

Fig.15 The second time turn-on waveforms

表4 模块开关特性

Tab.4 Module switch characteristics

电压等级/ kV电流等级/ A电压时间/ns损耗/mJ电压速度/(kV/ms) 开通关断开通关断上升下降 64.3261251.861.9238185 85.8311243.103.0565206 107.2381424.664.6358217

本文提出了基于15 kV高压SiC MOSFET芯片在双面封装结构下的终端邻域绝缘结构,并基于该结构设计了一款15 kV/10 A双面模块。局部放电测试证明了该绝缘结构与封装工艺的适配性和有效性。对比文献[22]方案较高的电压过冲,基于本文提出的绝缘结构封装的双面模块电压上升无明显过冲,展现出该结构较低的寄生电感,与仿真结果一致。热冲击测试证明了本文提出的粘接绝缘框架与芯片终端有可靠连接,显示了引入的新结构的热、机械可靠性。此外,双面结构给未来双面水冷散热预留了设计条件。从图14和图15可以得到,该功率模块有着较快的电压下降前沿,电压下降速度可达217 kV/ms,在高压脉冲功率发生器中有一定的应用前景。该模块在10 kV母线电压下,开关损耗一共9.29 mJ,表明其可以在较高频率下工作的同时保持较低的开关损耗,预示着可以应用到高压、高频变换器中。

本文针对15 kV/10 A高压SiC MOSFET模块封装中的芯片终端邻域电场集中问题,基于采用源极焊接金属柱的双面互联方式,提出自研高分子粘结剂与聚酰亚胺绝缘框架的封装方案,显著提升了模块的绝缘可靠性与动态性能。通过TCAD电场仿真,明确了金属柱互联情况下芯片终端邻域的电场强度分布规律。提出采用芯片终端粘接300 mm绝缘框架覆盖高电场强度区域的绝缘方案,实验表明,模块在12 kV直流电压下无局部放电。在10 kV母线电压下的动态测试中,开关速度达217 kV/ms(开通)与58 kV/ms(关断),总开关损耗仅为9.29 mJ,支持高频运行。相较于传统键合线结构,该设计通过金属柱互联工艺与优化绝缘框架,有效地抑制了电压过冲,可以为高压SiC器件在柔直输电、固态断路器及脉冲功率系统中的应用提供技术支撑。未来研究将聚焦于多芯片并联集成与双面液冷散热设计,以进一步提升模块功率密度与长期可靠性。

参考文献

[1] 王来利, 赵成, 张彤宇, 等. 碳化硅功率模块封装技术综述[J]. 电工技术学报, 2023, 38(18): 4947- 4962.

Wang Laili, Zhao Cheng, Zhang Tongyu, et al. Review of packaging technology for silicon carbide power modules[J]. Transactions of China Electro- technical Society, 2023, 38(18): 4947-4962.

[2] 杨亚宇, 邰能灵, 黄文焘, 等. 船舶中压直流综合电力系统(一): 系统结构和电力电子变换器[J]. 电工技术学报, 2024, 39(21): 6647-6665.

Yang Yayu, Tai Nengling, Huang Wentao, et al. Shipboard medium-voltage DC integrated power system i: system architecture and power electronic converter[J]. Transactions of China Electrotechnical Society, 2024, 39(21): 6647-6665.

[3] 李文艺, 王亚林, 尹毅. 高压功率模块封装绝缘的可靠性研究综述[J]. 中国电机工程学报, 2022, 42(14): 5312-5326.

Li Wenyi, Wang Yalin, Yin Yi. Review of packaging insulation reliability for high voltage power module[J]. Proceedings of the CSEE, 2022, 42(14): 5312-5326.

[4] Yan Feifei, Wang Laili, Yang Tao, et al. Design of packaging structure in high voltage power modules to avoid surface breakdown[C]//2020 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Suita, Japan, 2020: 1-5.

[5] DiMarino C M, Mouawad B, Johnson C M, et al. 10-kV SiC MOSFET power module with reduced common-mode noise and electric field[J]. IEEE Transactions on Power Electronics, 2020, 35(6): 6050-6060.

[6] Wang Liang, Zeng Zheng, Sun Peng, et al. Electric- field-dominated partial discharge in medium voltage SiC power module packaging: model, mechanism, reshaping, and assessment[J]. IEEE Transactions on Power Electronics, 2022, 37(5): 5422-5432.

[7] Yan Feifei, Wang Laili, Wang Haihua, et al. Elec- trical trees in silicone GEL influenced by different frequency and pulsewidth under unipolar high- frequency square wave voltage[J]. IEEE Transactions on Dielectrics and Electrical Insulation, 2024, 31(3): 1208-1216.

[8] Zhang Zichen, Ngo K D T, Lu Guoquan. Characteri- zation of a nonlinear resistive polymer-nanoparticle composite coating for electric field reduction in a medium-voltage power module[J]. IEEE Transactions on Power Electronics, 2022, 37(3): 2475-2479.

[9] 孟兆通, 张天栋, 张昌海, 等. 电气绝缘用非线性电导材料研究进展[J]. 电工技术学报, 2023, 38(21): 5691-5711.

Meng Zhaotong, Zhang Tiandong, Zhang Changhai, et al. Research progress of nonlinear conductive materials for electrical insulation[J]. Transactions of China Electrotechnical Society, 2023, 38(21): 5691- 5711.

[10] 王泽, 于志新, 蒋华平, 等. 高dVDS/dt下界面陷阱对碳化硅MOSFET场限环终端耐压影响研究[J/OL].电源学报, 1-7[2025-07-29]. https://link.cnki.net/ urlid/12.1420.tm.20250515.1505.010.

Wang Ze, Yu Zhixin, Jiang Huaping, et al. Study on the effect of interface traps on field limiting rings withstand voltage of silicon carbide MOSFET at high dVDS/dt[J/OL]. Journal of Power Supply, 1-7[2025- 07-29]. https://link.cnki.net/urlid/12.1420.tm.20250515. 1505.010.

[11] Ebihara K, Kawahara K, Hino S, et al. Investigation of the robust edge termination applied to 6.5kV SiC MOSFET[J]. Materials Science Forum, 2018, 924: 778-781.

[12] Cao Xiao, Wang Tao, Ngo K D T, et al. Parametric study of joint height for a medium-voltage planar package[J]. IEEE Transactions on Components and Packaging Technologies, 2010, 33(3): 553-562.

[13] 文腾. 压接型IGBT器件内部瞬态电场的计算方法及应用研究[D]. 北京: 华北电力大学, 2022.

Wen Teng. Calculation method and application of transient electric field inside press-pack IGBT device[D]. Beijing: North China Electric Power University, 2022.

[14] Johannesson D, Nawaz M, Nee H P. Assessment of junction termination extension structures for ultrahigh- voltage silicon carbide pin-diodes; a simulation study[J]. IEEE Open Journal of Power Electronics, 2021, 2: 304-314.

[15] Liu Zhaocheng, Cui Xiang, Li Xuebao, et al. A novel chip surface shielding structure for promoting insulation capability of high voltage semiconductor chip[J]. IEEE Transactions on Electron Devices, 2022, 69(1): 439-443.

[16] Sun Peiyuan, Wang Laili, Yuan Tianshu, et al. A comprehensive study on electric field coupling effects of medium-voltage SiC power module and opti- mization design[C]//2024 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 2024: 2556-2561.

[17] Passmore B, Cole Z, McGee B, et al. The next generation of high voltage (10 kV) silicon carbide power modules[C]//2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, USA, 2016: 1-4.

[18] Lin Xiang. Device voltage balancing from device- level to converter-level in high power density medium voltage converter using 10 kV SiC MOSFETs[D]. Blacksburg: Virginia Polytechnic Institute and State University, 2022.

[19] 金晓行, 李士颜, 田丽欣, 等. 6.5kV高压全SiC功率MOSFET模块研制[J]. 中国电机工程学报, 2020, 40(6): 1753-1759.

Jin Xiaoxing, Li Shiyan, Tian Lixin, et al. Development of 6.5kV high voltage all-SiC power MOSFET module[J]. Proceedings of the CSEE, 2020, 40(6): 1753-1759.

[20] 尚海, 梁琳, 王以建, 等. 6.5kV SiC MOSFET模块加权优化设计与实验研究[J]. 电工技术学报, 2022, 37(19): 4911-4922.

Shang Hai, Liang Lin, Wang Yijian, et al. Weighted optimization design and experimental study of 6.5kV SiC MOSFET module[J]. Transactions of China Electrotechnical Society, 2022, 37(19): 4911-4922.

[21] 郝凤斌, 李士颜, 杨阳, 等. 15 kV超高压SiC功率模块封装研究[J]. 电力电子技术, 2023, 57(7): 137- 140.

Hao Fengbin, Li Shiyan, Yang Yang, et al. Study on packaging of 15 kV EHV SiC power module[J]. Power Electronics, 2023, 57(7): 137-140.

[22] Pang Lei, Long Tianjun, He Kun, et al. A compact series-connected SiC MOSFETs module and its appli- cation in high voltage nanosecond pulse generator[J]. IEEE Transactions on Industrial Electronics, 2019, 66(12): 9238-9247.

[23] Ning Puqi, Liang Zhenxian, Wang Fei. Double-sided cooling design for novel planar module[C]//2013 Twenty-Eighth Annual IEEE Applied Power Elec- tronics Conference and Exposition (APEC), Long Beach, CA, USA, 2013: 616-621.

[24] Gao Yuan, Yin Kai, Bak C L, et al. Impacts of the bottom copper layer of direct-bond copper substrates on the partial discharge performance in power modules[J]. IEEE Transactions on Power Electronics, 2025, 40(4): 5999-6009.

[25] Sun Peiyuan, Wang Laili, Yuan Tianshu, et al. Comparative evaluation of 10 kV SiC MOSFET power module insulation ability through chip neighborhood range electric field modelling[C]//2024 IEEE 7th International Electrical and Energy Conference (CIEEC), Harbin, China, 2024: 5159-5164.

[26] Li Shiyan, Liu Hao, Huang Runhua, et al. Simulation, fabrication and characterization of 6500V 4H-SiC power DMOSFETs[C]//2017 14th China International Forum on Solid State Lighting: International Forum on Wide Bandgap Semiconductors China (SSLChina: IFWS), Beijing, China, 2017: 144-147.

[27] Deng Xiaochuan, Tan Ben, Li Juntao, et al. Design, fabrication and characterization of ultra-high voltage 4H-SiC MOSFET transistors[C]//2018 14th IEEE Inter- national Conference on Solid-State and Integrated Circuit Technology (ICSICT), Qingdao, China, 2018: 1-3.

[28] Koizumi A, Jun Suda, Kimoto T. Temperature and doping dependencies of electrical properties in Al-doped 4H-SiC epitaxial layers[J]. Journal of Applied Physics, 2009, 106: 013716.

[29] International Electrotechnical Commission. IEC 60270[S/OL]:[2025-06-05]. https://webstore.iec.ch/en/publication/65087.

Abstract The bottleneck hindering the application of silicon carbide (SiC) MOSFET chips at voltage levels of 10 kV and above is the lack of reliable packaging structures. Traditional insulation enhancement technologies for high-voltage silicon carbide MOSFET modules focus on the triple junction. However, the chip neighborhood is also a high-field-strength region. Currently, this issue has been identified in 6.5 kV devices, and some improved structures have been proposed. Nevertheless, for higher voltages, especially in 15 kV silicon carbide MOSFET devices, insulation design in the chip neighborhood remains unexplored. This article reports the fabrication and test results of a 15 kV/10 A high-voltage silicon carbide power MOSFET module with insulation enhancement design for the chip neighborhood.

An electric-field analysis model of the chip terminal area was established using TCAD software. Based on the electric field simulation results, it was determined that the module's source terminal would use metal pillars for interconnection rather than bonding wires to reduce the electric field intensity in this region. Additionally, a self-developed high-thermal-reliability adhesive was used to bond the polyimide frame, enhancing the insulation capability of the chip terminal area.

Partial discharge tests indicate that this structure exhibits no partial discharges under operating voltages of 12 kV. Furthermore, compared with the bonding wire structure, the metal pillar structure offers a lower parasitic inductance of 4.81 nH, preventing voltage overshoot during the module's turn-off. Under 15 kV/10 A working conditions, dynamic tests of the module show that the SiC MOSFET exhibits rapid switching characteristics. The voltage turn-on and turn-off speeds are 217 kV/ms and 58 kV/ms, respectively, and the turn-on time (turn-on loss) and turn-off time (turn-off loss) are 38 ns (4.66 mJ) and 142 ns (4.63 mJ), respectively. It is demonstrated that the 15 kV SiC power module can operate at 50 kHz while maintaining low switching losses. The 15 kV high-voltage SiC module exhibits superior dynamic performance and has significant potential for pulsed power, electrical energy conversion, and power distribution networks.

keywords:15 kV SiC MOSFET, chip neighborhood, adhesive, dual-pulse test

DOI: 10.19595/j.cnki.1000-6753.tces.250436

中图分类号:TN305.94

国家重点研发计划资助项目(2023YFB2407400)。

收稿日期 2025-03-20

改稿日期 2025-07-30

袁天舒 男,1995年生,博士研究生,研究方向为高压碳化硅功率模块封装测试。E-mail: yuantianshu@stu.xjtu.edu.cn

王来利 男,1982年生,教授,博士生导师,研究方向为电力电子封装集成。E-mail: llwang@mail.xjtu.edu.cn(通信作者)

(编辑 陈 诚)