图1 电池充电阶段

Fig.1 Battery charging stage

摘要 三相CLLC谐振变换器凭借其高效率、高功率密度和低输出纹波等优异特性,在电动汽车车载充电领域备受关注。该变换器通过切相策略,在负载电流降低时关断一个或两个桥臂,覆盖电池充电的预充电、恒流充电、恒压充电三个阶段,从而有效缓解轻载效率下降的问题。为了进一步提高变换器的效率并实现能量的双向传输,采用同步整流(SR)控制成为必要手段。该文提出一种基于扩展谐波的三相CLLC谐振变换器同步整流算法,通过分析切相策略下三种工作模式的参数特性及驱动信号差异,建立扩展谐波阻抗模型,精确计算不同工作模式下二次侧开关管的导通时间,并利用三阶拟合模型显著减少DSP的运算量。为验证所提算法的可行性,设计并搭建一台基于SiC器件的2.5 kW实验样机。实验结果表明,该算法在显著提升变换器全负载范围效率的同时,有效抑制了二次侧SiC MOSFET的发热。

关键词:三相CLLC谐振变换器 切相策略 同步整流 扩展谐波 拟合模型

三相CLLC谐振变换器因其宽增益、高效率、全负载软开关等优异性能被广泛应用于电动汽车充电领域[1-4]。随着宽禁带(Wide Band Gap, WBG)半导体器件的应用[5-6],高频GaN和SiC器件更有利于实现谐振变换器中磁性元件的集成,以实现更高的功率密度和效率。

对于中高功率级别的充电器,采用交错并联的结构是更好的选择[7-8]。与半桥和全桥结构相比,三相CLLC谐振转换器不仅可以满足高功率密度、高效率、高可靠性的需求,而且由于其输入和输出电流纹波更小,可以减小滤波器件的尺寸[9-11]。

然而,三相CLLC谐振变换器开关数量多、磁性元件多,在轻载时由于过多的开关损耗、驱动损耗和磁损耗,导致其效率下降[12]。文献[13]提出了一种适用于三相CLLC谐振变换器的切相方法,通过关断一个桥臂来减小开关损耗和磁心损耗,且无需改变变换器的开关频率。文献[14]提出了一种新型的拓扑结构,变换器可以在三相模式、单相全桥模式和单相半桥模式切换,覆盖了电池充电的三个阶段:预充电阶段、恒流充电阶段和恒压充电阶段,使得变换器能够在全负载范围保持较高的效率。然而这种结构需要增加额外的二极管来满足半桥模式,增加了系统的复杂度和额外的成本。文献[15]提出了一种基于三相CLLC谐振变换器的切相策略,在无需增加额外器件的基础上,变换器可以工作在三桥(3B)、二桥(2B)和一桥(1B)模式,显著提升了变换器轻载时的效率。

为了进一步提升变换器的效率,采用同步整流控制至关重要[16]。得益于SiC MOSFET极低的导通电阻,将二次侧的二极管替换为可控的SiC MOSFET,不仅能够实现能量的双向流动,还能进一步降低变换器的损耗。文献[17]针对谐振变换器的不同SR策略进行了全面综述和深入比较。文献[18-21]基于基波分析(Fundamental Harmonic Analysis, FHA)法建立了变换器的等效模型,对SR控制策略进行了系统研究,并提出了有效提升效率的方法。

传统上,基波分析法在谐振变换器的建模中被广泛应用,且在靠近谐振频率时具有较高的精度。然而,对于CLLC谐振变换器,当一次侧和二次侧LC谐振电路的参数不匹配时,谐振频率不再唯一,从而导致FHA模型的精度下降。文献[22]深入分析了FHA模型的局限性,并提出了一种基于扩展谐波分析(Extended Harmonics Analysis, EHA)的方法,该方法考虑了方波激励中其他奇次谐波的影响,从而更精确地计算出二次侧谐振电流的过零点。文献[23]介绍了一种基于GaN器件的半桥LLC转换器的数字SR控制策略,该策略采用扩展谐波阻抗模型来精确计算导通时间,将转换器的效率提升至98.1%。然而,针对三相CLLC谐振变换器的SR控制策略研究仍然较少,尤其是在切相策略下适应不同工作模式的SR方案尚未广泛研究。

针对上述问题,本文提出了一种基于扩展谐波的三相CLLC谐振变换器同步整流算法。针对切相策略下的不同工作模式,建立了扩展谐波阻抗模型,综合考虑了死区时间的影响,精确计算出不同工作模式二次侧MOSFET的导通时间,从而实现了变换器在全负载范围内的效率提升。此外,利用Matlab对计算所得的导通时间进行拟合,进一步降低了DSP的运算量。最后,通过搭建实验样机验证了所提算法的可行性。

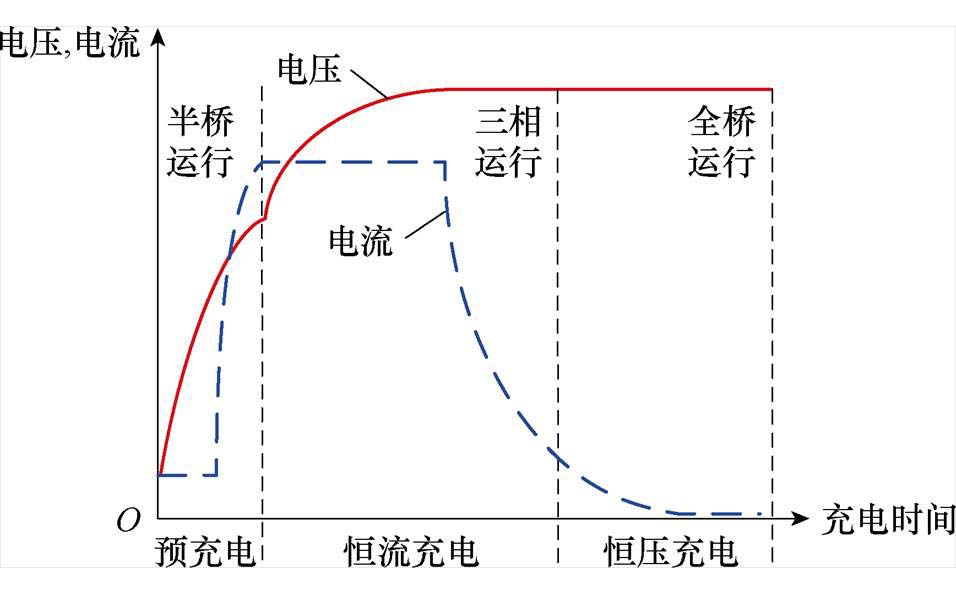

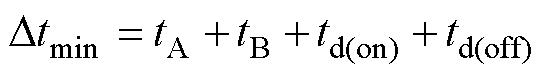

电池充电阶段如图1所示,电动汽车电池充电的过程可以分为三个阶段:预充电阶段、恒流充电阶段和恒压充电阶段。三相CLLC谐振变换器可以通过切相策略,工作在半桥运行、三相运行和全桥运行和模式来覆盖电池充电的三个阶段,使变换器在全负载范围内保持较高的效率运行。

图1 电池充电阶段

Fig.1 Battery charging stage

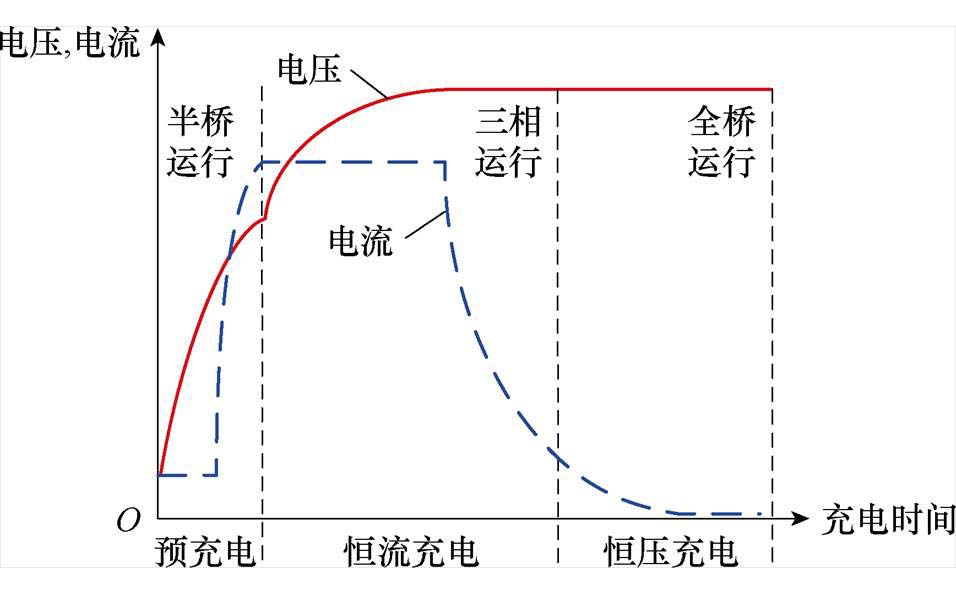

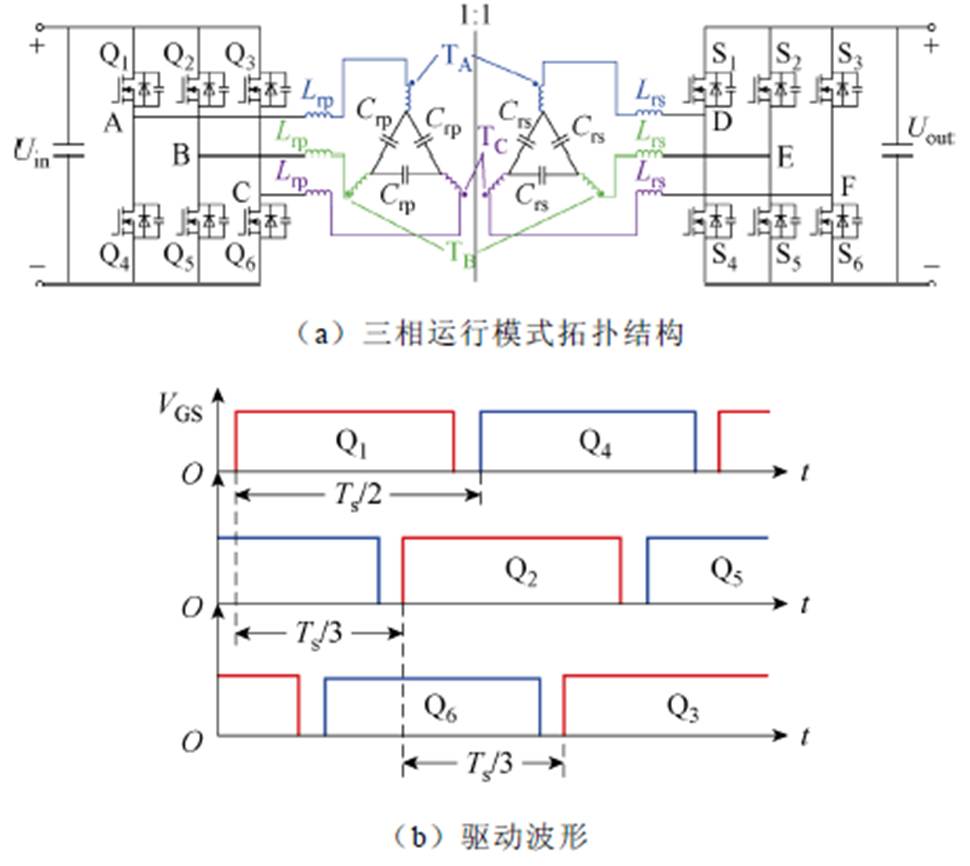

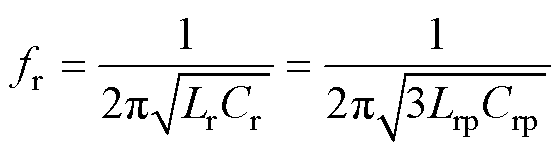

在恒流充电阶段,谐振变换器以三相模式运行,三个桥臂驱动信号彼此相差120°,每个桥臂的上、下管驱动信号以180°互补导通。拓扑结构和驱动波形如图2所示。图2中,Q1~Q6为一次侧开关管,S1~S6为二次侧开关管,TA、TB、TC为变压器,Lrp、Lrs分别为一、二次侧谐振电感,Crp、Crs分别为一、二次侧谐振电容,Ts为开关周期。在此阶段,变换器为电池提供恒定的大电流,使电池电压迅速上升。通过三相模式分担负载,降低开关器件的导通损耗,从而提高效率。同时,谐振电容以三角形联结方式,有效地解决了三相CLLC谐振变换器的均流问题。此外,由于谐振电容没有直流偏置,有助于实现平稳的软启动过程[13]。

图2 三相运行模式(恒流充电阶段)

Fig.2 Three-phase operating mode (constant current charging stage)

本文采用的变压器电压比为1 1,一、二次侧结构完全对称,故谐振电感Lr=Lrp=Lrs,由于谐振电容采用三角形联结,其值为星形联结的1/3,故谐振电容Cr=3Crp,三相运行模式时,谐振频率fr满足

1,一、二次侧结构完全对称,故谐振电感Lr=Lrp=Lrs,由于谐振电容采用三角形联结,其值为星形联结的1/3,故谐振电容Cr=3Crp,三相运行模式时,谐振频率fr满足

(1)

(1)

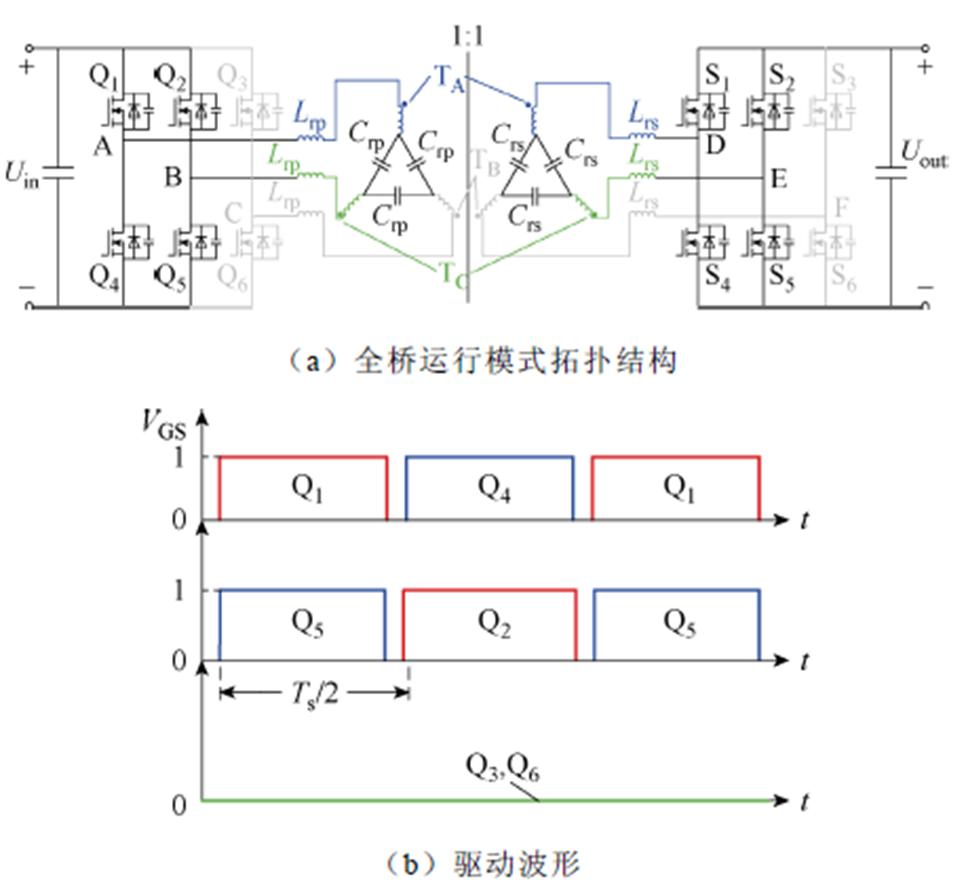

当电池容量达到70%~90%时,为防止过充并降低电池的热损伤风险,充电过程进入恒压阶段。在此阶段,电池电压保持恒定,充电电流逐渐减少,最终达到轻负载状态。图3给出了恒压充电阶段的拓扑结构和驱动信号波形。在这个阶段,C相的一、二次侧桥臂停止工作,其他两个桥臂的驱动信号以180°相移的方式导通。此时,拓扑结构类似于全桥谐振变换器。

图3 全桥运行模式(恒压充电阶段)

Fig.3 Full-bridge operating mode (constant voltage charging stage)

图3a可知,当变换器切换为全桥运行模式时,其等效谐振电感Lr2和谐振电容Cr2分别为

(2)

(2)

故此时全桥运行模式的谐振频率fr2为

(3)

(3)

对比式(1)可知,三相运行模式和全桥运行模式的谐振频率相同,因此切相后谐振变换器无需改变开关频率。

当电池电压保持恒定,充电电流开始减小至轻载条件时,切相策略可以通过减少开关器件和磁性元件的数量来提高效率,因为一个桥臂被关闭,不再承担负载,故没有电流通过,从而减少了开关损耗、驱动损耗和磁性元件的磁心损耗和绕组损耗。

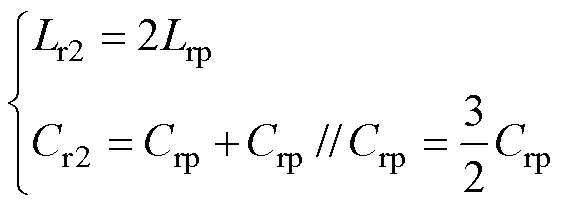

当电池完全放电时,其内部的化学状态可能变得不稳定。如果直接用大电流充电,可能会对电池造成损害,甚至带来安全隐患。因此,预充电阶段通过提供低电压和低电流逐渐“唤醒”电池。图4给出了预充电时的拓扑结构:在关闭C相的基础上,保持B相的Q5导通,Q2关断,此时拓扑结构类似半桥电路,变换器的增益为全桥变换器的一半。通过半桥运行模式,能够有效地将电池从完全放电状态恢复到正常状态,为更高效的充电阶段做准备。

图4 半桥运行模式(预充电阶段)

Fig.4 Half-bridge operating mode (pre-charging stage)

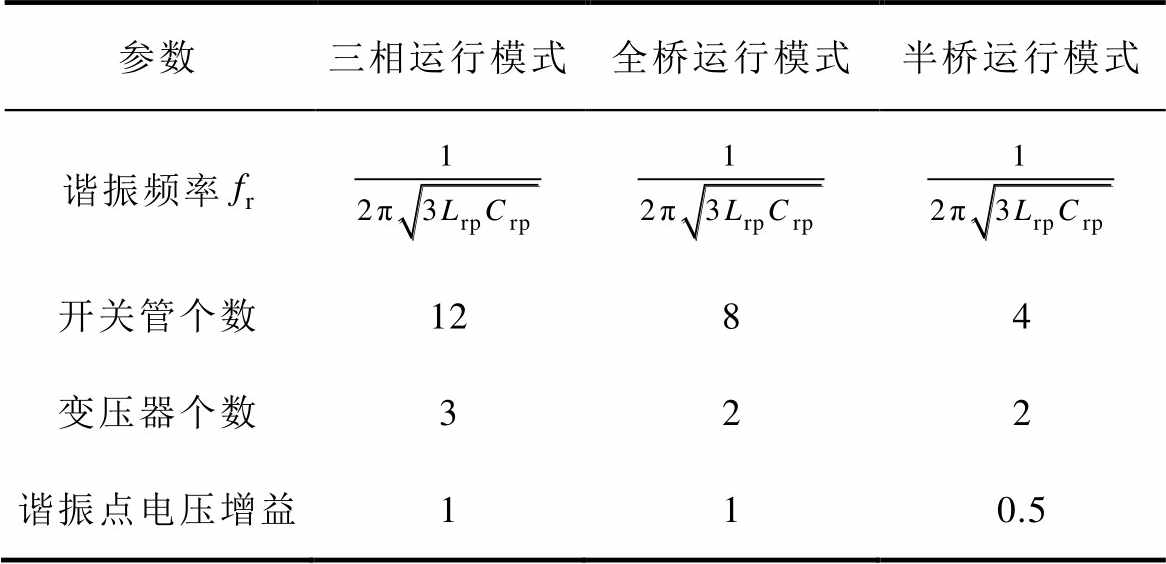

半桥模式在全桥模式的基础上,进一步减少了开关器件和驱动电路的数量,且谐振频率仍保持不变。因此当负载更轻时,切换到半桥运行,可以进一步提升变换器的效率。三种运行模式参数的对比见表1。

表1 三种运行模式参数对比

Tab.1 Comparison of parameters for three operating modes

参数三相运行模式全桥运行模式半桥运行模式 谐振频率fr 开关管个数1284 变压器个数322 谐振点电压增益110.5

SiC MOSFET的体二极管具有较高的压降和较长的反向恢复时间,但其导通电阻仅为几十mW。因此,通过对二次侧的SiC MOSFET(以下简称SR MOSFET)施加驱动信号,可以进一步提高变换器的效率。此外,同步整流控制必须适用于电池充电的各个阶段。本节基于扩展谐波分析法,提出了一种适用于不同工作模式的SR控制方法,且适用于经过切相策略后的所有运行模式,包括三相模式、全桥模式和半桥模式。

通常情况下,SR MOSFET的驱动存在以下四种状态:①延迟开通;②提前关断;③提前开通;④延迟关断。如果关断时间提前,电流将从SR MOSFET的体二极管流过,导通损耗将会增加。同样,如果延迟导通,电流也将流过体二极管。晚开通和早关断只会牺牲变换器效率,并不会影响变换器的正常运行[17]。然而,当SR MOSFET提前开通和延迟关断时,则输出电容放电,导致输出电流反向流过SR MOSFET传输到一次侧,这种能量反向会产生环流,严重时导致电路中的元器件击穿,因此应当避免这两种状态。

图5显示了SR MOSFET的理想导通波形。通常情况下,当流入SR MOSFET的电流为正时,应使其导通;当流入电流为负时,应使其关断。由于流入SR MOSFET的电流近似呈正弦,在电流开始和过零时幅值较小,因此轻微的导通延迟或提前关断对变换器效率的影响可以忽略不计[17]。因此,SR MOSFET可以与一次侧MOSFET实现同步导通[19, 21-22],通过计算导通时间ton,确定SR MOSFET的关断时刻。

图5 SR MOSFET理想导通波形

Fig.5 Ideal conduction waveforms of SR MOSFET

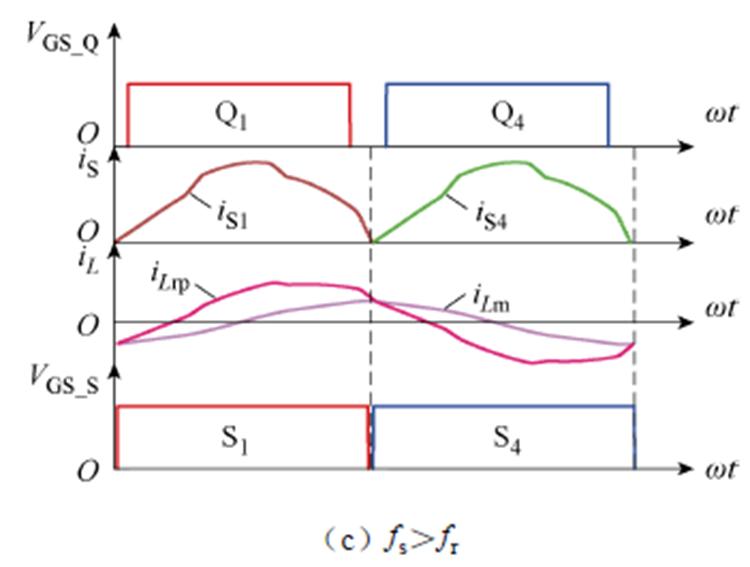

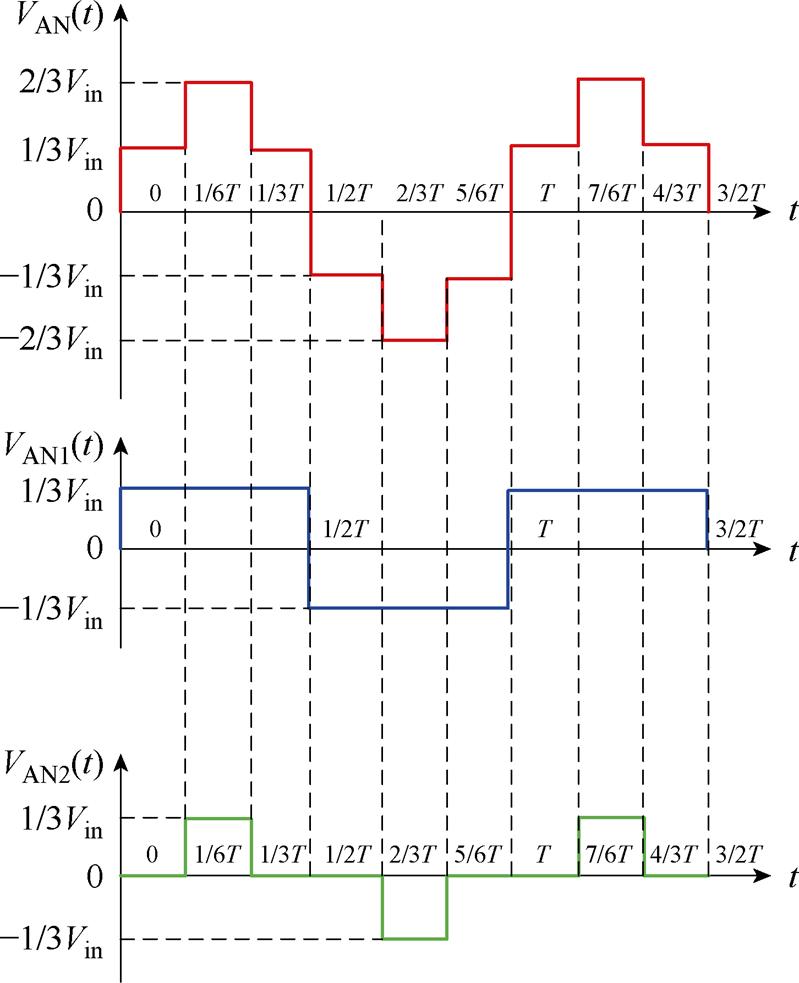

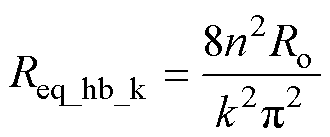

图6给出了变换器在三相模式时基于扩展谐波的等效电路模型。图6中,Req_3ph_k为三相运行模式下二次侧折合到一次侧的等效负载,Z1k为二次侧谐振电感Lrs、谐振电容3Crs和Req_3ph_k的串联阻抗,Z2k为励磁电感Lm和Z1k的并联阻抗,Z3k为谐振变换器输入阻抗。其输入信号为阶梯型方波信号VAN(t)。三相模式输入电压波形如图7所示,VAN(t)可以被拆分为两个频率和幅值相同的周期性方波信号VAN1(t)和VAN2(t)。

图6 三相模式扩展谐波阻抗模型

Fig.6 Three-phase operating mode EHA model

图7 三相模式输入电压波形

Fig.7 Three-phase mode input voltage waveforms

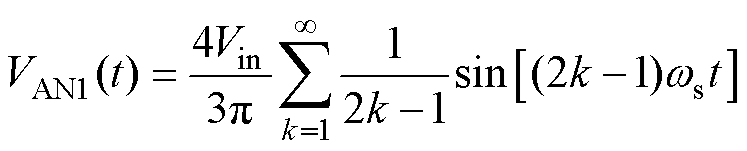

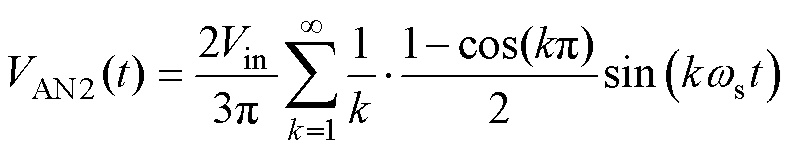

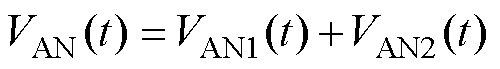

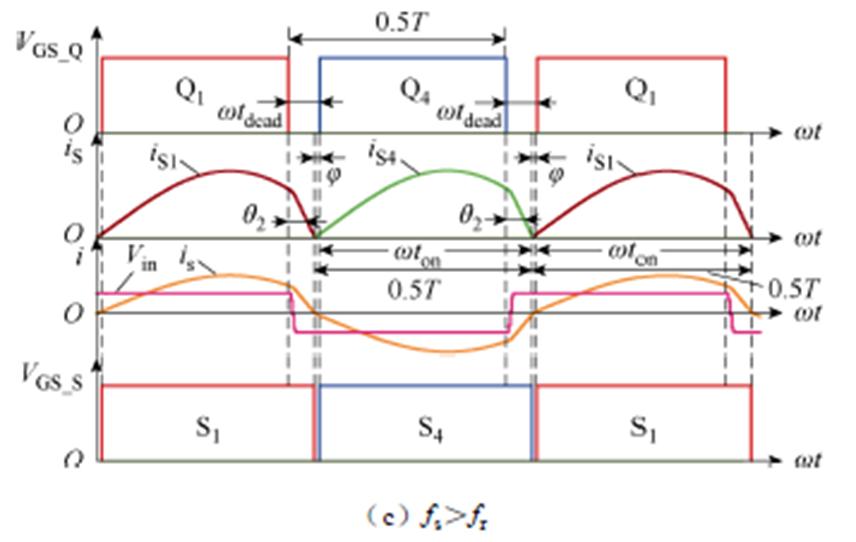

对VAN1(t)和VAN2(t)分别进行傅里叶级数展开可得

(4)

(4)

(5)

(5)

(6)

(6)

式中,ws为变换器的工作角频率;Vin为CLLC输入电压。

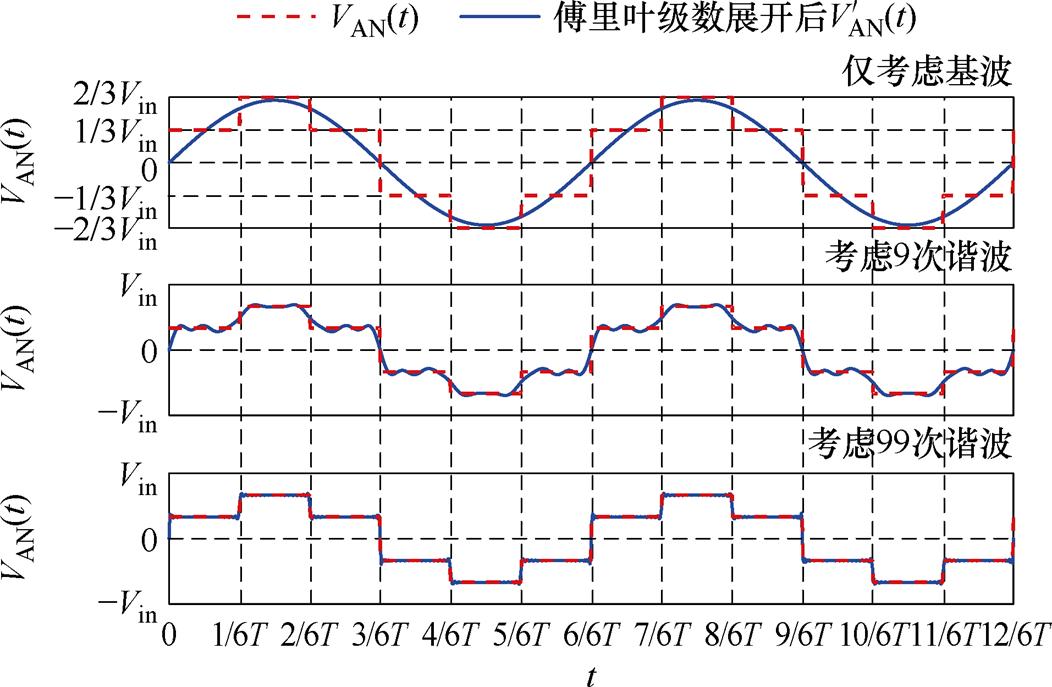

图8给出了经过傅里叶级数展开后,仅考虑基波、9次谐波和99次谐波时的波形与原始阶梯波VAN(t)的对比。可以看出,随着谐波成分数量的增加,重构的信号逐渐逼近原始方波信号。这表明,引入更多高次谐波能够更准确地还原原始方波信号,故其相较于FHA模型的计算,在偏离谐振点时依然会有较高的精度。

图8 傅里叶级数展开后输入电压波形

Fig.8 Input voltage waveforms after Fourier series expansion

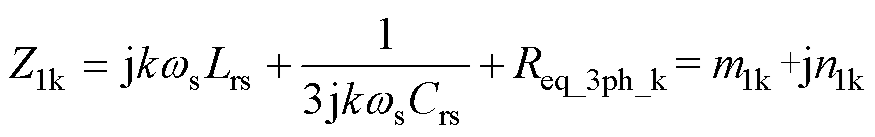

根据图6所示的三相模式EHA模型,可以计算出阻抗Z1k为

(7)

(7)

其中

(8)

(8)

(9)

(9)

式中,Ro为输出负载。

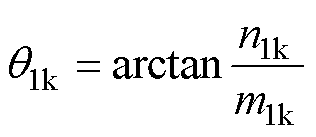

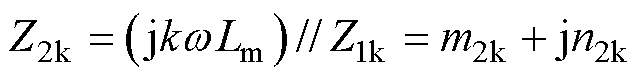

Z1k的阻抗角q1k为

(10)

(10)

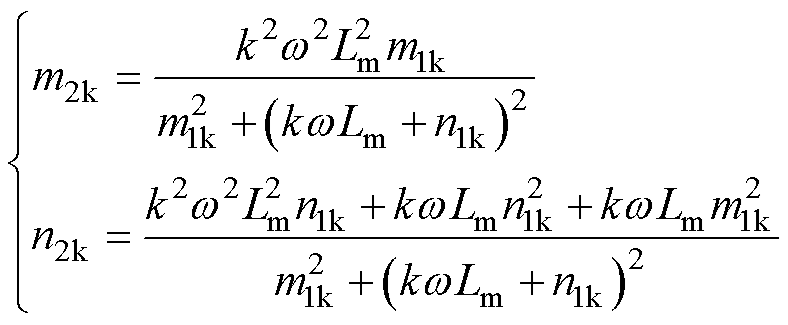

阻抗Z2k为

(11)

(11)

其中

(12)

(12)

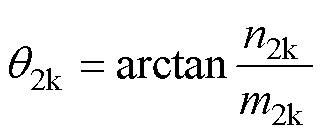

Z2k的阻抗角q2k为

(13)

(13)

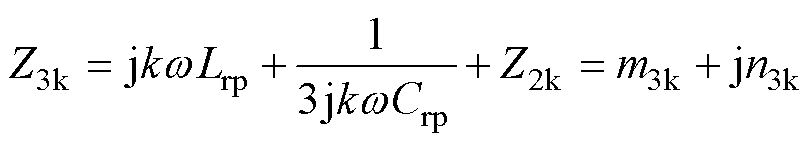

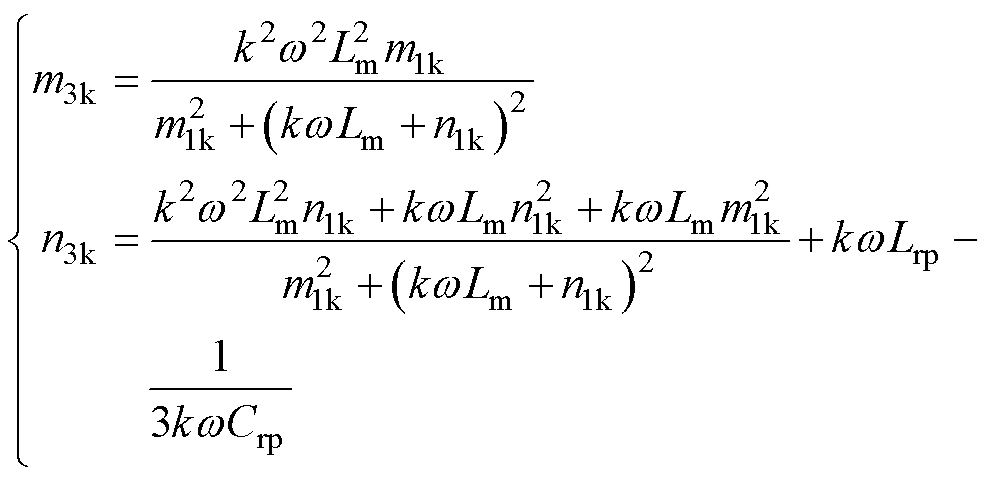

阻抗Z3k为

(14)

(14)

其中

(15)

(15)

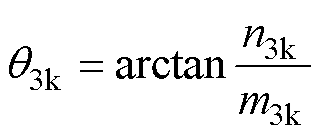

Z3k的阻抗角q3k为

(16)

(16)

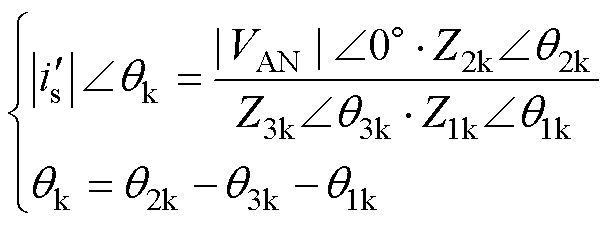

不妨设输入阶梯波电压的相位为0°,则可以根据扩展谐波阻抗模型,计算出二次侧等效到一次侧的谐振电流 为

为

(17)

(17)

通过叠加定理,可求解时域下二次侧谐振电流为

(18)

(18)

式中,Is为谐振电流的有效值。

为了求解输入信号和谐振电流的相位差q,可以通过令 =0并利用Matlab计算其过零点实现。

=0并利用Matlab计算其过零点实现。

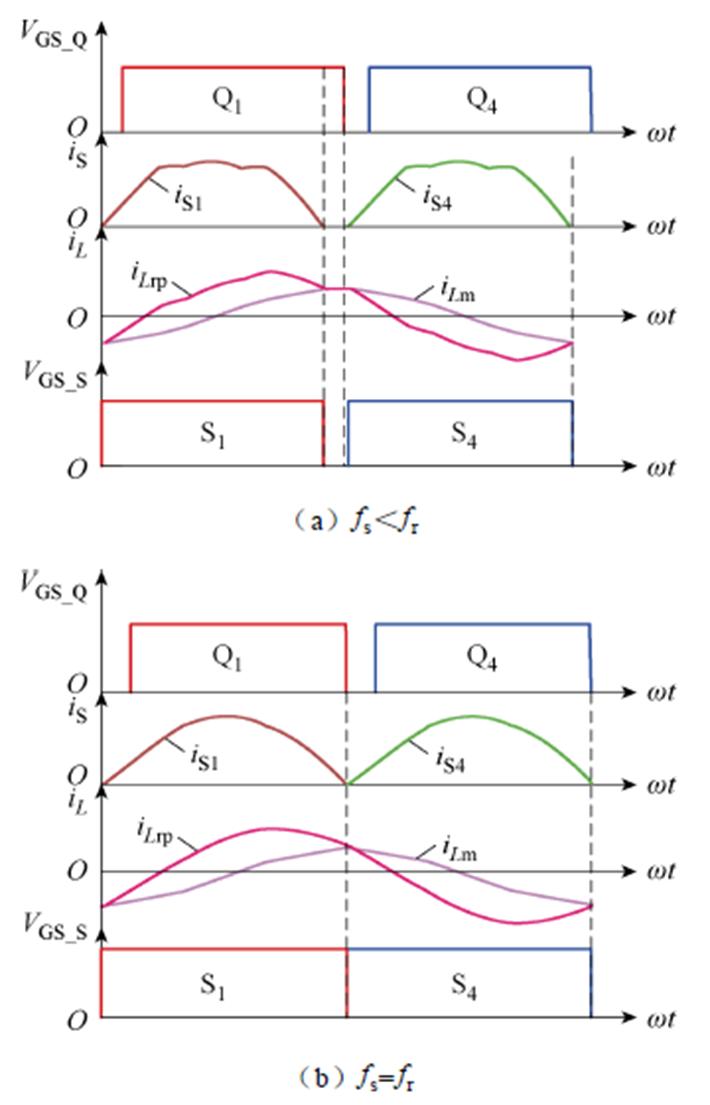

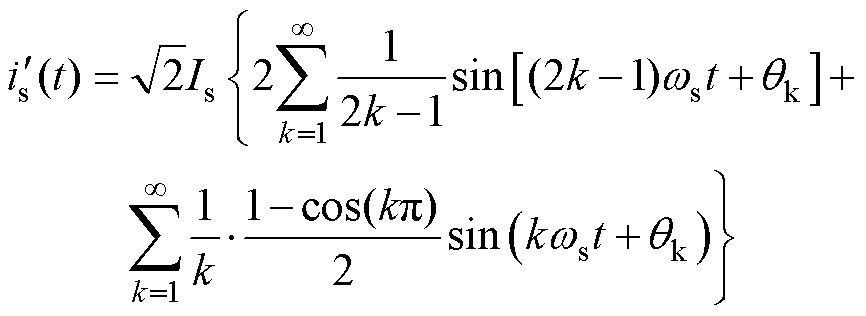

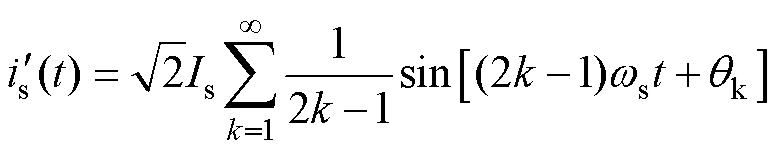

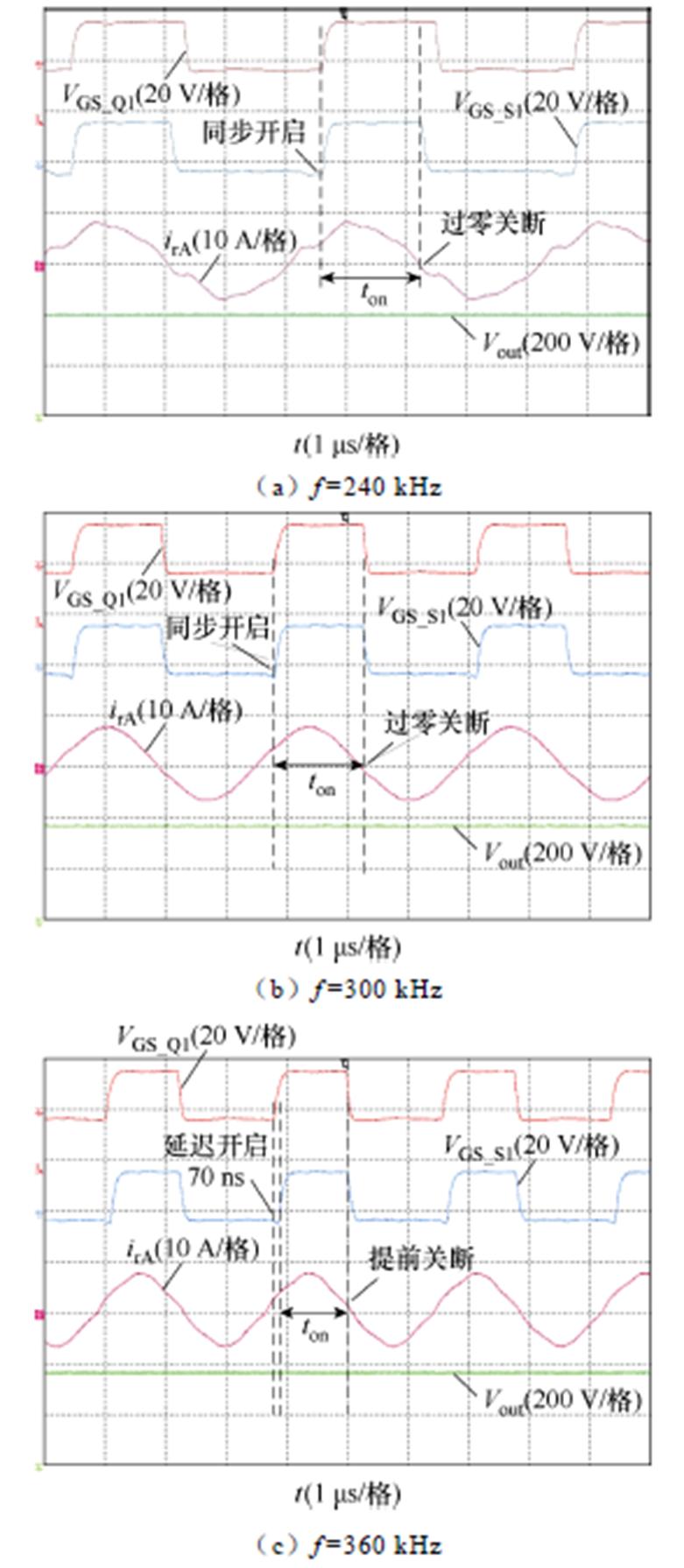

设二次侧谐振电流的过零点与SR MOSFET开通时刻的相位差为j,结合图9所示三相模式不同频率SR MOSFET重要波形可以得到

(19)

(19)

式中,fs为变换器工作频率;tdead为死区时间。

图9 三相模式不同频率SR MOSFET重要波形

Fig.9 Important waveforms of SR MOSFET in three-phase mode with different frequencies

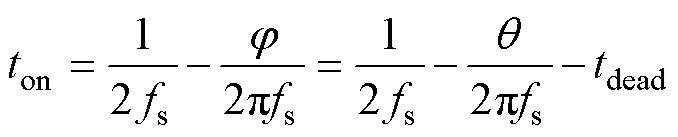

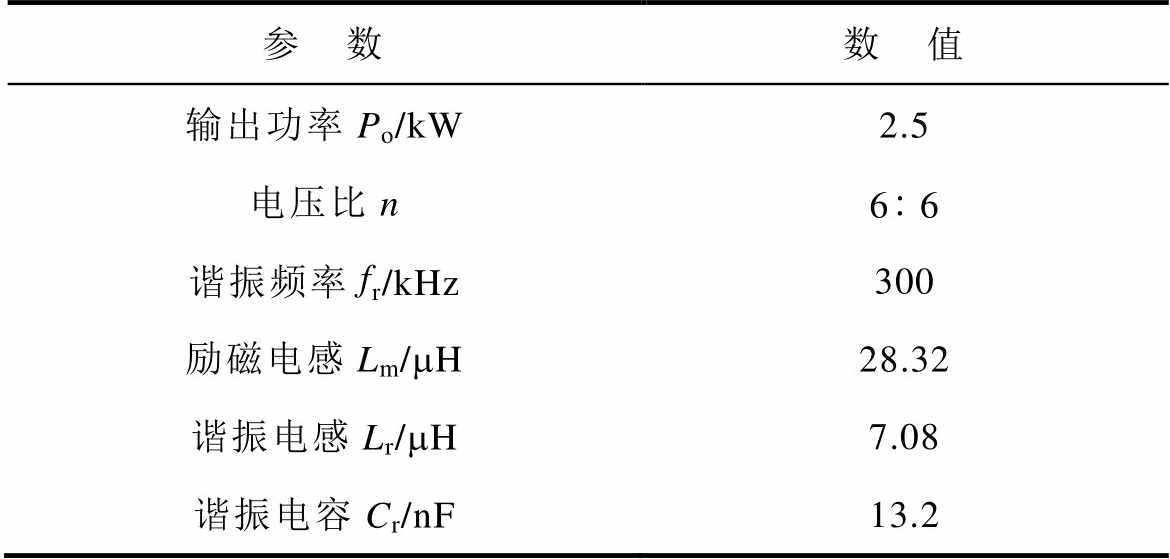

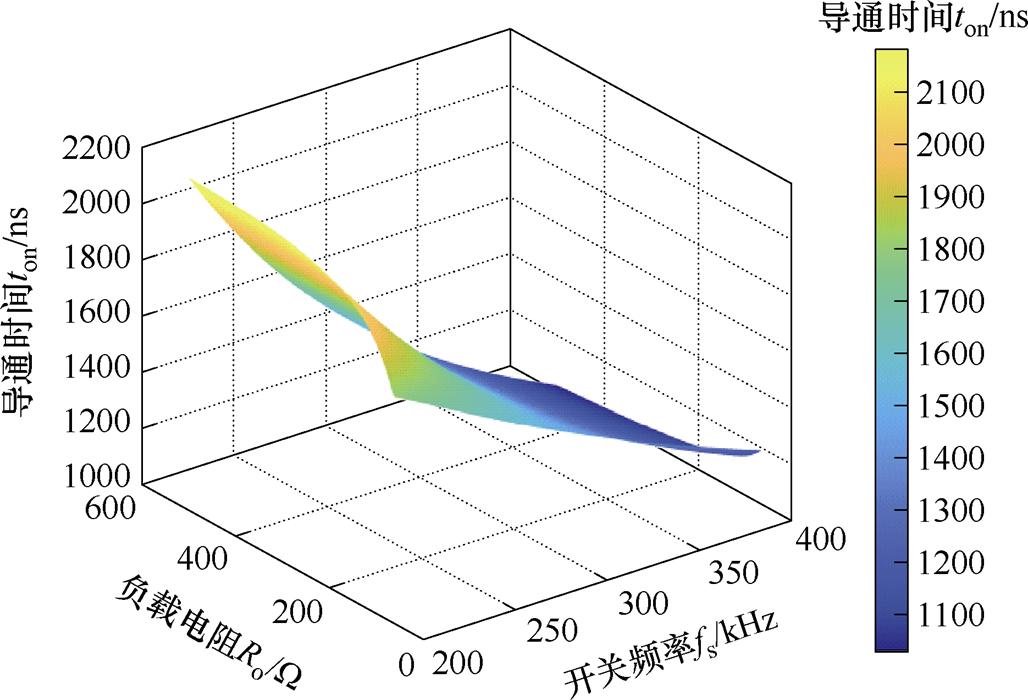

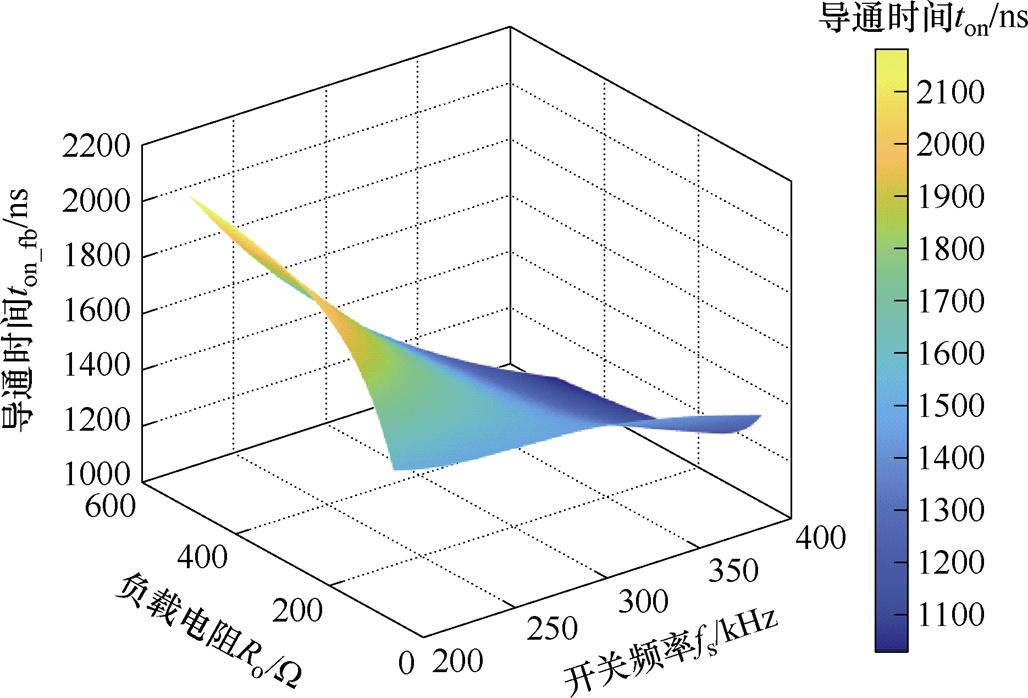

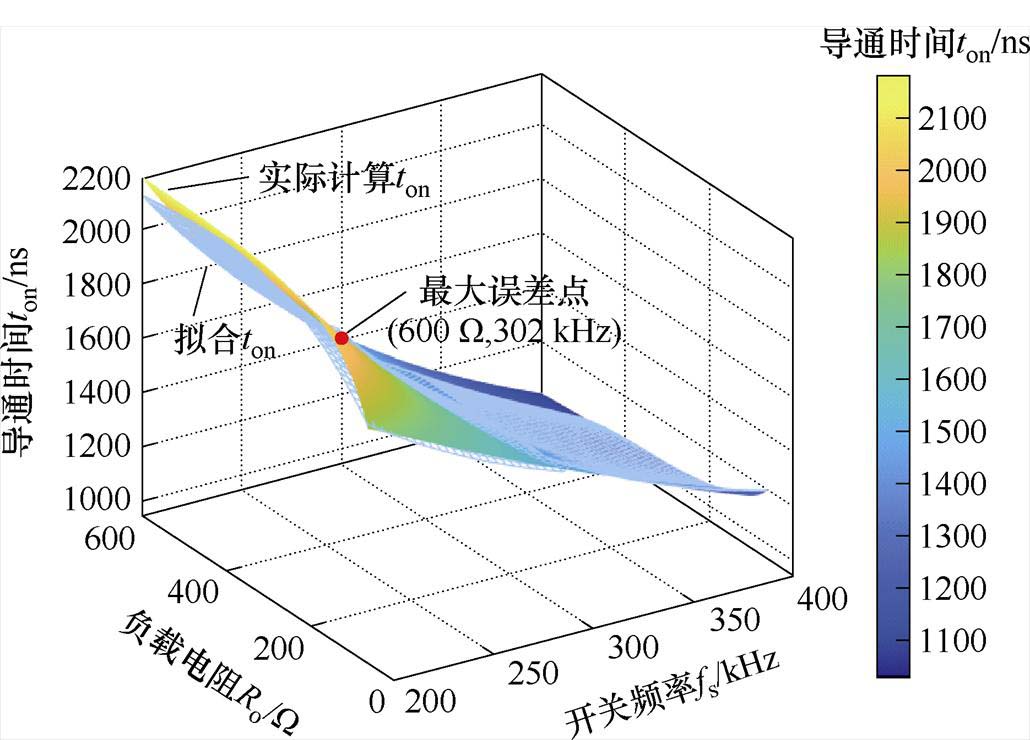

由式(7)~式(19)可知,q由变换器谐振参数和等效负载决定,当谐振参数确定后,导通时间ton仅和开关频率fs和输出负载Ro有关。本文所设计的变换器参数见表2,代入式(19)可得到导通时间与开关频率和输出负载的关系如图10所示。

表2 变换器参数

Tab.2 The parameters of the converter

参 数数 值 输出功率Po/kW2.5 电压比n66 谐振频率fr/kHz300 励磁电感Lm/mH28.32 谐振电感Lr/mH7.08 谐振电容Cr/nF13.2

图10 SR MOSFET ton与fs和Ro的关系

Fig.10 The relationship between SR MOSFET ton,fs and Ro

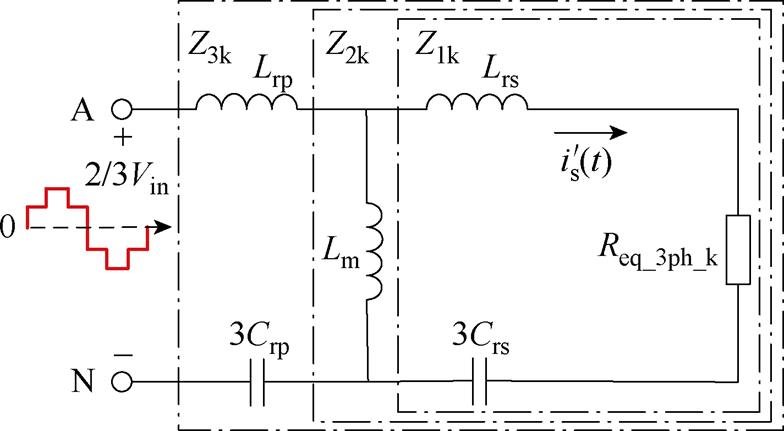

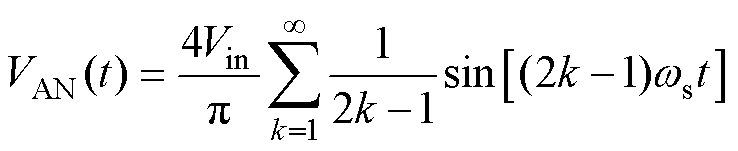

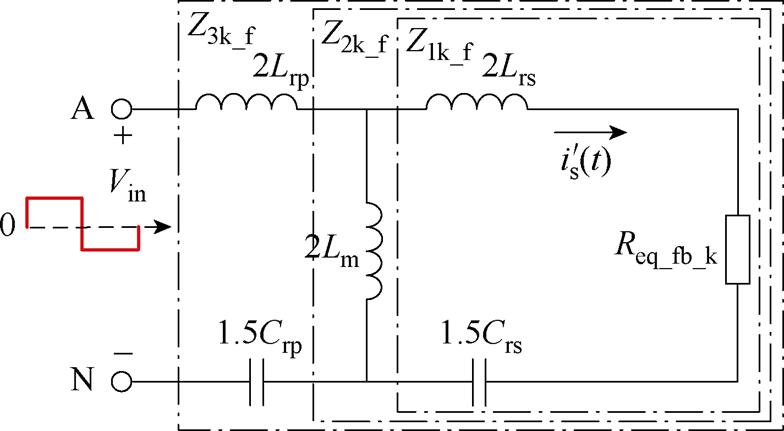

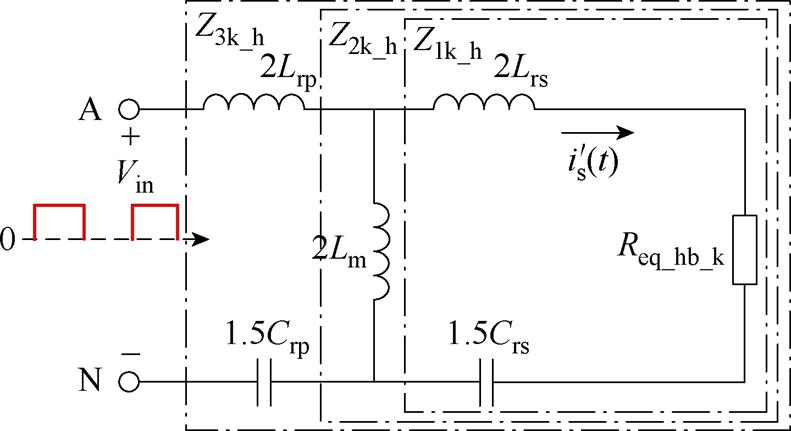

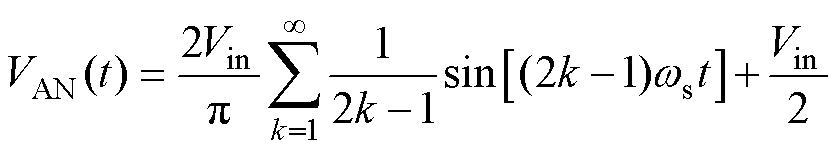

图11给出全桥模式扩展谐波阻抗模型。图11中,Req_fb_k为全桥运行模式下二次侧折合到一次侧的等效负载,Z1k_f为二次侧谐振电感Lrs、谐振电容1.5Crs和Req_fb_k的串联阻抗,Z2k_f为励磁电感2Lm和Z1k_f的并联阻抗,Z3k_f为谐振变换器输入阻抗。输入信号VAN为方波信号,经过傅里叶级数展开 后,得

(20)

(20)

图11 全桥模式扩展谐波阻抗模型

Fig.11 Full-bridge operating mode EHA model

Req_fb_k表示为

(21)

(21)

通过对比三相模式下的扩展谐波阻抗模型可以发现,在切相后,全桥模式下的一、二次侧谐振电容减小为原来的1/2,而谐振电感增大为原来的2倍。根据式(7)~式(19)中关于三相模式阻抗的计算方法,可以进一步计算全桥模式下的二次侧谐振电流为

(22)

(22)

同理,可以令 =0,求解出全桥模式下输入信号和谐振电流的相位差

=0,求解出全桥模式下输入信号和谐振电流的相位差 。

。

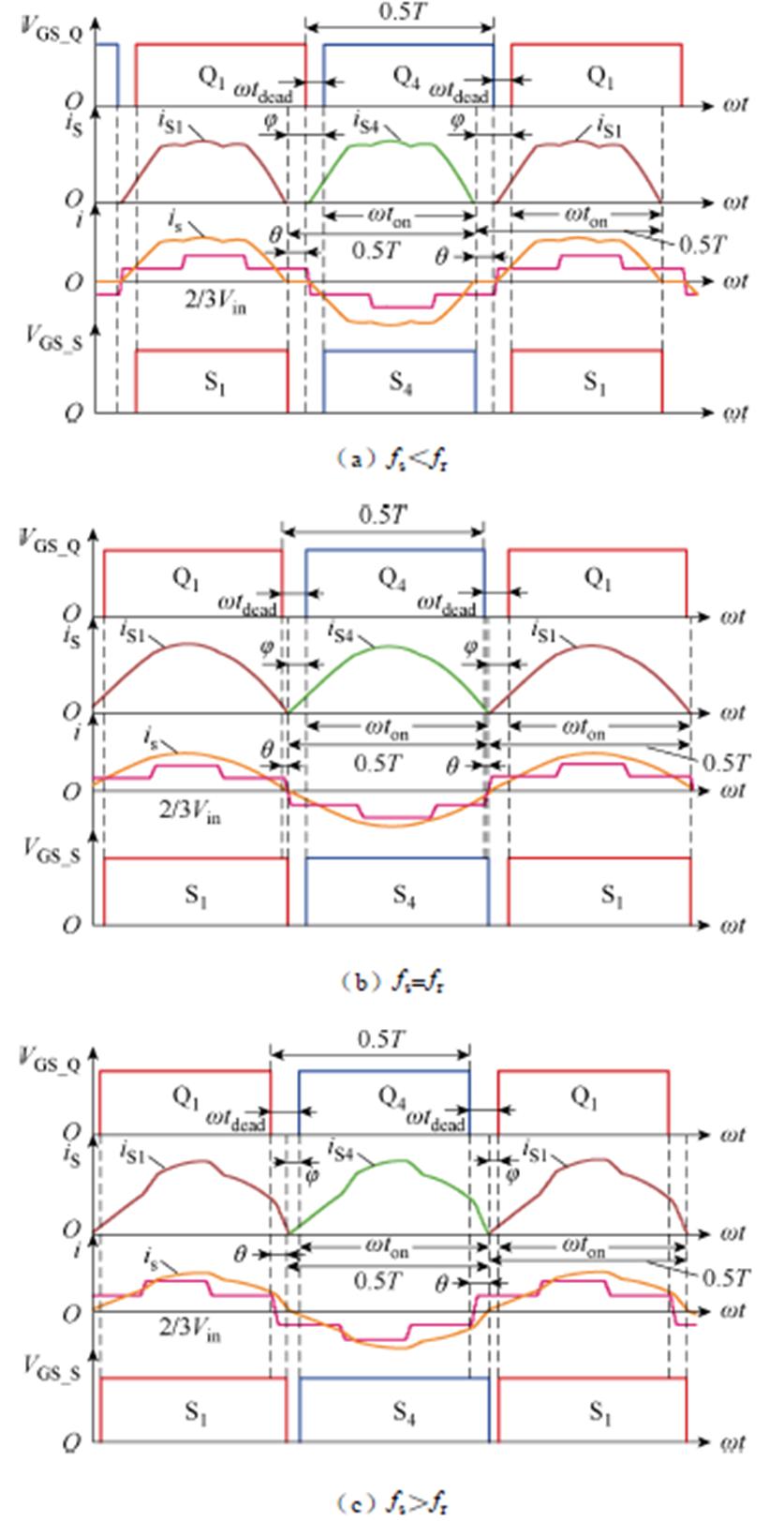

令 =0可以求解其过零点,从而得到全桥模式输入信号和谐振电流的相位差

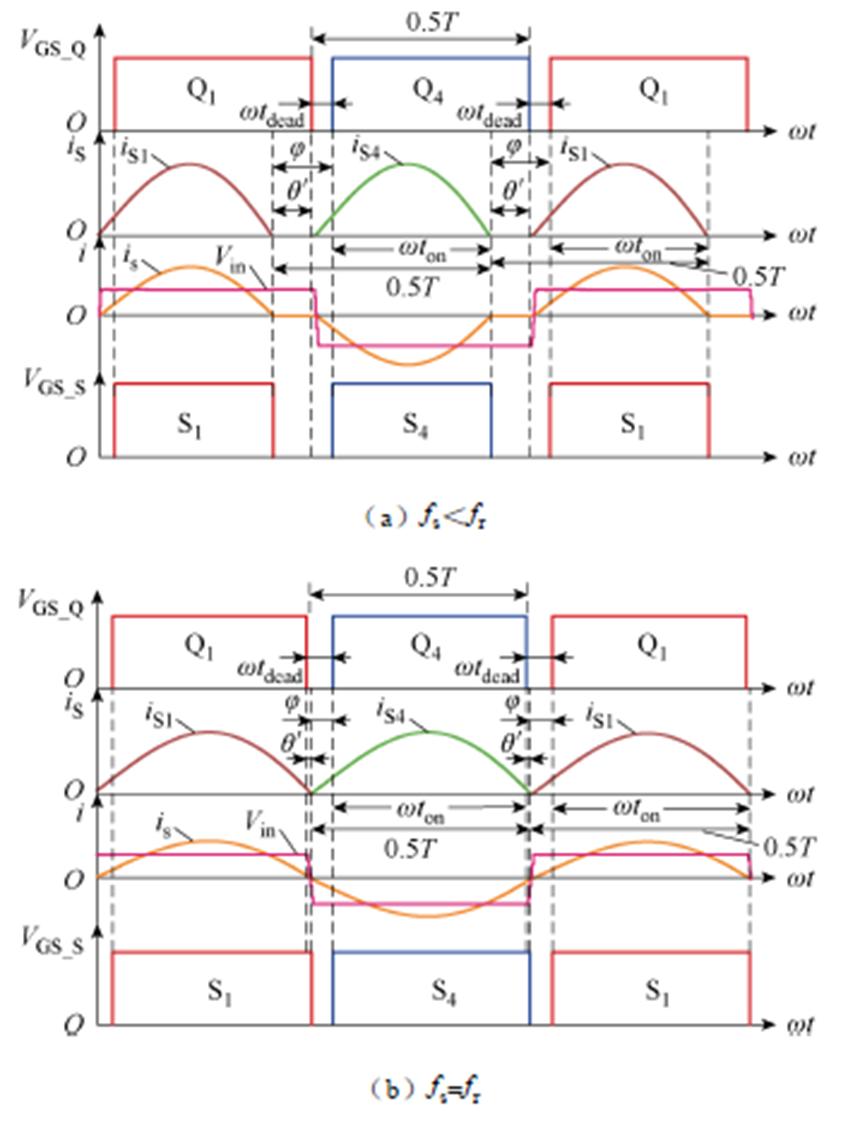

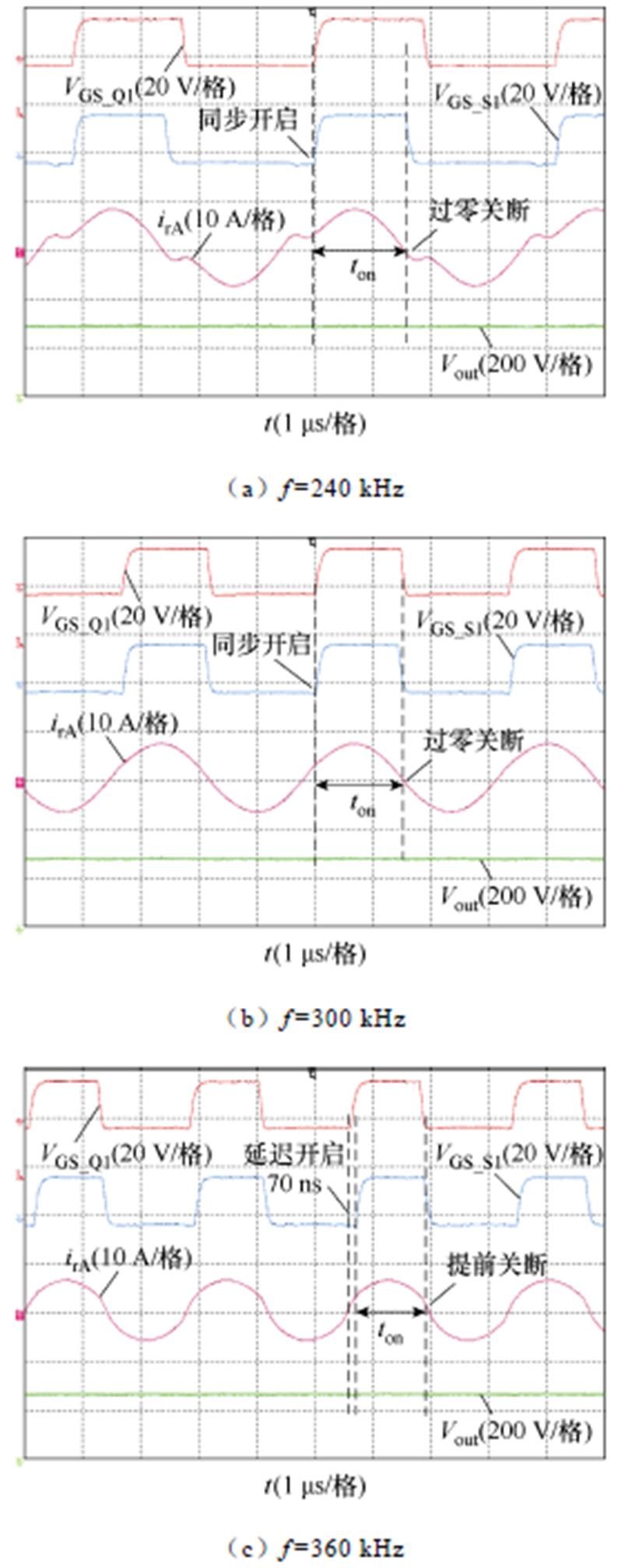

=0可以求解其过零点,从而得到全桥模式输入信号和谐振电流的相位差 。结合图12所示全桥模式不同频率SR MOSFET重要波形,可以计算出不同频率下全桥模式的导通时间ton_fb为

。结合图12所示全桥模式不同频率SR MOSFET重要波形,可以计算出不同频率下全桥模式的导通时间ton_fb为

(23)

(23)

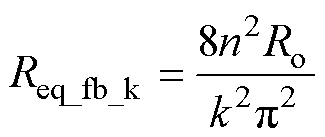

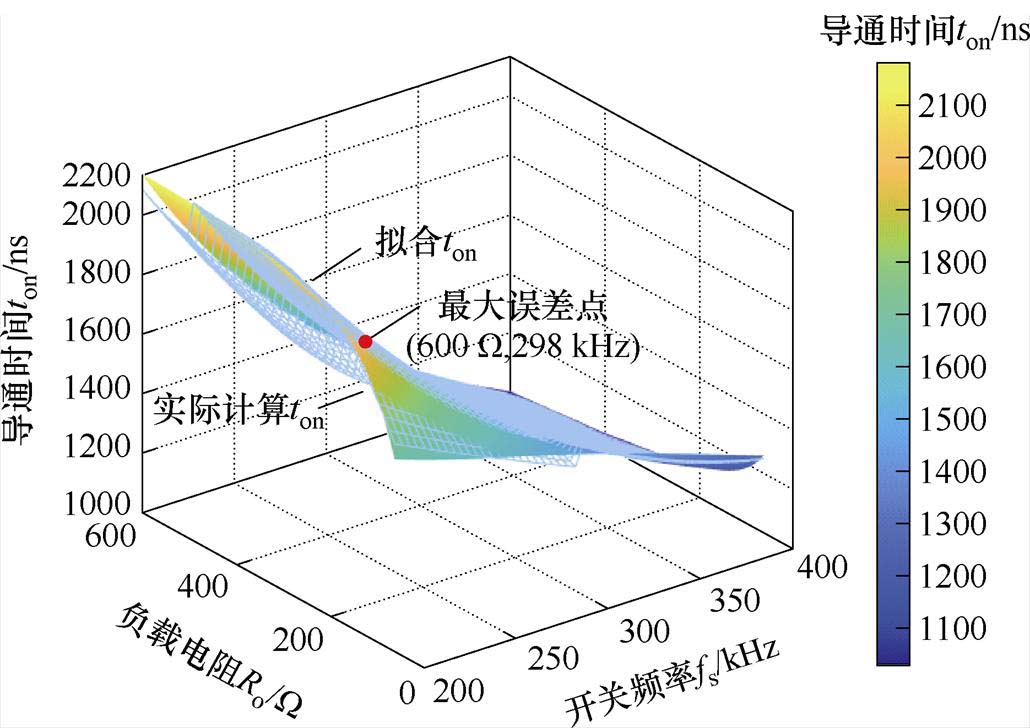

由式(23)可以得到出全桥模式下导通时间ton_fb、开关频率fs和输出负载Ro之间的关系如图13所示。

图12 全桥模式不同频率SR MOSFET重要波形

Fig.12 Important waveforms of SR MOSFET in full-bridge mode with different frequencies

图13 SR MOSFET ton_fb与fs和Ro的关系

Fig.13 The relationship between SR MOSFET ton_fb,fs and Ro

半桥运行模式下的EHA等效模型如图14所示。图14中,Z1k_h为二次侧谐振电感Lrs、谐振电容1.5Crs和Req_hb_k的串联阻抗,Z2k_h为励磁电感2Lm和Z1k_h的并联阻抗,Z3k_h为谐振变换器输入阻抗。Req_hb_k为半桥运行模式下二次侧折合到一次侧的等效负载,其值为

(24)

(24)

图14 半桥模式扩展谐波阻抗模型

Fig.14 Half-bridge operating mode EHA model

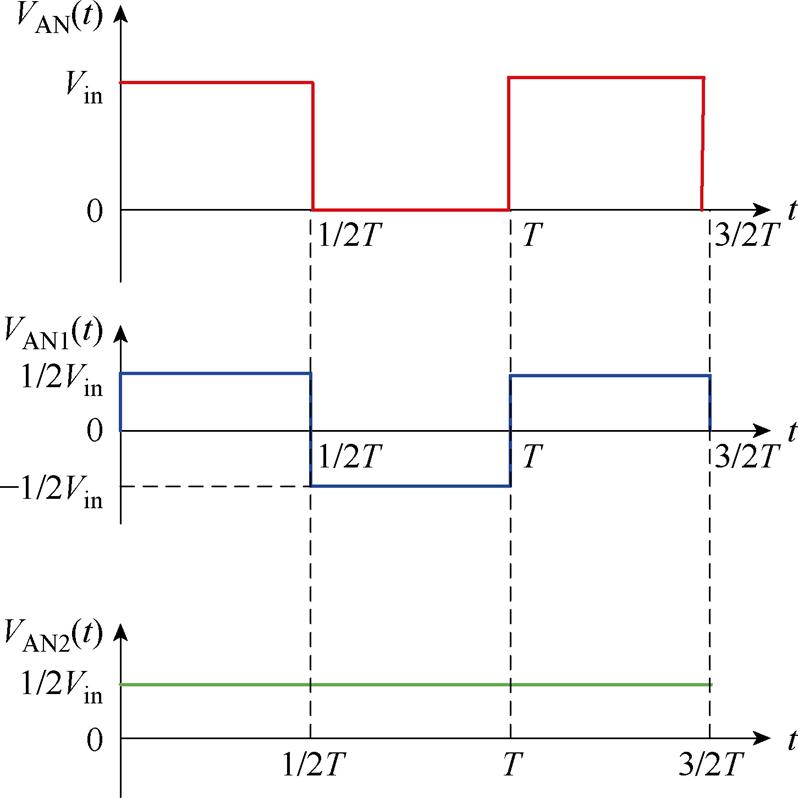

半桥模式输入电压波形如图15所示,输入信号经过傅里叶级数展开后,可得VAN(t)为

(25)

(25)

图15 半桥模式输入电压波形

Fig.15 Half-bridge mode input voltage waveforms

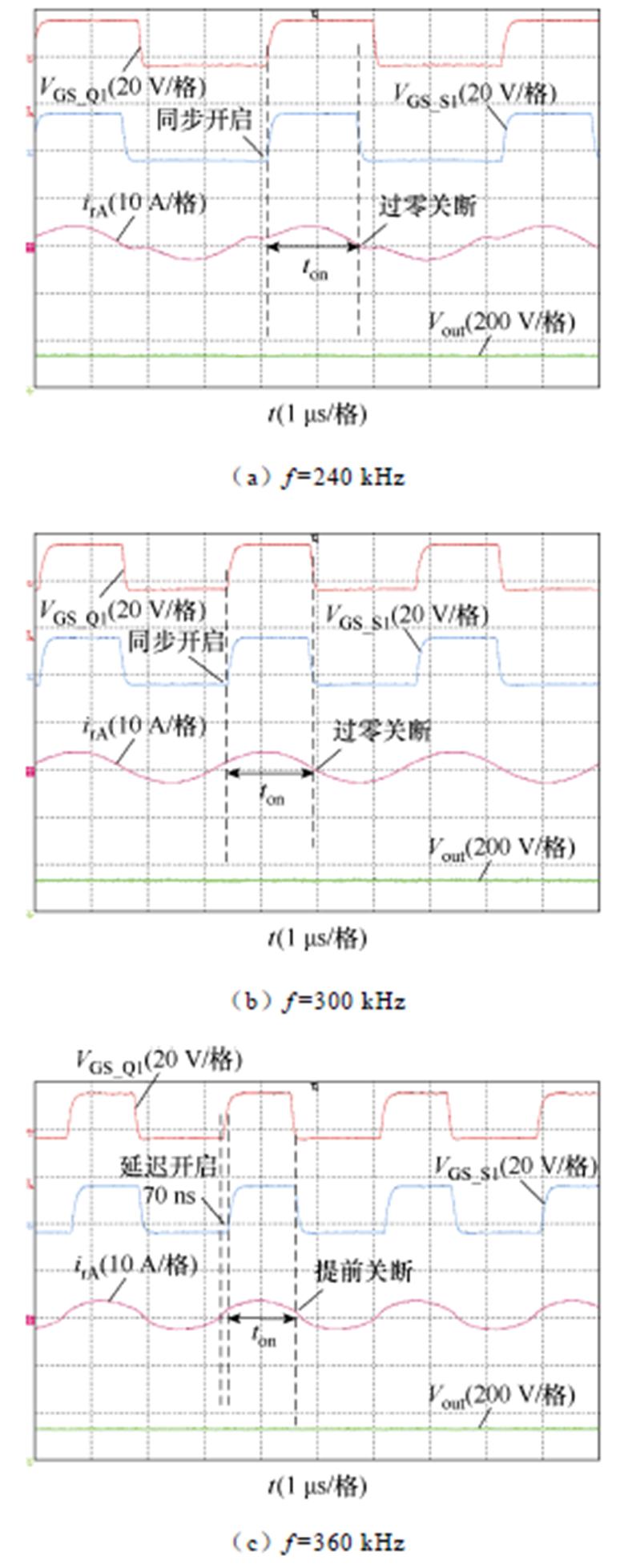

通过对比图11和图14可以发现,除输入方波的差异外,两种模式下的参数完全一致。此外,由于输入电压幅值对谐振电流过零点的最终计算结果无实际影响,半桥模式和全桥模式的计算结果保持一致,导通时间ton相同。因此,后续分析和计算将主要针对三相模式和全桥模式,半桥模式不再重复讨论。

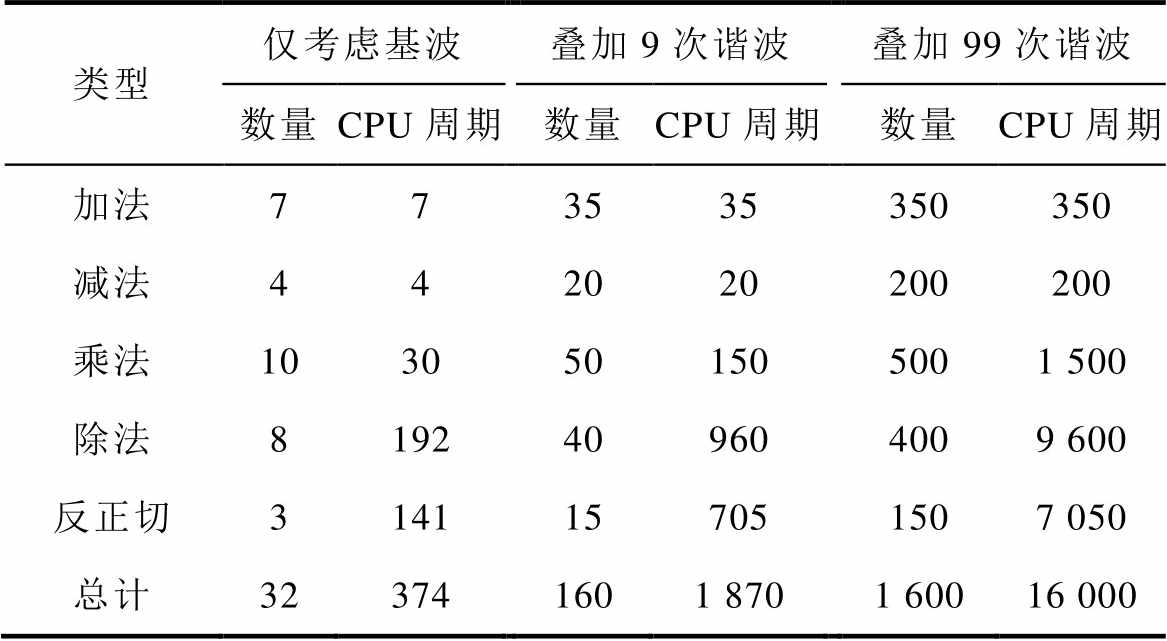

基于上述分析可知,计算导通时间ton需要进行大量复杂的阻抗和三角函数计算,尤其是在追求更高精度的情况下,引入更多次谐波会使计算量成倍增长。在高频系统中,这种计算不仅会占用大量处理时间,还可能因计算误差导致系统运行异常。表3列出了叠加不同次谐波时DSP运算量的对比,直观体现了谐波阶数对计算复杂度的影响。

表3 DSP运算量对比

Tab.3 Comparison of DSP computational complexity

类型仅考虑基波叠加9次谐波叠加99次谐波 数量CPU周期数量CPU周期数量CPU周期 加法773535350350 减法442020200200 乘法1030501505001 500 除法8192409604009 600 反正切3141157051507 050 总计323741601 8701 60016 000

由于ton本质上只与输出负载Ro和开关频率fs有关,通过对这两个参数进行预先的数据拟合,可以显著简化实时计算的复杂度[18-19, 21]。通过将复杂的在线计算转化为简单的函数调用操作,极大地提升了计算效率,同时增强了系统的实时性和可靠性。

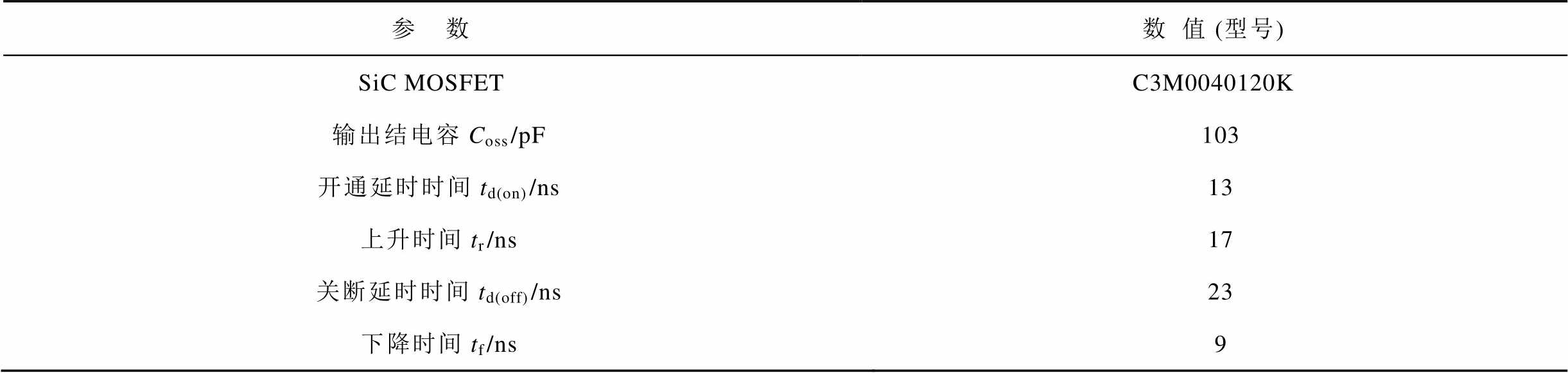

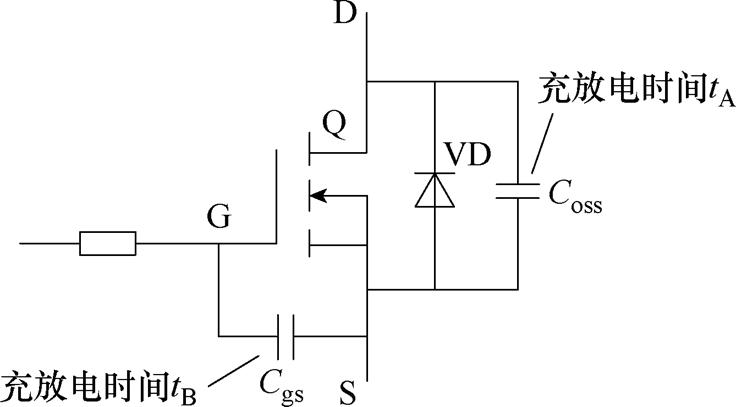

由图9可知,当开关频率fs小于谐振频率fr时,SR MOSFET会早于一次侧MOSFET关断;而当开关频率fs大于谐振频率fr时,SR MOSFET的关断会滞后于一次侧MOSFET,每个周期的导通时间显著延长。因此,在过谐振情况下,为了避免因死区时间过短而导致SR MOSFET产生额外的开通损耗,甚至可能引发上下管直通的严重故障,需综合考虑SiC MOSFET的上升时间tr和下降时间tf以及满足其寄生电容实现完全充放电所需时间,设置一定的延迟开通和提前关断时间。表4列出了本文样机所使用的SiC MOSFET参数,其寄生电容特性如图16所示。

表4 SiC MOSFET参数

Tab.4 The parameters of SiC MOSFET

参 数数值 (型号) SiC MOSFETC3M0040120K 输出结电容Coss/pF103 开通延时时间td(on)/ns13 上升时间tr/ns17 关断延时时间td(off)/ns23 下降时间tf/ns9

图16 SiC MOSFET寄生电容特性

Fig.16 Parasitic capacitance of SiC MOSFET

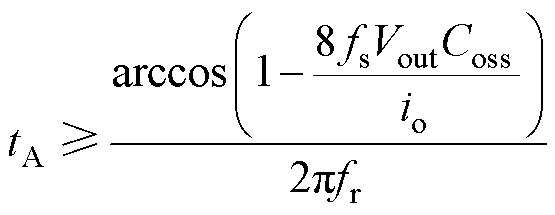

为了实现寄生电容完全充放电[18],需满足

(26)

(26)

式中,tA为SiC MOSFET实现完全充放所需时间。由式(26)可以求得二次侧SR MOSFET实现零电压软开关(Zero Voltage Switching, ZVS)的最小时间。

此外,栅源极两端电容Cgs也会对SiC MOSFET的开通和关断时间产生重要影响[24-25]。如果同一桥臂的驱动信号所设置的死区时间过短,可能导致两个开关管同时进入线性工作区,从而引发直通现象。因此,需综合考虑Cgs的充放电时间tB,以避免因死区时间不足而导致开关管严重发热或直通故障。同时,开关管的开通延时时间td(on)和关断延时时间td(off)特性也需要考虑在内,故SR MOSFET的最小延迟开通和提前关断时间为

(27)

(27)

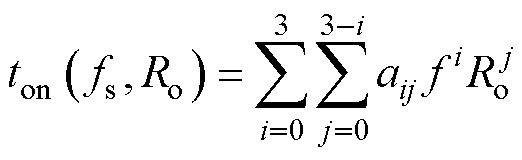

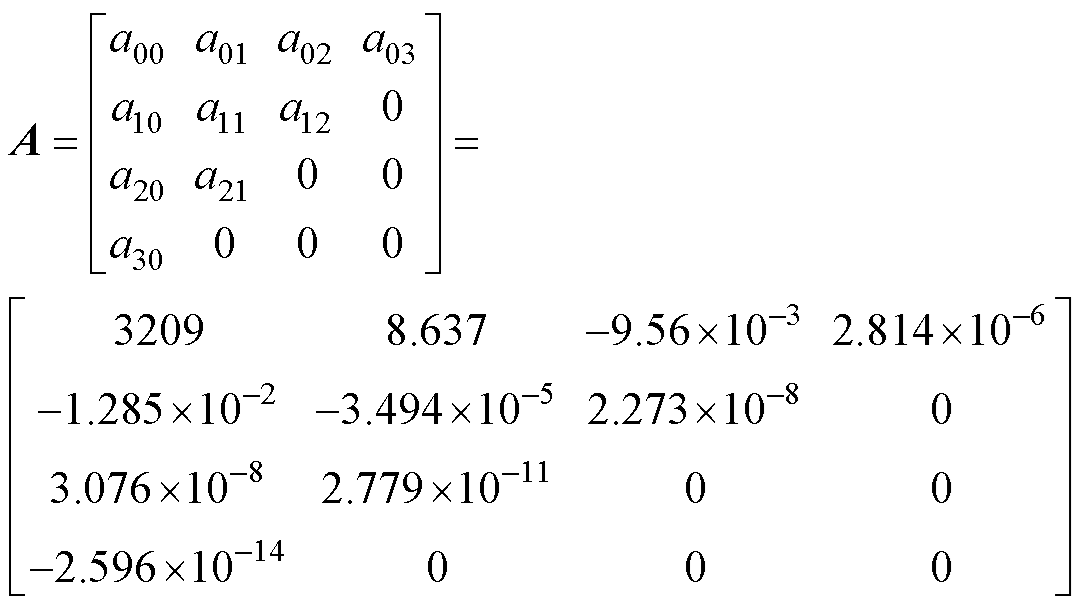

为了提高拟合精度,本文利用Matlab采用三阶多项式模型进行分频段拟合,当开关频率fs≤fr时,拟合函数为

(28)

(28)

系数矩阵A为

(29)

(29)

当开关频率fs>fr时,拟合函数为

(30)

(30)

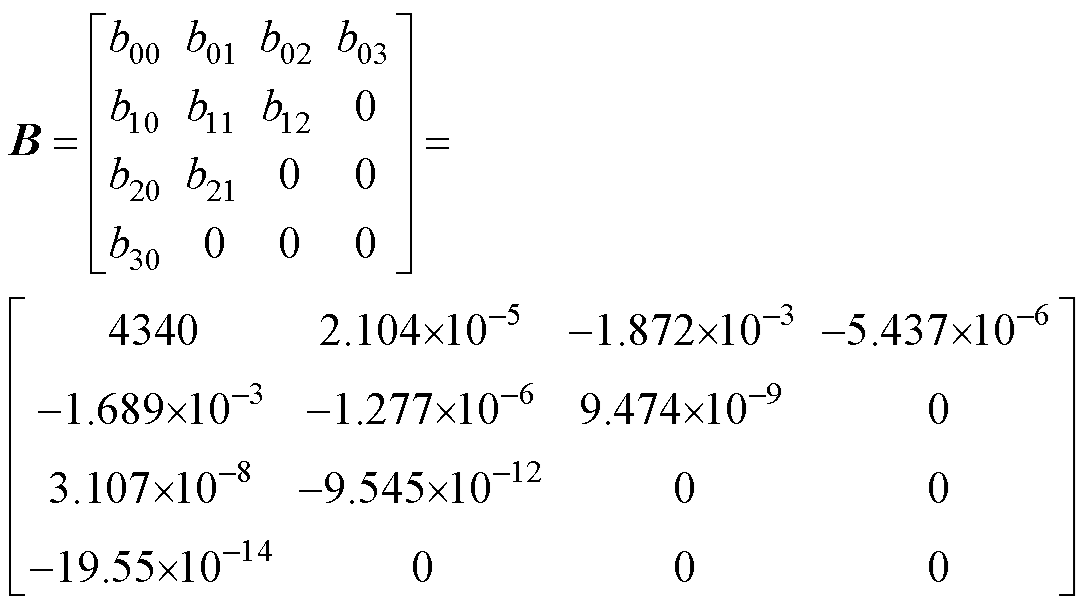

系数矩阵B为

(31)

(31)

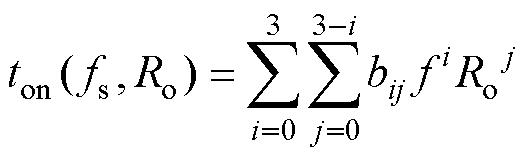

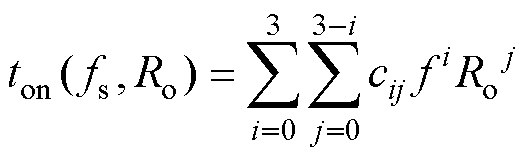

同理,全桥和半桥运行模式下,当开关频率fs≤fr时,拟合函数为

(32)

(32)

系数矩阵C为

(33)

(33)

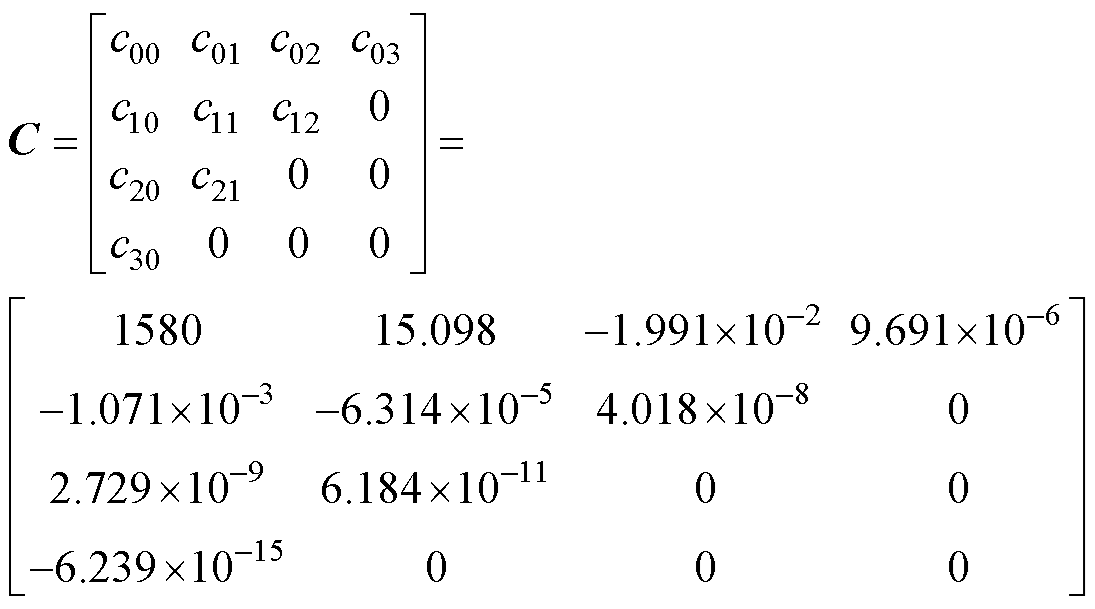

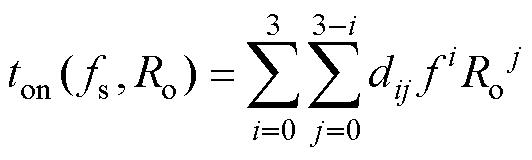

当开关频率fs>fr时,拟合函数为

(34)

(34)

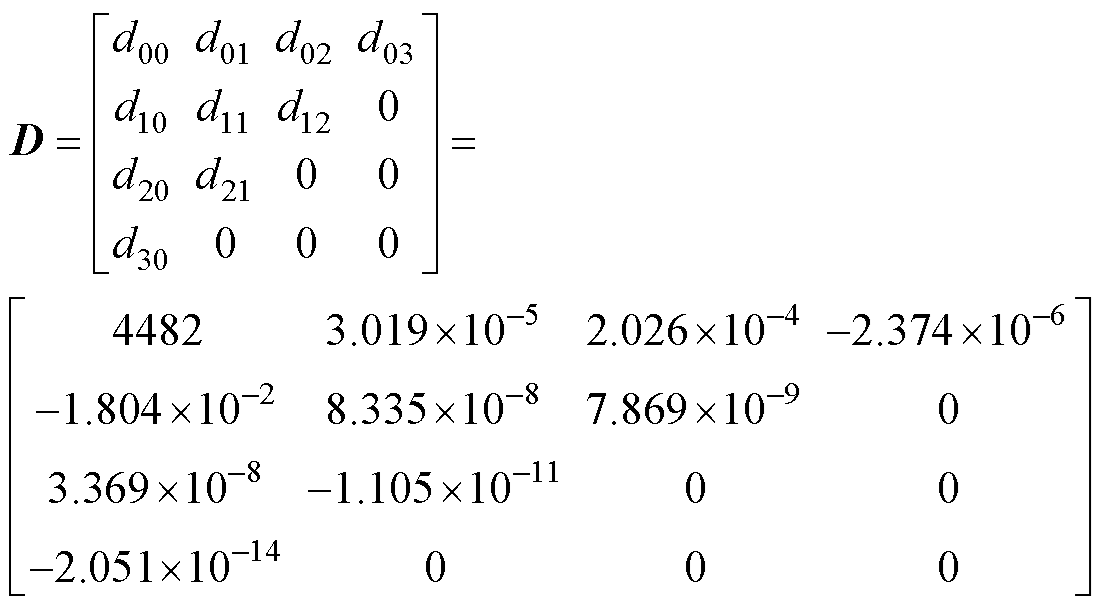

系数矩阵D为

(35)

(35)

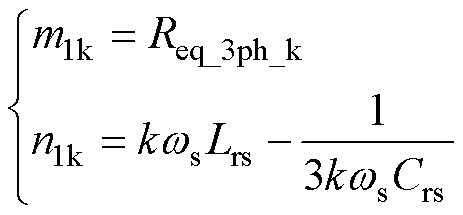

图17展示了三相运行模式下SR MOSFET导通时间的拟合模型计算结果与实际计算结果的对比。从图17中可以看出,拟合模型与实际计算的导通时间高度吻合,证明了拟合模型具有较高的精度和可靠性。在图中标注了误差最大的点,该点对应负载为600 W、频率为302 kHz。此时,实际计算的导通时间为1 401 ns,而拟合模型计算的导通时间为1 345 ns,误差为56 ns,误差率为3.99%。

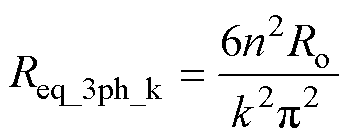

图18为全桥和半桥运行模式下SR MOSFET导通时间拟合模型计算与实际计算结果的对比。从图18中可以看出,拟合模型同样与实际计算结果保持较高的一致性。在标注的误差最大的点上,对应负载为600 W、频率为298 kHz,理论计算值为1 394 ns,拟合值为1 354 ns,最大误差为40 ns,误差率为2.87%。

图17 三相模式导通时间对比

Fig.17 Comparison of conduction time in three-phase mode

图18 全桥模式和半桥模式导通时间对比

Fig.18 Comparison of conduction time in full-bridge mode and half-bridge mode

相比复杂的数学运算(如除法和反正切运算),采用三阶拟合模型只需进行9次加法和18次乘法,大幅度降低了计算复杂度,避免了高运算周期的非线性函数运算。这一优化有效减轻了DSP的计算负担,提高了系统的实时性和响应速度。

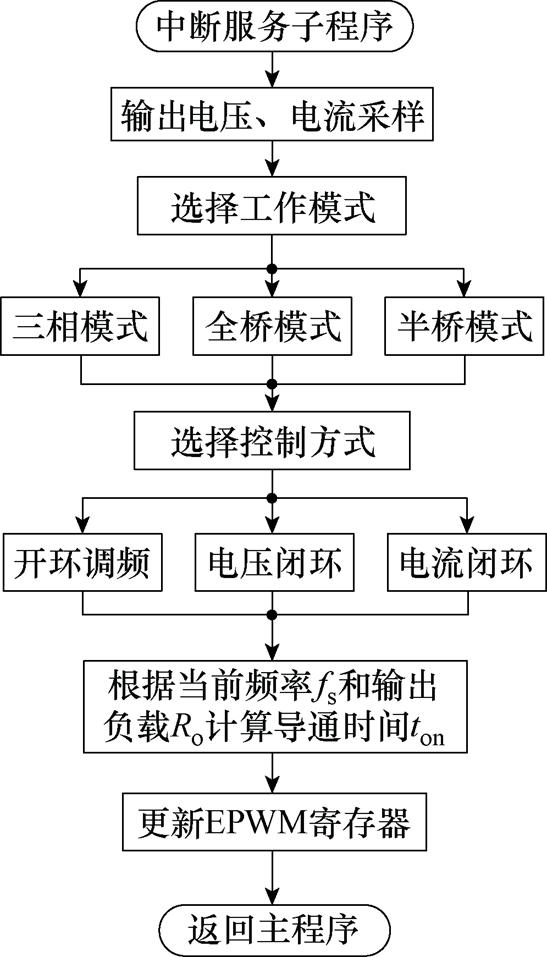

所提出的基于扩展谐波的三相CLLC谐振变换器同步整流控制流程如图19所示,首先,系统通过DSP的中断服务子程序对输出电压和电流进行采样,进而识别当前变换器的输出负载Ro。接下来,系统根据当前的负载情况选择相应的工作模式和控制策略。具体来说,工作模式可选择三种类型:三相模式、全桥模式及半桥模式;同时,控制方式可依据系统需求选择适当的类型。一旦工作模式和控制方式确定后,系统将根据变换器当前的工作频率fs和输出负载Ro利用拟合函数计算出二次侧MOSFET的导通时间ton。最后,导通时间值会通过增强型脉宽调制(Enhanced Pulse Width Modulation, EPWM)寄存器进行更新,从而调整一次、二次侧MOSFET驱动电路的波形。更新完成后,系统将等待下一次中断服务程序的触发,以继续进行动态调整。通过该流程,三相CLLC谐振变换器能够在不同工作模式下实现高效的同步整流控制,从而提升整个系统电力转换的效率。

图19 所提同步整流控制流程

Fig.19 The proposed synchronous rectification control flowchart

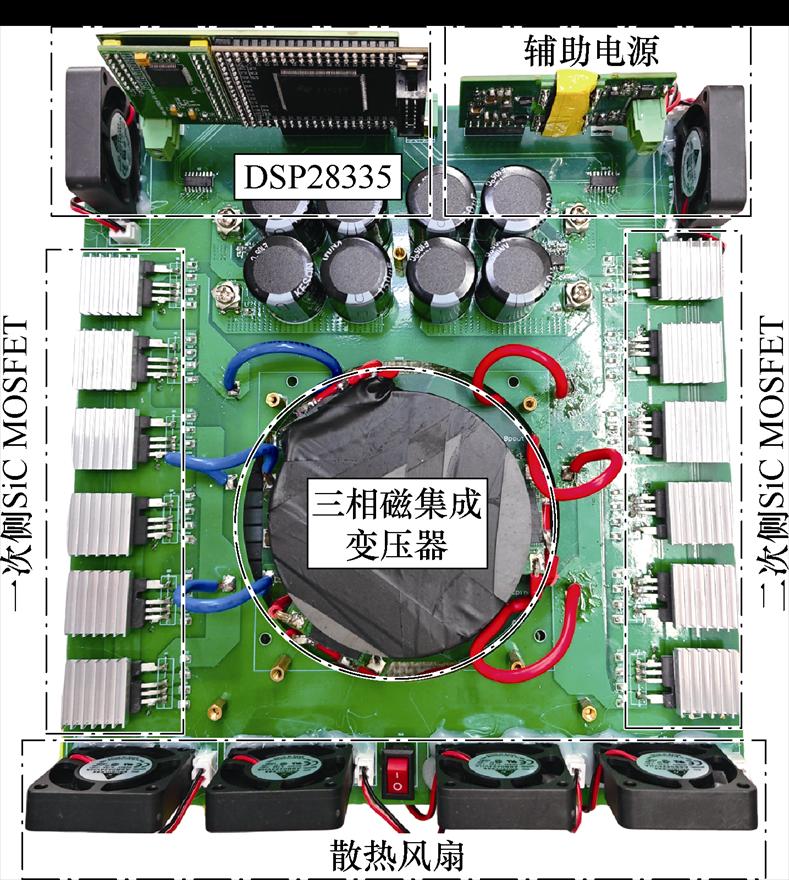

为进一步验证所提算法的可行性,搭建了一台三相CLLC谐振变换器实验样机如图20所示。为了减小变换器的体积,采用了三相磁集成变压器。一、二次侧开关管均采用了Wolfspeed公司1.2 kV SiC器件C3M0040120K,数字控制器采用了TI公司的TMS320F28335。

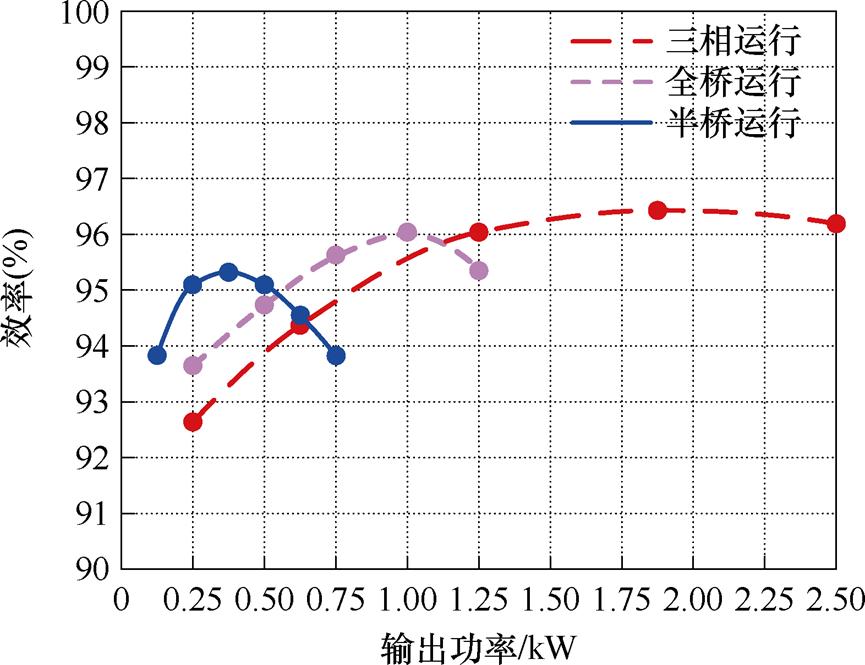

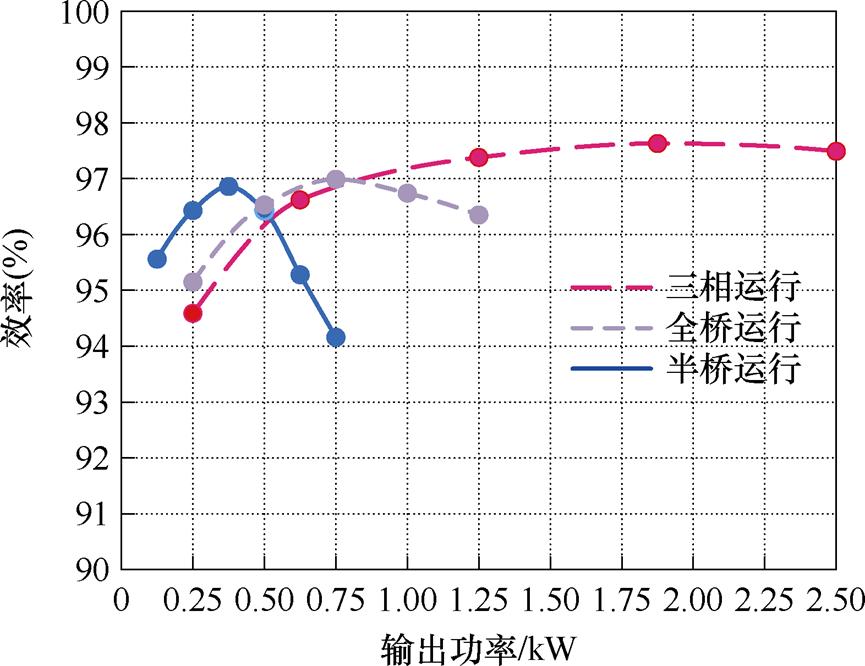

图21给出了不同运行模式下的效率曲线。可以看出,与传统控制方式相比,切相策略可以显著提高变换器轻载时的效率。

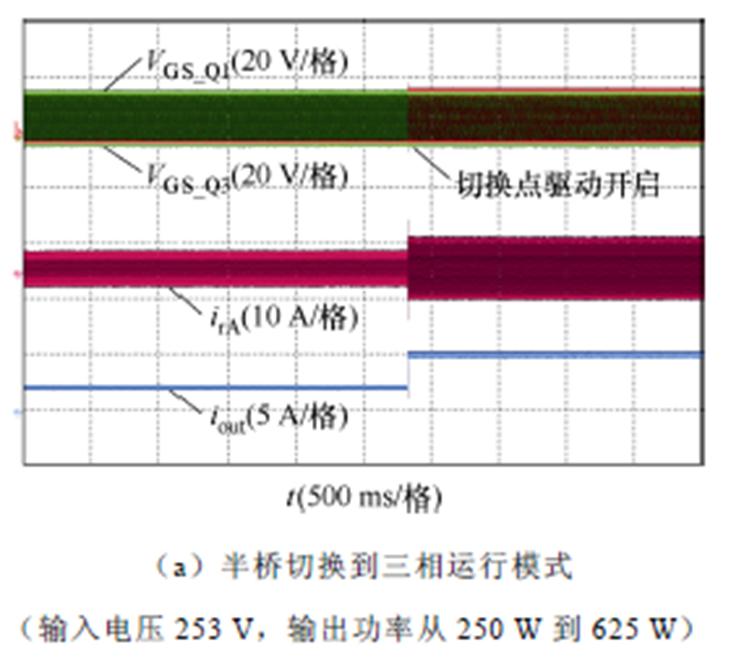

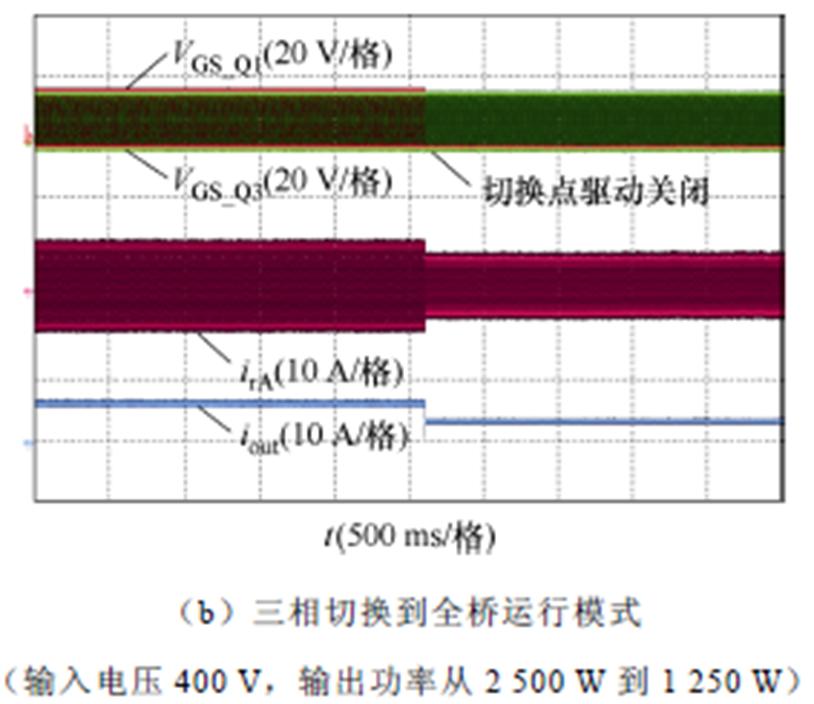

三相模式、全桥模式、半桥模式的动态切换如图22所示。图22a显示了当负载从10%变为25%时,变换器从半桥运行模式切换到三相运行模式,模拟电池从预充电阶段进入恒流充电阶段的过程;图22b显示了从满载变为半载时,变换器从三相运行模式切换到全桥运行模式,模拟电池从恒流充电阶段进入恒压充电阶段的过程,切换响应速度较快。

图20 三相CLLC谐振变换器实验样机

Fig.20 A prototype of a three-phase CLLC resonant converter

图21 不同运行模式下效率对比

Fig.21 Efficiency comparison under different operating modes

图23展示了在三相运行模式下采用本文提出的SR控制时,不同频率下的波形,其中输入电压为400 V,负载电阻为64 W,输出功率为2.5 kW。实测波形与理论波形相符,均出现了延迟开通和提前关断现象。

图22 不同运行模式的动态切换

Fig.22 Dynamic switching under different operating modes

图23 三相运行模式SR波形

Fig.23 SR waveforms in three-phase operation mode

为进一步验证所提SR控制的有效性,图24和图25分别展示了在全桥运行模式(输入电压282 V,负载电阻64 W,输出功率1 250 W)和半桥运行模式(输入电压253 V,负载电阻64 W,输出功率250 W)下的波形。

图24 全桥运行模式SR波形

Fig.24 SR waveforms in full-bridge operation mode

可以看出,当开关频率高于谐振频率时,二次侧SR MOSFET会在整流电流过零点之前关断,使部分电流流经体二极管。然而,由于这些延迟和提前关断时间处于死区时间内且电流值极小,导通损耗可以忽略不计。实验结果表明,所提出的SR控制适用于切相策略后的所有模式。

图25 半桥运行模式SR波形

Fig.25 SR waveforms in half-bridge operation mode

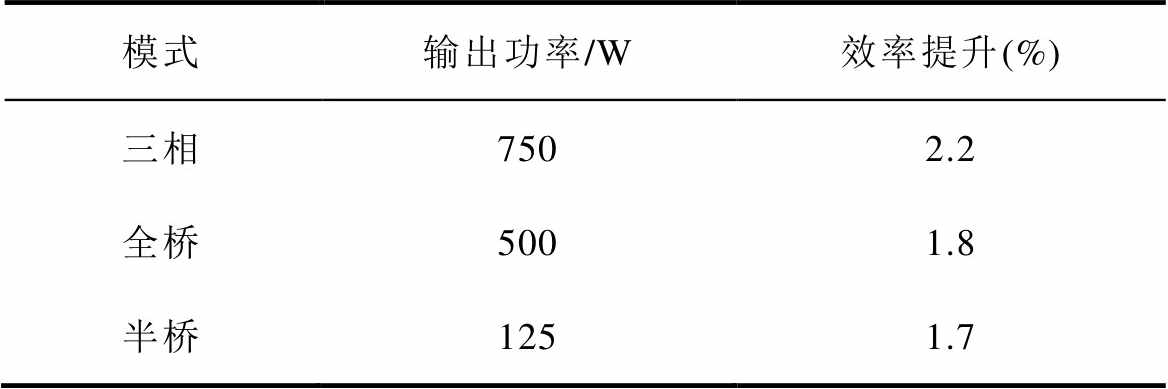

图26给出了采用SR控制后变换器不同模式下的效率曲线。对比图21可知,采用所提SR控制后,三种模式下的效率均有所提升。为了更直观地说明SR控制在不同模式下提升效率的效果,表5列出了各模式下效率提升最显著的点。

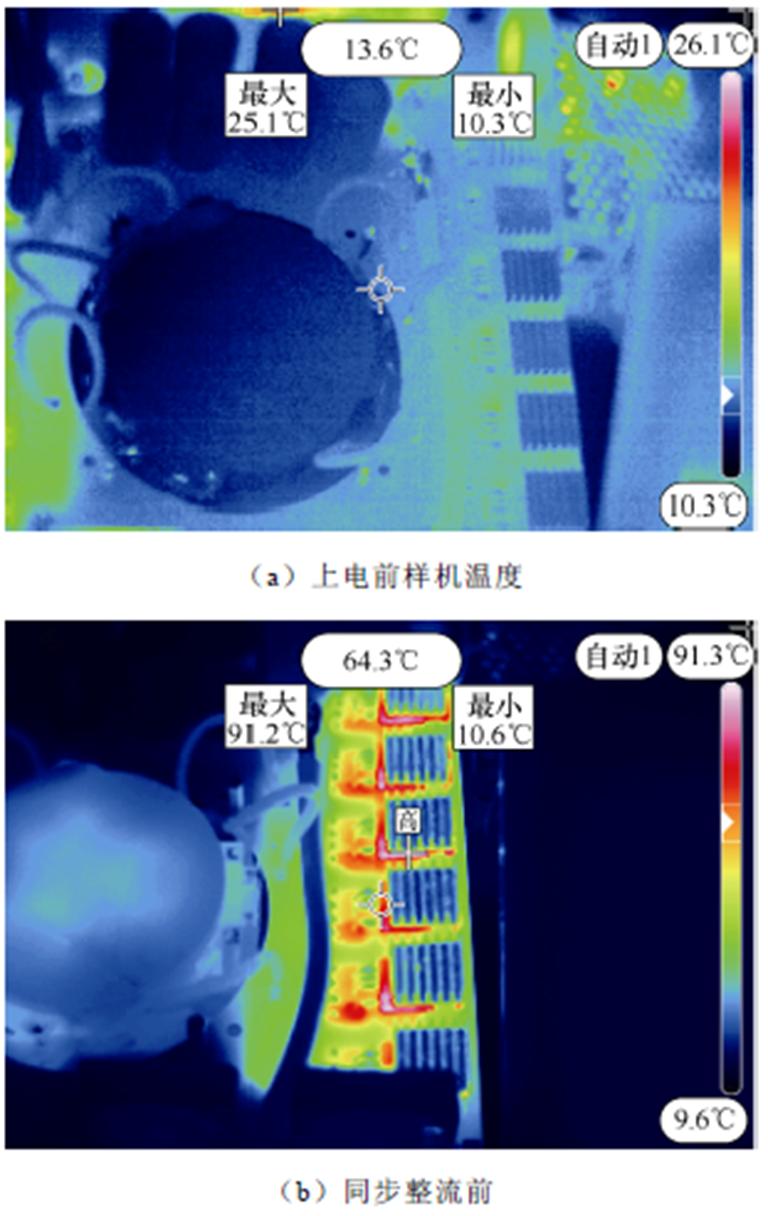

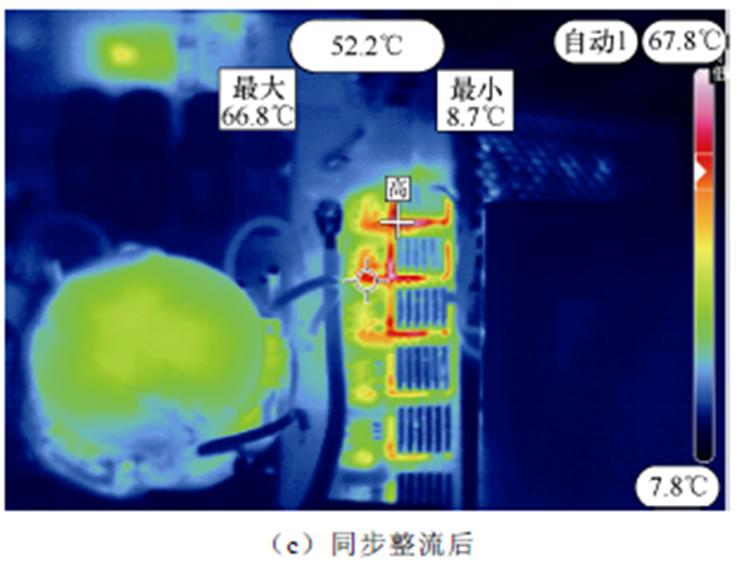

此外,采用同步整流后,不仅可以提升效率,还能有效缓解SR MOSFET的发热问题。使用同步整流前后SR MOSFET温度对比如图27所示,本文在输入电压400 V,频率300 kHz,功率2.5 kW,室温10.3℃的测试环境下,对比了同步整流前后的SR MOSFET温度分布,当运行稳定后,采用同步整流前整流侧最高温度为91.2℃,采用同步整流后整流侧最高温度为66.8℃,温度降低了24.4℃。

图26 使用SR控制后变换器效率

Fig.26 Converter efficiency after using the SR control

表5 不同模式效率提升最显著情况

Tab.5 Most significant efficiency improvements in different modes

模式输出功率/W效率提升(%) 三相7502.2 全桥5001.8 半桥1251.7

图27 使用同步整流前后SR MOSFET温度对比

Fig.27 Comparison of SR MOSFET temperatures before and after using the SR control

针对三相CLLC谐振变换器在电能转换过程中面临的高效率需求、轻载效率下降以及同步整流实现复杂等关键挑战,本文提出了一种基于扩展谐波分析的三相CLLC谐振变换器同步整流控制算法。通过研究切相策略下变换器三种工作模式的特性及驱动信号差异,建立了扩展谐波阻抗模型,精确计算了不同工作模式下SR MOSFET的导通时间。同时,利用三阶拟合模型显著减少了控制系统的运算量。为验证算法的可行性,设计并搭建了一台基于SiC器件的2.5 kW实验样机。实验结果表明,所提同步整流控制算法显著提升了三相CLLC谐振变换器在全负载范围内的效率,并有效地缓解了SR MOSFET的发热。

参考文献

[1] 王建渊, 郭俊玲, 闫瑾, 等. 基于CLLLC变频扩展移相分段调制的宽增益车载充电机研究[J]. 电工技术学报, 2025, 40(18): 5998-6013.

Wang Jianyuan, Guo Junling, Yan Jin, et al. Research on wide gain vehicle charger based on CLLLC frequency conversion extended phase shift segment modulation[J]. Transactions of China Electrotechnical Society, 2025, 40(18): 5998-6013.

[2] 程鹤, 徐恺, 李朋圣, 等. 三相CLLC谐振变换器磁集成平面变压器设计与优化[J]. 电工技术学报, 2024, 39(12): 3774-3786.

Cheng He, Xu Kai, Li Pengsheng, et al. Design and optimization of three-phase CLLC resonant converter with magnetic integrated planar transformer[J]. Transactions of China Electrotechnical Society, 2024, 39(12): 3774-3786.

[3] 赵烈, 裴云庆, 刘鑫浩, 等. 基于基波分析法的车载充电机CLLC谐振变换器参数设计方法[J]. 中国电机工程报, 2020, 40(15): 4965-4977.

Zhao Lie, Pei Yunqing, Liu Xinhao, et al. Design methodology of CLLC resonant converters for electric vehicle battery chargers[J]. Proceedings of the CSEE, 2020, 40(15): 4965-4977.

[4] 赵剑, 张哲, 李召端, 等. 三端口CLLC固态变压器的设计与优化[J]. 电工技术学报, 2024, 39(23): 7542-7553.

Zhao Jian, Zhang Zhe, Li Zhaoduan, et al. Design and optimization of three-port CLLC solid-state trans- former[J]. Transactions of China Electrotechnical Society, 2024, 39(23): 7542-7553.

[5] 杨勇, 宋大威, 顾占彪, 等. 星载1MHz GaN LLC变换器低反向导通损耗控制[J]. 电工技术学报, 2022, 37(24): 6183-6190.

Yang Yong, Song Dawei, Gu Zhanbiao, et al. Low reverse conduction loss control for 1MHz GaN-based LLC converter used in satellite application[J]. Transactions of China Electrotechnical Society, 2022, 37(24): 6183-6190.

[6] 廖志贤, 李彬彬, 索之闻, 等. 磁集成三端口电力电子变压器的改进控制方法[J]. 电力系统自动化, 2023, 47(11): 133-143.

Liao Zhixian, Li Binbin, Suo Zhiwen, et al. Improved control method for three-port power electronic trans- former based on magnetic integration[J]. Automation of Electric Power Systems, 2023, 47(11): 133-143.

[7] 李加明, 任小永, 周治成, 等. 基于谐振网络优化的双向LLC-DCX多模块并联系统均流优化研究[J]. 电工技术学报, 2023, 38(10): 2720-2730, 2756.

Li Jiaming, Ren Xiaoyong, Zhou Zhicheng, et al. Research on current sharing optimization of bidire- ctional LLC-DCX multi-module parallel system based on resonant network optimization[J]. Transactions of China Electrotechnical Society, 2023, 38(10): 2720- 2730, 2756.

[8] 杨玉岗, 武艳秋, 孙晓钰, 等. 交错并联双向CLLC型谐振变换器中U+U型磁集成变压器的设计[J]. 电工技术学报, 2021, 36(2): 282-291.

Yang Yugang, Wu Yanqiu, Sun Xiaoyu, et al. Design of U+U type magnetic integrated transformer in interlaced bidirectional CLLC resonant converter[J]. Transactions of China Electrotechnical Society, 2021, 36(2): 282-291.

[9] Jin Feng, Nabih A, Chen Chen, et al. A high efficiency high density DC/DC converter for battery charger applications[C]//2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 2021: 1767-1774.

[10] 谢飞, 许建平, 郭夏, 等. 基于虚拟阻抗的三相Buck整流器输入不平衡控制策略[J]. 电工技术学报, 2024, 39(14): 4456-4466.

Xie Fei, Xu Jianping, Guo Xia, et al. A control strategy based on virtual impedance for three-phase Buck rectifier under unbalanced phase-voltages[J]. Transactions of China Electrotechnical Society, 2024, 39(14): 4456-4466.

[11] 缪哲语, 仝昊, 吕征宇, 等. 一种多模态宽范围箝位桥并联型LLC变换器控制方法[J]. 电源学报, 2022, 20(4): 1-10.

Miao Zheyu, Tong Hao, Lü Zhengyu, et al. Variable- mode control method for wide-range diode clamped bridge paralleled LLC converter[J]. Journal of Power Supply, 2022, 20(4): 1-10.

[12] Arshadi S A, Ordonez M, Mohammadi M, et al. Efficiency improvement of three-phase LLC resonant converter using phase shedding[C]//2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 2017: 3771-3775.

[13] Li Bin, Li Qiang, Lee F C. Phase shading for light load efficiency improve in three-phase resonant converter with integrated PCB winding mag- netics[C]//2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019- ECCE Asia), Busan, Korea, 2019: 2362-2367.

[14] Arshadi S A, Ordonez M, Eberle W, et al. Three- phase LLC battery charger: wide regulation and improved light-load operation[J]. IEEE Transactions on Power Electronics, 2020, 36(2): 1519-1531.

[15] Jin Feng, Nabih A, Li Qiang. Light load efficiency improvement of three phase CLLC resonant converter for on-board charger applications[C]//2022 IEEE Applied Power Electronics Conference and Expo- sition (APEC), Houston, TX, USA, 2022: 1-7.

[16] Guo Shuaichen, Wang Xuehua. A synchronous recti- fication scheme for three-phase LLC considering phase shedding[C]//2023 IEEE PELS Students and Young Professionals Symposium (SYPS), Shanghai, China, 2023: 1-6.

[17] Wei Yuqi, Luo Quanming, Mantooth H A. Syn- chronous rectification for LLC resonant converter: an overview[J]. IEEE Transactions on Power Electronics, 2021, 36(6): 7264-7280.

[18] 廖嘉睿, 杭丽君, 但志敏, 等. 宽范围CLLLC双向同步整流数字控制方法[J]. 电工技术学报, 2022, 37(14): 3632-3642.

Liao Jiarui, Hang Lijun, Dan Zhimin, et al. Digital control method of wide-range CLLLC bidirectional synchronous rectification[J]. Transactions of China Electrotechnical Society, 2022, 37(14): 3632-3642.

[19] 李浩然, 崔超辉, 王生东, 等. 基于二阶拟合模型的SiC双向LLC数字同步整流控制[J]. 电工技术学报, 2022, 37(24): 6191-6203.

Li Haoran, Cui Chaohui, Wang Shengdong, et al. Two-order fitting model-based digital synchronous rectifier control for SiC bidirectional LLC con- verter[J]. Transactions of China Electrotechnical Society, 2022, 37(24): 6191-6203.

[20] 刘和平, 陈红岩, 苗轶如, 等. 混合式LLC电路谐振与同步整流数字式控制[J]. 中国电机工程学报, 2015, 35(9): 2272-2278.

Liu Heping, Chen Hongyan, Miao Yiru, et al. Hybrid LLC circuit resonant and synchronous rectifier digital control[J]. Proceedings of the CSEE, 2015, 35(9): 2272-2278.

[21] Li Haoran, Sun Yibo, Wang Shengdong, et al. Bidi- rectional control with fitting model-based syn- chronous rectification and input ripple current feedforward for SiC bidirectional CLLC EV charger[J]. IEEE Transactions on Industrial Elec- tronics, 2022, 70(9): 9136-9146.

[22] Sankar A, Mallik A, Khaligh A. Extended harmonics based phase tracking for synchronous rectification in CLLC converters[J]. IEEE Transactions on Industrial Electronics, 2019, 66(8): 6592-6603.

[23] Li Haoran, Hu Cungang, Cui Chaohui, et al. Digital synchronous rectifier control using extended harmo- nics impedance model for high-frequency GaN-based LLC converters[J]. IEEE Transactions on Industrial Electronics, 2024, 71(10): 12312-12322.

[24] 张新闻, 刘文泽, 杨树德, 等. MOSFET输出电容对CLLLC谐振变换器模型的优化[J]. 电工技术学报, 2024, 39(22): 7228-7238.

Zhang Xinwen, Liu Wenze, Yang Shude, et al. Optimization of CLLLC resonant converter modeling by MOSFET output capacitance[J]. Transactions of China Electrotechnical Society, 2024, 39(22): 7228- 7238.

[25] 丁四宝, 王盼宝, 王卫, 等. SiC/Si混合开关时间延迟及其信号调制方法[J]. 电工技术学报, 2025, 40(4): 1129-1144.

Ding Sibao, Wang Panbao, Wang Wei, et al. Analysis of SiC/Si HyS Loss characteristics and its driving signal modulation circuit[J]. Transactions of China Electrotechnical Society, 2025, 40(4): 1129-1144.

Abstract The CLLC resonant converter has been widely used in electric vehicle (EV) chargers due to its excellent performance, including wide gain, high efficiency, and soft switching under full load. Adopting an interleaved parallel structure is a better choice for medium- to high-power chargers. Compared to half-bridge and full-bridge structures, the three-phase CLLC resonant converter meets the demands for high power density, high efficiency, and high reliability while reducing the size of filter components due to its small input and output current ripple. The EV battery charging process is divided into pre-charging, constant current charging, and constant voltage charging. The three-phase CLLC resonant converter covers all three charging stages using a phase-shedding strategy, operating in three-phase, full-bridge, and half-bridge modes, ensuring high efficiency under full load.

To further improve the converter's efficiency, synchronous rectification control is applied. By utilizing the extremely low conduction resistance of SiC MOSFETs and replacing the diodes on the secondary side with controllable SiC MOSFETs, bidirectional energy flow is enabled, and the converter’s losses are reduced. The fundamental harmonic approximation (FHA) method has traditionally been used for modeling resonant converters with high accuracy near the resonant frequency. However, in the case of the CLLC resonant converter, multiple resonant frequencies emerge due to parameter mismatches, leading to a decrease in the accuracy of the FHA model. A synchronous rectification (SR) algorithm is proposed for the three-phase CLLC resonant converter. An extended harmonic impedance model is established for different operating modes under phase-shifting control, considering the effect of dead time. The conduction time of the secondary side MOSFETs for each mode is accurately calculated, improving the converter’s efficiency across the whole load range.

The control strategy is implemented as follows. The system samples the output voltage and current to determine the output load Ro. It selects three operating modes: three-phase, full-bridge, or half-bridge modes. The appropriate control strategy is then determined according to system requirements. Once the mode and strategy are set, a fitting function calculates the conduction time of the secondary-side MOSFETs based on the converter’s operating frequency fs and output load Ro. The system updates this value through the EPWM register, optimizing the drive waveforms of the primary and secondary-side MOSFETs. After updating, the system enters standby mode and waits for the next interrupt to continue dynamic adjustments.

A 2.5 kW experimental prototype using SiC devices was built. Experimental results show that half-bridge and full-bridge modes had higher efficiency under light-load conditions than the three-phase mode, effectively improving light-load efficiency. Under full-load conditions, applying the proposed synchronous rectification (SR) control improved efficiency in all three modes. Temperature tests indicate that SR control enhances system efficiency and reduces SR MOSFET heating.

Keywords:Three-phase CLLC resonant converter, phase-shedding strategy, synchronous rectification, extended harmonics, fitting mode

中图分类号:TM46

DOI: 10.19595/j.cnki.1000-6753.tces.242309

江苏省自然科学基金项目(BK20231500)和徐州市基础研究计划项目(KC22046)资助。

收稿日期 2024-12-19

改稿日期 2025-01-22

程 鹤 男,1987年生,副教授,硕士生导师,研究方向为新能源发电技术,新能源电动汽车,电力电子变换器,车载高功率密度充电器,新型电机设计,电机驱动系及其控制等。

E-mail: chenghecumt@163.com

徐 恺 男,1998年生,硕士研究生,研究方向为车载高功率密度充电器。

E-mail: 976671368@qq.com(通信作者)

(编辑 陈 诚)