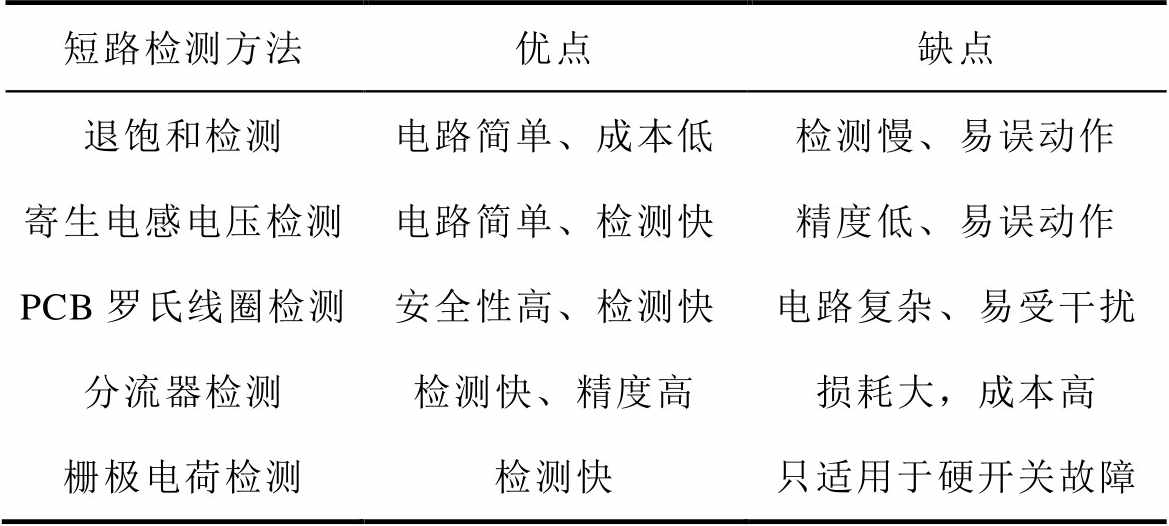

Tab.1 Comparison of advantages and disadvantages of different short-circuit detection schemes

短路检测方法优点缺点 退饱和检测电路简单、成本低检测慢、易误动作 寄生电感电压检测电路简单、检测快精度低、易误动作 PCB罗氏线圈检测安全性高、检测快电路复杂、易受干扰 分流器检测检测快、精度高损耗大,成本高 栅极电荷检测检测快只适用于硬开关故障

摘要 SiC MOSFET广泛应用于电力电子变换设备中,快速、准确且可靠的短路保护电路已成为推广其应用的关键技术之一。该文对SiC MOSFET的各类短路过程进行分析,利用器件短路时漏源极电压迅速增加的特点,设计短路保护电路的拓扑结构和功能,检测SiC MOSFET栅极和漏极电压,并将该信号进行分析、锁存、隔离、滤波处理,若器件发生短路,则输出短路信号给栅极驱动芯片。在此基础上,采用基本逻辑器件和高速器件设计保护电路,理论上分析计算该电路在不同短路类型下的响应时间。计入所有影响保护速度的因素,该电路能在600 ns内实现SiC MOSFET短路保护,尤其是在发生负载短路故障时能将短路保护时间缩短至200 ns以内,其响应速度受不同母线电压影响较小。搭建实验平台,测试了该电路在不同母线电压、短路类型、驱动能力等情况下的短路保护性能,实验结果与理论分析和设计要求相符合。

关键词:SiC MOSFET 短路保护 栅极电压检测 漏极电压检测

随着第三代宽禁带半导体的发展,以碳化硅金属氧化物半导体场效应晶体管(Silicon Carbide Metal-Oxide-Semiconductor Field-Effect Transistor, SiC MOSFET)为代表的功率器件具有开关和导通损耗小、工作频率高、热导率高、击穿场强高等优势[1-3]。相较于常规高压大功率硅基功率器件,SiC MOSFET更加适应于高压、高温、高频和高可靠性等应用领域[4-5]。然而与同量级硅基器件相比,SiC MOSFET的芯片面积更小、电流密度更大,导致其在短路状态下承受更强的电热应力,并且随着工作温度、驱动电压和母线电压的升高,其短路耐受时间也会越短,目前商业用SiC MOSFET的短路耐受时间约为2 ms,如果进一步考虑重复短路对器件寿命的影响,该时间会更短[6-7]。因此在SiC MOSFET短路发生时,需要保护电路快速检测和动作,同时还要求该电路具有对原电路影响小、精度高、损耗低、避免过保护和欠保护等特点。

目前,SiC MOSFET的短路保护方法主要是在绝缘栅双极型晶体管(Insulated Gate Bipolar Transistor, IGBT)短路保护的基础上,针对SiC MOSFET短路时表现出的外在特性进行的改进,具体包含五种方案[8]:退饱和检测(Desaturation fault protection, DESAT)、寄生电感电压检测、PCB罗氏线圈检测、分流器检测和栅极电荷检测。

DESAT[9-10]是最典型的短路保护电路,其原理简单、成本低,被广泛应用于IGBT短路保护中。其主要缺点是,为了避免误保护,需要在器件开通时添加一段消隐时间屏蔽短路检测,这使得保护速度延缓。若将IGBT的DESAT电路直接应用于SiC MOSFET,还会导致器件因动作时间过长而损坏,以及因判断不准确而使器件误关断等问题。

寄生电感电压检测[11-13]使用SiC MOSFET器件的功率源极和辅助源极之间的寄生电感,短路发生时通过器件的电流迅速增加,较大的di/dt会在寄生电感上产生压降,经处理后可得到器件漏源极电流大小,进而判断其是否发生短路。该方案成本低、无盲区,易于集成于驱动芯片内。但当短路回路中的电感值较大时,di/dt减小,会导致测量精度下降,且器件开通时也会产生较大di/dt,造成保护电路误触发,此外该方案还对寄生电感上的噪声特别敏感。

PCB罗氏线圈检测[14-15]方案,直接检测通过SiC MOSFET的漏源极电流,判断器件是否短路。该方案的测量元件与主电路相隔离,安全性高,且测量迅速,但PCB罗氏线圈的设计和短路信号处理较为复杂且难以实现,检测易受干扰。

分流器检测通过测量串接在主电路中的采样电阻两端压降,利用欧姆定律求得回路电流来判断器件是否发生短路。该方案结构简单、检测速度快、测量精度高。但由于采样电阻的存在,会导致成本增加、发热量大以及额外的功率损耗等问题。

电力电子器件在正常开通时,其栅极电荷值大于发生硬开关短路时的电荷值,通过对栅极电荷检测[16]可快速判断其是否发生硬开关故障,但SiC MOSFET的米勒电容较小,正常开通时米勒效应不明显,易造成保护误触发,且该方案无法实现负载短路故障的检测及保护。

上述五种对SiC MOSFET的短路保护方法各有优劣,表1对各个方法的优缺点进行总结与对比。

表1 不同短路检测方法优缺点对比

Tab.1 Comparison of advantages and disadvantages of different short-circuit detection schemes

短路检测方法优点缺点 退饱和检测电路简单、成本低检测慢、易误动作 寄生电感电压检测电路简单、检测快精度低、易误动作 PCB罗氏线圈检测安全性高、检测快电路复杂、易受干扰 分流器检测检测快、精度高损耗大,成本高 栅极电荷检测检测快只适用于硬开关故障

综上所述,尽管后四种方法的短路保护速度较快,但由于它们各自存在一些缺点,因此并未得到广泛应用。相比之下,DESAT方案具有电路简单、低成本和易于集成等优势,在实际应用中使用场景更为普遍,但其还存在以下问题:①检测过程存在盲区,且短路保护速度较慢,通常保护时间大于1 ms;②DESAT只能设定一个固定的消隐时间,无法适应多种使用工况。本文提出一种基于栅极和漏极电压检测的短路保护方案,继承了DESAT的优点,并克服其保护速度慢、适应性较差等缺点,从而实现了快速、准确且可靠的短路保护。

SiC MOSFET发生短路故障时器件的开关状态按类型可分为两类:硬开关故障(Hard Switching Fault, HSF)、负载短路故障(Fault Under Load, FUL)。

HSF指的是SiC MOSFET在开通前,其漏源极电压较高且回路阻抗较小,当器件开通时立即发生短路,类似的情况如串扰引起的SiC MOSFET误开通或器件损坏导致的桥臂直通;FUL指SiC MOSFET在正常工作且完全开通后,由于外部电路发生故障,导致SiC MOSFET漏源极电流迅速增加而达到短路状态,类似的状况有相间短路、对地短路等。

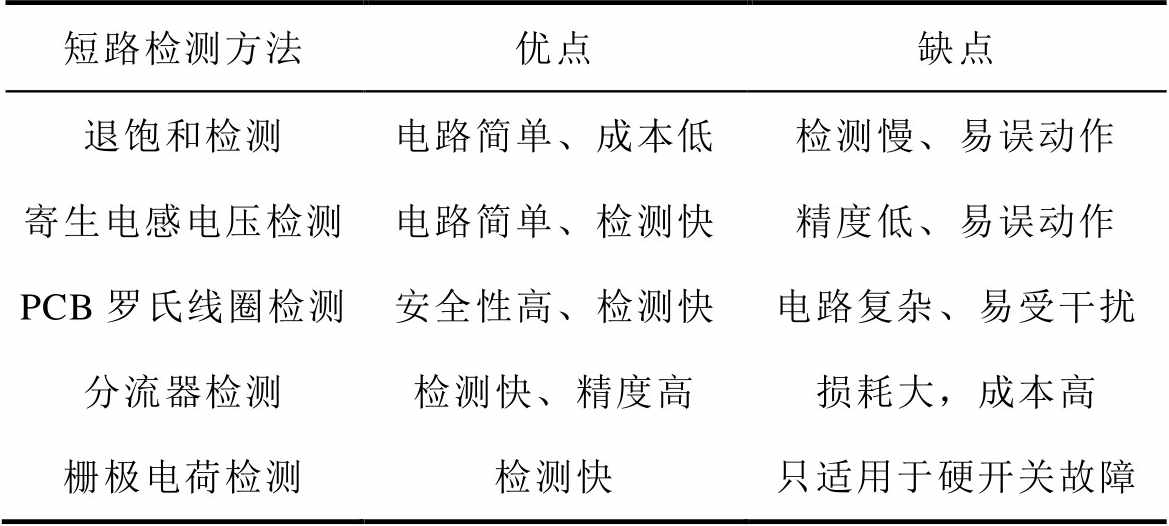

为分析SiC MOSFET短路特性,通常利用双脉冲测试电路进行实验,其电路拓扑如图1所示。双脉冲测试根据需要可设定多种实验工况,被广泛运用于电力电子器件的各种性能测试中。图1中,Q1、Q2为SiC MOSFET,VDC为直流电压源,CDC为母线支撑电容,Lload为负载,Lsc为短路时拓扑等效电感。

图1 双脉冲测试电路拓扑

Fig.1 The circuit of double pulse test

测试前需保持栅极驱动1、2输出低电平。用短粗铜棒代替负载电感Lload,此时测试对象Q2漏源极电压Vds约等于母线电压VDC,当栅极驱动2输出高电平时,由于主回路阻抗较小,Q2即发生HSF;用合适的阻性负载代替Lload,使Q2处于开通状态,当栅极驱动1输出高电平,就可让Q2实现FUL。

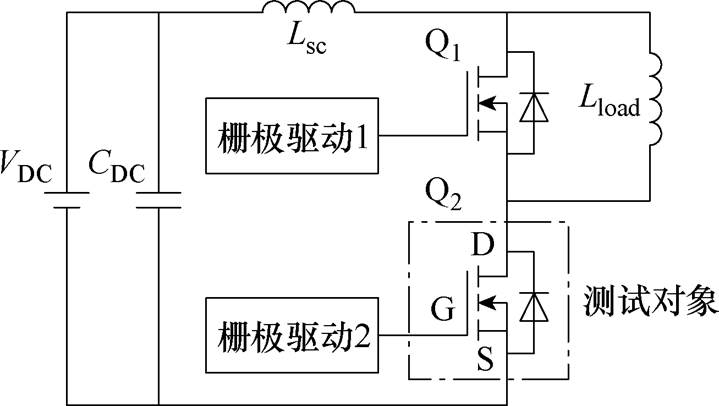

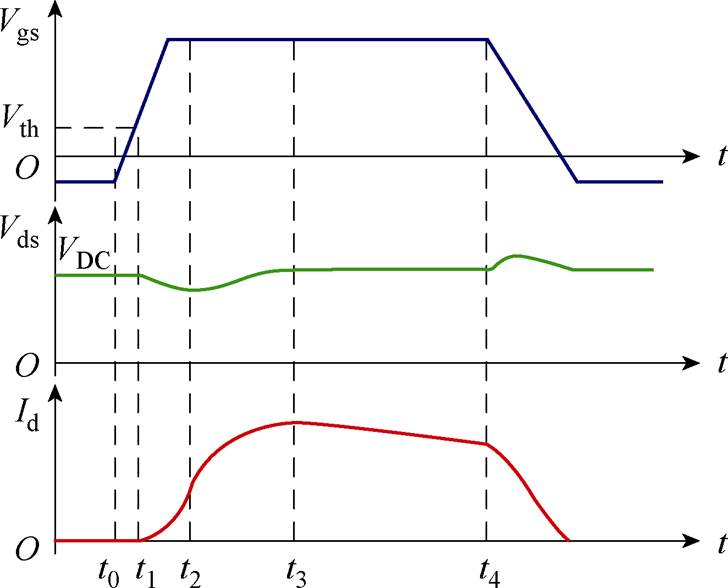

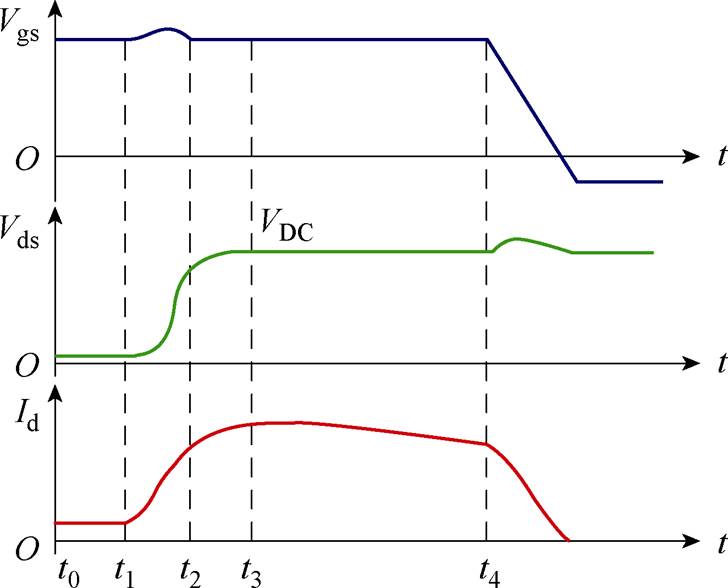

当SiC MOSFET发生HSF时,其短路阻抗较小,回路的电感值通常只有零点几微亨,所以短路时电流变化率较大,其漏源极电流能迅速超过器件的额定值,造成严重的短路。SiC MOSFET发生HSF过程可分为五个阶段,其电压电流波形如图2所示。

第一阶段t0~t1:在栅极电压Vgs未到达开通阈值Vth之前,器件处于截止状态,漏源极电压Vds约等于母线电压VDC,漏极电流Id≈0。

第二阶段t1~t2:t1时刻,Vgs达到阈值电压Vth,短路发生。随后Id加速上升,过大的Id使得其结温不断升高,由于SiC MOSFET导通电阻与结温呈正相关,因此也将不断增加,所以di/dt在t2时刻达到一个最大值后降低。同时,过大的di/dt在短路等效电感Lsc上产生电压,导致SiC MOSFET的Vds下降。

图2 HSF波形

Fig.2 The waveforms of HSF

第三阶段t2~t3:随着di/dt的不断降低,Id增长速度逐渐减慢,在t3时刻达到电流最大值。此过程中还伴随着Vds上升至VDC附近。

第四阶段t3~t4:加载在SiC MOSFET上的Vds和Id产生较大的功率,以热能损耗的形式使得器件结温迅速升高,导致沟道载流子迁移率降低,di/dt变为负数,Id下降。

第五阶段t4之后:若短路保护及时动作,驱动SiC MOSFET关断,则Id会迅速下降,同时伴随着因di/dt作用在Lsc上引起的Vds电压上升,直至SiC MOSFET完全关断。

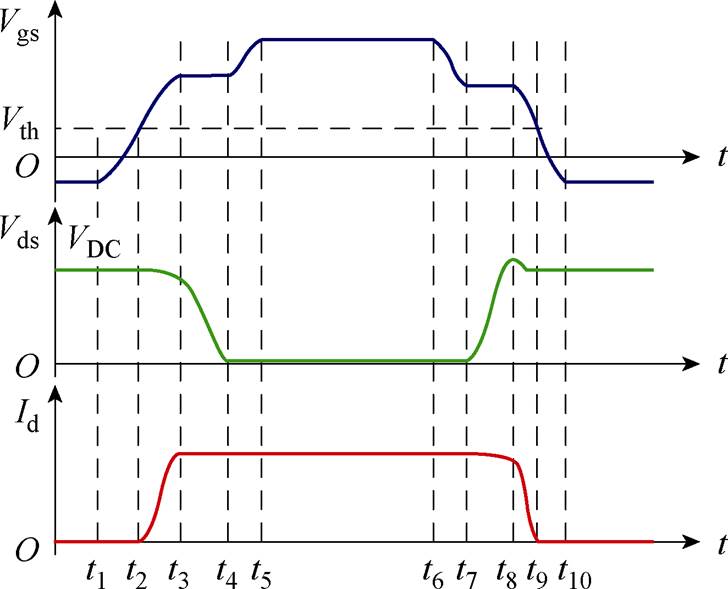

SiC MOSFET发生FUL时的电压电流波形如图3所示,其过程也分为五个阶段。

图3 FUL波形

Fig.3 The waveforms of FUL

第一阶段t0~t1:SiC MOSFET正常工作且处于完全导通状态,Vgs为高电平,Vds为器件的正向导通压降,Id为正常的负载电流。

第二阶段t1~t2:t1时刻发生短路,Id迅速上升至饱和电流,Vds也迅速上升至VDC附近,由于di/dt作用在Lsc上,使得Vds比VDC小,同时较大的漏源极电压变化率du/dt会产生位移电流对米勒电容进行充电,造成Vgs出现电压尖峰。

第三、四、五阶段t2之后:同HSF,不再赘述。

通过对SiC MOSFET发生HSF和FUL时的波形进行分析,发现在短路过程中都有着共同的特征:①栅极电压Vgs大于阈值电压Vth,且Vgs上升时无米勒效应;②漏源极电压Vds快速上升至母线电压附近;③漏极电流Id迅速超过器件额定电流并增长到某一值后略微下降。现有的五种主流SiC MOSFET的短路检测方案都是基于上述三种短路特性中某一特性所设计,虽能实现短路检测,但在准确性、快速性及可靠性上都各有局限。

本文提出一种短路保护电路,将栅极电压检测和漏源极电压检测相结合,通过检测栅极电压判断器件是否完全开通,检测漏源极电压判断器件电压是否超过设定值,当两个条件都满足时,则触发短路保护。该电路优点如下:①短路检测及保护响应速度快;②针对HSF,可通过改变栅极驱动能力来调节短路保护时间的长短;③保护速度受母线电压影响较小;④该电路结构简单,成本低且易集成于芯片内。

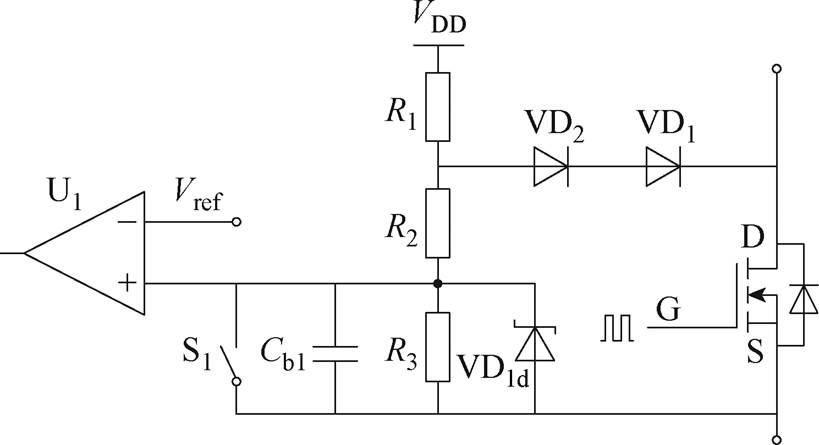

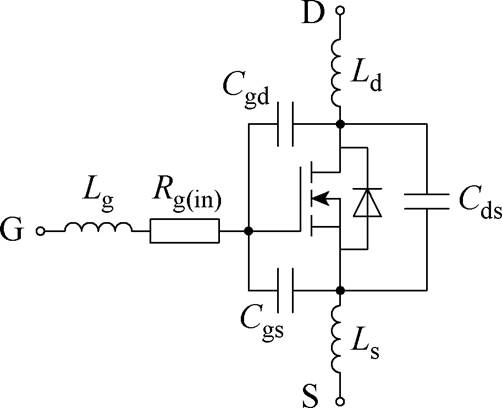

目前SiC MOSFET及IGBT的短路保护通常使用DESAT方案,故选取最为经典的电压源型DESAT具体分析其拓扑及工作原理,其电路如图4所示。

图4 电压源型DESAT电路

Fig.4 The circuit of voltage source DESAT

开关管S1的驱动信号与SiC MOSFET相反,若SiC MOSFET处于关断状态,其漏源极电压Vds接近母线电压VDC,快恢复二极管VD1、VD2反向截止(为减小二极管的寄生电容对电路影响,通常会使用两个及以上二极管串联),高压隔离,此时开关管S1处于开通状态,迅速给消隐电容Cbl放电,将比较器U1正输入端电压拉低,屏蔽检测。

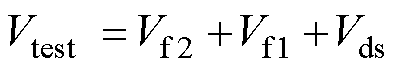

当SiC MOSFET开通时,结合图5所示器件正常开关的波形进行分析:t1时刻栅极驱动输出高电平,开关管S1关断,此时器件未完全开通,Vds仍处于较高水平,VD1、VD2反向截止,电压源VDD通过电阻R1、R2和R3给Cbl充电,使U1正输入端电压逐渐升高。这个过程会持续到t4时刻,当Vds降至较低水平时,VD1、VD2变为正偏,此时VD2阳极电压Vtest为

(1)

(1)

式中,Vf1、Vf2分别为二极管VD1、VD2正向导通压降。Vtest再经R2、R3分压输出到U1正输入端。

图5 SiC MOSFET正常开关波形

Fig.5 The waveforms of SiC MOSFET under normal operating

倘若器件发生短路,Vds迅速升高,VD1、VD2再次反向截止,Cbl开始充电,直至其电压超过所设置的参考电压Vref,触发短路保护,使SiC MOSFET关断。

消隐电容Cbl在t1~t4时间段内通过减缓比较器输入端电压的上升速度,屏蔽SiC MOSFET开通过程中的短路保护防止保护误动作,提高了该电路的实用性。但通常DESAT只能通过调节消隐电容大小来设置一个固定的消隐时间,故消隐时间通常设置为器件开通时间的1.2~2倍。

然而,较长的消隐时间会减缓短路检测及保护的响应速度,且单一的消隐时间无法满足器件在各种工况运行时的要求。此外,开关管S1为了实现给Cbl快速放电的功能,通常设置的回路阻抗较小,导致流过S1瞬时电流较大,加上长期处于高频开关状态,易损坏造成电路失效。

本文提出一种基于栅极和漏极电压检测的快速短路保护电路,取消了DESAT电路中的消隐电容Cbl和开关管S1,改用检测SiC MOSFET栅极和漏源极电压来判断器件是否发生短路,来实现快速准确且可靠的短路检测及保护。

2.2.1 电路拓扑及原理

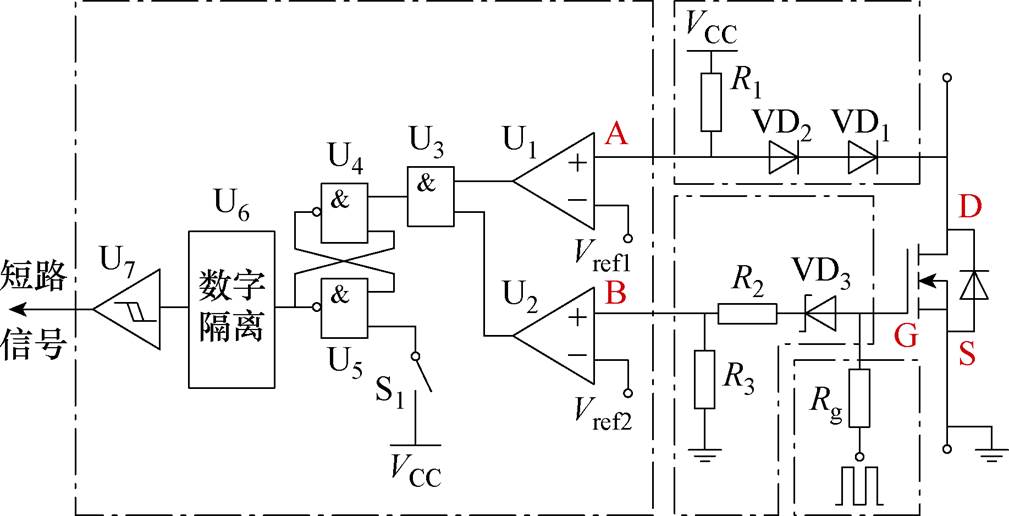

本文所提出的基于栅极和漏极电压检测的快速短路保护电路拓扑如图6所示。

图6 基于栅极和漏极电压检测的短路保护电路拓扑

Fig.6 The short-circuit protection circuit based on grid and drain voltage detection

该电路按功能还可分为四部分:驱动电路、漏源极电压检测电路、栅极电压检测电路和逻辑处理电路。

驱动电路通过外部的栅极驱动器输出驱动信号,经电阻Rg传递到SiC MOSFET的栅极,来控制器件的开通和关断,通过改变Rg阻值可以调节器件开关速度。

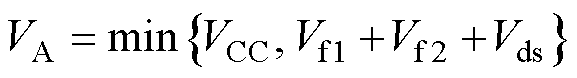

漏源极电压检测电路主要由电阻R1,高压二极管VD1、VD2及SiC MOSFET串联组成,VD1、VD2可以隔离漏源极高压,防止损坏检测电路,检测点A的电压VA可表示为

(2)

(2)

式中,VCC为供电电压;Vds与Id的对应关系可通过查询SiC MOSFET手册中输出特性曲线得知。

栅极电压检测电路由肖特基二极管VD3及电阻R2、R3串联组成,VD3起隔离栅极负压作用,防止电压超出比较器处理范围,检测点B的电压VB可表示为

(3)

(3)

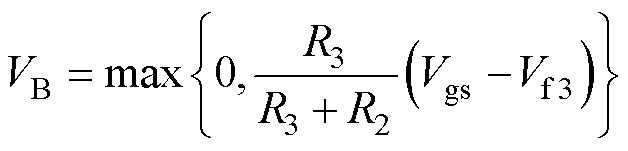

式中,Vf3为二极管VD3正向导通压降。含寄生参数的SiC MOSFET等效电路如图7所示。器件开通时,Vgs在栅极驱动器输出的低电平VEE和高电平VDD之间切换。

图7 SiC MOSFET等效电路

Fig.7 The equivalent circuit of SiC MOSFET

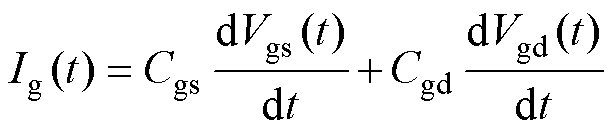

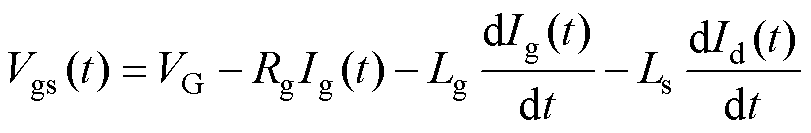

结合图6、图7,以器件开通过程为例,将这个过程简化为:栅极驱动器输出的电压VG通过栅极驱动电阻Rg(包含外接驱动电阻以及栅极内部电阻Rg(in))和栅极、源极杂散电感Lg、Ls给SiC MOSFET的栅源极电容Cgs和栅漏极电容Cgd充电,得到

(4)

(4)

(5)

(5)

式中,Ig为栅极驱动器输出的电流,联合式(3)~式(5)即可解出检测点B电压VB的准确值。

逻辑处理电路通过比较器U1、U2分别将检测到的电压与预先设定的参考电压Vref1和Vref2比较,输出比较信号到与门U3,当检测到短路故障时,U3输出高电平到SR锁存器(由或非门U4、U5组成)防止信号消失,再经数字隔离U6将该信号输出到施密特触发器U7,经其处理后输出短路信号到SiC MOSFET驱动控制侧,由栅极驱动器驱动器件关断,其中U7用于减少噪声及瞬态脉冲对电路的影响,按键S1为故障信号复位按键。

为进一步提高该短路保护电路的可靠性,还可在电路中增加滤波电路,并根据不同的使用场景进行相应调整,滤波造成的信号延时通常在10~30 ns。此外,还需在比较器前增加电压限幅电路防止比较器损坏。

2.2.2 电路参数设计

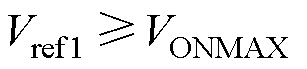

为实现快速的SiC MOSFET短路检测,防止器件损坏,需根据使用环境下的器件导通时正常工作最大的电流所对应的正向导通压降VONMAX选取合适的漏源极电压比较值,即

(6)

(6)

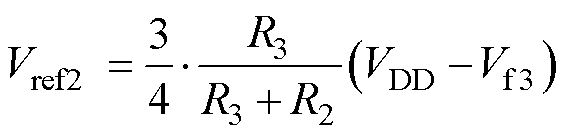

考虑到SiC MOSFET开关时的栅极和漏源极电压会有一个变化过程,如图5所示,在t3~t4、t7~t8阶段时Vds迅速变化造成Vgs出现米勒平台,为增加此方案的可靠性,将栅极比较值设置得大于米勒平台电压,可避免短路保护在SiC MOSFET正常开关期间保护误触发。本文选取的实际栅极电压比较值约为栅极驱动电压高电平VDD的3/4,即

(7)

(7)

Vref1和Vref2通过在0~VCC之间串联电阻进行分压得到。

2.2.3 保护过程分析

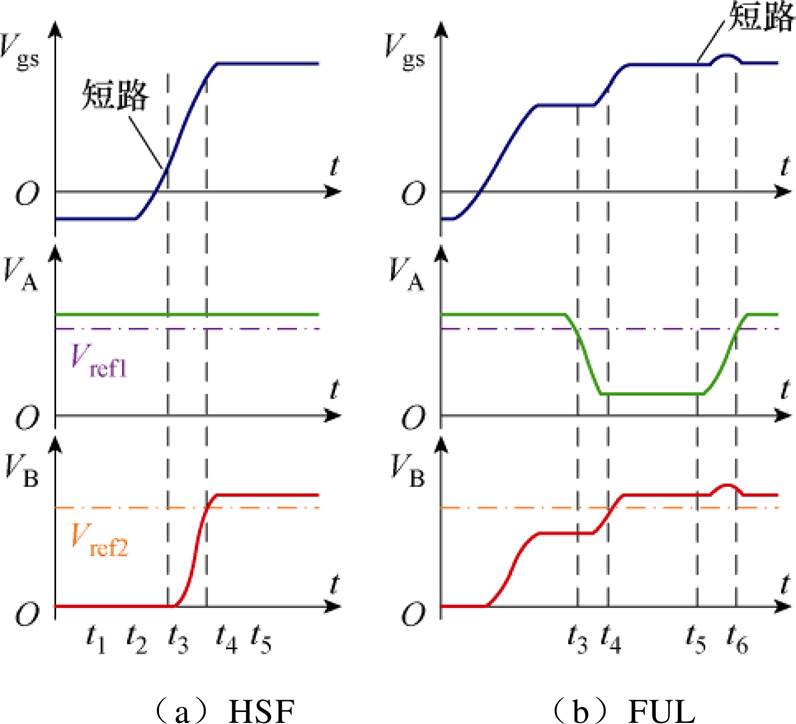

该电路检测点A和B分别在发生不同短路类型时的电压波形如图8所示。

图8 检测点电压波形

Fig.8 The voltage waveforms of detection point

若SiC MOSFET发生HSF,在t1时刻栅极电压上升至阈值电压,器件短路,此时VA>Vref1,VB<Vref2,经逻辑处理电路后,向外输出低电平。随着栅极电压的不断上升,VB也会跟着快速升高,在t2时刻VB>Vref2,经处理后输出高电平的短路信号驱动芯片,关闭SiC MOSFET。

若SiC MOSFET发生FUL,在t5时刻短路,此时由于VA<Vref1,VB>Vref2,不会触发保护,但随着SiC MOSFET退出饱和区,Vds迅速增大,导致VA电压上升,在t2时刻VA>Vref1触发短路保护。

SiC MOSFET正常开通时,Vds快速下降导致Vgs波形中出现米勒平台,当Vds趋于稳定后Vgs才会继续上升。利用这一条件,将Vref2值设为略小于栅极驱动电压值,可以防止SiC MOSFET开通时保护误动作。如图8b所示,在t3~t4阶段,VA、VB均小于所设参考电压,可提供一段死区时间,防止两个比较器同时输出高电平,SiC MOSFET正常关断时亦如此。此方法可代替传统DESAT中消隐电容的作用,无需提前设计消隐时间,且能适应器件不同的开通时间。

经分析,影响该保护电路速度的因素主要有四点:①HSF检测时间受短路时SiC MOSFET栅极电压上升速度影响,而栅极电压上升速度主要由栅极驱动能力大小决定;②FUL检测时间受短路时SiC MOSFET漏源极电压上升的速度影响,漏源极电压上升速度主要由器件栅极电压及漏源极电流大小决定;③所设定的电压参考值Vref1、Vref2影响短路检测的速度;④短路保护时间受电路中各种元器件的响应速度影响。

2.2.4 HSF保护响应速度分析

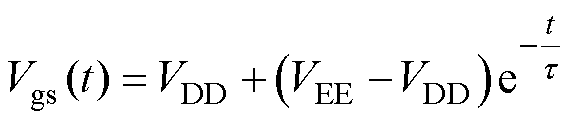

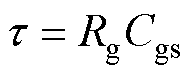

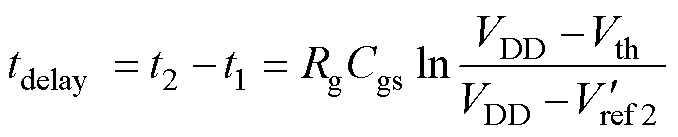

由于HSF发生前后SiC MOSFET漏源极电压Vds变化小,不考虑此电压变化给电路带来的影响,并忽略栅极驱动能力和杂散电感的影响,可将SiC MOSFET的HSF发生过程等效为栅极驱动电压VDD经电阻Rg向栅源极电容Cgs充电的过程,即

(8)

(8)

(9)

(9)

当Vth≤Vgs(t)≤ (见图8中t1~t2阶段)时,器件短路,但保护未触发。

(见图8中t1~t2阶段)时,器件短路,但保护未触发。

(10)

(10)

式中,tdelay为HSF检测延时; 为所设定的参考电压所对应的器件栅极电压实际电压。

为所设定的参考电压所对应的器件栅极电压实际电压。

此外还需考虑所设置滤波延时tfilter、逻辑处理电路的处理时间tproc以及驱动芯片传播延时tpd。当该电路检测到短路,并向外输出隔离的短路信号时,可通过拉低栅极驱动的输入电平或使能信号以及直接禁用驱动芯片等方法,使SiC MOSFET关断进而保护整个电路。除去SiC MOSFET关断时间外,完整的HSF短路检测及保护动作时间为

(11)

(11)

由于SiC MOSFET的Cgs为nF级,栅极驱动电阻小于20 W,这就导致Vgs变化的时间常数较小,正常情况下tdelay≤400 ns;因脉冲和噪声信号维持时间短,tfilter<30 ns,逻辑处理电路使用高速器件和基本逻辑器件,响应速度快,tproc≤20 ns。SiC MOSFET的驱动芯片传播延时,通常tpd<150 ns,该电路在发生HSF故障下,可在600 ns内实现短路检测和保护动作。若选用tpd较小的驱动芯片,还可实现500 ns内的短路保护。

2.2.5 FUL保护响应速度分析

针对FUL,由于设置的退饱和动作值一般只有几伏,器件短路即发生退饱和,几乎无检测延时,所以FUL短路保护时间为

(12)

(12)

故该电路可在200 ns内实现FUL短路保护。

该电路在SiC MOSFET发生不同类型短路故障的保护时间均低于行业所设定的2 ms,提高了短路保护速度,减少器件的性能退化,防止设备损坏。

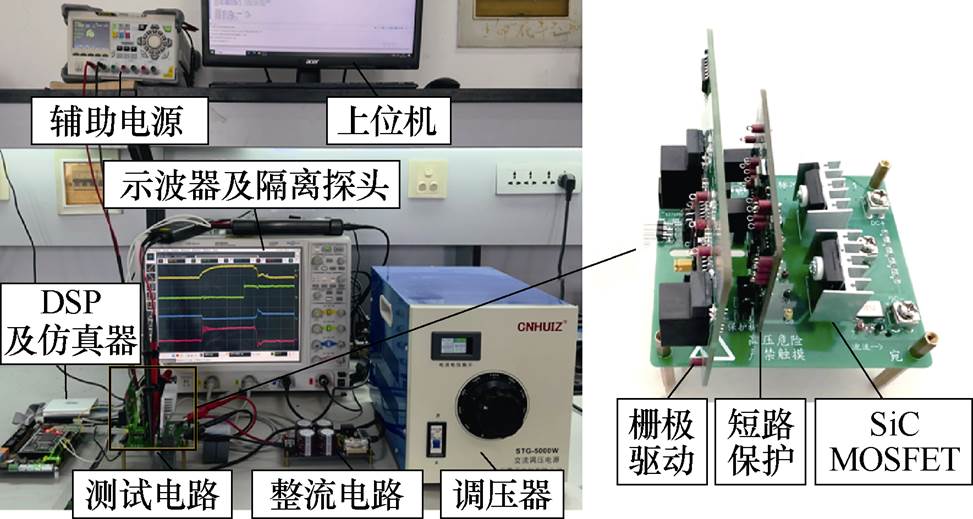

为了验证所提出的电路对SiC MOSFET短路保护性能,以及测试该电路在不同短路故障、母线电压及栅极驱动能力等因素下所受的影响,将所设计的电路接入图1所示的双脉冲测试电路,完成测试平台的搭建,如图9所示。

图9 实验平台

Fig.9 The experimental platform

利用DSP产生PWM信号,经栅极驱动电路控制双脉冲测试电路的上下桥臂SiC MOSFET开通和关断。按第1节所述短路实现方案分别使SiC MOSFET发生HSF和FUL。

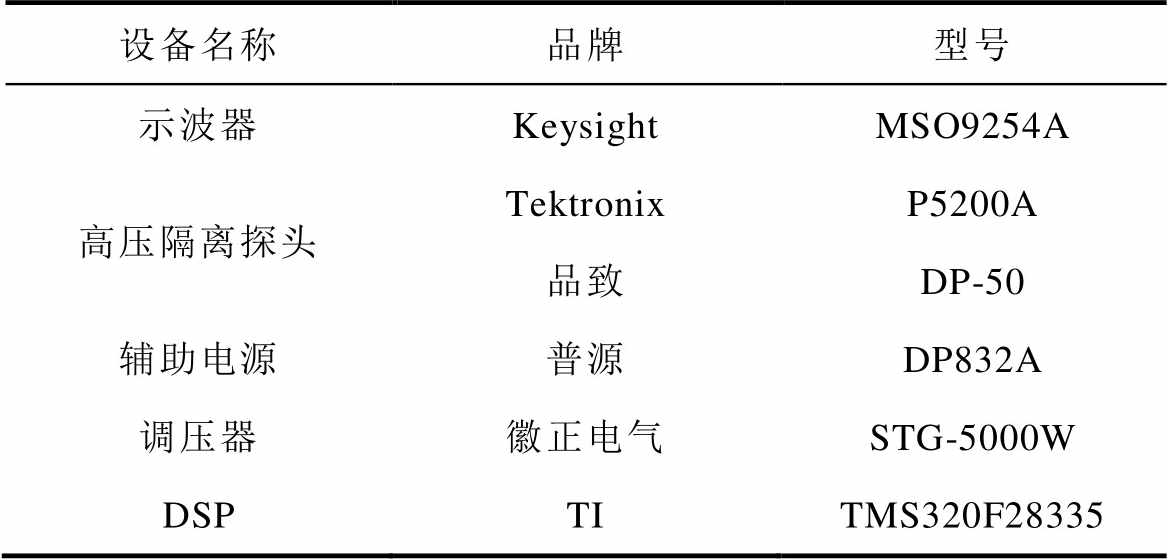

用于短路测试的SiC MOSFET为Wolfspeed公司的C3M0040120K(1 200 V, 66 A)。实验采用的主要设备及型号见表2。

表2 主要设备及型号

Tab.2 The main equipments and types

设备名称品牌型号 示波器KeysightMSO9254A 高压隔离探头TektronixP5200A 品致DP-50 辅助电源普源DP832A 调压器徽正电气STG-5000W DSPTITMS320F28335

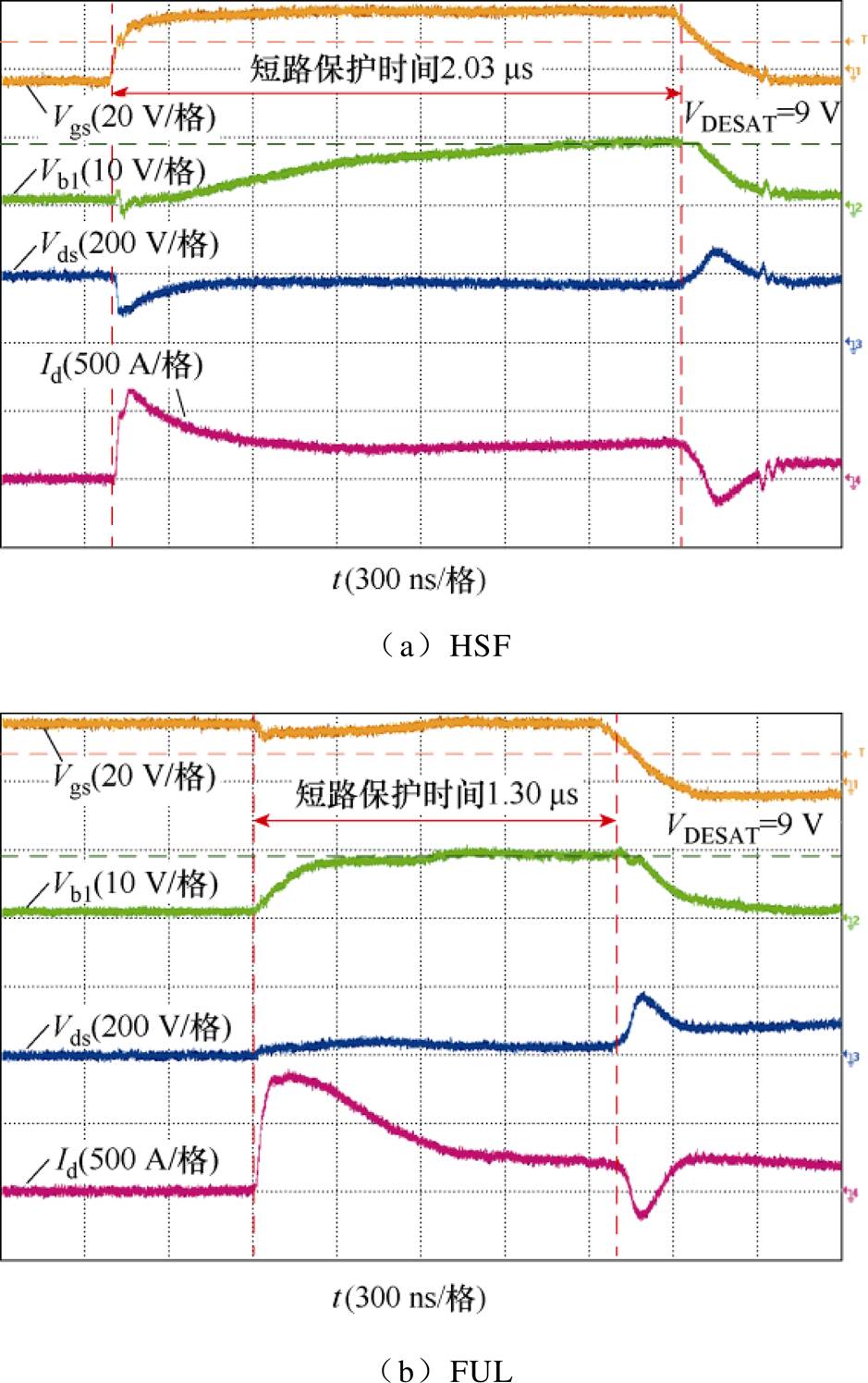

传统DESAT保护电路响应速度快慢主要取决于所设消隐时间。为了提高短路保护可靠性,通常会将消隐时间设计得较大,为测试传统DESAT的性能,选用TI公司集成此功能的栅极驱动芯片UCC21750,并设计其外围电路。该电路在母线电压为200 V时,SiC MOSFET发生HSF及FUL的波形如图10所示。图中,Vbl为消隐电容电压;VDESAT为短路保护参考电压。

图10 DESAT短路保护波形

Fig.10 The waveforms of DESAT short circuit protection

从实验结果可以看出,在母线电压为200 V时,传统DESAT保护电路在SiC MOSFET发生不同类型的短路时,需1~2 ms的时间才检测出短路故障,并将SiC MOSFET关断,其消隐时间较大地限制了保护响应速度。

3.2.1 硬开关故障

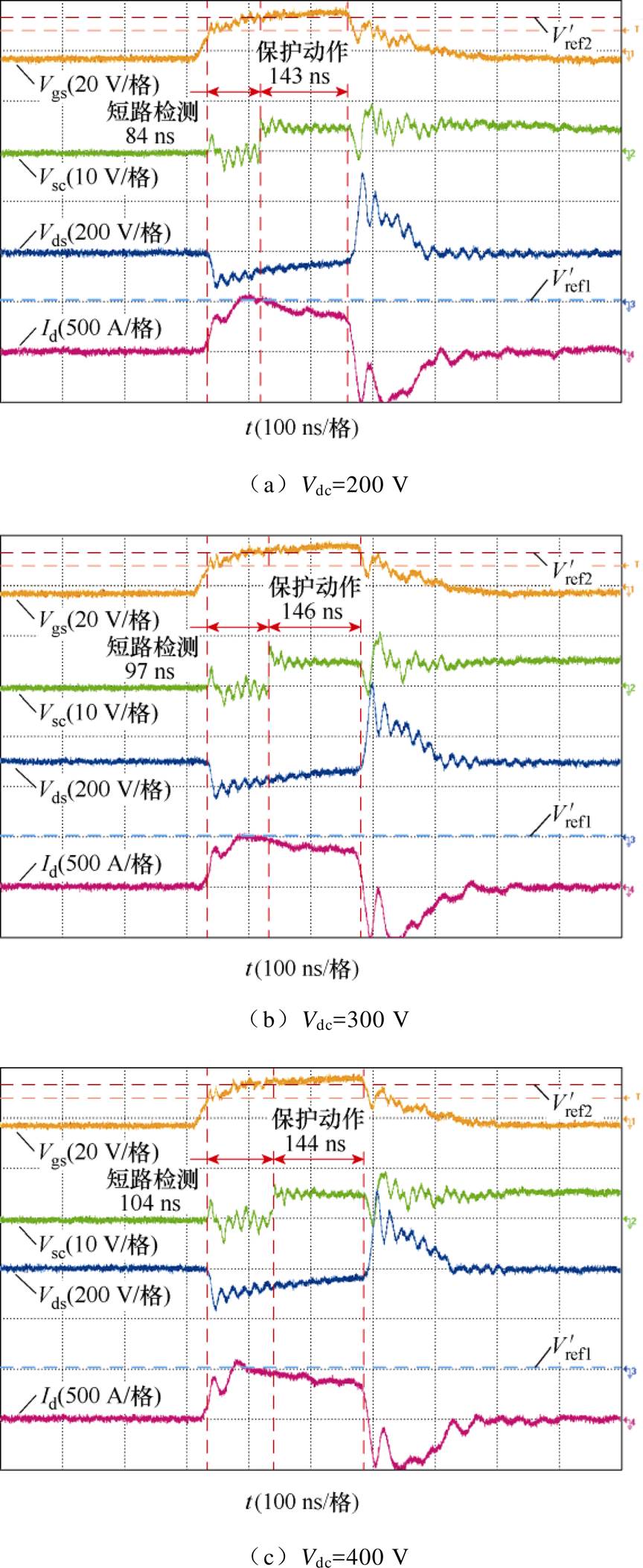

为测试所提出的短路保护电路针对SiC MOSFET在不同母线电压下发生HSF的响应情况,采用和传统DESAT一致的实验方案,并将栅极驱动芯片UCC21750的DESAT功能禁用,此外用短粗铜棒短接双脉冲测试平台上桥臂SiC MOSFET的漏源极,将母线电压Vdc分别设置为200、300和400 V进行实验,同时利用DSP发出PWM信号控制下桥臂开通制造HSF,其实验波形如图11所示。Vgs所采用的栅极驱动电压为+18 V和-2 V,栅极驱动电阻为6 W;Vsc为检测到的短路信号; 为所设定的参考电压所对应的器件漏源极实际电压,本实验设定Vref1=Vref2=3.3 V,对应的

为所设定的参考电压所对应的器件漏源极实际电压,本实验设定Vref1=Vref2=3.3 V,对应的 =2.5 V,

=2.5 V, =13.2 V。

=13.2 V。

图11 不同母线电压下的短路保护实验波形

Fig.11 The experimental waveforms of short-circuit protection at different bus voltages

短路保护响应时间可分为短路检测时间和保护动作时间两部分,短路检测时间包含短路检测延时、滤波延时以及逻辑处理电路的处理时间,保护动作时间为驱动芯片传播延时。在SiC MOSFET发生HSF时相应的短路检测时间见表3。保护动作时间大约为150 ns。

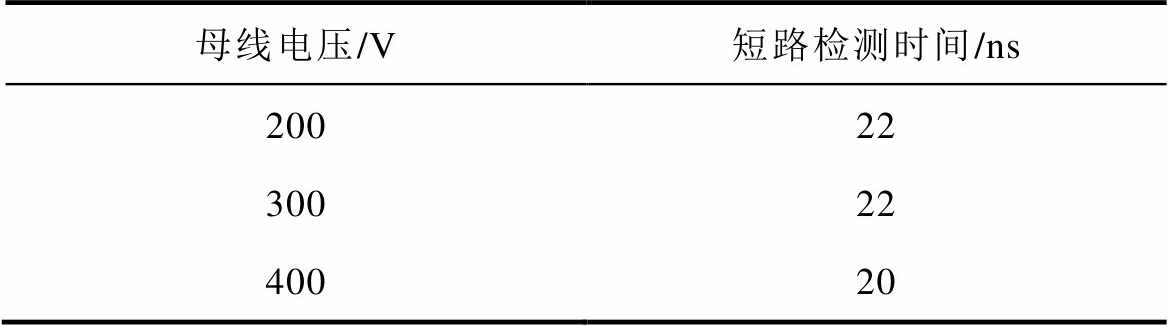

表3 不同母线电压下短路检测时间

Tab.3 The short-circuit detection time at different bus voltages

母线电压/V短路检测时间/ns 20084 30097 400104

由图11和表3可看出,所提出的短路保护方案受母线电压影响较小,且在该环境下短路保护时间均小于300 ns。

3.2.2 负载短路故障

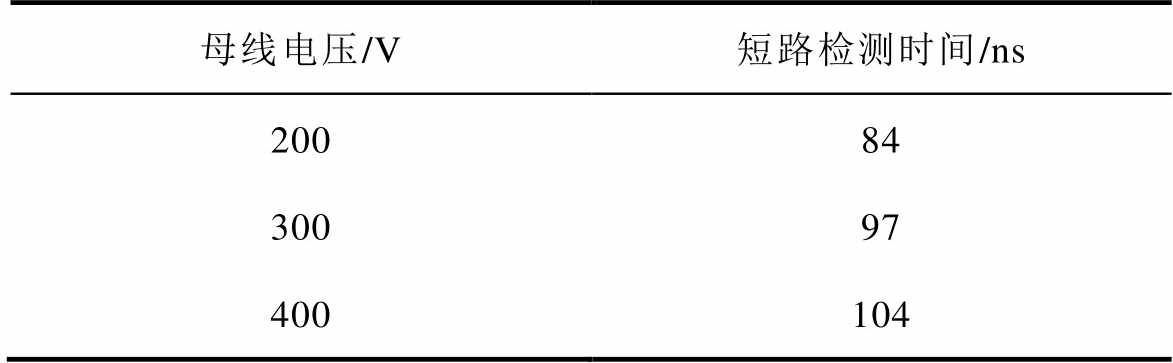

通过使能栅极驱动芯片的控制引脚,将双脉冲测试平台的下桥臂SiC MOSFET保持开通状态,利用DSP和栅极驱动芯片控制上桥臂器件开通,使被测SiC MOSFET发生FUL。并设置不同母线电压进行实验。实验波形如图12所示。

图12 不同母线电压下的短路保护实验波形

Fig.12 The experimental waveforms of short-circuit protection at different bus voltages

在SiC MOSFET发生FUL时相应的短路检测时间见表4。其保护动作时间同HSF实验。

表4 不同母线电压下短路检测时间

Tab.4 The short-circuit detection time at different bus voltages

母线电压/V短路检测时间/ns 20022 30022 40020

因为HSF发生前,被测SiC MOSFET已经完全开通,也就意味着其栅极电压处于高电平状态,发生短路时,只要发生退饱和现象就会迅速检测到短路故障,比起HSF实验去掉了栅极电压上升时间所带来的延时,实现极快的FUL检测及保护速度。实验表明,所提出的短路保护可在FUL发生200 ns内实现短路检测和保护动作,且受母线电压影响小。

部分传统DESAT保护在设计时会考虑到栅极驱动能力对SiC MOSFET开通时间带来的影响,根据实际工况优化其消隐时间,但在实际应用中还会通过调节栅极驱动电阻的大小来控制SiC MOSFET开关速度,进而调节器件开关损耗或抑制器件上的关断过电压等。针对实际情况调节DESAT的消隐时间工作量大、费时费力。因此大部分DESAT保护的消隐时间往往设置的较大以满足各种工况,但其又与SiC MOSFET较短的短路耐受时间相互矛盾。

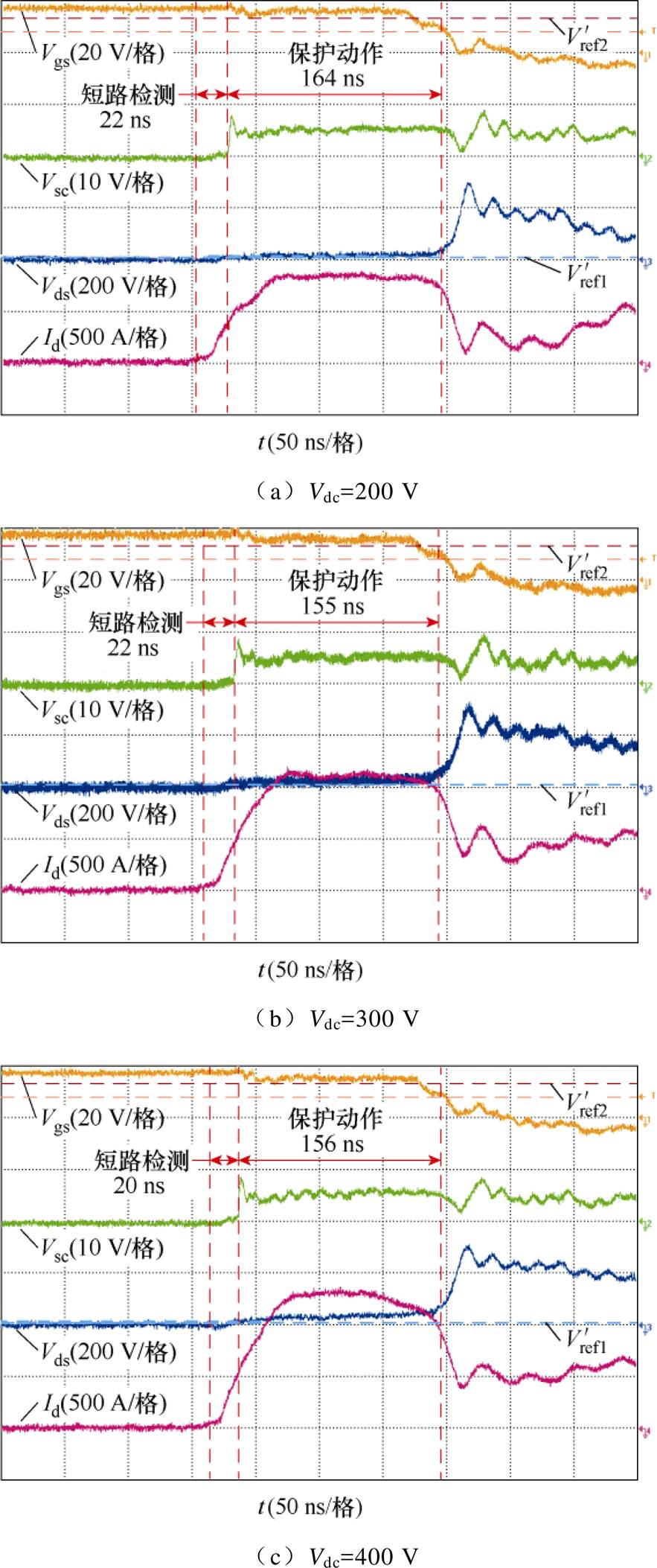

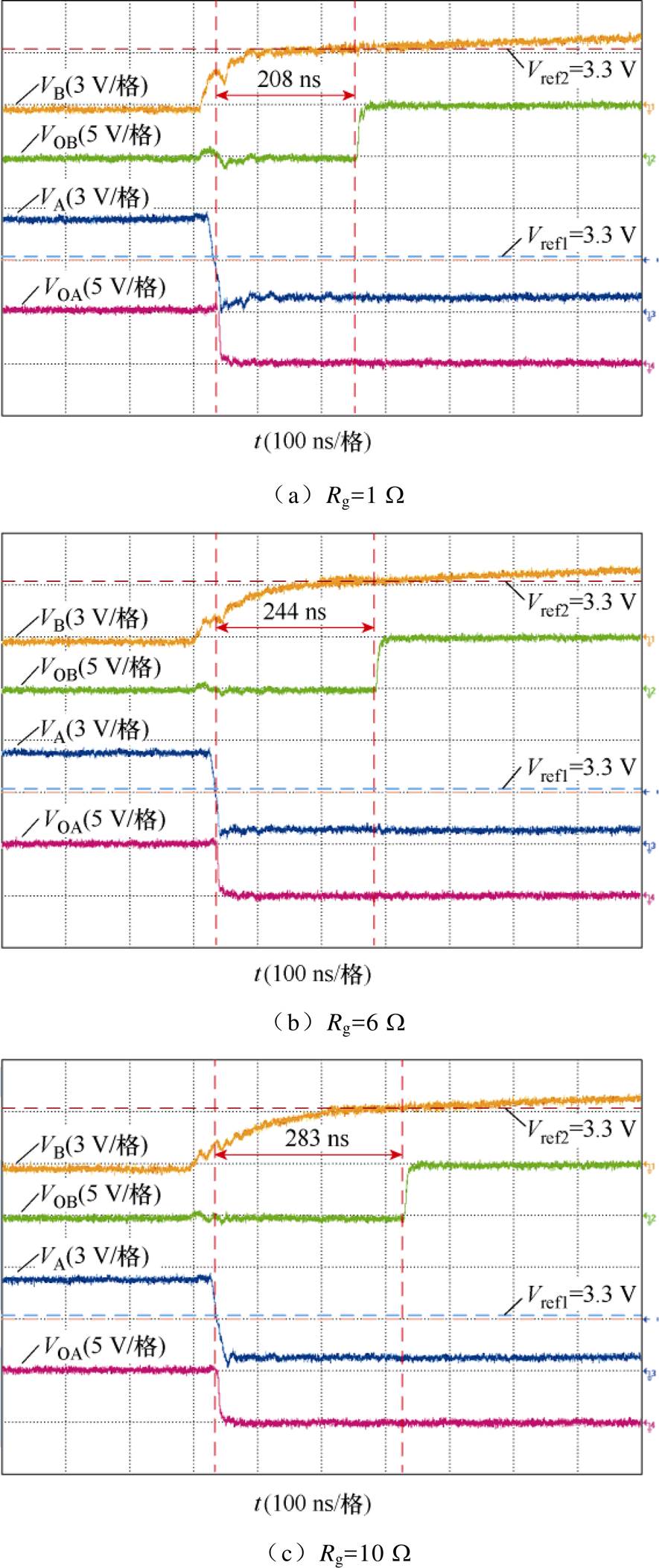

所提出的短路保护电路通过检测栅极电压来判断SiC MOSFET是否开通,完美地解决了因器件的开通时间所导致保护误动作的问题。因SiC MOSFET开通时间受栅极驱动能力影响,所以分别用1、6及10 W 的栅极驱动电阻来限制SiC MOSFET开通速度进行实验,并观察器件正常开通时两个比较器输入端的电压波形,实验波形如图13所示。VOB为比较器U2输出电压VOA为比较器U1输出电压;Vref1、Vref2为所设定的参考电压。

图13 不同栅极驱动电阻下的检测点电压波形

Fig.13 Test point voltage waveforms under different grid drive resistance

由实验结果可以看出,SiC MOSFET在正常的开通过程中两个比较器不会同时输出高电平,有效地防止了器件在正常工作时短路保护误动作。随着栅极驱动电阻的增大,SiC MOSFET的开通速度也会减慢,相应的HSF短路保护检测时间也会增加。

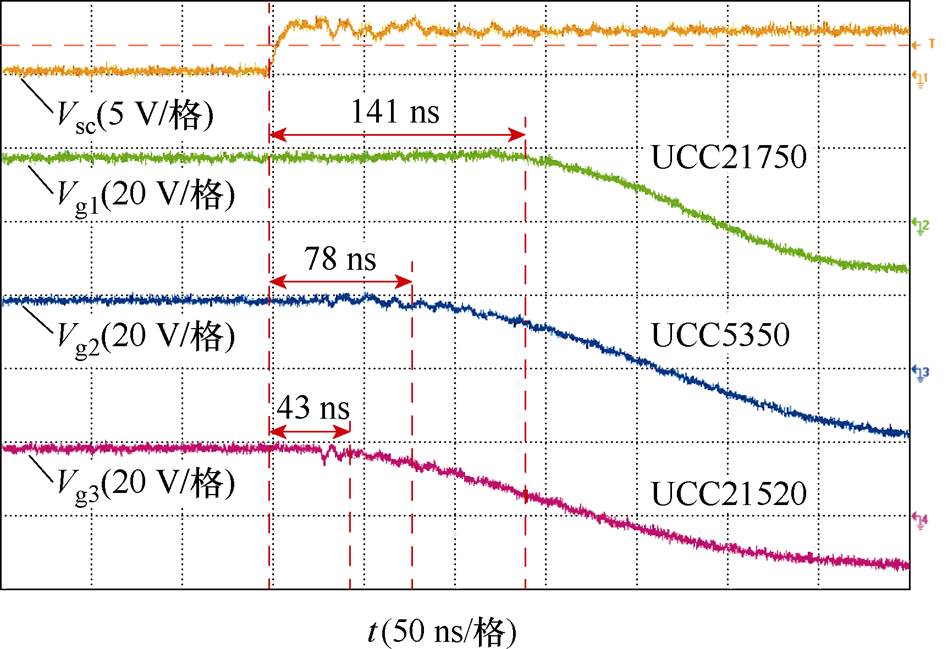

在SiC MOSFET短路保护过程中,保护动作时间同样影响着保护的响应速度,本文所提出电路的保护动作时间主要取决于栅极驱动芯片的性能,故采用TI公司生产的不同级别的驱动芯片对该电路进行测试,所采用的芯片型号分别为UCC21750、UCC5350、UCC21520。不同栅极驱动芯片的保护实验波形如图14所示,Vsc为短路信号,Vg1、Vg2、Vg3分别为三种栅极驱动芯片输出的栅极电压。

图14 不同栅极驱动芯片的保护实验波形

Fig.14 The experimental waveforms of protection at different grid driver chips

从实验结果可以看出,以上三种驱动芯片的保护动作时间差异较大,保护动作时间在40~150 ns内。栅极驱动芯片在技术方面和器件参数存在一定差异,UCC21520相较于UCC21750功能较少,其电路结构简单且滤波器较少,故其保护动作时间较短,经实验测试仅为43 ns。由于所设计的保护电路已包含施密特触发器和外部滤波电路,故可通过选用延时较小的栅极驱动芯片来提升所设计电路的响应速度。

为了测试所设计的短路保护电路的可靠性,分别对不同母线电压下的HSF及FUL短路保护进行测试,实验结果显示,该保护电路均能实现快速短路保护。此外还分别测试了SiC MOSFET在10、50及100 kHz的开关频率下,正常的空载和带载实验,实验中该短路保护电路均正常工作。

本文针对SiC MOSFET的短路过程及短路保护电路展开研究,分析了SiC MOSFET短路特性和DESAT电路的工作原理及不足,并提出了一种基于栅极和漏极电压检测的短路保护电路,计算了该电路在不同短路类型下的响应时间,对该电路的快速性、准确性、可靠性进行实物测试分析,并与DESAT进行对比实验。实验结果与理论分析和设计要求相符合,结果表示:

1)所设计的短路保护电路在SiC MOSFET发生不同类型短路故障的保护时间均低于器件短路耐受时间:对于硬开关故障,可以在600 ns内实现快速、准确且可靠的短路保护,如果选用延时更小的栅极驱动芯片,还可将短路保护时间缩短至500 ns内;在发生负载短路故障时能将SiC MOSFET短路保护时间缩短至200 ns以内。

2)所设计短路保护电路的保护速度受母线电压影响较小,具有结构简单、成本低、速度快、精度高、可靠性高等特点,为SiC MOSFET在不同使用工况下的短路故障提供一种可行的解决方案。

参考文献

[1] 陈杰, 邓二平, 赵子轩, 等. 不同老化试验方法下SiC MOSFET失效机理分析[J]. 电工技术学报, 2020, 35(24): 5105-5114.

Chen Jie, Deng Erping, Zhao Zixuan, et al. Failure mechanism analysis of SiC MOSFET under different aging test methods[J]. Transactions of China Elec- trotechnical Society, 2020, 35(24): 5105-5114.

[2] 王来利, 赵成, 张彤宇, 等. 碳化硅功率模块封装技术综述[J]. 电工技术学报, 2023, 38(18): 4947- 4962.

Wang Laili, Zhao Cheng, Zhang Tongyu, et al. Review of packaging technology for silicon carbide power modules[J]. Transactions of China Electro- technical Society, 2023, 38(18): 4947-4962.

[3] 邹铭锐, 曾正, 孙鹏, 等. 基于变电阻驱动的SiC器件开关轨迹协同调控[J]. 电工技术学报, 2023, 38(16): 4286-4300.

Zou Mingrui, Zeng Zheng, Sun Peng, et al. Coordinated switching trajectory regulation of SiC device using variable resistance gate driver[J]. Transactions of China Electrotechnical Society, 2023, 38(16): 4286-4300.

[4] 李佳炜. SiC MOSFET去饱和保护电路分析与优化[D]. 武汉: 华中科技大学, 2022.

Li Jiawei. Analysis and optimization of SiC MOSFET desaturation protection circuit[D]. Wuhan: Huazhong University of Science and Technology, 2022.

[5] 任鹏, 涂春鸣, 侯玉超, 等. 基于Si和SiC器件的混合型级联多电平变换器及其调控优化方法[J]. 电工技术学报, 2023, 38(18): 5017-5028.

Ren Peng, Tu Chunming, Hou Yuchao, et al. Research on a hybrid cascaded multilevel converter based on Si and SiC device and its control optimization method[J]. Transactions of China Electrotechnical Society, 2023, 38(18): 5017-5028.

[6] 康建龙, 辛振, 陈建良, 等. SiC MOSFET短路失效与退化机理研究综述及展望[J]. 中国电机工程学报, 2021, 41(3): 1069-1083.

Kang Jianlong, Xin Zhen, Chen Jianliang, et al. Review and prospect of short-circuit failure and degradation mechanism of SiC MOSFET[J]. Pro- ceedings of the CSEE, 2021, 41(3): 1069-1083.

[7] 文阳, 杨媛, 宁红英, 等. SiC MOSFET短路保护技术综述[J]. 电工技术学报, 2022, 37(10): 2538- 2548.

Wen Yang, Yang Yuan, Ning Hongying, et al. Review on short-circuit protection technology of SiC MOSFET[J]. Transactions of China Electrotechnical Society, 2022, 37(10): 2538-2548.

[8] 吴海富, 张建忠, 赵进, 等. SiC MOSFET短路检测与保护研究综述[J]. 电工技术学报, 2019, 34(21): 4519-4528.

Wu Haifu, Zhang Jianzhong, Zhao Jin, et al. Review of short-circuit detection and protection of silicon carbide MOSFETs[J]. Transactions of China Elec- trotechnical Society, 2019, 34(21): 4519-4528.

[9] 李虹, 胡肖飞, 王玉婷, 等. 适用于SiC MOSFET的漏源电压积分自适应快速短路保护电路研究[J]. 中国电机工程学报, 2024, 44(4): 1542-1552.

Li Hong, Hu Xiaofei, Wang Yuting, et al. Research on adaptive fast short-circuit protection circuit of drain-source voltage integration for SiC MOSFET[J]. Proceedings of the CSEE, 2024, 44(4): 1542-1552.

[10] Guo Zhehui, Li Hui. dv/dt sensing-based short-circuit protection for medium-voltage SiC mosfets[J]. IEEE Transactions on Power Electronics, 2023, 38(9): 10554-10558.

[11] Lee S, Kim K, Shim M, et al. A digital signal processing based detection circuit for short-circuit protection of SiC MOSFET[J]. IEEE Transactions on Power Electronics, 2021, 36(12): 13379-13382.

[12] Xue Ju, Xin Zhen, Wang Huai, et al. An improved di/dt-RCD detection for short-circuit protection of SiC mosfet[J]. IEEE Transactions on Power Elec- tronics, 2021, 36(1): 12-17.

[13] Ouyang Wenyuan, Sun Pengju, Xie Minghang, et al. A fast short-circuit protection method for SiC MOSFET based on indirect power dissipation level[J]. IEEE Transactions on Power Electronics, 2022, 37(8): 8825-8829.

[14] 项鹏飞, 郝瑞祥, 郝一, 等. 基于PCB罗氏线圈的SiC MOSFET简化短路保护电路研究[J]. 中国电机工程学报, 2022, 42(19): 7194-7204.

Xiang Pengfei, Hao Ruixiang, Hao Yi, et al. Simplified short-circuit protect circuits based on PCB rogowski coils for SiC MOSFETs[J]. Proceedings of the CSEE, 2022, 42(19): 7194-7204.

[15] Mocevic S, Wang Jun, Burgos R, et al. Comparison and discussion on shortcircuit protections for silicon-carbide MOSFET modules: desaturation versus rogowski switch-current sensor[J]. IEEE Transactions on Industry Applications, 2020, 56(3): 2880-2893.

[16] Picot-Digoix M, Richardeau F, Blaquière J M, et al. Quasi-flying gate concept used for short-circuit detection on SiC power MOSFETs based on a dual-port gate driver[J]. IEEE Transactions on Power Electronics, 2023, 38(6): 6934-6938.

Abstract SiC MOSFETs are extensively used in various power electronic conversion equipment. A fast, accurate, and reliable short-circuit protection circuit has become one of the key technologies for its popularization and application. When a short circuit occurs in the SiC MOSFET, the short-circuit protection circuit must achieve rapid detection and judgment, filter out interference signals, and drive the SiC MOSFET to turn off reliably. Additionally, this circuit should possess characteristics such as low loss and minimal impact on the main circuit.

In this paper, diverse short-circuit processes of SiC MOSFETs are analyzed. Considering the rapid increase advantage in drain-source voltage during device short-circuiting, the short-circuit protection circuit’s topology and functionality are designed with gate and drain voltage detection of the SiC MOSFET for decision-making. Subsequently, the signal is analyzed, latched, isolated, and filtered. If a device experiences a short circuit fault, the corresponding signal triggers output to activate gate driver chips for effective device protection. The short-circuit protection circuit possesses sufficient speed, accuracy, and reliability. Accordingly, a short-circuit protection circuit for SiC MOSFETs is designed using logic and high-speed components. The response time of the circuit under different short circuits is calculated, including detection delay, filtering delay, processing time, and propagation delay. The proposed short-circuit protection circuit allows for appropriate adjustment of filtering time to different operating conditions, which has good anti-interference performance.

The double-pulse test platform for SiC MOSFET is constructed to evaluate the short-circuit protection performance under different bus voltages, short-circuit types, driving capacities, and gate driver conditions. The experimental results agree with theoretical analysis and design requirements, confirming that the proposed circuit is superior to the classic desaturation fault protection (DESAT) circuit.

Theoretical analysis and experimental results demonstrate that the short-circuit protection circuit designed for different short-circuit faults exhibits a short protection time compared to the device's short-circuit tolerance time. Fast, precise, and reliable short-circuit protection can be achieved within 600 ns for hard switch faults. Selecting a grid driver chip with reduced delay can further reduce the short-circuit protection time to within 500 ns. In case of a fault under load, the short circuit protection time of SiC MOSFET can be minimized to less than 200 ns. The gate driver capability primarily affects its protection time, while the bus voltage has minimal effects. The greater the gate drive capability, the shorter the short circuit protection time. The proposed circuit exhibits a simple structure, low cost, high speed, high precision, and high reliability. It provides a viable solution for addressing the short-circuit fault in SiC MOSFET under various operating conditions and enhances the safety and reliability of SiC MOSFET equipment.

keywords:SiC MOSFET, short-circuit protection, grid voltage detection, drain voltage detection

DOI: 10.19595/j.cnki.1000-6753.tces.240129

中图分类号:TM46

国家自然科学基金区域创新发展联合基金资助项目(U21A20146)。

收稿日期 2024-01-19

改稿日期 2024-03-29

宛新春 男,1999年生,硕士研究生,研究方向为SiC MOSFET器件的应用和电机控制器设计。E-mail: 2210310112@stu.ahpu.edu.cn

陈其工 男,1961年生,二级教授,博士生导师,研究方向为网络控制、电力电子技术、智能微电网系统等。E-mail: qgchen@ahpu.edu.cn(通信作者)

(编辑 陈 诚)