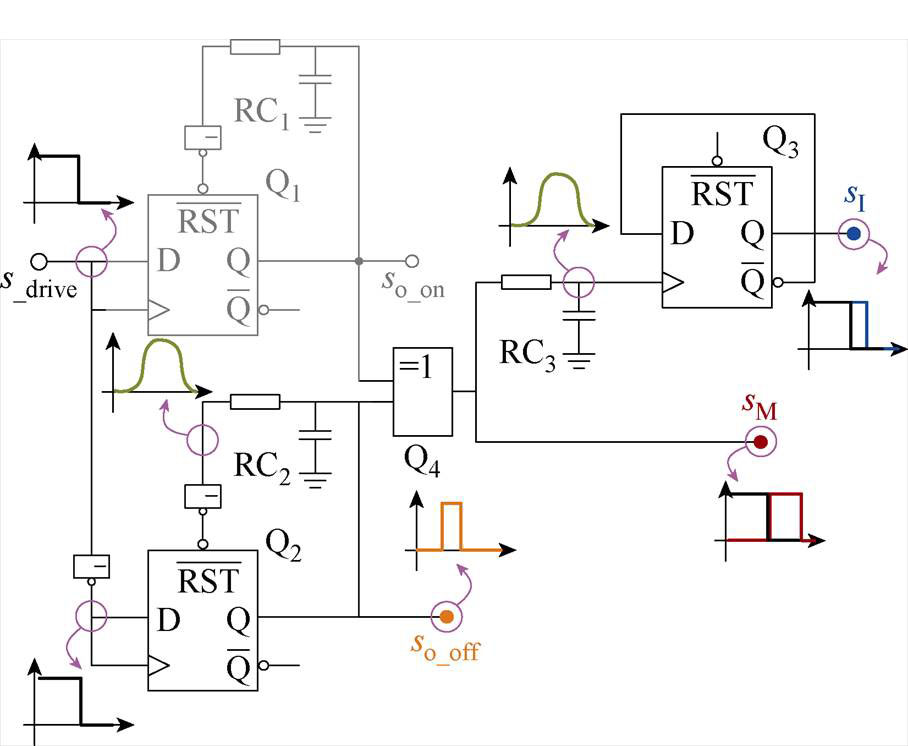

图1 SiC/Si HyS典型结构及其控制信号

Fig.1 The typical schematic of SiC/Si HyS and the switching patterns

摘要 SiC MOSFET和Si IGBT并联构成的混合开关(SiC/Si HyS)结构是一种优化效率和成本的综合解决方案。依靠SiC MOSFET的低导通时间构建Si IGBT的零电压开通和关断,并继承Si IGBT在高负载电流下的低导通损耗特性,从而提升系统整体效率。为了更简单高效地生成SiC/Si HyS的SiC MOSFET和Si IGBT驱动信号,该文提出一种针对最小SiC导通模式的信号调制电路,通过配置对应的RC缓冲电路中的电阻、电容值即可调节控制模式中的四个时间尺度,该方法具有灵活简单等优点。首先,理论分析最小SiC导通模式下的SiC/Si HyS结构损耗分布特性;其次,给出信号调制电路原理并介绍信号调制电路的工作原理,建立RC缓冲电路参数和时间尺度之间的函数方程;最后,基于搭建的SiC/Si HyS硬件平台,在双脉冲测试电路中验证最小SiC导通模式下的SiC/Si HyS损耗特性和所提信号调制电路的有效性,并在1.5 kW两电平逆变器中检验所提信号调制电路的动态运行特性。

关键词:SiC MOSFET Si IGBT 混合开关 开关损耗 信号调制

随着功率半导体器件材料及半导体功率器件封装技术的发展,以碳化硅金属氧化物半导体场效应晶体管(Silicon Carbide Metal-Oxide Semiconductor Field Effect Transistor, SiC MOSFET)为代表的宽禁带半导体功率器件凭借其高耐受温度、高开关频率、高耐受电压和低导通损耗等特性[1-3],有望替代传统硅基功率半导体器件,为电力电子设备的高效率和高功率密度提供更多解决方案。但是受制于SiC MOSFET自身生产成本和器件封装结构等问题[4-5],硅基绝缘栅双极型晶体管(Silicon Insulated Gate Bipolar Transistor, Si IGBT)在大电流应力应用场景下仍具备更小的导通电阻,因此目前在工业领域内Si IGBT仍是电力电子设备采用的主流功率半导体器件。

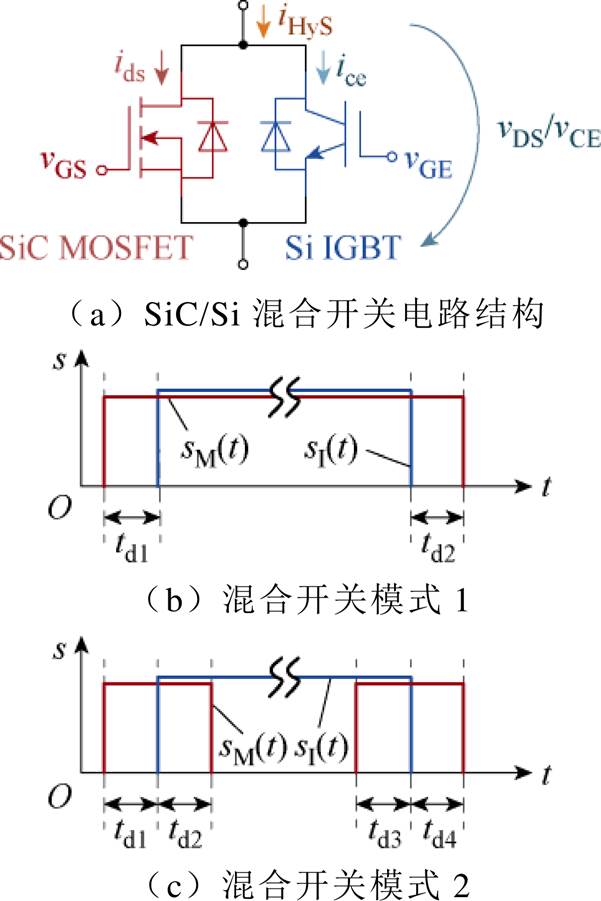

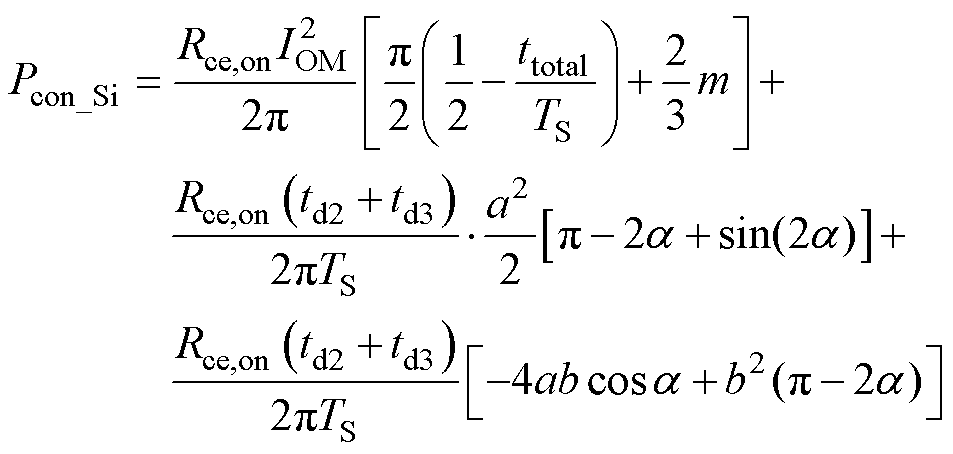

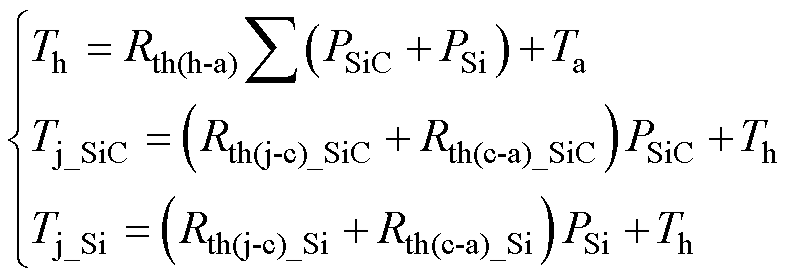

受到Si IGBT自身材料特性的限制,很难进一步提升工作频率。因此,有学者提出将SiC MOSFET和Si IGBT并联的混合开关(Hybrid Switch, HyS)结构,其典型结构如图1a所示,在HyS中利用SiC MOSFET作为辅助开关[6-7],构建Si IGBT的零电压开通和关断条件,从而减小Si IGBT的开关损耗,解决IGBT的电流拖尾问题。SiC MOSFET的引入提升了系统的开关频率,且相比同功率等级的SiC MOSFET系统具备更低的成本。

图1 SiC/Si HyS典型结构及其控制信号

Fig.1 The typical schematic of SiC/Si HyS and the switching patterns

由于SiC MOSFET和Si IGBT两种器件的动态特性差异较大,已有学者针对两种功率半导体器件并联的电流分配方式[8-9]和与之相对应的工作模式开展研究[10-11]。文献[12]建立了SiC/Si HyS不同工作模式下的器件损耗特性模型。文献[13]提出了针对SiC/Si HyS结温均衡的控制策略,避免传统工作模式下单个SiC MOSFET过热导致的热失效问题。文献[14]在构建工作模式时将寄生电感对开关特性的影响纳入其中,综合考虑成本和系统电流裕度,考虑器件选型,保证SiC/Si HyS结构的可靠稳定。此外SiC/Si HyS的时间尺度也与实际应用场景下负载电流大小相关,对此有学者提出基于有源控制的SiC/Si HyS控制策略,基于实际运行电流灵活调节延迟时间,保证系统的运行损耗最小[15-17]。文献[18-19]对SiC/Si HyS结构中个体器件失效的影响和对应器件失效后的控制策略展开研究。上述文献成果证明了SiC/Si HyS在并网逆变器[20-21]、电机驱动[22]和直流断路器[23]等电能传输系统应用场景中,已成为一种介于全Si IGBT器件系统和全SiC MOSFET功率器件之间的折中方案。

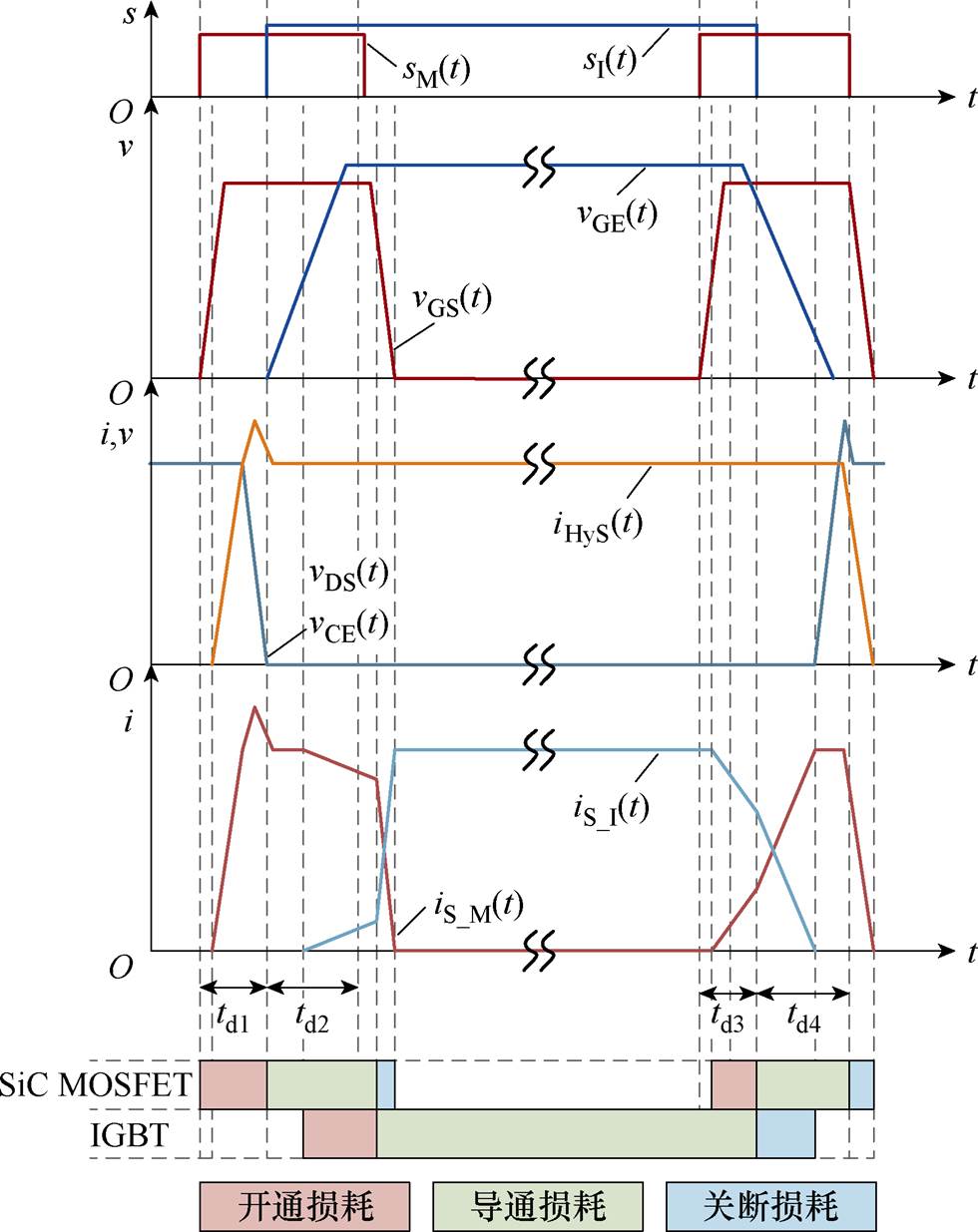

上述研究主要针对如图1b所示的并联导通模式,在其整个导通周期SiC MOSFET和Si IGBT都会完全导通,并分别承担一部分电流,因此在设计SiC MOSFET和Si IGBT的电流容量时需要综合考虑系统的成本和功率等级,进而选择合适的功率器件。SiC MOSFET的电流容量和Si IGBT的电流容量按照更低的配比从而降低HyS的成本[14]。为了进一步降低SiC MOSFET的电流容量,有学者提出如图1c所示的混合开关最小SiC导通模式[24-25],令SiC MOSFET只在Si IGBT的开关动作瞬间导通,构建Si IGBT的零电压导通,此外最小SiC导通模式可以有效地降低SiC MOSFET的导通损耗,弥补器件之间电流分布不均衡导致的损耗和结温偏差,并对SiC MOSFET的器件成本做进一步缩减[25]。

为了便于研究最小SiC导通模式下的时间延迟对SiC/Si HyS的损耗特性的影响,本文提出一种针对最小SiC导通模式的信号调制电路,该电路依靠配置RC缓冲的电阻电容值即可实现对四个时间尺度的调节。首先,对最小SiC导通模式下的SiC/Si HyS的整体损耗特性进行分析,获取四个时间尺度对整体损耗的影响;其次,为了简化控制系统的运算负荷,提出一种针对最小SiC导通模式的信号调制电路,并对其工作原理与参数设计进行分析;再次,设计实验验证平台;最后,对实验结果进行对比分析。

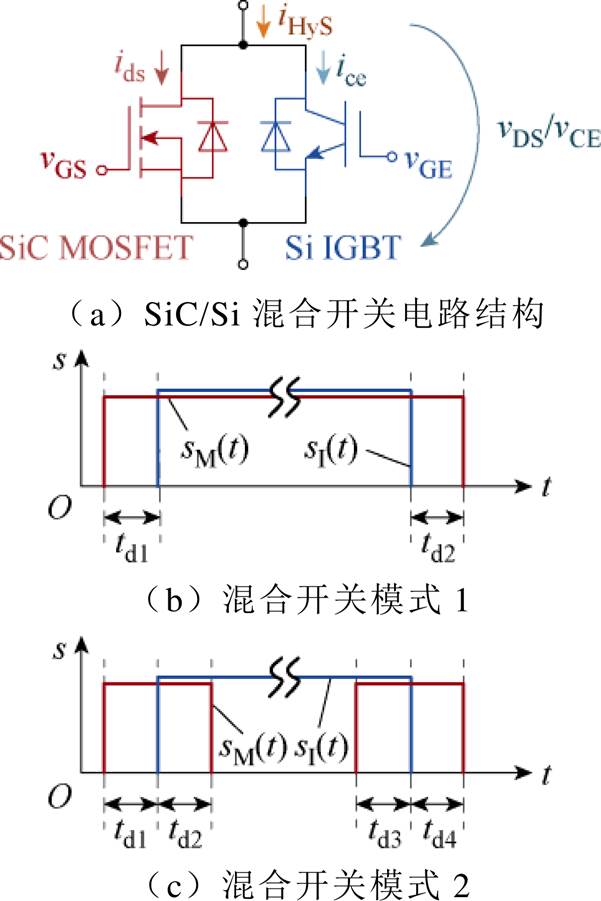

SiC/Si HyS最小SiC导通模式的一个开关周期内的典型波形如图2所示。相比于SiC MOSFET和Si IGBT并联导通模式中的两个时间尺度,最小SiC导通模式下存在td1~td4四个时间尺度控制调节SiC MOSFET和Si IGBT的导通关断,因此,其损耗特性更为复杂。

图2 最小SiC导通模式下的典型波形

Fig.2 The typical waveforms of the minimum SiC condition control mode

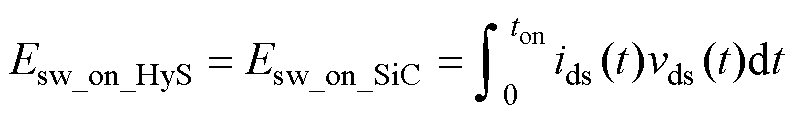

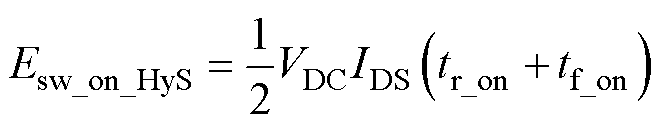

由于SiC MOSFET的开关动作时间远小于Si IGBT的动作时间(典型的SiC MOSFET的上升/下降时间约18 ns,Si IGBT的上升/下降时间约120 ns),在td1≥0和td4≥0的情况下,对于最小SiC导通模式下的SiC/Si HyS的开关损耗皆为SiC MOSFET的开关损耗。SiC/Si HyS损耗Esw_on_HyS可以利用SiC MOSFET开通时间ton对开关损耗Esw_on_SiC进行表示,即

(1)

(1)

式中,ids(t)为SiC MOSFET的漏源极电流。

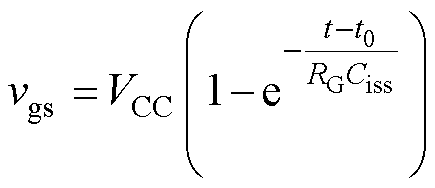

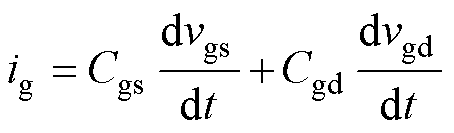

SiC MOSFET的栅源极电压vgs可以根据栅源极回路电流ig方程进行求解,得

(2)

(2)

(3)

(3)

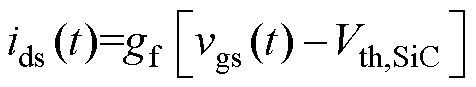

式中,t0为驱动电压变化初始时刻;VCC为驱动正电压;RG为栅极回路电阻;Ciss为SiC MOSFET的输入电容;vgd为栅漏极电压;Cgs、Cgd分别为SiC MOSFET的栅源极电容和米勒电容。漏源极电流ids由vgs控制为

(4)

(4)

式中,gf为SiC MOSFET导纳;Vth,SiC为SiC MOSFET的阈值电压。

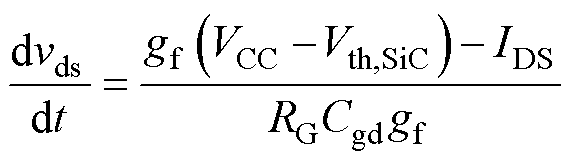

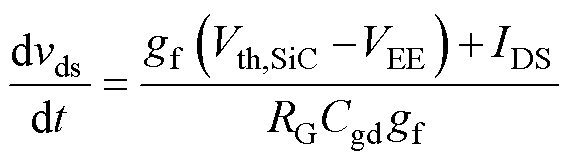

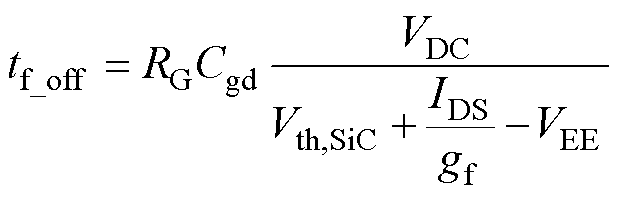

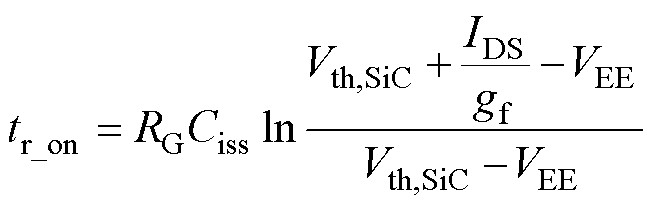

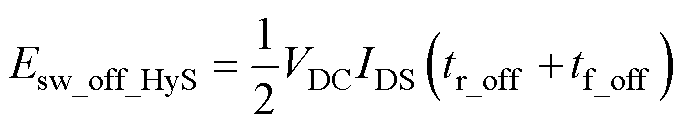

在ids达到SiC MOSFET漏源极输出电流IDS后,vgs维持在米勒电压,根据式(3)和式(4),进一步求解得到漏源极电压vds变化率[26-27]为

(5)

(5)

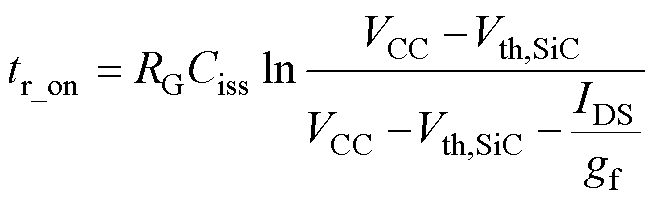

在IDS确定的条件下,由式(4)和式(5),可以估算整个开通过程持续时间,电流上升时间tr_on和电压下降时间tf_off分别为

(6)

(6)

(7)

(7)

式中,VDC为直流母线电压。由于ids和vds变化近似呈线性,则开通损耗可以表示为

(8)

(8)

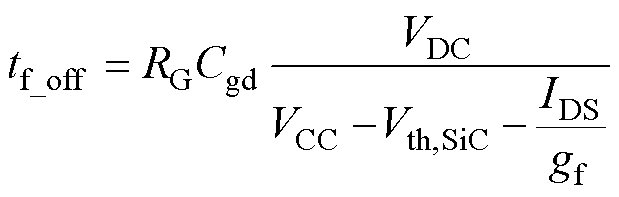

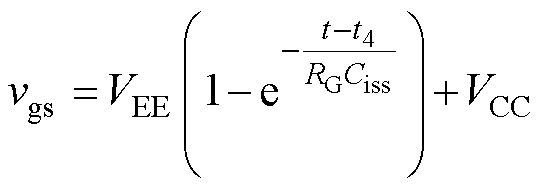

关断损耗和开通损耗近似,关断过程中SiC MOSFET的栅源极电压vgs和漏源极电压vds变化率可分别表示为

(9)

(9)

(10)

(10)

式中,t4为vgs开始下降的时刻;VEE为驱动负电压。基于式(9)可以估算出关断过程中,SiC MSOFET的电流下降时间tf_off和电压上升时间tr_on分别为

(11)

(11)

(12)

(12)

结合式(12),可以估算SiC/Si HyS的关断损ESW_off_HyS,即SiC MOSFET的关断损耗ESW_off_SiC可以表示为

(13)

(13)

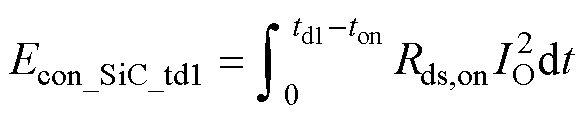

如图2所示,在最小SiC导通模式下的SiC/Si HyS的导通损耗Econ_HyS,由每个时间尺度内的器件损耗构成,可以视为四个部分。第一部分为第1个时间尺度(td1)和第4个时间尺度(td4)内的SiC MOSFET的导通损耗Econ_SiC_td1和Econ_SiC_td4,可分别表示为

(14)

(14)

e (15)

式中,ton和toff分别为SiC MOSFET的开通、关断过程的持续时间;IO为流过SiC/Si HyS的负载电流;Rds,on为SiC MOSFET的导通电阻。

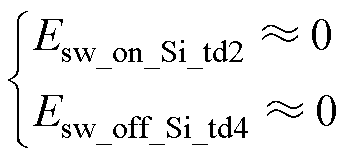

第二部分为t2和t4时刻开始阶段所对应的Si IGBT的开关损耗Esw_on_Si_td2和Esw_off_Si_td4。在td2和td4的开始时刻,SiC/Si HyS的端电压为SiC MOSFET的饱和压降(2~4 V),因此Si IGBT可以近似视为零电压导通和关断,故而有

(16)

(16)

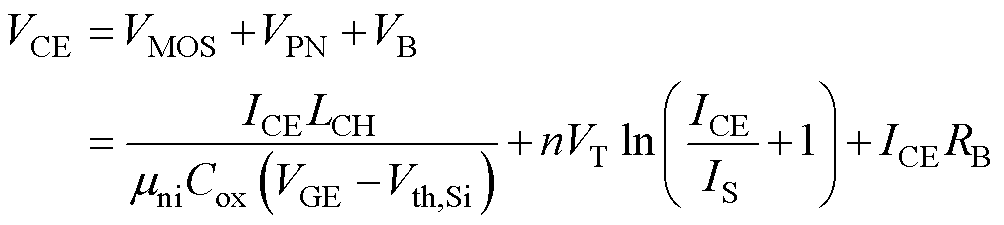

第三部分为td2和td4时间尺度内,SiC MOSFET和Si IGBT的并联导通损耗。Si IGBT的器件结构可以等效为一个MOSFET串联一个NPN型双极性结型晶体管(Bipolar Junction Transistor, BJT),因此IGBT的导通电压为MOSFET的漏源极电压VMOS、BJT的PN结的正向导通电压VPN以及器件内部键合线等效电阻上的压降VB三者的总和[28],即

(17)

(17)

式中,ICE为Si IGBT的集电极-发射极电流;LCH为沟道长度;mni为内部电子迁移率;COX为栅极氧化层等效电容;Vth,Si为IGBT的开通电压;n为电流注入系数;VT为热电压;IS为反向饱和电流;RB为键合线等效电阻。

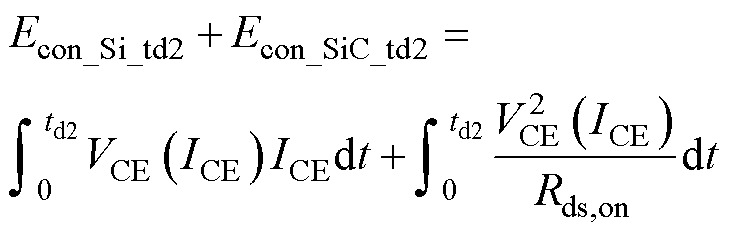

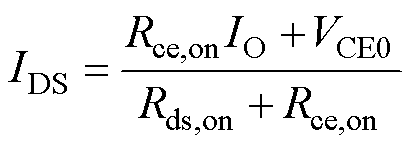

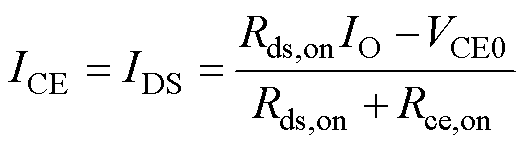

根据式(17),Si IGBT的导通电阻在低ICE阶段呈非线性,在IGBT刚刚导通的阶段,其等效导通电阻Rce,on远大于SiC MOSFET的导通电阻Rds,on。当td2的持续时间较短或负载电流较小时,该阶段的整体损耗仍然以SiC MOSFET的导通损耗为主。结合式(17),td2时间内的Si IGBT的导通损耗Econ_Si_td2和SiC MOSFET的总导通损耗Econ_SiC_td2之和可以表示为

(18)

(18)

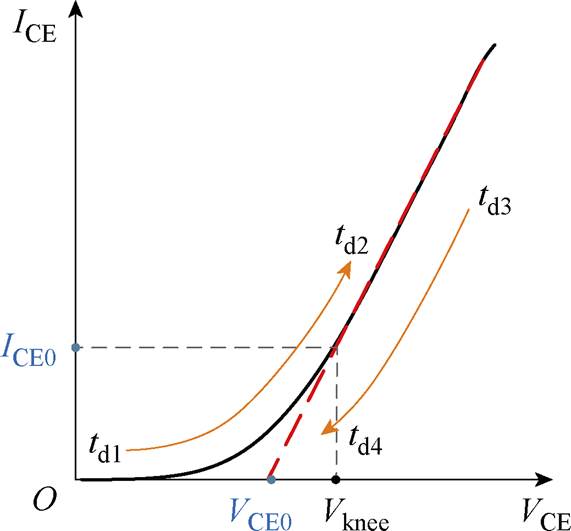

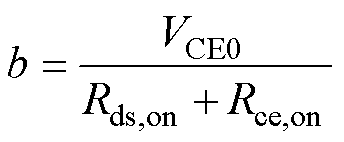

Si IGBT输出特性曲线如图3所示,设Si IGBT的膝点电压Vknee所对应的发射极-集电极电流为ICE0,当ICE>ICE0时,可以视为IGBT进入线性电阻区,其饱和压降VCE可以表示为

(19)

(19)

式中,VCE0为Si IGBT的输出特性曲线的线性区域延长线和VCE轴的交点。

图3 Si IGBT输出特性曲线

Fig.3 The forward conduction characteristics of Si IGBT

从td3时刻开始,如果ICE>ICE0,Si IGBT处于线性电阻区,此时流过SiC/Si HyS的电流可以分别表示为

(20)

(20)

(21)

(21)

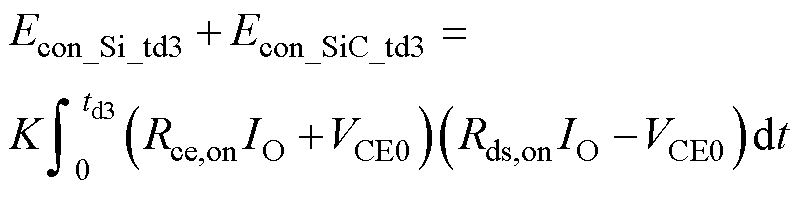

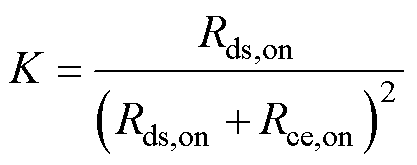

对于td3内的Si IGBT和SiC MOSFET的导通损耗Econ_Si_td3和Econ_SiC_td3之和可以表示为

(22)

(22)

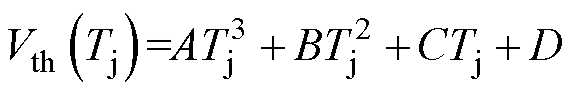

其中

(23)

(23)

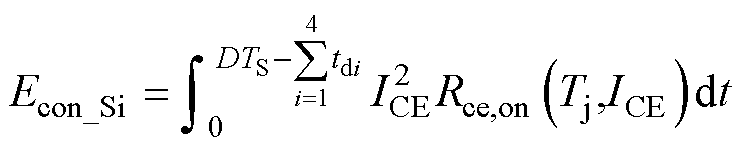

当实际输出电流IO<ICE0时,Econ_Si_td3和Econ_SiC_td3的计算方法和式(18)相同。最后一部分损耗为Si IGBT单独导通导致的导通损耗,该阶段的导通损耗Econ_Si可以表示为

(24)

(24)

式中,tdi为第i个时间尺度;TS开关周期。

综上所述,在最小SiC导通模式下的SiC/Si HyS的导通损耗可以依靠式(10)、式(11)、式(14)、式(18)和式(24)计算得到。以两电平全桥逆变器为基础,进一步探讨SiC/Si HyS在最小SiC导通模式下四个时间尺度对导通损耗的影响。忽略死区时间内,SiC MOSFET体二极管的导通损耗以及Si IGBT并联续流二极管的导通损耗和反向恢复损耗。在一个工频周期内,流过上/下半桥SiC/Si HyS的等效电流示意图如图4所示。

图4 一个工频周期内的导通电流示意图

Fig.4 The conduction stage during one fundamental period

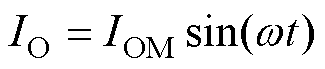

逆变器的输出的电流IO可以表示为

(25)

(25)

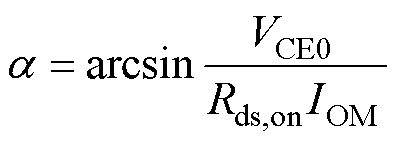

式中,IOM为输出电流的幅值。由于Si IGBT的导通压降呈非线性,为了简化分析,在[0, a]和[p-a, p]区间内输出电流小于ICE0的部分,假设Si IGBT的导通电阻远大于SiC MOSFET的导通电阻,输出电流全部流过SiC/Si HyS内的SiC MOSFET。在区间[a, p]内,Si IGBT进入线性电阻区,和SiC MOSFET共同承担负载电流。区间节点a 由Si IGBT的近似线性输出特性曲线与横坐标交点VCE0进行估算为

(26)

(26)

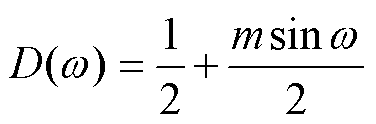

对于正弦脉宽调制(Sine Pulse Width Modu- lation, SPWM)下,一个开关周期内的器件占空 比[29-30]可以表示为

(27)

(27)

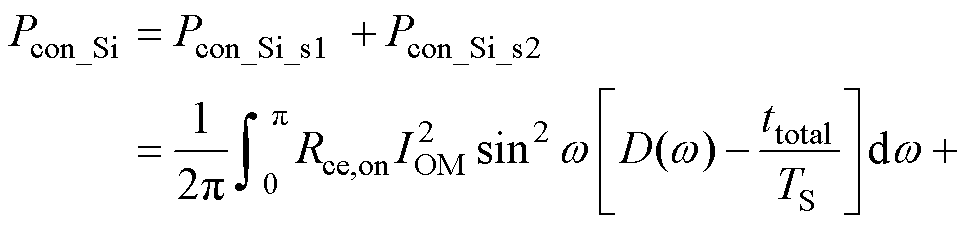

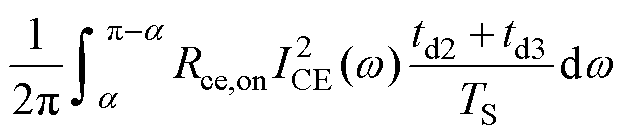

式中,m为调制比。Si IGBT的导通损耗分为两部分:①区间[0, p]内,Si IGBT单独导通引起的导通损耗Pcon_Si_s1;②区间[a, p-a]区间内,SiC MOSFET和Si IGBT共同导通引起的导通损耗Pcon_Si_s2。因此,Si IGBT的导通损耗可以表示为

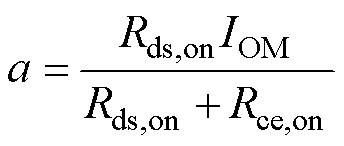

(28)

(28)

式中,ttotal为四个时间尺度之和。Si IGBT分担的电流ICE可以用表达式(21)进行计算,代入式(28)中有

(29)

(29)

其中

(30)

(30)

(31)

(31)

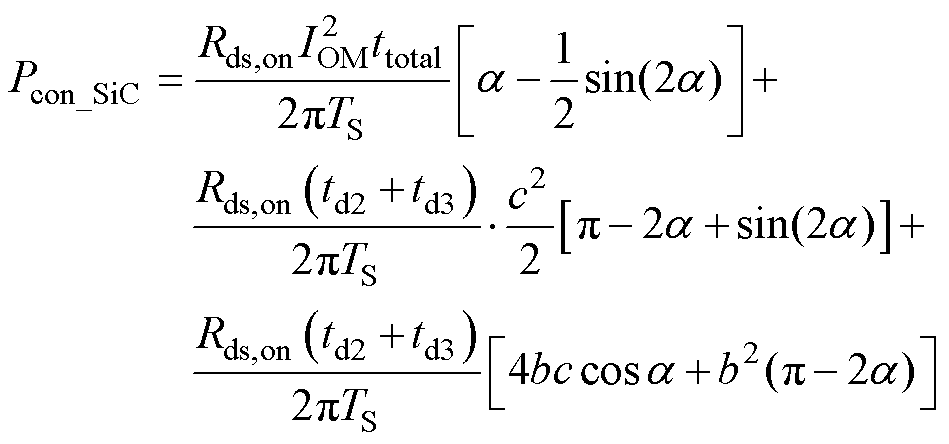

同理,SiC MOSFET的导通损耗包含两部分:①阶段1中四个时间尺度内的导通损耗Pcon_SiC_s1;②阶段2中SiC MOSFET与Si IGBT共同导通阶段导致的导通损耗Pcon_SiC_s2。SiC/Si HyS在最小SiC MOSFET导通模式下,SiC MOSFET的总导通损耗Pcon_SiC可以表示为

(32)

(32)

将式(20)代入式(32),SiC MOSFET的导通损耗可进一步表示为

(33)

(33)

(34)

(34)

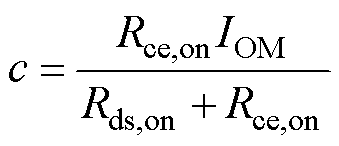

Si IGBT导通损耗与时间尺度的影响如图5所示。图5a和图5b分别为10 A和40 A输出电流幅值下,不同时间尺度对SiC/Si HyS的Si IGBT导通损耗的影响趋势,其中SiC MOSFET导通电阻参考C3M0075120D手册给出的典型值75 mW,IGBT的导通电阻利用对CRG40T120AK3S手册中输出特性曲线进行线性拟合得到,导通电阻线性为19 mW,VCE0=1.3 V。由于忽略了Si IGBT在小电流负载区域内的导通电阻,因此图5得到的结果相比于实际导通损耗偏小。在输出电流较小的时候,由于Si IGBT的等效导通电阻相对较大,因此提升SiC MOSFET的导通时间有助于降低Si IGBT的整体损耗;随着负载电流的提升,Si IGBT的导通电阻降低,降低SiC MOSFET的导通时间有利于降低所需SiC MOSFET的电流,也有利于减小SiC MOSFET的导通损耗 占比。

图5 Si IGBT导通损耗与时间尺度的影响

Fig.5 The relationship between the conduction loss of Si IGBT and the time scales

SiC MOSFET的开关特性和导通电阻易受温度影响,因此进一步分析结温变化对SiC/Si HyS损耗特性的影响。

1.3.1 开关损耗

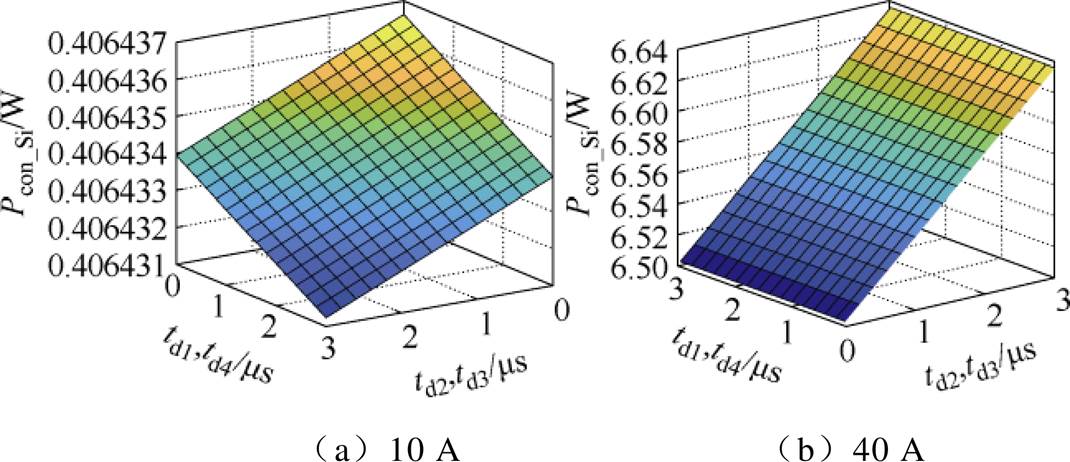

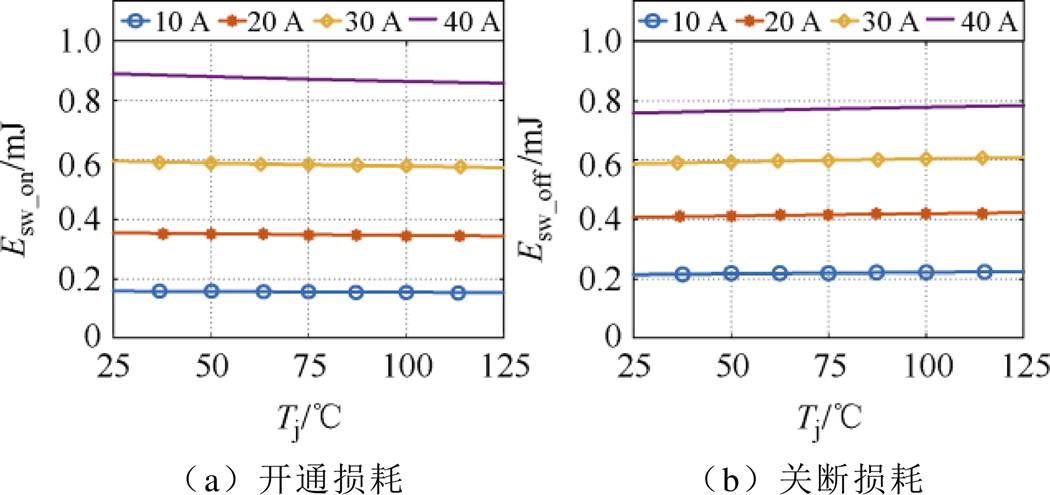

根据式(8)和式(13),当SiC MOSFET的结温更高时,阈值电压随之降低,其温度特性方程[29-30]可以表示为

(35)

(35)

式中,A、B、C、D为拟合系数。

结合SiC MOSFET(C3M0075120D)数据手册中给出的Vth的温度曲线,可以得到拟合系数分别为A=2.6×10-9,B=7.92×10-6,C=4.7×10-3,D=2.820 6。结合式(8)和式(13),不同结温和不同负载电流下的SiC MOSFET开关损耗特性如图6所示,母线电压设定为500 V。随着结温的上升,阈值电压下降,开通过程提前,降低了开通时间,所以随着器件结温的增加,开通损耗随着结温的上升有所增加。阈值电压的降低造成了关断过程的延后,因此随着结温上升,关断损耗随之降低。

图6 不同结温下的开关损耗变化趋势

Fig.6 Switching loss under various junction temperature

1.3.2 导通损耗

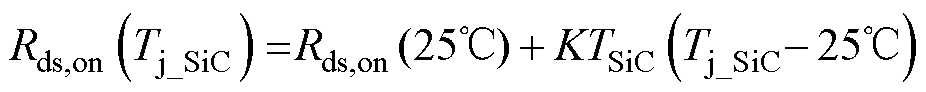

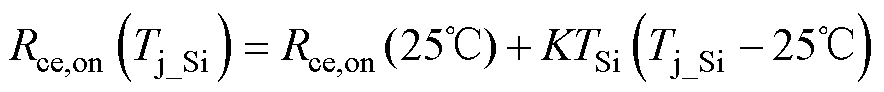

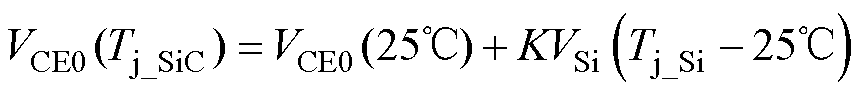

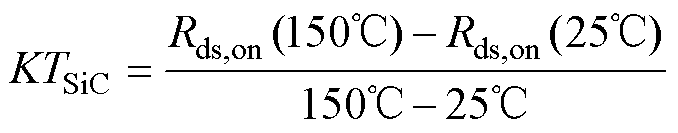

无论是SiC MOSFET亦或是Si IGBT,器件的导通电阻都会随着结温的升高而升高,在考虑结温变化时,两种器件的导通电阻和Si IGBT饱和导通电压方程中的VCE0结温方程皆近似为一阶线性方程,分别表示为

(36)

(36)

(37)

(37)

(38)

(38)

式中,Tj_SiC和Tj_Si分别为SiC MOSFET和Si IGBT的结温;KTSiC、KTSi和KVSi为温度系数,依靠数据手册中25℃和150℃的值计算

(39)

(39)

KTSi和KVSi的表达式和式(39)的形式相同。随着结温的升高,SiC MOSFET和Si IGBT的导通电阻增加,势必造成整体的导通损耗增加。

SiC/Si HyS的热阻等效模型如图7所示,Rth(j-c)为器件结到外壳的等效热阻;Rth(c-a)为器件外壳到空气的等效热阻;Rth(c-h)和Rth(h-a)分别为器件管壳到散热器和散热器到空气的热阻。前两者可以从器件手册查询,Rth(c-h)为器件和散热片之间导热硅脂和绝缘垫片的等效热阻[31-32]。

图7 SiC/Si HyS热阻等效电路

Fig.7 Foster network of SiC/Si HyS

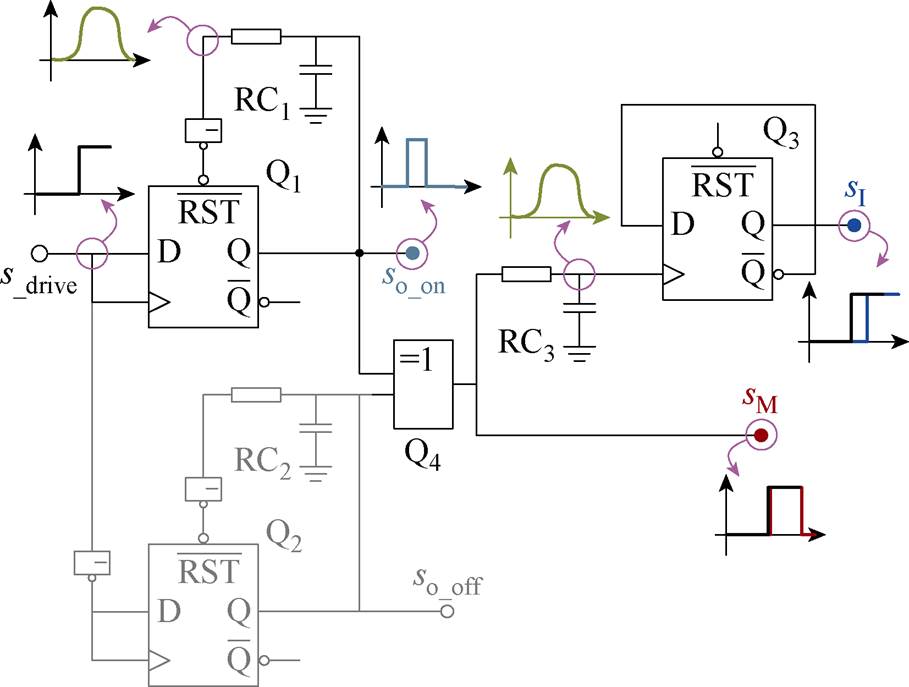

根据图7所示的等效电路,由于Rth(c-a) Rth(c-h)+Rth(h-a),可以列写各个节点温度表达式为

Rth(c-h)+Rth(h-a),可以列写各个节点温度表达式为

(40)

(40)

式中,PSiC为SiC MOSFET的开关损耗和导通损耗之和;PSi为Si IGBT的导通损耗与并联二极管的反向恢复损耗、导通损耗之和。根据手册给出的器件最大工作温度可以估算Rth(h-a),从而对散热片的尺寸进行设计,选择合适的散热风扇。

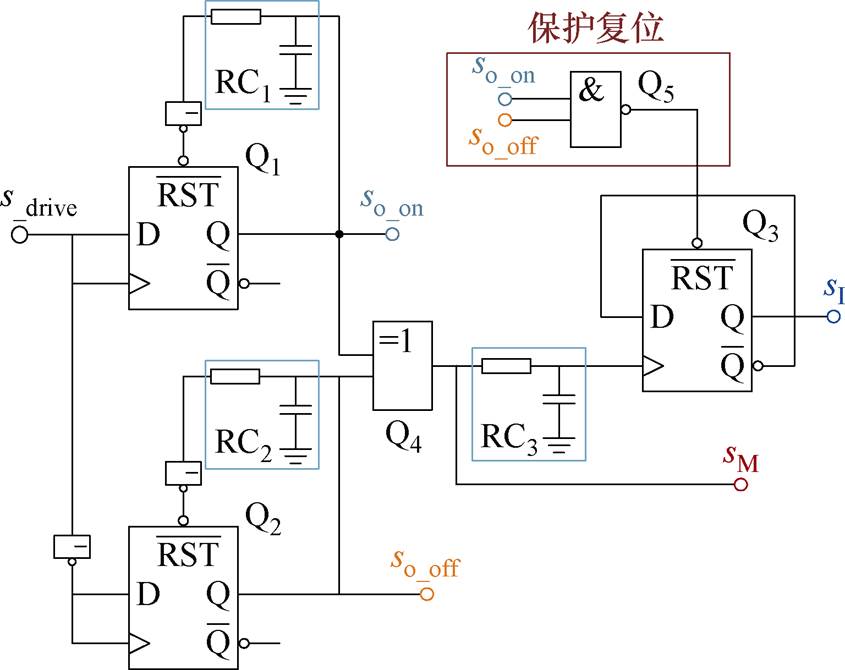

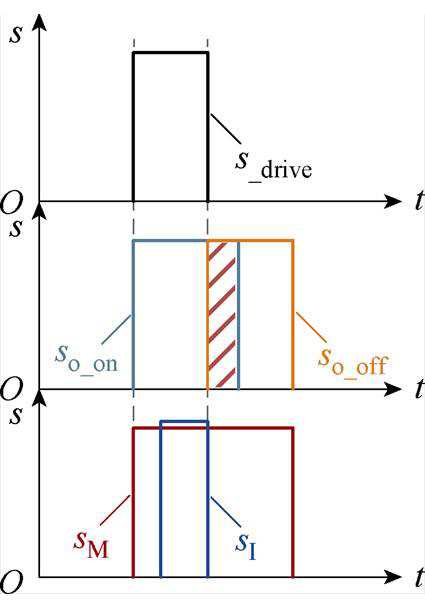

对于SiC/Si HyS,需要分别对SiC MOSFET和Si IGBT的控制信号进行处理,在电路结构复杂、开关管数量较多或者控制策略较为繁琐的电路中,需额外进行延迟运算来分别生成SiC MOSFET和Si IGBT的控制信号,不仅增加了系统的运算负荷,对信号内部的调制方式和控制器的计算能力也有了更高的要求。相比于并联导通模式,最小SiC导通模式下的SiC MOSFET需要在Si IGBT的开通和关断瞬间进行导通,为IGBT提供零电压开关条件,因此最小SiC导通模式下的SiC/Si HyS的控制系统更为繁杂。为简化系统的控制策略,本文提出如图8所示的驱动信号调制电路。只需对单驱动信号进行调制,就可分别生成对应的SiC MOSFET的脉冲信号和Si IGBT的内缩信号。信号调制电路由三个D触发器(Q1~Q3)和一个或门(Q4)组成,对于最小SiC导通模式下的四个时间尺度(td1~td4)可以依靠三组RC延迟缓冲电路(RC1~RC3)进行独立调节。整体调制电路结构简单、控制灵活。此外,为了防止驱动信号脉冲过小导致的延迟时间远大于的导通时间,电路中加入保护复位功能。图8中,s_drive为输入的驱动信号;so_on和so_off分别对应SiC MOSFET的开通脉冲和关断脉冲;sM和sI对应调制电路输出的SiC MOSFET和Si IGBT的驱动信号。

图8 所提出SiC/Si信号调制电路

Fig.8 The proposed signal modulation circuit for SiC/Si HyS

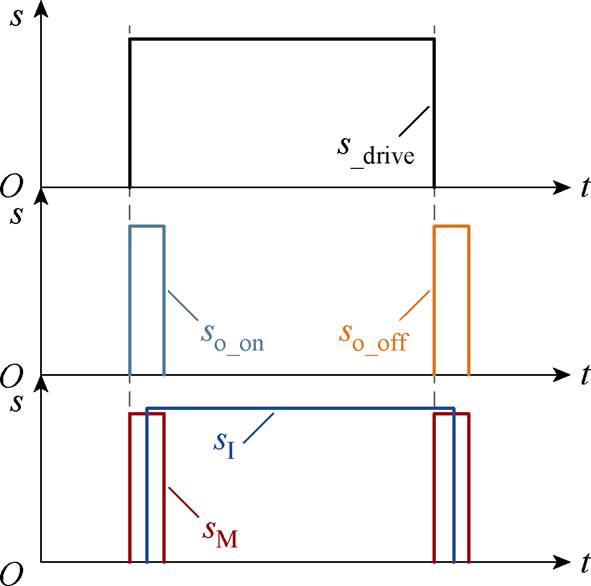

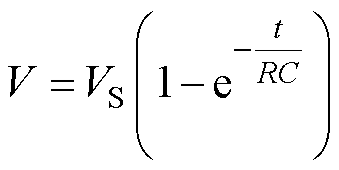

图9为提出的SiC/Si HyS驱动信号调制电路的输出波形。具体的电路工作原理如下:

图9 所提出信号调制电路输出波形

Fig.9 The output waveforms of the proposed signal modulation circuit

(1)开通过程:所提出的信号调制电路在开通阶段的等效电路如图10所示,当s_drive由低电平转变为高电平时,触发Q1,so_on同步由低电平转变为高电平。同时so_on开始为RC1缓冲电路进行充电,达到非门电路的触发阈值电平,将Q1的重置引脚RST拉低,so_on同步转变为低电平。当so_on的上升沿经过RC3缓冲后(见图10所示的上升斜率较低的脉冲),触发Q3,sI信号取反,由低电平转为高电平,驱动Si IGBT开始导通。

图10 开通过程等效电路

Fig.10 Equivalent circuit of the turn-on transient

(2)关断过程:关断瞬态的等效电路如图11所示,关断信号的生成与开通过程类似,在s_drive转变为低电平的同时,经过非门产生的信号驱动Q2输出高电平so_off,so_off经过RC2的延迟后重置Q2,再次将so_off置低。后级so_off触发Q3,对sI取反,经过RC3的延迟后,由高电平转变为低电平,生成Si IGBT关断信号。

图11 关断过程等效电路

Fig.11 Equivalent circuit of the turn-off transient

驱动信号s_drive依靠D触发器和RC缓冲电路生成开通脉冲so_on和关断脉冲so_off,两个脉冲经过或门进行逻辑运算,得到SiC MOSFET驱动信号sM。当s_drive的占空比较小时,可能会出现so_off的上升沿出现在so_on的下降沿之前,窄脉冲下波形如图12所示。在这种情况下后级Q3无法进行二次触发,sI无法取反将会一直维持高电平,直到下个s_drive的上升沿,这种结果将会导致上下桥臂功率器件直通烧毁器件。为了避免此种故障信号,除了设置合适的SiC/Si HyS的时间尺度,在信号调制电路中加入复位电路(见图9中的与非门),对Q3进行复位,强制拉低sI,避免Si IGBT的持续导通。

图12 窄脉冲下波形

Fig.12 The waveforms under a smaller duty width

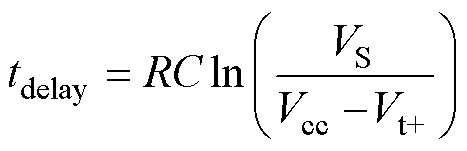

最小SiC导通模式下的SiC/Si HyS涉及td1~td4四个时间尺度,全部由RC缓冲电路进行设置,只需要配置相对应的电容和电阻,即可设置所需的时间尺度。根据上述的电路理论分析,可以得到对应调节关系:RC1调节td1+td2;RC2调节td3+td4;RC3调节td1和td3。对于RC缓冲电路可以简单等效为一个一阶RC充电电路,电容电压可以表示为

(41)

(41)

式中,VS为供电电压。当电容电压上升至非门高电平阈值电平Vt+触发后级电路,因此延迟时间可以计算对应的延迟时间tdelay可以表示为

(42)

(42)

根据式(42)可以调节RC缓冲电路电阻电容值,进一步实现对SiC/Si HyS驱动信号的四个时间尺度进行设定或调节。

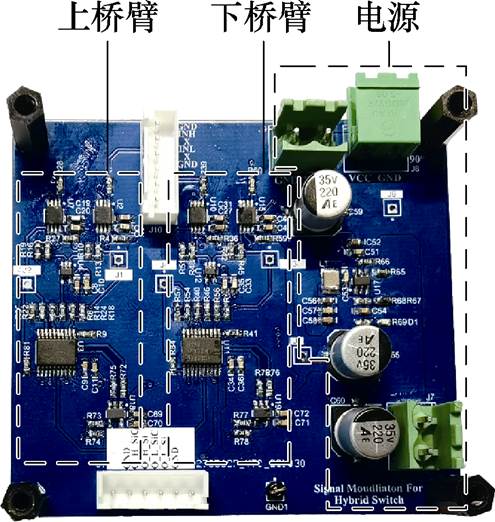

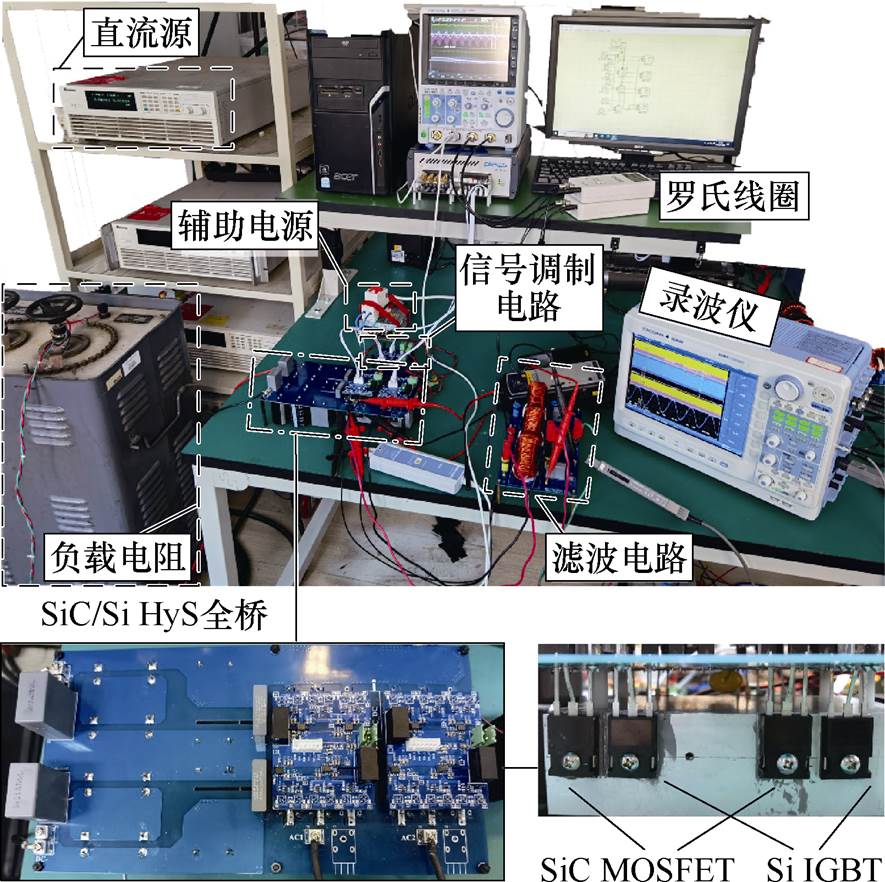

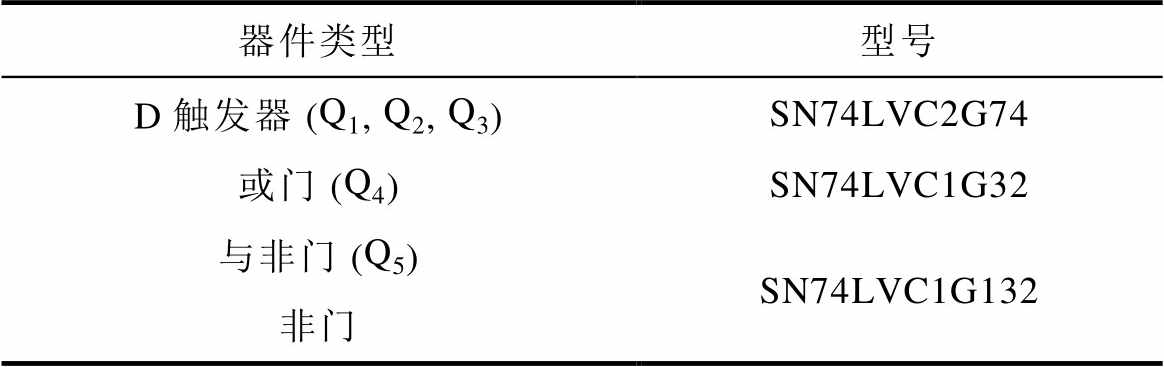

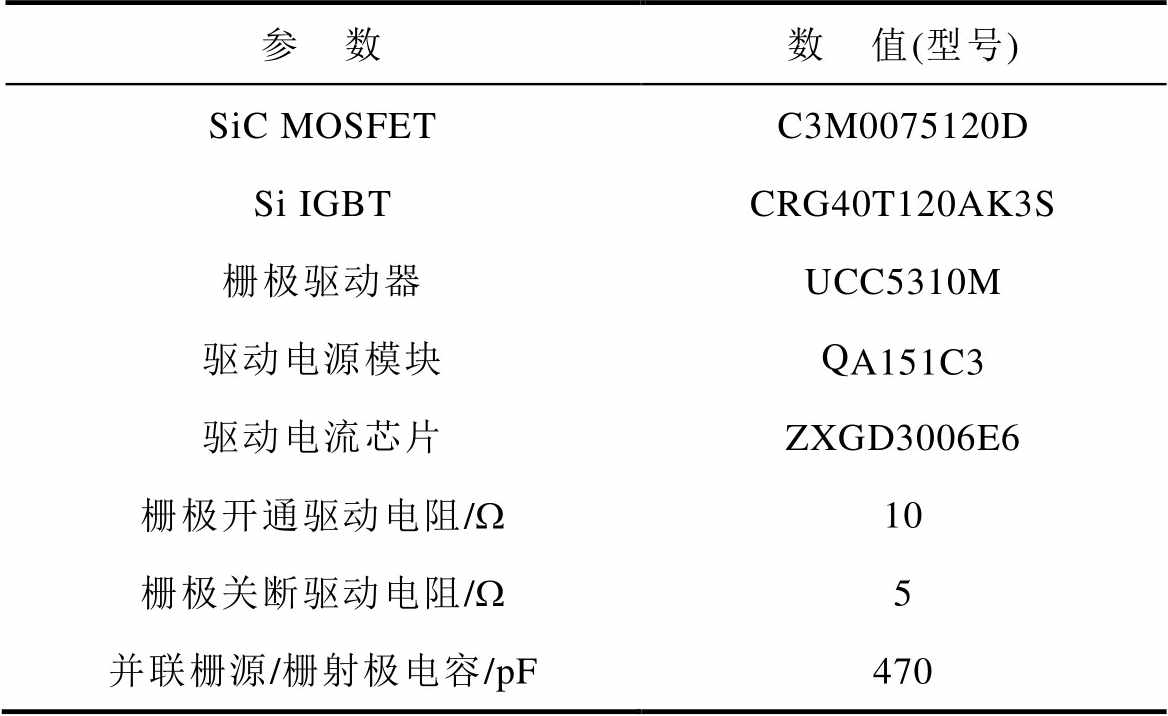

为了验证所提出的SiC/Si HyS的信号调制电路和最小SiC导通模式下整体损耗分布情况,搭建了如图13所示的信号调制电路样机和如图14所示的SiC/Si HyS全桥功率测试平台,具体的器件型号和硬件电路参数见表1和表2,其中表1列出的器件对应图8所示的电路。

由于SiC MOSFET基本处于开关瞬态的脉冲电流负载下,出于成本考虑,搭建的SiC/Si HyS实验平台采用的SiC MOSFET为1 200 V/32 A,Si IGBT的功率等级为1 200 V/80 A,电流配比为1 2。此外两种功率器件都采用TO-247-3封装。为了降低功率侧电流对栅极驱动电流回路的干扰,分别在SiC MOSFET和Si IGBT的栅极驱动侧并联470 pF电容和10 kW 的电阻,构建RC吸收回路降低栅极电压振铃。两种功率器件的栅极驱动开通电阻均为15 W,关断电阻为7.5 W。SiC MOSFET和Si IGBT的驱动电源正负电压为15.5 V和-4.7 V。

2。此外两种功率器件都采用TO-247-3封装。为了降低功率侧电流对栅极驱动电流回路的干扰,分别在SiC MOSFET和Si IGBT的栅极驱动侧并联470 pF电容和10 kW 的电阻,构建RC吸收回路降低栅极电压振铃。两种功率器件的栅极驱动开通电阻均为15 W,关断电阻为7.5 W。SiC MOSFET和Si IGBT的驱动电源正负电压为15.5 V和-4.7 V。

图13 所提出信号调制电路样机

Fig.13 The picture of the proposed signal modulation circuit for SiC/Si HyS

图14 基于SiC/Si HyS的全桥逆变测试平台

Fig.14 The full-bridge inverter platform based on SiC/Si HyS

表1 信号调制电路器件

Tab.1 The proposed signal modulation circuit

器件类型型号 D触发器 (Q1, Q2, Q3)SN74LVC2G74 或门 (Q4)SN74LVC1G32 与非门 (Q5)SN74LVC1G132 非门

表2 SiC/Si HyS全桥电路

Tab.2 The SiC/Si HyS full-bridge circuit

参 数数 值(型号) SiC MOSFETC3M0075120D Si IGBTCRG40T120AK3S 栅极驱动器UCC5310M 驱动电源模块QA151C3 驱动电流芯片ZXGD3006E6 栅极开通驱动电阻/W10 栅极关断驱动电阻/W5 并联栅源/栅射极电容/pF470

首先,针对所提出的信号调制电路进行测试,拟合得到不同环节下的RC调节时间常数,进一步验证输出信号保护模块的作用。其次,验证最小SiC导通模式下的四个时间尺度对SiC/Si HyS损耗特性的影响,依靠所提出的信号调制电路,结合双脉冲测试电路,分析不同时间尺度对损耗和SiC/Si HyS开关特性的影响。最后,在全桥电路下验证所提出信号调制电路的动态特性和SiC/Si HyS功率器件的温度分布。

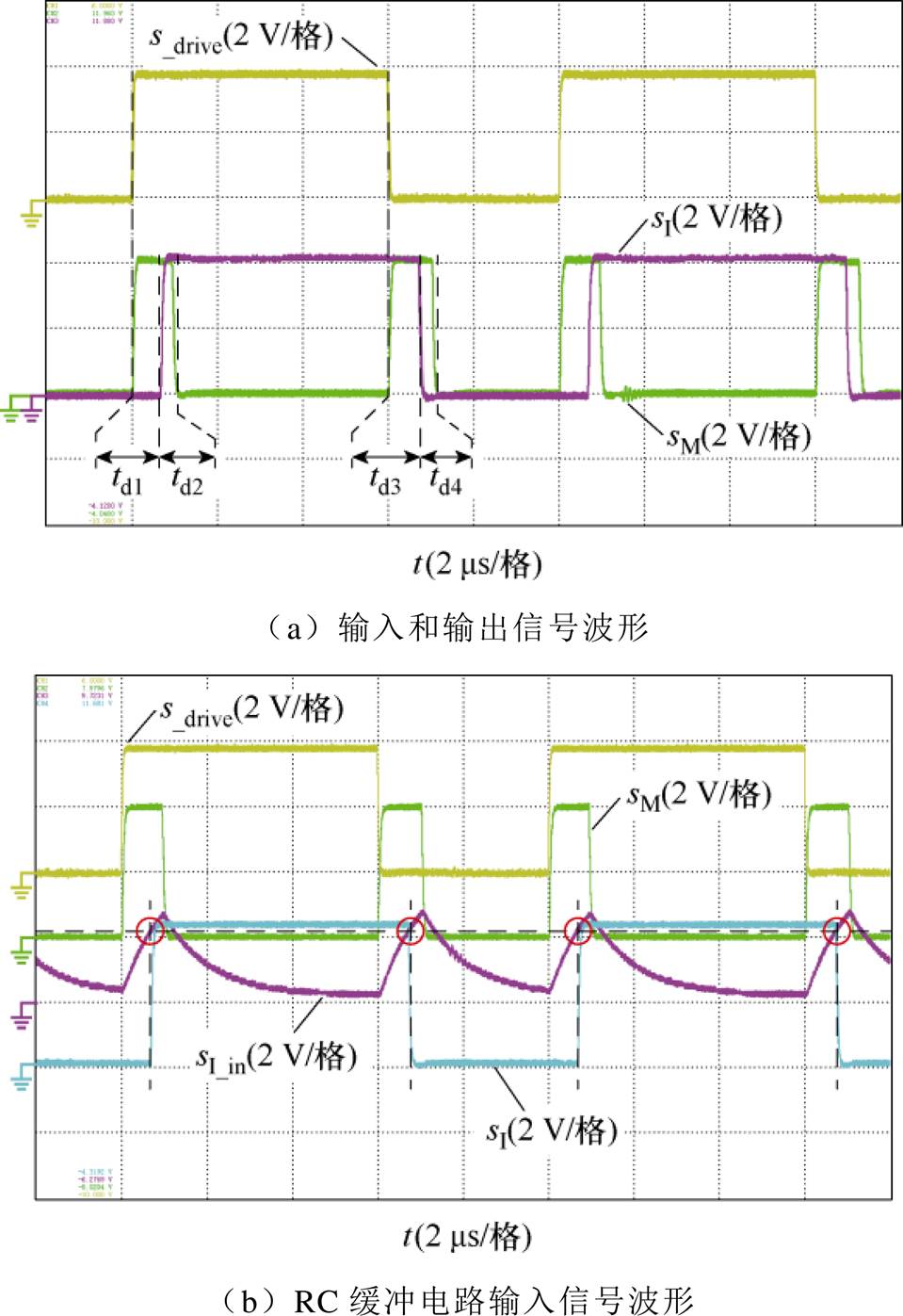

图15所示为所提出的SiC/Si HyS驱动信号调制电路的输入和输出波形,输入信号的频率为50 kHz,占空比为60%。图15a为输入信号s_drive和调制后输出的SiC MOSFET和Si IGBT的驱动信号sM和sI,其信号和图9所示的电路原理所对应。依靠s_drive的上升沿和下降沿产生对应的脉冲电压,来构建Si IGBT驱动信号,利用RC缓冲结构和触发器的阈值电压,实现对最小SiC导通模式的时间尺度进行调节。如图15b所示,sI_in为sM输入缓冲电路RC3后的输出电压波形。根据sI的信号电平变化和对应sI_in的电平电压,可以确定Q3的时钟输入高电平触发阈值电压为2.05 V。

图15 信号调制电路输出波形

Fig.15 The output waveforms of the proposed signal modulation circuit

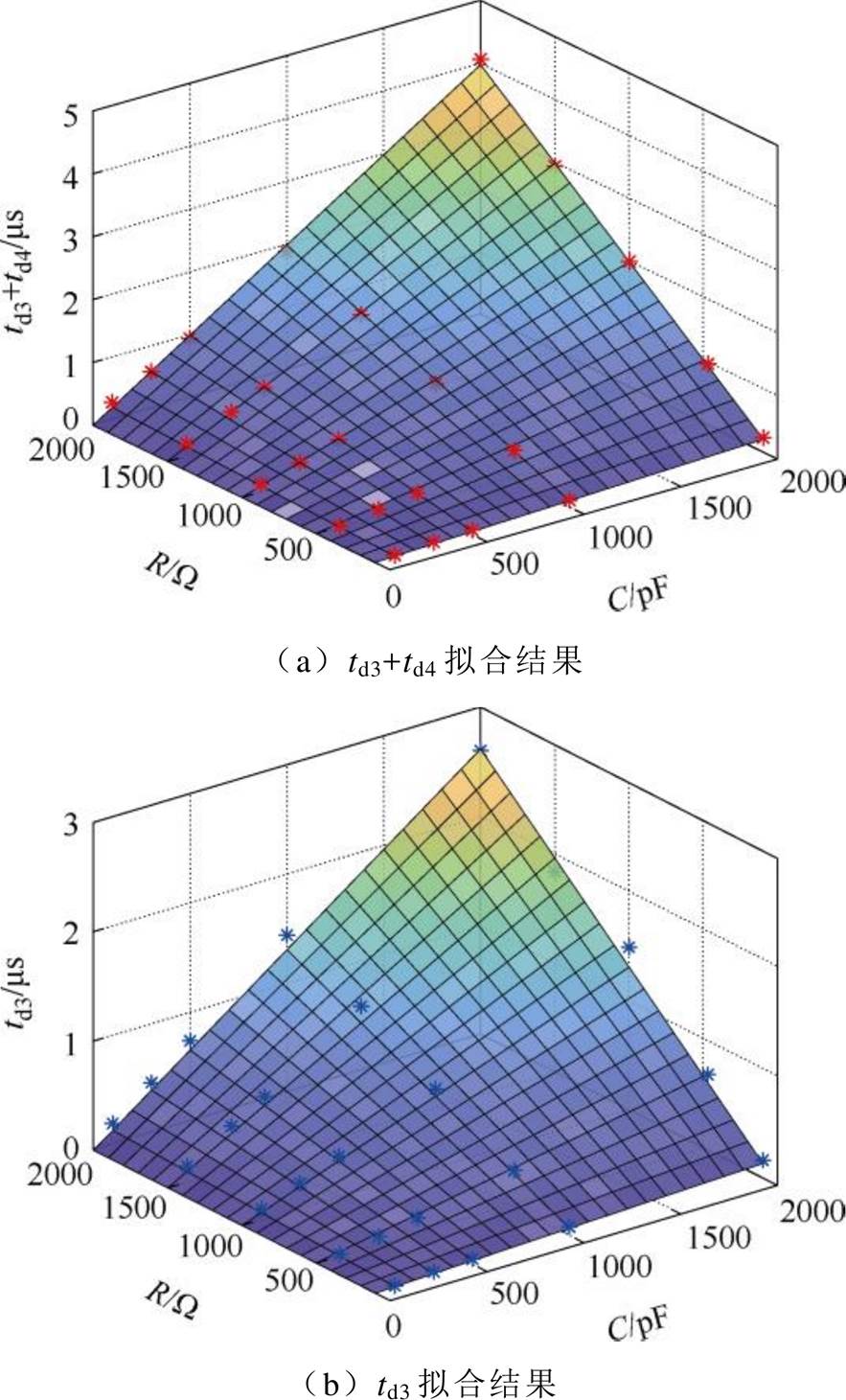

尽管sM和sI都是依靠相同的D触发器电路生成,但sI的生成又经过一个或门运算,因此sM和sI可以视为存在两个不同的阈值电压。根据式(42),假设K为阈值电压系数,阈值电压可以表示为Vt+= KVS。sM和sI环节对应的阈值电压系数分别为KM和KI,实际测试的RC缓冲电路延迟时间和KM、KI的拟合曲线如图16所示。图16a为KM=0.63下拟合得到的延迟时间td3+td4和实际测量值(图中的红色数据点),实际测量值和拟合数据基本一致;如图16b所示,在KI=0.48下的拟合延迟时间和实际时间常数td3基本相同。后续的实验参数选择依据上述拟合得到的KM和KI。

图16 延迟时间常数拟合

Fig.16 Matching delay time under various RC

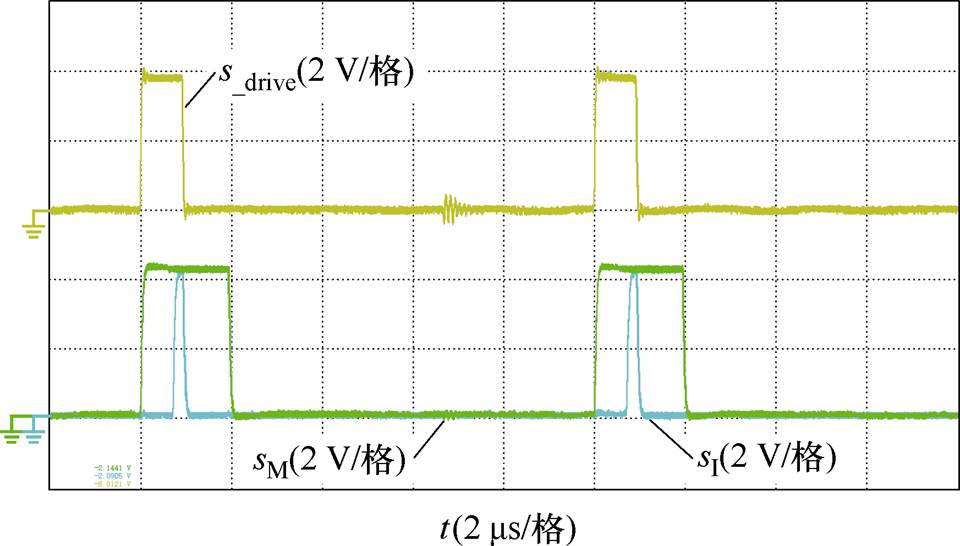

窄输入脉冲下输出波形如图17所示,当输入信号脉冲宽度较小时,s_drive导致生成对应的上升沿脉冲so_on和下降沿生成的脉冲so_off,在经过与门运算后导致两个脉冲重合,sM变为单个脉冲,为了防止缺失下第2个触发脉冲拉低sI,加入信号保护电路后,当so_on和so_off同时为高,保护信号被拉低,直接重置生成sI的D触发器Q3,sI被拉低。信号重置电路的加入避免了由于缺少第二个触发上升沿而导致sI保持高电平的信号乱序情况。

图17 窄输入脉冲下输出波形

Fig.17 The output waveforms under the narrow pulse

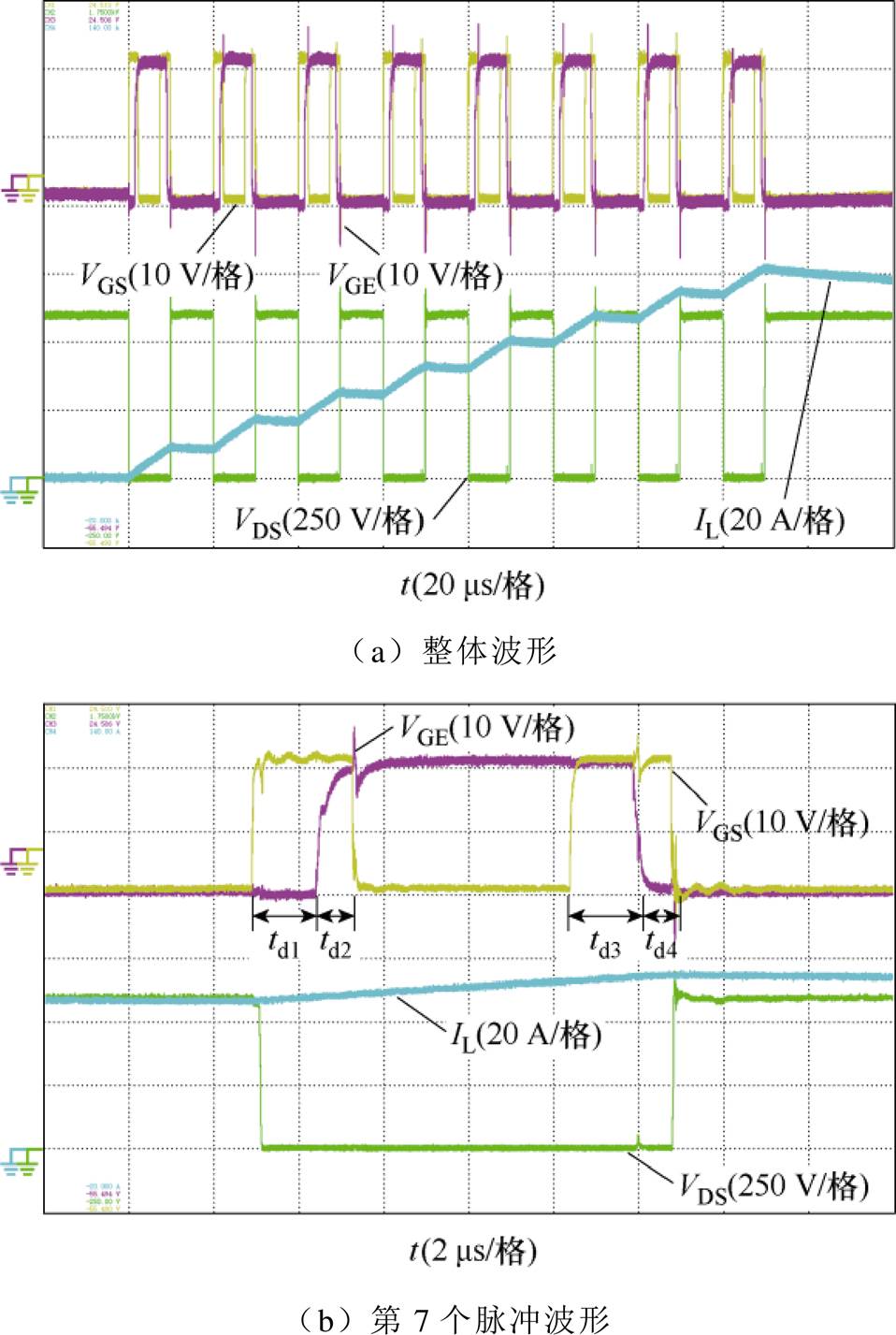

为了进一步验证最小SiC导通模式下SiC/Si HyS的损耗特性,将搭建的SiC/Si HyS硬件测试平台配置为双脉冲测试电路,负载电感为676 mH,母线电压为600 V,测试信号频率为50 kHz,脉冲宽度为10 ms。由于所提出的信号调制电路会比原本信号多出td3+td4的脉冲宽度,为了保证脉冲结束时刻负载电流的一致性,输入信号脉冲宽度根据时间尺度进行调节。图18所示为td1=td3=1.5 ms,td2=td4= 1 ms调制下的相关电压电流波形,其中VGS和VGE分别为SiC MOSFET和Si IGBT驱动电压;VDS为SiC/Si HyS的端电压;IL为负载电感电流。

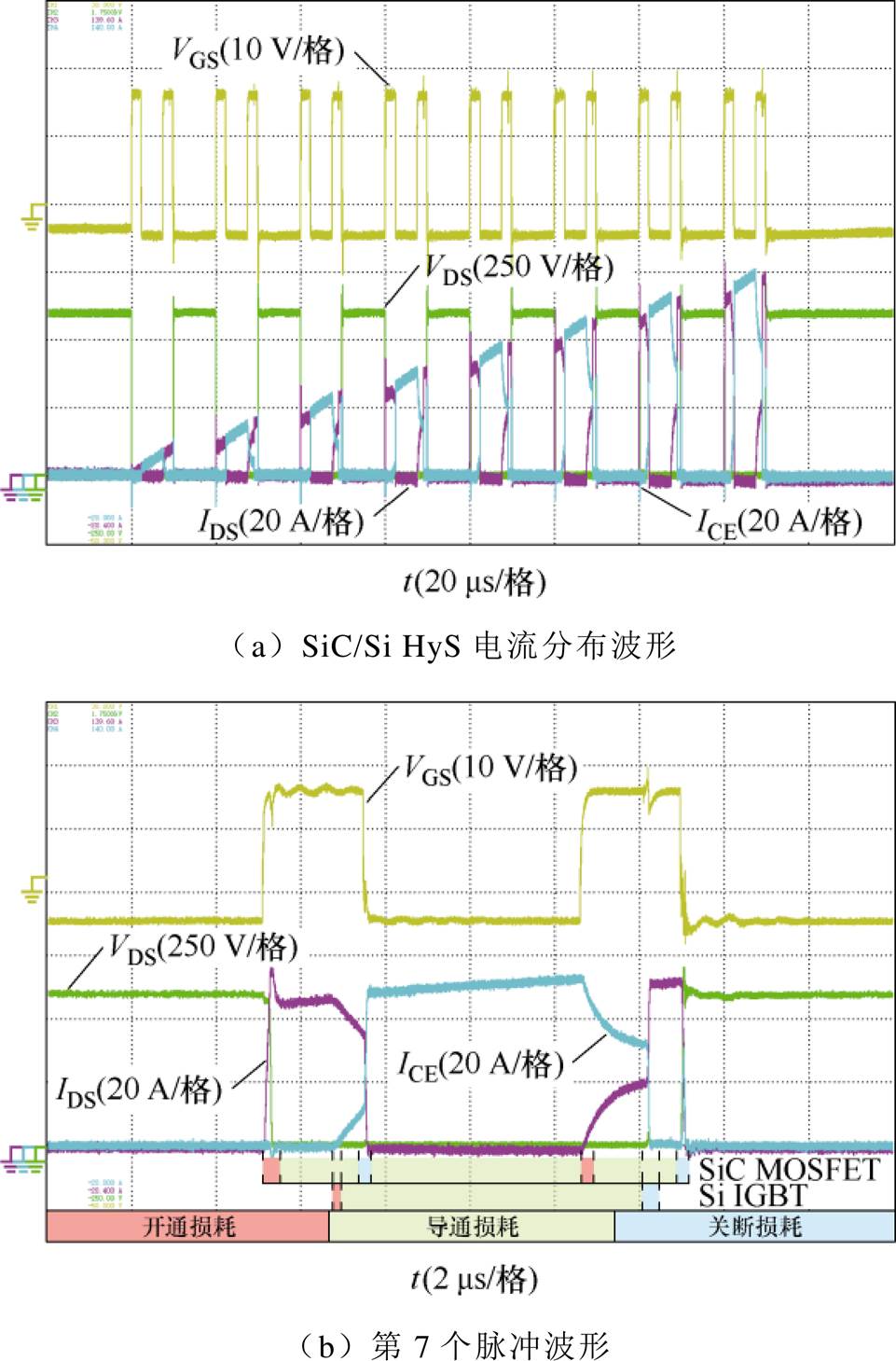

图19所示为SiC MOSFET和Si IGBT的电流分布情况,IDS和ICE分别SiC MOSFET漏源极输出电流和Si IGBT集电极-发射极电流。在td1阶段,仅有SiC MOSFET导通,SiC MOSFET承担全部负载电流。从td2开始,Si IGBT随之导通,在Si IGBT导通初期,导通电阻相对较小,因此Si IGBT承担电流仍小于SiC MOSFET直到td2阶段结束,SiC MOSFET关断,Si IGBT承担全部电流。在td3阶段内,Si IGBT从低导通电阻过渡到和SiC MOSFET并联,因此ICE>IDS。在整个导通阶段的器件损耗可以和图2所对应。

图18 双脉冲电路实验波形

Fig.18 The waveforms of the double-pulse test

图19 控制脉冲2下的电流分布

Fig.19 The current distribution of control pulse 2

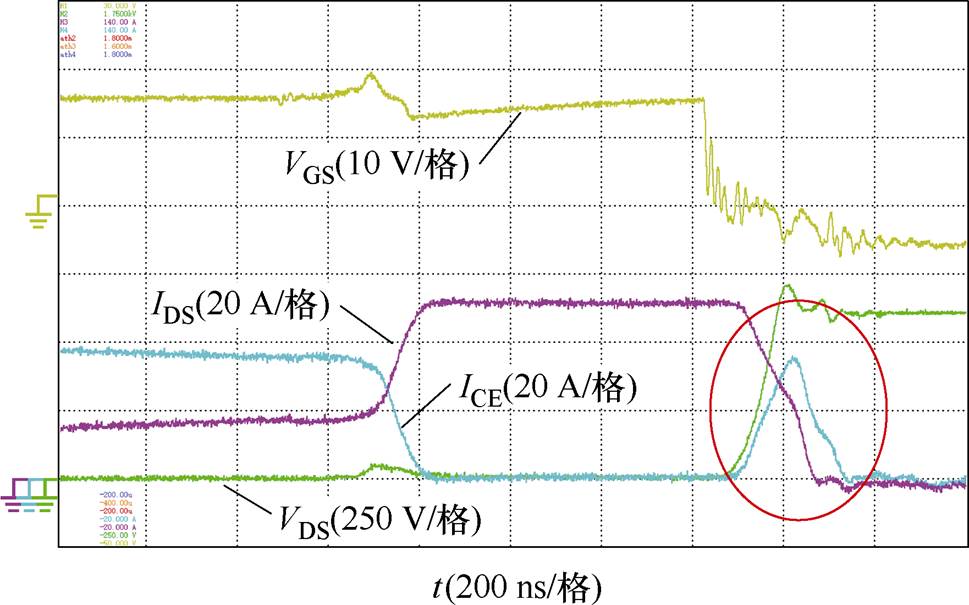

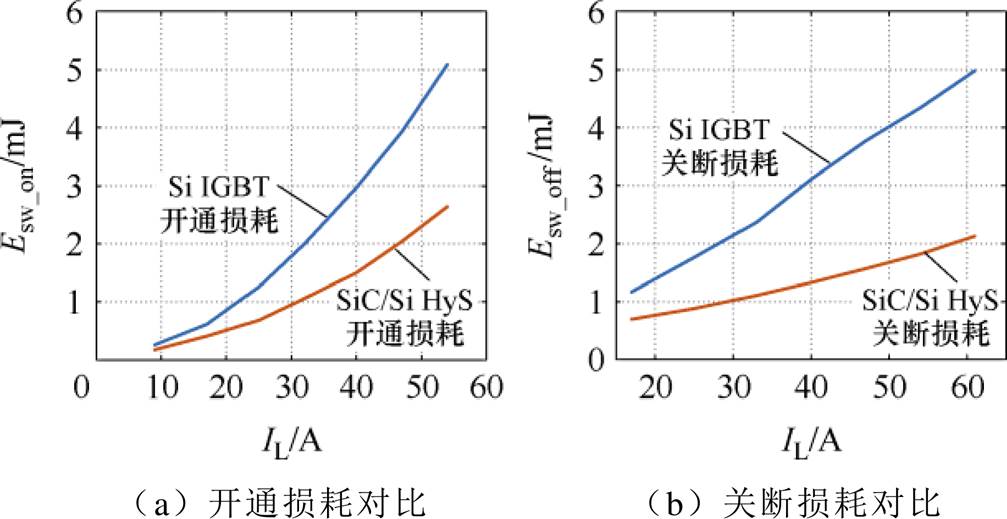

关断过程Si IGBT拖尾电流如图20所示,尽管SiC MOSFET已经完全关断,但Si IGBT的拖尾电流仍会存在,因此拖尾电流的存在导致SiC/Si HyS的实际开关损耗比单个SiC MOSFET的开关损耗更大。Si IGBT和SiC/Si HyS开关损耗对比如图21所示,在相同负载电流下,Si IGBT和SiC/Si HyS的开关损耗对比。尽管在关断过程中,Si IGBT的拖尾电流会增加开关损耗,但是得益于SiC MOSFET的低导通、关断时间,SiC/Si HyS的开关损耗相比于Si IGBT的开关损耗有所降低,尤其在高负载电流下,开关损耗减小超过50%。

图20 关断过程Si IGBT拖尾电流

Fig.20 The trail current of Si IGBT during turn-off transient

图21 Si IGBT和SiC/Si HyS开关损耗对比

Fig.21 The comparison of switching loss between Si IGBT and SiC/Si HyS

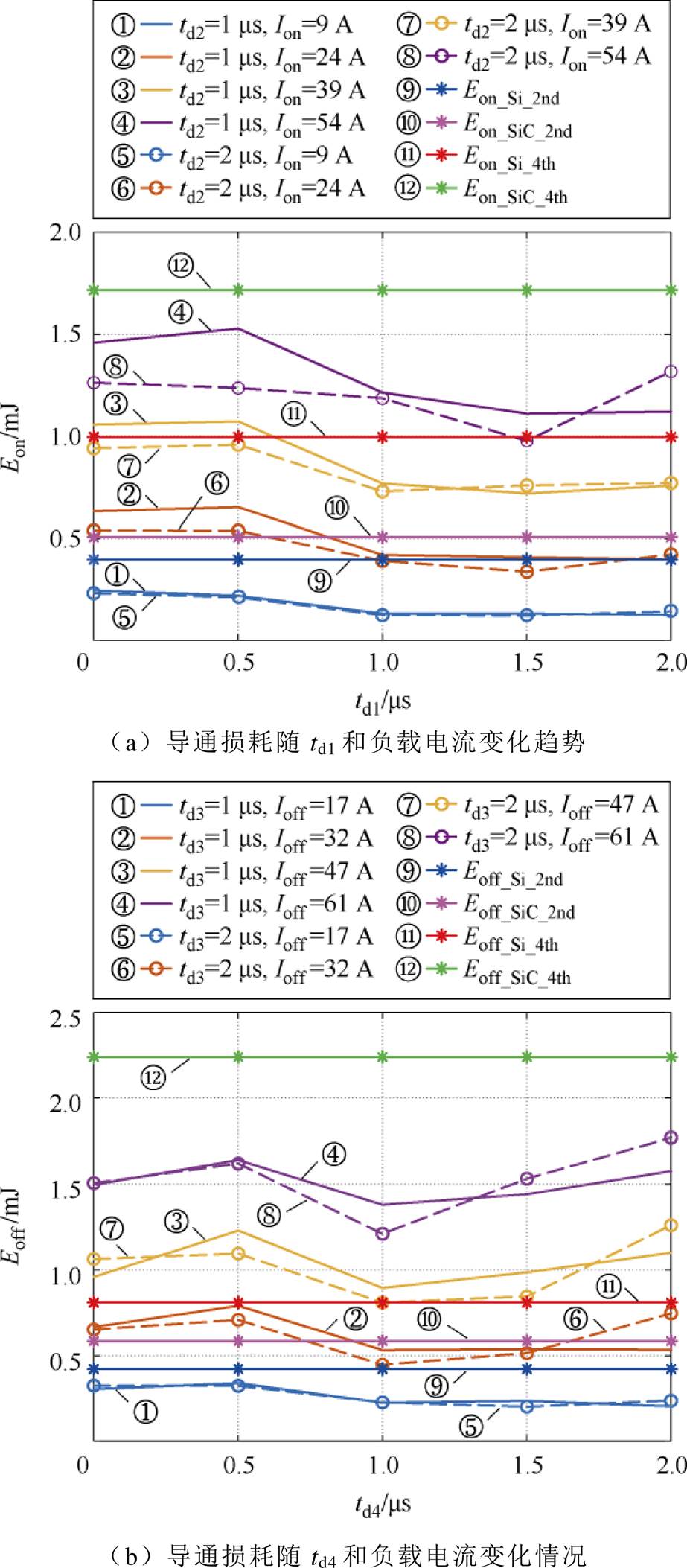

不同负载电流和时间尺度对导通损耗的影响如图22所示,为不同时间尺度和负载电流下的导通损耗分布情况。Eon为SiC MOSFET完全导通后(SiC/Si HyS的VDS降低至母线电压的10%)到整个导通周期一半时间内的导通损耗。Eoff为导通周期一半到SiC MOSFET开始进入关断过程(VDS上升至10%的母线电压)时间内的总导通损耗。Eon和Eoff所对应的导通时间皆为5 ms。Ion和Ioff分别为开通和关断时刻的负载电流。Eon_Si_2nd和Eon_SiC_2nd为对应Ion=24 A的负载条件下,单个Si IGBT和单个SiC MOSFET所对应的导通损耗,Eon_Si_4th和Eon_SiC_4th为对应Ion=54 A的负载条件下的导通损耗。Eoff_Si_2nd和Eoff_SiC_2nd为对应Ioff=32 A的导通周期内的损耗;Eoff_Si_4th Eoff_SiC_4th则为对应Ioff=61 A的导通周期内的损耗。

图22 不同负载电流和时间尺度对导通损耗的影响

Fig.22 The condition loss varying the time delay and load current

在低负载电流下,Si IGBT的导通电阻在非线性区内,其导通电阻将会大于SiC MOSFET的导通电阻,因此随着时间尺度的增加,SiC MOSFET的导通时间增加,整体的导通损耗降低。随着负载电流提升,Si IGBT导通电阻降低,随着td1和td4的增加,SiC MOSFET的单独导通时间增加,导致SiC/Si HyS的导通损耗变大,但比起相同负载电流下SiC MOFET单独导通的导通损耗,SiC/Si HyS的导通损耗更小。

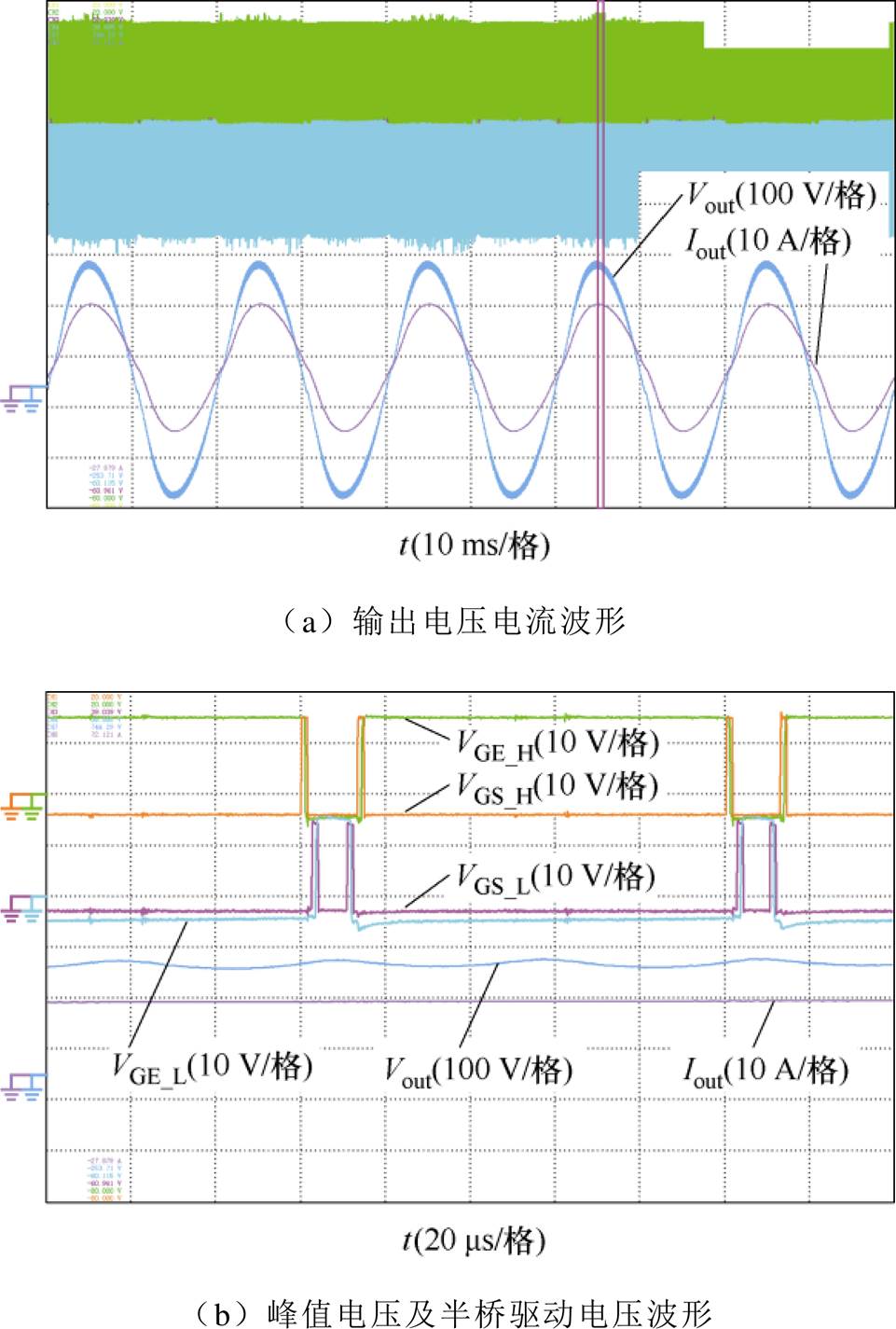

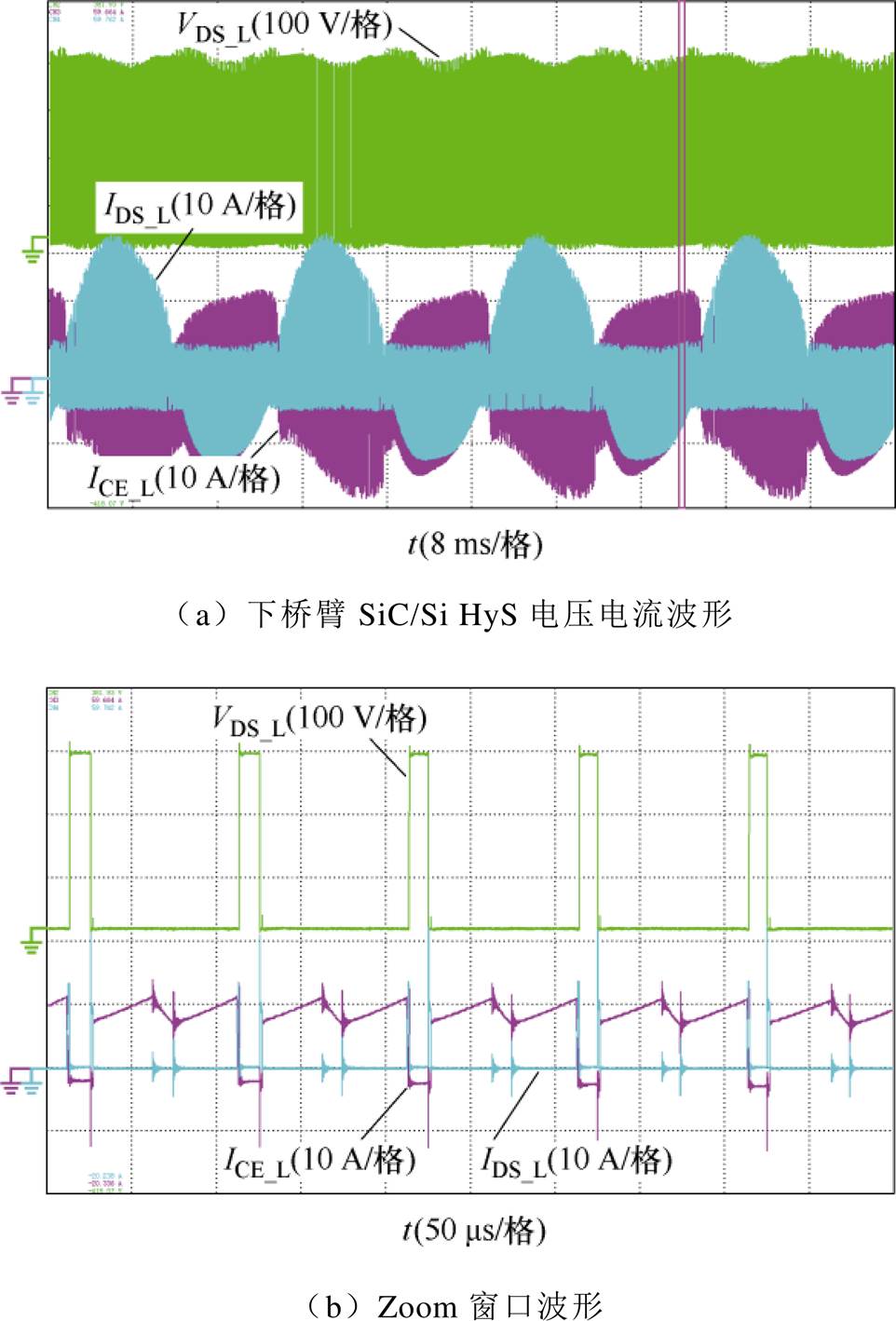

为了进一步验证所提出的信号调制电路的动态性能,将其应用于单极性倍频SPWM下的两电平逆变器,开关频率为10 kHz,以降低SiC MOSFET的开关损耗。输出侧经过LC滤波,滤波电感为4 mH,电容为1 mF。图23为单个桥臂的上、下半桥SiC/Si HyS的驱动电压和两电平逆变器的输出电压、电流波形,SiC/Si HyS的四个时间尺度配置为td1=td2=td3=td4= 800 ns,考虑时间尺度td3+td4=1.6 ms,单极性倍频SPWM的上、下半桥驱动信号的死区时间设定为2.5 ms。输出侧接阻性负载,输出功率为1.5 kW。图24为下桥臂中SiC MOSFET和Si IGBT的电流IDS_L和ICE_L。在单极性倍频SPWM下,所提出SiC/Si HyS驱动信号调制电路可以在占空比实时调节下保持稳定运行,输出对应SiC/Si HyS所需的驱动信号。

图23 单级倍频SPWM逆变输出电压波形

Fig.23 The output voltage waveforms under single-stage frequency doubling modulation SPWM

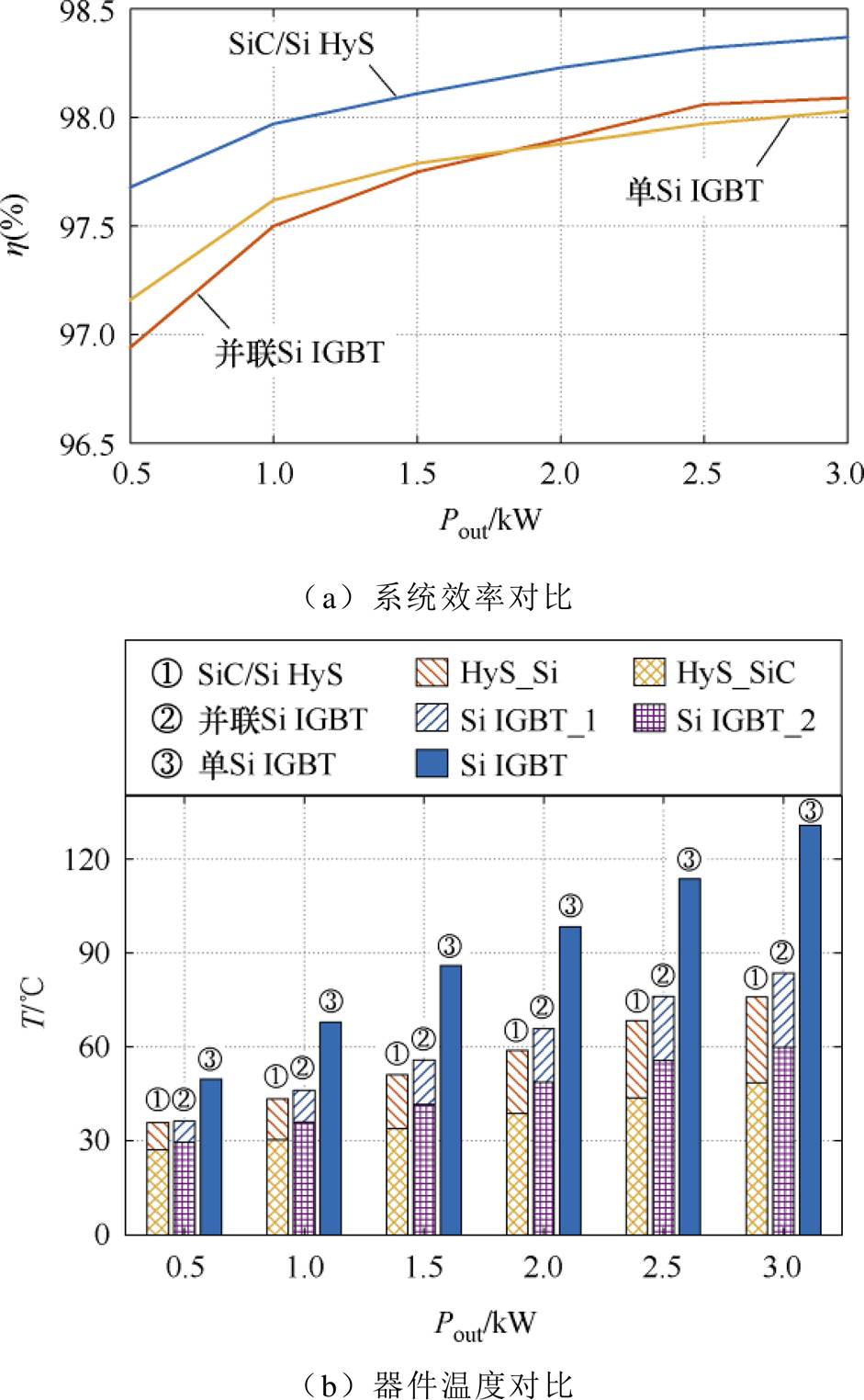

最小SiC MOSFET导通模式下的SiC/Si HyS和全Si IGBT系统的效率h 及器件温度T对比曲线如图25所示,运行时间和散热系统完全相同。SiC/Si HyS系统比全Si IGBT系统具有更高效率,SiC MOSFET具备更低的开关损耗,同时也为Si IGBT构建了零电压软开关条件。对于并联Si IGBT系统,Si IGBT在低电流负载下的导通电阻更高,因此在低功率等级下并联Si IGBT系统效率对比单Si IGBT系统效率更低,直至负载电流提升后,并联Si IGBT系统效率有所增加。对于SiC/Si HyS系统,Si IGBT只承担导通损耗,SiC MOSFET承担开关损耗,因此器件的发热相比于并联Si IGBT更低,器件表现温度更低。SiC/Si HyS在效率提升和器件温度控制方面更具优势。

图24 下桥臂SiC/Si HyS电压、电流波形

Fig.24 The voltage and current waveforms of SiC/Si HyS

图25 不同功率等级下效率和器件温度分布对比

Fig.25 The comparison of efficiency and temperature of devices with various power level

本文分析了最小SiC MOSFET导通模式下的损耗分布特性,在此基础上提出一种结构简单的信号调制电路,该电路可以依靠调节RC参数,灵活配置最小SiC MOSFET导通模式下的四个时间尺度。分析了所提电路的工作原理,建立时间尺度与RC参数之间函数关系,并通过所搭建的实验样机和硬件测试平台对所提出的方法进行验证,进一步阐述了最小SiC导通模式的时间尺度对SiC/Si HyS结构损耗分布的影响;在单极性倍频调制控制模式下的1.5 kW两电平逆变器中,验证了所提信号调制电路具有良好的动态性能和稳定性。在效率和器件温度分布方面,SiC/Si HyS结构更具优势。

参考文献

[1] Zhou Yimin, Wang Zhiqiang, Xin Guoqing, et al. Dead time optimization for synchronous switching of SiC MOSFETs considering nonlinear gate capa- citance[J]. IEEE Transactions on Power Electronics, 2023, 38(5): 5665-5669.

[2] 董振邦, 徐云飞, 李卫国, 等. 应用于电力系统的SiC MOSFET器件开关特性优化控制方法[J]. 中国电机工程学报, 2020, 40(增刊1): 254-264.

Dong Zhenbang, Xu Yunfei, Li Weiguo, et al. Optimized control method for switching chara- cteristics of SiC MOSFET devices applied to power systemsr[J]. Proceedings of the CSEE, 2020, 40(S1): 254-264.

[3] 邵天骢, 郑琼林, 李志君, 等. 基于干扰动态响应机理的SiC MOSFET驱动设计[J]. 电工技术学报, 2021, 36(20): 4204-4214.

Shao Tiancong, Zheng Qionglin, Li Zhijun, et al. SiC MOSFET gate driver design based on interference dynamic response mechanism[J]. Transactions of China Electrotechnical Society, 2021, 36(20): 4204- 4214.

[4] 王来利, 赵成, 张彤宇, 等. 碳化硅功率模块封装技术综述[J]. 电工技术学报, 2023, 38(18): 4947- 4962.

Wang Laili, Zhao Cheng, Zhang Tongyu, et al. Review of packaging technology for silicon carbide power modules[J]. Transactions of China Electro- technical Society, 2023, 38(18): 4947-4962.

[5] 张少昆, 孙微, 范涛, 等. 基于分立器件并联的高功率密度碳化硅电机控制器研究[J]. 电工技术学报, 2023, 38(22): 5999-6014.

Zhang Shaokun, Sun Wei, Fan Tao, et al. Research on high power density silicon carbide motor controller based on parallel connection of discrete devices[J]. Transactions of China Electrotechnical Society, 2023, 38(22): 5999-6014.

[6] 肖标, 郭祺, 涂春鸣, 等. 面向开关时序与驱动电压自主协同调控的SiC/Si混合开关驱动电路[J]. 电工技术学报, 2025, 40(4): 1117-1128.

Xiao Biao, Guo Qi, Tu Chunming, et al. SiC/Si hybrid switch drive circuit with autonomous and coor- dinated[J]. Transactions of China Electrotechnical Society, 2025, 40(4): 1117-1128.

[7] 任鹏, 涂春鸣, 侯玉超, 等. 基于Si和SiC器件的混合型级联多电平变换器及其调控优化方法[J]. 电工技术学报, 2023, 38(18): 5017-5028.

Ren Peng, Tu Chunming, Hou Yuchao, et al. Research on a hybrid cascaded multilevel converter based on Si and SiC device and its control optimization method[J]. Transactions of China Electrotechnical Society, 2023, 38(18): 5017-5028.

[8] Minamisawa R A, Vemulapati U, Mihaila A, et al. Current sharing behavior in Si IGBT and SiC MOSFET cross-switch hybrid[J]. IEEE Electron Device Letters, 2016, 37(9): 1178-1180.

[9] Tan Changyu, Stecca M, Soeiro T B, et al. Performance evaluation of an electric vehicle traction drive using Si/SiC hybrid switches[C]//2021 IEEE 19th International Power Electronics and Motion Control Conference (PEMC), Gliwice, Poland, 2021: 278-283.

[10] Wang Bo, Yu Jiajun, Yu Hengyu, et al. A modeling method for Si/SiC hybrid switch based on finite state machine[C]//2021 IEEE 1st International Power Electronics and Application Symposium (PEAS), Shanghai, China, 2021: 1-5.

[11] Ning Puqi, Yuan Tianshu, Kang Yuhui, et al. Review of Si IGBT and SiC MOSFET based on hybrid switch[J]. Chinese Journal of Electrical Engineering, 2019, 5(3): 20-29.

[12] Li Zongjian, Wang Jun, Ji Bing, et al. Power loss model and device sizing optimization of Si/SiC hybrid switches[J]. IEEE Transactions on Power Electronics, 2020, 35(8): 8512-8523.

[13] Wang Jun, Li Zongjian, Jiang Xi, et al. Gate control optimization of Si/SiC hybrid switch for junction temperature balance and power loss reduction[J]. IEEE Transactions on Power Electronics, 2019, 34(2): 1744-1754.

[14] Deshpande A, Luo Fang. Practical design conside- rations for a Si IGBT SiC MOSFET hybrid switch: parasitic interconnect influences, cost, and current ratio optimization[J]. IEEE Transactions on Power Electronics, 2019, 34(1): 724-737.

[15] Li Zongjian, Wang Jun, Deng Linfeng, et al. Active gate delay time control of Si/SiC hybrid switch for junction temperature balance over a wide power range[J]. IEEE Transactions on Power Electronics, 2020, 35(5): 5354-5365.

[16] He Jiangbiao, Katebi R, Weise N. A current- dependent switching strategy for Si/SiC hybrid switch-based power converters[J]. IEEE Transactions on Industrial Electronics, 2017, 64(10): 8344-8352.

[17] 李宗鉴, 王俊, 江希, 等. Si IGBT/SiC MOSFET混合器件及其应用研究[J]. 电源学报, 2020, 18(4): 58-70.

Li Zongjian, Wang Jun, Jiang Xi, et al. Si IGBT/SiC MOSFET hybrid switch and its applications[J]. Journal of Power Supply, 2020, 18(4): 58-70.

[18] Peng Zishun, Wang Jun, Liu Zeng, et al. Fault- tolerant inverter operation based on Si/SiC hybrid switches[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 545-556.

[19] Wang Jun, Jiang Xi, Li Zongjian, et al. Short-circuit ruggedness and failure mechanisms of Si/SiC hybrid switch[J]. IEEE Transactions on Power Electronics, 2019, 34(3): 2771-2780.

[20] Peng Zishun, Wang Jun, Liu Zeng, et al. A variable- frequency current-dependent switching strategy to improve tradeoff between efficiency and SiC MOSFET overcurrent stress in Si/SiC-hybrid-switch- based inverters[J]. IEEE Transactions on Power Electronics, 2021, 36(4): 4877-4886.

[21] 李宗鉴, 王俊, 余佳俊, 等. SiC JMOS和SiC DMOS在Si/SiC混合器件单相逆变器中的应用研究[J]. 中国电机工程学报, 2019, 39(19): 5674-5682.

Li Zongjian, Wang Jun, Yu Jiajun, et al. Application of SiC JMOS and SiC DMOS in Si/SiC hybrid switch based single-phase inverter[J]. Proceedings of the CSEE, 2019, 39(19): 5674-5682.

[22] Gu Cong, Wang Xiaolin, Deng Zhiquan. Evaluation of three improved space-vector-modulation strategies for the high-speed permanent magnet motor fed by a SiC/Si hybrid inverter[J]. IEEE Transactions on Power Electronics, 2021, 36(4): 4399-4409.

[23] Liu Haichen, Zhou Jiale, Zhao Tiefu, et al. Si IGBT and SiC MOSFET hybrid switch-based solid state circuit breaker for DC applications[C]//2022 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 2022: 1-6.

[24] Zhang Li, Zheng Zhongshu, Lou Xiutao. A review of WBG and Si devices hybrid applications[J]. Chinese Journal of Electrical Engineering, 2021, 7(2): 1-20.

[25] Stecca M, Tan Changyu, Xu Junzhong, et al. Hybrid Si/SiC switch modulation with minimum SiC MOSFET conduction in grid connected voltage source converters[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2022, 10(4): 4275- 4289.

[26] 刘平, 陈梓健, 苗轶如, 等. 基于开关瞬态反馈的SiC MOSFET有源驱动电路[J]. 电工技术学报, 2022, 37(17): 4446-4457.

Liu Ping, Chen Zijian, Miao Yiru, et al. Active gate driver for SiC MOSFET based on switching transient feedback[J]. Transactions of China Electrotechnical Society, 2022, 37(17): 4446-4457.

[27] Qian Cheng, Wang Zhiqiang, Xin Guoqing, et al. Datasheet driven switching loss, turn-ON/OFF over- voltage, di/dt, and dv/dt prediction method for SiC MOSFET[J]. IEEE Transactions on Power Electronics, 2022, 37(8): 9551-9570.

[28] 黄海宏, 彭岚, 王海欣. 并联IGBT占空比的温度特性建模与分析[J]. 电工技术学报, 2024, 39(14): 4422-4431.

Huang Haihong, Peng Lan, Wang Haixin. Modeling and analysis of temperature characteristics of parallel IGBTs duty cycle[J]. Transactions of China Elec- trotechnical Society, 2024, 39(14): 4422-4431.

[29] 谭亚雄, 张梦洋, 刘元, 等. 一种连续函数描述的高精度SiC MOSFET模型[J]. 电工技术学报, 2024, 39(18): 5719-5731.

Tan Yaxiong, Zhang Mengyang, Liu Yuan, et al. A high-precision SiC MOSFET model with continuous function description[J]. Transactions of China Elec- trotechnical Society, 2024, 39(18): 5719-5731.

[30] Sun Kai, Wu Hongfei, Lu Juejing, et al. Improved modeling of medium voltage SiC MOSFET within wide temperature range[J]. IEEE Transactions on Power Electronics, 2014, 29(5): 2229-2237.

[31] 范迦羽, 郑飞麟, 王耀华, 等. 计及热阻与发射极电感匹配的并联IGBT芯片稳态结温均衡方法[J]. 电工技术学报, 2022, 37(12): 3028-3037.

Fan Jiayu, Zheng Feilin, Wang Yaohua, et al. Steady Temperature Equalization Method for the Parallel IGBTs Considering the Thermal Resistance and the Matching Emitter Parasitic Inductance[J]. Transa- ctions of China Electrotechnical Society, 2022, 37(12): 3028-3037.

[32] 崔曼, 胡震, 张腾飞, 等. 基于壳温信息的功率器件可靠性分析[J]. 电工技术学报, 2023, 38(24): 6760-6767.

Cui Man, Hu Zhen, Zhang Tengfei, et al. Reliability analysis of power device based on the case tempera- tures[J]. Transactions of China Electrotechnical Society, 2023, 38(24): 6760-6767.

Abstract Silicon carbide (SiC) metal-oxide-semiconductor field effect transistors (MOSFETs) are increasingly preferred over Silicon (Si) insulated-gate bipolar transistors (IGBTs) due to their superior switching capabilities and high temperature withstand. Nonetheless, Si IGBTs maintain their position as the primary power devices in industrial settings, attributed to their greater durability and reduced on-resistance when dealing with high currents. However, the limited switching frequency of IGBTs impedes the advancement of power electronic converters, as the lingering currents during the off-transition phase lead to elevated switching losses. A hybrid SiC/Si switch (HyS) offers a balanced solution, optimizing cost and switching performance. Typical SiC/Si HyS control methods involve deactivating Si IGBTs sooner and reactivating them after SiC MOSFETs. The minimum conduction strategy for SiC MOSFETs within the SiC/Si HyS configuration ensures that SiC MOSFETs operate exclusively during the Si IGBTs’ switching intervals, which contributes to minimizing the expenses associated with SiC MOSFETs and the required chip space.

Since SiC MOSFET is activated twice during the switching transients of Si IGBT, the minimum SiC MOSFET conduction mode has two more controllable time scales than the common mode of SiC/Si HyS. By dissecting each sub-stage, the loss characteristics of the minimum SiC conduction mode are quantitatively analyzed. A visual relationship regarding the time scale and load current on the conduction loss is provided in a two-level sinusoidal inverter. At low-current conditions, the output characteristic of the Si IGBT is nonlinear, resulting in increased time scales that help to reduce the conduction loss.

A signal modulation circuit is proposed to conveniently generate the control signal for the minimum SiC MOSFET conduction HyS. The proposed circuit comprises one OR gate (Q4) and three D flip-flops (Q1~Q3). The time delay is generated by adjusting the input signal rate with the RC buffer circuit. The rising edge of sO_on and sO_off generates the driving signal for Si IGBT. The pulse of s_drive may be narrower than sO_on orsO_off, resulting in overlapping sO_on andsO_off. Consequently, sI fails to be pulled down by the rising edge of sO_off. Therefore, a NAND gate Q5 is added to reset Q3 when an overlapping signal occurs.

A simple signal modulation circuit is proposed for the minimum SiC MOSFET conduction mode of SiC/Si HyS to generate the corresponding driving signals for SiC MOSFET and Si IGBT. The four-time scales of the minimum SiC MOSFET conduction mode can be flexibly adjusted by adopting the calculated values of the RC buffer circuit. The loss characteristics of the minish SiC MOSFET conduction mode of SiC/Si HyS are described quantitatively. Subsequently, the paper introduces the operation principle and functional relationship of the RC buffer circuit. The relationship between the time scale and RC values is validated using the signal modulation circuit prototype. Combined with the signal modulation circuit and a double-pulse test circuit, the effect of the time scale of the minimum SiC conduction mode on the loss distribution of the SiC/Si HyS structure is verified. The proposed signal modulation circuit has good dynamic performance and stability in a 1.5 kW two-level inverter under the unipolar frequency-doubling modulation control mode. Furthermore, the experimental results show that SiC/Si HyS achieves better efficiency and temperature-escalating performance.

keywords:SiC MOSFET, Si IGBT, hybrid switch, switching loss, signal modulation

DOI: 10.19595/j.cnki.1000-6753.tces.240254

中图分类号:TM92

国家自然科学基金资助项目(52377173)。

收稿日期 2024-02-08

改稿日期 2024-02-24

丁四宝 男,1994年生,博士研究生,研究方向宽禁带器件驱动技术和串联均压控制等。E-mail: 19B906033@stu.hit.edu.cn

王盼宝 男,1984年生,副教授,博士生导师,研究方向为微电网运行控制与互联技术、高集成度变换器拓扑与优化技术等。E-mail: wangpanbao@hit.edu.cn(通信作者)

(编辑 陈 诚)