(1)

(1)

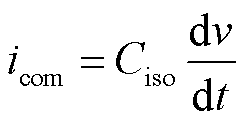

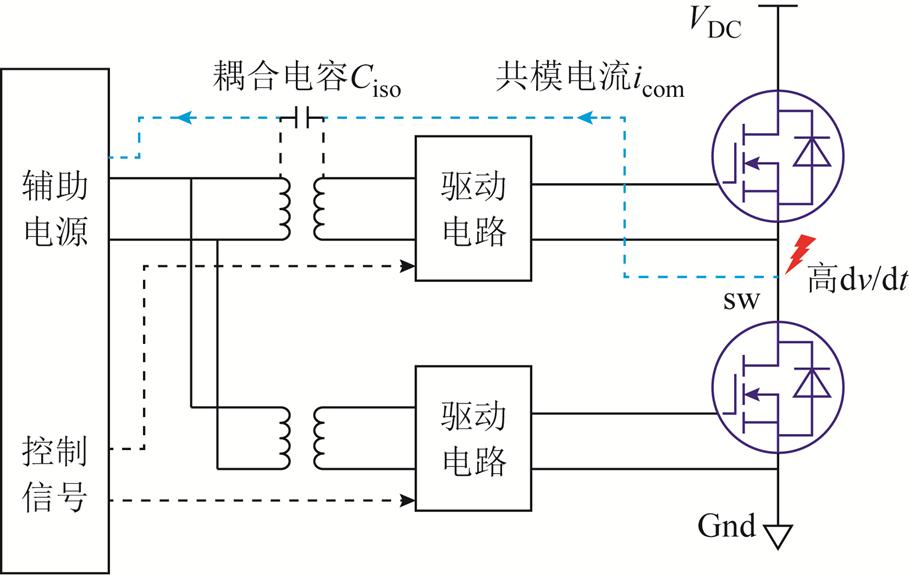

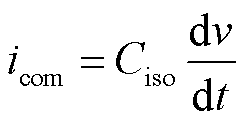

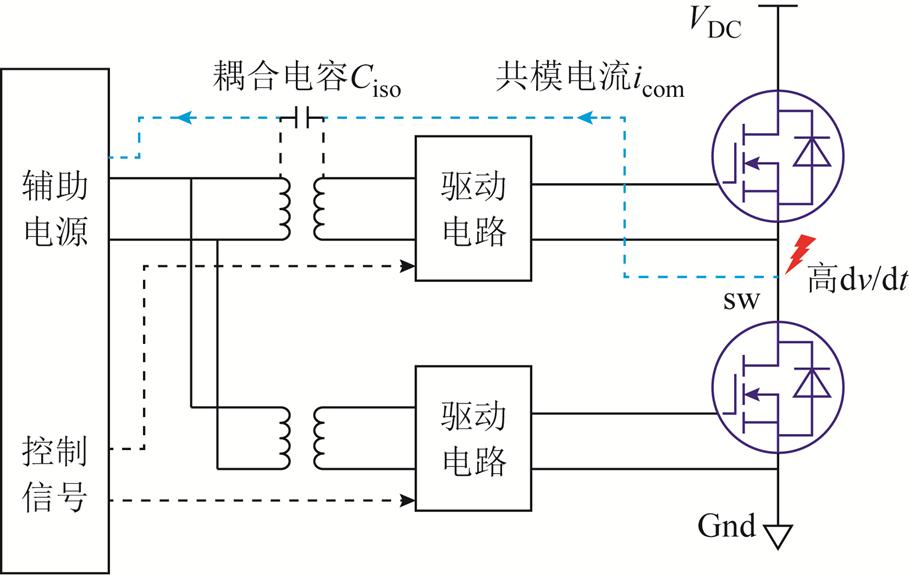

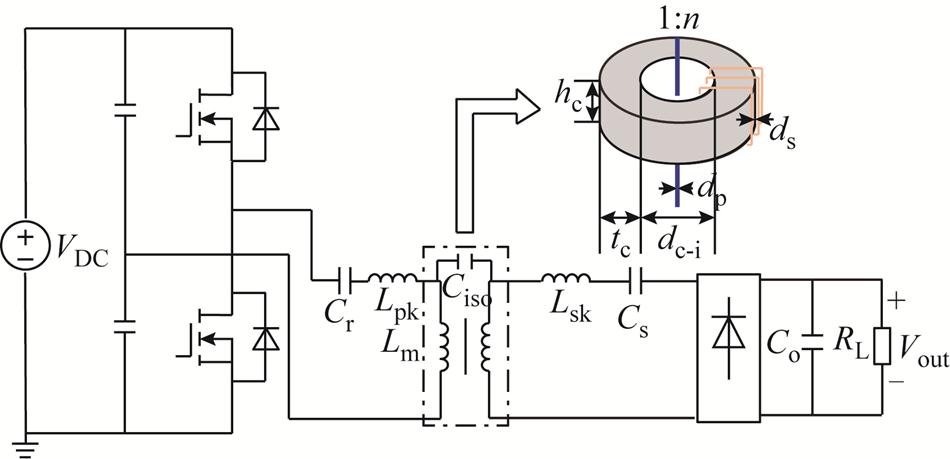

图1 高dv/dt共模干扰回路

Fig.1 High dv/dt common mode interference circuit

摘要 高压碳化硅(SiC)器件驱动电路的隔离电源面临更高的dv/dt冲击,极易引起强共模干扰而导致器件失效。高频电流互感器(HCT)型取能是一种新型高压SiC器件隔离取能方法,但是其耦合电容与结构参量关联特性不清,难以有效提升抗dv/dt性能和实现小型化。该文首先,构建了HCT型隔离取能结构的三维仿真模型,系统地探究了其关键结构参量(隔离距离、偏心位置、绕组绕制方式、匝数等)对耦合电容的影响特性;然后,提出了HCT型取能结构多参量影响下的耦合电容优化方法,同等体积下达到耦合电容最小;最后,通过实验验证了所述方法和所研装置的有效性。结果表明,仅通过调整HCT型隔离取能结构穿心位置可降低约20%的耦合电容,所研取能装置隔离容值仅为0.74 pF,比传统设计和同类商业产品分别降低了55%和70%,最大无局部放电电压达到15.5 kV。

关键词:高压SiC器件 隔离取能装置 低耦合电容 电流互感器

近年来,Wolfspeed、Rohm、GeneSiC等半导体公司相继推出了1.7 kV和3.3 kV等商业化高压碳化硅(SiC)功率器件[1],弗吉尼亚理工大学和俄亥俄州立大学等高校就10 kV及以上的SiC功率器件应用展开了研究[2-3]。基于高压SiC器件构建的新一代电力变换系统具有器件少、效率高、体积小等优势,现已逐步应用于中高压变频器、固态变压器、并网逆变器等领域[4-5]。然而,对比常规的Si器件,SiC器件的开关速度和dv/dt冲击具有10倍以上的激增,可达到100 kV/μs[6]。强dv/dt冲击会通过SiC器件驱动电路隔离电源的耦合电容造成强共模电流瞬态干扰,进而导致驱动脉冲触发故障产生器件烧毁击穿事故[7]。因此,迫切需要研究SiC器件耐高压和低耦合电容的隔离取能方法,提高SiC器件及装备应用的安全可靠性。

目前主要的隔离取能结构分为无磁心型和有磁心型两类。无磁心型隔离取能结构主要有光纤传能(Power over Fiber, PoF)和无线电能传输(Wireless Power Transformer, WPT)。PoF型隔离取能结构通过光纤实现能量传递,理论上完全消除了耦合电容,但由于光纤发射器输出功率低(小于0.5 W)且价格昂贵,不利于规模化应用[8]。WPT通过空气或其他绝缘介质实现了电气隔离,整体设计去磁心化,但其发射和接收线圈体积相对较大,存在功率密度低、空间电磁干扰等问题[9-11]。

磁心型隔离取能结构分为变压器(Voltage Transformer, VT)型和电流互感器(Current Transformer, CT)型。VT型是最常见的隔离取能结构,通过一次、二次绕组耦合实现能量传递,通过间隔距离实现电气隔离[12-14]。该传能方法的结构和控制简单,但是存在寄生参量大,隔离电压提升带来体积/质量急剧增大的问题。现有高压VT型隔离取能结构实现约5~15 kV隔离电压,但是在高功率密度设计下电压难以突破20 kV,耦合电容较大,通常在4 pF以上。

高频电流互感器(High-Frequency Current Transformer, HCT)型隔离取能是一种新的高压SiC器件取能方法。它通过单根导线和高频电磁场耦合的方式实现传能,因超高频电磁耦合带来的高集成度和一次绕组侧单匝线圈带来的低耦合电容这两个优势,是极具潜力的高压强抗dv/dt隔离取能方法。传统电流互感器型取能方法应用于高压输电线路上,通过工频(50 Hz/60 Hz)高压输电母线大电流产生的电磁场感应取能,并为传感器或监测装置供能。然而,传统CT型取能装置体积大、质量大,输出功率受限于大母线电流,无法满足强抗dv/dt和高功率密度的SiC器件应用场景[15-16]。

亚琛工业大学J. Gottschlich等[17]于2016年首先提出了HCT型隔离取能结构,传输频率为50 kHz,显著减小了传统CT型取能装置的体积和质量,并在1.7 kV的SiC半桥模块得以应用。弗吉尼亚理工大学的D. Boroyevich等[18]在2018年提出了更高频率传输和集中式绕组结构的HCT型装置,传输频率达到1 MHz,其空气介质下的耦合电容为2.0 pF,最大无局部放电电压峰值约为10 kV。德州大学A. Q. Huang等[19]在2020年提出了基于分散式绕组结构的HCT取能装置,并应用在7.2 kV/60 A SiC器件上,耦合电容减小为3.0 pF,最大无局部放电电压峰值为6.5 kV。然而,以上HCT型取能的研究侧重在功率传输模型、高效传输方法和绝缘性能的分析验证上,其位型结构特征参量与寄生耦合电容关联特性不明晰,优化方法缺失,极大地限制了其抗dv/dt能力的提高。

因此,本文首先对高dv/dt电压下的共模干扰进行了分析,通过HCT型隔离取能结构研究甄选了影响耦合电容的关键结构参数;然后,采用有限元仿真构建了HCT型隔离取能结构的三维结构物理模型,系统性地探究并揭示了其关键结构参量(隔离距离、偏心位置、绕组绕制方式、匝数等)对隔离耦合电容影响的关联规律,提出了其耦合电容抑制的设计方法;最后,通过构建的HCT型隔离取能结构耦合电容测试平台及样机验证了所述特性和方法的有效性。结果表明,在不改变磁心结构的前提下,仅通过穿心位置和绕组绕制方式的调整可有效降低耦合电容,优化后所研装置隔离电容仅为0.74 pF,比同类商业产品降低70%以上。同时局部放电试验结果表明,所研装置最大无局放电压达15.5 kV。本文的研究为高压SiC器件及其装备的高隔离、强抗干扰、高紧凑度的驱动装置取能提供了新路径。

高dv/dt共模干扰回路如图1所示,其以SiC器件半桥电路为例说明了耦合电容Ciso与高压共模干扰的形成关联。高压SiC器件能实现几千到几万Hz的开关频率,开断瞬间半桥电路中性点sw处的dv/dt可达100 kV/μs甚至更高[20]。上半桥驱动电路及隔离取能结构二次侧的地电位与高dv/dt的sw处相连,产生强高压和高dv/dt地电位变化。隔离取能结构一次侧由于通过低电压供电,地电位与大地相连,通常为0 V。因此,高dv/dt源会通过隔离取能装置的Ciso形成流经驱动电路、隔离取能装置和低压侧辅助电路的强共模干扰电流。共模电流大小主要由Ciso和半桥电路开断过程中的dv/dt决定,如式(1)所示。

(1)

(1)

图1 高dv/dt共模干扰回路

Fig.1 High dv/dt common mode interference circuit

因此,过大的隔离耦合电容将会产生极强的共模电流干扰,对一次侧控制电路、隔离电源供电、驱动电路均会造成未知的电流冲击,严重影响其工作可靠性,甚至造成高压SiC器件误触发引发烧毁事故。

HCT型隔离取能装置的工作原理如图2所示,主要由高频半桥逆变电路、谐振网络、HCT型隔离取能结构、全桥整流电路、驱动电路代表的直流负载组成。与传统变压器型隔离取能装置不同,本文采用的隔离取能结构一次侧仅采用单匝穿心母线,简化了结构设计。此外,HCT采用的高频传输策略显著降低了传统CT型取能装置磁心体积和高耦合系数的要求。与高压SiC器件dv/dt干扰强度密切关联的是HCT结构一次、二次侧耦合产生的寄生耦合电容Ciso。

图2 HCT型隔离取能装置工作原理

Fig.2 Schematic diagram of HCT isolated power transfer device

图2中黑色点画线框为HCT隔离取能结构,主要由一次绕组、高频磁心、二次绕组组成。一次绕组为蓝色标注部分,位于磁心中点,其核心位型结构参数包括长度、直径、穿心位置。高频磁心为灰色圆环部分,用于增强一二次侧电磁场耦合度,其核心结构参数包括内径、高度、厚度。二次绕组为杏色部分,用于接收能量并给负载供能,其核心结构参数包括绕制方式、直径、匝数。这三部分均对HCT传能结构的Ciso产生作用但影响特性未知。图中,dp为一次绕组的直径,dc-i为磁心的内径,tc为磁心的厚度,hc为磁心的高度,n为二次绕组的匝数。

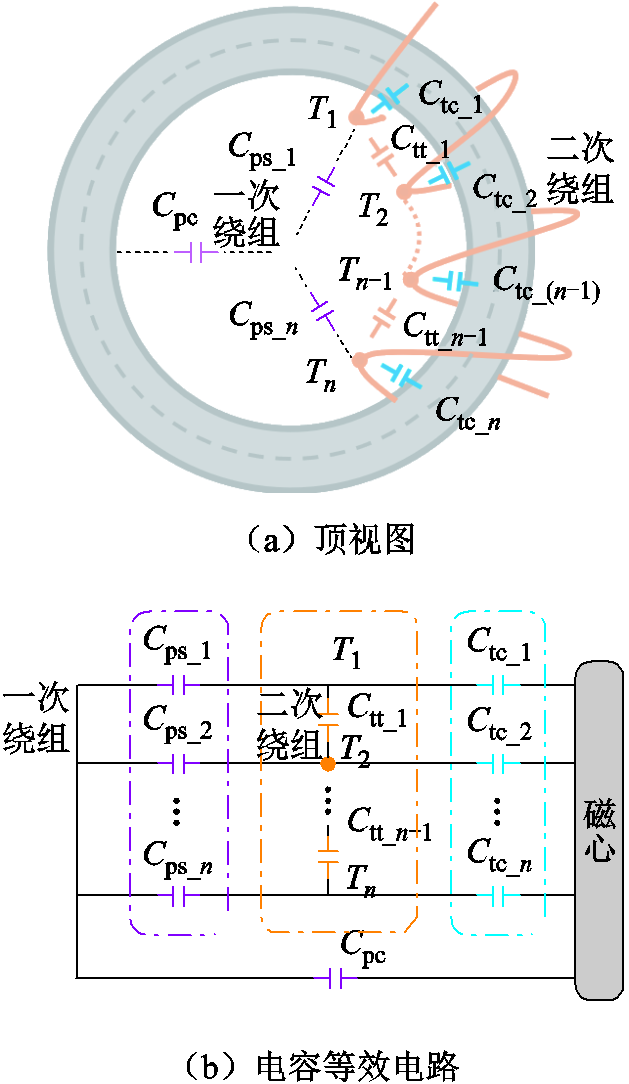

二次绕组匝数为n时,带分布电容的HCT型隔离取能结构示意图如图3所示。

图3 带分布电容的HCT型隔离取能结构示意图

Fig.3 Circuit configuration of HCT isolated power transfer

图3a为顶视图,对于HCT型结构来说,耦合电容Ciso主要由匝心电容Cpc、Ctc和匝间电容Cps、Ctt组成。匝心电容Cpc为一次绕组同磁心形成的电容,在文中用浅紫色表示;匝心电容Ctc为二次绕组同磁心形成的电容,在图中用蓝色表示;匝间电容Cps为一次绕组同二次绕组形成的电容,用深紫色表示;匝间电容Ctt为二次绕组间形成的电容,用杏色表示。图3b为各分布电容的等效电路。各分布电容可以通过等效为两平行的导体板进行计算,分布电容的计算公式为

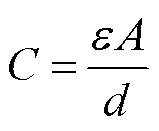

(2)

(2)

式中,ε为电介质的相对介质常数;A为导体板之间的有效面积;d为两个导体板之间的距离。

由于HCT型隔离取能结构参数多,难以通过理论建模实现Ciso的精准规律表征。因此,本文借助有限元分析来准确地探究不同结构参量对Ciso的影响规律,进而提出优化方法和最佳结构参量取值。在实际应用中,一次绕组的直径和穿心位置,磁心的内径、高度和厚度,二次绕组的绕制方式和匝数是影响HCT结构Ciso的主要因素。因此本文主要对这7个参量进行分析和优化。

为了阐明HCT关键结构参量对Ciso的影响规律,本节构建了HCT传能结构的三维仿真模型,从一次绕组、磁心、二次绕组三个核心部件及其对应的7个关键参量进行系统分析,具体内容如下。

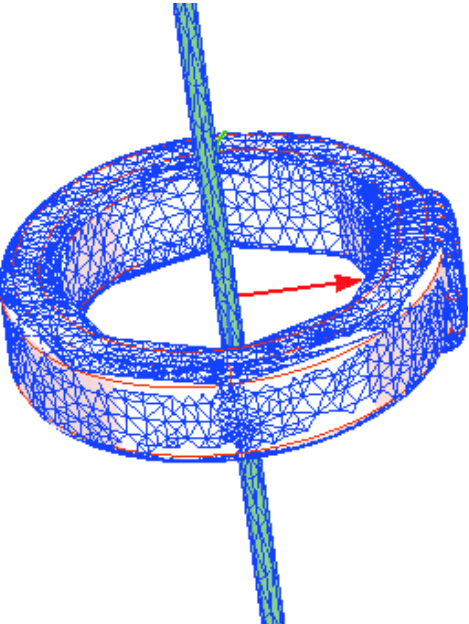

本节主要采用Ansys Q3D有限元仿真软件搭建了HCT型隔离取能结构的基准仿真模型,通过合理的网格划分和计算,能准确获取HCT型隔离取能结构一、二次侧耦合电容值,即Ciso大小。

为了更有效地对HCT型隔离取能结构进行建模和分析,本文参考了现有HCT实物装置的结构尺寸。现有设计的磁心结构常采用圆环体,最大内径约65 mm[21],最小内径为15 mm[16],厚度为5~18 mm,高度为7~15 mm,但未提供选择磁心结构的理论依据。基于此,本文结合现有设计搭建了HCT型隔离取能结构有限元模型,如图4所示。一次绕组穿过圆环磁心结构中心位置,二次绕组具有单侧集中式和均匀分散式结构。仿真模型结构参量见表1。在此基准模型基础上,本文充分考虑了磁心、一次绕组、二次绕组结构参量变化对Ciso的影响,探究不同参数变化范围内Ciso的影响规律,可包含现有HCT和优化后的结构设计参量。由于高压SiC 器件在实际运行中开关频率可达到几千至几万Hz,其振荡频率将达到MHz级别,因此本文将分析频率定为1 MHz。HCT型隔离取能装置在运行过程中传输功率较小,并不会造成明显温升,温度在60℃以内[22]。在此温度范围内,空气等介质的介电常数几乎不变,因此在有限元仿真中忽略了温度带来的影响。

图4 HCT型隔离取能结构有限元模型

Fig.4 The FEM model of HCT isolated power transfer

表1 有限元模型仿真参数值

Tab.1 Simulation parameters of the FEM model

参数数值 磁心内径/mm30 高度/mm10 厚度/mm5 二次绕组匝数5 直径/mm1.2 一次绕组直径/mm2 穿心位置磁心中心

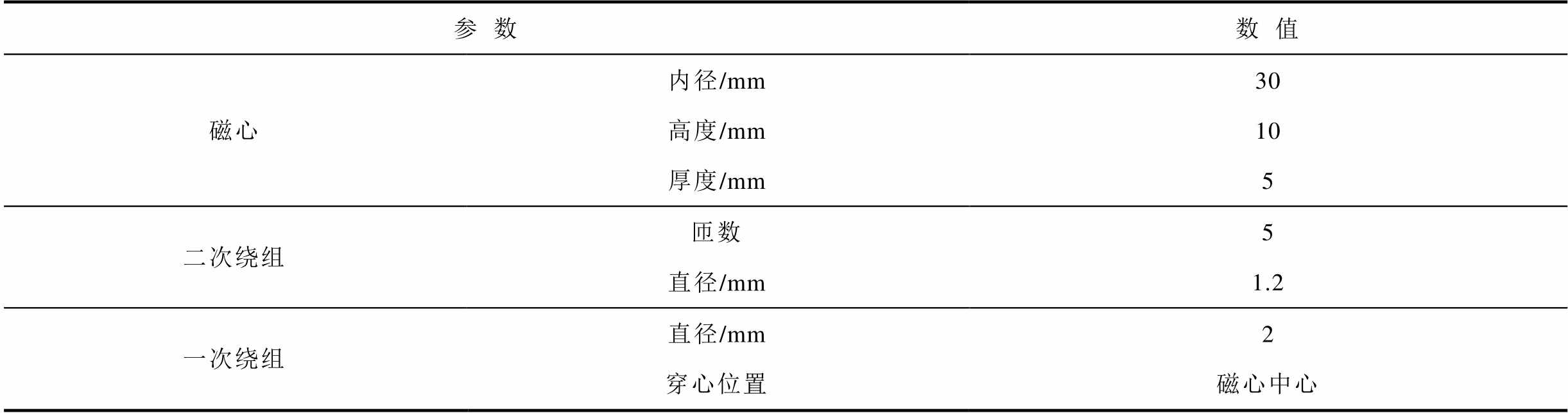

为了保证运算的效率和准确性,本文对不同的网格剖分方式进行了分析。本次有限元仿真的网络剖分设置见表2。通过对比结果发现,第5组剖分对应的网格数量在保证较准确的耦合电容计算值的同时,具有良好的运算效率。在该剖分方式上,本文进一步对比了两组现有HCT隔离取能装置耦合电容的实测值和仿真值,具体结果见表3。仿真值与实测值的误差值在0.04 pF以内,不超过4.5%。因此,本文建立的仿真模型和剖分方式具有良好的准确性和可靠性。

表2 有限元仿真网络剖分设置

Tab.2 Network segmentation setup of FEM simulation

序号网络剖分数量耦合电容Ciso/pF仿真时长/s 磁心一次绕组二次绕组总数 118 32820 07818 32859 0881.073 07152 235 82823 26436 02295 1141.107 85262 339 55924 01640 696104 2711.101 95293 451 14352 81626 714130 6731.106 48244 539 83663 14825 288128 2721.001 63448 646 74415 832131 956194 5320.991 16446 754 06211 964174 686240 7120.994 32491 8140 17222 936452 500615 6080.999 281 083

表3 不同磁心的Ciso仿真值与实测值对比

Tab.3 Comparison of simulated and measured Ciso for different cores

序号实测值/pF仿真值/pF误差(%) 10.981 90.965 81.63 21.1961.2454.09

本文首先探究了二次绕组结构参数对隔离耦合电容Ciso的影响规律,通过讨论绕制方式(集中绕制和分散绕制)对Ciso的影响规律,进而优先确定最佳二次绕组绕制方式。此外,还进一步探明了不同绕制匝数对Ciso的影响。

现有HCT取能结构二次绕组有集中绕制和分散绕制两种结构,如图5所示。不同绕制方式对耦合电容的影响见表4。结果表明,在不改变HCT取能整体结构的前提下,采用单边集中式绕组具有更低Ciso值,比分散式绕组结构降低了约18.82%。在采取分散绕制结构时,尽管二次绕组匝间距离有所增加,但分散绕制导致二次绕组单匝相对于一次绕组和磁心的相对面积Aps和Asc增大。因此,二次绕组在采取分散绕制结构时,Ciso也相应增加。本文后续仿真主要考虑集中式绕组HCT结构。

图5 二次绕组绕制方式

Fig.5 Method of winding the secondary windings

表4 不同绕制方式对耦合电容的影响

Tab.4 Impact of the secondary winding structure on Ciso

绕制方式耦合电容Ciso/pF 分散绕制1.233 集中绕制1.001

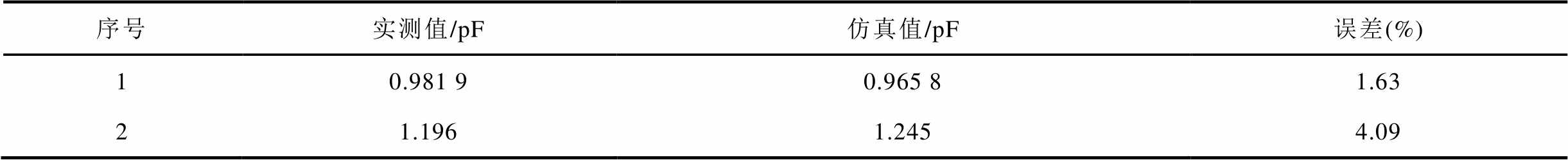

二次绕组匝数对耦合电容的影响如图6所示。结果表明二次绕组匝数的增加会显著提高Ciso,但在匝数较多(n>4)时Ciso会进入缓慢增长阶段,整体呈对数关系。以单匝匝数为二次绕组最小值,仅0.68 pF。结合分布电容等效电路分析,匝数的增加使得二次绕组与磁心之间的分布电容Csc以及二次绕组与一次绕组之间的分布电容Cps的数量增加,从而导致整体耦合电容值的升高。由于二次绕组匝数增多也能增强HCT型取能结构的耦合系数进而增强传能效率,因此本文在兼顾低Ciso和高耦合系数两个参量基础上选择4~6匝为二次绕组优化匝数。

图6 二次绕组匝数对耦合电容的影响

Fig.6 Impact of turns of the secondary winding on Ciso

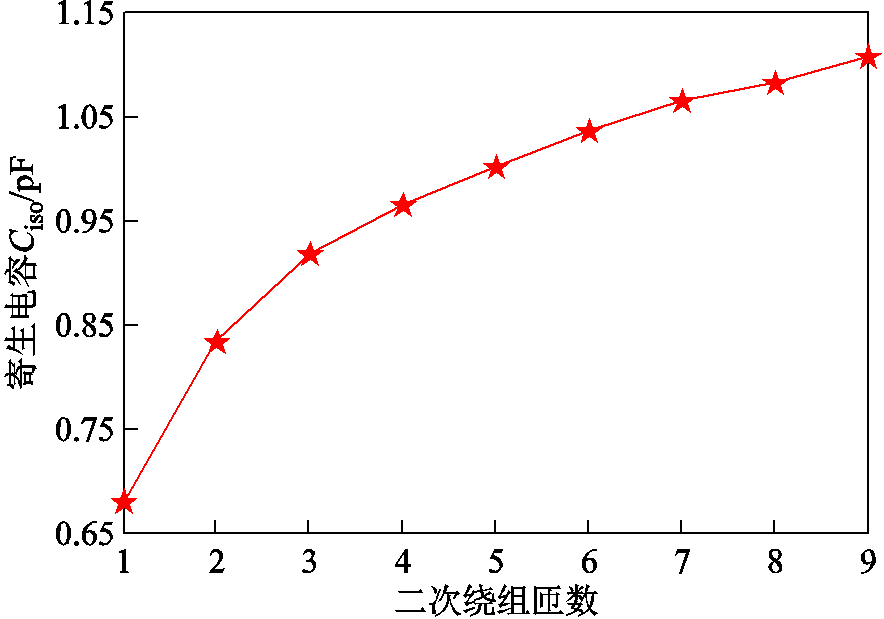

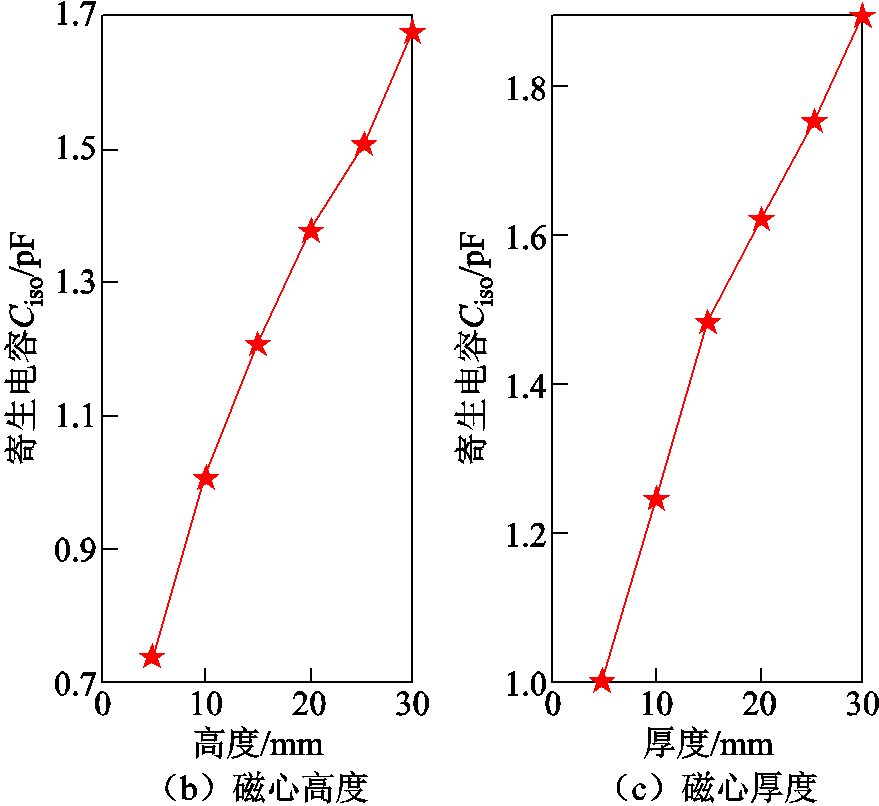

高频磁心结构是HCT取能装置的主体部分。本节分别对内径、高度和厚度这三个关键参量影响下的耦合电容Ciso变化特性展开研究。磁心结构对耦合电容的影响规律如图7所示,分别显示了在宽参量变化范围内高频磁心内径、高度、厚度与Ciso的关联关系。

图7a表明,耦合电容Ciso随着磁心内径增大而逐步下降,两者呈现出近一次线性关系。10 mm内径下Ciso约为1.152 pF,当内径增大至70 mm时,Ciso降低到仅为0.672 pF。磁心内径的增加会导致一次绕组与二次绕组匝间电容Cps的距离dps,以及一次绕组与磁心的匝心电容Cpc的距离dpc的增大,这有助于减小Cps、Cpc。图7b和图7c显示随着磁心高度hc和厚度tc的增大,Ciso会显著上升(最大值到1.894 pF)。磁心高度的增加表示二次绕组、一次绕组以及磁心的有效面积A增大,进而导致Cps及Csc的增加。而磁心厚度的增加则是提高了二次绕组同磁心的有效面积Asc,这同样导致了匝心电容Csc的增加。

图7 磁心结构对耦合电容的影响规律

Fig.7 Impact of the core structure on Ciso

图7结果表明:当HCT磁心内径大于30 mm,高度小于10 mm,厚度小于5 mm时,耦合电容Ciso能有效降低到1 pF以内。因此,通过揭示磁心结构特征参量与Ciso准确关联关系,在保证耦合电容Ciso<1 pF约束下能准确选择最小的磁心内径、高度、厚度值,进而实现装置小型化的目标。

传统一次绕组结构分析仅考虑一次绕组穿过磁心位置(穿心位置)固定在磁心圆心中点的工况。然而,对HCT磁心来说,一次绕组具有在磁心内不同位置移动的自由度。该自由度不会对HCT整体结构尺寸和一二次耦合度产生影响,但能用来降低Ciso。本节首先分析了一次绕组直径对耦合电容Ciso的影响,然后重点探究一次绕组在不同穿心位置处Ciso的分布特性,并找到最佳穿心位置,进而实现Ciso最小化。

一次绕组内径对耦合电容的影响如图8所示,表明了一次绕组内径与Ciso的关联规律。Ciso随着一次绕组内径增大而增大。当一次绕组直径大于2 mm时,Ciso会高于1.000 pF,0.5 mm内径的一次绕组对应的耦合电容仅0.748 pF。一次绕组直径的增加可提高一次绕组对二次绕组、一次绕组对磁心的有效面积Aps、Apc,从而导致匝心绕组Cpc及匝间绕组Cps的增加。通过选取内径小的一次绕组能够有效抑制耦合电容,但内径过小会导致传输电流和耦合系数过小不利于功率传输,因此本文将一次绕组内径范围定为1.5~2.0 mm。

图8 一次绕组内径对耦合电容的影响

Fig.8 Impact of the diameter of the primary winding on Ciso

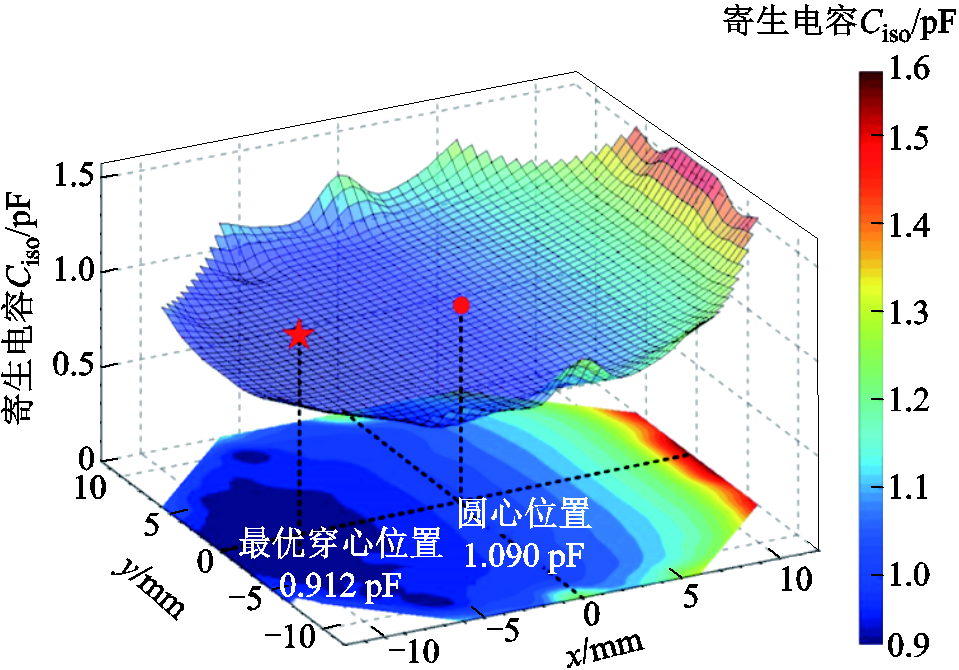

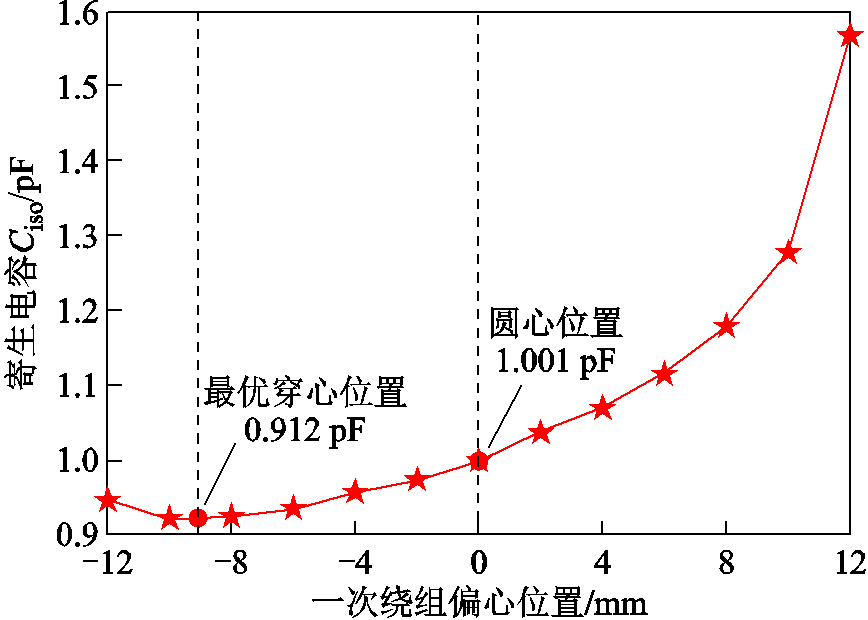

图9为一次绕组在磁心内部不同穿心位置的Ciso空间三维分布和二维投影图。其中,x轴代表二次绕组所处的横向轴线,y轴代表通过磁心中心点的纵向轴线,z轴为Ciso大小。中心点(0, 0, 0)为磁心圆心位置。上层图代表Ciso的三维分布图,下层图为三维分布图的二维投影,色柱代表了Ciso由0.900 pF到1.600 pF的变大趋势。结果表明一次绕组不同穿心位置对应Ciso会产生显著差异,最小Ciso并不是在磁心中心位置。Ciso由中心点往x轴负向偏移会先降低后抬升,但是往x轴正向、y轴正向、y轴负向偏移均会逐渐上升。在x轴正向10 mm贴近二次绕组处,Ciso出现最大值1.568 pF。因此,通过探究最小Ciso位置,可以在不改变CT磁心整体结构的基础上,有效抑制Ciso。

图9 不同一次绕线穿心位置下Ciso全局的分布特性

Fig.9 Distribution characteristics of Ciso with different positions of the primary winding

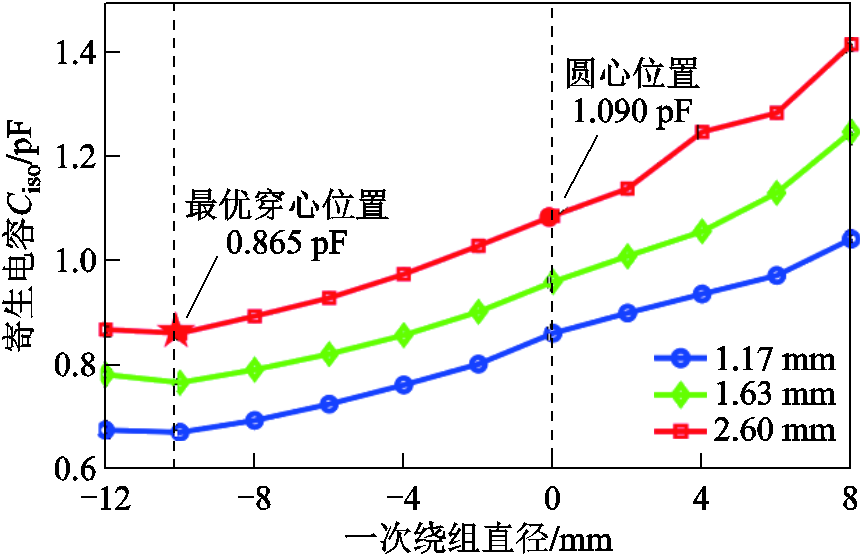

一次绕组在x轴上偏移对耦合电容的影响如图10所示。图10更清晰地显示了一次绕组穿心位置随着横向轴向偏移的Ciso变换规律。其中,纵向轴线位置恒为0 mm,横向轴线位置从最大负向偏移(-12 mm)到最大正向偏移(+12 mm)变化。Ciso在磁心中心位置约为1.001 pF,在负向位置随着x轴增大Ciso会先下降再略微升高,在-9 mm出现最小值约0.912 pF。在x轴负向较大值(-12 mm)时出现Ciso逐渐升高是因为一次绕组穿心位置非常接近一次侧磁心。一次绕组往x轴负方向的偏移导致一次绕组与二次绕组隔离距离dps的增大,进而减小了匝间电容Cps。然而,同时也使得一次绕组与磁心的距离dpc缩小,导致匝心电容Cpc增加。在偏移初期,匝间电容Cps的减小占主导因素。然而,当一次绕组靠近磁心之后,匝心电容逐渐占据主导地位,最终导致总的Ciso略微上升。仿真表明,在不改变HCT型隔离电源位型结构的前提下,仅改变一次绕组的偏心位置便可实现Ciso的抑制效果,最小值相比于圆心处的Ciso减小了8.9%。

图10 一次绕组在x轴上偏移对耦合电容的影响

Fig.10 Impact of the eccentric position of the primary winding on the x-axis on Ciso

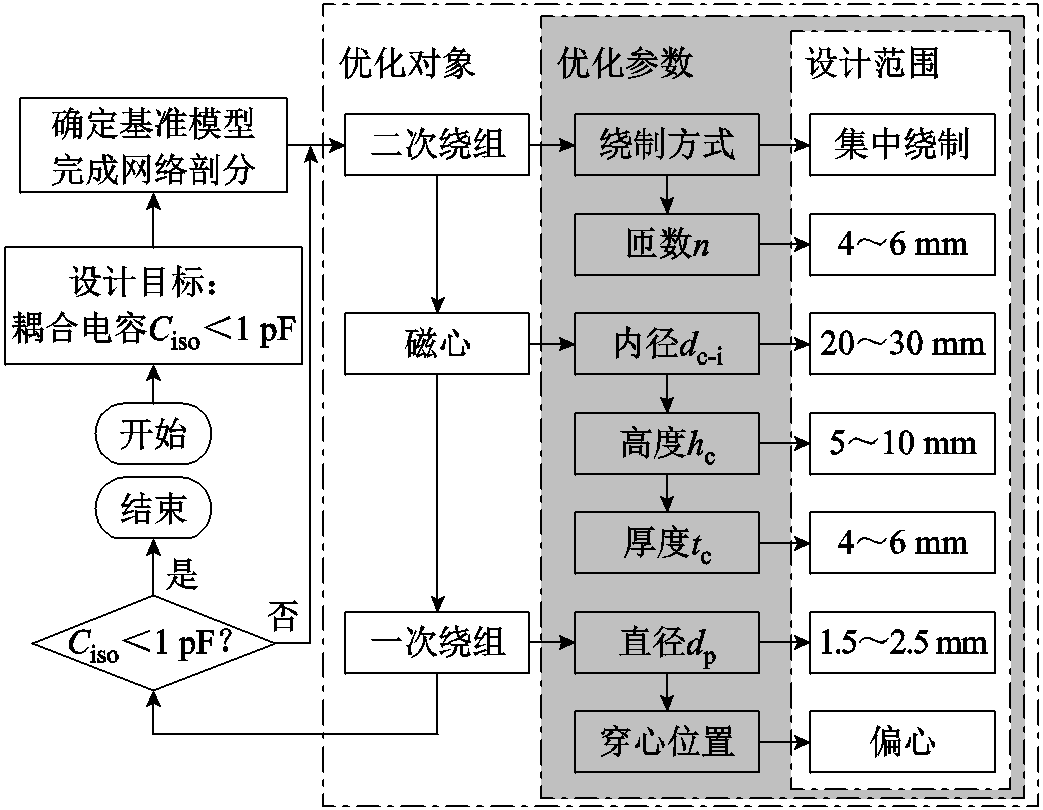

前文已深入探讨了HCT型隔离取能结构中关键结构参数对耦合电容Ciso的影响规律。在最终设计确定HCT型隔离取能装置的关键设计参数时,需权衡Ciso、装置体积及传输能力多个考虑因素,目标是在不增大磁心结构尺寸的前提下,实现耦合电容的最优抑制效果。基于此,本文提出了HCT型隔离取能装置Ciso优化设计方法,流程如图11所示。

首先确定了优化设计目标,本文以HCT型隔离取能装置Ciso降低至1 pF以下为例。然后确定HCT型结构有限元基准模型,并完成合适的网络剖分。接着针对HCT型取能结构的二次绕组、磁心、一次绕组三个对象核心参量分别进行优化。根据前文阐明的关键结构参量对Ciso的关联特性确定绕制方式和参量范围,如图11中所示为设定1 pF目标下推荐的设计参量值。若最终设计通过仿真验证Ciso<1 pF,则完成本次优化设计;反之,继续进行设计参量的选定。

图11 耦合电容优化设计方法流程

Fig.11 Optimized design scheme of Ciso for the HCT isolated power transfer

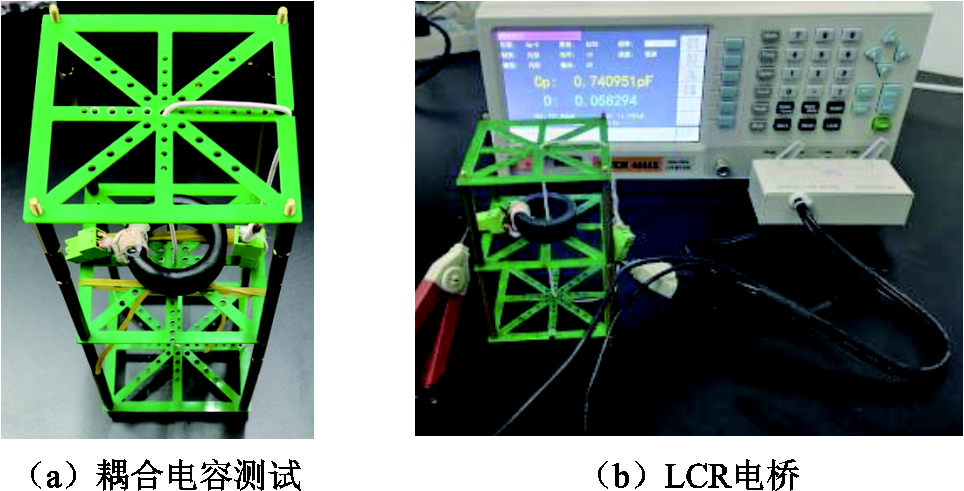

为了验证HCT取能结构关键参量与耦合电容Ciso影响关联规律的准确性,本文搭建了如图12所示的耦合电容测试平台。在测试平台中,NiZn铁氧体因其具有良好的高频特性作为HCT隔离取能的磁心材料,一次和二次绕组采用利兹线以减小绕组的高频趋肤效应。本平台设计了一个米字型框架以实现一次绕组在磁心的不同穿心位置控制。耦合电容是隔离取能装置固有的参量,主要由装置结构和材料属性决定,高压电场和高dv/dt作用并不会改变取能结构和材料属性,因此对耦合电容的影响非常小,通过测量静态参数是现在常用准确表征隔离取能装置耦合电容的手段[10-11]。因此本文采用胜利仪器公司的4092E LCR电桥系列作为测量工具,可实现1 Hz~1 MHz的宽频测量。本测试平台能对不同尺寸的磁心、绕组结构、穿心位置下的耦合电容Ciso进行准确测量。

图12 耦合电容测试平台

Fig.12 Coupling capacitance test platform

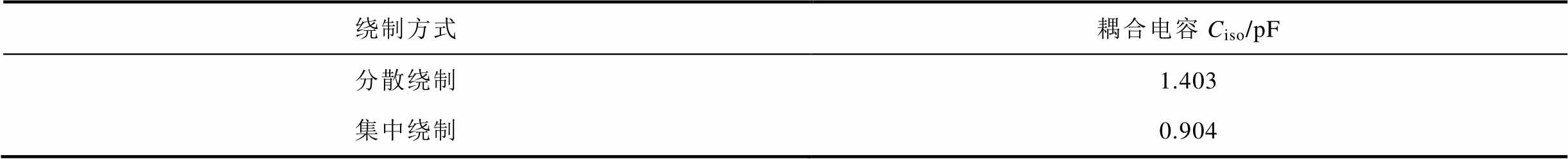

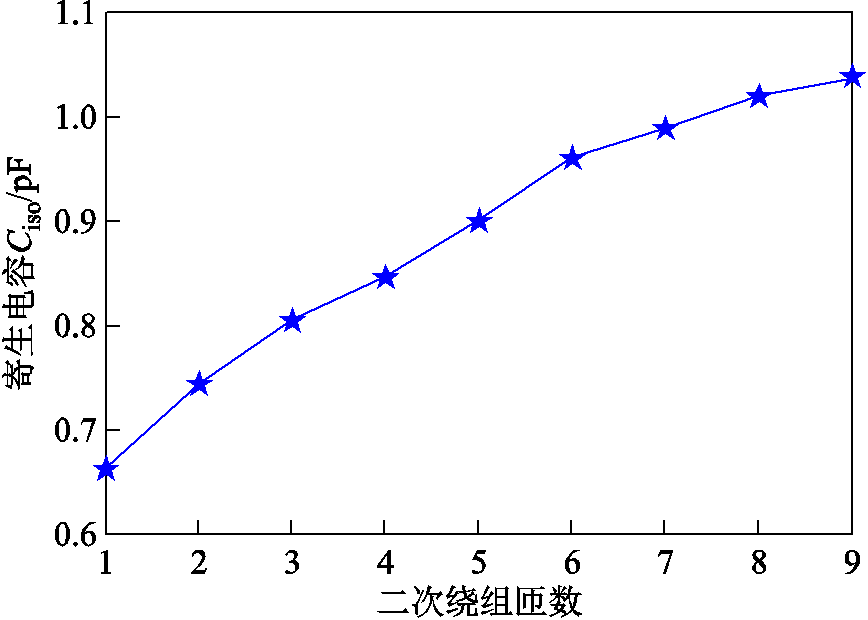

本节首先实验探究了二次绕组绕制方式和绕组匝数对耦合电容Ciso的影响规律。不同绕制方式的耦合电容见表5。表5表明分散绕制方法下耦合电容值约1.40 pF,集中绕制显著减小了Ciso值,仅为0.86 pF,两者的数值大小和变化规律与仿真较为一致。二次绕组匝数对耦合电容的影响如图13所示,表明了二次绕组1~9匝对应Ciso的变化规律。结果表明,Ciso从0.65 pF逐渐增大到1.04 pF,并呈现增长率先快后慢的趋势,数值与变化趋势同样与仿真较为吻合。

表5 不同绕制方式的耦合电容

Tab.5 Test results of secondary winding structures on Ciso

绕制方式耦合电容Ciso/pF 分散绕制1.403 集中绕制0.904

图13 二次绕组匝数对耦合电容的影响

Fig.13 Test results of turns of secondary winding on Ciso

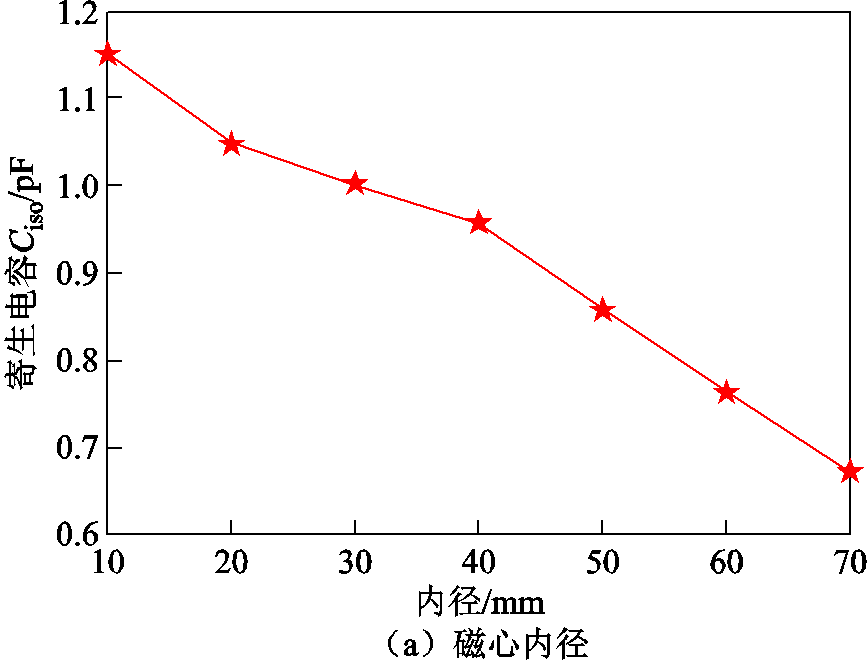

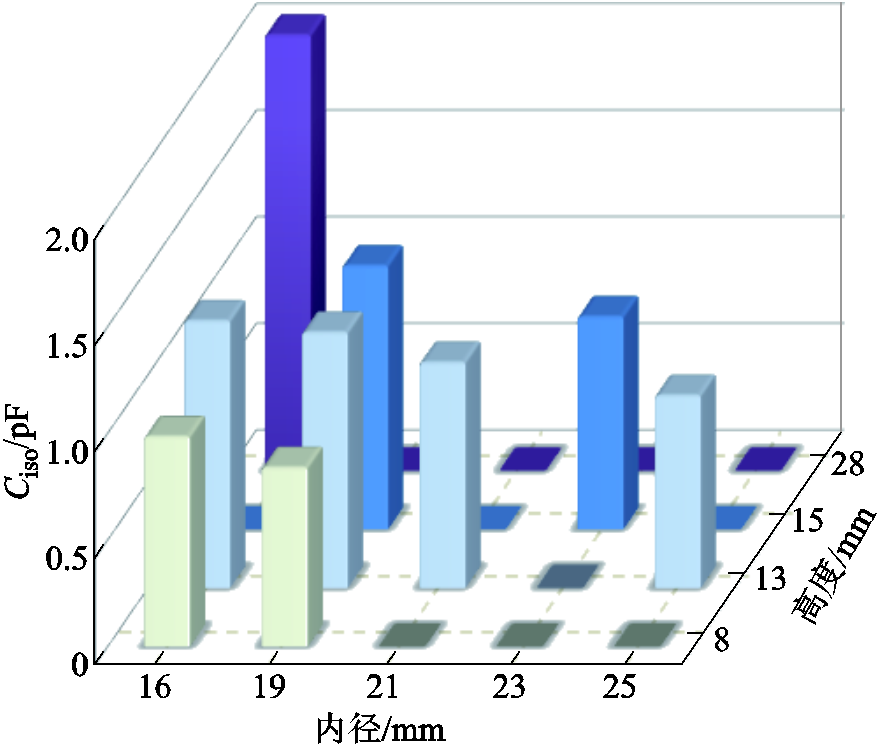

为验证磁心结构参数对耦合电容的影响特性,本文选取了九款同材料不同尺寸的NiZn铁氧体磁环,并测量了对应不同尺寸HCT隔离取能装置的耦合电容,测试结果如图14所示。本文选取的磁心厚度皆为6 mm,内径从16~25 mm变化,高度从8~28 mm变化。其中,16 mm和19 mm内径下各有三种不同高度的磁心。结果显示,随着磁心高度的增加,Ciso呈现出增加的趋势,实验结果与仿真结果相一致。当磁心内径为16 mm、高度为28 mm时,Ciso高达2.040 pF。对应相同厚度和相同高度(13mm)下不同内径的磁心,实验结果表明随着磁性内径的增大,Ciso逐渐减小,变化趋势与实验较为吻合,当磁心内径为25 mm,高度为13 mm时,Ciso仅为0.904 pF。

图14 不同磁心尺寸的耦合电容

Fig.14 Measured Ciso of different core sizes

一次绕组穿心位置和线径对耦合电容Ciso的影响如图15所示。测试中穿心位置以磁心中心点为原点,横坐标代表了与二次绕组中点相连的轴线,即仿真图10中的x轴。

图15 一次绕组耦合位置和直径对耦合电容的影响

Fig.15 Impact of the primary winding position and diameter on Ciso

实验结果同样显示磁心中点位置Ciso为1.09 pF(以2.6 mm线径为例),并不是Ciso最小处。Ciso随着横坐标负向方向先降低后略微增大,最小值出现在-10 mm处左右,仅为0.865 pF,比中点处位置降低了约20.6%。该实验结果与仿真非常吻合,验证了仿真规律的准确性。此外,随着线径的降低,Ciso会出现整体曲线下降的趋势,但随横坐标变化规律三者一致。因此,实验结果同样证明,改变一次绕组穿心至负向偏移磁心中点值最佳位置,便可有效降低Ciso。

综上所述,二次绕组、磁心和一次绕组关键结构参量的实验测试结果同仿真结果相符,验证了所揭示特征规律的有效性,为HCT型隔离电源耦合电容的优化奠定了理论基础。

本节基于有限元仿真和实验验证结果确定了优化设计的HCT隔离取能结构参数。其中,磁心结构尺寸内径为25 mm、高度为13 mm、厚度为6 mm,二次绕组采用集中式绕组方式,直径为1.16 mm的利兹线,匝数为5匝,一次绕组直径为1.63 mm的利兹线,磁心原点偏心位置-10 mm。

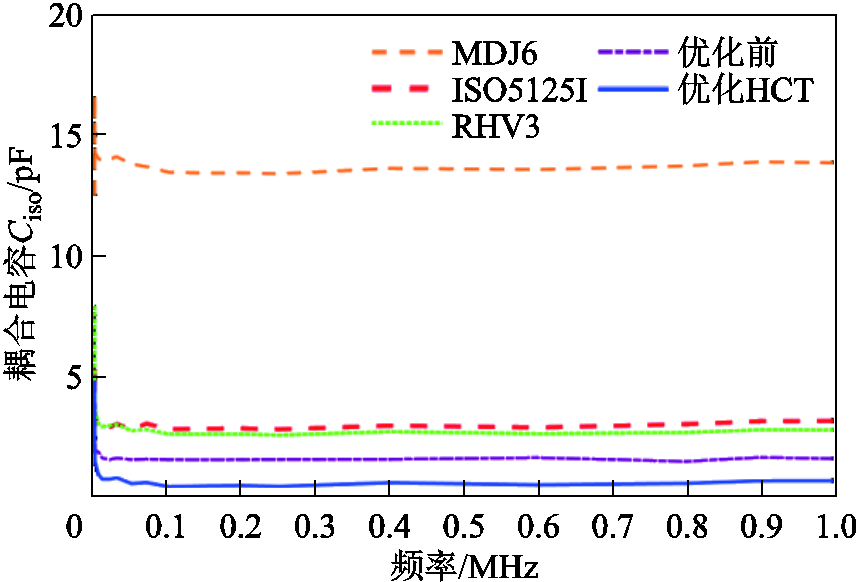

为了验证优化设计后HCT取能装置的隔离耦合电容Ciso的性能,本节首先与现有同类商业高压隔离电源进行对比分析。同类产品具有10~15 kV隔离电压能力,分别为日本Murata的MDJ6、美国Power Integrations的ISO5125I、德国Recom的RHV3。测试频率为1 Hz~1 MHz。不同商业隔离电源和所研装置Ciso对比如图16所示。由图16可知,MDJ6款隔离电源在现有同类商业产品中具有最高的Ciso,约为13.5 pF,RHV3系列具有最小的Ciso,约为2.74 pF。本文优化设计后的HCT取能装置Ciso仅为0.74 pF,相较于前两者分别减低了约94.5%和73%,相较于优化前HCT隔离取能结构1.65 pF的耦合电容值,降低了约55%。

图16 不同商业隔离电源和所研装置Ciso对比

Fig.16 Comparison of Ciso between different commercial isolation power supplies and the developed device

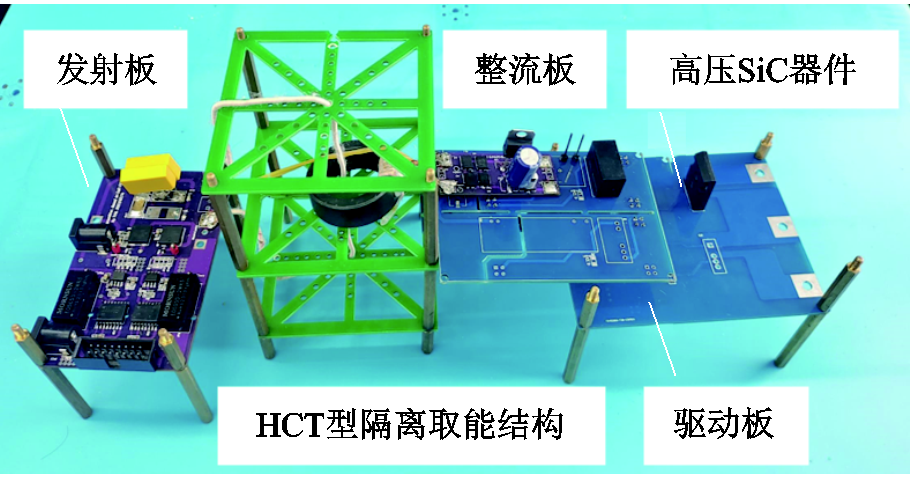

此外,本文进一步研制了基于优化设计HCT隔离取能装置及SiC器件驱动工作测试平台,如图17所示。该平台用于测试HCT隔离取能装置对SiC器件驱动的供能能力和工作状态。测试平台包括基于GaN器件的高频交流一次发射板,优化设计的HCT型隔离取能结构,整流电路,高压SiC器件驱动板和3.3 kV SiC器件(MSC400SMA330B4)。其中,HCT型取能传输频率为1 MHz,SiC器件测试开关频率为5 kHz和50 kHz,驱动板工作功率约2.5 W。

图17 优化设计的HCT隔离取能装置

Fig.17 HCT-based power transfer device with the optimized design method

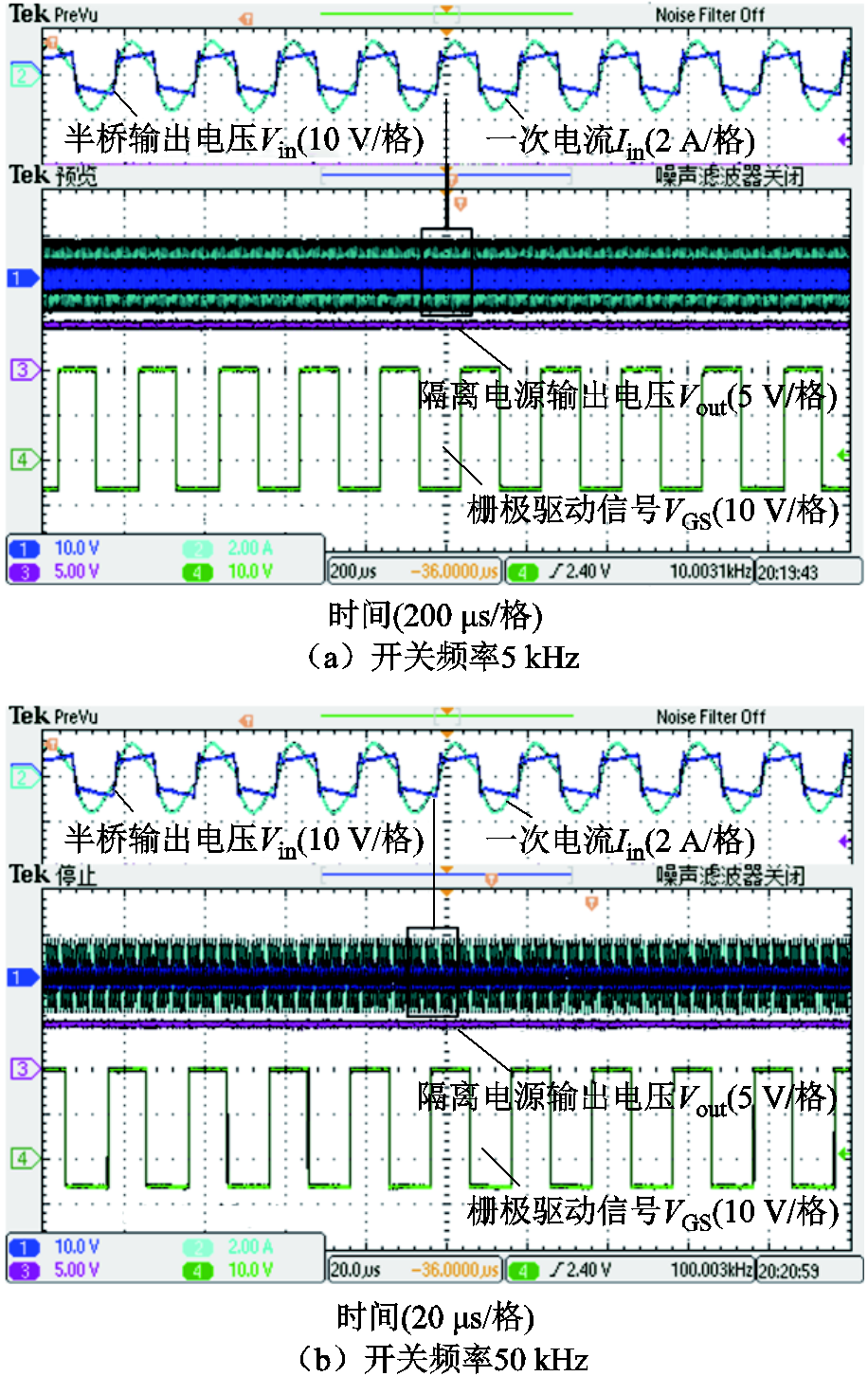

基于HCT型隔离取能装置的高压SiC驱动系统实验波形如图18所示。从上到下依次为一次电压源Vin、一次电流Iin、二次侧整流后直流输出电压Vout、高压SiC器件驱动信号VGS。如图18所示,在5 kHz和50 kHz 工况下,一次侧能产生稳定可控的1 MHz 高频交流电流,优化的HCT装置能稳定地给负载端驱动电路供能,并产生稳定的5 V输出电压;驱动电路产生了高压SiC器件工作所需的-6 V和+20 V的关断和开通电压,上升和下降沿没有出现过冲现象。该结果显示优化设计后的HCT隔离取能装置能给SiC器件驱动电路所需的功率稳定传能,实现了SiC器件的准确关断和开通控制。

图18 基于HCT隔离取能装置的SiC驱动实验波形

Fig.18 Experimental results of the HCT-based SiC gate driver

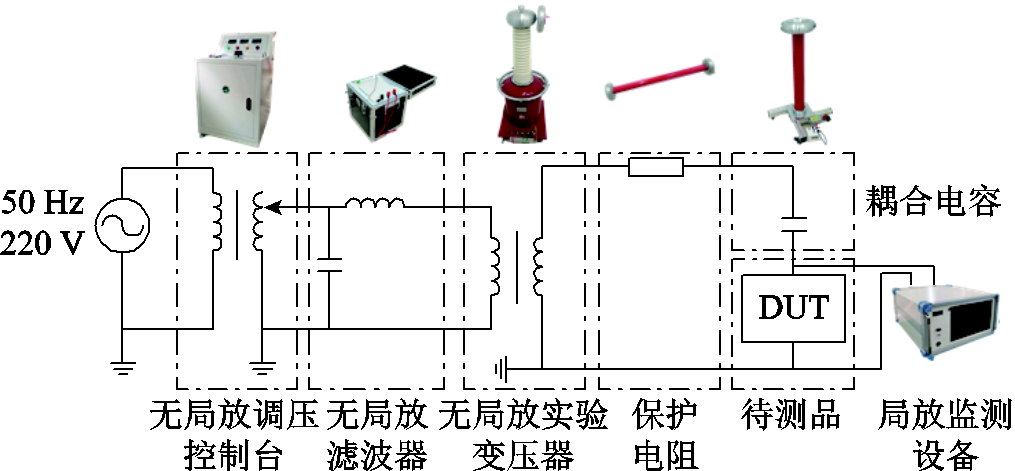

本文采用局部放电实验平台对HCT型隔离取能装置的局部放电特性进行了研究,确定了所研装置的最大耐受电压。该实验平台能产生最高50 kV(RMS值)的工频测试电压,如图19所示。本文以无局部放电电压最大值来衡量HCT取能装置隔离耐压能力。在保持低耦合电容和对耦合电容特征规律不产生显著影响的基础上,本文对HCT装置隔离性能做了一定的优化。在一次绕组外层添加了薄硅胶层作为绝缘护套,绝缘层厚度约为2 mm;在磁心外层包裹了一层绝缘纸来实现二次绕组和磁心的隔离。绝缘优化后,耦合电容由原来的0.74 pF增加到0.82 pF。因此,增加的绝缘层对耦合电容的影响很小,同时并不会影响传输性能。

图19 局部放电实验平台

Fig.19 Partial discharge experimental platform

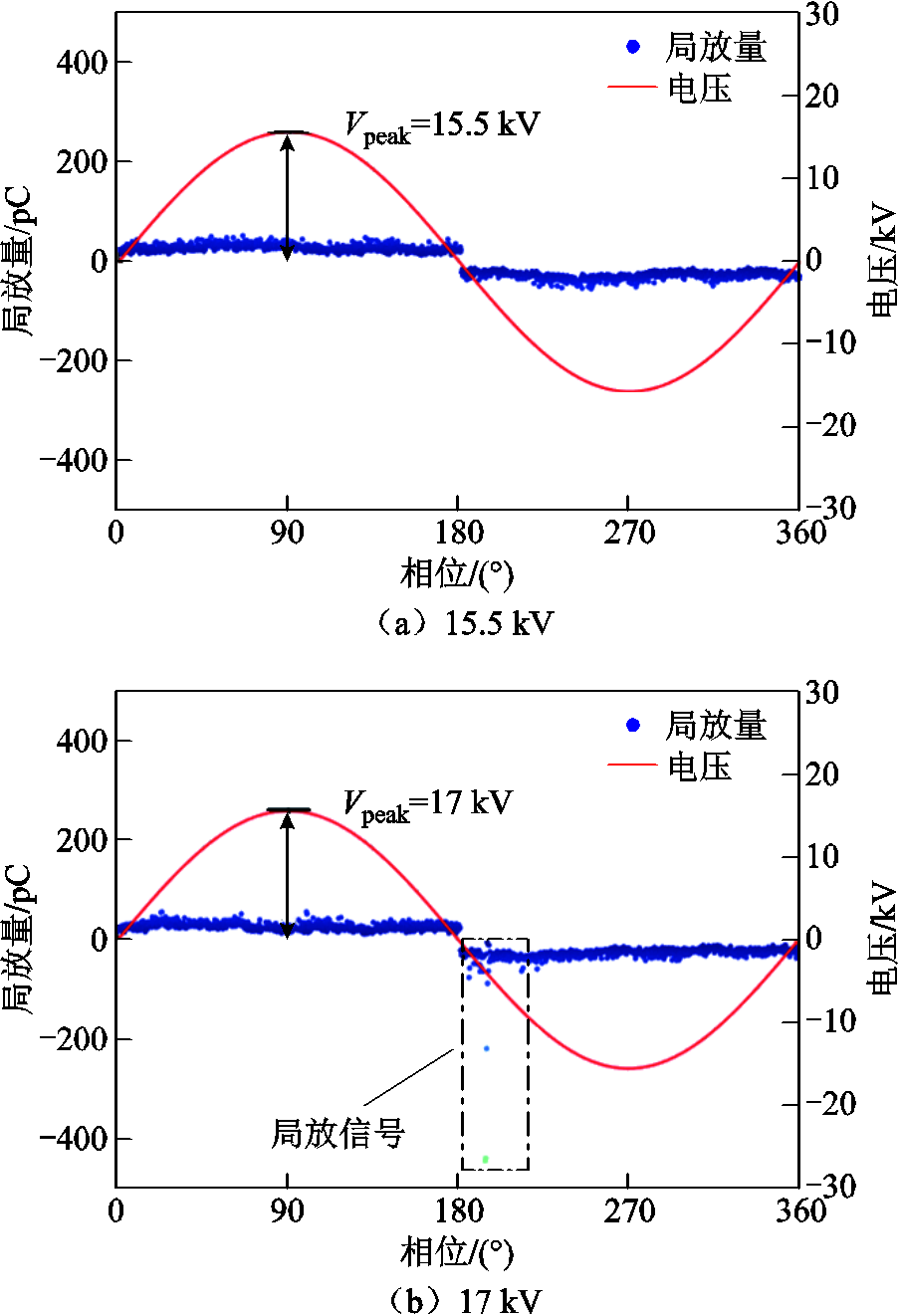

HCT隔离取能装置局部放电测试结果如图20所示。其中左侧纵轴为待测对象的局部放电量,右侧纵轴为施加电压值。图20a表明在所研装置两端施加15.5 kV(峰值)时未出现局部放电现象。然而,当电压升至17 kV(峰值)时,监测到了明显的局部放电信号,如图20b所示。本次优化后的HCT隔离取能装置不仅能实现极低的耦合电容,也能实现很高的隔离耐压,对比现有空气介质下HCT隔离取能装置电压等级提升55%。

图20 HCT隔离取能装置局部放电测试结果

Fig.20 Results of partial discharge test for the HCT-based power transfer device

本文主要对高压SiC器件HCT型隔离取能结构的耦合电容特性和抑制方法进行了研究,对二次绕组、磁心、一次绕组7个关键结构参量进行分析,提出HCT型隔离电源低耦合电容的优化设计方法,搭建了HCT型耦合电容测量平台和高压HCT型驱动装置样机进行实验验证。结果清晰阐明了HCT型取能关键结构参量与隔离电容的关联关系,通过调整一次绕组穿心位置和集中式二次绕组可有效降低耦合电容。优化设计的HCT型隔离取能装置耦合电容降低到0.74 pF,比传统设计和同类商业产品分别减小55%和70%,同时,最大无局部放电电压达到15.5 kV,实现高隔离能力。本文的研究能有效降低SiC器件取能电源的隔离电容,从而提升抗dv/dt能力,给新一代高压SiC器件应用的隔离驱动供能提供新思路。

参考文献

[1] 盛况, 董泽政, 吴新科. 碳化硅功率器件封装关键技术综述及展望[J]. 中国电机工程学报, 2019, 39(19): 5576-5584.

Sheng Kuang, Dong Zezheng, Wu Xinke. Review and prospect of key packaging technologies for silicon carbide power devices[J]. Proceedings of the CSEE, 2019, 39(19): 5576-5584.

[2] DiMarino C M, Mouawad B, Johnson C M, et al. 10-kV SiC MOSFET power module with reduced common-mode noise and electric field[J]. IEEE Transactions on Power Electronics, 2020, 35(6): 6050-6060.

[3] 高范强, 李子欣, 李耀华, 等. 面向交直流混合配电应用的10kV-3MV·A四端口电力电子变压器[J]. 电工技术学报, 2021, 36(16): 3331-3341.

Gao Fanqiang, Li Zixin, Li Yaohua, et al. 10kV-3MV·A four-port power electronic transformer for AC-DC hybrid power distribution applications[J]. Transactions of China Electrotechnical Society, 2021, 36(16): 3331-3341.

[4] 王来利, 赵成, 张彤宇, 等. 碳化硅功率模块封装技术综述[J]. 电工技术学报, 2023, 38(18): 4947-4962.

Wang Laili, Zhao Cheng, Zhang Tongyu, et al. Review of packaging technology for silicon carbide power modules[J]. Transactions of China Electrotechnical Society, 2023, 38(18): 4947-4962.

[5] Huang A Q. Power semiconductor devices for smart grid and renewable energy systems[J]. Proceedings of the IEEE, 2017, 105(11): 2019-2047.

[6] Anurag A, Acharya S, Bhattacharya S, et al. A gen-3 10-kV SiC MOSFET-based medium-voltage three-phase dual active bridge converter enabling a mobile utility support equipment solid state transformer[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2022, 10(2): 1519-1536.

[7] Ji Shiqi, Zhang Li, Huang Xingxuan, et al. A novel voltage balancing control with dv/dt reduction for 10-kV SiC MOSFET-Based medium voltage modular multilevel converter[J]. IEEE Transactions on Power Electronics, 2020, 35(11): 12533-12543.

[8] Zhang Xuan, Li He, Brothers J A, et al. A gate drive with power over fiber-based isolated power supply and comprehensive protection functions for 15-kV SiC MOSFET[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2016, 4(3): 946-955.

[9] Nguyen V T, Pawaskar V U, Gohil G. Isolated gate driver for medium-voltage SiC power devices using high-frequency wireless power transfer for a small coupling capacitance[J]. IEEE Transactions on Industrial Electronics, 2021, 68(11): 10992-11001.

[10] Spro O C, Lefranc P, Park S, et al. Optimized design of multi-MHz frequency isolated auxiliary power supply for gate drivers in medium-voltage converters[J]. IEEE Transactions on Power Electronics, 2020, 35(9): 9494-9509.

[11] Sun Keyao, Xu Yue, Wang Jun, et al. Insulation design of wireless auxiliary power supply for medium voltage converters[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2021, 9(4): 4200-4211.

[12] Teng Fei, Feng Hao, Lukic S. Gate driver power supply with air-gapped transformer for medium voltage converters[C]//2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 2022: 451-456.

[13] Kadavelugu A, Bhattacharya S. Design considerations and development of gate driver for 15 kV SiC IGBT[C]//2014 IEEE Applied Power Electronics Conference and Exposition - APEC, Fort Worth, TX, USA, 2014: 1494-1501.

[14] Dalal D N, Christensen N, Jørgensen A B, et al. Gate driver with high common mode rejection and self turn-on mitigation for a 10 kV SiC MOSFET enabled MV converter[C]//2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), Warsaw, Poland, 2017: 1-10.

[15] 邢家维, 金能, 林湘宁, 等. 基于小波包变换的电流互感器饱和识别及有效数据运用策略[J]. 电工技术学报, 2019, 34(6): 1170-1179.

Xing Jiawei, Jin Neng, Lin Xiangning, et al. A novel strategy of current transformer saturation identification and valid data application based on wavelet packet[J]. Transactions of China Electrotechnical Society, 2019, 34(6): 1170-1179.

[16] 王祎凡, 任春光, 张佰富, 等. 基于电压源型PWM整流电路的输电线路测量与感应取电一体化互感器实现方法[J]. 电工技术学报, 2023, 38(1): 13-25.

Wang Yifan, Ren Chunguang, Zhang Baifu, et al. Implementation method of integrated transformer for transmission line measurement and inductive power taking based on voltage source PWM rectifier[J]. Transactions of China Electrotechnical Society, 2023, 38(1): 13-25.

[17] Gottschlich J, Schäfer M, Neubert M, et al. A galvanically isolated gate driver with low coupling capacitance for medium voltage SiC MOSFETs[C]// 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), Karlsruhe, Germany, 2016: 1-8.

[18] Hu Jiewen, Wang Jun, Burgos R, et al. High-density current-transformer-based gate-drive power supply with reinforced isolation for 10-kV SiC MOSFET modules[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(3): 2217-2226.

[19] Sen S, Zhang Liqi, Feng Xianyong, et al. High isolation auxiliary power supply for medium-voltage power electronics building block[C]//2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 2020: 2249-2253.

[20] Anurag A, Acharya S, Kolli N, et al. Gate drivers for medium-voltage SiC devices[J]. IEEE Journal of Emerging and Selected Topics in Industrial Electronics, 2021, 2(1): 1-12.

[21] Peftitsis D, Antivachis M, Biela J. Auxiliary power supply for medium-voltage modular multilevel converters[C]//2015 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Europe), Geneva, Switzerland, 2015: 1-11.

[22] Yan Ning, Dong Dong, Burgos R. A multichannel high-frequency current link based isolated auxiliary power supply for medium-voltage applications[J]. IEEE Transactions on Power Electronics, 2022, 37(1): 674-686.

Abstract High-voltage silicon carbide (SiC) switches are developing rapidly and draw increasing attention. The new generation of power conversion system based on high-voltage SiC switches has advantages of smaller number of devices, higher efficiency, smaller size, etc. Thus, high-voltage SiC devices have been gradually applied to medium-voltage motor drives, solid-state transformers, grid-connected inverters and other fields. However, the isolated power supplies for the driver circuit of SiC switches are facing high dv/dt challenges, which can easily cause strong common-mode interference and device failure.

High-frequency current transformer (HCT) is a novel method of isolated power transfer for high-voltage SiC devices. However, characteristics between its coupling capacitance and structural parameters are still unclear, complicating the improvement of dv/dt performance and the pursuit of miniaturization.

A 3D simulation model of HCT-type isolated power transfer structure is firstly constructed, and the structural parameters are extracted through finite element simulation to systematically study the influence of structural parameters (isolation distance, eccentric position, winding mode, number of turns, etc.) on the coupling capacitance. On this basis, an optimization method of the coupling capacitance of the HCT-type device under the influence of multiple parameters is proposed to achieve the minimum coupling capacitance. Finally, the effectiveness of the proposed method and the developed device is verified by experiments.

The results show that the coupling capacitance can be reduced by approximately 20% simply by adjusting the location of the penetration center of the HCT-type device. The coupling capacitance of the developed isolated power transfer device is only 0.74 pF, which is 55% and 70% lower than the conventional design and similar products, respectively. In addition, a high-voltage test platform is established, and the maximum voltage without any partial discharge of the developed device, up to 15.5 kV, is obtained through experimental tests. Finally, a prototype of the isolated power supply is built based on the proposed design, and the device was verified by experiments. Result showed that it could provide a stable energy supply to the 3.3 kV SiC devices at different frequencies. The research in this paper provides a new path of the isolated power for high-voltage SiC devices with high isolation, high interference immunity, and high compactness.

Keywords:High-voltage SiC switch, isolated power supply, low coupling capacitance, current transformer

中图分类号:TM452

DOI: 10.19595/j.cnki.1000-6753.tces.240021

国家高层次青年人才项目(HW2021005)和重庆市自然科学基金面上项目(cstc2021jcyj-msxmX0871)资助。

收稿日期 2024-01-04

改稿日期 2024-02-29

潘建宇 男,1989年生,博士,教授,研究方向为中高压变换器控制、SiC电驱动和高电压放电防护技术。

E-mail:panjianyu@cqu.edu.cn(通信作者)

唐海博 男,1998年生,硕士研究生,研究方向为碳化硅器件应用。

E-mail:tanghaibo@cqu.edu.cn

(编辑 赫 蕾)