图1 基于半桥拓扑的双脉冲测试电路

Fig.1 Double pulse test circuit based on half-bridge topology

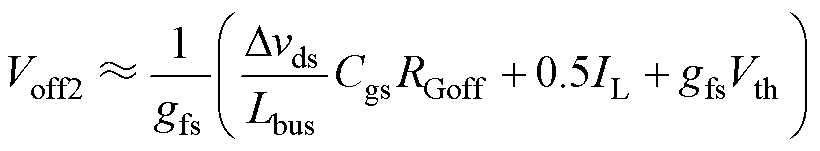

摘要 SiC MOSFET具有低导通电阻、低开关损耗、高开关频率以及优异的反向恢复特性。器件过快的开关速度,会导致严重的开关过冲、振荡和串扰。此外其短路承受能力弱,需要保护电路具备更快的响应速度,但较高的开关变化率,又使得保护电路的快速响应与抗噪声能力难以兼顾。为确保其安全可靠工作,该文提出基于多段式电平调控的驱动与保护方法。驱动方法解决开关过程多个目标的协同优化问题,在获得较快的开关速度和低损耗的同时,有效地抑制过冲和振荡;保护方法提出了增加补偿回路的导通压降检测电路,降低了温度和负载变化对检测精度的影响,同时提出了两段式降低栅压的关断方法,增大故障检测盲区时间以降低干扰噪声影响,并采用软关断技术,抑制关断过电压。

关键词:SiC MOSFET 多电平驱动 开关轨迹 短路保护 软关断

碳化硅金属-氧化物半导体场效应晶体管(SiC MOSFET)具有低导通电阻、低开关损耗、高开关频率、高耐压值以及优异的温度特性。SiC MOSFET开通时,其体二极管具有出色的反向恢复特性,反向恢复电流低;关断时,不会产生拖尾电流。这些优异的特性,使得SiC MOSFET在高温、高压、高频等应用环境中具有广阔的发展前景,使得整个电力电子装置的转换效率、功率密度及稳定性大幅 提升。

SiC MOSFET在高频开关过程中,过高电压电流变化率,会导致严重的开关应力过冲、振荡和串扰[1-2]。在短路工况下,与Si器件相比,SiC MOSFET芯片面积小,电流密度更高,导致其短路承受能力较弱;SiC MOSFET需要更高的栅极电压,栅极电压的增高会加剧栅极氧化层退化问题[3-5]。这些副作用限制了SiC型装置电压等级和功率密度的进一步提升。为确保SiC MOSFET在较高的开关速度下安全运行,要求驱动电路能够调控SiC器件的开关轨迹,保护电路能够快速识别短路故障并安全关断。

国内外学者对SiC MOSFET驱动方式、过电流检测和短路关断等方面展开多项研究。针对高频开关调控方面,为了抑制应力过冲和振荡,最直接的方法是增加栅极电阻,但是单纯的增加栅极电阻,会增加开关延时和损耗。文献[6-7]提出通过变栅极电阻来调节器件开关过程,结构简单、控制容易。文献[8-9]提出通过变栅极电压调节开关轨迹,但是电平数量有限,隔离电源和驱动电路设计复杂,无法适应多种工况的控制需求。文献[10-11]提出通过调节栅极驱动电流或增加辅助电流来抑制过冲和振荡,电流控制电路的结构复杂、成本高,同时也增加了开关损耗。

针对大功率SiC器件短路检测和保护方面问题,目前成熟的短路检测技术主要基于饱和压降的退饱和检测和基于电流变化率的di/dt检测[4]。退饱和检测技术[12-13]直接检测器件短路时的漏源电压Vds,这种方法可能受到高dvds/dt的干扰,检测回路易受寄生参数和温度影响导致测量偏差;di/dt检测方法[14-15]利用源端的寄生电感测量漏极电流,检测速度快于退饱和保护,但是无法实现低电流变化率的保护,只适用于单管保护,应用范围受限。文献[16]提出了通过di/dt检测触发漏源电压Vds检测,利用两种检测方法同时保护器件,提升了保护检测的可靠性,同样针对低电流变化率的过电流工况,可能导致无法触发保护。文献[17]提出了利用电阻分压采集Vds电压,该电路需承受高电压,因此采集电阻值和分压比较大,不适合精确检测Vds,适合短路故障判定。文献[18]提出了开通短路和正常工况下dvds/dt存在明显差异,通过检测开通的dvds/dt可快速识别短路故障,但针对导通后的故障检测依旧采用传统二极管检测方法。文献[19]提出短路故障会导致栅极电流ig增大,但未给出短路电流与ig的关系,并指出栅极电流的快速准确采集是个难题。

针对SiC器件开关过程控制、过电流检测和故障关断的需求,本文提出了一种多电平驱动和保护电路以及开关轨迹的调控方法。通过逻辑处理单元和数模转换电路实现多电平的可控输出,输出电压幅值和阶梯实时可调节,实现对速度、损耗、过冲、振荡和串扰等开关轨迹特征量的协同优化。同时,针对不同回路电感下的短路工况,提出了反时限两段式保护策略,并选取适合的故障关断方式降低短路电流变化率,限制关断过电压。此外,通过降低栅极电压限制短路电流增大,提升短路耐受时间,进而增大故障判定时间来滤除噪声干扰。

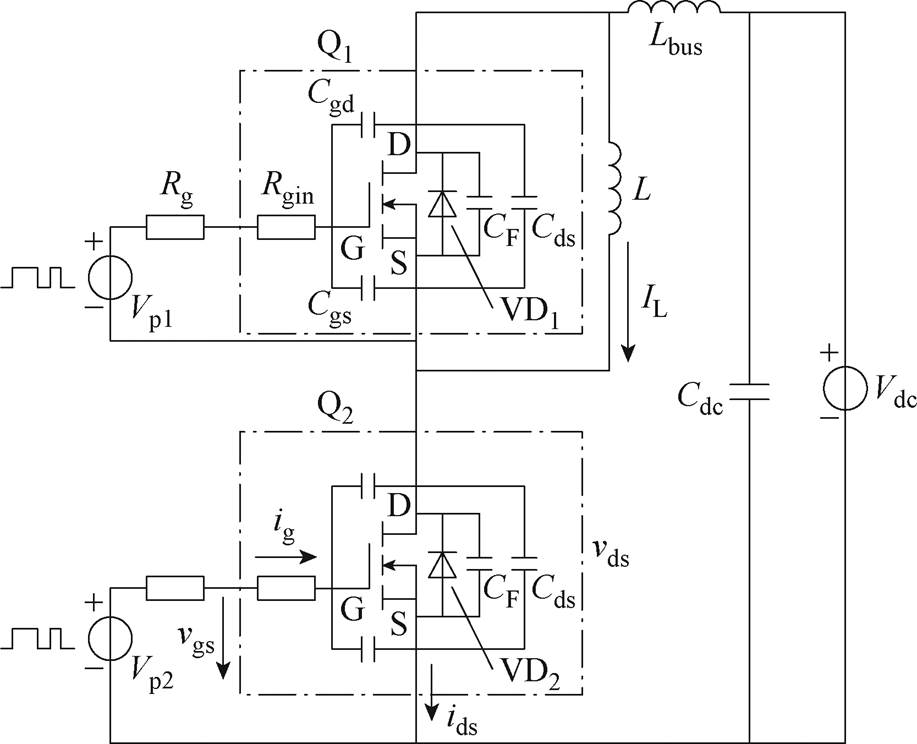

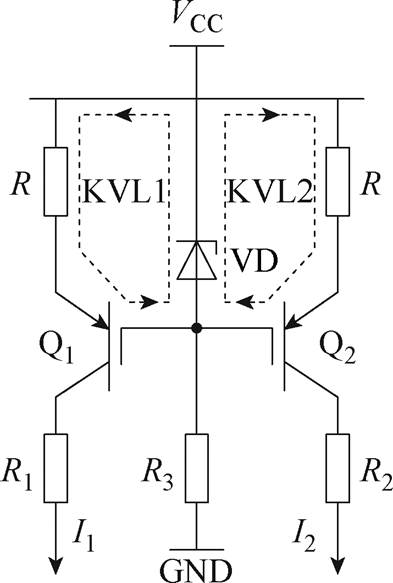

基于半桥拓扑的双脉冲测试是评估SiC MOSFET开关特性的有效手段,双脉冲测试电路如图1所示。Q1、Q2为SiC MOSFET,VD1、VD2为器件体二极管。Lbus为功率回路寄生电感,L为电感负载,IL为负载电流,CF为体二极管寄生电容,vds和ids分别为漏-源极电压和漏极电流,vgs和ig分别为器件的栅-源极电压和栅极电流,Cgs、Cgd和Cds分别为器件的栅-源电容、栅-漏电容和漏-源电容,Vp为栅极驱动电压,Rg为栅极驱动电阻,Rgin为器件的栅极内电阻。

图1 基于半桥拓扑的双脉冲测试电路

Fig.1 Double pulse test circuit based on half-bridge topology

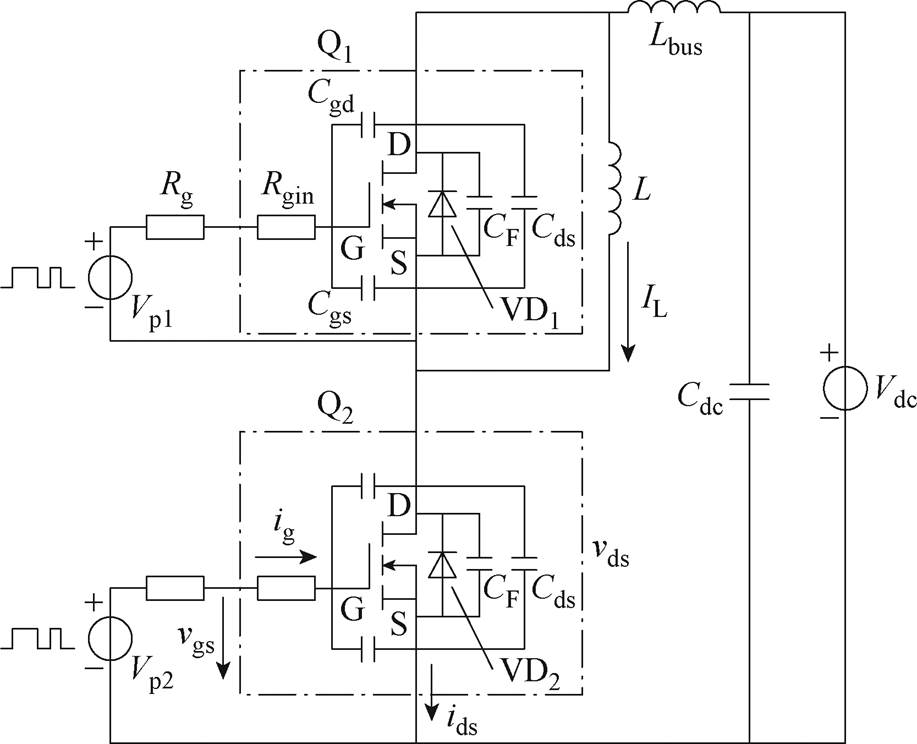

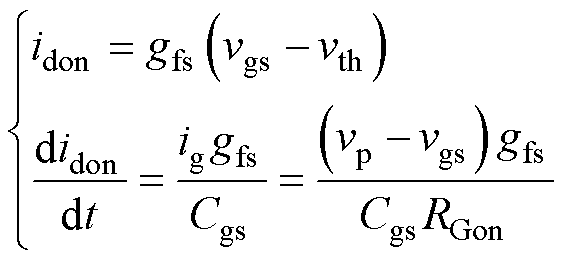

SiC MOSFET开通关断过程如图2所示,Vth和Vmp分别为SiC MOSFET器件的阈值电压和米勒平台电压,Dids和Dvds分别为器件的开通电流过冲和关断电压过冲。开关轨迹分为稳态阶段和动态阶段,稳态阶段电压和电流可认为保持稳定不变,动态阶段可根据电压电流不同的变换过程从Ⅰ~Ⅷ细分为8个阶段。

图2 SiC MOSFET开通关断过程

Fig.2 SiC MOSFET turn-on and turn-off process

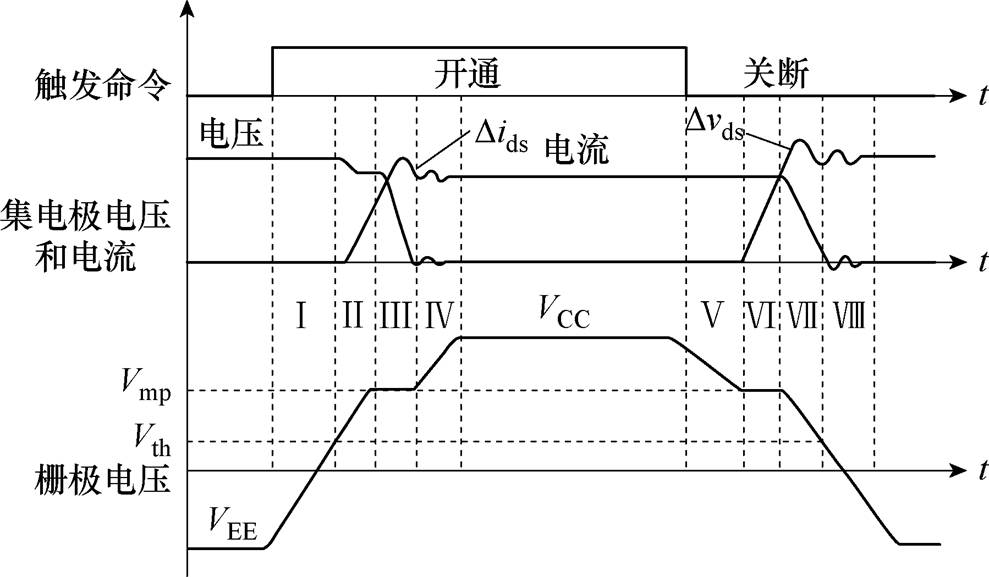

SiC MOSFET的驱动电压直接影响开关过程的电压变化率dvds/dt、电流变化率dids/dt以及电压电流过冲。在简化的开关轨迹模型中,开关过程的电压、电流变化率及过冲电压模型分析如下[6]。

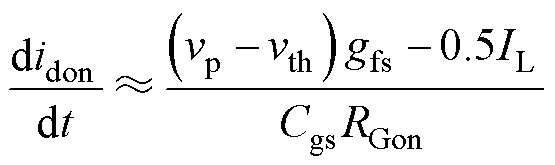

开通过程,在电流上升阶段Ⅱ,栅极电压vgs从vth上升至vmp,由于母线寄生杂感的影响,vds电压略有降低,该阶段电流idon及变化率didon/dt表示为

(1)

(1)

式中,RGon为栅极开通回路Rgon和Rgin之和;gfs为器件的跨导。当vgs从vth过渡到vmp,电流从0增大至IL时,平均电流变化率分别选取vth和vmp点取平均值后,表示为

(2)

(2)

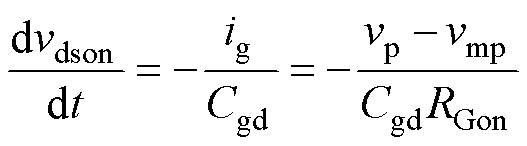

在电压下降和反向恢复电流阶段Ⅲ,栅极电流ig主要为米勒电容Cgd充电,栅极电压vgs维持vmp电压,施加到器件上的电压vp>vmp,该阶段,电流ids为IL与反向恢复电流之和,电压变化率表示为

(3)

(3)

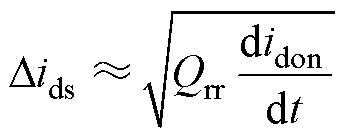

电流过冲发生在反向恢复电流阶段Ⅲ,主要由上桥臂二极管的反向恢复电流引起,与漏极电流上升率didon/dt有关。开通过冲电流Dids可表示为

(4)

(4)

式中,Qrr为上桥臂二极管的反向恢复电荷。当二极管参数确定后,可以通过降低didon/dt来减小Dids。

开通电流过冲后的Ⅳ阶段,Q1完全导通,体二极管寄生电容CF存储的过冲能量向母线寄生电感Lbus释放,两者形成振荡回路。

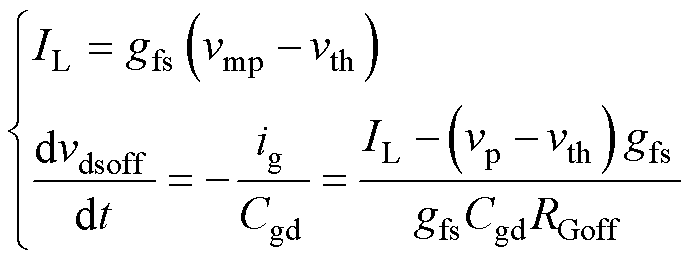

关断过程,在电压上升阶段Ⅵ,当vgs电压维持vmp,施加到器件上的电压vp<vmp,该阶段器件电流近似为IL,类似开通过程,电压变化率表示为

(5)

(5)

在电流下降阶段Ⅶ,当vgs电压从vmp降到vth,电流从IL增大至0时,平均电流变化率分别选取vmp和vth点取平均值后,类似开通过程,表示为

(6)

(6)

电压过冲发生在电流下降阶段Ⅶ,主要由功率回路的寄生电感Lbus引起,与电流下降率didoff/dt有关,当Lbus一定时,通过降低didoff/dt来减小Dvds。关断过电压Dvds表示为

(7)

(7)

关断电压过冲后的Ⅷ阶段,Q1完全关断,VD2完全导通,漏-源电容Cds存储的过冲能量向Lbus释放,两者形成振荡回路。

通过上述分析,SiC MOSFET开关过程中的电压、电流变换率均与驱动电压有关,通过改变vp即可实现对开关过程电压、电流变化率的有效调控,抑制开关电流过冲Dids和电压过冲Dvds,并减小振荡幅值,缩短振荡时间。

SiC MOSFET短路事件可能在变换器的任何时间和任何状态下发生,短路特性与直流母线电压、电流方向、幅值以及短路位置等参数有关。根据故障电流大小可分为过电流故障和短路故障,前者通常为负载侧短路故障,且短路回路电感很大,故障电流上升缓慢;后者通常为桥臂直通故障,短路回路电感小,电流上升迅速。不论哪种故障发生,SiC MOSFET都承受着巨大的短路能量,巨大的能量可能会在短时间内烧毁器件,因此需要驱动单元快速识别故障并准确保护。

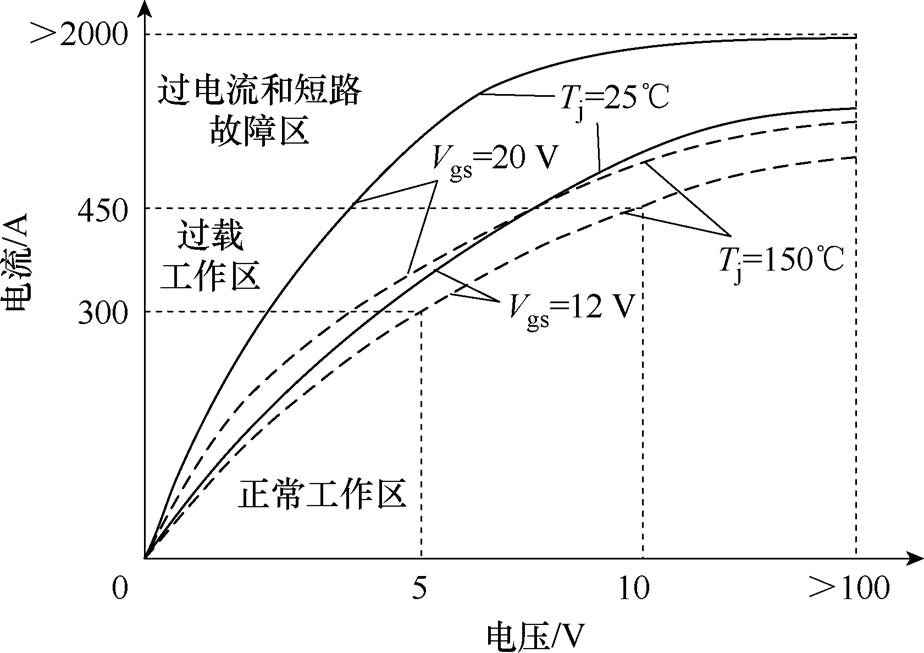

SiC MOSFET在正常导通时,一直工作于饱和状态,漏-源极电压Vds维持低电压,当发生短路故障时,漏-源极电压Vds由低电压逐渐升高直至母线电压,其电压特性与电流、温度变化有关。以Cree公司1 700 V/300 A的SiC MOSFET为例,其输出特性描述了导通压降随电流和温度的变化关系曲线,如图3所示。在同等电流条件下,温度越高、导通压降越高,栅极驱动电压越高、导通压降越低。SiC MOSFET的过载能力小于IGBT,通常将额定电流至1.5倍额定电流作为过载区,超过1.5倍额定电流应采取过电流保护,此时导通压降仅为几伏;当电流超过5倍额定电流应采取短路保护,此时SiC MOSFET出现严重的退饱和现象,导通压降接近母线电压。

图3 电压和电流关系曲线

Fig.3 Voltage and current relational curves

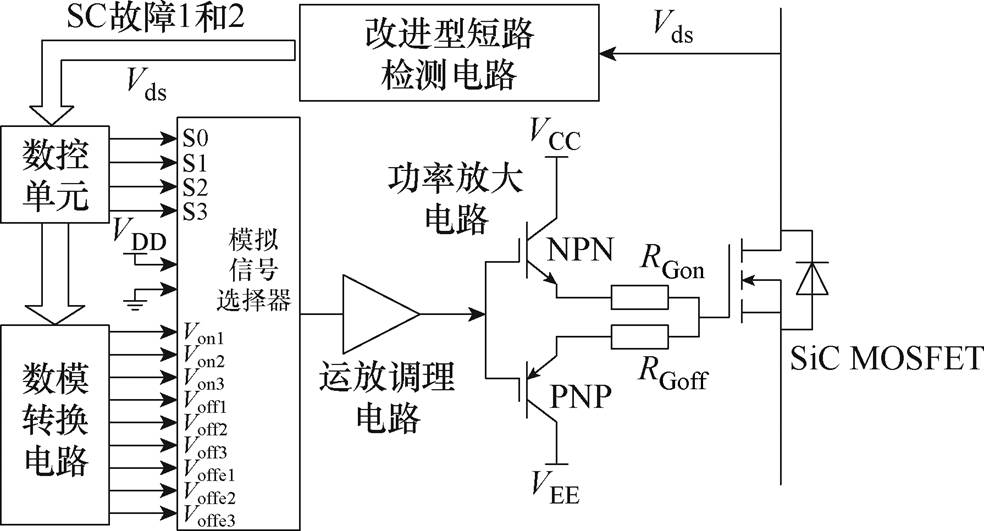

SiC MOSFET多电平驱动与保护电路如图4所示,包含多电平数控单元、数模转换电路、模拟信号选择器、运放调理电路、功率驱动电路和短路故障检测电路。该电路采用多电平方式控制SiC MOSFET的开关过程和故障软关断,可动态调整每种电压投切时间,实现对器件开关轨迹的精细化调控。针对不同类型的SiC器件,只需重新调整各阶段的开关电压和投切时间。

图4 多电平驱动与保护电路

Fig.4 Multi-level driving and protection circuit

以下为各单元的功能说明:

1)多电平信号的生成方法

(1)数控单元采用FPGA芯片,通过高频PWM信号,经过二阶低通滤波器,生成多路稳定的电平信号。

(2)FPGA通过控制模拟信号选择器(74HC4067)地址管脚来选择想要输出的电平到SiC器件的栅极,该芯片最大支持16路信号输入,定义S3引脚作为故障模式位,采用故障关断算法时S3位置1,采用正常开通关断算法时S3清0。

2)多电平驱动方法

(1)模拟选择器输出的电平信号经过运放调理电路,将0~3.3 V的电压转变为-5 V(VEE)~20 V(VCC)。

(2)运放输出信号经过驱动芯片(ZXGD3006E6TA)和NPN、PNP构成功率放大电路,为器件提供驱动电压和电流,不同的电平信号共用一路驱动电路。

3)短路检测方法

(1)故障检测单元利用二极管检测器件退饱和状态来识别电流故障,增加镜像电流源补偿回路,抵消检测回路引起的测量偏差,相比传统二极管检测方式,提高了Vds故障电压的检测精度。

(2)采集到的Vds电压与故障阈值进行比较,超过阈值被判定为故障,保护单元采用两段式反时限保护策略,Vds故障电压越高,FPGA判定时间越短。

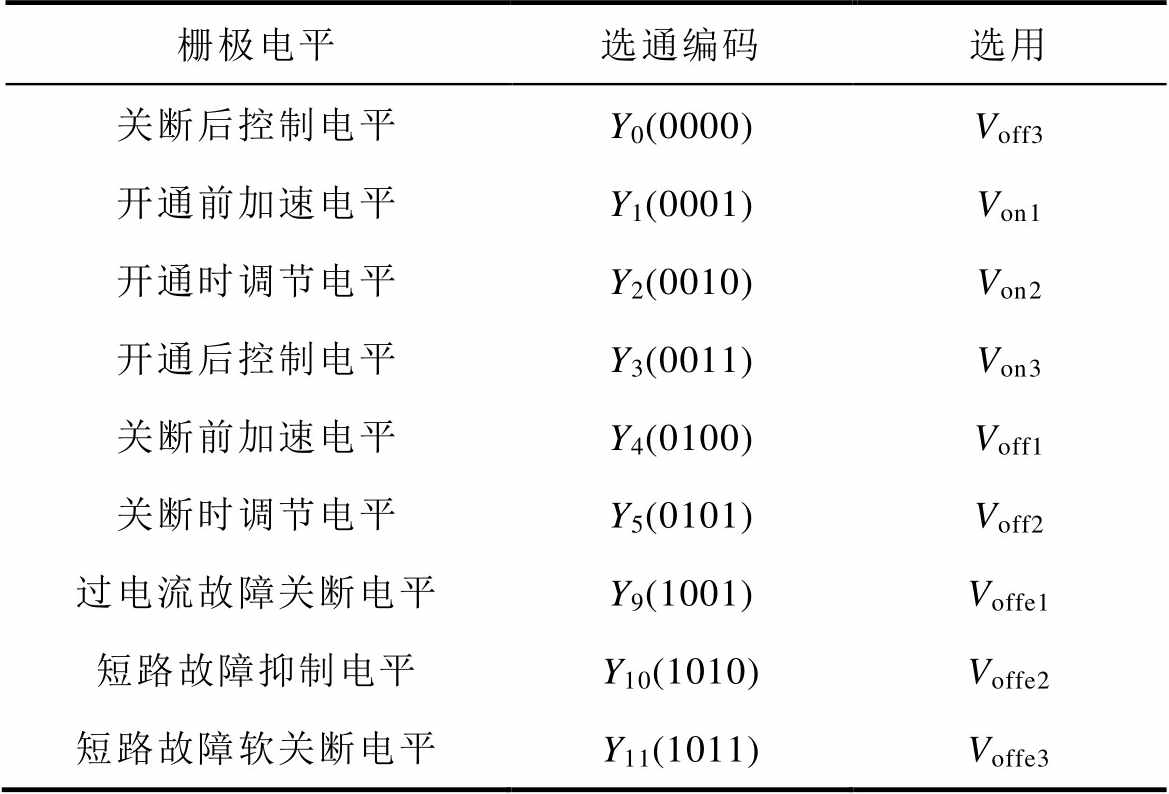

由于正常开关过程和短路故障对驱动电压的要求不同,将电平信号划分为四种,分别用于开通过程控制、正常关断过程控制、过电流关断控制、短路关断控制。电平调节单元可输出9路电平信号,详见表1,每种电压都可独立设定。控制单元通过在选择器的控制引脚施加不同选择命令,能够输出对应的电平信号,并可实现栅极驱动电压的ns级切换。根据器件工作状态选择相关的电平信号输出到器件栅极,实现器件开关过程的动态调节,以及故障工况的安全关断。

表1 每路电平信号的功能定义

Tab.1 Functional definition of each level voltage

栅极电平选通编码选用 关断后控制电平Y0(0000)Voff3 开通前加速电平Y1(0001)Von1 开通时调节电平Y2(0010)Von2 开通后控制电平Y3(0011)Von3 关断前加速电平Y4(0100)Voff1 关断时调节电平Y5(0101)Voff2 过电流故障关断电平Y9(1001)Voffe1 短路故障抑制电平Y10(1010)Voffe2 短路故障软关断电平Y11(1011)Voffe3

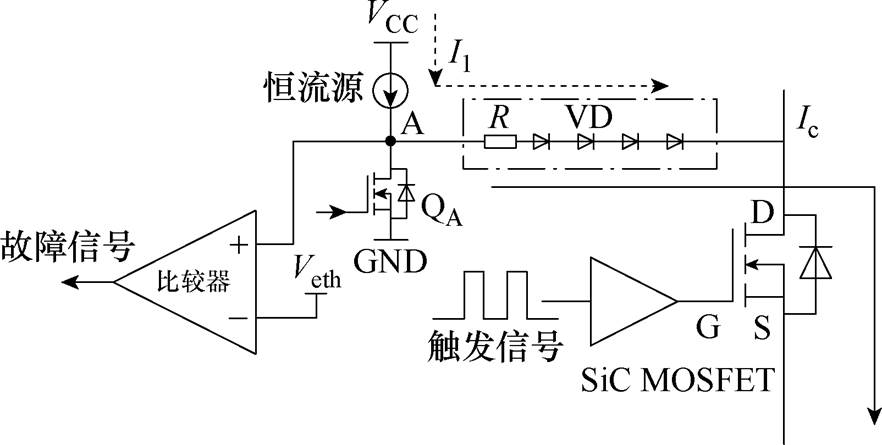

SiC MOSFET与驱动器并联连接,无法直接检测故障电流,需通过检测导通压降Vds来识别电流故障,可以采用二极管式退饱和检测电路,检测回路串联接入二极管,如图5所示。在SiC MOSFET导通时,二极管正向导通,激励电流源产生检测电流,经过限流电阻和二极管流入SiC MOSFET。当A点电压VA上升超过阈值Veth时,比较器翻转输出故障闭锁信号;当SiC MOSFET关断时,二极管反向截止,故障检测使能MOS管QA导通,将A点电压下拉至低电平,故障检测电路被屏蔽。

图5 传统二极管式短路检测电路

Fig.5 Traditional diode mode short-circuit detection circuit

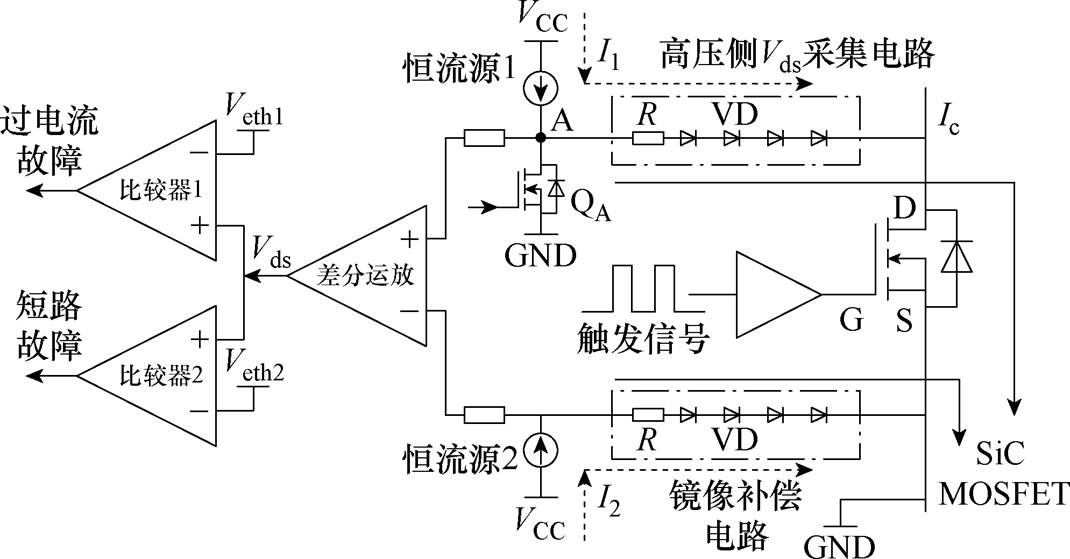

在SiC MOSFET 完全开通后,A点电压VA的大小可以表示为

(8)

(8)

式中,VD为二极管正向导通压降;VA检测结果包含了SiC MOSFET的导通压降、二极管导通压降和限流电阻电压。该检测值会受到检测电流和温度变化影响,导致Vds检测误差大,其结果可用于短路故障判定,无法对过电流状态进行准确测量。另外针对高压SiC器件需要更多的二极管串联来承受反向击穿电压,A点电位升高,容易触及阈值Veth,引发误保护。

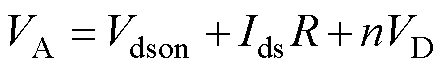

当SiC MOSFET的工作电流超过额定范围,如超出额定电流的1.5倍,此时导通压降仅有几伏,传统的Vds检测方式难以准确识别。为提高故障时电压Vds的检测精度,提出一种基于镜像电流源补偿检测回路的导通压降检测电路,如图6所示。该电路同时兼顾了SiC MOSFET过载和短路故障的识别。

图6 改进型Vds电压检测电路

Fig.6 Improved Vds voltage detection circuit

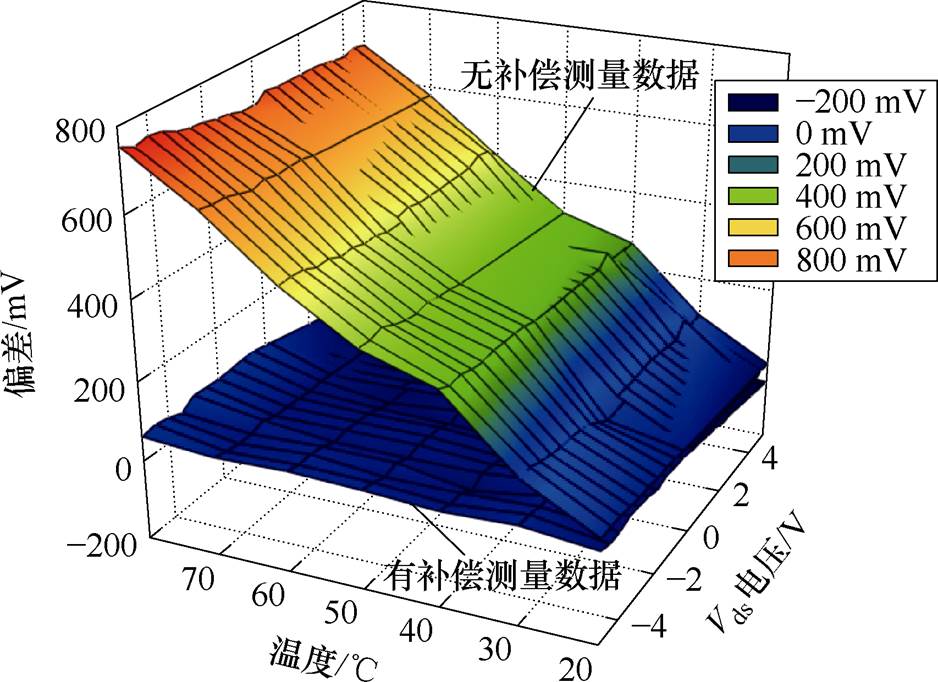

利用多个性能近似的PNP晶体管产生双路镜像的恒流源,分别用于高压检测电路激励源I1和镜像补偿电路的激励源I2,每个支路串联相同的限流电阻和检测二极管,保证在同样激励电流和温度下,两个支路的检测结果经过差分运放后可抵消高压检测电路的测量误差。

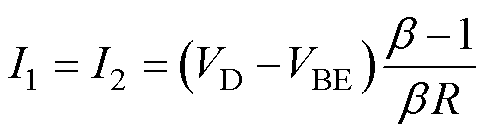

镜像双路恒流源电路由稳压管VD、相同特性晶体管Q1和Q2以及限流电阻构成,如图7所示,两个晶体管的VBE、基极电流IB和集电极电流IC相同,其中,IC=bIB,b为晶体管的电流放大系数。

图7 双路镜像恒流源电路

Fig.7 Double mirror constant current source circuit

根据基尔霍夫电压定律(KVL),激励电流源大小满足

(9)

(9)

差分运放输入端口的电压大小满足

(10)

(10)

差分运放输出电压为输入“+”端信号与输入“-”端信号的差值,由式(10)可知,运放输出结果抵消二极管的非线性特征、限流电阻压降、温度、负载波动等带来的影响,最终精确地检测出导通压降Vds,实现SiC器件的精准保护。此外,控制单元可利用模数转换器(A-D)采集导通压降,用于对器件工作电流、结温、损耗的评估。

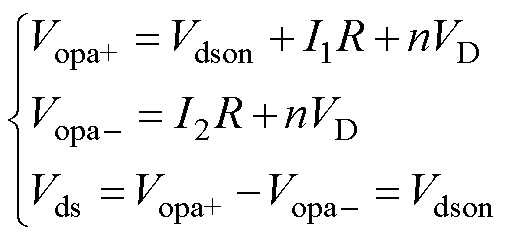

基于上述改进型检测电路,设计满足-5~5 V的导通压降检测多电平驱动单元,验证环境温度从20~80℃下的采集精度,并与传统无补偿回路的检测电路做对比,试验结果如图8所示,传统无补偿回路检测电路的误差随着温度的增大,偏差达到750 mV。改进型检测电路在全温度范围内检测误差小于±50 mV,远远优于传统检测电路。

图8 两种导通压降Vds检测电路的测试结果

Fig.8 The test results of two type Vds detection circuits

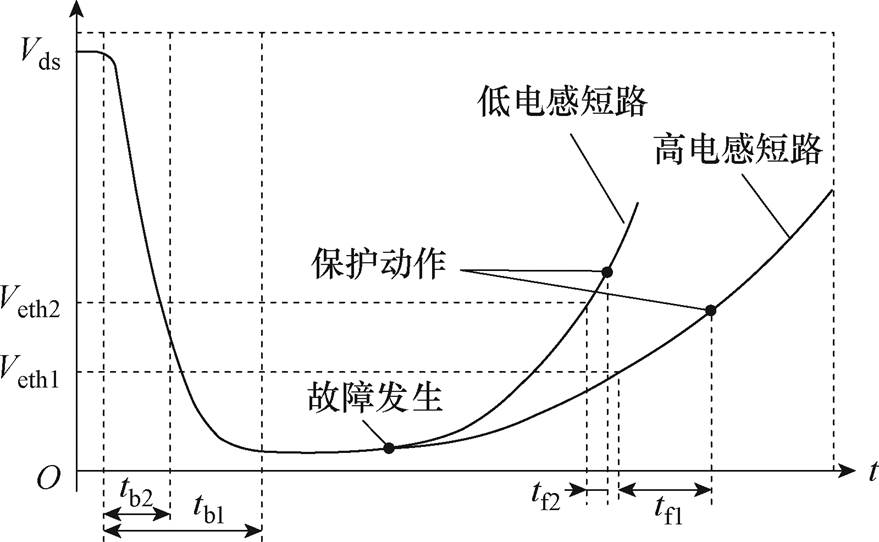

多电平驱动单元依据短路故障的严重程度采取两段式反时限保护策略,故障电流越大,设定的保护阈值越高,判定时间越短;反之,故障电流越小,设定的保护阈值越低,判定时间越长。两段式反时限保护策略如图9所示,第一段比较器的阈值电压为Veth1,设定值依据SiC器件在高结温下1.5倍电流对应的导通压降,保护判定时间包含检测盲区时间tb1和滤波检测时间tf1,在SiC MOSFET完全导通前,需要预留足够的盲区时间tbl防止检测电路误触发。第二段比较器阈值电压为Veth2,设定值大于在高结温下5倍电流对应的导通压降,保护判定时间包含检测盲区时间tb2和滤波检测时间tf2,设定值应该满足器件的短路耐受能力。不同的厂家器件耐受时间不同,如英飞凌对外宣称其Cool SiC MOSFET具有3 ms的短路承受时间,CREE和Rohm 公司的短路承受时间约为2 ms。

图9 两段式反时限保护策略

Fig.9 Two-stage inverse time protection strategy

SiC MOSFET的开关过程可分为八阶段,第Ⅰ和第Ⅴ阶段为开关延时,该阶段有着较为清晰的界限,通常以Vth为界,但其他阶段没有清晰的界限。其他阶段时间的长短与器件的工作电压和电流有着密切的关系,工作电流越高,电流上升和下降时间越长;同理,工作电压越高,电压的下降和上升时间越长。为此,考虑多电平驱动功能的兼容性,将开通和关断过程分为六个调控阶段,分别为开通前加速、开通米勒平台调控、完全开通、关断前加速、关断米勒平台调控和完全关断,每个阶段可独立调整输出电平和调控时间。

本文提出的多电平驱动保护电路,不仅能够实现SiC MOSFET的动态特性调控,还能依据不同的故障类型智能选择合适的保护算法,按照类型分为正常关断策略、过电流故障关断策略和短路故障软关断策略。通过不同的关断算法,既保证了SiC MOSFET在正常开关时对损耗的要求,又满足在过电流、短路等故障时对电压尖峰抑制的需求。

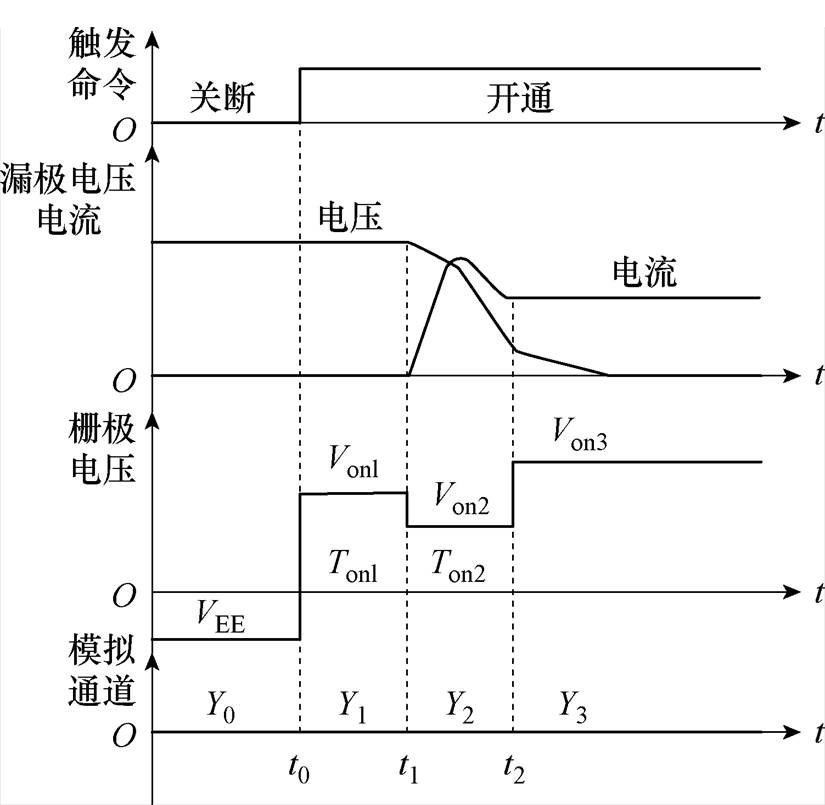

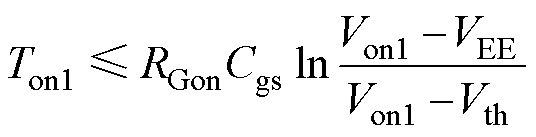

多电平驱动采用三段式电平开通策略如图10所示。t0~t1为导通延时阶段,施加较大的栅极电压Von1,通常电平接近VCC,用于缩短开通时间,且Ton1时间应在电流上升前停止施加,计算公式为

图10 正常工况三段式开通策略

Fig.10 Three-stage turn-on strategy in normal conditions

(11)

(11)

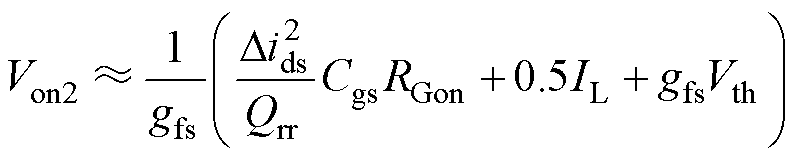

t1~t2为电流上升和二极管反向恢复阶段,基于1.2节过冲电流与栅压的关系式(2)、式(4),按照式(12)选择合适栅极电压Von2,介于Vth与VCC之间,控制电流上升率,减小反向恢复的过冲电流。Ton2时间需大于电流上升和电压拖尾振荡时间之和,但Ton2时间越长,开通损耗越大。随后采用最大电平Von3,通常电平接近VCC,使SiC MOSFET完全导通。

(12)

(12)

多电平驱动采用三段式电平关断策略如图11所示,t0~t1为关断延时阶段,施加较小的栅极负电压Voff1,通常电平接近VEE,用于缩短关断时间,且Toff1时间应在电流下降前停止施加。

(13)

(13)

t1~t2为电流下降和电压过冲阶段,基于1.2节过冲电压与栅压的关系式(6)和式(7),按照式(14)选择合适栅极电压Voff2,介于Vmp与VEE之间,控制电流下降率,减小关断电压过冲。Toff2时间需大于电流下降和电压振荡时间之和,但Toff2时间越长,关断损耗越大。随后采用最小负电平Voff3,通常电平接近VEE,使SiC MOSFET完全关断。

(14)

(14)

图11 正常工况三段式关断策略

Fig.11 Three-stage turn-off strategy in normal conditions

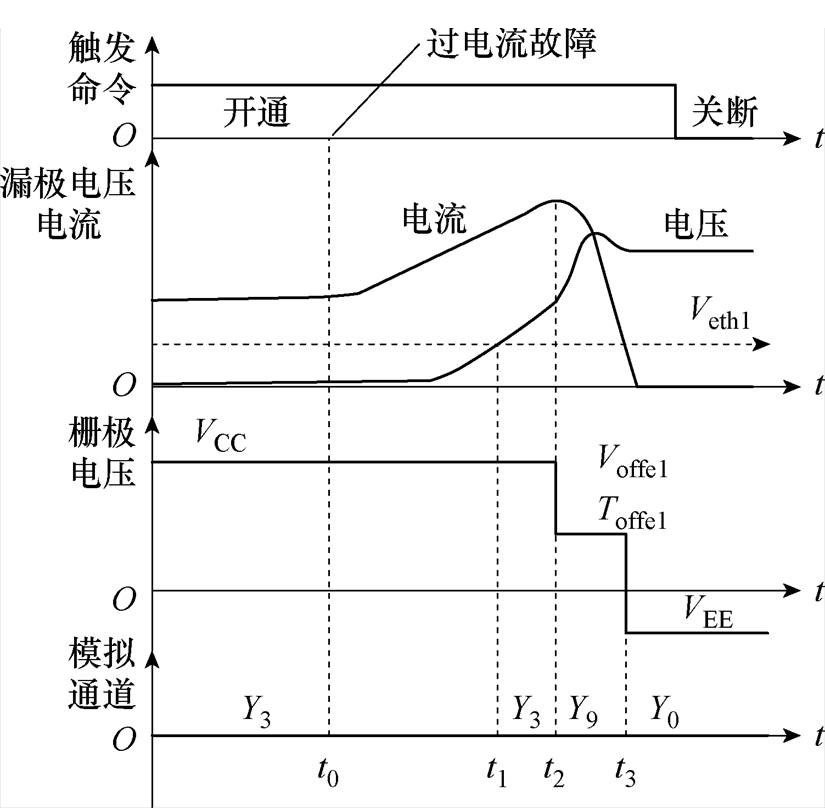

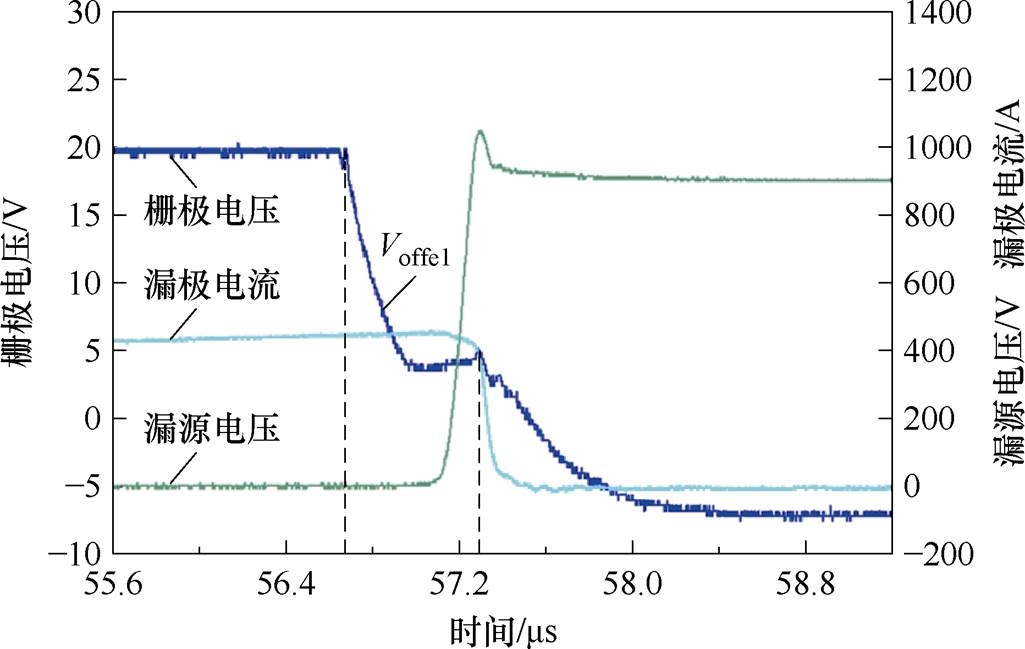

当发生负载短路时,回路电感较大,SiC MOSFET故障电流缓慢爬升,导通压降逐渐增大。t1时刻,故障电流对应的导通压降超过比较阈值Veth1;t1~t2时间为驱动的滤波时间tf1,如果该时间内一直超过比较阈值,则触发过电流软关断策略如图12所示;t2时刻,采用软关断电平Voffe1缓慢关断故障电流,减少关断过电压,Voffe1的选择方式参考式(14),此时的电流为过载电流。关断时间Toff3更长,Toffe1应大于Toff1与Toff2之和,且小于上下桥臂死区时间。t3时刻,施加负压VEE保持器件完全关断。

图12 过电流故障关断策略

Fig.12 Overcurrent fault turn-off strategy

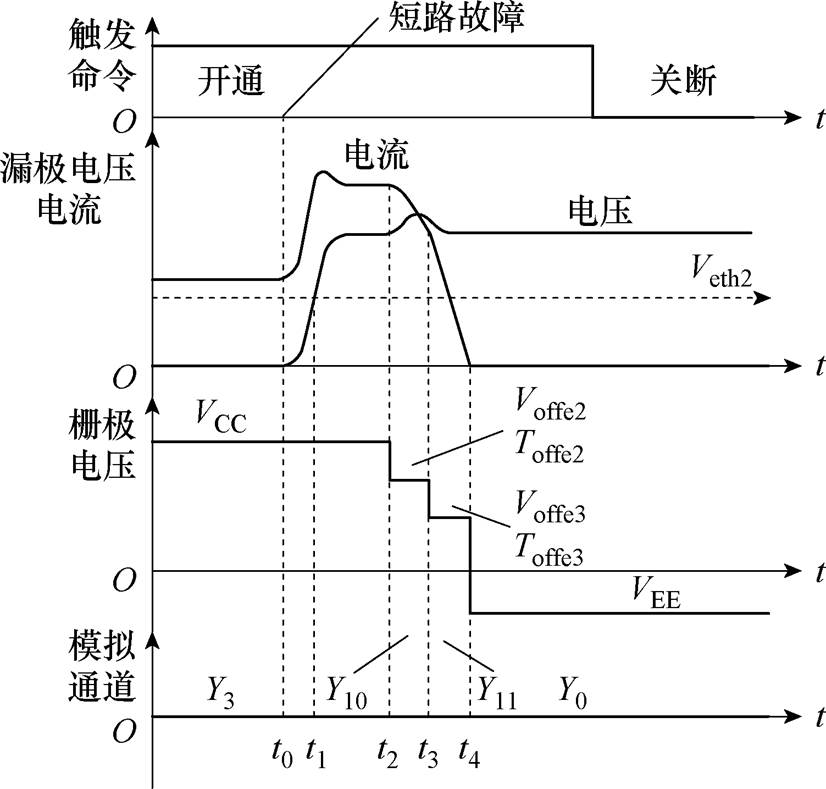

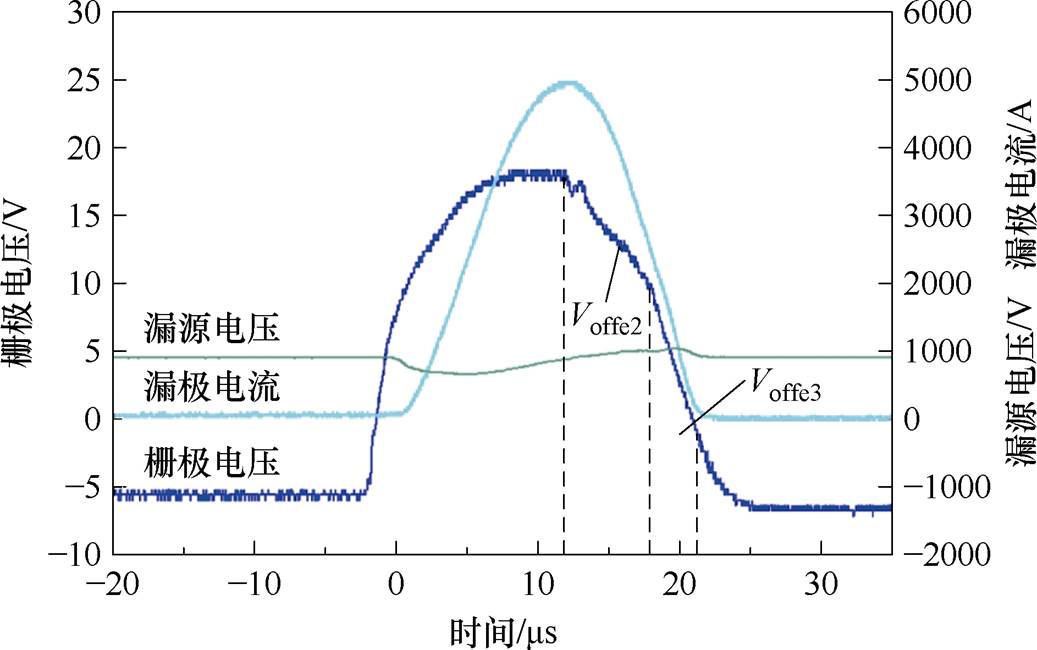

当SiC MOSFET发生短路故障时,故障电流迅速上升,导通压降会迅速增大至母线电压,如图13所示。t1时刻,故障电流对应的压降超过比较阈值Veth2;t1~t2为驱动器的滤波时间tf2,如果该时间内压降一直超过比较阈值,则触发短路软关断策略,该滤波时间远小于过电流滤波时间tf1;t2时间,降低栅极电压至Voffe2,该电压接近正常电流时的米勒电压Vmp,使器件继续保持导通状态,SiC器件的电流会被限制在较低水平;t3时刻,如果管压降不再高于比较阈值,则恢复正常工况;反之,作为短路故障采用短路软关断电平Voffe3关断故障电流,Voffe3的选择方式参考式(14),此时的电流为短路电流。当故障电流接近0时,t4时刻采用负电压完全关断。t1~t4时间为短路故障保护时间,一般不超过3 ms。

图13 直通短路故障软关断策略

Fig.13 Direct short-circuit soft turn-off strategy

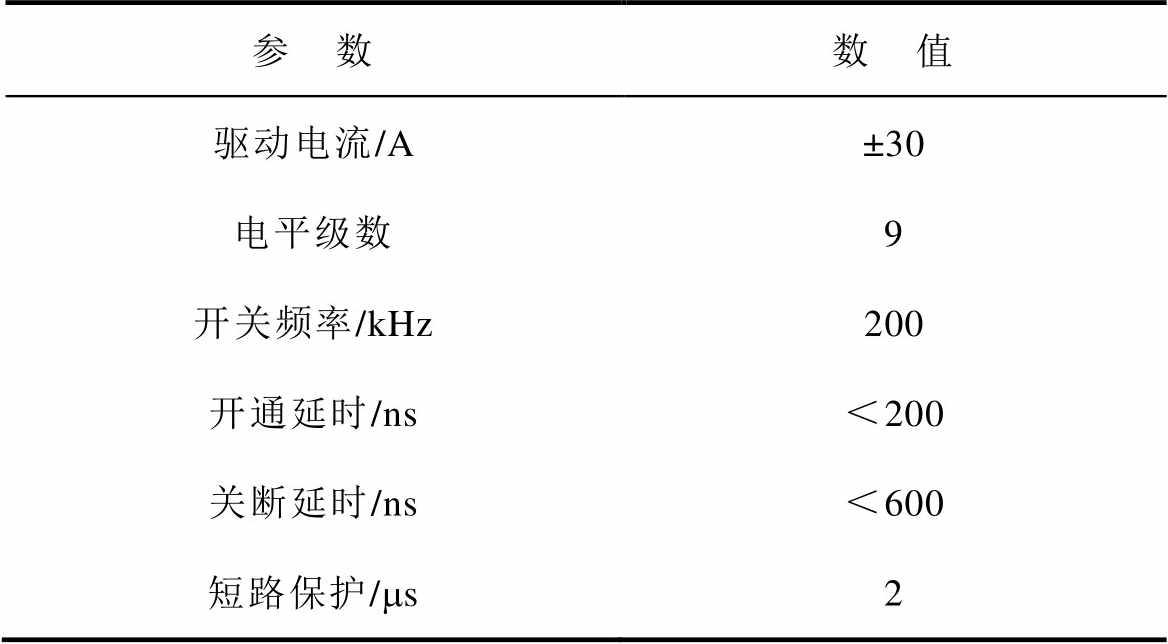

设计满足1 200~1 700 V电压等级、半桥式SiC MOSFET控制保护的驱动器,驱动器集成了多电平驱动电路、短路检测和软关断算法,关键性能参数详见表2,可用于桥式变流器、开关电源、变频器等,满足了器件大电流驱动、高频工作的需求。针对不同的应用工况,实际关断电平的选取,与工作电压电流、故障类型、回路杂感、器件耐受能力等有关。

表2 多电平驱动器性能参数

Tab.2 The multi-level driver performance parameters

参 数数 值 驱动电流/A±30 电平级数9 开关频率/kHz200 开通延时/ns<200 关断延时/ns<600 短路保护/ms2

为验证驱动器开关特性调控、短路检测和保护功能的有效性,搭建了如图14所示的双脉冲试验平台。被测试器件选用CREE公司CAS300M17BM2,是1 700 V/300 A的SiC MOSFET。直流电容为6.5 mF,负载电抗为55 mH,母排杂感为10 nH。

图14 双脉冲和短路测试平台

Fig.14 Double pulse and short circuit test platform

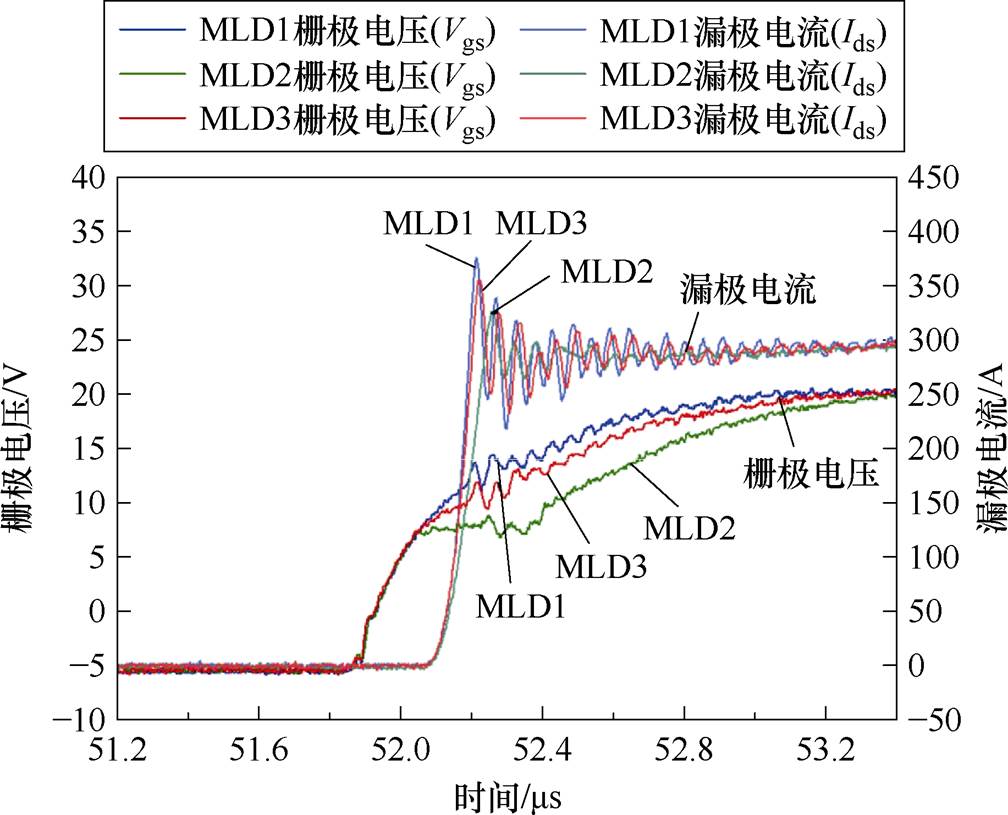

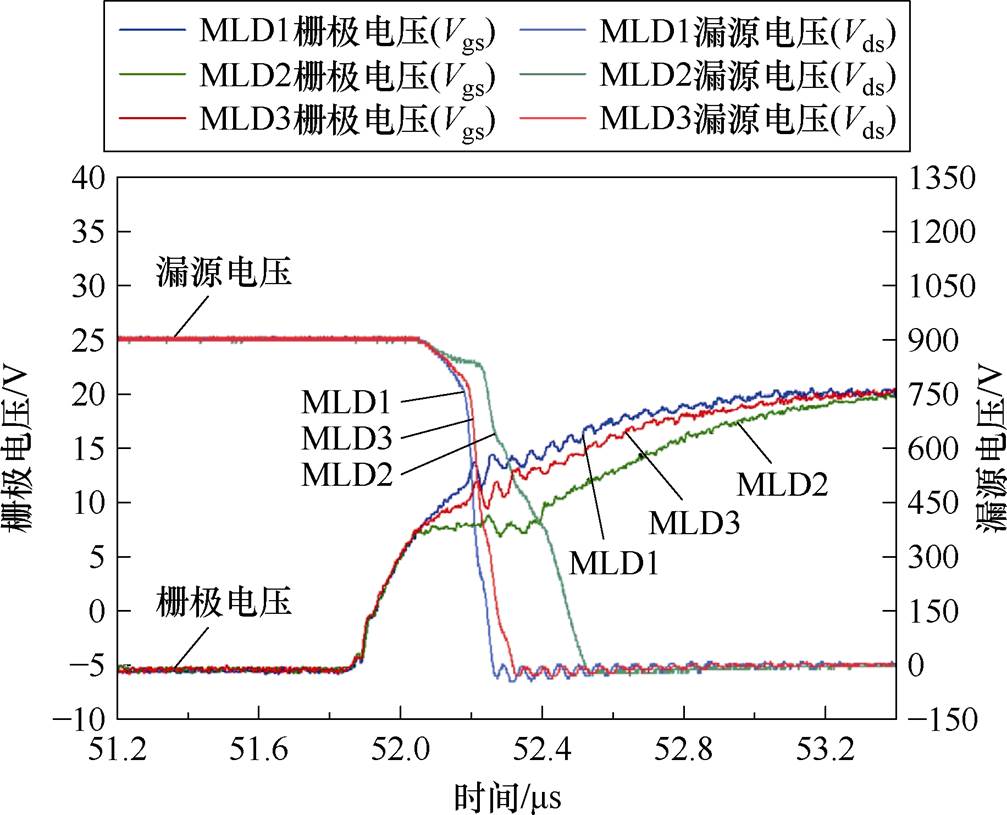

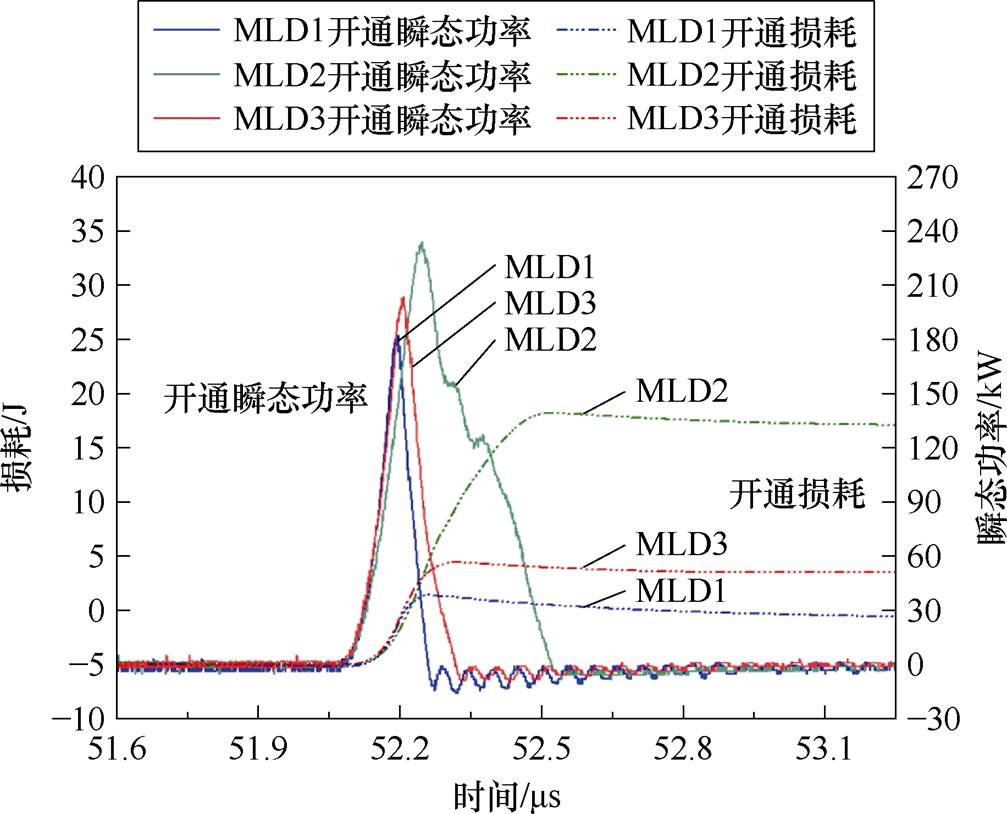

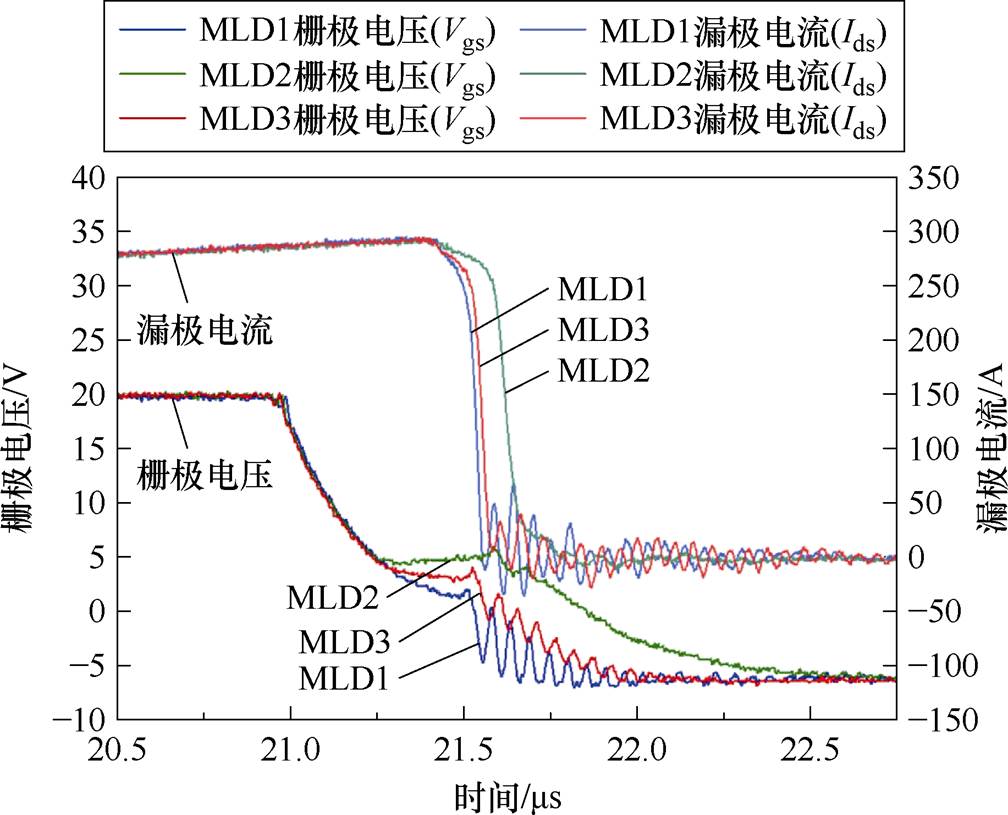

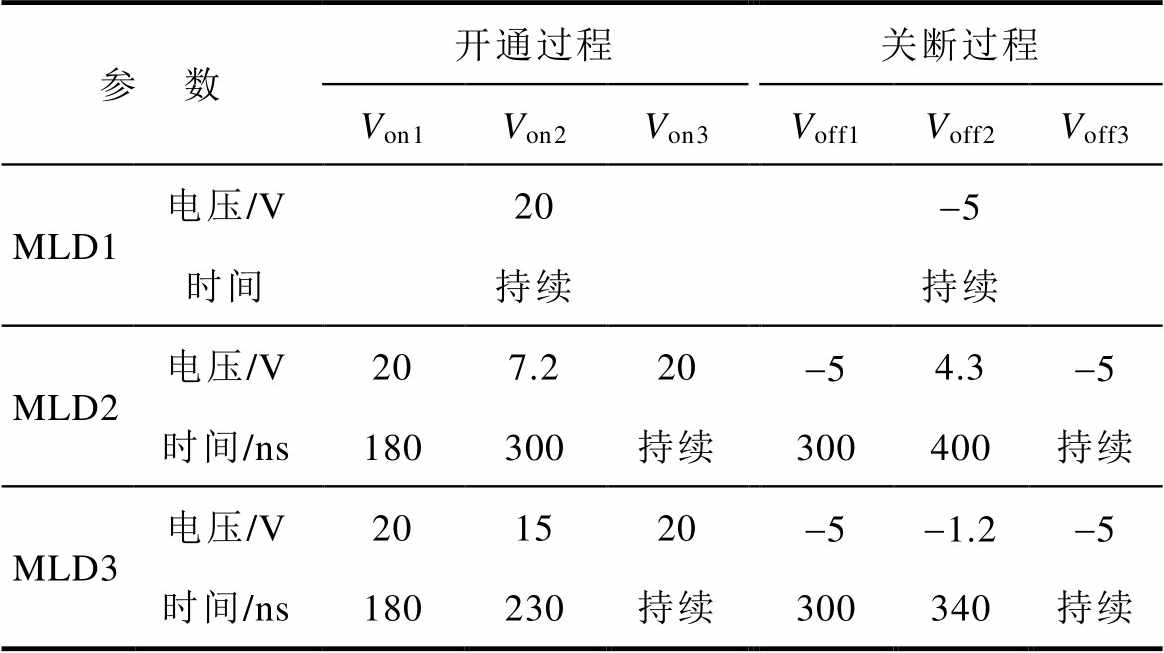

为了验证所设计的多电平驱动器(Multi-Level Driver, MLD)的调控效果,设定三种不同试验参数作为对照,三种MLD开通、关断电流,电压和损耗特性对比如图15~图20所示。MLD1开通关断过程仅有一个电平,分别为正电源VCC和负电压VEE,MLD2和MLD3开通关断过程各有三个电平,选取的电平电压和控制时间详见表3,其中MLD1以提升开关速度为目标;MLD2以抑制开关过冲和振荡为目的;MLD3在开关速度、过冲和损耗之间寻求平衡点。

图15 三种MLD开通电流特性对比

Fig.15 Comparison results of three MLDs turn-on current characteristics

图16 三种MLD开通电压特性对比

Fig.16 Comparison results of three MLDs turn-on voltage characteristics

图17 三种MLD开通损耗特性对比

Fig.17 Comparison results of three MLDs turn-on loss characteristics

图18 三种MLD关断电流特性对比

Fig.18 Comparison results of three MLDs turn-off current characteristics

图19 三种MLD关断电压特性对比

Fig.19 Comparison results of three MLDs turn-off voltage characteristics

图20 三种MLD关断损耗特性对比

Fig.20 Comparison results of three MLDs turn-off loss characteristics

表3 三种多电平驱动的试验参数

Tab.3 Three multi-level drivers test parameters

参 数开通过程关断过程 Von1Von2Von3Voff1Voff2Voff3 MLD1电压/V20-5 时间持续持续 MLD2电压/V207.220-54.3-5 时间/ns180300持续300400持续 MLD3电压/V201520-5-1.2-5 时间/ns180230持续300340持续

三种驱动器保持相同的驱动电阻,开通电阻为2.2 W,关断电阻为1 W。SiC MOSFET的双脉冲试验电压为900 V,电流为300 A。

三种驱动器测试结果见表4,从开关延时、反向恢复电流、电压过冲、损耗等方面进行对比分析。在开关延时阶段,MLD2和MLD3通过采用加速控制策略,使得开关延时与MLD1相近。在电压电流变化阶段,MLD1采用最大的开通电压和关断电压,开通关断延时最短、损耗最小,但是开关过冲最大,且开关振荡最剧烈;MLD2采用最小的开通电压和关断电压,开关过冲和振荡得到很好抑制,但是开关延迟最大、开关速度最慢、损耗最大;MLD3选用折中的调节参数,同时兼顾了开关速度、过冲和损耗。因此,MLD3试验参数更适合SiC器件的应用要求。

表4 三种多电平驱动器的试验结果

Tab.4 Three multi-level drivers test results

试验结果MLD1MLD2MLD3 开通过程开通延时/ns170175172 开通时间/ns350595392 反向恢复电流/A823062 开通di/dt/(kA/ms)4.32.43.7 开通dv/dt/(/kV/ms)9.33.57.1 开通损耗/mJ11.843.817.5 拖尾振荡时间/ns400200280 关断过程关断延时/ns500505510 关断时间/ns580745650 关断过电压/V230140190 关断di/dt/(/kA/ms)6.33.25.3 关断dv/dt/(/kA/ms)13.87.110.6 关断损耗/mJ25.335.428.2 拖尾振荡时间/ns60040300

为验证驱动器导通压降检测和保护功能的有效性,分别开展过电流和短路保护试验,两者采用不同的检测参数和保护关断算法。驱动的两段反时限配置参数:过电流保护阈值Veth1=5.4 V,保护时间为2 ms;短路保护阈值Veth2=9.5 V,保护时间为800 ns。两种保护的关断参数详见表5。

表5 多电平驱动的两段式保护参数

Tab.5 The multi-level driver two-stage protection parameters

保护类型栅极电压保护参数 电压/V时间/ns 过电流保护Voffe14.5600 Voff3-5持续 短路保护Voffe211.5500 Voffe39200 Voff3-5持续

过电流保护试验基于图1的双脉冲试验电路,下管Q2作为被测对象,上管Q1处于关断状态。脉冲发生器向Q2发送开通命令,直流电容经电感和下管Q2放电,电感电流持续增大,当驱动器检测到Q2的导通压降达到过电流判定阈值Veth1,触发过电流保护策略,关断Q2。

过电流故障关断试验波形如图21所示,SiC MOSFET的峰值电流为430 A,驱动器采用软关断策略,最大关断尖峰仅有109 V,关断电压过冲和振荡得到抑制。

图21 过电流故障关断试验波形

Fig.21 Over-current fault turn-off test waveforms

短路试验电路基于图1的双脉冲试验电路,上管Q1用导线短接,电容电压充电到900 V,脉冲发生器向Q2发送开通命令,当下管Q2导通时,导致上、下管形成直通短路,短路电流迅速增大,当驱动2检测到Q2的导通压降超过短路判定阈值Veth2,触发短路保护策略,关断Q2。

短路故障软关断试验波形如图22所示,SiC MOSFET的峰值电流达到4.98 kA,是额定电流的16倍,采用软关断策略,最大关断尖峰仅有102 V,比正常关断和过电流关断的尖峰还小,实现了短路电流下的安全关断。

图22 短路故障软关断试验波形

Fig.22 Short-circuit fault turn-off test waveforms

通过建立栅极电压与开关过程的电压、电流变化率的关系模型,解释了栅极电压对开关轨迹的影响规律,改变驱动电压可实现开关过程电流变化率的有效调控,抑制开关过冲Dids和Dvds,并减小振荡幅值。为此,提出了基于多段式栅极电平调控的SiC MOSFET的驱动和保护方法,设计出多电平SiC驱动器,通过修改软硬件参数可以适配多种电压和封装样式的SiC器件。

在开关轨迹方面,多电平驱动器采用三段式变电压调控策略,在不同阶段独立调控栅极充放电电流,实现开关轨迹的多目标协同优化,在获得较快开关速度和低损耗的同时,有效抑制过冲和振荡。

在保护方面,提出了增加补偿回路的导通电压检测电路,降低了温度和负载变化的影响,检测精度大幅度提升。采取两段式反时限保护方法,实现过电流和短路故障的独立检测和保护。通过两段式降低栅极电压的关断方法,能够限制短路电流增大,提高短路故障检测盲区的时间以降低干扰噪声影响,并采用软关断技术,有效抑制关断过电压和振荡。

参考文献

[1] 盛况, 任娜, 徐弘毅. 碳化硅功率器件技术综述与展望[J]. 中国电机工程学报, 2020, 40(6): 1741- 1753.

Sheng Kuang, Ren Na, Xu Hongyi. A recent review on silicon carbide power devices technologies[J]. Proceedings of the CSEE, 2020, 40(6): 1741-1753.

[2] Yuan Xibo, Laird I, Walder S. Opportunities, challenges, and potential solutions in the application of fast- switching SiC power devices and converters[J]. IEEE Transactions on Power Electronics, 2021, 36(4): 3925-3945.

[3] Yu Baowei, Guo Xizheng, Bu Xucong, et al. Research on the SiC MOSFETs short circuit detection and protection optimization method[C]//2020 IEEE Vehicle Power and Propulsion Conference (VPPC), Gijon, Spain, 2020: 1-7.

[4] 吴海富, 张建忠, 赵进, 等. SiC MOSFET短路检测与保护研究综述[J]. 电工技术学报, 2019, 34(21): 4519-4528.

Wu Haifu, Zhang Jianzhong, Zhao Jin, et al. Review of short-circuit detection and protection of silicon carbide MOSFETs[J]. Transactions of China Electro- technical Society, 2019, 34(21): 4519-4528.

[5] 左璐巍, 辛振, 蒙慧, 等. 动态高温反偏应力下的SiC MOSFET测试平台及其退化机理研究[J]. 电源学报, 2024, 22(3): 211-219.

Zuo Luwei, Xin Zhen, Meng Hui, et al. Test platform and degradation mechanism of SiC MOSFET under dynamic high-temperature reverse bias stress[J]. Journal of Power Supply, 2024, 22(3): 211-219.

[6] 邹铭锐, 曾正, 孙鹏, 等. 基于变电阻驱动的SiC器件开关轨迹协同调控[J]. 电工技术学报, 2023, 38(16): 4287-4300.

Zou Mingrui, Zeng Zheng, Sun Peng, et al. Coor- dinated switching trajectory regulation of SiC device using variable resistance gate drive[J]. Transactions of China Electrotechnical Society, 2023, 38(16): 4287-4300.

[7] Chen Jiangui, Li Yan, Liang Mei, et al. A novel gate driver for suppressing overcurrent and overvoltage of SiC MOSFET[C]//2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019- ECCE Asia), Busan, Korea, 2019: 1-7.

[8] Wei Yuqi, Du Liyang, Du Xia, et al. Multi-level active gate driver for SiC MOSFETs with paralleling operation[C]//2021 IEEE 22nd Workshop on Control and Modelling of Power Electronics (COMPEL), Cartagena, Colombia, 2021: 1-7.

[9] Zhao Shuang, Dearien A, Wu Yuheng, et al. Adaptive multi-level active gate drivers for SiC power devices[J]. IEEE Transactions on Power Electronics, 2019, 35(2): 1882-1898.

[10] Geng Chengfei, Zhang Donglai, Wu Xuanqin, et al. A novel active gate driver with auxiliary gate current control circuit for improving switching performance of high-power SiC MOSFET modules[C]//2020 IEEE 1st China International Youth Conference on Elec- trical Engineering (CIYCEE), Wuhan, China, 2020: 1-7.

[11] Sukhatme Y, Miryala V K, Ganesan P, et al. Digitally controlled gate current source-based active gate driver for silicon carbide MOSFETs[J]. IEEE Transactions on Industrial Electronics, 2020, 67(12): 10121- 10133.

[12] 文阳, 杨媛, 宁红英, 等. SiC MOSFET短路保护技术综述[J]. 电工技术学报, 2022, 37(10): 2538-2548.

Wen Yang, Yang Yuan, Ning Hongying, et al. Review on short-circuit protection technology of SiC MOSFET[J]. Transactions of China Electrotechnical Society, 2022, 37(10): 2538-2548.

[13] 杨旭, 葛兴来, 柴育恒, 等. 一种基于反向串联稳压二极管钳位的IGBT导通压降在线监测电路[J]. 中国电机工程学报, 2022, 42(12): 4547-4561.

Yang Xu, Ge Xinglai, Chai Yuheng, et al. An online monitoring circuit for IGBT conduction voltage drop based on reverse series zener diodes clamping[J]. Proceedings of the CSEE, 2022, 42(12): 4547-4561.

[14] 宁红英, 孙旭霞, 杨媛. 一种基于diC/dt反馈控制的大功率IGBT驱动保护方法[J]. 电工技术学报, 2015, 30(5): 33-41.

Ning Hongying, Sun Xuxia, Yang Yuan. A high- power IGBT drive protection method based on diC/dt feedback control[J]. Transactions of China Electro- technical Society, 2015, 30(5): 33-41.

[15] Lee S, Kim K, Shim M, et al. A digital signal processing based detection circuit for short-circuit protection of SiC MOSFET[J]. IEEE Transactions on Power Electronics, 2021, 36(12): 13379-13382.

[16] Ouyang Wenyuan, Sun Pengju, Xie Minghang, et al. A fast short-circuit protection method for SiC MOSFET based on indirect power dissipation level[J]. IEEE Transactions on Power Electronics, 2022, 37(8): 8825-8829.

[17] Li Hong, Wang Yuting, Qiu Zhidong, et al. Short- circuit protection circuit of SiC MOSFET based on drain-source voltage integral[C]//2021 IEEE Work- shop on Wide Bandgap Power Devices and Appli- cations in Asia (WiPDA Asia), Wuhan, China, 2021: 344-349.

[18] Guo Zhehui, Li Hui. dv/dt sensing-based short-circuit protection for medium-voltage SiC MOSFETs[J]. IEEE Transactions on Power Electronics, 2023, 38(9): 10554-10558.

[19] Kochoska S, Guitart J R, Richert L, et al. Gate current peaks due to CGD overcharge in SiC MOSFETs under short-circuit test[C]//2023 35th International Sym- posium on Power Semiconductor Devices and ICs (ISPSD), Hong Kong, China, 2023: 246-249.

Abstract SiC MOSFETs feature low on-resistance, low switching losses, high switching frequencies, and excellent reverse recovery characteristics. Fast switching speeds can lead to severe switching overshoot, oscillations, and crosstalk. In addition, the short-circuit tolerance is weak, and the protection circuit requires a faster response time. Additionally, the fast response and anti-noise capabilities of the short-circuit protection circuit are challenging to balance at higher switching rates. Therefore, this paper proposes a driving and protection strategy based on multi-stage voltage level control. Driving strategy solves the cooperative optimization of multiple objectives in the switching trace. In terms of protection, a detection circuit with on-state voltage compensation is proposed, which reduces the influence of temperature and load changes on detection accuracy. In addition, a two-stage gate voltage reduction method is proposed to improve the time of fault detection in the blind zone and reduce the influence of interference noise. The soft turn-off technology is used to suppress the turn-off overvoltage.

Firstly, the mathematical relationship model between the gate voltage and the voltage/current change rate of the switching process is established. Changing the driving voltage level enables effective control of the current and voltage change rate in the switching process. Switching overshoot Did and Dvds are suppressed, and the oscillation amplitude is reduced. Secondly, after analyzing the problems of desaturation detection and di/dt detection methods for current faults in SiC MOSFETs, this paper proposes an improved detection circuit for desaturation voltage, incorporating a compensation circuit to mitigate the impact of temperature changes and load fluctuations. Finally, a multi-level drive circuit and an improved protection method are proposed for SiC MOSFET.

A double-pulse experiment and a short circuit test verify the designed multi-level driver. In terms of switching trace control, the multi-level driver employs a three-stage variable voltage control strategy to regulate the gate charge and discharge current at various switching stages. It can realize the multi-objective collaborative optimization of the switching trace. The overshoot and oscillation of SiC MOSFETs are effectively suppressed while achieving fast switching speed and low loss. In terms of short-circuit protection, a detection circuit is proposed to increase the conduction voltage of the compensation loop, which reduces the influence of temperature and load changes. The detection accuracy is greatly improved. The two-stage inverse time protection method enables the independent detection and protection of overcurrent and short-circuit faults. The two-stage turn-off method limits the increase of short-circuit current. The detection time of blind areas under short-circuit faults can be increased to reduce the influence of interference noise, and the soft turn-off technology can be used to suppress the turn-off overvoltage and oscillation.

keywords:SiC MOSFET, multi-level driver, switching trace, short-circuit protection, soft turn-off

DOI: 10.19595/j.cnki.1000-6753.tces.242096

中图分类号:TM46

国家电网公司科技资助项目(5500-202358691A-3-3-JC)。

收稿日期 2024-11-21

改稿日期 2025-04-22

白建成 男,1988年生,硕士研究生,研究方向为大功率可关断器件的驱动和保护及特高压柔性直流输电技术。E-mail: baijiancheng@epri.sgcc.com.cn(通信作者)

客金坤 男,1986年生,硕士研究生,研究方向为大功率IGBT器件特性及数字驱动芯片技术。E-mail: kejinkun@epri.sgcc.com.cn

(编辑 陈 诚)