图1 SiC MOSFET体二极管双极退化机制

Fig.1 Bipolar degradation mechanism of SiC MOSFET body diodes

摘要 双极退化不仅阻碍了碳化硅(SiC)MOSFET体二极管的应用,还制约了高压大功率SiC MOSFET器件的发展。研究变换器中造成SiC MOSFET体二极管双极退化的应力等效评估方法,并掌握其退化特性,对指导SiC器件应用、提升器件及系统运行可靠性具有重要意义。该文在可靠性测试标准基础上,提出一种基于脉冲电流应力调控的SiC MOSFET体二极管双极退化应力等效评估方法。并通过实验研究,掌握了脉冲电流等级、芯片结温、脉冲宽度对SiC MOSFET体二极管双极退化的影响规律。实验结果表明,当脉冲电流等级与芯片结温同时接近额定限值时,发生了明显的双极退化,且随着脉冲宽度的增大,退化程度加深。而在小脉冲电流、高芯片结温与大脉冲电流、低芯片结温两种条件下,双极退化现象均不明显。实验结果一方面验证了该文所提评估方法的适用性;另一方面也为SiC器件的应用和推广提供了性能提升指导与实验支撑。

关键词:SiC MOSFET体二极管 双极退化 脉冲电流应力 应用指导

近年来,随着电力电子技术的蓬勃发展,以碳化硅(SiC)MOSFET为代表的第三代宽禁带半导体器件逐步替代硅基(Si)器件,开始广泛应用于各种领域[1-5]。在变换器中,为了获得更好的反向特性,通常反并联肖特基二极管。随着制造工艺的进步,SiC MOSFET反向特性显著提升,开始逐渐取代肖特基二极管,作为续流回路在功率变换电路中得到了广泛应用。目前已有商用SiC功率模块在尝试无反并联二极管的封装设计,简化了电路拓扑,极大地减小了回路寄生参数,改善了电磁干扰(Electromagnetic Interference, EMI)环境[6-7]。然而,体二极管在正向偏置时,处于双极性运行条件,易激发漂移区缺陷而发生双极退化现象,影响SiC MOSFET的正向及反向特性[8-9],可能造成器件损耗增大、阻断能力下降等可靠性和鲁棒性问题[10],阻碍了SiC器件应用的推广。因此,研究SiC MOSFET体二极管双极退化评估方法,并分析其退化特性,对指导SiC器件开发、应用有着重要意义。

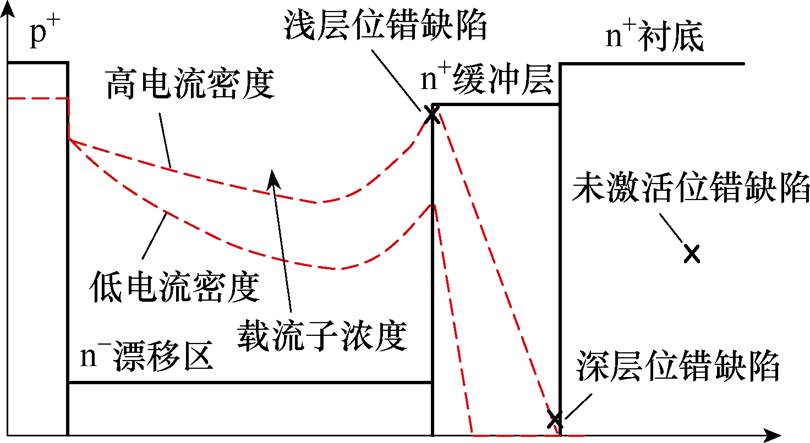

针对SiC MOSFET体二极管的可靠性评估,其关键在于激发SiC芯片漂移区或衬底可能存在的缺陷。当SiC MOSFET体二极管导通时,电子和空穴载流子注入或激发后复合,释放能量使SiC晶体上早先存在的基面位错(Basal Plane Dislocation, BPD)触发,在高温应力的作用下,BPD发生滑移,分裂为Si核和C核两个部分位错,其中Si核部分位错由于电流传导而滑动,会导致堆垛层错(Stacking Fault, SF)在外延层中蔓延至芯片表面[11],具体过程如图1所示。SF减小了芯片有源区面积,导致载流子寿命显著降低,不仅增加了反向偏置的漏电流,影响器件的阻断特性,还会使局部电流密度升高,导通压降增大,器件的可靠性下降[12]。高压SiC MOSFET的漂移区更厚,缺陷更多,从而导致其体二极管可靠性更差,严重阻碍了高压大功率SiC MOSFET的发展[13]。

图1 SiC MOSFET体二极管双极退化机制

Fig.1 Bipolar degradation mechanism of SiC MOSFET body diodes

SiC MOSFET体二极管的可靠性评估,一方面旨在反馈指导SiC器件开发,即通过迭代优化工艺,提升体二极管性能以及减少缺陷。这需要高分辨率的退化现象以及尽可能短的评估周期。在退化现象分辨率不高的情况下,需要通过提高良品阈值来保证器件的高可靠性,这可能会导致良品率低,造成成本增加。尽可能短的评估周期可以在不造成器件过应力失效的前提下快速掌握所测试工艺下的缺陷情况。另一方面进行可靠性评估可以指导SiC器件的应用,为应用端划定保证器件高可靠、高性能的许用阈值。标准高效的SiC MOSFET体二极管可靠性评估方法不仅可以支撑高可靠SiC器件研发,也是SiC器件长期稳定可靠运行的重要保障。

目前,已有大量针对SiC MOSFET器件体二极管双极退化的实验研究,包括直流应力、脉冲应力、重复浪涌应力等。2013年,T. Funaki在直流应力下发现SiC MOSFET的体二极管双极退化主要发生在应力早期阶段[14]。对于直流应力,2019年和2021年还有学者在直流功率循环的测试过程中,发现降温过程注入的测温小电流也会引发双极退化现象,导致体二极管压降的温度特性曲线漂移[15-16]。这些实验中SiC MOSFET器件的最高结温通常为安全工作区上限。2024年,Cheng Zijun等将体二极管直流应力中的栅极偏置应力和温度应力提取为高温栅偏应力,并进行了分离应力实验,实验结果表明,体二极管压降和导通电阻的增大是由于体二极管双极退化导致而非栅偏应力[17]。2020年,R. Green等对不同厂家的商用SiC MOSFET体二极管进行了直流应力和脉冲应力测试,有两款商用器件发生了显著的双极退化,实验结果表明,由于工艺分散性,不同厂商不同批次器件存在较大分散性[18]。针对脉冲应力,2014年,有学者将SiC MOSFET体二极管置于升-降压电路中,使器件体二极管承受脉冲电流应力,经过10 000 h的连续运行,没有发现双极退化现象[19]。但其运行结温较低,仅为100℃。2021年,德国开姆尼兹工业大学的J. Lutz等研究了重复浪涌电流和直流应力下商用SiC MOSFET体二极管的双极退化现象。在直流应力下未观察到明显的双极退化,而电流等级更高的浪涌电流会造成显著的双极退化[20]。但是,浪涌电流不可避免地会造成一定程度的封装退化,可能会被误判为发生了双极退化[21]。综上所述,虽然已有不同应力下SiC MOSFET体二极管双极退化的实验研究,但存在不一致的实验结果,如直流应力下的不同退化情况。这可能是器件发展工艺提升,在外延生长期间减少了位错缺陷的形成以及增长,使得较小的应力不足以在早期激发双极退化的发展。脉冲电流应力更贴近实际工况,且与直流应力相比,在相同芯片结温下可对器件施加更大的电流应力。

电流密度和温度被认为是造成双极退化的关键应力。2020年,A. Iijima等在改变电流密度和温度的条件下,估计了4H-SiC PiN二极管中堆垛层错扩张/收缩的临界条件,认为随着电流密度的减小与实验温度的升高,堆垛层错不断收缩,双极退化现象减弱[22]。与之相反,同年Yang Long等研究了温度对基面位错从衬底向外延生长的影响,结果表明随着温度的升高,漂移区的基面位错密度显著增加,提高了双极退化现象发生的概率[23]。2023年,Wu Yifei等提出采用较大的电流脉冲可以确保器件双极退化现象完全发生[24]。

虽然以上研究考察了不同工况、不同应力下的双极退化现象,但对综合应力作用的分析不足,导致对不同工况应力造成双极退化的影响规律尚不明确。同时,由于应力条件不一,在现有研究中存在不一致结论。2022年,IEC 63275-2: 2022首次规定了双极退化实验的标准实验条件[25],但目前参照标准条件进行的双极退化实验研究较少。因此,有必要按照标准内容,研究SiC MOSFET体二极管双极退化评估方法,提高激发缺陷发展的灵敏度,并掌握其双极退化特性。

为尽可能地仅触发体二极管双极退化而不引发其他退化机制,同时贴近体二极管的实际运行工况,本文首先参照标准搭建了基于脉冲电流应力调控的加速老化实验平台,并讨论了脉冲电流等级、等效脉冲宽度、脉冲频率与SiC器件结温间的耦合关系。然后基于“测量-应力-测量”评估逻辑,分析了电流等级、等效脉冲宽度和芯片结温三种应力对体二极管双极退化的影响规律,并提出了可能的退化机理。最后提出了一种体二极管双极退化脉冲应力评估方法,并给出了SiC器件体二极管的许用阈值。所提脉冲应力评估方法依照标准,实现了在短期内充分激发漂移区或衬底缺陷发展,获得明显的双极退化现象。为反馈指导器件开发、迭代优化芯片工艺提供了理论与实验支撑,并具有普适性,可服务于高压SiC器件研发。采用所提脉冲应力评估方法也为应用端测定了许用阈值,对保障SiC器件高性能高可靠应用具有重要意义。

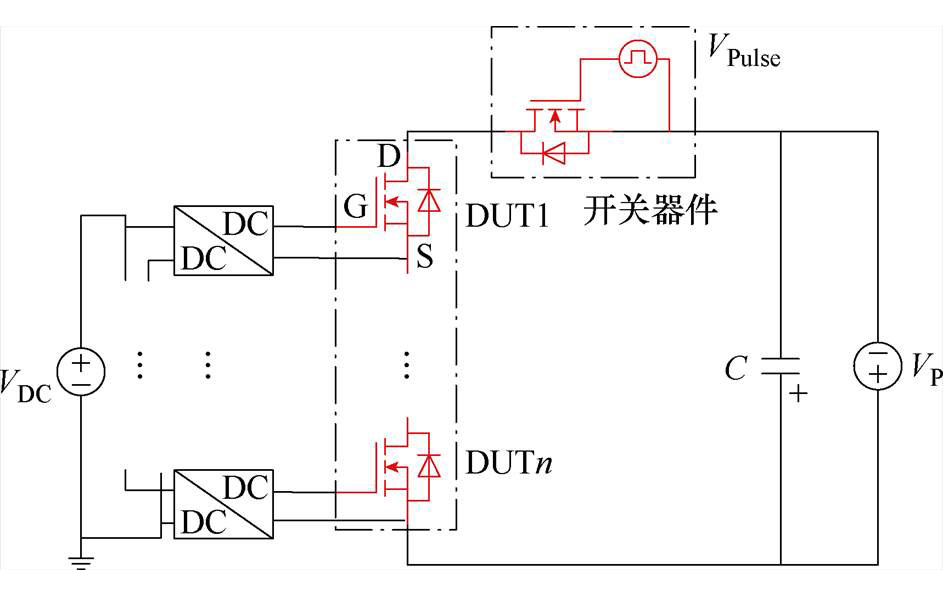

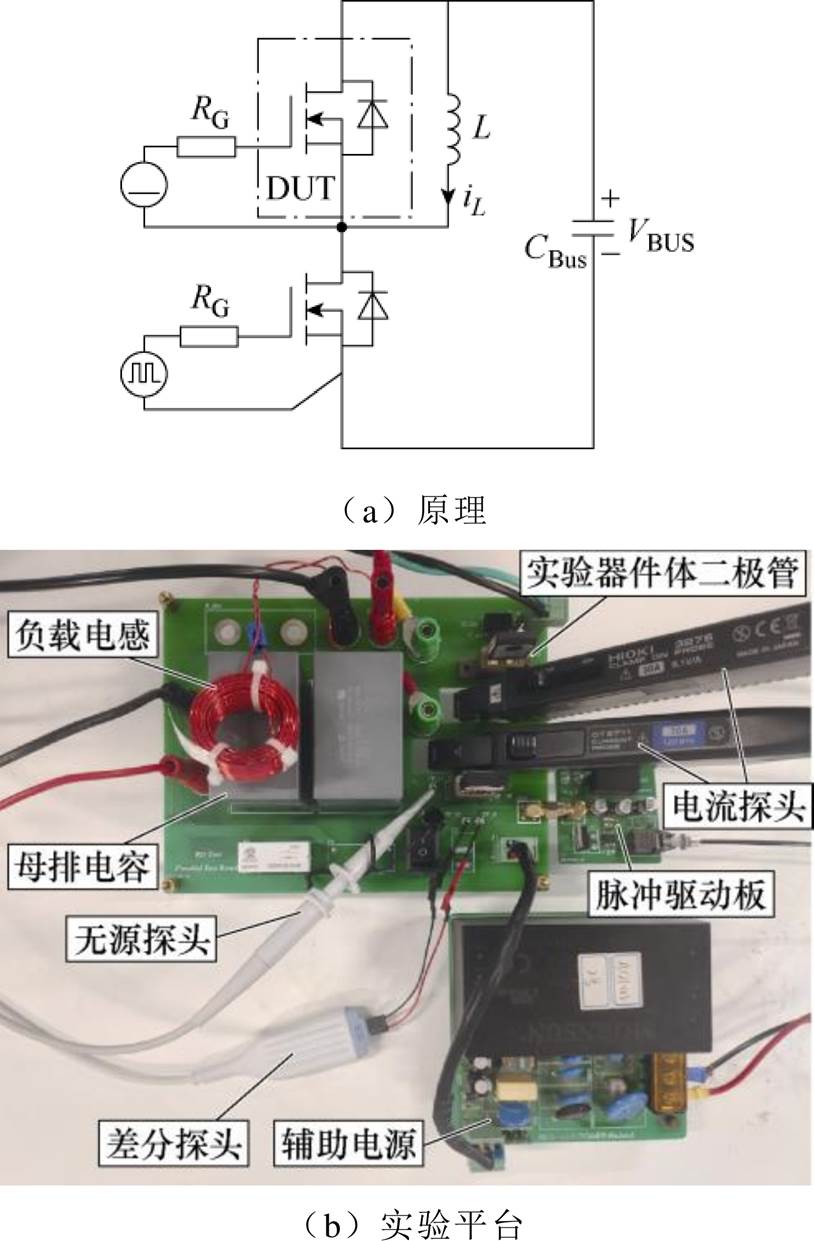

脉冲实验平台电路原理如图2所示。图中,VDC为直流源电压,DC-DC为降压电源模块,被测器件(Devices Under Test, DUT)为SiC MOSFET实验器件,D为器件漏极,G为器件栅极,S为器件源极,C为母线电容,VP为工作在电压源模式的功率源电压,开关器件为开尔文连接的SiC MOSFET,VPulse为脉冲驱动部分输出电压,其中脉冲驱动部分包括直流源、光纤信号发生器、带有DC-DC隔离电源模块的驱动板。

图2 脉冲实验平台电路原理

Fig.2 Circuit principle of pulse experimental bench

脉冲实验平台如图3所示。在脉冲模式下,功率源两端并联母线电容,以保证输出恒定的直流电压。主回路串联一个SiC MOSFET作为开关器件,直流源和光纤信号发生器通过驱动板对开关器件栅极施加脉冲驱动电压信号,通过开关器件不断动作,保证在实验器件体二极管上施加脉冲电流应力。直流源通过DC-DC降压电源模块,对栅源极施加恒定负压,保证在实验过程中沟道完全关断,只有体二极管通流[26]。DC-DC模块可以隔离电压,防止功率回路器件发生由于串联导致的驱动共地问题。

图3 脉冲实验平台

Fig.3 Pulse experimental bench

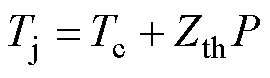

脉冲实验平台采用风扇散热,热电偶监控实验器件和开关器件的温度,通过热网络法计算芯片结温,保证实验过程中器件结温不超过手册限值,防止发生热失效。计算公式为

(1)

(1)

式中,Tj为器件结温;Tc为器件壳温;Zth为热阻;P为器件发热功率。

由于散热硅胶垫和热电偶影响,器件热阻Zth远大于手册上给出的数值。为得到准确的器件热阻,首先测量不同实验器件体二极管的温度校准曲线,之后在体二极管上施加恒定电流,得到此时发热功率和稳态壳温,再根据温度校准曲线计算得到器件热阻Zth。

为研究造成体二极管双极退化的关键应力以及体二极管双极退化特性,本文通过控制变量的方法调整脉冲频率及占空比,保证在改变某一实验条件时,其余实验条件不变。

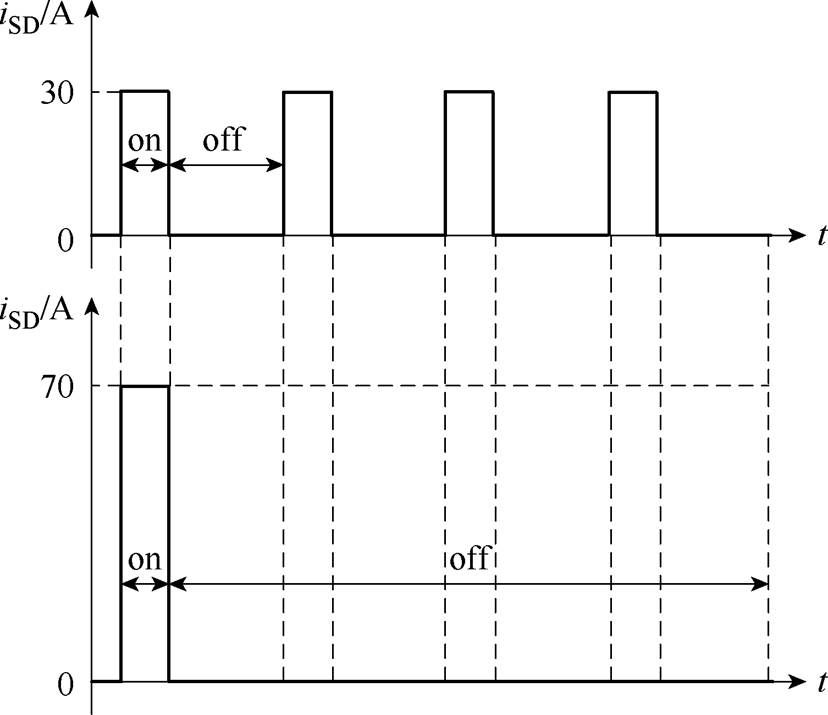

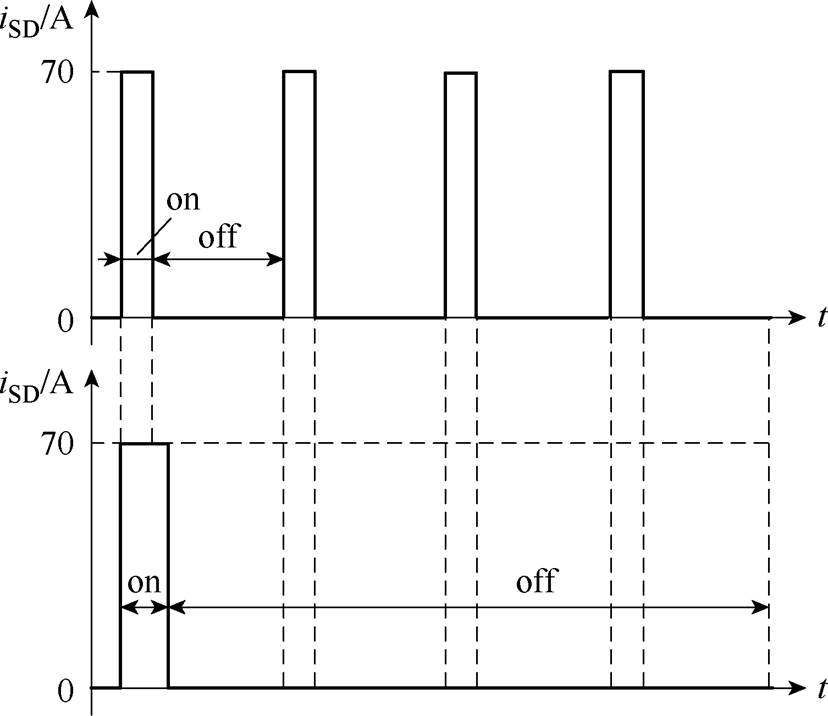

如图4所示为控制等效脉冲宽度与芯片结温不变,改变电流等级的脉冲电流示意图。当改变频率及占空比时,脉冲电流的脉冲宽度不变,即实际逆变电路中不同桥臂切换导通的时间间隔不变,也就是脉冲宽度不变,保证实验过程中芯片结温一致,仅改变了脉冲电流等级。因此,当调整频率及占空比时,仅改变了实验过程中单位时间内的累计导通时间。根据双极退化产生机理,在堆垛层错完全扩展后,双极退化程度将不再加深。而累计导通时间只会影响双极退化现象出现的早晚,对于是否会出现双极退化以及双极退化程度不会产生影响。因此在对比不同电流等级对双极退化特性的影响时,可以忽略频率及占空比的影响。

图4 电流等级对比实验脉冲电流示意图

Fig.4 Schematic diagram of pulse current in current level comparison experiment

控制等效脉冲宽度与电流等级不变,改变芯片结温的脉冲电流示意图如图5所示,与电流等级对比实验类似,当改变频率及占空比时,脉冲电流的脉冲宽度与电流等级均保持不变,仅改变了芯片结温。

图5 芯片结温对比实验脉冲电流示意图

Fig.5 Schematic diagram of pulse current in chip junction temperature comparison experiment

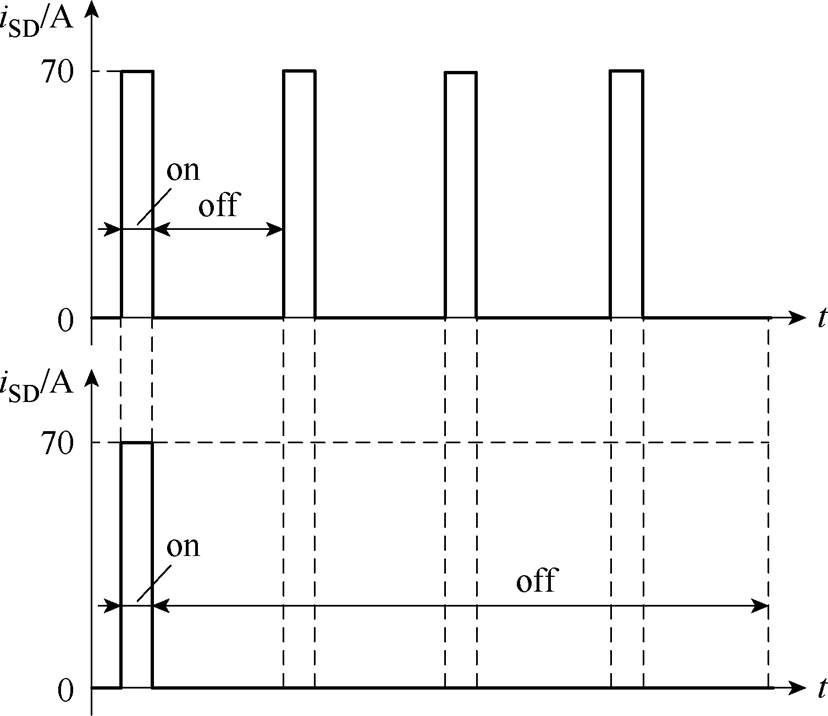

仅改变等效脉冲宽度的脉冲电流示意图如图6所示,通过调整频率及占空比,改变了脉冲电流宽度,即脉冲宽度,而电流等级与芯片结温均保持不变,保证了实验过程中对无关变量的控制,仅考察脉冲宽度改变的影响。

图6 脉冲宽度对比实验脉冲电流示意图

Fig.6 Schematic diagram of pulse witch comparison experiment

综上所述,通过脉冲电流应力调控方法实现了对电流等级、等效脉冲宽度和芯片结温三种应力的单一应力调控。

通过测量SiC MOSFET在应力前后的静动态特性,评估器件体二极管双极退化特性。

1)静态参数及动态参数测量

单次应力完成后将器件静置一段时间,保证器件内部不存在热量积累。静置结束后,使用功率分析仪测试静态参数,通过双脉冲测试获得实验器件体二极管的反向恢复曲线,提取反向恢复电荷。功率分析仪及双脉冲测试平台分别如图7、图8所示。

图7 功率分析仪

Fig.7 Power aralyzer

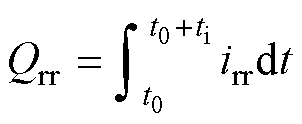

实验过程中,对体二极管饱和压降、正向通态电阻进行测量,根据IEC 60747-2: 2016标准给出的计算方法[27],提取体二极管反向恢复电荷Qrr,计算公式为

图8 双脉冲测试原理及实验平台

Fig.8 Double pulse test principle and platform

(2)

(2)

式中,irr为反向恢复电流;t0为反向恢复电流过零点时刻;ti为反向恢复电流减小到2%反向恢复电流峰值时刻。

2)实验器件退化判据及实验结束判据

相关标准规定,单次实验结束后,若器件的正向通态电阻RDS(on)、反向导通电压VSD变化超过初始值的20%,即认为器件失效。相关研究单位普遍采用100 h或48 h作为实验时间[28],本文初步设置实验时间为100 h。

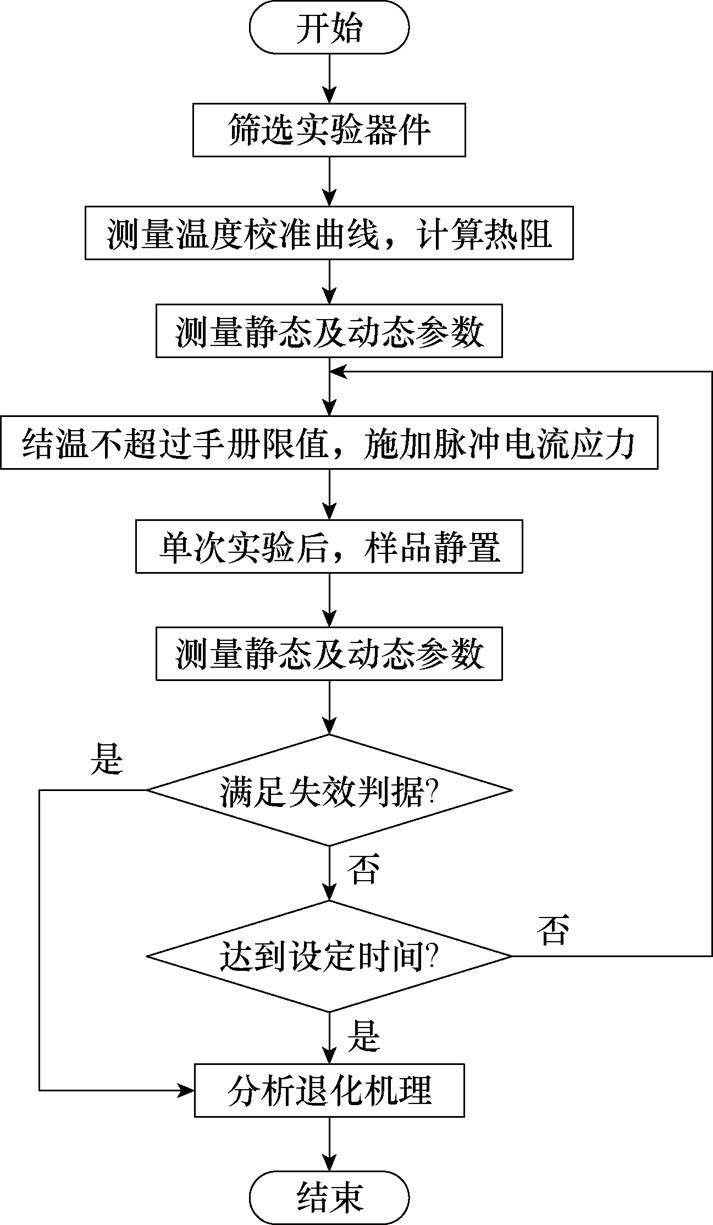

综上所述,进行双极退化加速等效实验期间,每隔固定时间对实验器件的静动态参数进行测量,直到实验器件满足失效判据或者达到设定的实验时间停止实验,实验流程如图9所示。

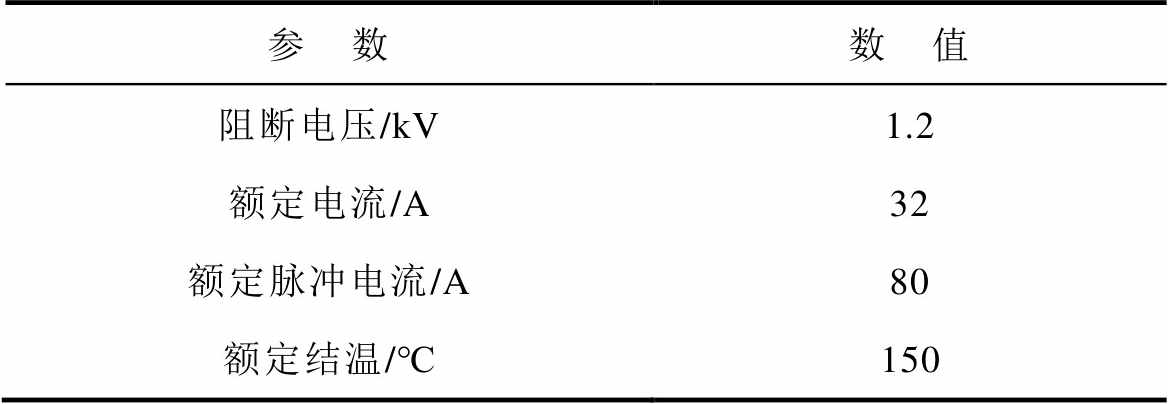

本文选择某商用1.2 kV SiC MOSFET为实验样本,实验参数见表1。

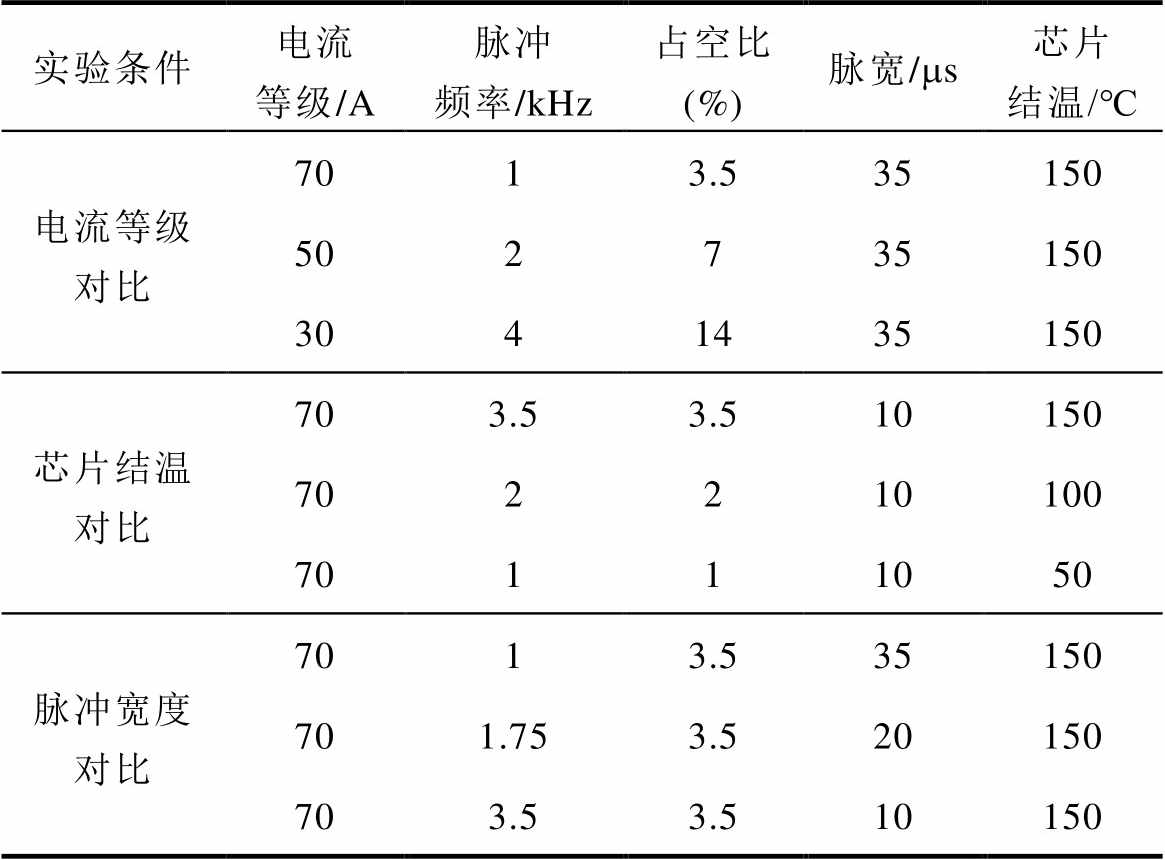

依照IEC 63275-2: 2022标准内容,在保证实验器件芯片结温不超过限值,防止实验过程中实验器件发生失效的前提下,施加额定脉冲电流,同时控制芯片结温在150℃以下。基于本文所提脉冲电流应力调控方法,研究单一应力对体二极管双极退化特性的影响,不同电流等级、芯片结温和脉冲宽度的对比实验条件见表2。

图9 实验流程

Fig.9 Experimental flow chart

表1 实验参数

Tab.1 Experimental device parameters

参 数数 值 阻断电压/kV1.2 额定电流/A32 额定脉冲电流/A80 额定结温/℃150

表2 不同工况应力下双极退化实验条件

Tab.2 Experimental conditions for bipolar degradation under different stress conditions

实验条件电流等级/A脉冲频率/kHz占空比(%)脉宽/ms芯片结温/℃ 电流等级对比7013.535150 502735150 3041435150 芯片结温对比703.53.510150 702210100 70111050 脉冲宽度对比7013.535150 701.753.520150 703.53.510150

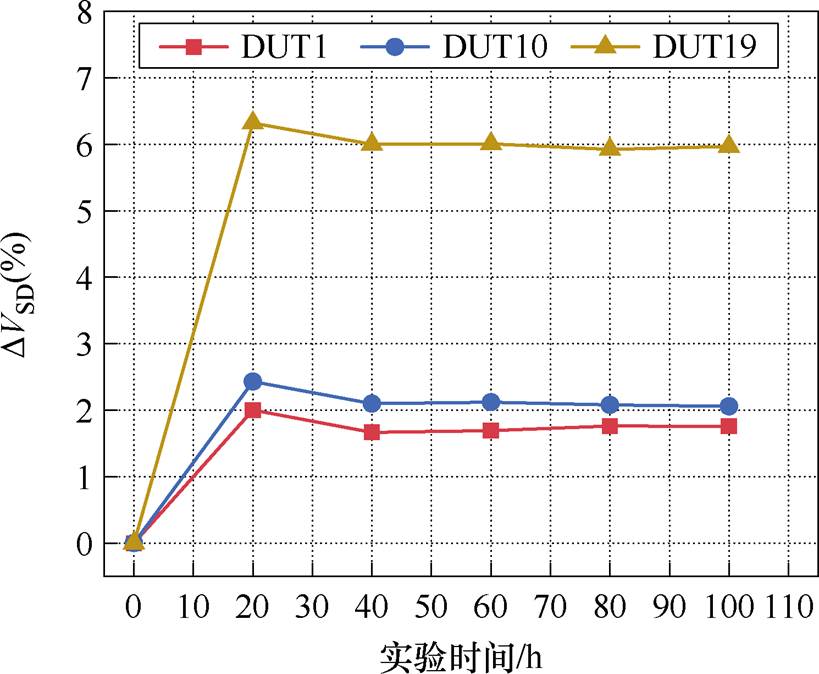

70 A/1 kHz/3.5%/35 ms/150℃下体二极管饱和压降的变化情况如图10所示。在脉冲电流应力下,实验器件的体二极管饱和压降均有明显增加,其中19号器件最为明显,在20 h时最大增加了0.26 V,偏离初始值6.32%。

图10 脉冲应力下体二极管饱和压降变化曲线

Fig.10 Voltage drop variation curves of body diode under pulse stress

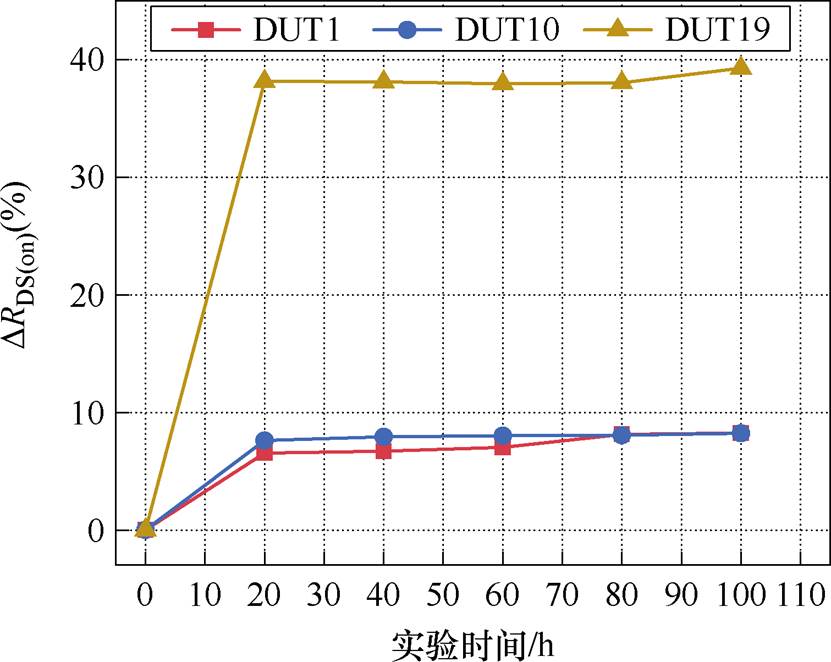

图11展示了正向通态电阻的变化情况。所有样本的正向通态电阻均有明显增加,同样是19号器件增加最大,20 h时增加了31.74 mW,相对初始值变化了39.26%,超过了20%,满足退化判据,体二极管发生了严重的双极退化。

图11 脉冲应力下MOSFET正向通态电阻变化曲线

Fig.11 MOSFET on state resistance variation curves under pulse stress

在相同的开关条件下对体二极管反向恢复特性进行测试,测试结果如图12所示,图12a中展示了反向恢复电流曲线峰值均有所增大,图12b中计算得到的反向恢复电荷也不断减少。这主要是由于堆垛层错捕获电荷,缩短了载流子寿命,不仅导致体二极管续流期间存储的电荷减少,反向恢复过程中的电荷也会减少,从而降低了反向恢复电流峰值,反向恢复电荷减少。

图12 脉冲应力下体二极管反向恢复特性

Fig.12 Reverse recovery characteristics of body diodes under pulse stress

实验结果表明,目前商用SiC MOSFET体二极管仍存在一定程度的双极退化现象,同时在实验进行的前几个小时内,双极退化可能就已经发展完全。因此,为了对比不同工况应力对双极退化现象的影响,后续对比实验每隔1 h测量实验器件静态及动态参数,直到参数不再变化。

2.2.1 不同电流等级

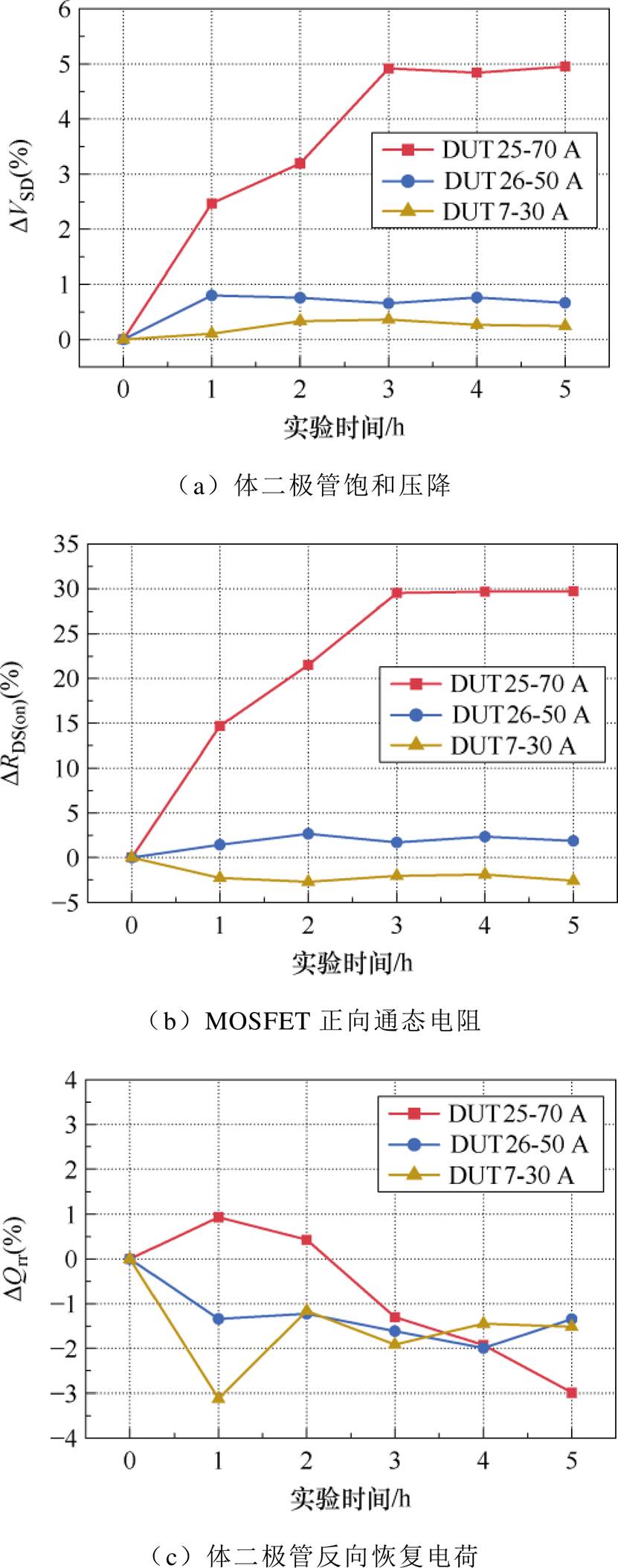

对比实验采用多个样本进行实验,选择静态参数变化最显著的样本进行对比。不同电流等级下器件参数变化曲线如图13所示。

图13a、图13b中,在70 A的脉冲电流下,体二极管饱和压降和正向通态电阻变化十分明显,分别增加了4.95%和29.7%。而在50 A和30 A的脉冲电流下,体二极管饱和压降变化不超过1%,正向通态电阻甚至出现了减小的趋势。

体二极管反向恢复电荷变化情况如图13c所示,在不同电流等级下,各实验器件的反向恢复电荷均有减少,但变化的趋势和数值大体相同。

图13 不同电流等级下器件参数变化曲线

Fig.13 Device parameter variation curves under different current levels

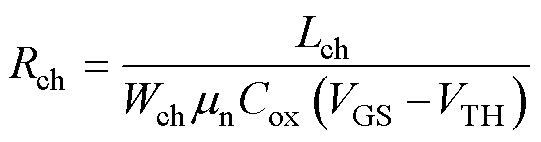

由于实验过程中对实验器件持续施加负栅压,在高温条件下,器件栅氧层发生退化,导致阈值电压减小,而在正向通态电阻的构成中,沟道电阻和积累区电阻与阈值电压相关,即

(3)

(3)

(4)

(4)

式中,Rch为沟道电阻;RA为积累区电阻;Lch为沟道长度;Wch为沟道宽度;mn为反型层沟道的电子迁移率;LA为积累区长度;WA为积累区宽度;mnA为积累区的电子迁移率;Cox为氧化层电容;VGS为栅极驱动电压;VTH为阈值电压。

由式(3)、式(4)可知,随着阈值电压降低,正向通态电阻不断减小。由于对比实验所施加的脉冲电流等级不断减小,载流子复合释放的能量未能激发堆垛层错完全扩展。因此,相比于堆垛层错,阈值电压对正向通态电阻的影响将更为显著,进而导致正向通态电阻有所减小。

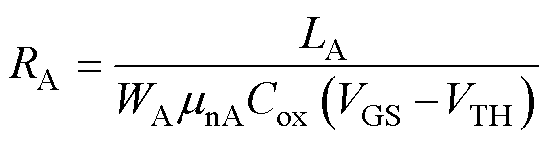

2.2.2 不同芯片结温

不同芯片结温下器件参数变化如图14所示。高温下体二极管饱和压降与正向通态电阻均有明显变化,分别增加了3.05%和17.21%。随着芯片结温降低,体二极管饱和压降几乎保持初始值不变,而正向通态电阻由于阈值电压的影响,则同样出现了减小的趋势。

如图14c所示,不同芯片结温下各实验器件的反向恢复电荷几乎没有减少,变化趋势和数值也大体相同。

2.2.3 不同脉冲宽度

不同脉冲宽度下器件参数变化如图15所示。尽管各实验条件下的脉冲宽度不同,但实验器件的体二极管饱和压降与正向通态电阻均有明显增加,随着脉冲宽度减小,体二极管饱和压降最大增加4.92%、4.63%、3.05%,正向通态电阻最大增加29.7%、22.42%、17.21%,变化幅值不断减小。

图14 不同芯片结温下器件参数变化曲线

Fig.14 Device parameter variation curves under different chip junction temperatures

图15c展示了体二极管反向恢复电荷的变化情况。不同于前两个对比实验,在不同脉冲宽度下,体二极管的反向恢复电荷出现了不同的变化趋势。在大脉冲宽度下,反向恢复电荷出现了减小的趋势,随着脉冲宽度的减小,反向恢复电荷的变化幅值也不断减小。

图15 不同脉冲宽度下器件参数变化曲线

Fig.15 Device parameter variation curves under different pulse width

通过对比实验,讨论了电流等级、芯片结温、脉冲宽度三种工况应力分别增大时,单一应力对双极退化特性的影响。实验结果表明,当脉冲电流等级和芯片结温同时接近额定值时,会发生明显的双极退化现象,且脉冲宽度越大,双极退化程度越深。

根据双极退化产生机理,当导通电流越大、温度越高时,少数载流子复合就会释放更多的能量,同时通流时间越长,也会使少数载流子复合的概率提高,间接增加了复合释放的能量,进而引起堆垛层错不断扩展,降低了漂移区内的电流密度,导致通态电压和电阻的增加。当电流、温度、通流时间都较小时,载流子复合概率低,释放的能量不足以克服堆垛层错扩展的能级[29],双极退化将很难发生。

虽然电流等级、芯片结温、脉冲宽度均会影响双极退化现象的发生,但对于体二极管饱和压降、正向通态电阻、反向恢复电荷等参数的影响存在差异。对于体二极管饱和压降和正向通态电阻,当电流等级从70 A降低到50 A,芯片结温从150℃降低到100℃时,参数变化百分比差值较大,表明电流等级与芯片结温在这个范围内变化时,会对双极退化程度造成很大影响。当电流等级从50 A降低到30 A,芯片结温从100℃降低到50℃时,参数变化百分比差值较小,可以认为工况应力在该区间内变化时,几乎不会对双极退化程度产生影响。这个现象主要与基面位错的存在位置有关。

电流等级和芯片结温主要通过体二极管双极运行过程中少数载流子复合释放能量,进而影响基面位错转变为堆垛层错,导致双极退化现象的发生。图16展示了体二极管通流期间载流子浓度的变化情况,其中电流等级在低电流密度时,主要影响漂移区的浅层位错缺陷转变为堆垛层错,而在高电流密度下,少数载流子的复合过程会出现在衬底附近甚至在衬底内部,复合释放的能量更大,从而导致衬底内部的深层位错缺陷转变为堆垛层错向漂移区扩展[30]。

图16 体二极管通流期间载流子浓度示意图

Fig.16 Schematic diagram of carrier concentration during the flow period of the body diode

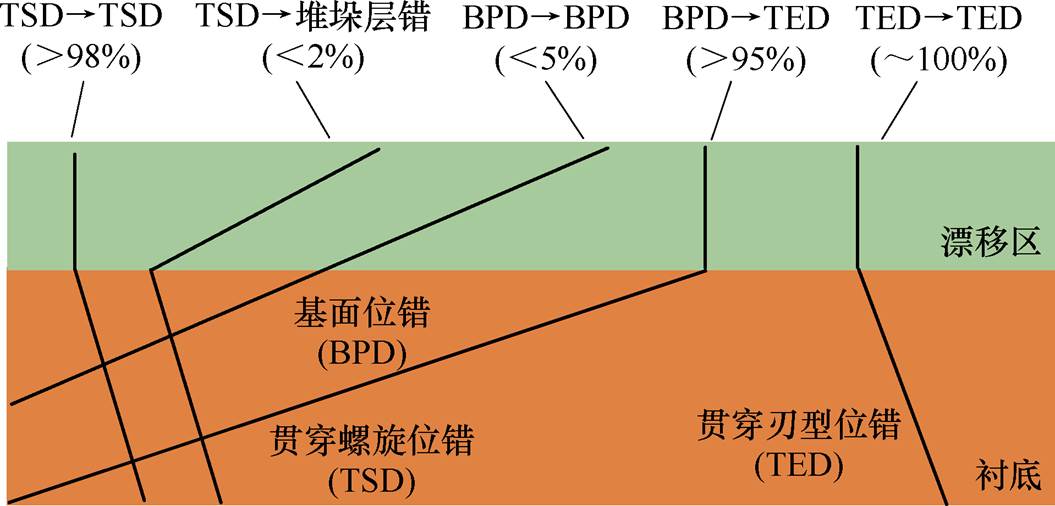

因此,4H-SiC生长过程中位错缺陷示意图如图17所示,尽管在工艺生产过程中,保证衬底的基面位错转化为漂移区中无影响的贯穿刃型位错,大大降低了漂移区中基面位错的密度,但在高电流密度下,依旧会引起衬底内部的基面位错转变为堆垛层错扩展,由于衬底内部基面位错的密度是漂移区密度的10倍以上,将会导致严重的双极退化现象[31]。同样地,芯片结温也有着类似影响,在低温条件下,仅会导致漂移区的堆垛层错扩展,而在高温条件下,会引起衬底的基面位错转变为堆垛层错扩展到漂移区[32]。

图17 4H-SiC生长过程中位错缺陷示意图

Fig.17 Schematic diagram of dislocation defects during the growth process of 4H SiC

结合对比实验结果,只有同时在接近额定脉冲电流以及额定芯片结温条件下,少数载流子复合释放的能量更高,激发衬底内部的高基面位错密度转变为高堆垛层错密度,出现了严重的双极退化现象。当持续减小脉冲电流等级或者芯片结温时,少数载流子复合释放的能量无法激发衬底的基面位错,只能使漂移区的基面位错转变为堆垛层错,从而导致双极退化程度较低且保持不变。而随着脉冲宽度由35 ms减小到10 ms,体二极管饱和压降与正向通态电阻变化百分比差值相差不大,双极退化程度减半,表明脉冲宽度在设定的范围内变化时,转化为堆垛层错的位错缺陷位置相同。

对于表2中反向恢复电荷参数,当改变电流等级与芯片结温时,变化差值不是十分明显,甚至在改变芯片结温时,差值几乎没有变化,但随着脉冲宽度改变,反向恢复电荷变化百分比均有所降低。由于体二极管的反向恢复电荷主要与载流子寿命有关,而堆垛层错边缘部分对于外部载流子寿命影响较大[33]。根据本文的对比实验结果,脉冲宽度越长,反向恢复电荷减小的幅值越大,主要是由于较长的脉冲宽度影响了堆垛层错的扩展过程,导致堆垛层错的轮廓周长更长,进而降低了漂移区的载流子寿命,使反向恢复电荷在不同脉冲宽度下出现了较大变化,而电流等级与芯片结温对堆垛层错的轮廓周长影响较小,导致反向恢复电荷参数变化不大。

根据以上实验结果的机理分析,在实际运行过程中,电流等级、芯片结温以及脉冲宽度均会对体二极管双极退化程度产生影响。只有同时保持高芯片结温和大电流脉冲,体二极管才会出现明显的双极退化现象;当单独降低电流等级或芯片结温时,体二极管参数均在初始值附近变化,基本没有发生双极退化现象。此外,随着脉冲宽度不断减小,体二极管双极退化程度不断降低,双极退化现象有所缓解。

因此在器件开发阶段,应采用额定脉冲电流等级和额定芯片结温作为体二极管评估条件,通过迭代优化工艺直至在额定条件下无双极退化现象发生。或根据实验研究获得脉冲电流和芯片结温的许用阈值,作为额定值标定的参考。

在实际应用中,SiC MOSFET体二极管可能遭遇瞬态过电流情况,工作在倍数于额定直流的脉冲电流工况,或远高于额定直流的浪涌电流工况,这就极有可能导致双极退化现象的发生。因此,在实际应用过程中,应尽量避免体二极管同时在高电流脉冲和高芯片结温的应用场景下工作。若在应用中器件体二极管易通过浪涌电流等高过电流脉冲,则应加强模块散热能力,降低芯片工作结温,尽量避免器件在额定芯片结温下工作。而为了提高器件热利用率,使器件可以长期可靠地工作在接近芯片额定结温,则需通过电路拓扑结构、驱动与保护的协同优化调控,尽可能降低体二极管过电流值,以抑制双极退化现象发生。当芯片结温及过电流值均无法调控时,应在控制逻辑上尽量减小脉冲宽度,即过电流时间,也可有效缓解双极退化现象。

本文搭建了模拟实际工况的SiC MOSFET体二极管脉冲电流应力加速老化等效实验平台,依照标准条件对目前商用SiC MOSFET器件进行了双极退化实验,研究了电流等级、芯片结温、脉冲宽度对SiC MOSFET体二极管双极退化的影响规律,提出了有效触发体二极管缺陷发展的脉冲电流应力评估方法,并从应用角度提出了体二极管双极退化抑制方法,综合以上研究,主要结论如下:

1)基于仅有体二极管导通的第三象限通流模式,搭建了脉冲电流应力加速老化实验平台,符合体二极管的实际运行情况。采用温度校准曲线及热阻计算方法控制结温,相比于传统控制壳温的实验方法,更能保证实验过程中温度参数的一致性,避免实验器件由于结温越限发生失效。提出了脉冲电流应力调控方法,实现了单一应力调控。

2)开展了双极退化实验,获得了电流等级、芯片结温、脉冲宽度对双极退化的影响规律,目前商用SiC MOSFET器件在接近额定脉冲电流以及额定芯片结温条件下,存在明显的双极退化现象。由于位错缺陷位置的影响,电流等级与芯片结温的变化对双极退化程度影响较大,导致体二极管饱和压降最大变化差值为4.95%、3.05%,正向通态电阻最大变化差值为29.7%、17.21%。脉冲宽度的影响则相对较小,参数变化差值为1.91%及12.5%。由于脉冲宽度与堆垛层错的轮廓周长有关,导致不同脉冲宽度下,反向恢复电荷参数变化有较大差异,而电流等级与芯片结温则对堆垛层错的轮廓周长影响较小,反向恢复电荷参数的变化不大。

3)在SiC器件开发阶段,应采用额定脉冲电流等级和额定芯片结温作为体二极管评估条件,通过迭代优化工艺直至在额定条件下无双极退化现象发生。或根据实验研究获得脉冲电流和芯片结温的许用阈值,作为额定值标定的参考。

4)结合双极退化实验结果,从应用角度提出了体二极管双极退化的抑制方法。在实际应用中,需避免体二极管工作在高电流脉冲和高芯片结温的应用场景下,对于浪涌电流等高过电流脉冲,应加强模块散热能力,避免器件工作在额定芯片结温附近;而为了提高器件热利用率,则需通过电路拓扑结构、驱动与保护的协同优化调控,尽可能降低体二极管过电流值,以抑制双极退化现象发生。此外,在控制逻辑上尽量减小体二极管的脉冲宽度,也可有效缓解双极退化现象。

参考文献

[1] 盛况, 任娜, 徐弘毅. 碳化硅功率器件技术综述与展望[J]. 中国电机工程学报, 2020, 40(6): 1741- 1753.

Sheng Kuang, Ren Na, Xu Hongyi. A recent review on silicon carbide power devices technologies[J]. Proceedings of the CSEE, 2020, 40(6): 1741-1753.

[2] 张少昆, 孙微, 范涛, 等. 基于分立器件并联的高功率密度碳化硅电机控制器研究[J]. 电工技术学报, 2023, 38(22): 5999-6014.

Zhang Shaokun, Sun Wei, Fan Tao, et al. Research on high power density silicon carbide motor controller based on parallel connection of discrete devices[J]. Transactions of China Electrotechnical Society, 2023, 38(22): 5999-6014.

[3] 李锦, 党恩帅, 范雨顺, 等. 一种碳化硅与硅器件混合型三电平有源中点钳位零电压转换软开关变流器[J]. 电工技术学报, 2024, 39(8): 2496-2510.

Li Jin, Dang Enshuai, Fan Yushun, et al. A hybrid three-level active-neutral-point-clamped zero-voltage transition soft-switching converter with silicon carbide and silicon devices[J]. Transactions of China Electrotechnical Society, 2024, 39(8): 2496-2510.

[4] 徐浩东, 罗嗣勇, 毕闯, 等. 基于SiC MOSFET同步Buck DC-DC变换器的宽频混合EMI滤波器设计[J]. 电工技术学报, 2024, 39(10): 3060-3069.

Xu Haodong, Luo Siyong, Bi Chuang, et al. Design of wide-frequency hybrid EMI filter for SiC MOSFET synchronous Buck DC-DC converter[J]. Transactions of China Electrotechnical Society, 2024, 39(10): 3060-3069.

[5] 马荣耀, 唐开锋, 潘效飞, 等. 车用碳化硅功率模块的电热性能优化与评估[J]. 电源学报, 2024, 22(3): 78-86.

Ma Rongyao, Tang Kaifeng, Pan Xiaofei, et al. Electro-thermal performance optimization and evalu- ation of automotive SiC power module[J]. Journal of Power Supply, 2024, 22(3): 78-86.

[6] Wang Zhaohui, Zhang Junming, Wu Xinke, et al. Evaluation of reverse recovery characteristic of silicon carbide metal-oxide-semiconductor field- effect transistor intrinsic diode[J]. IET Power Elec- tronics, 2016, 9(5): 969-976.

[7] 赵正平. SiC电力电子学产业化技术的创新发展(续)[J]. 半导体技术, 2022, 47(4): 249-265, 287.

Zhao Zhengping. Innovation and development on the industrialization technology of SiC power electronics (continued)[J]. Semiconductor Technology, 2022, 47(4): 249-265, 287.

[8] Agarwal A, Fatima H, Haney S, et al. A new degradation mechanism in high-voltage SiC power MOSFETs[J]. IEEE Electron Device Letters, 2007, 28(7): 587-589.

[9] Ni Ze, Lü Xiaofeng, Yadav O P, et al. Overview of real-time lifetime prediction and extension for SiC power converters[J]. IEEE Transactions on Power Electronics, 2020, 35(8): 7765-7794.

[10] Li Kaiwei, Sun Pengju, Wu Shuo, et al. Experimental investigation on avalanche robustness of SiC MOSFETs in the aging process[C]//2022 4th Inter- national Conference on Power and Energy Tech- nology (ICPET), Beijing, China, 2022: 1227-1231.

[11] Kimoto T, Cooper J A. Characterization Techniques and Defects in Silicon Carbide[M]. Solaris south Tower, Singapore: John Wiley & Sons Singapore Pte J, Ltd, 2014: 125-187.

[12] Levinshtein M E, Ivanov P A, Palmour J W, et al. Bipolar degradation of high voltage 4H-SiC PiN diodes in pulse regime[J]. Materials Science Forum, 2011, 679/680: 539-542.

[13] Lachichi A, Mawby P. Modeling of bipolar degra- dations in 4H-SiC power MOSFET devices by a 3C-SiC inclusive layer consideration in the drift region[J]. IEEE Transactions on Power Electronics, 2022, 37(3): 2959-2969.

[14] Funaki T. A study on performance degradation of SiC MOSFET for burn-in test of body diode[C]//2013 4th IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Rogers, AR, USA, 2013: 1-5.

[15] Hoffmann F, Soler V, Mihaila A, et al. Power cycling test on 3.3kV SiC MOSFETs and the effects of bipolar degradation on the temperature estimation by VSD-method[C]//2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 2019: 147-150.

[16] Fu Jianzhi, Mansour W, Kapino G, et al. Comparative investigation of body diode reliability of 1, 2-kV SiC power switches for the temperature measurement[C]// 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 2021: 2224-2228.

[17] Cheng Zijun, Lü Mingen, Zhao Dongsheng, et al. Bipolar degradation of SiC MOSFET body diode under constant current stress[C]//2024 25th Inter- national Conference on Electronic Packaging Tech- nology (ICEPT), Tianjin, China, 2024: 1-5.

[18] Green R, Lelis A J, Nouketcha F L. Effects of pulsed and DC body-diode current stress on the stability of 1200-V SiC MOSFET I-V characteristics[J]. Materials Science Forum, 2020, 1004: 1027-1032.

[19] Bolotnikov A, Glaser J, Nasadoski J, et al. Utilization of SiC MOSFET body diode in hard switching applications[J]. Materials Science Forum, 2014, 778/ 779/780: 947-950.

[20] Palanisamy S, Basler T, Lutz J, et al. Investigation of the bipolar degradation of SiC MOSFET body diodes and the influence of current density[C]//2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2021: 1-6.

[21] Pu Shi, Yang Fei, Vankayalapati B T, et al. Aging mechanisms and accelerated lifetime tests for SiC MOSFETs: an overview[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2022, 10(1): 1232-1254.

[22] Iijima A, Kimoto T. Estimation of the critical condition for expansion/contraction of single Shockley stacking faults in 4H-SiC PiN diodes[J]. Applied Physics Letters, 2020, 116(9): 092105.

[23] Yang Long, Zhao Lixia, Wu Haiwang. Effect of temperature on conversion of basal plane dislocations to treading edge dislocations during 4H-SiC homoepitaxiy[J]. Journal of Crystal Growth, 2020, 531: 125360.

[24] Wu Yifei, Li Chengxi, Ran Li, et al. Evaluation of bipolar degradation in SiC MOSFETs for converter design[C]//2023 IEEE Energy Conversion Congress and Exposition (ECCE), Nashville, TN, USA, 2023: 5359-5365.

[25] IEC. Semiconductor devices-reliability test method for silicon carbide discrete metal-oxide semiconductor field effect transistors—part 2: test method for bipolar degradation by body diode operating: IEC 63275-2[S]. Geneva: International Electrotechnical Commission, 2022.

[26] 陈杰, 邓二平, 赵子轩, 等. 不同老化试验方法下SiC MOSFET失效机理分析[J]. 电工技术学报, 2020, 35(24): 5105-5114.

Chen Jie, Deng Erping, Zhao Zixuan, et al. Failure mechanism analysis of SiC MOSFET under different aging test methods[J]. Transactions of China Elec- trotechnical Society, 2020, 35(24): 5105-5114.

[27] IEC. Semiconductor devices-part 2: discrete devices- rectifier diodes: IEC 60747-2 Ed. 3.0 b: 2016[S]. Geneva: International Electrotechnical Commission, 2016.

[28] 张秋, 闫美存. SiC MOSFET体二极管双极退化可靠性试验方法研究[J]. 信息技术与标准化, 2022(9): 36-39.

Zhang Qiu, Yan Meicun. Research on reliability test method for bipolar degradation of SiC MOSFET body diode[J]. Information Technology & Standardization, 2022(9): 36-39.

[29] Iijima A, Kimoto T. Electronic energy model for single Shockley stacking fault formation in 4H-SiC crystals[J]. Journal of Applied Physics, 2019, 126(10): 105703.

[30] Hayashi S, Yamashita T, Senzaki J, et al. Relationship between depth of basal-plane dislocations and expanded stacking faults by application of forward current to 4H-SiC PiN diodes[J]. Applied Physics Express, 2019, 12(5): 051007.

[31] Konishi K, Yamamoto S, Nakata S, et al. Stacking fault expansion from basal plane dislocations converted into threading edge dislocations in 4H-SiC epilayers under high current stress[J]. Journal of Applied Physics, 2013, 114(1): 014504.

[32] Nishihara Y, Kamei K, Momose K, et al. Comparative evaluation of forward voltage degradation due to propagating and converted basal plane dislocations[J]. Materials Science Forum, 2018, 924: 143-146.

[33] Nakayama K, Sugawara Y, Tsuchida H, et al. Drift phenomena of forward and reverse recovery characteristics in 0001 4H-SiC PiN diode[J]. Japanese Journal of Applied Physics, 2011, 50(4S): 04DF04.

Abstract The bipolar degradation phenomenon hinders the application of silicon carbide (SiC) MOSFET body diodes and restricts the development of high-voltage, high-power SiC MOSFET devices. Investigating stress-equivalent evaluation methods for bipolar degradation in converter applications and understanding its degradation characteristics are essential for guiding SiC device applications and enhancing the operational reliability of devices and systems.

Building upon existing reliability testing standards, this paper proposes a pulse current stress-regulated equivalent evaluation method for bipolar degradation in SiC MOSFET body diodes. Through experimental investigations, the effects of pulse current level, junction temperature, and pulse width on bipolar degradation were systematically characterized. Experimental results reveal that significant bipolar degradation occurs when both pulse current level and junction temperature approach their rated limits simultaneously, with degradation severity increasing with pulse width. However, negligible degradation was observed under two conditions: low pulse current with high junction temperature and high pulse current with low junction temperature.

For SiC device development, two implementation strategies are recommended: (1) Adopting rated pulse current levels and junction temperatures as standard evaluation conditions, with iterative process optimization until bipolar degradation is eliminated under these rated parameters; (2) Utilizing experimentally derived allowable thresholds for pulse current and junction temperature as reference benchmarks for rating calibration. In practical applications, three critical countermeasures should be implemented. First, avoid operating body diodes under concurrent high-current pulses and elevated junction temperatures. Enhanced thermal management should be employed for surge current scenarios to prevent junction temperature from approaching rated limits. Second, implement co-optimization of circuit topology, gate driving, and protection mechanisms to minimize body diode overcurrent levels, thereby suppressing bipolar degradation and improving thermal utilization efficiency. Third, the pulse width in the control logic design should be strategically reduced to mitigate degradation effects. These comprehensive solutions provide valuable technical references for suppressing bipolar degradation and advancing the industrialization of high-reliability SiC power devices.

keywords:SiC MOSFET body diodes, bipolar degradation, pulse current stress, application guidance

DOI: 10.19595/j.cnki.1000-6753.tces.250174

中图分类号:TN386.1

中国南方电网有限责任公司科技资助项目(GDKJXM20231033)。

收稿日期 2025-02-03

改稿日期 2025-03-24

张浩然 男,1997年生,博士研究生,研究方向为高压大功率电力电子器件可靠性评估。E-mail: haoranzhang@ncepu.edu.cn

孙 鹏 男,1994年生,讲师,研究方向为高压大功率电力电子器件封装、测试与状态监测。E-mail: sunpeng@ncepu.edu.cn(通信作者)

(编辑 陈 诚)