浮动式Boost DC-DC变换器共模噪声分析

王一帆 刘雪山 奉榆杰

(四川大学电气工程学院 成都 610065)

摘要 目前,针对非隔离型DC-DC变换器的共模噪声研究主要集中在通过运用噪声抵消、疏导等方法减小变换器的传导噪声,对于输出浮动式DC-DC变换器的共模噪声产生机理尚无明确的分析和研究。首先,该文通过分析输出浮动式Boost DC-DC变换器在正常工作状态下各节点对参考点之间的电位变化,得出输出浮动式Boost变换器高传导共模噪声的成因;其次,在考虑变换器各元件寄生参数的情况下,构建共模噪声等效模型并对其进行简化,分析不同噪声源引起的共模电流大小和方向;最后,搭建4台不同拓扑的实验样机,测试了各样机传导共模噪声的幅值并进行对比,验证了理论分析的正确性。

关键词:共模噪声 输出浮动式变换器 等效模型 寄生参数

0 引言

随着第三代宽禁带半导体的广泛应用,开关变换器的开关频率在不断地提高[1-3]。然而,高开关频率所带来的电磁干扰(Electromagnetic Interference, EMI)问题也越发突出,其不仅会影响设备的正常工作状态,严重时甚至危及周围人的人身安全[4-5]。EMI主要包含传导噪声和辐射噪声,而传导噪声又可分为共模(Common Mode, CM)和差模(Differential Mode, DM)噪声。为了减小EMI从而满足开关变换器的电磁兼容(Electromagnetic Compatibility, EMC)标准,国内外学者对其进行了大量的研究[6-8]。

在开关变换器中,高频的开关动作会在电路中产生高dv/dt节点,称为动点;与之对应的相对于参考电位无电压变化的节点则称为静点。这些电路的动点通过对大地的杂散电容相对于电源输入端形成共模位移电流,从而产生开关变换器的共模噪声。特别地,当DC-DC变换器的输入与输出无公共点连接时,变换器的输出电压相对于输入是浮动的。针对这种输出浮动式DC-DC变换器,在光伏、燃料电池和储能系统等新能源领域,学术界研究较为广泛,尤其侧重于研究具有高电压增益的DC-DC变换器,以满足新能源系统输出的直流电压直接作为后级逆变器的供电需求,由此衍生出了许多输出浮动式的DC-DC变换器[9-11]。文献[12]研究了三种结构简单的Boost型DC-DC变换器,在没有极高占空比的情况下实现了高升压增益。文献[13]提出了一种新型的具有耦合电感和倍压电路的高升压浮动式Boost 型DC-DC变换器,该变换器可在适当的占空比和低电压应力的情况下实现高电压增益。文献[14]研究了一种不使用电压倍增单元的非隔离浮动式高增益Boost DC-DC变换器,实现了高电压增益。文献[15]基于基本Boost变换器,根据励磁电感和续流二极管在电路中的位置变换,列举了两种输出浮动式Boost电路拓扑。然而,输出浮动式Boost拓扑结构在工程界已经被发现具有严重的EMI问题[16-17],但针对具体拓扑的分析尚不明确,缺少对EMI产生机理和抑制技术的相关研究。

目前,针对基本输入输出静点连接型Boost DC- DC变换器的EMI抑制技术,国内外学者进行了大量的研究[18-23]。文献[18]建立了Boost变换器的EMI分析模型,基于该模型,提出了采用阻抗平衡原理来消除共模噪声的理论和方法。文献[19]通过在电感上增加一个辅助绕组,从而减小Boost变换器的共模噪声。文献[20]提出了以反相1 1变压器代替Boost变换器的反相辅助绕组的方法,该方法可以极大地减小变压器二次侧分布电容,从而有效降低变换器的共模噪声。文献[21]提出了一种共模电压消除法来降低功率变换器的共模噪声,通过增加连接在输入电压和变换器输入端之间的两个绕组,并将它们与励磁电感或变压器耦合,可以产生抵消变换器共模噪声的电压。文献[22]基于电感的分裂绕组配置,在不增加电路体积的情况下,提出了一种新的非隔离DC-DC变换器共模噪声消除方法。文献[23]通过对共模噪声抑制机理的分析,基于大匝比的反相绕组法,建立了插入损耗下的完整数学模型。然而,针对输出浮动式Boost变换器的共模噪声产生机理尚无明确的、系统性的分析。

1变压器代替Boost变换器的反相辅助绕组的方法,该方法可以极大地减小变压器二次侧分布电容,从而有效降低变换器的共模噪声。文献[21]提出了一种共模电压消除法来降低功率变换器的共模噪声,通过增加连接在输入电压和变换器输入端之间的两个绕组,并将它们与励磁电感或变压器耦合,可以产生抵消变换器共模噪声的电压。文献[22]基于电感的分裂绕组配置,在不增加电路体积的情况下,提出了一种新的非隔离DC-DC变换器共模噪声消除方法。文献[23]通过对共模噪声抑制机理的分析,基于大匝比的反相绕组法,建立了插入损耗下的完整数学模型。然而,针对输出浮动式Boost变换器的共模噪声产生机理尚无明确的、系统性的分析。

本文以输出浮动式Boost DC-DC变换器为研究对象,深入分析了共模传导噪声的产生机理,推导了考虑电路寄生参数的共模噪声等效模型。搭建了4台不同拓扑的实验样机,通过测试各样机传导共模噪声的幅值并进行了对比,验证了理论分析的正确性。

1 输出浮动式Boost变换器共模噪声分析

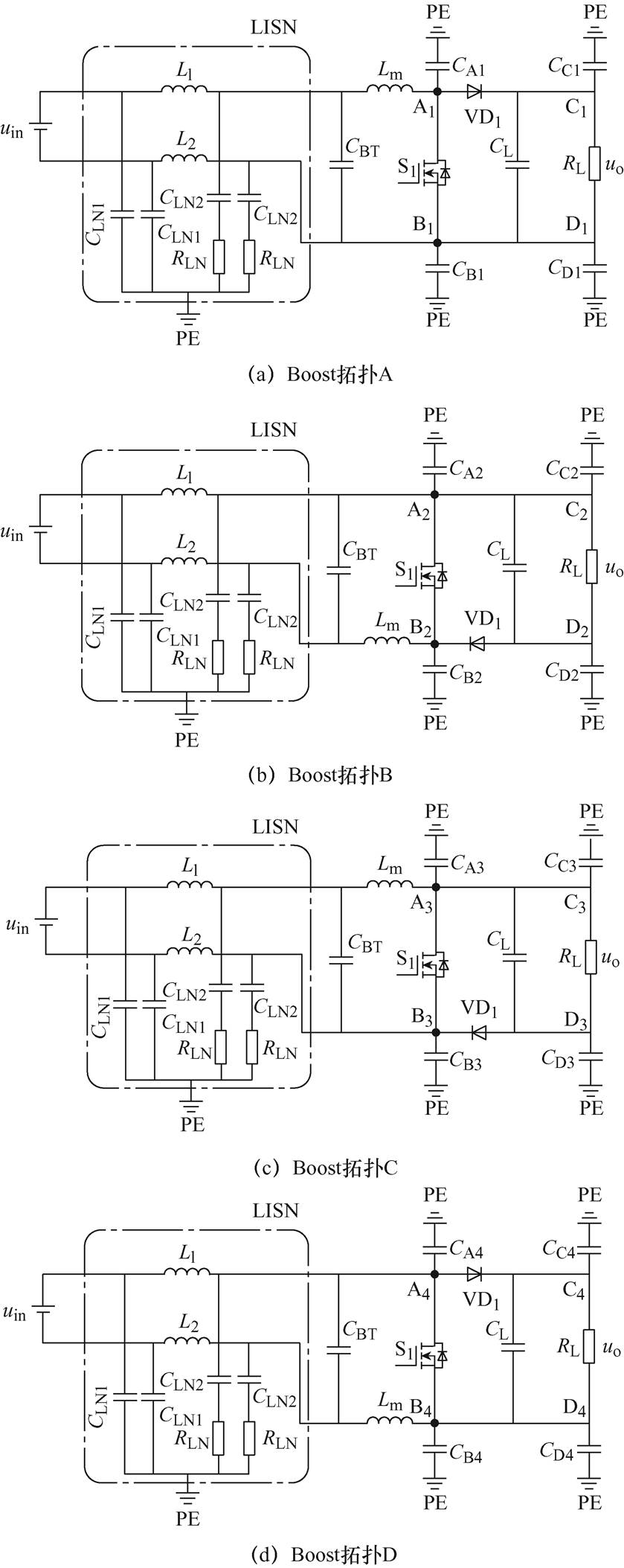

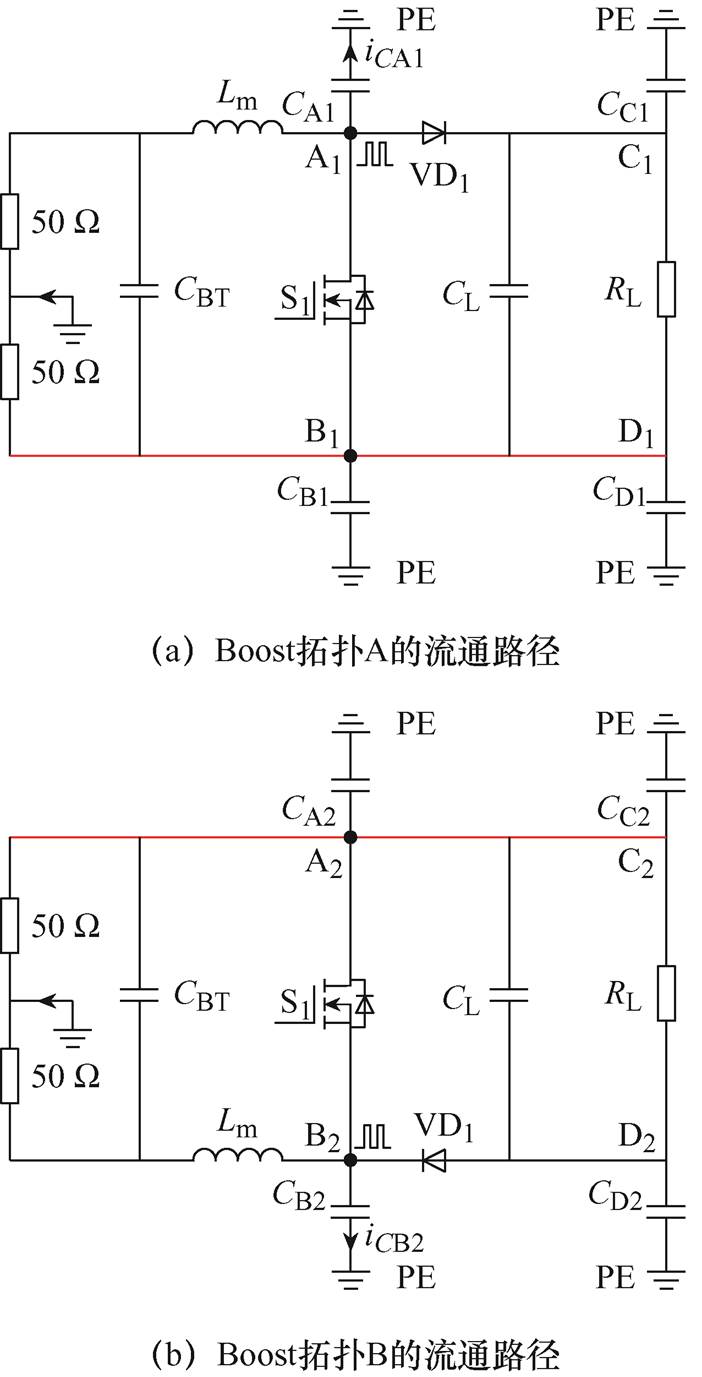

基于Boost变换器的四种拓扑结构如图1所示[15]。图1中,电感L1、L2,电容CLN1、CLN2和采样电阻RLN组成线性阻抗稳定网络(Line Impedance Stabilization Network, LISN),其中,L1=L2=50 mH,CLN1=1 mF,CLN2=0.1 mF,RLN=50 W,uin和uo分别为变换器的输入、输出电压,Lm为电路的励磁升压电感,S1为高频MOSFET开关管,VD1为续流二极管,CBT、CL分别为输入、输出电容,RL为电路输出的负载电阻,节点Ai、Bi、Ci、Di(i=1, 2, 3, 4)分别为开关管的漏极和源极、负载端的正极和负极,CAi、CBi、CCi、CDi(i=1, 2, 3, 4)分别为开关管漏极和源极、负载端的正极和负极对保护地(ProtectiveEarth, PE)的寄生电容。

由对输出浮动式变换器的结构描述可知,图1中的Boost拓扑A与Boost拓扑B为输入输出静点连接结构;而Boost拓扑C和Boost拓扑D则是输出浮动式结构。为了验证输出浮动式拓扑高共模噪声的成因,下面对四种拓扑在正常工作状态下的共模噪声产生机理进行分析。

在分析变换器共模噪声时,需要在输入侧设定相对于整个变换器的零电位参考点,参考点需具有相对于PE的电动势差为恒定不变的特点。图1中,由于励磁电感Lm分别与节点A1、B2、A3和B4相连,在变换器正常工作状态下,其相对于PE的电压是高频变化的,因此选择节点B1、A2、B3和A4为零电位参考点,下面将分析变换器在正常工作状态下各节点相对于参考点的电位变化。

为简化分析过程,先做出如下假设:①输入电压uin、输出电压uo恒定不变;②所有元件均为理想元件;③输入电容CBT和输出电容CL足够大。

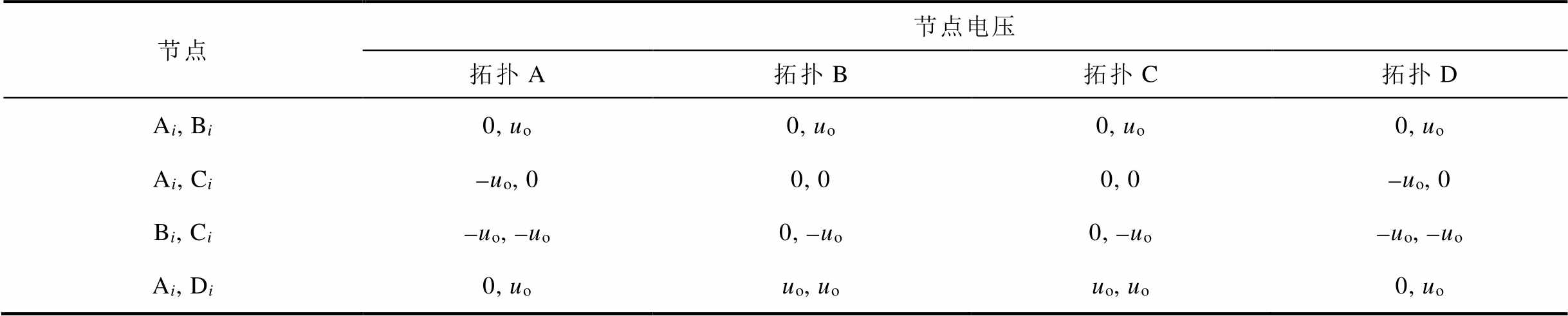

根据开关管S1的导通和关断,变换器有两个工作模态,相应的节点间电压大小见表1。

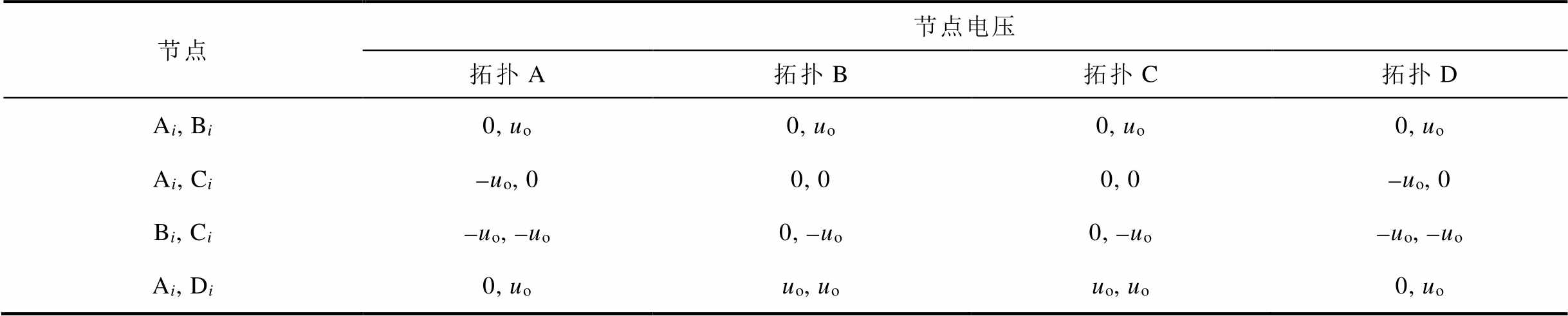

表1 各拓扑节点电压

Tab.1 Voltage of each topology node

节点节点电压 拓扑A拓扑B拓扑C拓扑D Ai, Bi0, uo0, uo0, uo0, uo Ai, Ci-uo, 00, 00, 0-uo, 0 Bi,Ci-uo, -uo0, -uo0, -uo-uo, -uo Ai, Di0, uouo, uouo, uo0, uo

根据工作模态的分析可得出,随着开关管的高频开关动作,节点A1、B2、A3、C3、D3、B4、C4、D4相对于参考节点B1、A2、B3、A4的电压均以相同频率(即开关频率)高频变化,即都为电路中的动点。电路中高dv/dt节点会通过该点对地寄生电容产生流向PE的共模噪声电流,因此四种Boost变换器拓扑的共模噪声电流流通路径如图2所示。

图2中,输入侧的LISN网络可等效为两个50 W电阻并联在PE与输入电容CBT两端。由此分析得出,节点A1、B2、A3、C3、D3、B4、C4、D4均为动点,因此图2a中,共模噪声电流iCA1通过对地寄生电容CA1流入PE;图2b中,共模噪声电流iCB2通过对地寄生电容CB2流入PE;图2c中,共模噪声电流iCA3、iCC3、iCD3分别通过对地寄生电容CA3、CC3、CD3流入PE;图2d中,共模噪声电流iCB4、iCC4、iCD4分别通过对地寄生电容CB4、CC4、CD4流入PE,然后噪声电流通过LISN的50 W 采样电阻流回变 换器。

从以上分析可知,Boost拓扑A和Boost拓扑B具有一个动点,而Boost拓扑C和Boost拓扑D则具有三个动点。流经LISN的50 W 采样电阻上的共模噪声电流更大,理论上解释了Boost拓扑A和Boost拓扑B的共模噪声比Boost拓扑C和Boost拓扑D更低的原因。

由于Boost拓扑B与Boost拓扑A对称,因此其共模噪声模型可以根据Boost拓扑A推导得出,下面将着重分析Boost拓扑C和Boost拓扑D的共模噪声模型。

2 输出浮动式Boost变换器共模噪声模型

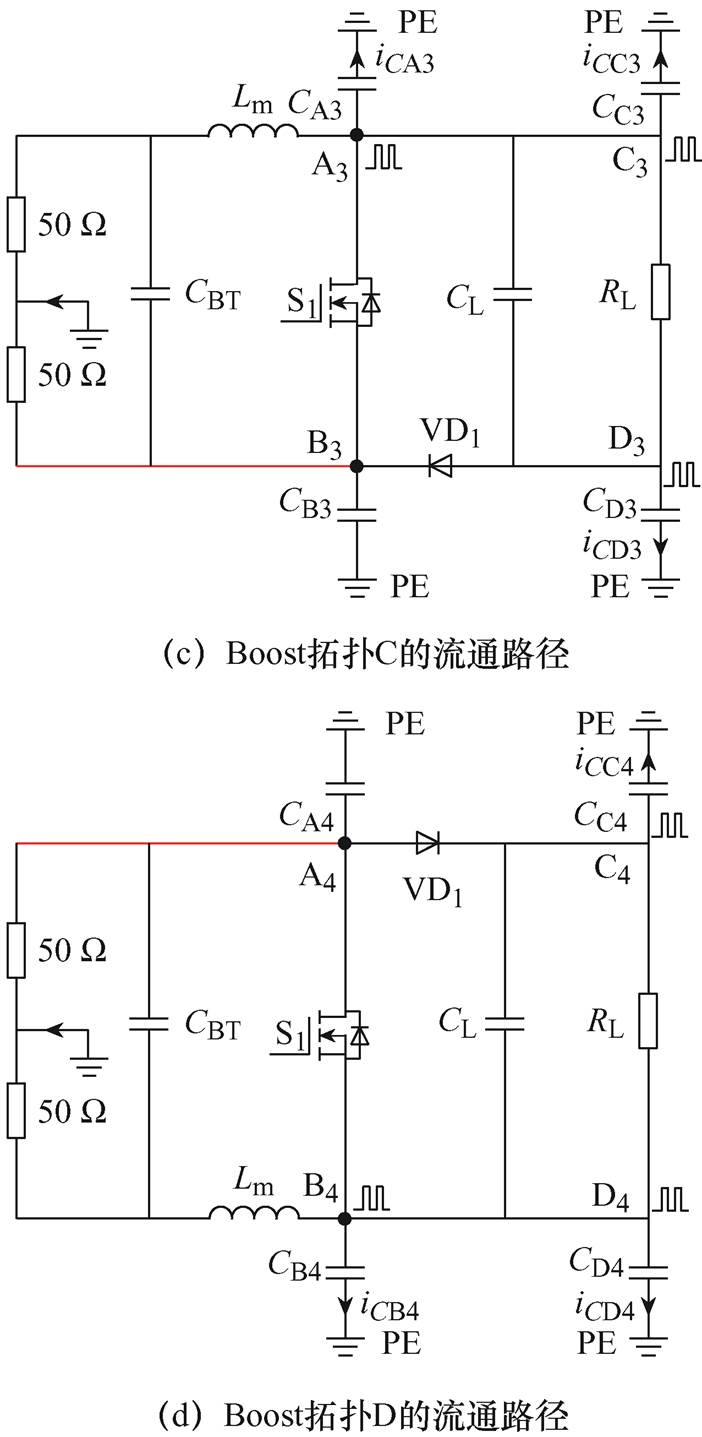

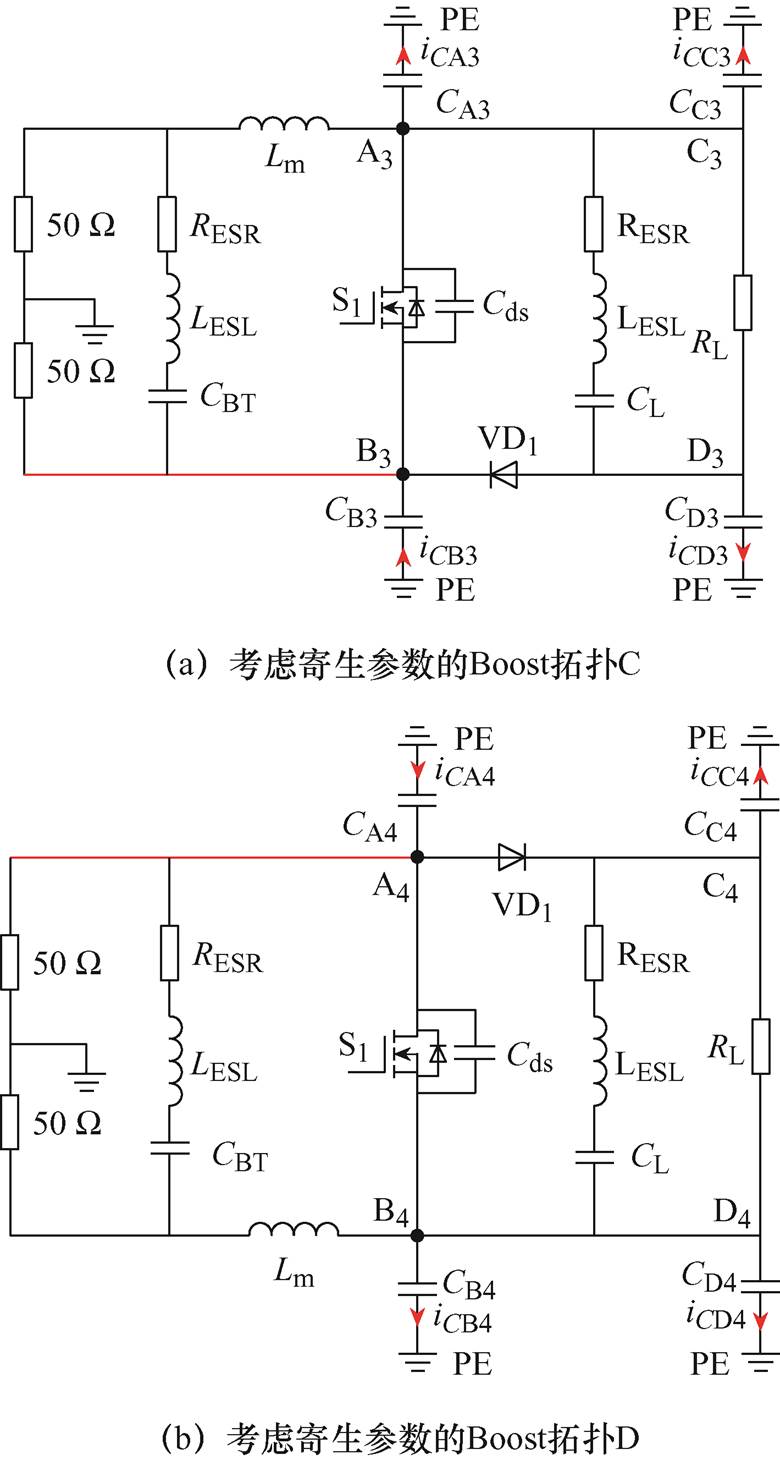

第1节分析是基于理想情况下四种Boost变换器的共模噪声分析,然而在实际的工程应用中,电路的印制电路板、开关器件、储能元件等由于制造工艺存在着如等效串联电阻(Equivalent Series Resistance, ESR)、等效串联电感(Equivalent Series Inductance, ESL)等寄生参数,在电路正常工作中,元器件的工作电压和电流波形在开关切换瞬间存在振铃和电压尖峰现象,从而影响电路的正常运行。且在共模噪声的高频段,寄生参数的影响尤为明显,因此有必要考虑器件寄生参数对变换器共模噪声的影响。考虑寄生参数的输出浮动式Boost变换器如图3所示,其中输入和输出电容CBT、CL寄生参数包含其等效串联电阻RESR和等效串联电感LESL,开关管S1包括寄生电容Cds。

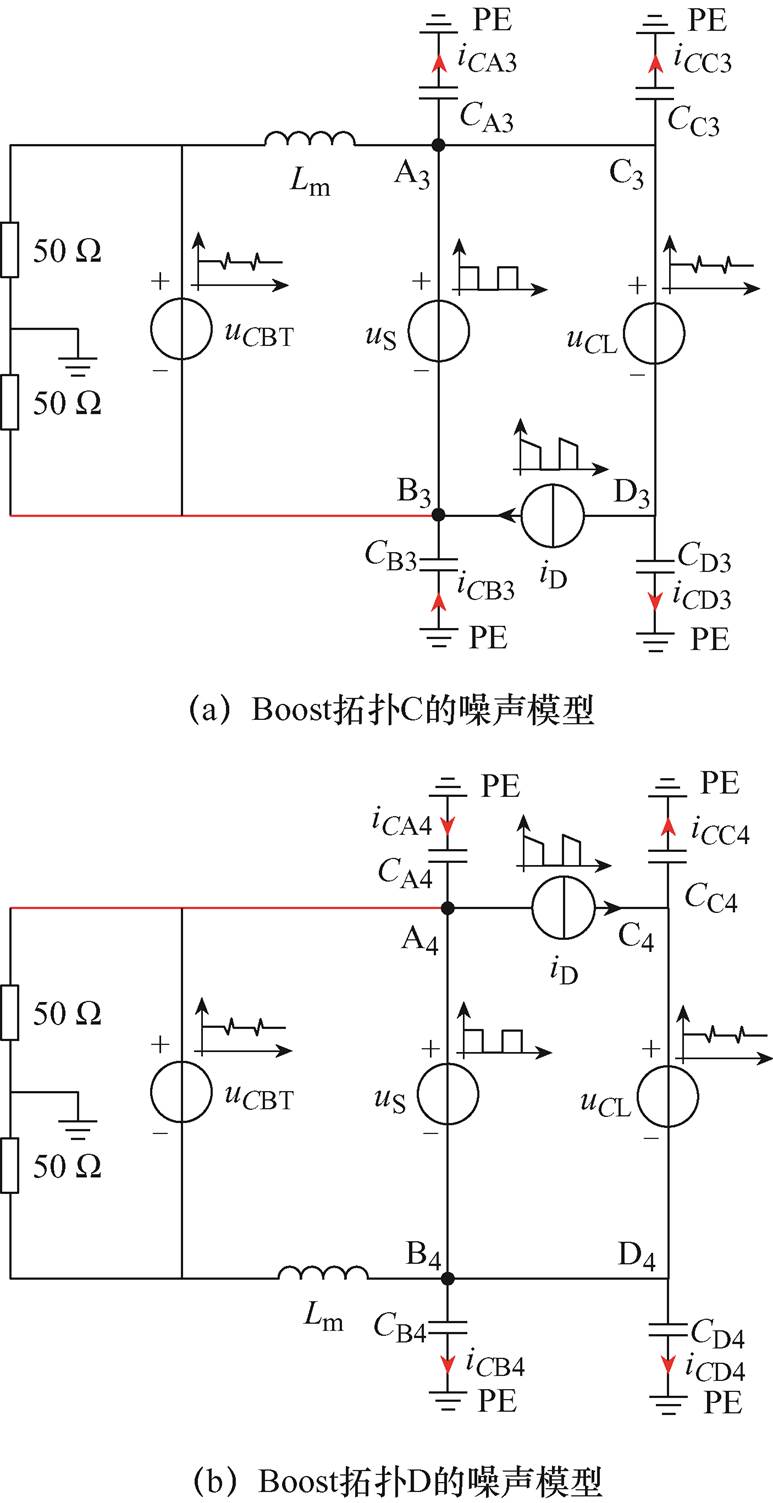

运用替代定理,将包含寄生参数正常工作的器件用相同波形的电压源和电流源进行等效替换[18],对输出浮动式Boost拓扑C和Boost拓扑D的共模噪声模型进行化简。根据基尔霍夫电压定律(Kirchhoff’s Voltage Law, KVL)和欧姆定律,对变换器4个节点间的电压和电流进行替换后,其共模噪声模型如图4所示,uCBT、uS和uCL分别为输入电容、开关管S1和输出电容相应的等效电压源,而iD则为二极管VD1的等效电流源。

图4中,电压源uCBT、uS、uCL和电流源iD由交流分量和直流分量组成,且都满足基尔霍夫电流定律(Kirchhoff's Current Law, KCL)和KVL。图5为考虑单一噪声源下,变换器的共模噪声简化模型。在噪声源的作用下,共模噪声电流通过各节点对地寄生电容,在与变换器与PE之间来回流动。

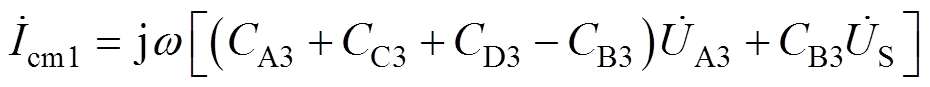

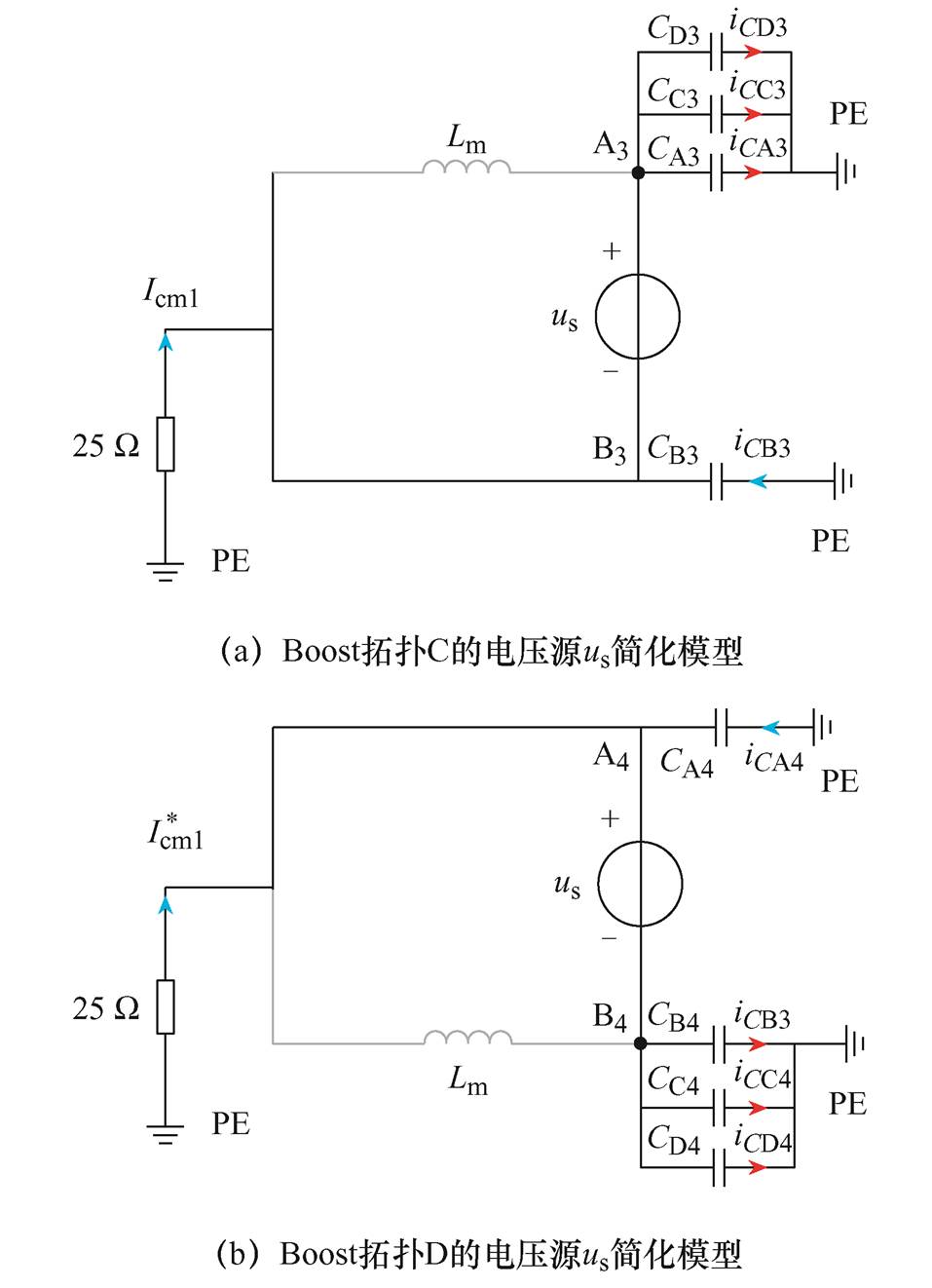

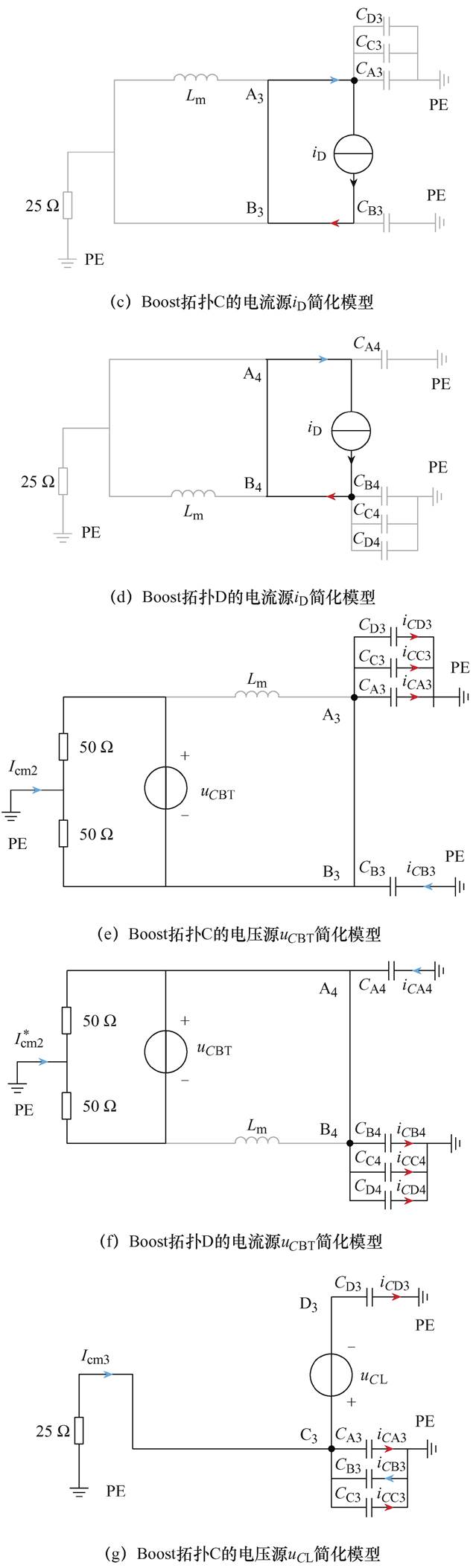

噪声源uS:采用叠加定理,当只考虑电压源uS(其他电压源短路、电流源断路)时,可以得到如图5a和图5b所示的等效电路。图5a中,节点A3、C3、D3分别通过寄生电容CA3、CC3、CD3向PE流入噪声电流,然后通过与PE连接的寄生电容CB3和LISN等效的25 W 采样电阻流入变换器,其中流经采样电阻的噪声电流Icm1即为该等效电路的总噪声电流。

流经寄生电容CA3、CB3、CC3和CD3的噪声电流分别为

式中, 、

、 、

、 和

和 分别为节点A3、B3、C3和D3相对PE的电压相量;w 为节点电压变化的角频率。

分别为节点A3、B3、C3和D3相对PE的电压相量;w 为节点电压变化的角频率。

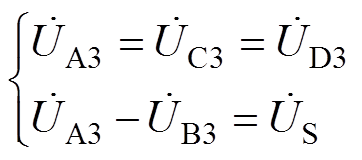

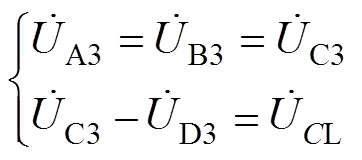

根据图5a中节点A3、B3、C3和D3的电位关系,有

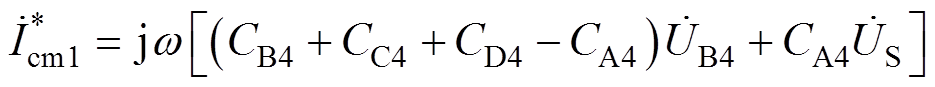

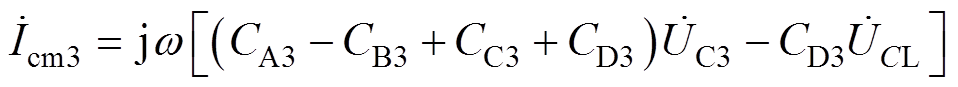

运用KCL定律,结合式(1)和式(2)可得出,在该简化电路下Boost拓扑C的共模噪声电流 为

为

(3)

(3)

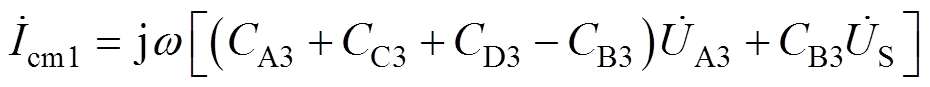

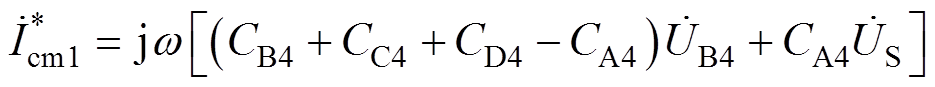

图5b中,节点B4、C4、D4分别通过寄生电容CB4、CC4、CD4向PE流入噪声电流,然后通过与PE连接的寄生电容CA4和LISN等效的25 W 采样电阻流入变换器。

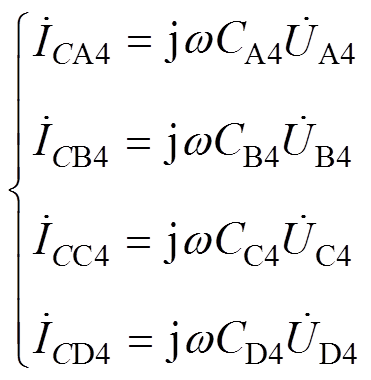

流经寄生电容CA4、CB4、CC4和CD4的噪声电流为

式中, 、

、 、

、 和

和 分别为节点A4、B4、C4和D4相对PE的电压相量。

分别为节点A4、B4、C4和D4相对PE的电压相量。

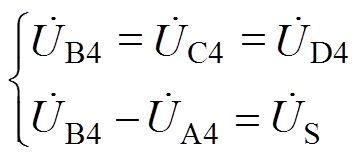

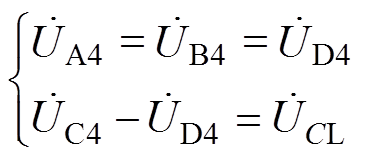

根据图5b中节点A4、B4、C4和D4的电位关系,有

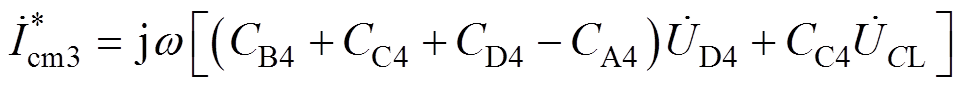

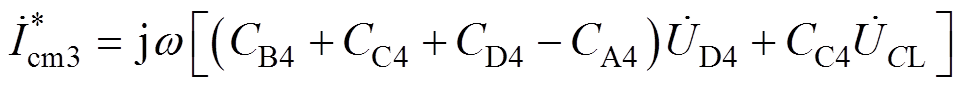

同理,运用KCL定律,结合式(4)和式(5)可得出,在噪声源uS作用下Boost拓扑D的共模噪声电流 为

为

(6)

(6)

图5a中,寄生电容CA3、CC3、CD3连接在电压源uS正极和PE之间,电压源uS负极和PE连接电容CB3;图5b中,寄生电容CA4连接在电压源uS负极和PE之间,电压源uS正极和PE连接电容CB4、CC4、CD4。

此时,由于电感Lm并联在噪声源uS两端,电感电流只在变换器内部传递流动,且主要影响差模噪声分量,不经过PE与LISN的采样电阻,因此其不会增大变换器的共模噪声。

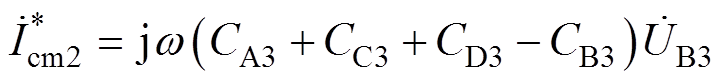

噪声源iD:当只考虑噪声电流源iD(其他电压源短路)时,可以得到如图5c和图5d所示的简化模型。图5c中,寄生电容CB3连接在电流源iD负极和PE之间,电流源iD正极和PE连接电容CA3、CC3、CD3。图5d中,寄生电容CA4连接在电流源iD负极和PE之间,电流源iD正极和PE连接电容CB4、CC4、CD4。

此时,由于在简化过程中,电压源uCBT、uS、uCL被视为短路,因此电流源iD被短路,故其不对共模噪声电流产生影响。

噪声源uCBT:当只考虑电压源uCBT(其他电压源短路、电流源断路)时,可以得到如图5e和图5f所示的等效电路。图5e中,寄生电容CA3、CB3、CC3和CD3连接在电压源uCBT负极和PE之间,电压源uCBT正极和采样电阻、励磁电感Lm相连。

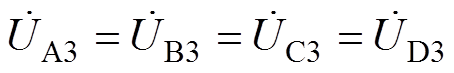

可以看出,由于噪声源uS、uCL被短路,电流源iD被断路,节点A3、B3、C3、D3连接在一起,故有

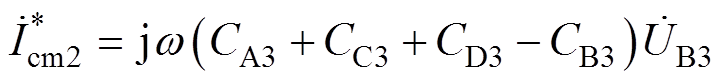

采用KCL定律,结合式(7)可得出在噪声源uCBT作用下,Boost拓扑C的共模噪声分量 为

为

(8)

(8)

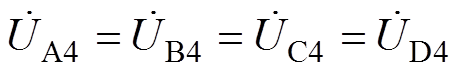

图5f中,寄生电容CA4、CB4、CC4和CD4连接在电压源uCBT正极和PE之间,电压源uCBT负极和采样电阻、励磁电感Lm相连。

由于噪声源uS、uCL被短路,电流源iD被断路,节点A4、B4、C4、D4连接在一起,故有

采用KCL定律,结合式(9)可得出在噪声源uCBT作用下,Boost拓扑D的共模噪声分量 为

为

(10)

(10)

此时,由于电感Lm并联在噪声源 两端,不对共模噪声电流产生影响,流经采样电阻的噪声电流Icm2即为该等效电路的总噪声电流。

两端,不对共模噪声电流产生影响,流经采样电阻的噪声电流Icm2即为该等效电路的总噪声电流。

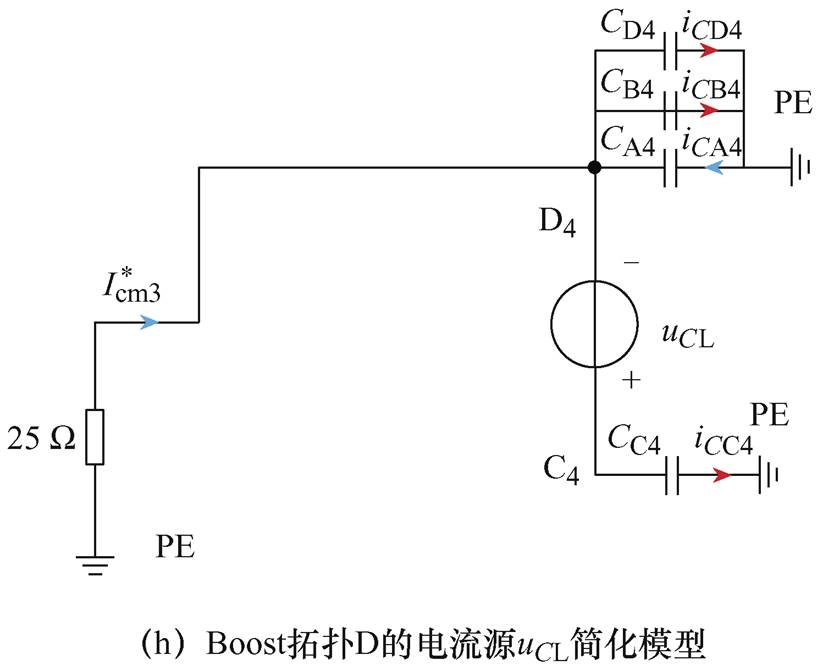

噪声源uCL:当只考虑电压源uCL(其他电压源短路、电流源断路)时,可以得到如图5g和图5h所示的等效电路。图5g中,寄生电容CD3连接在电压源uCL负极和PE之间,电压源uCL正极和PE连接电容CA3、CB3、CC3。

可以看出,由于噪声源uS、uCBT被短路,电流源iD被断路,节点A3、B3、C3连接在一起,故有

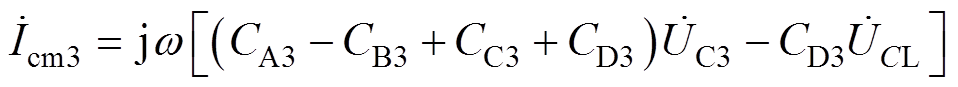

采用KCL定律,结合式(11)可得出在噪声源uCL作用下,Boost拓扑C的共模噪声分量 为

为

(12)

(12)

图5h中,寄生电容CC4连接在电压源uCL正极和PE之间,电压源uCL负极和PE连接电容CA4、CB4和CD4。

此时,由于噪声源uS、uCBT被短路,电流源iD被断路,节点A4、B4、D4连接在一起,故有

采用KCL定律,结合式(13)可得出在噪声源uCL作用下,Boost拓扑D的共模噪声分量 为

为

(14)

(14)

此时,电感Lm被短路,不对共模噪声电流产生影响,流经采样电阻的噪声电流Icm3即为该等效电路的总噪声电流。

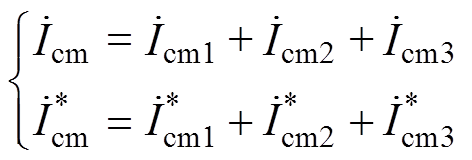

因此,对于Boost拓扑C和Boost拓扑D的总共模噪声电流 、

、 可分别表示为

可分别表示为

需要注意的是,由于节点B3和A4的共模噪声电流为流入变换器,因此增大节点对地寄生电容CB3和CA4有助于改善输出浮动式Boost变换器的共模噪声。在实际的情况下,寄生电容大小均为pF级,但开关管漏极的散热片对地寄生电容CAi(i=1, 2, 3, 4)往往远大于其他寄生电容。

3 实验验证

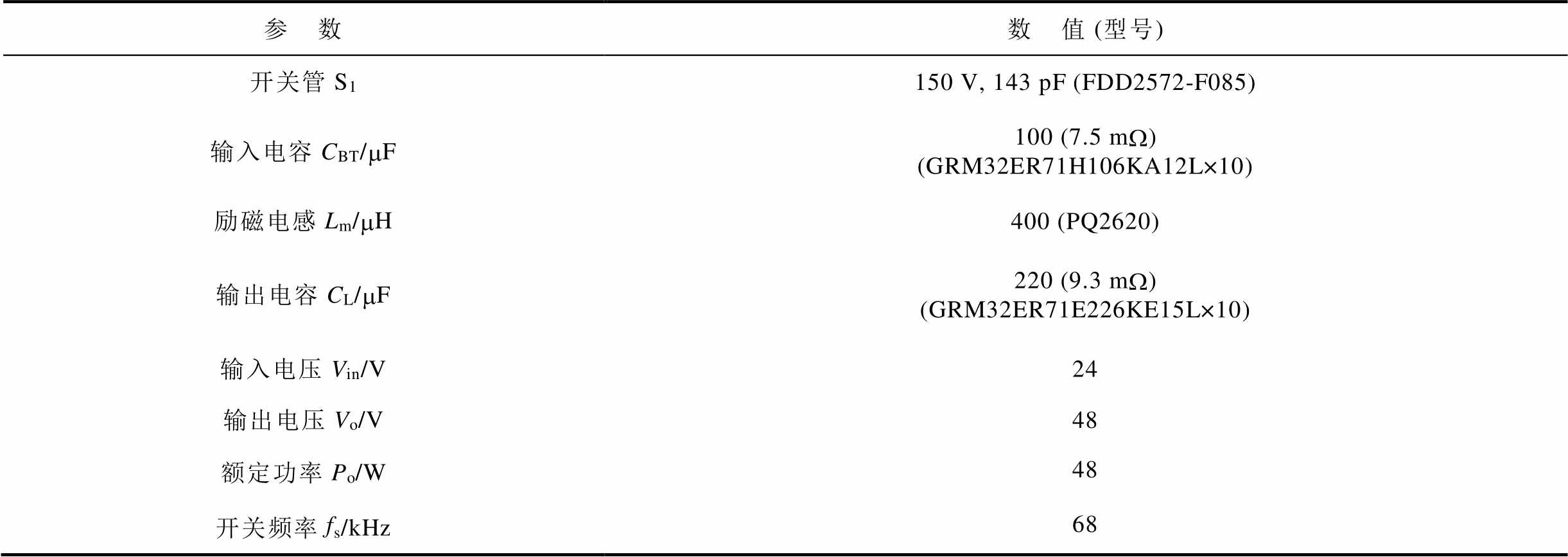

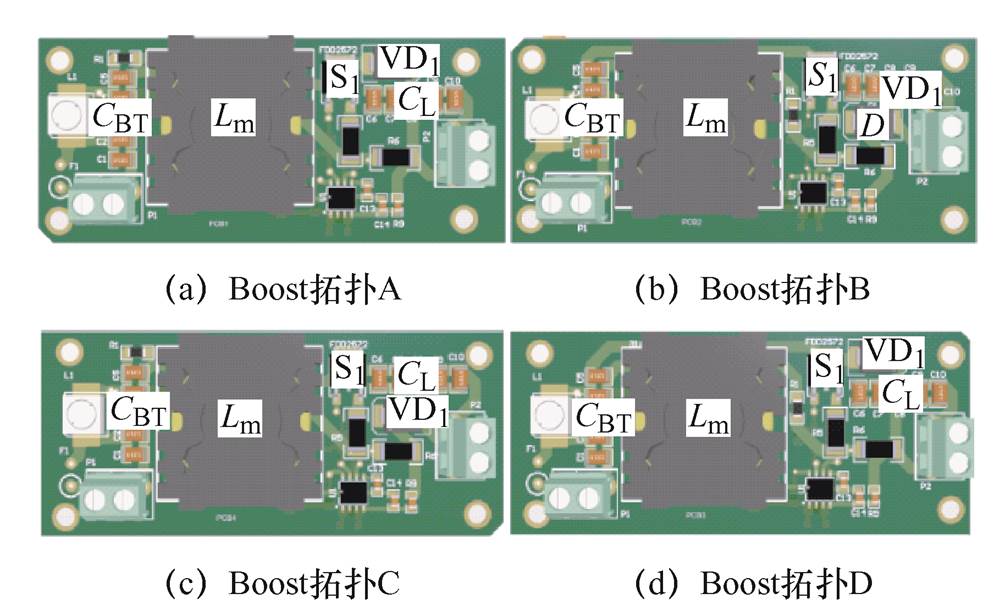

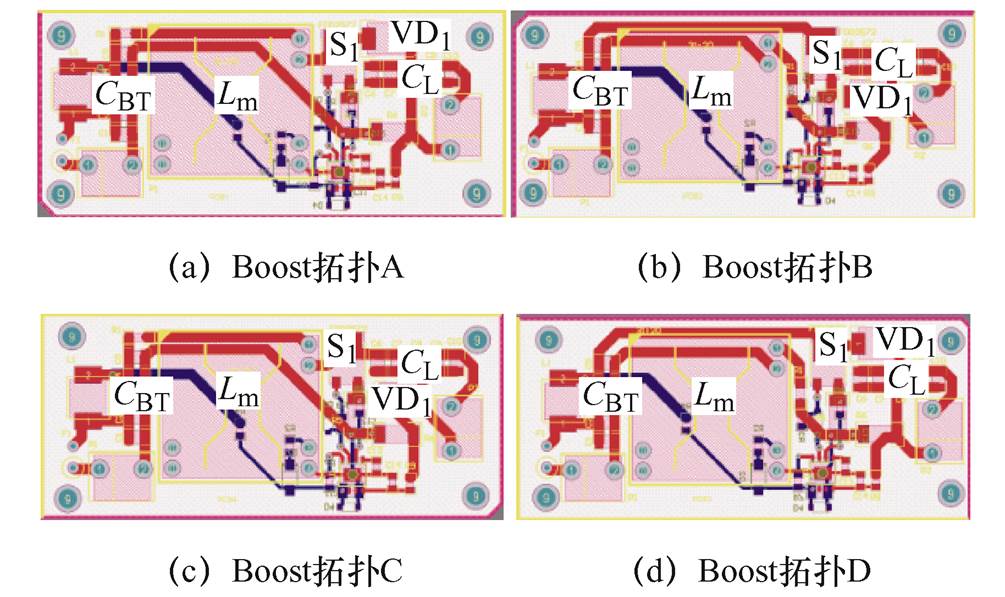

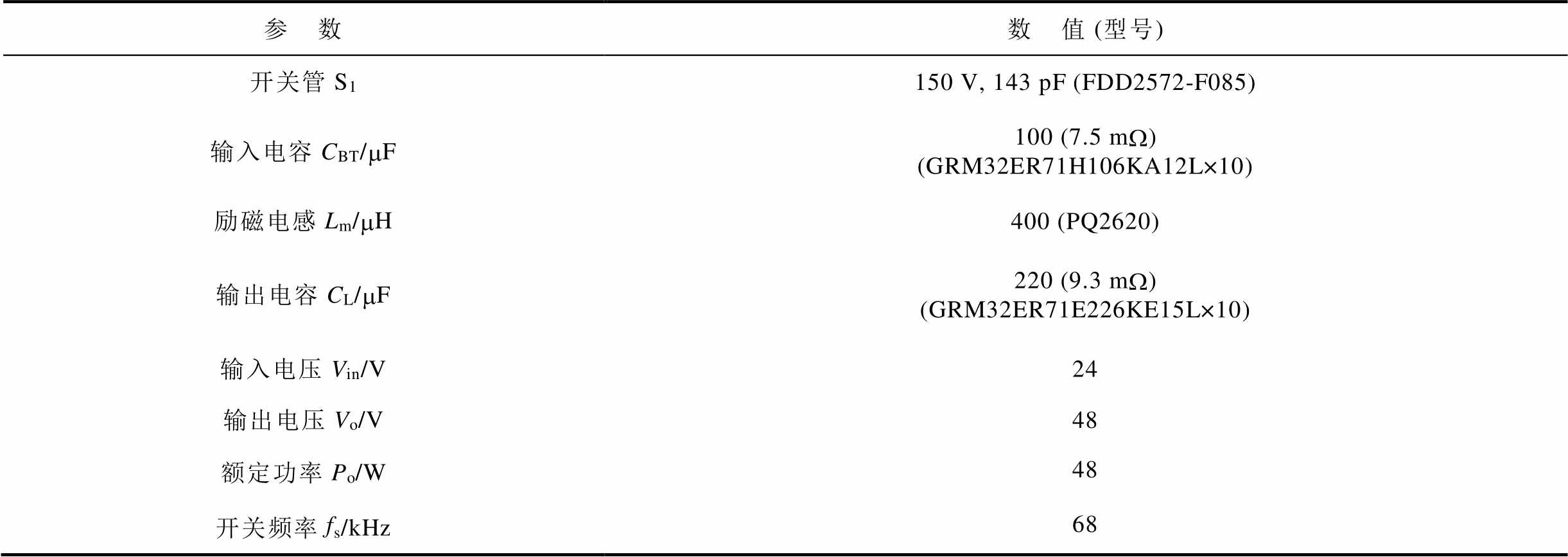

为了验证对输出浮动式Boost变换器共模噪声理论分析的正确性,基于Boost变换器的四种不同电路拓扑结构,搭建了4台输出功率为48 W的实验样机。样机的性能参数及器件的相关寄生参数见表2,样机在Altium Designer中的3D俯视图如图6、图7所示。

表2 样机性能参数及寄生参数

Tab. 2 Prototype performance parameters and parasitic parameters

参 数数 值 (型号) 开关管S1150 V,143 pF (FDD2572-F085) 输入电容CBT/mF100 (7.5 mW)(GRM32ER71H106KA12L×10) 励磁电感Lm/mH400 (PQ2620) 输出电容CL/mF220 (9.3 mW)(GRM32ER71E226KE15L×10) 输入电压Vin/V24 输出电压Vo/V48 额定功率Po/W48 开关频率fs/kHz68

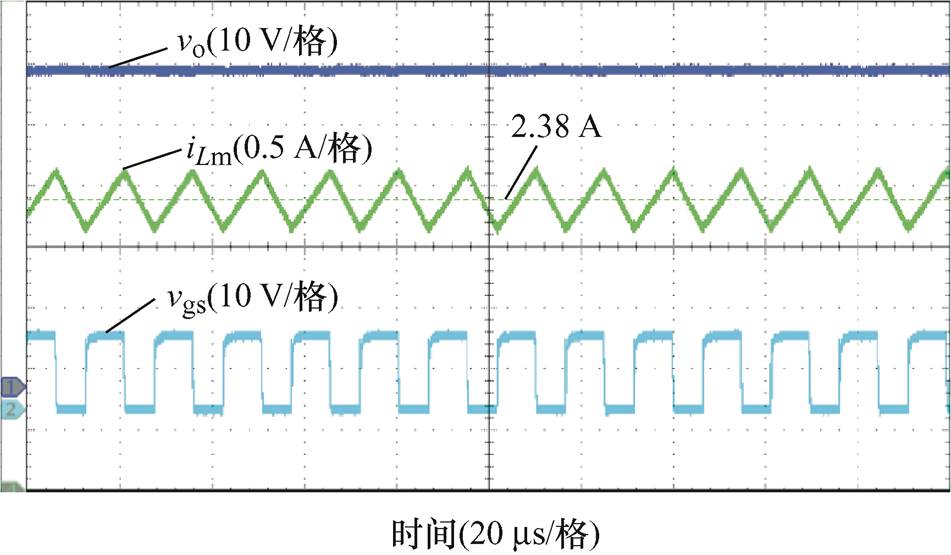

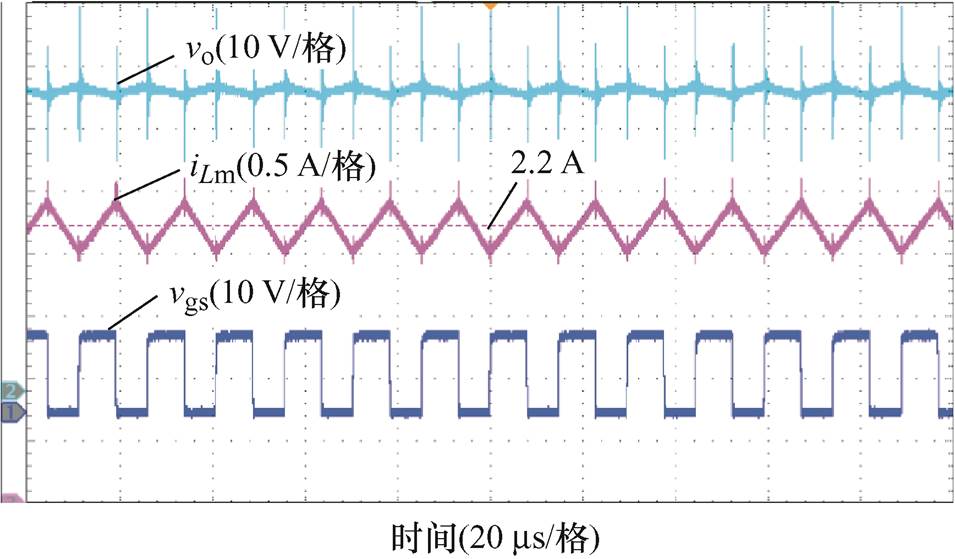

Boost拓扑A的输出电压、电感电流和开关管的驱动波形如图8所示。此时在图8中,随着开关导通和关断状态的切换,输出电压vo大约维持在48 V左右,电感电流iLm平均值维持在约为2.38 A。

为了进行不同拓扑工作状态的对比测试,实验对Boost拓扑D进行了调试,示波器测得的输出电压、电感电流和开关管的驱动波形如图9所示。

从图9中可以看出,Boost拓扑D的输出电压和电感电流,在开关状态切换处的波形畸变明显,这是由于在开关切换瞬间,Boost拓扑D相应各节点流入/流出的共模噪声电流经过电路的寄生阻抗和负载电阻所致。下面将通过对样机进行传导EMI测试,进一步说明变换器的共模噪声。

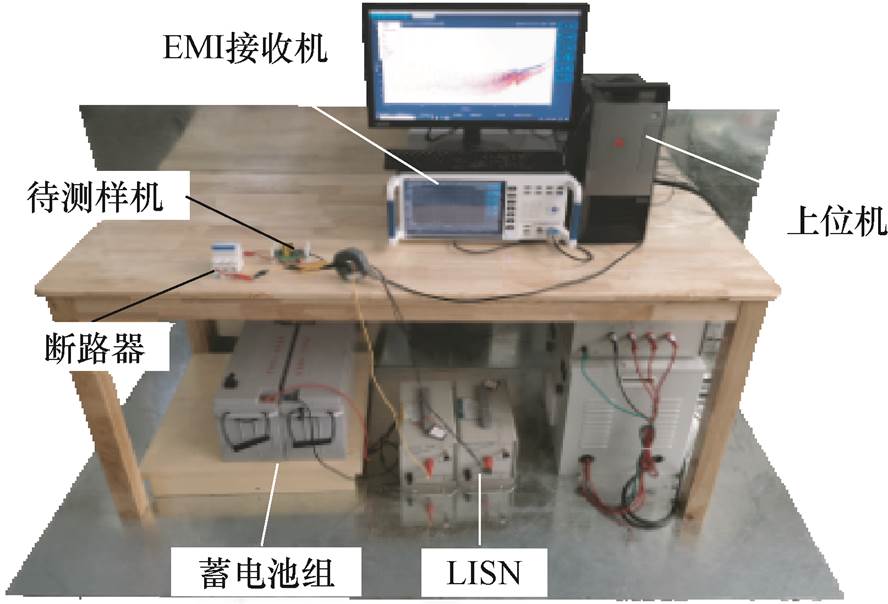

图10为输出浮动式Boost变换器样机传导EMI的测试环境,其中包含蓄电池组、LISN、EMI接收机、待测样机、断路器和上位机。EMI接收机和LISN采用北京科环世纪的KH3938B全自动电磁干扰测试接收机和KH3766 LISN设备,上位机可通过通信端口远程控制EMI接收机接收来自LISN设备的噪声信号。

为了尽量排除实验测试过程中的外来干扰因素,本文采用蓄电池组作为待测物的输入DC电源。

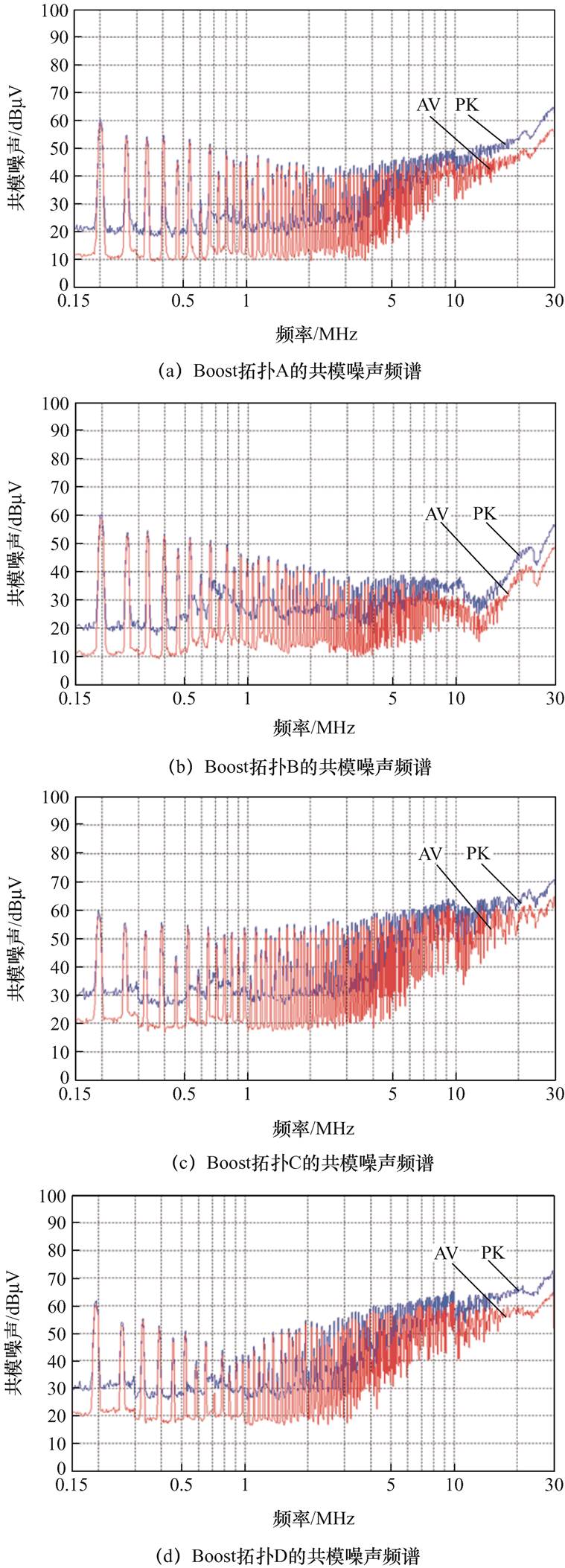

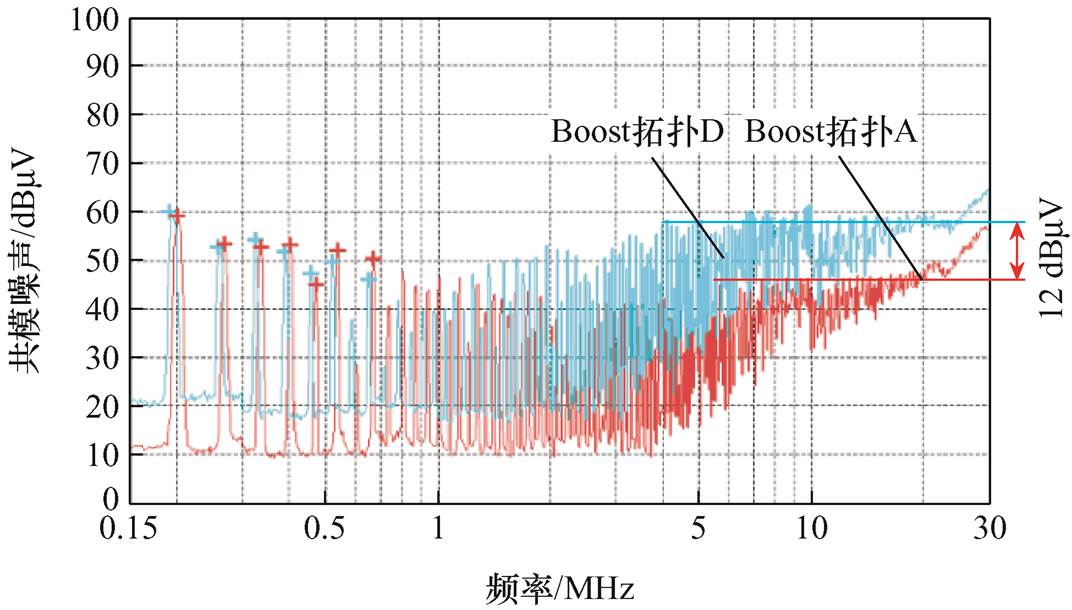

为了对比不同拓扑结构Boost变换器的传导噪声,分别对四台实验样机进行了传导噪声测试,测试结果如图11所示,图中,PK和AV分别代表EMI频谱的峰值和平均值。

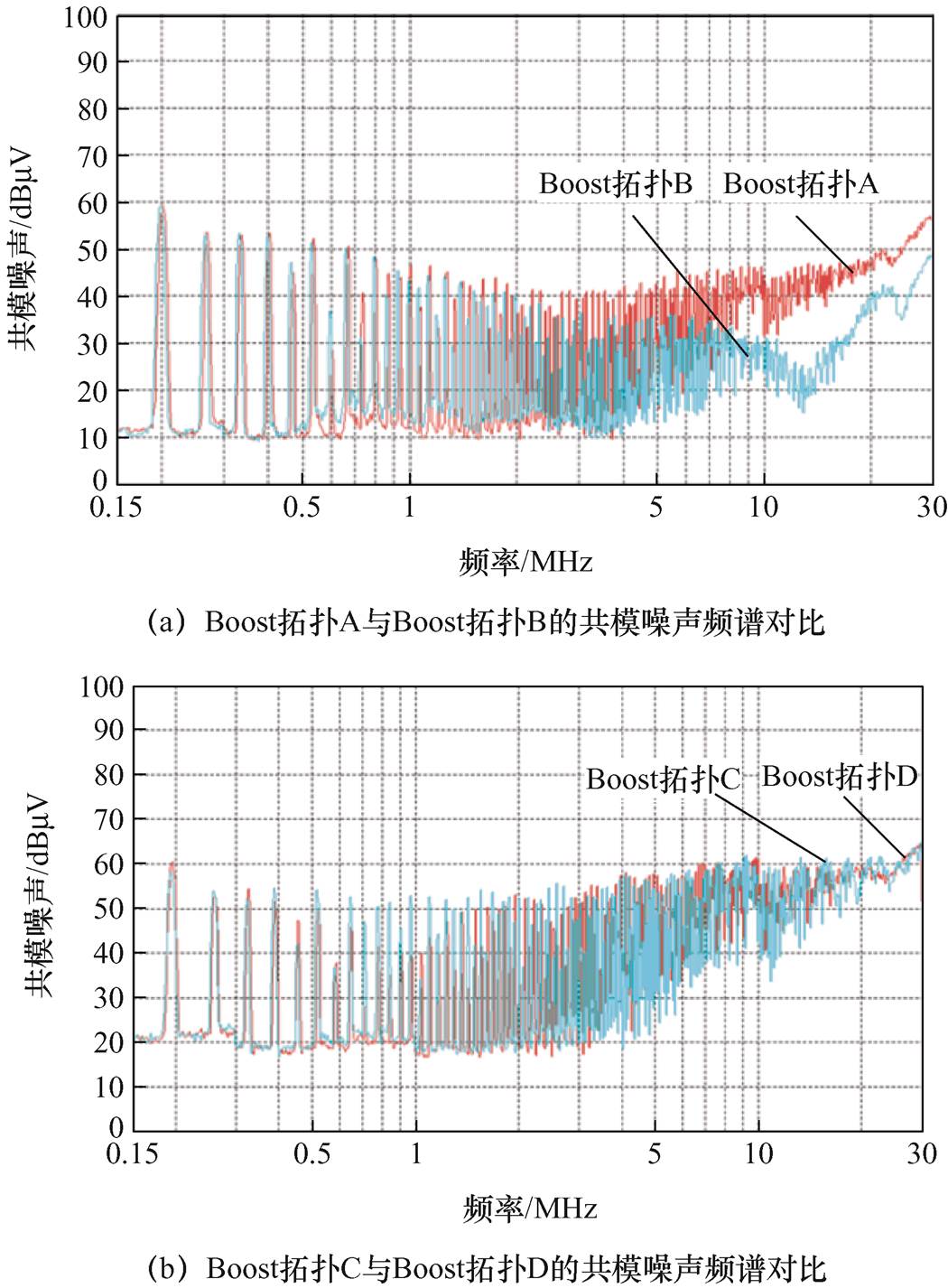

图12为Boost四种共模噪声频谱AV值对比。从图12a中可以看出,Boost拓扑A与Boost拓扑B的共模噪声在低频段基本一致,在高频段相差5~10 dBmV,这是因为Boost拓扑A的共模噪声电流所对应的对地寄生电容CA1略大于Boost拓扑B的共模噪声电流所对应的对地寄生电容CB1,因此在具有相同的dv/dt条件下,Boost拓扑A流入大地的共模噪声电流大于Boost拓扑B流入大地的共模噪声电流。

从图12b中可以看出,在测试频段为0.15~0.5 MHz之间,Boost拓扑C和Boost拓扑D的共模噪声频谱基本是一致的;在测试频段为0.5~5 MHz之间,Boost拓扑C的共模噪声频谱则略高于Boost拓扑D;在测试频段为5~30 MHz之间,Boost拓扑C和Boost拓扑D的共模噪声频谱的平均值保持同一水平。

Boost拓扑C与Boost拓扑D均为输出浮动式拓扑,在0.5 MHz以后共模噪声频谱整体比Boost拓扑A与Boost拓扑B的共模噪声频谱高,而在中频0.5~5 MHz区间的噪声差异主要由实验样机动点对地的寄生电容差异导致。

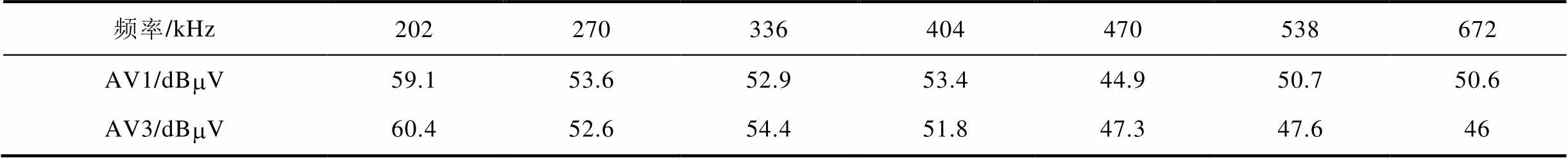

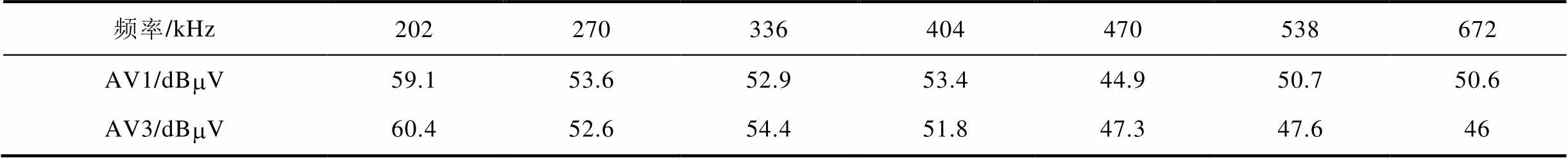

为验证输出浮动式Boost变换器的高EMI特性,对Boost拓扑A和Boost拓扑D进行AV值的对比测试,测试的传导共模噪声频谱如图13所示。从图13中可以看出,Boost拓扑D对比Boost拓扑A,其共模噪声增大了约12 dBmV。

表3列出了图13中传导共模噪声频谱的谐振频率幅值,其中AV1和AV3分别为Boost拓扑A与Boost拓扑D的传导共模噪声平均值。可以看出,在谐振频率处,Boost拓扑A与Boost拓扑D的共模噪声AV值相差范围在5 dBmV以内,这说明在谐振频率处,测试样机的共模噪声电流分量基本一致。

表3 谐振频率幅值

Tab. 3 Resonant frequency amplitude

频率/kHz202270336404470538672 AV1/dBmV59.153.652.953.444.950.750.6 AV3/dBmV60.452.654.451.847.347.646

4 结论

本文针对输出浮动式Boost变换器的共模噪声产生机理进行了研究,通过对变换器的工作状态分析得出,输出浮动式Boost变换器的动点相对于基本Boost变换器增加了2个,因此具有高传导共模噪声的特点。针对寄生参数对电路的影响,本文构建了相应的高频共模噪声等效模型,揭示了主噪声源对共模噪声的影响关系。实验对比结果得出:传统的输入和输出静点连接Boost变换器具有更优的共模噪声特性,输出浮动式Boost DC-DC变换器在工程应用上具有高共模噪声的局限性。

参考文献

[1] 桑汐坤, 王懿杰, 徐殿国. 基于输入并联输出串联的高效高升压比DC-DC变换器[J]. 电工技术学报, 2023, 38(20): 5488-5502. Sang Xikun, Wang Yijie, Xu Dianguo. High- efficiency high voltage gain DC-DC converter based on input parallel and output series connection[J]. Transaction of China Electrotechnical Society, 2023, 38(20): 5488-5502.

[2] Ansari S A, Moghani J S. A novel high voltage gain noncoupled inductor Sepic converter[J]. IEEE Transactions on Industrial Electronics, 2019, 66(9): 7099-7108.

[3] 黄何伟, 曹太强, 潘光绪, 等. 考虑回流功率因素的全桥CLL谐振变换器参数优化设计[J]. 电工技术学报, 2023, 38(20): 5503-5514. Huang Hewei, Cao Taiqiang, Pan Guangxu, et al. Parameter optimal design of full-bridge CLL resonant converter considering backflow power factor[J]. Transaction of China Electrotechnical Society, 2023, 38(20): 5503-5514.

[4] Zhang Zhe, Bazzi A M. A virtual impedance enhancement based transformer-less active EMI filter for conducted EMI suppression in power converters[J]. IEEE Transactions on Power Electronics, 2022, 37(10): 11962-11973.

[5] 郭昊, 李岩, 侯冰冰, 等. 基于正交频分复用-多进制正交幅度调制的DC-DC变换器能量信息一体化技术[J]. 电工技术学报, 2023, 38(16): 4353-4365. Guo Hao, Li Yan, Hou Bingbing, et al. Power information integration technology of DC-DC converters based on orthogonal frequency division multiplexing-multiple quadrature amplitude modulation[J]. Transaction of China Electrotechnical Society, 2023, 38(16): 4353-4365.

[6] Pahlevaninezhad M, Hamza D, Jain P K. An improved layout strategy for common-mode EMI suppression applicable to high-frequency planar transformers in high-power DC/DC converters used for electric vehicles[J]. IEEE Transactions on Power Electronics, 2014, 29(3): 1211-1228.

[7] Jin Meng, Ma Weiming, Pan Qijun, et al. Identification of essential coupling path models for conducted EMI prediction in switching power converters[J]. IEEE Transactions on Power Electro- nics, 2006, 21(6): 1795-1803.

[8] Ji Qing, Ruan Xinbo, Ye Zhihong. The worst conducted EMI spectrum of critical conduction mode Boost PFC converter[J]. IEEE Transactions on Power Electronics, 2015, 30(3): 1230-1241.

[9] 胡雪峰, 戴国瑞, 龚春英, 等. 一种高增益低开关应力改进交错型Boost变换器[J]. 电工技术学报, 2014, 29(12): 80-87. Hu Xuefeng, Dai Guorui, Gong Chunying, et al. An improved interleaved Boost converter with high gain and low switch voltage stress[J]. Transaction of China Electrotechnical Society, 2014, 29(12): 80-87.

[10] 刘昌咏, 赵晋斌, 毛玲, 等. 一种高降压比DC-DC变换器[J]. 电工技术学报, 2019, 34(20): 4264- 4271.Liu Changyong, Zhao Jinbin, Mao Ling, et al. A high step-down DC-DC converter[J]. Transaction of China Electrotechnical Society, 2019, 34(20): 4264-4271.

[11] 刘桂花, 王博鑫, 王卫, 等. 一种改进型高转换比两相串联电容变换器[J]. 电工技术学报, 2023, 38(增刊1): 114-123. Liu Guihua, Wang Boxin, Wang Wei, et al. An improved two-phase series-capacitor converter with high conversion ratio[J]. Transaction of China Electrotechnical Society, 2023, 38(S1): 114-123.

[12] Yang Lungsheng, Liang Tsorngjuu, Chen Jiannfuh. Transformerless DC-DC converters with high step-up voltage gain[J]. IEEE Transactions on Industrial Electronics, 2009, 56(8): 3144-3152.

[13] Yang Lungsheng, Liang Tsorngjuu, Lee Haucheng, et al. Novel high step-up DC-DC converter with coupled-inductor and voltage-doubler circuits[J]. IEEE Transactions on Industrial Electronics, 2011, 58(9): 4196-4206.

[14] Lakshmi M, Hemamalini S. Nonisolated high gain DC-DC converter for DC microgrids[J]. IEEE Transactions on Industrial Electronics, 2018, 65(2): 1205-1212.

[15] Coutellier D, Agelidis V G, Choi S. Experimental verification of floating-output interleaved-input DC- DC high-gain transformer-less converter topologies[C]// 2008 IEEE Power Electronics Specialists Conference, Rhodes, Greece, 2008: 562-568.

[16] Zhuo Shengrong, Gaillard A, Guo Liang, et al. Active disturbance rejection voltage control of a floating interleaved DC-DC Boost converter with switch fault consideration[J]. IEEE Transactions on Power Elec- tronics, 2019, 34(12): 12396-12406.

[17] Li Qian, Huangfu Yigeng, Xu Liangcai, et al. An improved floating interleaved Boost converter with the zero-ripple input current for fuel cell appli- cations[J]. IEEE Transactions on Energy Conversion, 2019, 34(4): 2168-2179.

[18] Wang Shuo, Kong Pengju, Lee F C. Common mode noise reduction for Boost converters using general balance technique[J]. IEEE Transactions on Power Electronics, 2007, 22(4): 1410-1416.

[19] Xin Wu, Pong Manhay, Lu Zhengyu, et al. Novel Boost PFC with low common mode EMI: modeling and design[C]//Fifteenth Annual IEEE Applied Power Electronics Conference and Exposition, New Orleans, LA, USA, 2000: 178-181.

[20] 林苏斌, 陈为, 董纪清, 等. Boost变换器共模噪声反相补偿法的高频特性分析与改善[J]. 中国电机工程学报, 2013, 33(27): 52-59, 9. Lin Subin, Chen Wei, Dong Jiqing, et al. High- frequency behaviors analysis and improvement of anti-phase compensation method for CM EMI noise suppression in Boost converters[J]. Proceedings of the CSEE, 2013, 33(27): 52-59, 9.

[21] Xie Lihong, Ruan Xinbo, Zhu Haonan, et al. Common-mode voltage cancellation for reducing the common-mode noise in DC-DC converters[J]. IEEE Transactions on Industrial Electronics, 2021, 68(5): 3887-3897.

[22] Xie Lihong, Yuan Xibo. Non-isolated DC-DC converters with low common-mode noise by using split-winding configuration[J]. IEEE Transactions on Power Electronics, 2022, 37(1): 452-461.

[23] 林苏斌, 周云, 张丽萍, 等. Boost电感反相绕组法的共模噪声抑制特性分析与设计[J]. 中国电机工程学报, 2022, 42(5): 1946-1957. Lin Subin, Zhou Yun, Zhang Liping, et al. Analysis and design of common mode noise suppression characteristics of Boost inductor anti-phase winding method[J]. Proceedings of the CSEE, 2022, 42(5): 1946-1957.

Analysis of Common Mode Noise in Floating Boost DC-DC Converters

Wang Yifan Liu Xueshan Feng Yujie

(College of Electrical Engineering Sichuan University Chengdu 610065 China)

Abstract Output-floating DC-DC converters are widely studied in new energy fields such as photovoltaics, fuel cells, and energy storage systems due to their high voltage gain. Taking the output-floating Boost DC-DC converter as the research object, this paper deeply analyzed the mechanism of common mode conducted noises and derived an equivalent model considering circuit parasitic parameters. Under the premise of adding a linear impedance stable network on the input side, the working mode analysis of four boost circuit topologies shows that the output-floating topology structure has three more high dv/dt nodes in the circuit compared to the input-output static point connection structure. With the switching state of the converter, the common mode noise current corresponding to these high dv/dt nodes can generate the common mode noise current flowing towards the ground on the flow path.

A model of an output-floating Boost circuit topology was established, taking into account the equivalent series resistance and equivalent series inductance of the input and output capacitors of the converter, as well as the parasitic capacitance of the switching transistor. Based on the substitution theorem and Kirchhoff voltage law, a common mode noise model for an output-floating Boost converter was derived by equivalently replacing a normally operating device containing parasitic parameters with voltage and current sources of the same waveform. At the same time, using the superposition theorem, the common mode noise model was simplified by considering a single noise voltage or current source. Based on Kirchhoff’s current law, the common mode noise acoustic current flowing through the parasitic capacitance of each converter node under the action of a single noise source and the total mode noise current on the linear impedance stable network sampling resistor were derived.

Four experimental prototypes with a rated power of 48 W were built. The output voltage, inductance current, and driving voltage were tested under 24 V input voltage working conditions. In a testing environment where common mode interference was conducted, four prototypes were tested. The common mode noise spectra were obtained through EMI receivers. It was found that the common mode noise of Boost topologies A and B is consistent in the low-frequency range and differs by 5 dBmV to 10 dBmV in the high-frequency range. The common mode noise spectra of boost topologies C and D are consistent in the 0.15 MHz to 0.5 MHz range. In the range of 0.5 MHz to 5 MHz, the common mode noise spectrum of Boost topology C is slightly higher than that of Boost topology D. The average value of the common mode noise spectra of Boost topologies C and D remains at the same level in the test frequency range of 5 MHz to 30 MHz. The common mode noise of Boost topology D is increased by approximately 12 dBmV compared to Boost topology A. Therefore, traditional input and output stationary point connected Boost converters have better common mode noise characteristics, while output- floating Boost DC-DC converters have high common mode noise limitations.

keywords:Common mode noise, output-floating converter, equivalent model, parasitic parameters

DOI:10.19595/j.cnki.1000-6753.tces.232092

中图分类号:TM46

国家自然科学基金资助项目(62371320)。

收稿日期 2023-12-16

改稿日期 2024-01-13

作者简介

王一帆 男,1998年生,硕士,研究方向为电力电子变换与控制、电磁兼容技术。E-mail: 18982674011@163.com

刘雪山 男,1981年生,副教授,硕士生导师,研究方向为高频开关变换器拓扑及其控制技术、电力电子技术及其应用等。E-mail: xueshan5851@163.com(通信作者)

(编辑 陈 诚)

1变压器代替Boost变换器的反相辅助绕组的方法,该方法可以极大地减小变压器二次侧分布电容,从而有效降低变换器的共模噪声。文献[21]提出了一种共模电压消除法来降低功率变换器的共模噪声,通过增加连接在输入电压和变换器输入端之间的两个绕组,并将它们与励磁电感或变压器耦合,可以产生抵消变换器共模噪声的电压。文献[22]基于电感的分裂绕组配置,在不增加电路体积的情况下,提出了一种新的非隔离DC-DC变换器共模噪声消除方法。文献[23]通过对共模噪声抑制机理的分析,基于大匝比的反相绕组法,建立了插入损耗下的完整数学模型。然而,针对输出浮动式Boost变换器的共模噪声产生机理尚无明确的、系统性的分析。

1变压器代替Boost变换器的反相辅助绕组的方法,该方法可以极大地减小变压器二次侧分布电容,从而有效降低变换器的共模噪声。文献[21]提出了一种共模电压消除法来降低功率变换器的共模噪声,通过增加连接在输入电压和变换器输入端之间的两个绕组,并将它们与励磁电感或变压器耦合,可以产生抵消变换器共模噪声的电压。文献[22]基于电感的分裂绕组配置,在不增加电路体积的情况下,提出了一种新的非隔离DC-DC变换器共模噪声消除方法。文献[23]通过对共模噪声抑制机理的分析,基于大匝比的反相绕组法,建立了插入损耗下的完整数学模型。然而,针对输出浮动式Boost变换器的共模噪声产生机理尚无明确的、系统性的分析。

(1)

(1)

、

、 、

、 和

和 分别为节点A

分别为节点A (2)

(2)

为

为 (3)

(3) (4)

(4)

、

、 、

、 和

和 分别为节点A

分别为节点A (5)

(5)

为

为 (6)

(6) (7)

(7)

为

为 (8)

(8) (9)

(9)

(10)

(10) 两端,不对共模噪声电流产生影响,流经采样电阻的噪声电流I

两端,不对共模噪声电流产生影响,流经采样电阻的噪声电流I (11)

(11)

为

为 (12)

(12) (13)

(13)

为

为 (14)

(14) 、

、 可分别表示为

可分别表示为 (15)

(15)