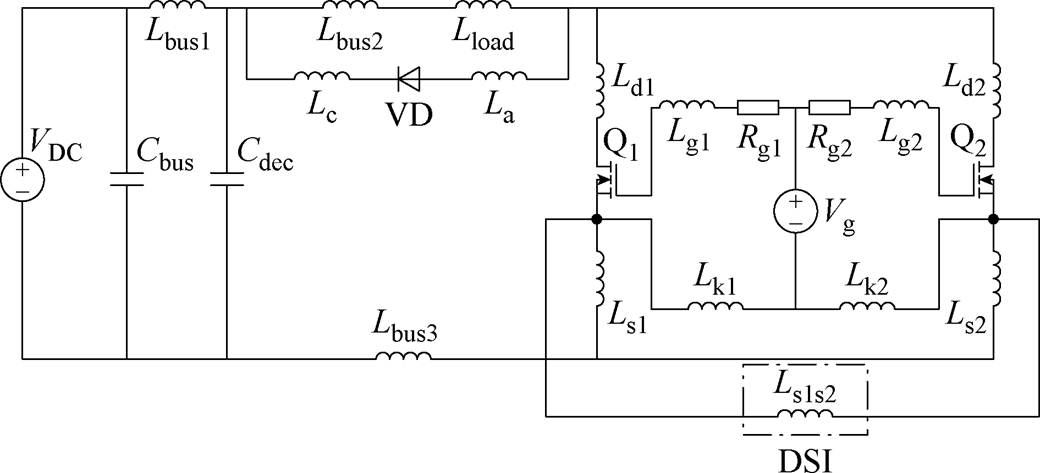

图1 优化功率模块的寄生电路模型

Fig.1 The parasitic circuit model of the optimized power module

摘要 并联SiC MOSFETs是提高大功率电力电子系统电流容量的经济高效方法。然而,在多芯片功率模块中,容易出现动态电流不平衡现象。该文提出一种在并联SiC MOSFETs芯片之间进行源极直连的动态均流方法。基于电路模型和理论分析,阐明动态电流不平衡机理和动态均流方法的作用机制。仿真和实验均验证了该机理和方法的有效性。研究表明,采用该文提出的动态均流方法后,并联SiC MOSFETs的动态电流差异和开关损耗差异降低大于50%;另外,在具有更多芯片并联的SiC功率模块中验证了该方法的有效性。与传统方法相比,且该方法无需增加额外的大体积元件,也无需改变直接覆铜陶瓷(DBC)基板的布局,实现简单,经济性高。同时,与传统的制程技术兼容性好,且不需要复杂设计或精确计算,能够很好地满足极简封装制程的要求。

关键词:并联SiC MOSFETs 动态电流不平衡 动态均流方法 源极直连(DSI)多芯片SiC功率模块

碳化硅(Silicon Carbide, SiC)金属-氧化物-半导体场效应晶体管(Metal-Oxide-Semiconductor Field Effect Transistor, MOSFET)具有高阻断电压、高开关频率、低导通电阻和出色的热性能[1-3]。因此,它被认为在大功率领域中具有广泛的应用前景,如混合动力或全电动汽车、新能源发电和充电桩[4-10]。随着对更高额定功率的需求持续上升[11-12],SiC MOSFET芯片需要更高的电流容量。然而,受限于制造水平和成本,单个芯片的有源区有限。因此,单个SiC MOSFET芯片的额定电流受到限制[13]。

SiC MOSFETs的并联工作是提高电流容量的有效解决方案[14-16]。然而,由于芯片布局的不对称、芯片参数的不匹配以及散热条件的不同,多芯片并联功率模块中的动态电流不平衡是不可避免的。不平衡的动态电流将带来一系列问题,包括电流过冲[17]、栅极电压振荡[18]、损耗不均匀[19]和结温不均匀[20]。值得特别注意的是,SiC MOSFET的阈值电压Vth具有明显的负温度特性。因此,结温较高的SiC MOSFET将具有较低的Vth,进而承受更高的动态电流[21],该机制会导致并联芯片中出现热失控现象,且开关频率和电流水平越高,热失控的风险也越高[22]。此外,Vth的减小也会增加串扰并引起误开通现象,这些都会降低芯片的预期寿命,导致提前失效,降低了系统的稳定性。因此,很有必要研究多芯片功率模块中,并联SiC MOSFETs的动态电流不平衡机理和动态均流方法。

过去的研究已对动态电流不平衡机理进行了探讨。开尔文源极连接已经被广泛用于并联SiC MOSFETs中,以提高开关速度和降低开关损耗[19, 23-24]。文献[23]的实验结果表明,采用开尔文源极连接可以有效地缓解动态电流不平衡现象。文献[24]的研究进一步得出,阈值电压和功率源极寄生电感不平衡是导致动态电流不平衡的主要因素,而其他寄生电感的不平衡影响相对较小。然而,这些研究中并没有揭示动态电流不平衡的内在机理。文献[19]的研究指出,栅极和驱动源极之间的电流差异反映了功率回路对驱动回路的扰动,且电流差异越大,动态电流不平衡越严重。尽管如此,该研究并未深入分析这一现象的产生原因及其内在机理。文献[25]揭示了动态电流不平衡的内在机理,不平衡的功率源极电流会导致源极电压差异和驱动回路差异,进而导致动态电流差异。但是,文献[25]没有说明功率回路和驱动回路之间的电流耦合和产生原因。因此,为进一步优化并联SiC MOSFETs的动态均流性能,仍需对并联芯片动态电流不平衡进行进一步分析。

对过去并联芯片的动态均流方法进行总结,可以分为有源方法和无源方法。有源方法主要集中在开发有源栅极驱动器(Active Gate Driver, AGD)技术[26]。例如,文献[27]利用电流传感器测量每个器件的电流,从而调整驱动信号实现动态电流的平衡;文献[28]则使用主从栅极驱动器进行驱动电压跟随,进而平衡动态电流。这些有源方法都能有效地改善并联SiC MOSFET分立器件的动态均流性能。然而,它们很难应用到多芯片功率模块中,因为功率模块内部没有足够的空间来插入电流传感器和处理电路。同时,这种方法显著增加了成本和复杂性。

无源方法通常是在功率模块内部添加额外的无源元件。在文献[29]中,通过引入陶瓷去耦电容器,以实现平衡的动态电流和较小的回路电感。文献[25]则在功率回路中加入RC缓冲器,减轻了动态电流的不平衡。然而,这些方法需要对无源元件进行精细设计,而且不可避免地增加了占地面积,破坏了原有的直接覆铜陶瓷(Direct Bonded Copper substrate, DBC)基板的布局。此外,文献[30]通过在每个驱动源分支使用电阻来缓解动态电流的不平衡。在文献[31-32]中,将耦合电感用于每个功率源极分支,实现动态电流平衡,这些方法需要使用额外的电阻或电感,增加了制造过程的复杂性。文献[33]中,在栅极回路中引入带辅助电路的附加电阻,来减轻不对称布局引起的环流,从而实现动态电流平衡。然而,这种方法需要增加额外的电流放大级和有源开关,增加了成本且降低了系统的稳定性。在上述方法中,当多于两个芯片并联时,添加无源元件的设计和制造过程将变得非常复杂。因此,这种方法也难以用在多芯片功率模块中。而且,添加这些无源元件也会增加总成本。

另一种无源方法是优化功率模块的结构。在文献[34-35]中提出了几种方案来实现功率回路,以获得平衡的动态电流。文献[36]介绍了具有多端子的布局结构。上述方案虽然能获得较好的动态均流效果,但需要改变原有DBC基板的布局,不利用实际应用。在文献[19, 37]中,调整键合线和铜迹长度以获得对称的功率源极寄生电感,实现动态电流平衡。然而,这种方法需要精确计算和控制键合线长度及连接处,相对复杂。

本文提出了一种在并联SiC MOSFETs芯片的源极之间采用直连(Direct Source Interconnection, DSI)的方式,来实现平衡的动态电流。并联SiC MOSFETs芯片的源极之间通常采用的是间接互连的方式。具体地,源极键合线一端在芯片源极;一端在DBC基板,并联芯片的源极间接通过DBC基板上的铜迹进行互连。在此基础上,本文提出的源极直连方式,指并联SiC MOSFETs芯片的源极之间直接通过键合线进行互连。该方法通过改变功率模块内部芯片之间的互连来实现均流,属于无源方法。与有源方法相比,该方法不需要复杂的传感器或处理电路,兼容性好;与以往无源方法相比,该方法不需要增加电阻、电感或电容等无源元件,实现简单,经济性高。而且,不需要改变原有DBC基板的布局,也不需要复杂的结构设计和精确的计算。此外,该方法与传统的制程技术兼容性好,能够很好地满足极简封装制程的要求。首先,本文深入分析了在开尔文源极连接下,采用DSI方法和未采用DSI方法时,并联SiC MOSFETs的动态电流不平衡机理。基于电路建模和数学分析,揭示了并联SiC MOSFETs在不平衡功率源极寄生电感下,功率回路和驱动回路之间电流耦合的机制,进一步明确了该电流耦合引起的驱动回路差异和动态电流差异。在推导的机理中,确定了影响动态电流不平衡的关键参数。基于上述机理,本文详细解释了DSI动态均流方法的作用机制。其次,本文设计了采用DSI动态均流方法的SiC功率模块,并针对不同DSI参数下功率模块的动态均流效果进行讨论。最后,本文通过仿真和实验,验证了在不同参数下,动态电流不平衡机理和DSI动态均流方法的有效性。

本节首先推导了并联芯片动态电流不平衡机理,然后利用该机理的结论,分析DSI动态均流方法的作用机制。过去的研究表明,在具有开尔文源极连接的多芯片并联电路中,引起动态电流不平衡的主要因素是功率源极寄生电感,相比之下,其他寄生电感对动态不均流的影响很小。因此,本节建立带开尔文源极连接的动态电路模型,研究不平衡功率源极寄生电感下的并联芯片动态电流不平衡机理。通过对比采用DSI方法的功率模块(优化功率模块)和未采用DSI方法的功率模块(初始功率模块)的结果,分析该动态均流方法的作用机制。

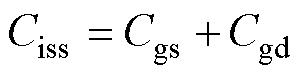

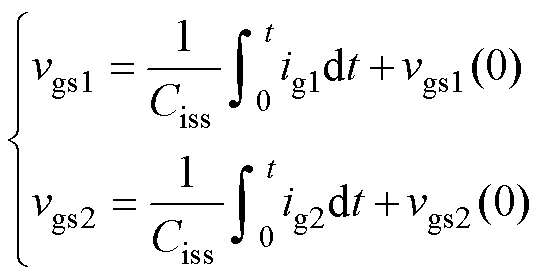

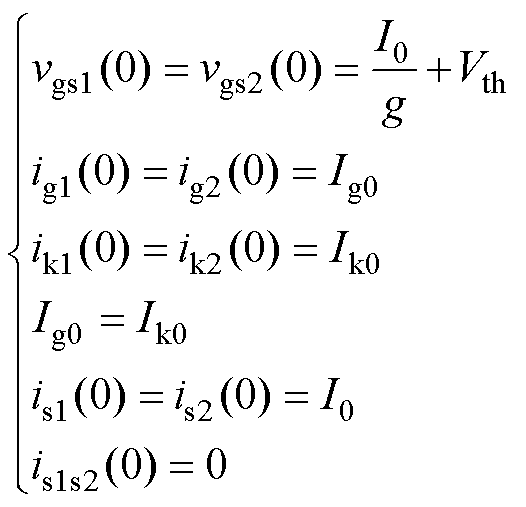

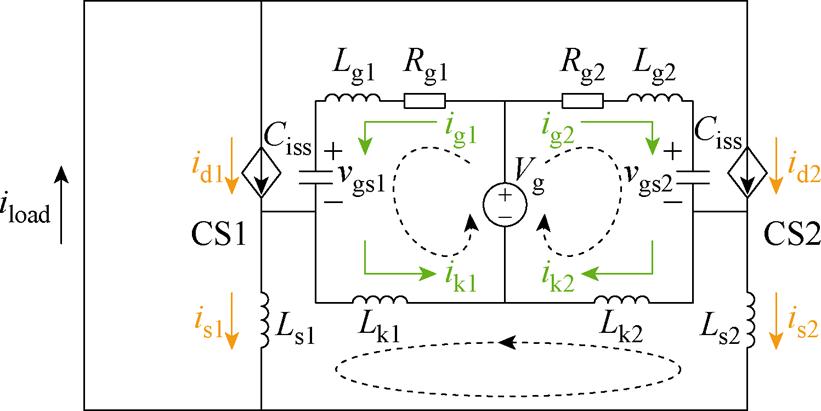

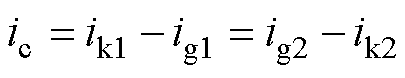

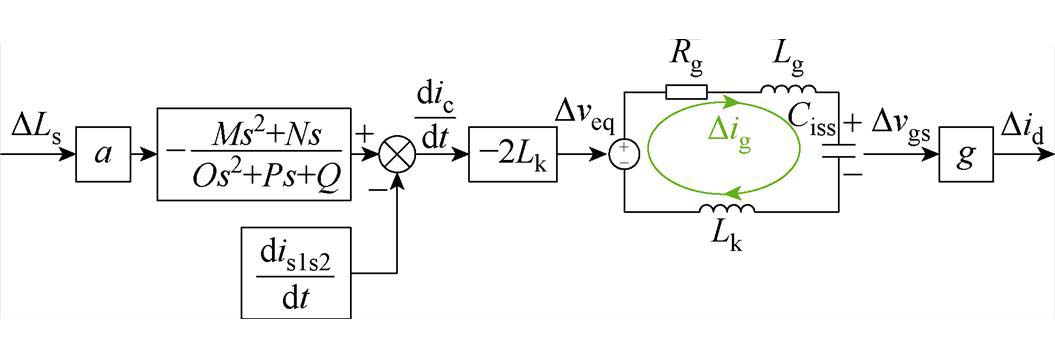

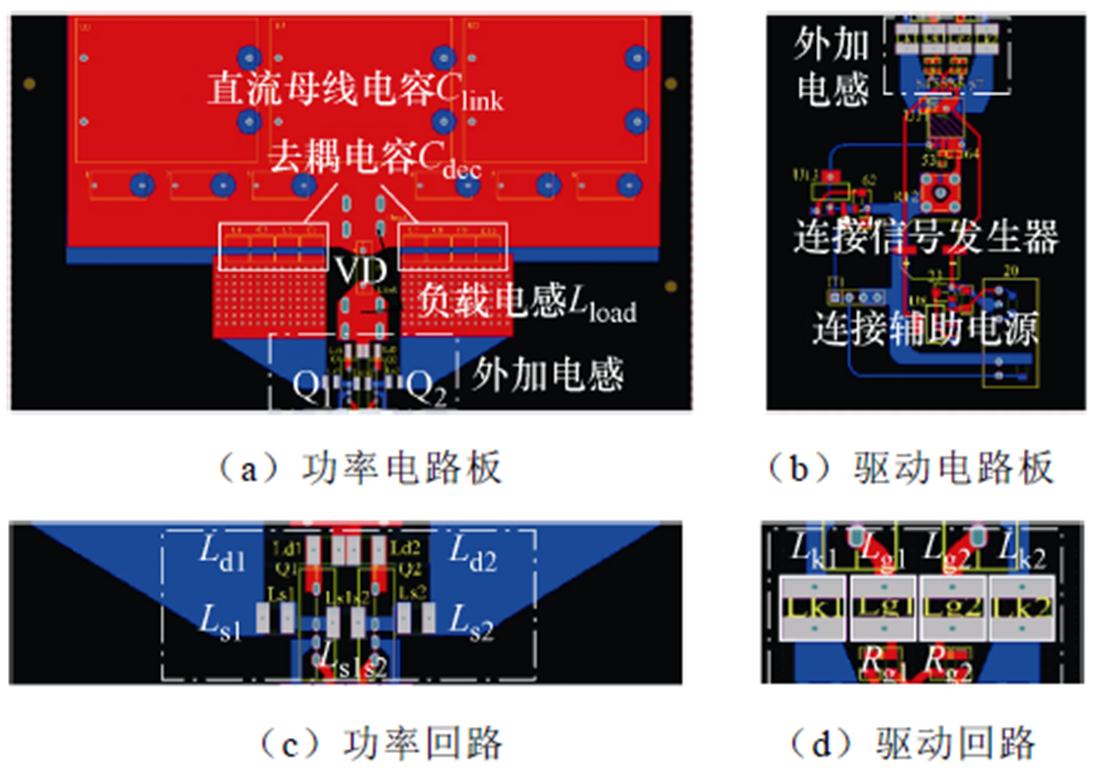

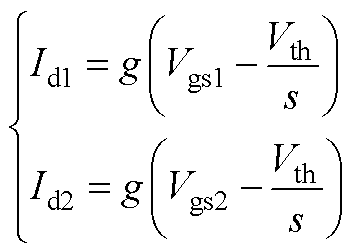

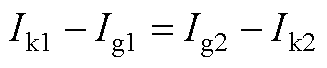

图1展示了具有两个SiC MOSFET并联的优化功率模块在双脉冲测试下的动态电路模型。其中,DSI动态均流方法引入的支路用点画线框突出表示。图1中各元件的含义见表1。

图1 优化功率模块的寄生电路模型

Fig.1 The parasitic circuit model of the optimized power module

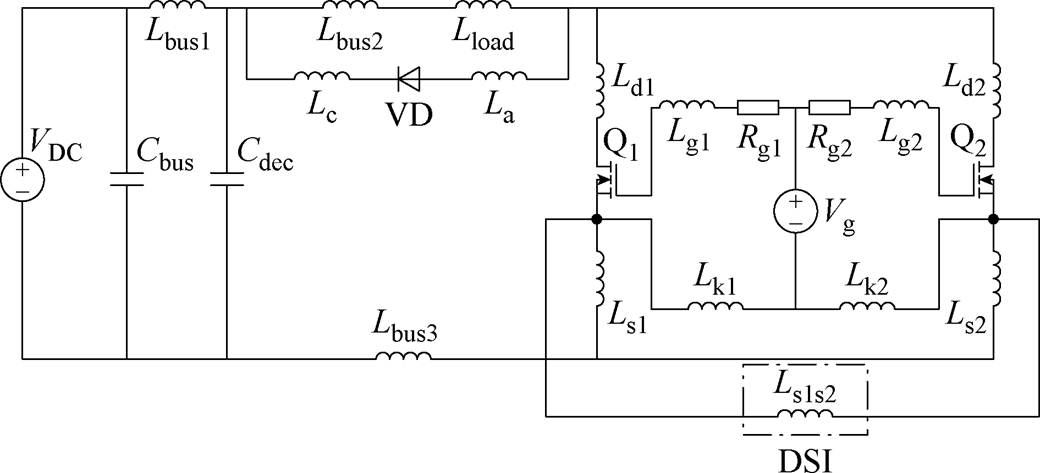

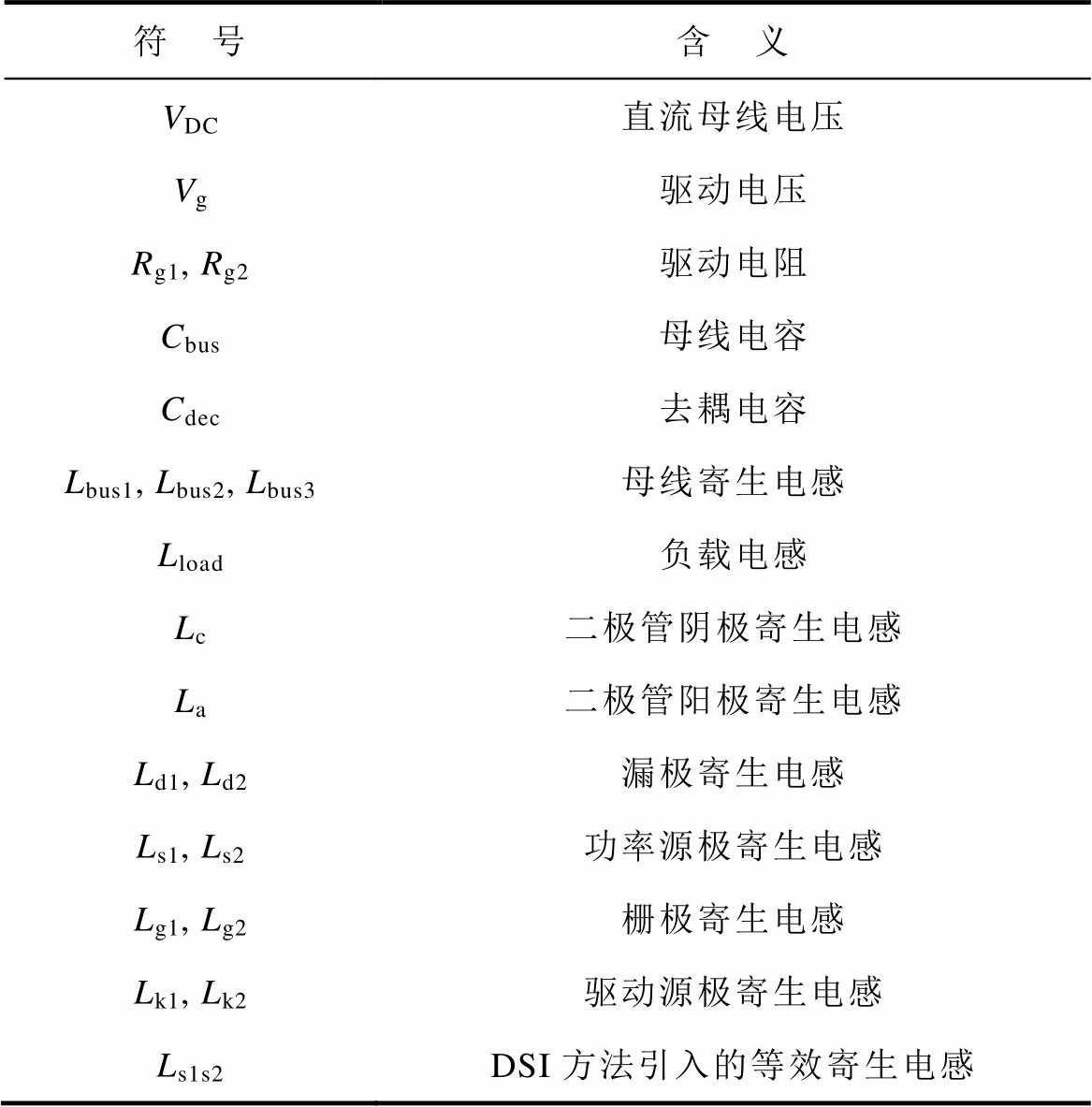

表1 各元件的含义

Tab.1 Meanings of each component

符 号含 义 VDC直流母线电压 Vg驱动电压 Rg1, Rg2驱动电阻 Cbus母线电容 Cdec去耦电容 Lbus1, Lbus2, Lbus3母线寄生电感 Lload负载电感 Lc二极管阴极寄生电感 La二极管阳极寄生电感 Ld1, Ld2漏极寄生电感 Ls1, Ls2功率源极寄生电感 Lg1, Lg2栅极寄生电感 Lk1, Lk2驱动源极寄生电感 Ls1s2DSI方法引入的等效寄生电感

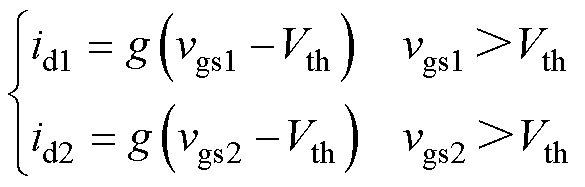

动态电流不平衡发生在开关瞬间。此时,SiC MOSFETs工作在饱和区。因此,Q1和Q2能等效建模为由栅源电压vgs控制的电流源id,表示为

(1)

(1)

式中,g为SiC MOSFET的跨导;Vth为SiC MOSFET的阈值电压。受本文研究功率源极寄生电感的影响,认为SiC MOSFETs中的g、Vth均相等。

漏源寄生电容Cds可以忽略[35],输入电容Ciss由栅漏寄生电容Cgd和栅源寄生电容Cgs并联而 成[38],表示为

(2)

(2)

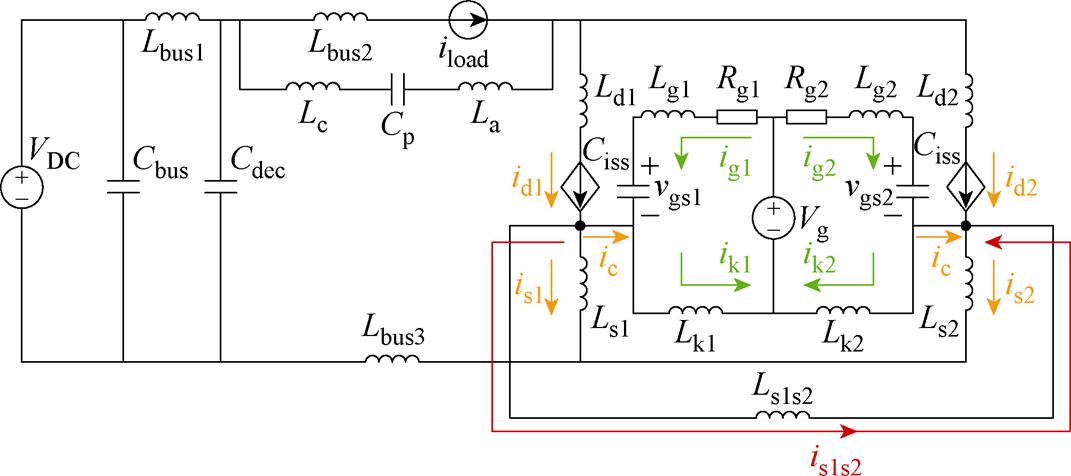

负载电感等效建模为电流源iload,续流二极管等效建模为寄生电容Cp。基于上述分析,图1中的电路可以等效为图2所示的优化功率模块的初始动态电路模型。

图2 优化功率模块的初始动态电路模型

Fig.2 The initial dynamic circuit model of the optimized power module

考虑到动态电流不平衡主要受并联支路差异的影响,且漏极寄生电感Ld1和Ld2与电流源串联。因此,图2电路可以进一步简化为图3所示的优化功率模块的简化动态电路模型。

图3 优化功率模块的简化动态电路模型

Fig.3 Simplified dynamic circuit model of the optimized power module

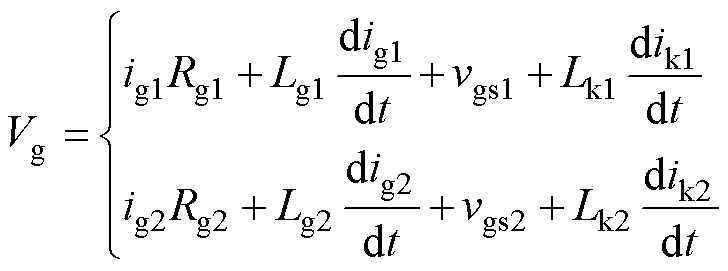

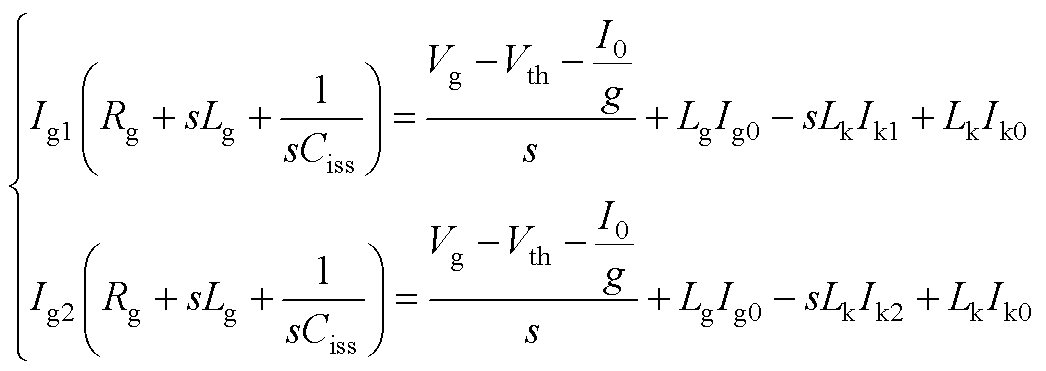

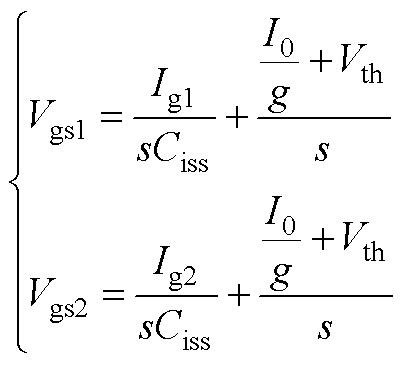

本文利用图3的简化电路进行后续分析。用基尔霍夫电压定律(Kirchhoff’s Voltage Law, KVL)求解图3中的4个闭合回路,如黑色虚线所示。将KVL应用于驱动回路中,可以表示为

(3)

(3)

式中,栅源电压vgs1和vgs2可分别表示为

(4)

(4)

式中,vgs1(0)和vgs2(0)分别为vgs1和vgs2在初始时刻的值。将开通或关断的开始时刻,即动态电流开始变化时刻,定义为电路的初始时间(t=0)。

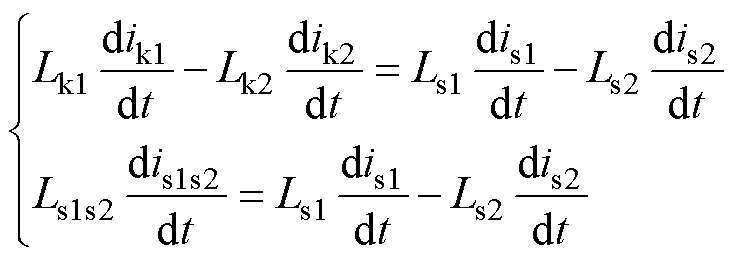

将KVL分别运用于包含Ls1、Ls2、Lk1和Lk2的回路以及包含Ls1、Ls2和Ls1s2的回路,其关系表 示为

(5)

(5)

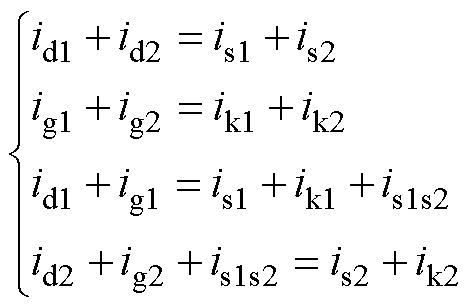

用基尔霍夫电流定律(Kirchhoff’s Current Law, KCL)求解图3中的功率回路、驱动回路和CS节点,表示为

(6)

(6)

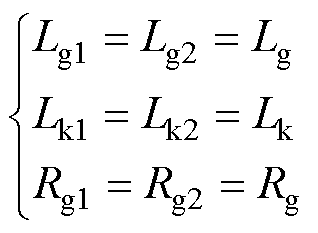

在进行后续推导之前,本文做出以下合理假设:

(1)本文重点研究不平衡功率源极寄生电感对动态均流的影响,认为

(7)

(7)

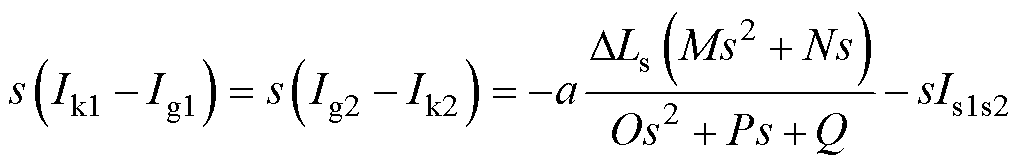

(2)忽略静态电流差异,图3电路中各参数的初始值定义为

(8)

(8)

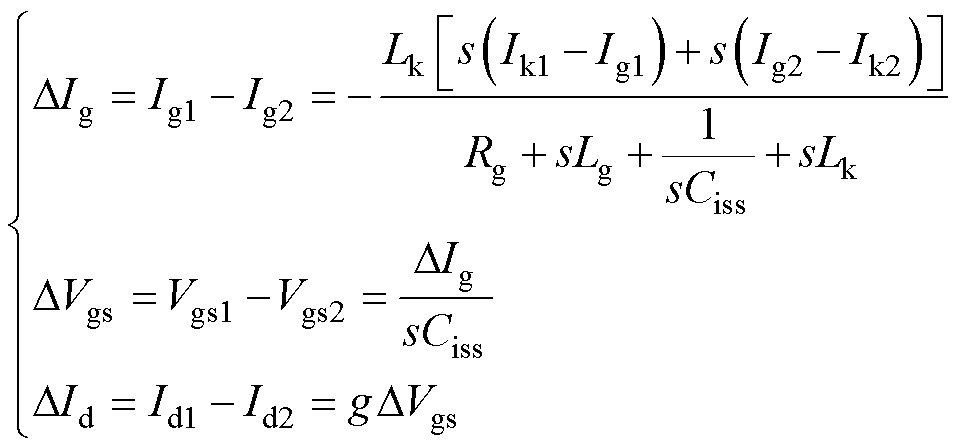

基于式(1)~式(8)进行拉普拉斯变换,得到式(A1)~式(A5),具体公式和推导过程见 附录。

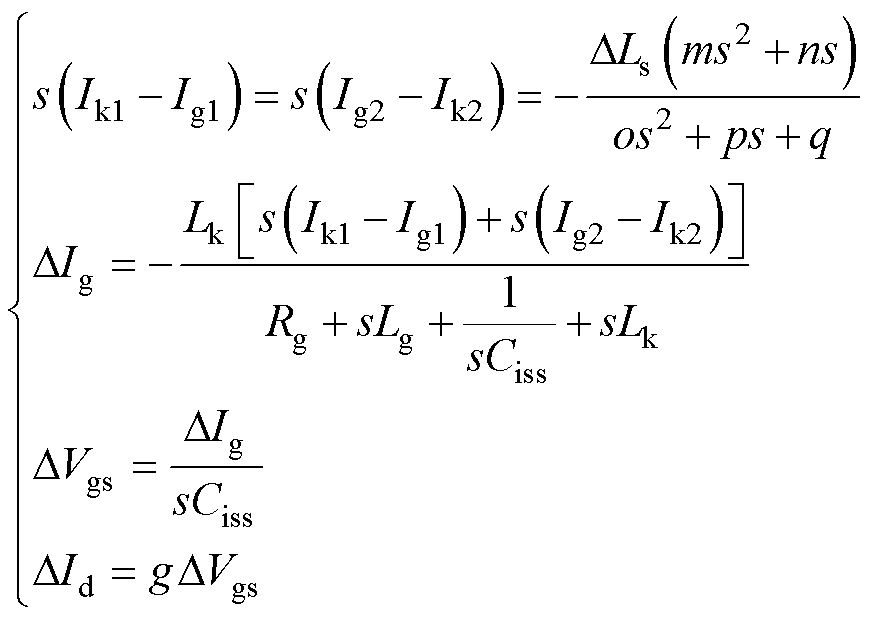

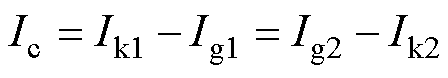

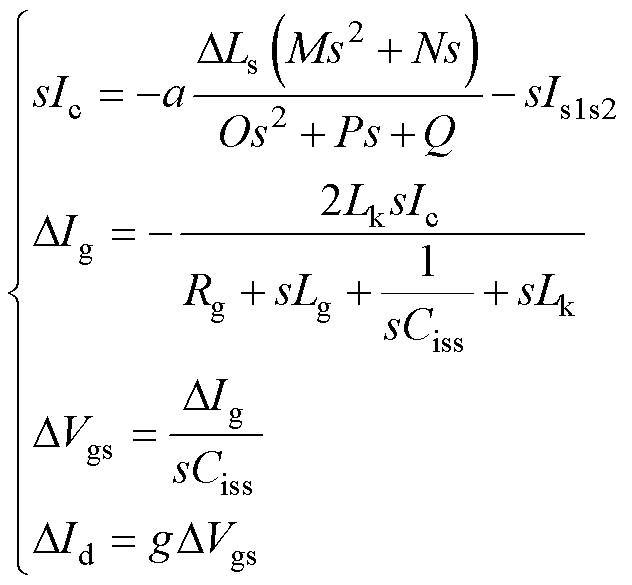

式(A1)~式(A3)中各自两个式子相减,再经过化简得到

(9)

(9)

式中,s为拉普拉斯算子。

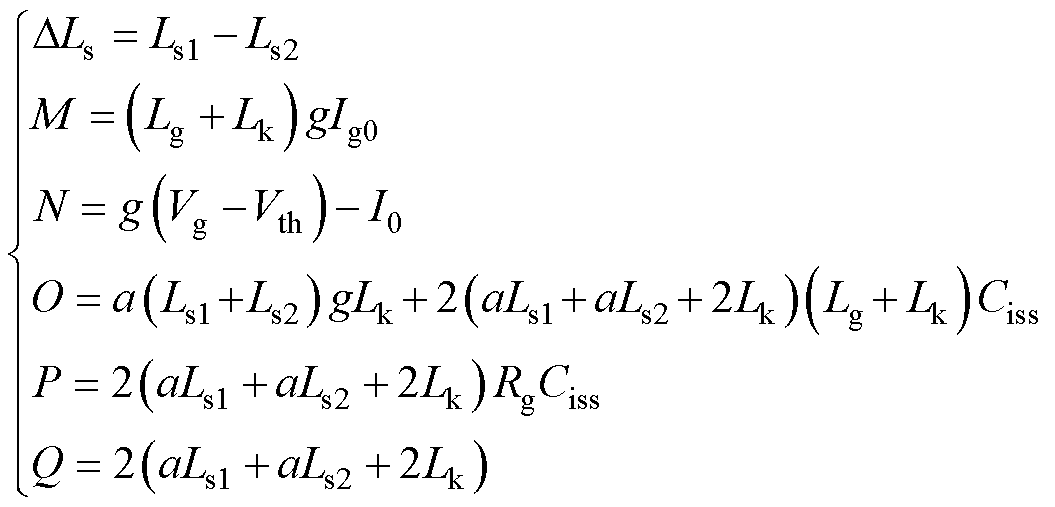

结合式(A1)~式(A5),化简得到

(10)

(10)

其中

(11)

(11)

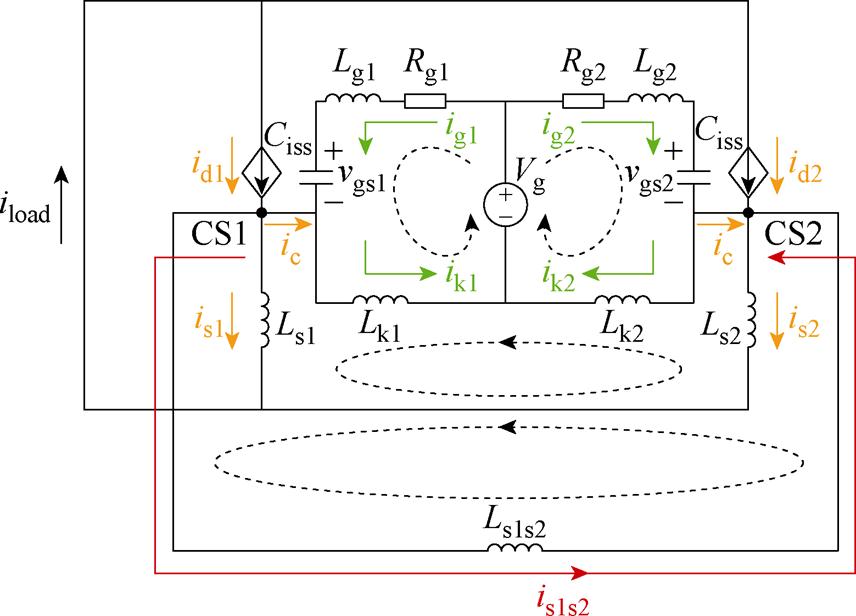

式中,a为不平衡电感衰减系数,a=Ls1s2/(Ls1+Ls2+Ls1s2),数值范围为0<a≤1,并且随Ls1s2的减小而减小。

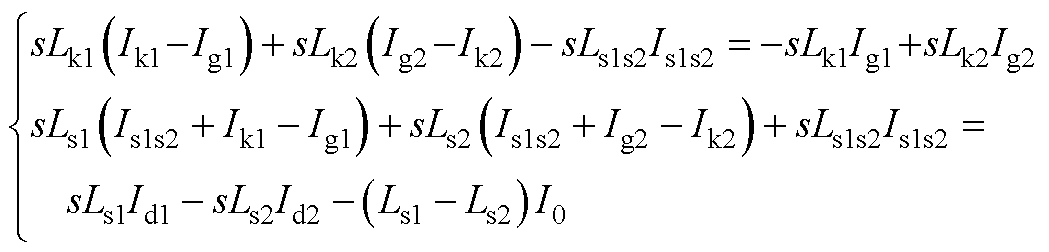

由式(9)~式(11)构成了优化功率模块的动态电流不平衡机理。移除Ls1s2支路,则可以得到初始功率模块的简化动态电路模型如图4所示。

图4 初始功率模块的简化动态电路模型

Fig.4 Simplified dynamic circuit model of the initial power module

此时,相当于Ls1s2支路开路,即Ls1s2 Ls1+Ls2,则不平衡电感衰减系数a=1。而且,无支路电流is1s2。

Ls1+Ls2,则不平衡电感衰减系数a=1。而且,无支路电流is1s2。

因此,由式(9)~式(11)变换可以得到,初始功率模块的动态电流不平衡机理为

(12)

(12)

其中

(13)

(13)

文献[23]研究指出,开尔文源极连接可以解耦功率回路和驱动回路,从而改善动态电流不平衡。但本研究揭示的机理表明,功率源极寄生电感差异DLs仍然会引起芯片栅极和驱动源极之间的差动电流,进而加剧功率回路和驱动回路的耦合程度。在一定时间内,差动电流越大,耦合越严重,进而导致更大的栅极差异和动态电流不平衡。

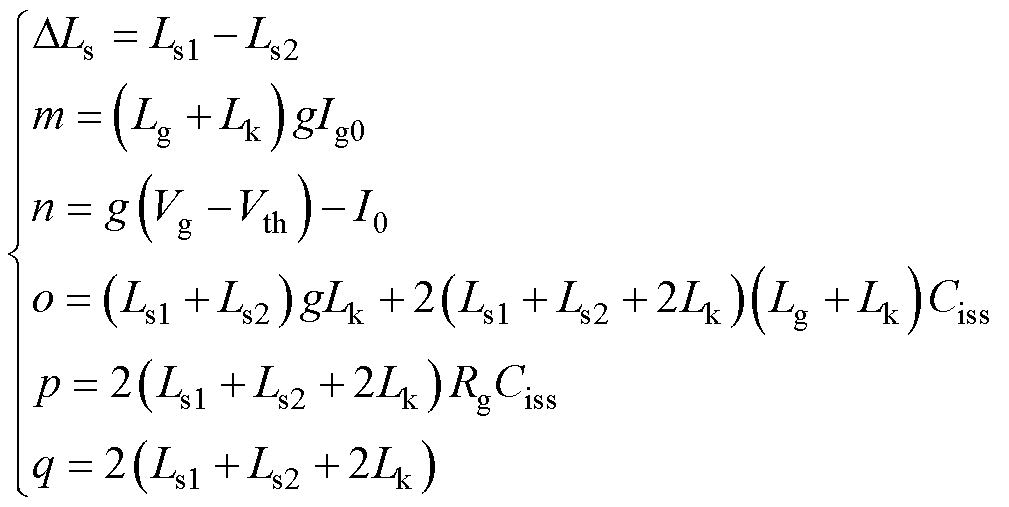

图5展示了DLs引起功率回路和驱动回路耦合的物理机制。若移除Ls1s2支路,则对应于初始功率模块的情况,在开关瞬间,功率源极寄生电感差异DLs会在动态电流的作用下产生感应电压差Dvs(即vs1-vs2)。该电压差会在功率回路中产生一个环流ic,并流经驱动回路,进而导致功率回路和驱动回路之间的电流耦合。然而,采用DSI方法后,Ls1s2支路的存在减小了环流 ic

ic ,具体而言,在开关瞬间,部分动态电流将流经Ls1s2支路,从而降低电压差

,具体而言,在开关瞬间,部分动态电流将流经Ls1s2支路,从而降低电压差 Dvs

Dvs 。此外,由该电压差产生的环流被分为两部分:ic流经驱动回路;is1s2流经Ls1s2支路。因此,采用DSI动态均流方法后,在一定时间内流经驱动回路的环流

。此外,由该电压差产生的环流被分为两部分:ic流经驱动回路;is1s2流经Ls1s2支路。因此,采用DSI动态均流方法后,在一定时间内流经驱动回路的环流 ic

ic 将减小,从而降低了功率回路和驱动回路的耦合程度,进而减小了动态电流的差异。

将减小,从而降低了功率回路和驱动回路的耦合程度,进而减小了动态电流的差异。

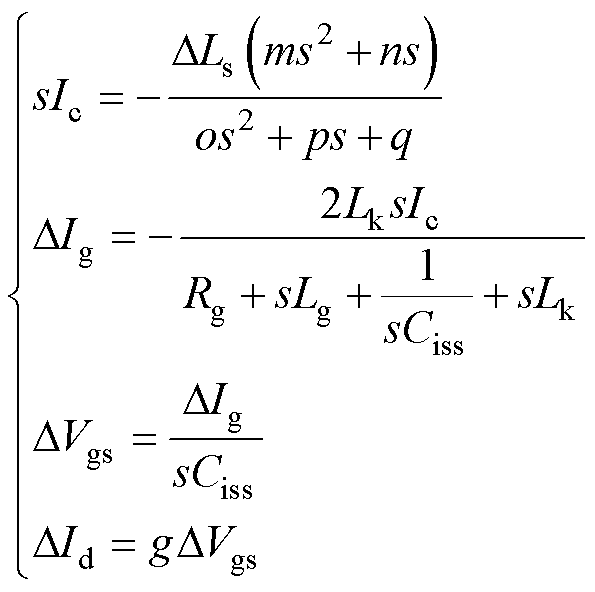

结合图4电路,栅极和驱动源极的差动电流,也就是环流ic,可以表示为

图5 不平衡功率源极寄生电感引起的环流示意图

Fig.5 Schematic diagram of the circulating current caused by the asymmetrical power source

(14)

(14)

由式(8)可知,ig1(0)=ik1(0)=ig2(0)=ik2(0),则环流ic初始值ic(0)=0,将式(14)进行拉普拉斯变换,可以得到

(15)

(15)

最终,结合式(12)和式(15),初始功率模块的动态电流不平衡机理可以表示为

(16)

(16)

在一定时间内,环流 ic

ic 的大小表征了功率回路和驱动回路的耦合程度,与文献[22]的结论一致。

的大小表征了功率回路和驱动回路的耦合程度,与文献[22]的结论一致。

结合式(9)、式(10)和式(15),优化功率模块的动态电流不平衡机理为

(17)

(17)

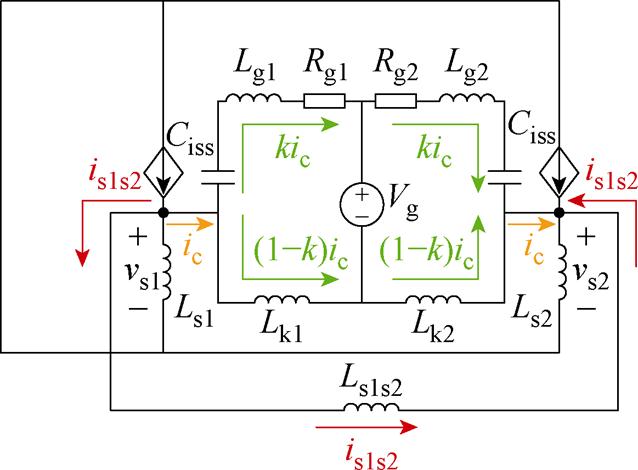

动态电流不平衡机理在时域解下的等效电路如图6所示。电路的初始条件为0,即Dig=0,Dvgs=0。若移a分量和-dis1s2/dt分量,则可得到初始功率模块的情况。结果表明,由DLs引起的环流ic在驱动源极电感Lk上产生感应电压-2Lkdic/dt,进而导致驱动回路中的Dig和Dvgs,最终形成动态电流差Did。dic/dt为引起驱动回路差异和动态电流不平衡的主要因素。

图6 动态电流不平衡等效电路

Fig.6 Dynamic current imbalance equivalent circuit

DSI方法旨在减小 dic/dt

dic/dt ,从而实现动态电流平衡,如图6中a分量和-dis1s2/dt分量所示。DSI动态均流方法的作用机制可以解释如下:采用DSI后,引入了不平衡电感衰减系数a(0<a≤1

,从而实现动态电流平衡,如图6中a分量和-dis1s2/dt分量所示。DSI动态均流方法的作用机制可以解释如下:采用DSI后,引入了不平衡电感衰减系数a(0<a≤1 和电流变化抑制分量-dis1s2/dt。这使得功率源极寄生电感差异降低至

和电流变化抑制分量-dis1s2/dt。这使得功率源极寄生电感差异降低至 aDLs

aDLs ,同时流经驱动回路的环流变化率还要减小

,同时流经驱动回路的环流变化率还要减小 dis1s2/dt

dis1s2/dt ,因此,由DLs引起的

,因此,由DLs引起的 dic/dt

dic/dt 减小。相应地,在驱动源极电感Lk上产生的感应电压

减小。相应地,在驱动源极电感Lk上产生的感应电压 2Lkdic/dt

2Lkdic/dt 也减小,进而减小了驱动回路差异

也减小,进而减小了驱动回路差异 Dig

Dig 和

和 Dvgs

Dvgs ,最终实现了

,最终实现了 Did

Did 的减小。采用DSI方法后,可以有效地减小

的减小。采用DSI方法后,可以有效地减小 dic/dt

dic/dt 和

和 Did

Did ,从而实现更加平衡的动态电流。

,从而实现更加平衡的动态电流。

图6中展示了DLs、dic/dt、Dig、Dvgs和Did之间的关系。结合式(8)、式(11)和式(13)可知,在开通时刻,DLs与dic/dt同号;在关断时刻,DLs与dic/dt异号。此外,图6中电路还表明dic/dt与Dig、Dvgs、Did异号。具体而言,当dic/dt>0时,Dig<0,Dvgs<0,从而导致Did<0;当dic/dt<0时,Dig>0,Dvgs>0,进而使得Did>0。基于上述动态电流不平衡机理,不同情况下的动态电流分布可以总结如下:

(1)当Ls1=Ls2,即DLs=0时,开通和关断时刻dic/dt=0。此时,Dig=0,Dvgs=0,Did=0,即id1=id2。

(2) 当Ls1<Ls2,即DLs<0时,开通时刻dic/dt<0,Dig>0,Dvgs>0,Did>0,即id1>id2;关断时刻dic/dt>0,Dig<0,Dvgs<0,Did<0,即id1<id2。

(3) 当Ls1>Ls2,即DLs>0时,开通时刻dic/dt>0,Dig<0,Dvgs<0,Did<0,即id1<id2;关断时刻dic/dt<0,Dig>0,Dvgs>0,Did>0,即id1>id2。

上述结论与文献[24]一致,即功率源极寄生电感越小,相应位置的MOSFET的开通电流越大,而关断电流越小。该结论在优化功率模块和初始功率模块都成立。

从图6也可以得到 DLs

DLs 、

、 dic/dt

dic/dt 、

、 Dig

Dig 、

、 Dvgs

Dvgs 和

和 Did

Did 之间的大小关系。在其他参数一定时,

之间的大小关系。在其他参数一定时, DLs

DLs 越小,则

越小,则 dic/dt

dic/dt 、

、 Dig

Dig 、

、 Dvgs

Dvgs 和

和 Did

Did 越小。为了获得较小的

越小。为了获得较小的 DLs

DLs 和

和 Did

Did ,往往需要重新进行复杂的设计[19, 34-37]。然而,采用DSI方法,不需要改变原有布局,

,往往需要重新进行复杂的设计[19, 34-37]。然而,采用DSI方法,不需要改变原有布局, dic/dt

dic/dt 也将明显减小。因此,可以减小

也将明显减小。因此,可以减小 Dig

Dig 和

和 Dvgs

Dvgs ,进而减小

,进而减小 Did

Did ,该方法简单有效。此时,若Ls1s2越小,a越小、

,该方法简单有效。此时,若Ls1s2越小,a越小、 dis1s2/dt

dis1s2/dt 越大,这将使得

越大,这将使得 dic/dt

dic/dt 越小,

越小, Did

Did 越小,均流效果越优。

越小,均流效果越优。

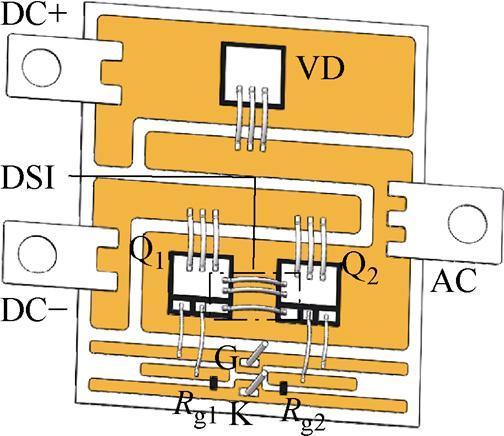

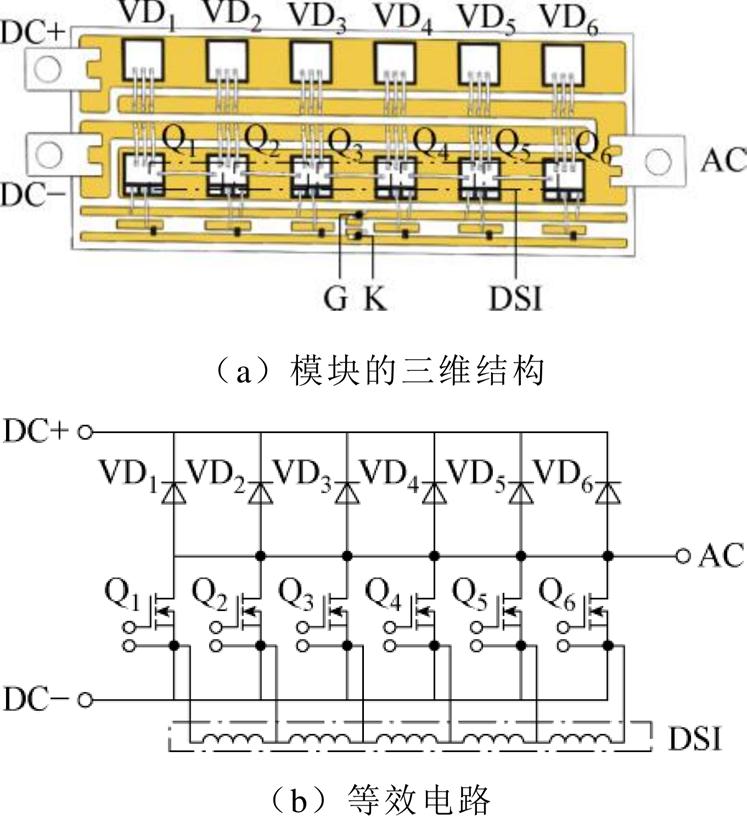

采用DSI方法的SiC功率模块结构如图7所示。模块中,高侧续流二极管VD使用SiC肖特基二极管(S6305),低侧开关使用两个SiC MOSFET(S4103)并联。为了实现动态均流,在相邻的芯片顶部通过键合线进行源极直连,互连的两端分别是相邻两个芯片的源极。该方法无须改变原有DBC基板和芯片布局,也无须额外添加大体积无源元件,因此具有高度的集成性和实现的简便性。此外,该方法便于和其他均流措施灵活结合使用。

图7 优化功率模块的结构

Fig.7 The structure of the optimized power module

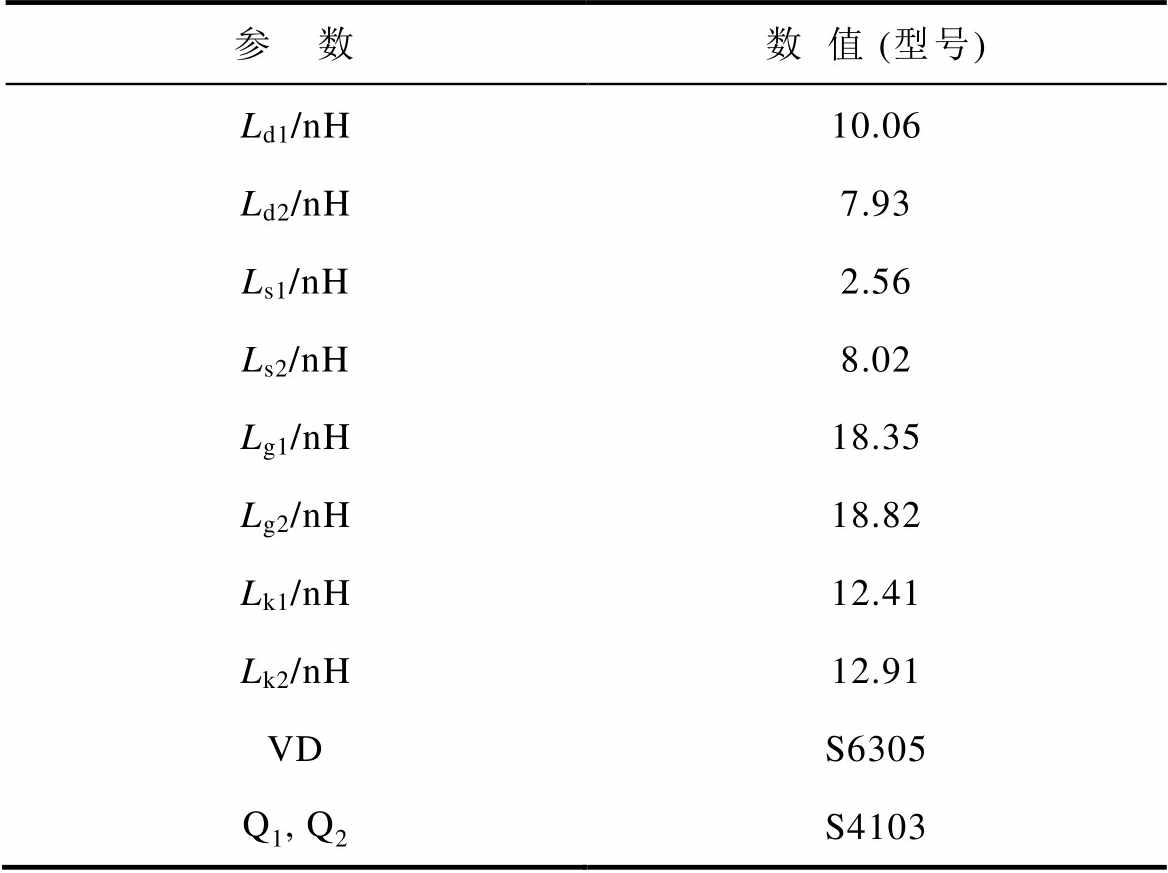

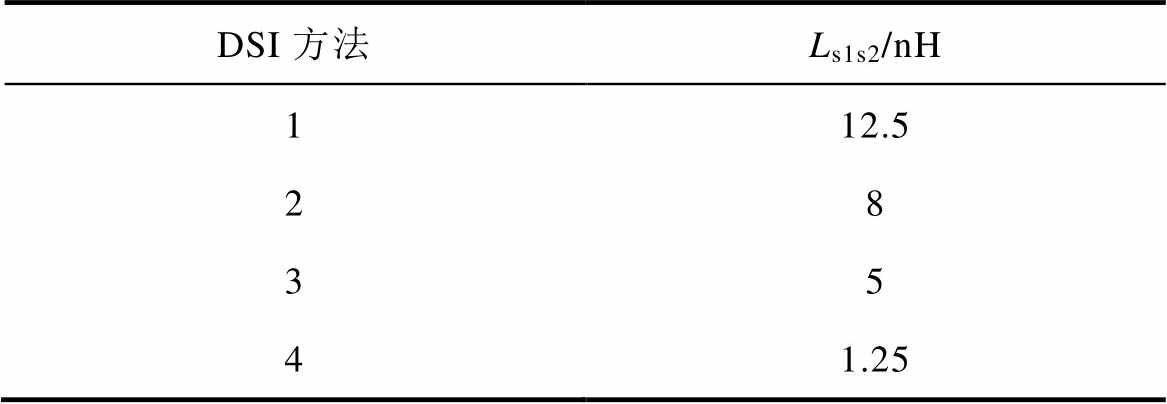

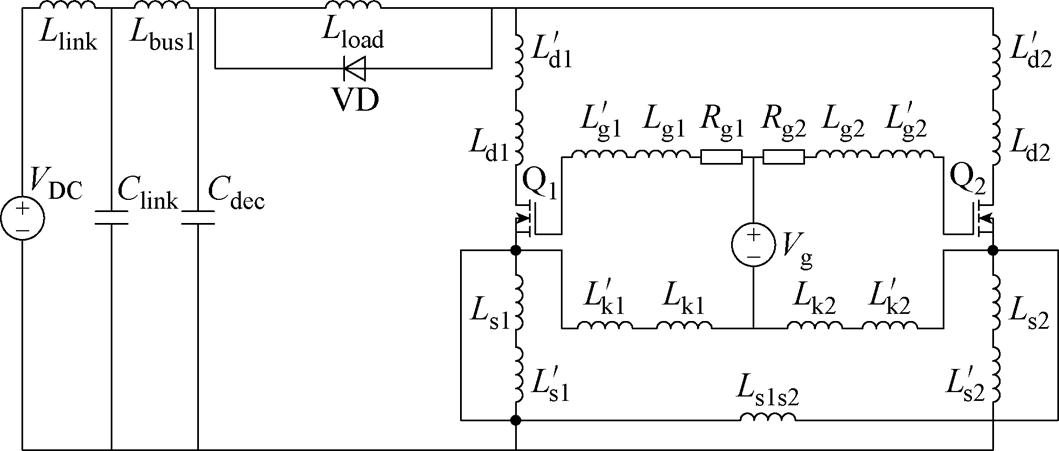

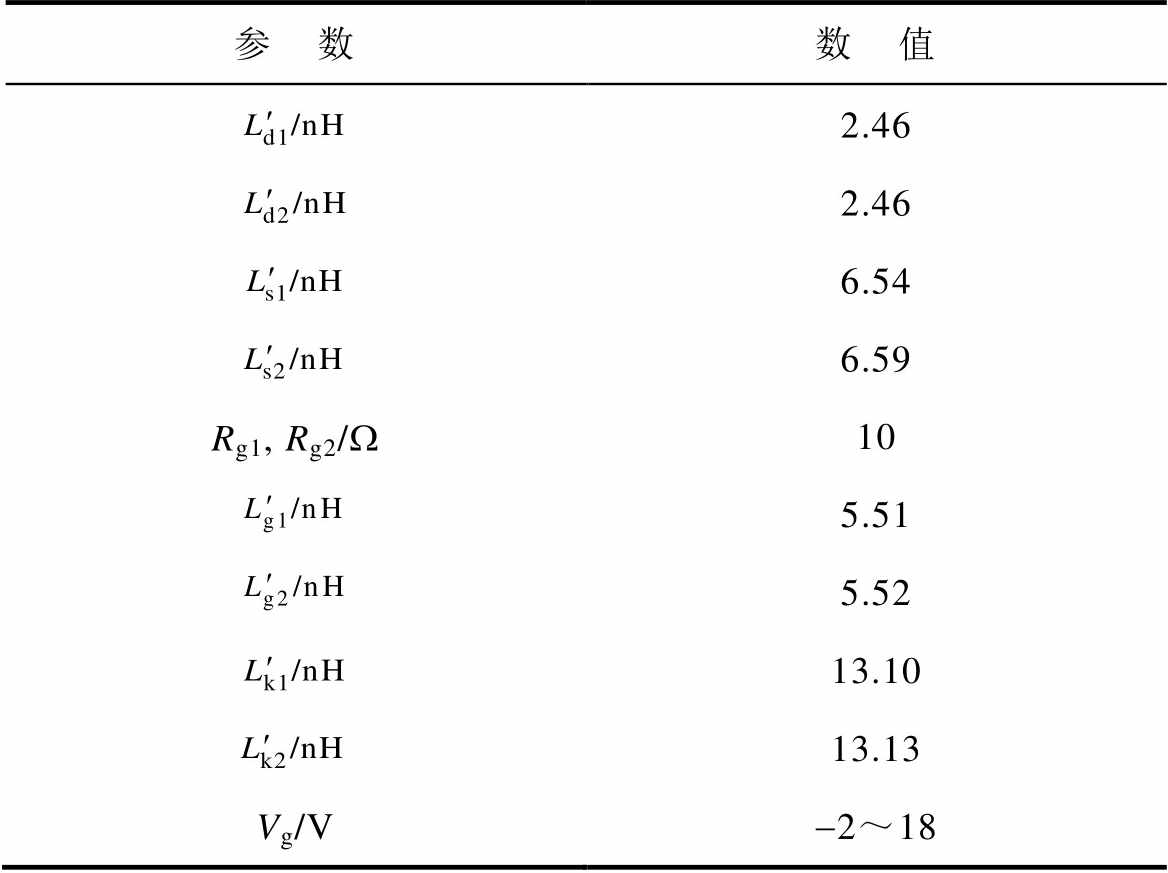

本文利用有限元仿真软件Q3D,提取了未采用DSI时初始功率模块的寄生参数,具体参数见表2。采用DSI方法后,优化功率模块的内部新增了等效寄生电感Ls1s2,表3展示了采用不同DSI参数时,等效寄生电感Ls1s2的数值。当调整DSI方法的键合线位置、数量或参数(如长度、高度和线径等)时,引入了不同数值的等效寄生电感Ls1s2,从而实现了不同程度的均流效果,后续部分将通过仿真和实验来研究不同DSI参数下的均流效果。

为了研究不同寄生参数下的动态电流不平衡机理以及DSI动态均流方法的有效性,需要制造多个功率模块。然而,这将耗费大量的时间、精力和材料。此外,不同功率模块使用的芯片也不一致,这将使得实验变量不唯一,从而严重影响实验结果的准确性和可靠性。鉴于此,本文从考虑实验的经济性、可重复性和准确性出发,选择基于分立器件并联电路进行研究。

表2 初始功率模块的参数

Tab.2 Parameters of the initial power module

参 数数值 (型号) Ld1/nH10.06 Ld2/nH7.93 Ls1/nH2.56 Ls2/nH8.02 Lg1/nH18.35 Lg2/nH18.82 Lk1/nH12.41 Lk2/nH12.91 VDS6305 Q1,Q2S4103

表3 不同DSI方法下的等效寄生电感数值

Tab.3 The equivalent parasitic inductance values under different DSI methods

DSI方法Ls1s2/nH 112.5 28 35 41.25

尽管实验采用了分立器件而非理论推导中的芯片并联,但通过合理的实验设计、严格的变量控制和精确的数据分析,实验结果仍然具有很强的说服力,能够有效验证功率模块中并联芯片的动态电流不平衡机理,以及DSI方法的动态均流效果。

为了等效反映SiC功率模块的特性,本文设计的分立器件并联电路PCB如图8所示。实验中使用的器件(包括VD、Q1和Q2)型号与功率模块中使用的完全一致。此外,设计了两个并联分立器件的PCB走线对称布局,并采用了相同的封装参数制造分立器件,从而确保测试回路的寄生参数保持一致。因此,可以认为两个并联分立器件的寄生电感差异取决于外部插入的电感差异,如图8中点画线框所示,在功率回路(Ld1、Ld2、Ls1、Ls2、Ls1s2)处和驱动回路(Lg1、Lg2、Lk1、Lk2)处分别插入相应的外加电感,以等效不同参数下的功率模块。当Ls1s2支路断开时,等效于未采用DSI方法的功率模块;而在Ls1s2支路插入电感时,则等效于采用DSI方法的功率模块。

外加电感的数值由有限元仿真软件Q3D提取的功率模块寄生参数结果确定。通过在Ls1和Ls2处分别插入不同组数值的功率源极寄生电感,可以研究不同模块参数下的动态电流不平衡机理;通过在Ls1s2处插入不同数值的等效电感,则可以研究不同DSI参数下的动态均流效果。在不同组实验中,只需要更换外加电感,而保持所用分立器件一致,使用并联分立器件的实验,不仅容易更换和控制电感值以验证结论,而且无需更换器件,测量过程也会更加灵活、方便和可靠。这在带有DBC基板的功率模块中是相当困难的。同时,实验结论同样适用于功率模块[24]。

图8 分立器件并联电路的双脉冲测试PCB

Fig.8 Double pulse test PCB for discrete device parallel circuits

为了验证动态电流不平衡机理和动态均流方法的有效性,本文在Pspice软件中搭建双脉冲测试电路进行仿真。其中,通过有限元仿真软件Q3D提取了功率模块和测试板的寄生参数,并用于电路仿真中,该仿真电路模拟了实际工况,精确反映了并联芯片的电流分布情况。通过将仿真结果与理论分析的结论进行对比,从而验证动态电流不平衡机理和动态均流方法的准确性和有效性。

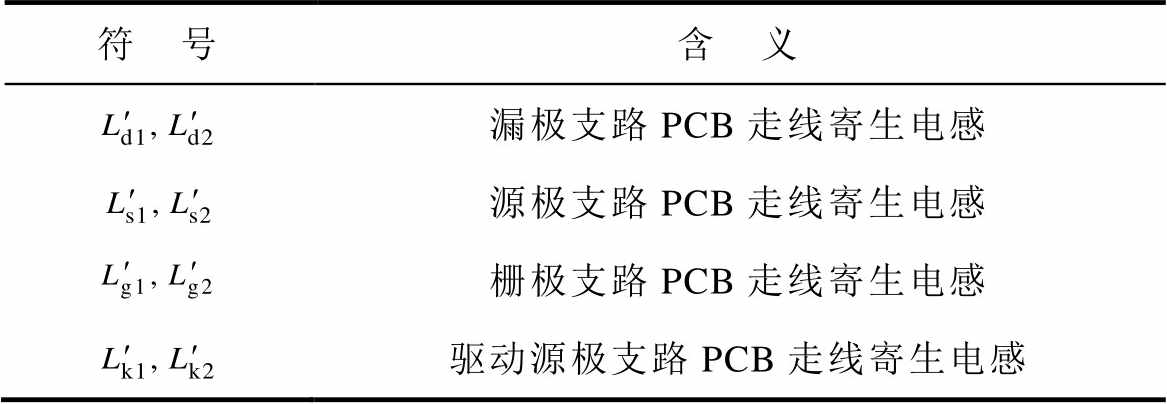

在Pspice中搭建了测试装置的等效电路进行仿真和分析,如图9所示。其中,功率模块的寄生电感,即为在功率回路和驱动回路插入的外加电感,用Ld1、Ld2、Ls1、Ls2、Ls1s2、Lg1、Lg2、Lk1、Lk2表示。不考虑互感影响。利用Q3D提取了此部分寄生电感,见表2和表3。

PCB测试回路走线的寄生电感部分用 、

、 、

、 、

、 、

、 、

、 、

、 、

、 表示,含义见表4,同样利用Q3D提取了此部分寄生电感见表5,采用表2、表3和表5的参数进行仿真。此外,为保持与实验一致,仿真中的直流母线电压VDC和负载电流Iload分别为300 V和60 A。

表示,含义见表4,同样利用Q3D提取了此部分寄生电感见表5,采用表2、表3和表5的参数进行仿真。此外,为保持与实验一致,仿真中的直流母线电压VDC和负载电流Iload分别为300 V和60 A。

图9 采用DSI方法的双脉冲测试电路的等效电路模型

Fig.9 Parasitic circuit model of the double pulse test circuit using the DSI method

表4 PCB测试回路走线寄生电感的含义

Tab.4 The meaning of parasitic inductance in PCB test loop traces

符 号含 义 漏极支路PCB走线寄生电感 源极支路PCB走线寄生电感 栅极支路PCB走线寄生电感 驱动源极支路PCB走线寄生电感

表5 PCB测试回路的参数

Tab.5 Parameters of the PCB test loop

参 数数 值 2.46 2.46 6.54 6.59 Rg1, Rg2/W10 5.51 5.52 13.10 13.13 Vg/V-2~18

通过移除Ls1s2支路,仿真电路转换为初始功率模块的电路;而添加Ls1s2支路后,仿真电路转换为优化功率模块的电路。

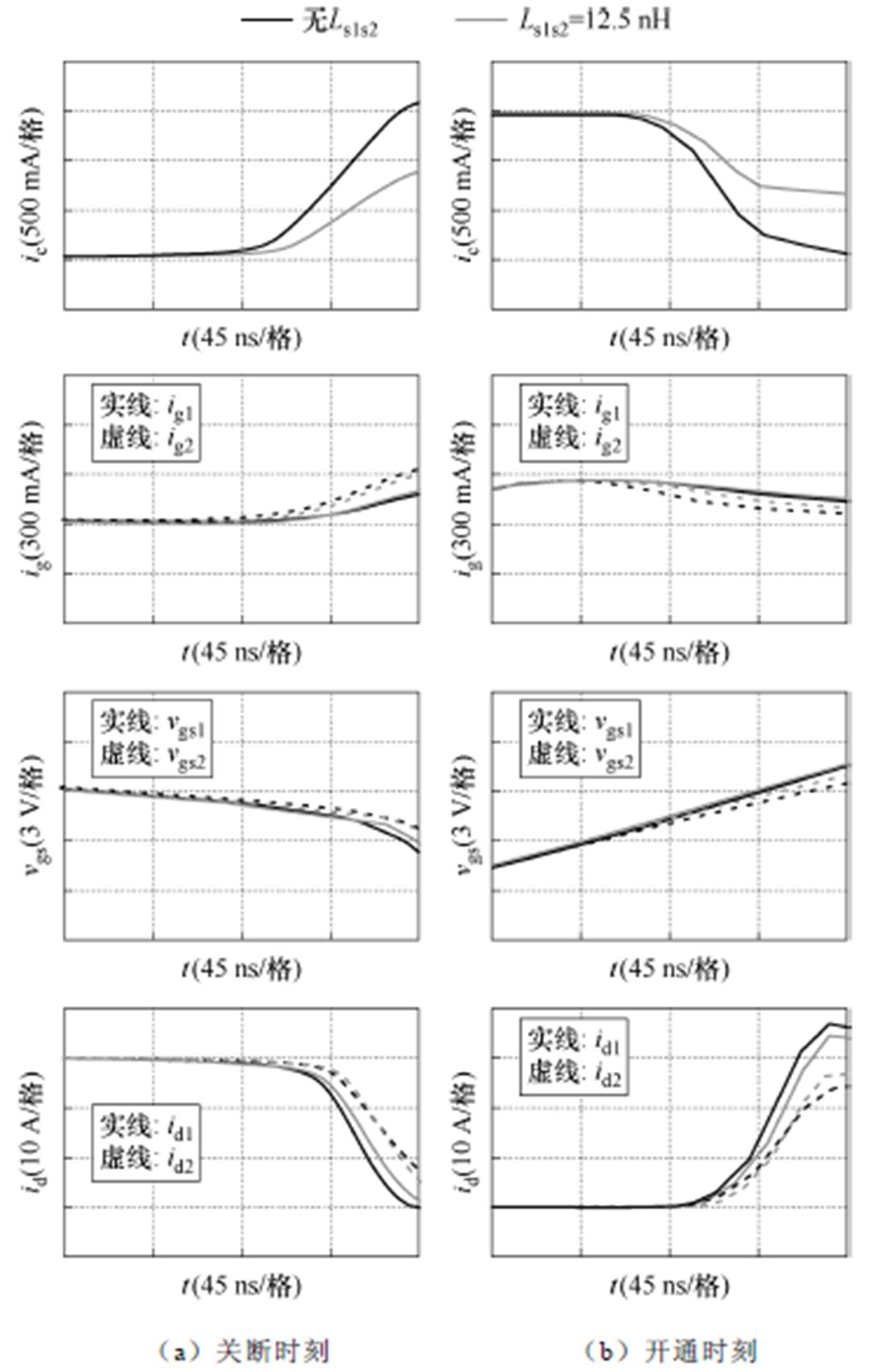

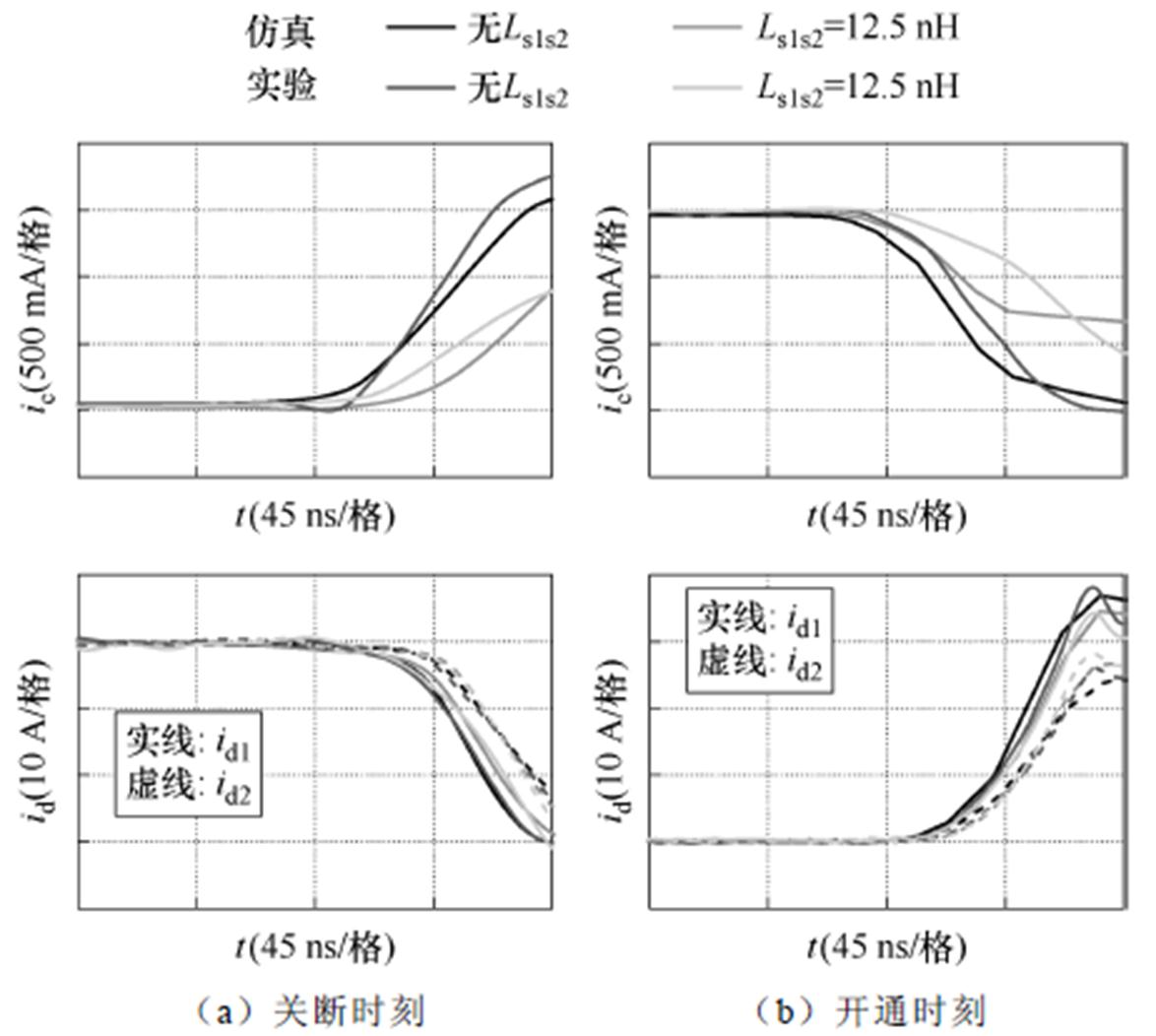

当Ls1s2选取表3的最大参数12.5 nH时,初始功率模块和优化功率模块的仿真波形对比如图10所示,无Ls1s2支路时的仿真波形也在图10中进行比较。由于Ls1<Ls2,在关断时刻,dic/dt>0,导致Dig<0,Dvgs<0,进而Did<0,即id1<id2;在开通时刻,dic/dt<0,导致Dig>0,Dvgs>0,进而Did>0,即id1>id2。在两种情况下,DLs、dic/dt、Dig、Dvgs和Did之间的符号关系都与动态电流不平衡机理的结论完全一致。然而,当采用DSI动态均流方法后,开通和关断时刻的 dic/dt

dic/dt 都明显减小,驱动回路差异

都明显减小,驱动回路差异 Dig

Dig 和

和 Dvgs

Dvgs 也随之减小,最终动态电流差异

也随之减小,最终动态电流差异 Did

Did 减小。这一结果与第1节中DSI动态均流方法的作用机制分析一致。因此,仿真结果验证了DSI动态均流方法的有效性。

减小。这一结果与第1节中DSI动态均流方法的作用机制分析一致。因此,仿真结果验证了DSI动态均流方法的有效性。

图10 初始功率模块和优化功率模块的仿真波形对比

Fig.10 Comparison of simulation waveforms between the initial and optimized power modules

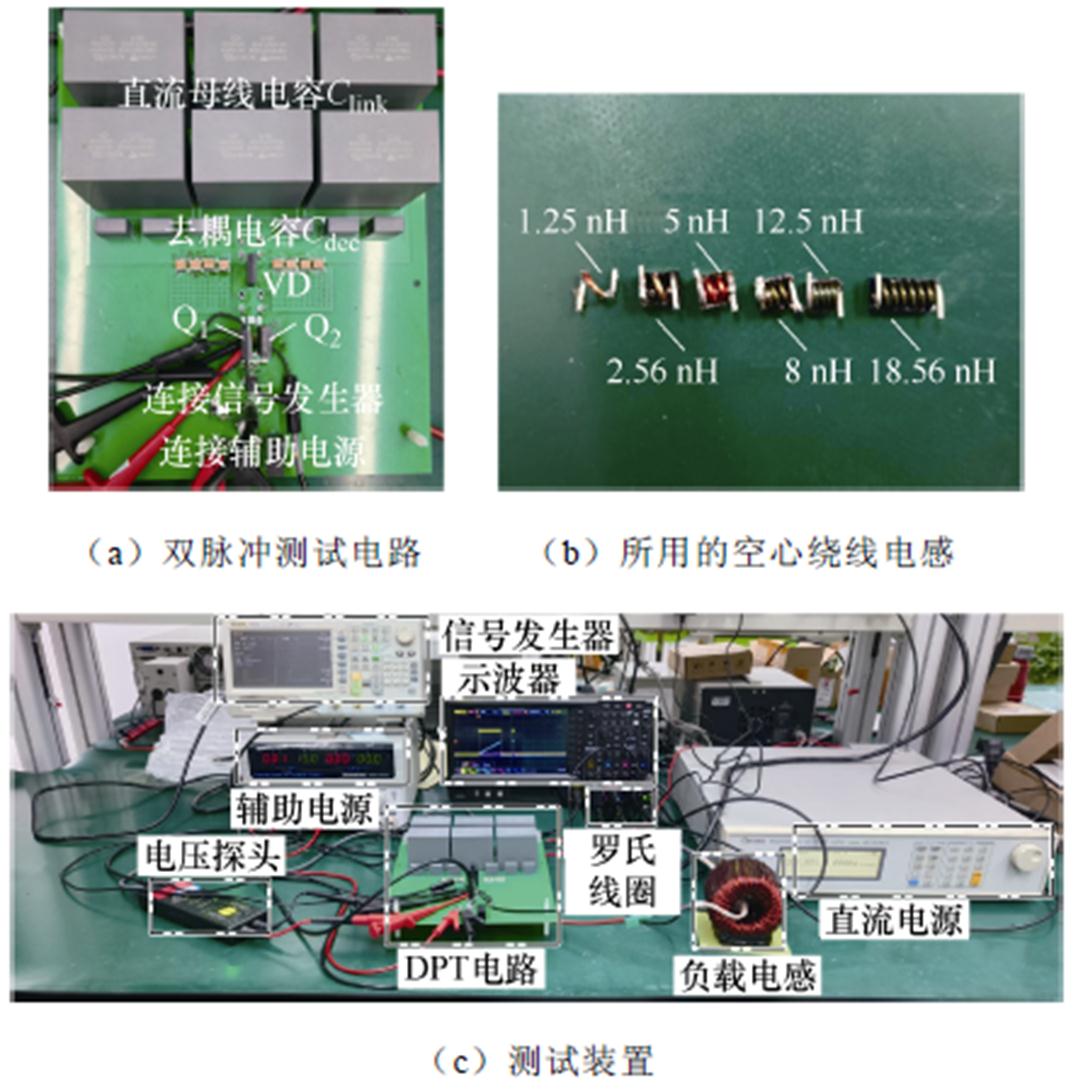

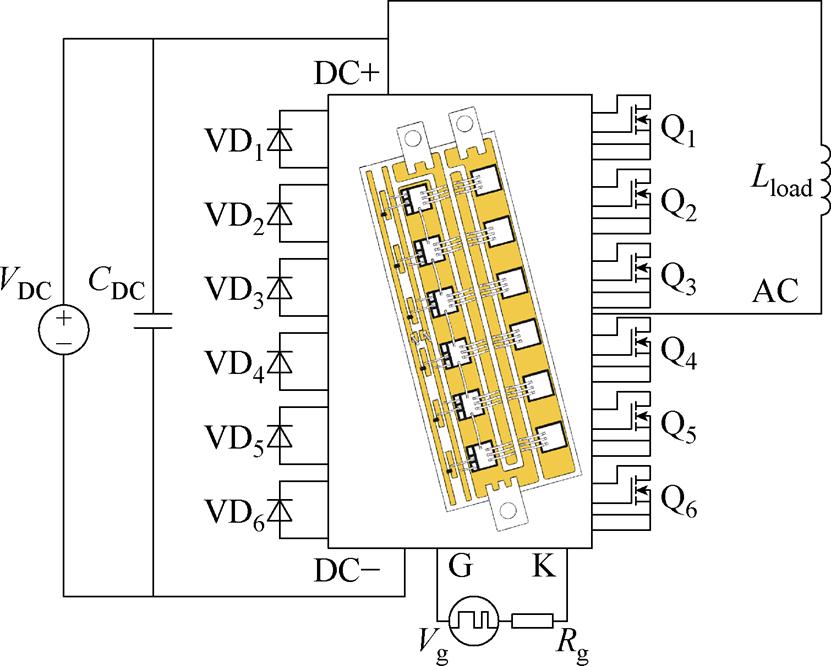

实验测试如图11所示。本文中,使用图11a所示的测试电路,在不同电路参数值下进行双脉冲测试,以验证动态电流不平衡机理和DSI动态均流方法的有效性。测试电路的PCB布局设计详见第2节,其结构为对称设计,为减小器件参数差异对实验结果的影响,使用Keysight B1505A功率器件分析仪对芯片进行筛选,在相同测试条件下,最终选用SiC MOSFETs的参数见表6。并联电路中每个支路都有焊盘连接到SiC MOSFET,在焊盘上焊接表2和表3中相应数值的空心绕线电感,如图11b所示,空心绕线电感的数值由Q3D仿真和环路分析仪Bode 100测试确定。通过改变电感的参数,可以验证不同参数的影响,除考察的参数外,其他参数均控制不变,以确保不同实验间的一致性。

图11 实验测试

Fig.11 Experimental test rig

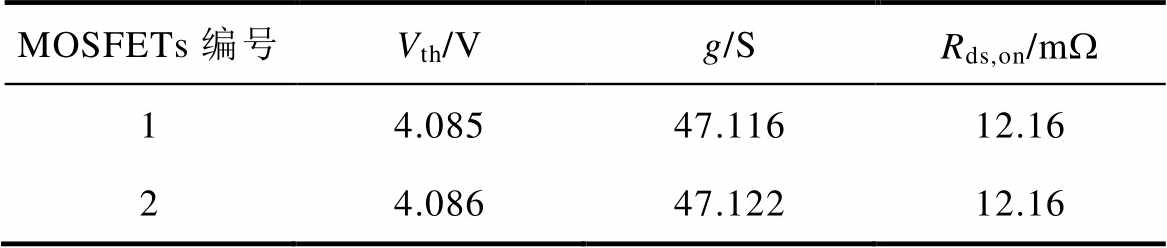

表6 所用SiC MOSFETs的静态参数

Tab.6 Static parameters of the SiC MOSFETs used

MOSFETs编号Vth/Vg/SRds,on/mW 14.08547.11612.16 24.08647.12212.16

测试装置如图11c所示。使用两个60 A/30 MHz罗氏线圈分别测量MOSFETs漏极端子上的电流id1和id2,以及两个30 A/30 MHz罗氏线圈分别测量MOSFETs栅极(或驱动源极)端子上的电流ig1和ig2(或ik1和ik2)。计算ic=ik1-ig1。使用150 V/200 MHz电压探头测量MOSFETs栅极和驱动源极端子上的电压vgs1和vgs2。由于空心绕线电感会在回路中引入较大的寄生电感,造成较大的关断过电压。而且,在负载电流较大时,电感磁饱和影响实验结果。因此,实验直流母线电压VDC和负载电流Iload分别设置为300 V和60 A。SiC MOSFETs在该条件下能够完全开通,所以实验得到验证。

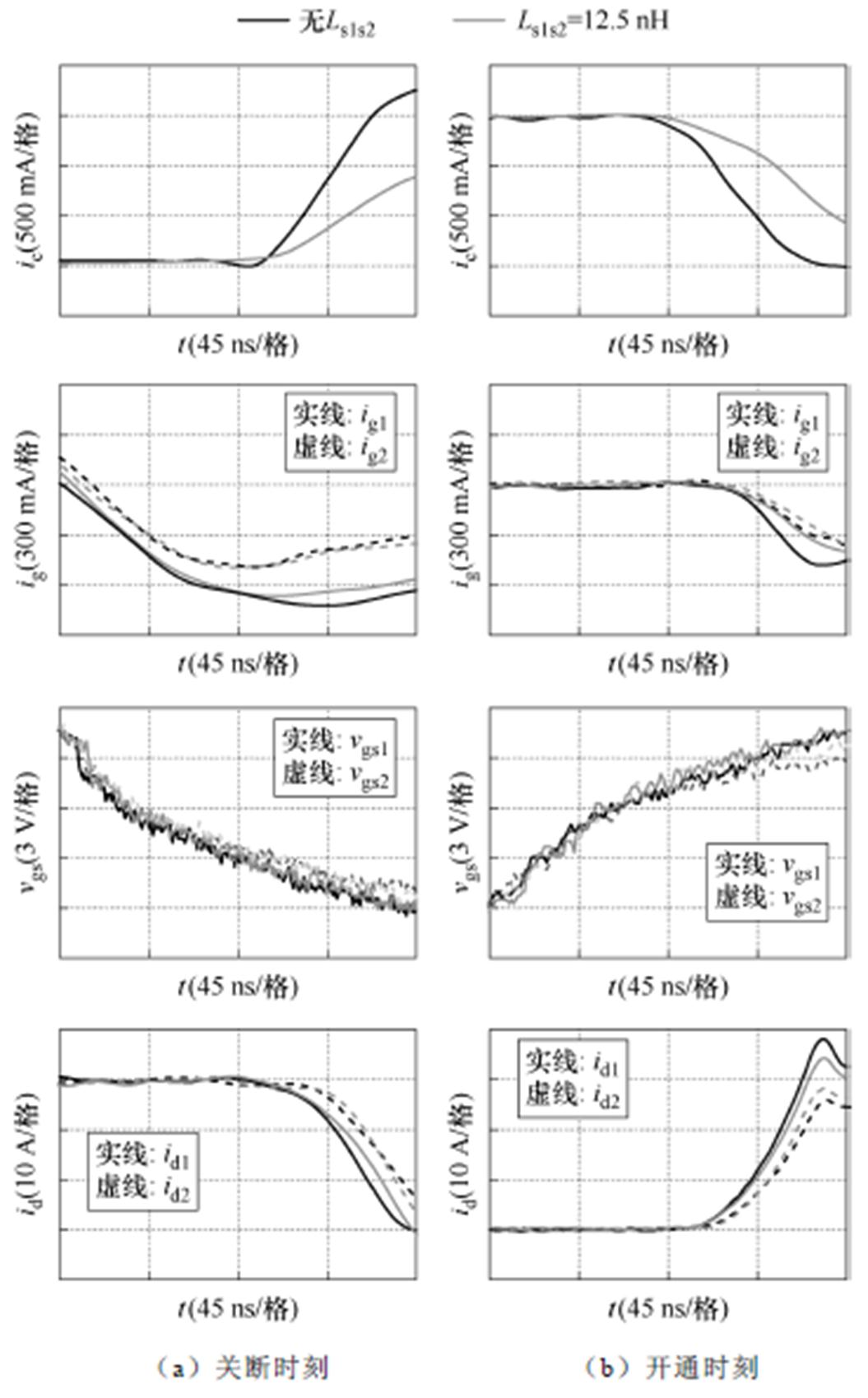

当未采用DSI均流方法,即不焊接Ls1s2时,实验波形如图12中黑色线所示。由于Ls1<Ls2,在关断时刻,dic/dt>0;而在开通时刻,dic/dt<0。在关断时刻,由于dic/dt>0,导致Dig<0,Dvgs<0,进而Did<0,即id1<id2;在开通时刻,由于dic/dt<0,导致Dig>0,Dvgs>0,进而Did>0,即id1>id2。实验波形与理论分析和仿真结果高度一致。

图12 初始功率模块和优化功率模块的实验波形对比

Fig.12 Comparison of experimental waveforms between the initial and optimized power modules

当采用DSI均流方法,即焊接Ls1s2时,实验波形如图12灰色线所示。在Ls1s2取最大值的情况下,DLs、dic/dt、Dig、Dvgs和Did之间的符号关系与理论分析和仿真结果完全一致。采用DSI动态均流方法后,无论是在开通还是关断时刻, dic/dt

dic/dt 都明显减小,同时

都明显减小,同时 Dig

Dig 和

和 Dvgs

Dvgs 也随之减小,最终导致

也随之减小,最终导致 Did

Did 明显减小。这与理论分析和仿真结果高度吻合,充分验证了DSI动态均流方法的有效性。

明显减小。这与理论分析和仿真结果高度吻合,充分验证了DSI动态均流方法的有效性。

图13进一步展示了在上述相同情况下,仿真波形和实验波形的对比。在仿真和实验波形中,DLs、dic/dt、Dig、Dvgs和Did之间的符号关系与理论分析一致。在Ls1s2取最大值(此时Ls1=2.5 nH,Ls2=8 nH,Ls1s2=12.5 nH)的情况下,不平衡电感衰减系数a约为0.6。此外,部分动态电流将通过Ls1s2支路流动,这些因素都使 dic/dt

dic/dt 减小,也使得DSI动态均流方法具有较明显的效果,本文提出的动态电流不平衡机理和DSI动态均流方法的有效性得到了充分验证。

减小,也使得DSI动态均流方法具有较明显的效果,本文提出的动态电流不平衡机理和DSI动态均流方法的有效性得到了充分验证。

图13 初始功率模块和优化功率模块的实验和仿真波形

Fig.13 Experimental and simulation waveforms of the initial and optimized power modules

尽管仿真与实验结果在整体趋势上保持一致,但两者之间仍存在一定的误差。为了更深入地理解实验设计的可靠性和结果的准确性,本文对误差源进行了详细分析,尤其是针对小电流测量中的误差,电流测量使用的是罗氏线圈,其精度和输出噪声限制了实际测量结果的准确性,特别是当测量小电流时,信号较弱,容易受到噪声的干扰,从而导致较大的误差。在本文中,使用了PEM公司生产的罗氏线圈,其典型精度为±2%,且由于不期望的噪声,最大误差可达0.1~0.2 A。此外,外部电磁干扰和信号噪声对测量结果的影响也不容忽视,实验环境中存在的电磁场可能与测量电路耦合,引入额外的噪声信号,从而影响测量精度。仿真模型与实际实验条件之间的差异也是导致误差的另一个重要因素,例如,仿真模型中的SiC器件参数与实际器件参数并不完全一致。通过对上述误差源的详细分析,明确了仿真与实验结果偏差的主要原因,尽管存在这些偏差,但采用DSI均流方法前后的波形变化趋势保持一致,这表明该方法具有较强的鲁棒性,从而达到了验证目的。

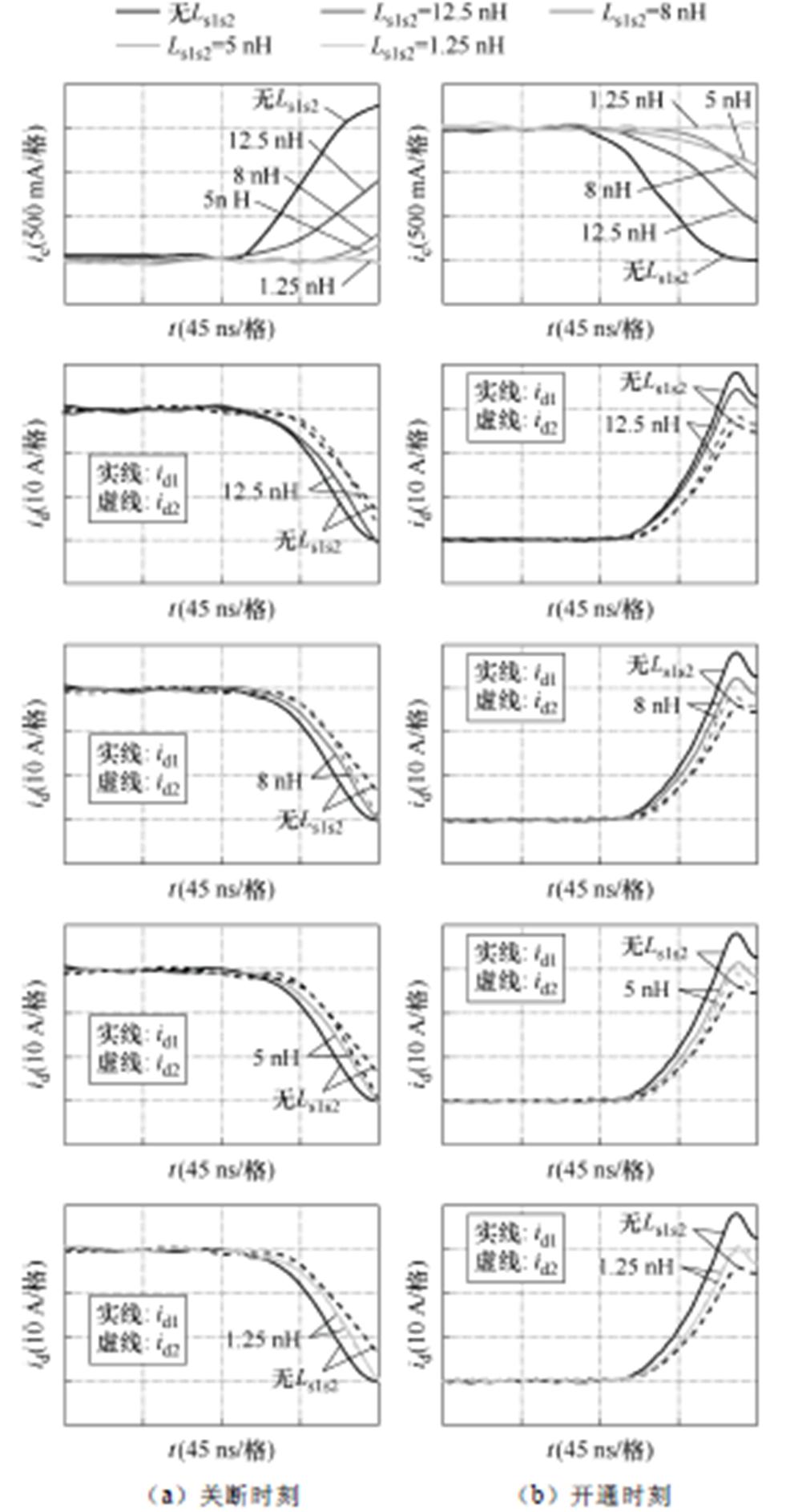

通过调整Ls1s2支路的电感值,可以实现不同DSI参数下优化功率模块的动态均流效果,实验波形如图14所示,初始功率模块的实验波形也用于图14中进行比较。采用DSI动态均流方法前,由于Ls1<Ls2,在关断时刻,dic/dt>0;而在开通时刻,dic/dt<0。因此,在关断时刻,Did<0,即id1<id2;在开通时刻,Did>0,即id1>id2。这一现象与动态电流不平衡机理的理论结论一致。采用DSI均流方法后,无论在开通还是关断时刻, dic/dt

dic/dt 都减小,进而使得

都减小,进而使得 Did

Did 明显减小,且随着Ls1s2减小,

明显减小,且随着Ls1s2减小, dic/dt

dic/dt 进一步减小,

进一步减小, Did

Did 也逐渐减小。这是因为Ls1s2减小时,不平衡电感衰减系数a减小,功率源极寄生电感差异也随之减小。同时,Ls1s2支路的阻抗减小,使得更多的动态电流流过Ls1s2支路,从而增大了电流变化抑制分量

也逐渐减小。这是因为Ls1s2减小时,不平衡电感衰减系数a减小,功率源极寄生电感差异也随之减小。同时,Ls1s2支路的阻抗减小,使得更多的动态电流流过Ls1s2支路,从而增大了电流变化抑制分量 -dis1s2/dt

-dis1s2/dt 。这些因素共同作用,进一步减小了

。这些因素共同作用,进一步减小了 dic/dt

dic/dt ,进而减小了

,进而减小了 Did

Did 。当Ls1s2足够小(Ls1=2.5 nH,Ls2=8 nH,Ls1s2=1.25 nH)时,a约为0.1,

。当Ls1s2足够小(Ls1=2.5 nH,Ls2=8 nH,Ls1s2=1.25 nH)时,a约为0.1, dis1s2/dt

dis1s2/dt 达到最大值,此时,

达到最大值,此时, dic/dt

dic/dt 几乎为0,id1与id2接近相等,

几乎为0,id1与id2接近相等, Did

Did 几乎为0,均流效果最佳。这一结果与理论分析和仿真验证高度一致,充分证明了DSI动态均流方法的有效性。

几乎为0,均流效果最佳。这一结果与理论分析和仿真验证高度一致,充分证明了DSI动态均流方法的有效性。

图14 不同DSI参数下优化功率模块的实验波形

Fig.14 Experimental waveforms of the optimized power module under different DSI parameters

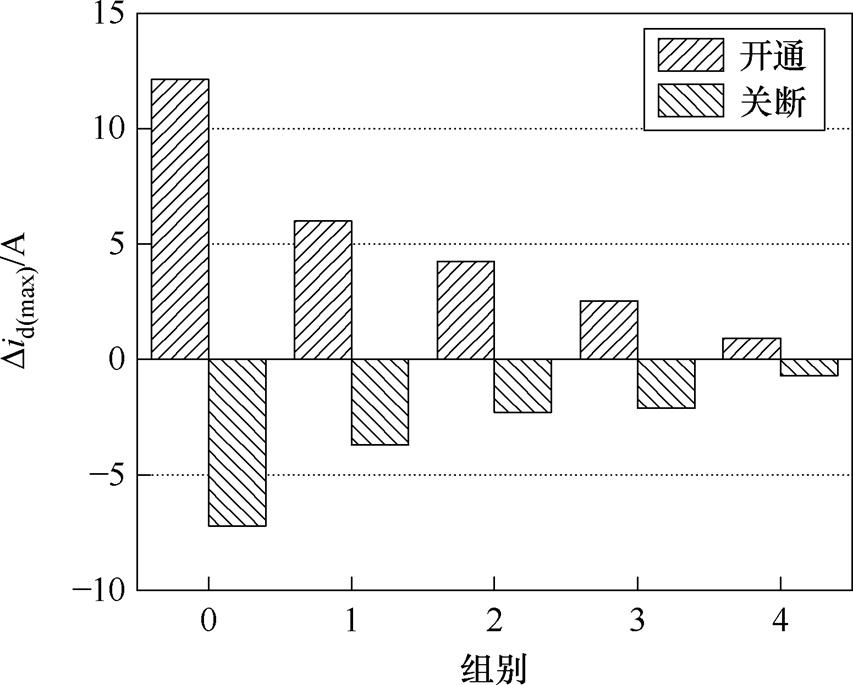

为进一步论证DSI动态均流方法的有效性,图15对比了上述不同组实验下优化功率模块的最大动态电流差异Did(max)。其中,0组代表无Ls1s2的情况;1~4组分别代表Ls1s2=12.5 nH, 8.0 nH, 5.0 nH, 1.25 nH的情况。开通时刻的Did(max)和关断时刻的Did(max)符号相反,这是因为Ls1<Ls2,在关断时刻,dic/dt>0,导致Did<0;而在开通时刻,dic/dt<0,导致Did>0。此外,开通时刻的动态电流不均衡现象更为显著,采用DSI均流方法后,最大动态电流差异 Did(max)

Did(max) 至少减小了50%。随着参数Ls1s2的减小,

至少减小了50%。随着参数Ls1s2的减小, Did(max)

Did(max) 也逐渐减小。该过程的物理机制可以解释如下:Ls1s2越小,其支路阻抗越小,在开关瞬间有更多动态电流通过该支路,因此,动态电流在DLs上感应的

也逐渐减小。该过程的物理机制可以解释如下:Ls1s2越小,其支路阻抗越小,在开关瞬间有更多动态电流通过该支路,因此,动态电流在DLs上感应的 Dvs

Dvs 将减小,由Dvs产生的环流也将减小,同时,阻抗减小的Ls1s2支路也将承担更多的环流,最终使得一定时间内流经驱动回路的

将减小,由Dvs产生的环流也将减小,同时,阻抗减小的Ls1s2支路也将承担更多的环流,最终使得一定时间内流经驱动回路的 ic

ic 减小,在驱动源极电感Lk上产生的感应电压

减小,在驱动源极电感Lk上产生的感应电压 -2Lkdic/dt

-2Lkdic/dt 也随之减小,进而减小驱动回路中的

也随之减小,进而减小驱动回路中的 Dig

Dig 和

和 Dvgs

Dvgs ,最终显著减小动态电流差异

,最终显著减小动态电流差异 Did

Did 。

。

图15 不同DSI参数下优化功率模块的Did(max)

Fig.15 Did(max) of the optimized power module under different DSI parameters

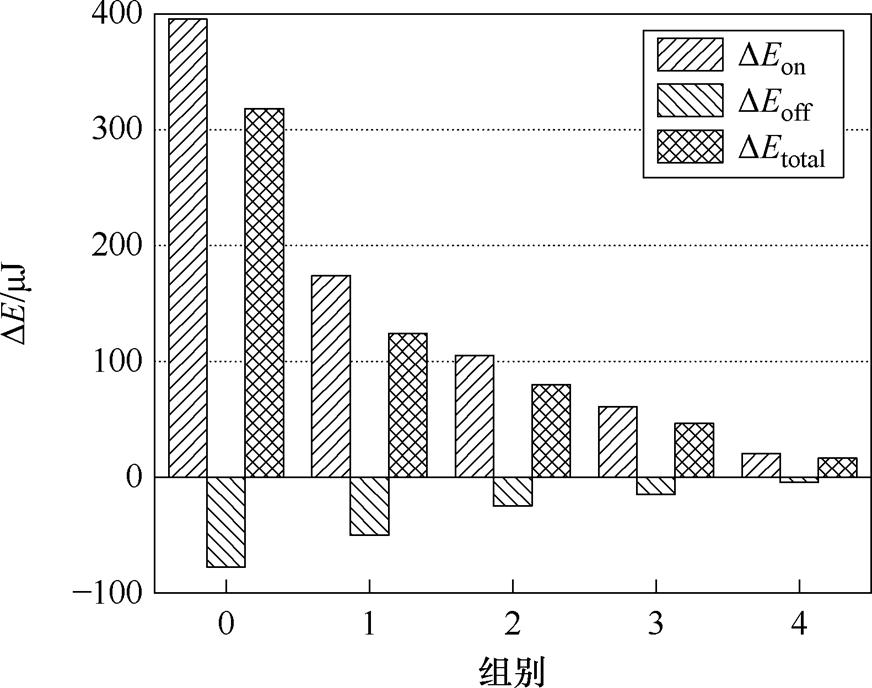

为研究DSI动态均流方法对开关损耗差异的影响,图16展示了不同DSI参数下优化功率模块的开通损耗差异DEon、关断损耗差异DEoff和总开关损耗差异DEtotal,DEon和DEoff符号相反,在某种程度下可以互相补偿。然而,开通损耗差异是造成总损耗差异的主要原因,DE随Ls1s2参数值的变化趋势与Did(max)一致,采用DSI动态均流方法后,总开关损耗差异 DEtotal

DEtotal 至少减小了60%,随着Ls1s2参数值减小,

至少减小了60%,随着Ls1s2参数值减小, DEon

DEon 和

和 DEoff

DEoff 也减小,进而

也减小,进而 DEtotal

DEtotal 也逐渐减小,最终,相比初始模块,优化模块的

也逐渐减小,最终,相比初始模块,优化模块的 DEtotal

DEtotal 减小高达95%,通过DSI动态均流方法,总开关损耗差异

减小高达95%,通过DSI动态均流方法,总开关损耗差异 DEtotal

DEtotal 明显减小了60%~95%。因此,采用DSI动态均流方法后,可以有效地降低总开关损耗差异。

明显减小了60%~95%。因此,采用DSI动态均流方法后,可以有效地降低总开关损耗差异。

图16 不同DSI参数下优化功率模块的DE

Fig.16 DE of the optimized power module under different DSI parameters

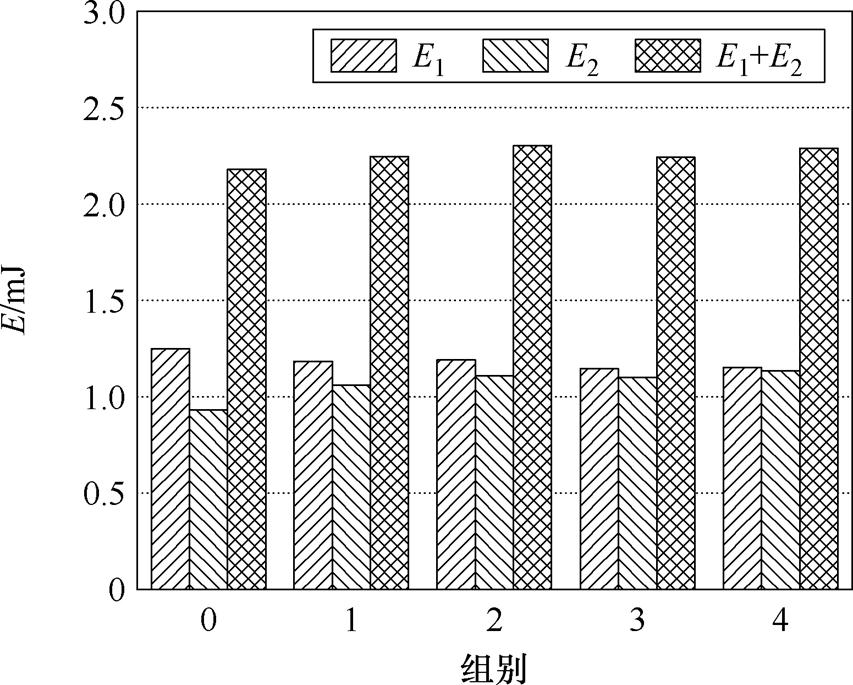

为了评估DSI动态均流方法对功率模块效率的影响,图17展示了不同DSI参数下优化功率模块的开关损耗,包括Q1的开关损耗E1、Q2的开关损耗E2,以及两者的开关损耗之和E1+E2。采用DSI动态均流方法后,E1随Ls1s2参数值减小而明显减小,E2则随Ls1s2参数值减小而明显增大。这一趋势使得E2逐渐接近E1,E2的增大速度略高于E1的减小速度,使得E1+E2略微增加。采用DSI动态均流方法后,总开关损耗E1+E2仅增加了3%~5%,优化功率模块的开关损耗与初始功率模块相比仅略有增加,说明DSI动态均流方法基本不会降低功率模块的效率。因此,DSI方法在实现动态均流的同时,能够有效地保持功率模块的效率水平,兼具均流效果和效率平衡的双重优势。

图17 不同DSI参数下优化功率模块的开关损耗E

Fig.17 Switching losses E of the optimized power module under different DSI parameters

为了进一步验证DSI动态均流方法在较多SiC MOSFETs并联时的有效性,本文对一个常见的多芯片并联半桥模块进行了优化设计。该SiC模块的结构如图18a所示。高侧续流二极管使用6个SiC肖特基二极管(S6305)并联,低侧开关使用6个SiC MOSFETs(S4103)并联,构成1 200 V/600 A大功率模块。并联的SiC MOSFETs均采用了开尔文源极连接,点画线框中显示了DSI动态均流方法在功率模块中的简单应用,该方法无需改变DBC基板和芯片布局,也无需外加无源元件,较容易集成,便于和其他方法结合,实现简单。图18b展示了该模块的简化等效电路模型,DSI动态均流方法的等效寄生参数被特别标出,其他寄生参数未被标出。

图18 具有更多并联芯片的优化功率模块的结构

Fig.18 Structure of the optimized power module with more paralleled chips

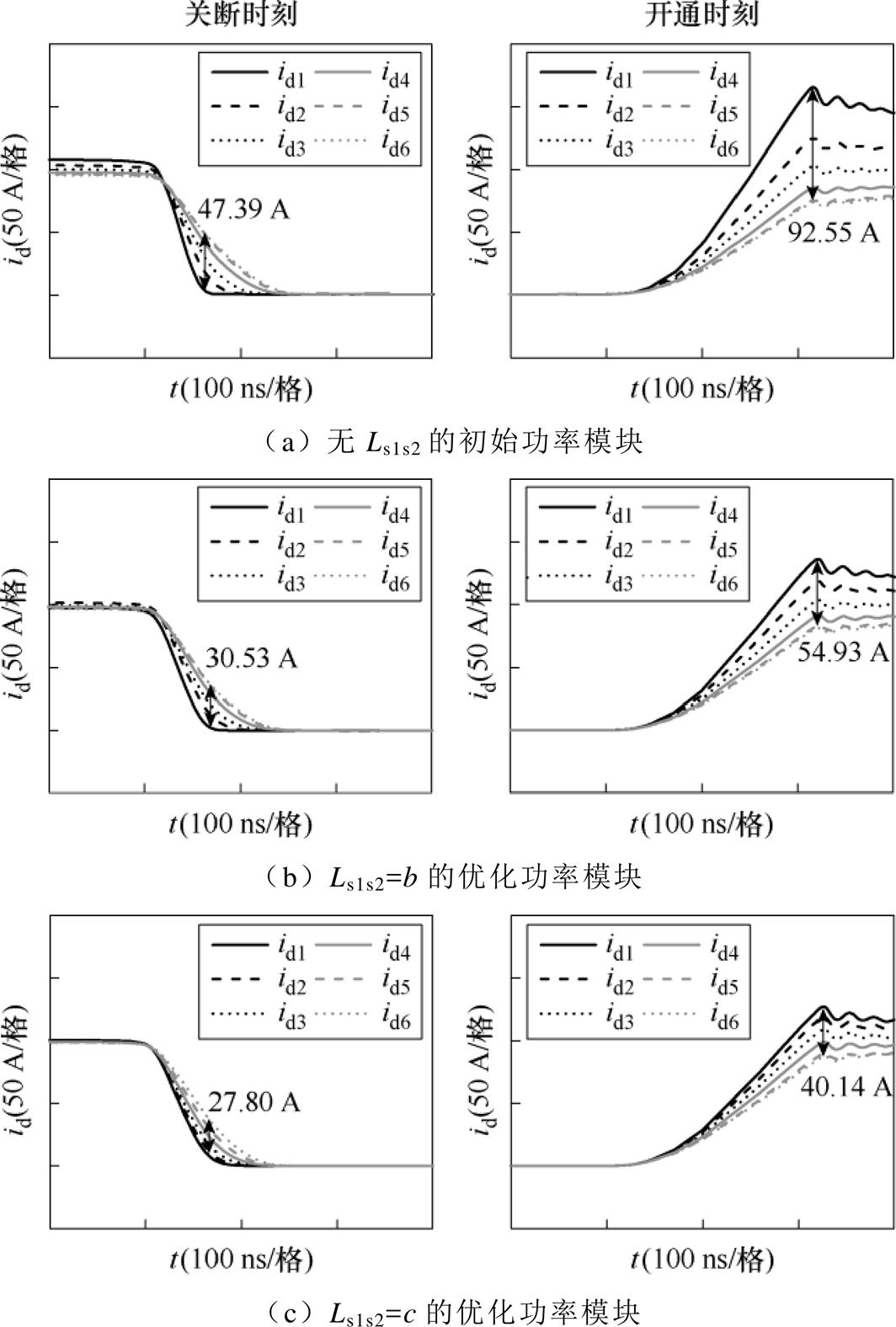

基于有限元仿真软件Q3D和电路软件Pspice的电磁耦合仿真方法,已经被广泛用于分析多芯片功率模块中的均流情况[19, 25, 34],因此,利用Q3D提取功率模块的寄生参数网络,在Pspice使用提取的寄生参数网络和器件模型进行双脉冲测试。低侧MOSFETs作为有源开关电磁耦合仿真拓扑如图19所示。通过改变模型结构进行仿真,可以得到采用DSI动态均流方法前后的仿真波形。仿真直流母线电压VDC和负载电流Iload分别设置为800 V和600 A。Q1~Q6的漏极电流分别表示为id1~id6。采用DSI动态均流方法前后,Q1~Q6的仿真波形如图20所示。

图19 低侧MOSFETs作为有源开关电磁耦合仿真拓扑

Fig.19 Electromagnetic coupling simulation topology for low side MOSFETs as the active switch

图20a展示了未采用DSI均流方法时的开通和关断波形,尽管采用了开尔文源极连接,动态电流的差异仍然显著,开通时刻的动态电流最大差异为92.55 A,占Iload/6的92.55%;关断时刻的动态电流最大差异为47.39 A,占Iload/6的47.39%。简单采用DSI动态均流方法后,等效寄生电感Ls1s2的电感值为b。此时开通和关断波形如图20b所示,可以看到,动态电流不平衡现象得到了显著改善,与初始功率模块相比,开通和关断时刻的动态电流最大差异分别减小了40.65%和35.58%。进一步调整DSI的参数,使等效寄生电感Ls1s2电感值减小到c(c<b ,此时,动态电流差异可以进一步减小,如图20c所示。与初始功率模块相比,开通和关断时刻的动态电流最大差异分别减小了56.63%和41.34%,因此,通过调整DSI的参数来减小Ls1s2,如改变键合线位置、增大键合线的线径、减小键合线的长度或增加键合线的数量,可以显著提升均流效果。DSI动态均流方法在较多MOSFETs并联时的有效性得到了验证,在后续的研究中,将基于上述仿真结果,开展一系列实验,以进一步验证DSI方法在更多芯片并联功率模块中的有效性。

,此时,动态电流差异可以进一步减小,如图20c所示。与初始功率模块相比,开通和关断时刻的动态电流最大差异分别减小了56.63%和41.34%,因此,通过调整DSI的参数来减小Ls1s2,如改变键合线位置、增大键合线的线径、减小键合线的长度或增加键合线的数量,可以显著提升均流效果。DSI动态均流方法在较多MOSFETs并联时的有效性得到了验证,在后续的研究中,将基于上述仿真结果,开展一系列实验,以进一步验证DSI方法在更多芯片并联功率模块中的有效性。

图20 具有更多并联芯片的功率模块的开通和关断波形

Fig.20 Turn-ON and turn-OFF waveforms of the power module with more paralleled chips

上述结果表明,在多芯片并联应用中,DSI方法相较于传统的开尔文源极连接法展现出显著的性能优势。尽管开尔文源极连接能够优化单个芯片的开关性能,但在多芯片并联时,其动态电流不平衡问题仍然突出,相比之下,DSI方法可以进一步有效缓解功率回路和驱动回路之间的电流耦合现象,减小驱动回路差异和动态电流差异,从而显著改善动态电流的不平衡。同时,该方法也兼具开尔文源极连接法的优点,能够提高芯片的开关速度并降低开关损耗,此外,DSI方法简化了封装设计,降低了系统复杂性和成本,它仅需增加一步键合工序,无需改变功率模块的整体布局,也无需额外引脚,这使得DSI方法在实现上更为简洁高效。因此,在高功率密度和高频应用场景中,DSI方法不仅能够满足多芯片并联的动态均流需求,还具备更低的实现成本,使其成为一种更具优势的解决方案。

本文中,虽然重点探讨了DSI方法在动态电流平衡方面的优势,但对系统可能出现的电磁干扰(Electromagnetic Interference, EMI)问题尚未进行深入探讨。例如,额外的键合线可能会增加寄生电感,导致高频噪声和电压尖峰,DSI方法改变了电流回路的布局,可能会增加共模干扰的风险,尤其是在高频开关应用中,额外的键合线可能成为磁场耦合的路径,影响周围元件的稳定性。为降低DSI方法可能产生的EMI问题,可以考虑以下优化方向:首先,采用低噪声互连技术,如柔性PCB或铜夹片(Cu-Clip),以减少寄生电感和高频噪声;其次,通过调整栅极驱动电路中的电阻,适当降低开关速度,从而减少高频噪声,但需权衡开关损耗与EMI之间的关系;最后,通过这些措施,可以在保持DSI方法优势的同时,有效降低其对EMI的影响,从而提升系统的电磁兼容性。

本文提出了一种针对功率模块中并联SiC MOSFETs的动态均流方法,即在SiC MOSFETs的源极之间进行直连(DSI)。首先,通过电路建模和数学分析,推导了在采用DSI方法和未采用DSI方法时,并联SiC MOSFETs的动态电流不平衡机理,该机理表明,在具有开尔文源极连接的并联SiC MOSFETs电路中,功率源极寄生电感差异DLs会在开关瞬间产生环流ic,进而引起功率回路和驱动回路的电流耦合,这对并联SiC MOSFETs的瞬态电流分布具有显著影响。具体而言,DLs会引起dic/dt,进而导致驱动回路中的差异Dig和Dvgs,最终形成动态电流差异Did。在开通时刻,DLs与dic/dt同号;在关断时刻,DLs与dic/dt异号,而dic/dt则始终与Dig、Dvgs和Did异号,因此,dic/dt是引起驱动回路差异和动态电流不平衡的主要因素, dic/dt

dic/dt 越大,

越大, Dig

Dig 和

和 Dvgs

Dvgs 越大,

越大, Did

Did 也越大。通过仿真和实验共同验证了动态电流不平衡机理的准确性。

也越大。通过仿真和实验共同验证了动态电流不平衡机理的准确性。

基于动态电流不平衡机理,本文进一步分析了DSI动态均流方法的作用机制。研究结果表明,该方法可以显著减小 dic/dt

dic/dt ,从而缓解DLs引起的功率回路和驱动回路之间的电流耦合,实现动态电流平衡。该方法仅需增加一步键合线互连工序,无需额外的复杂操作,因此成本低廉且容易实现,与传统的多芯片功率模块的制造工艺兼容性好,仿真和实验都验证了该动态均流方法的有效性。采用DSI动态均流方法后,并联SiC MOSFETs的动态电流差异和开关损耗差异都减小了50%以上,动态均流效果显著。最后,本文还在具有更多芯片并联的功率模块中验证了该方法的有效性,值得注意的是,该均流方法同样适用于无键合线模块(如双面冷却模块和压接模块),只需改变DSI的实现方式(如采用铜夹片、钼块和银垫片)即可。

,从而缓解DLs引起的功率回路和驱动回路之间的电流耦合,实现动态电流平衡。该方法仅需增加一步键合线互连工序,无需额外的复杂操作,因此成本低廉且容易实现,与传统的多芯片功率模块的制造工艺兼容性好,仿真和实验都验证了该动态均流方法的有效性。采用DSI动态均流方法后,并联SiC MOSFETs的动态电流差异和开关损耗差异都减小了50%以上,动态均流效果显著。最后,本文还在具有更多芯片并联的功率模块中验证了该方法的有效性,值得注意的是,该均流方法同样适用于无键合线模块(如双面冷却模块和压接模块),只需改变DSI的实现方式(如采用铜夹片、钼块和银垫片)即可。

附 录

运用拉普拉斯变换,式(1)变换为

(A1)

(A1)

式中,s为拉普拉斯算子。

运用拉普拉斯变换,结合式(3)、式(4)、式(7)和式(8),变换得到

(A2)

(A2)

(A3)

(A3)

运用拉普拉斯变换,结合式(5)~式(8),变换得到

(A4)

(A4)

而且,由式(6)~式(8)可以得到

(A5)

(A5)

参考文献

[1] 谭亚雄, 张梦洋, 刘元, 等. 一种连续函数描述的高精度SiC MOSFET模型[J]. 电工技术学报, 2024, 39(18): 5719-5731.

Tan Yaxiong, Zhang Mengyang, Liu Yuan, et al. A high-precision SiC MOSFET model with continuous function description[J]. Transactions of China Elec- trotechnical Society, 2024, 39(18): 5719-5731.

[2] 盛况, 任娜, 徐弘毅. 碳化硅功率器件技术综述与展望[J]. 中国电机工程学报, 2020, 40(6): 1741-1753.

Sheng Kuang, Ren Na, Xu Hongyi. A recent review on silicon carbide power devices technologies[J]. Proceedings of the CSEE, 2020, 40(6): 1741-1753.

[3] 邹铭锐, 曾正, 孙鹏, 等. 基于变电阻驱动的SiC器件开关轨迹协同调控[J]. 电工技术学报, 2023, 38(16): 4286-4300.

Zou Mingrui, Zeng Zheng, Sun Peng, et al. Coordinated switching trajectory regulation of SiC device using variable resistance gate driver[J]. Transactions of China Electrotechnical Society, 2023, 38(16): 4286-4300.

[4] 丁四宝, 王盼宝, 王卫, 等. SiC/Si混合开关时间延迟及其信号调制方法[J]. 电工技术学报, 2025, 40(4): 1129-1144.

Ding Sibao, Wang Panbao, Wang Wei, et al. Analysis of SiC/Si HyS loss characteristics and its driving signal modulation circuit[J]. Transactions of China Electrotechnical Society, 2025, 40(4): 1129-1144.

[5] 徐浩东, 罗嗣勇, 毕闯, 等. 基于SiC MOSFET同步Buck DC-DC变换器的宽频混合EMI滤波器设计[J]. 电工技术学报, 2024, 39(10): 3060-3069.

Xu Haodong, Luo Siyong, Bi Chuang, et al. Design of broadband hybrid EMI filter in synchronous Buck DC-DC converter with SiC MOSFETs[J]. Transa- ctions of China Electrotechnical Society, 2024, 39(10): 3060-3069.

[6] 宛新春, 陈其工, 杨锦涛, 等. 基于栅极和漏极电压检测的SiC MOSFET短路保护电路研究[J]. 电工技术学报, 2025, 40(4): 1145-1155, 1168.

Wan Xinchun, Chen Qigong, Yang Jintao, et al. Research on SiC MOSFET short-circuit protection based on gate and drain voltage detection[J]. Transa- ctions of China Electrotechnical Society, 2025, 40(4): 1145-1155, 1168.

[7] 王议锋, 车超昌, 陈博, 等. 基于SiC器件的高压宽范围直流辅助电源[J]. 电工技术学报, 2025, 40(3): 786-799.

Wang Yifeng, Che Chaochang, Chen Bo, et al. high voltage wide range DC auxiliary power supply based on SiC devices[J]. Transactions of China Electro- technical Society, 2025, 40(3): 786-799.

[8] 肖标, 郭祺, 涂春鸣, 等. 面向开关时序与驱动电压自主协同调控的SiC/Si混合开关驱动电路[J]. 电工技术学报, 2025, 40(4): 1117-1128.

Xiao Biao, Guo Qi, Tu Chunming, et al. SiC/Si hybrid switch drive circuit with autonomous and coordinated control of switching sequences and driving voltages[J]. Transactions of China Electrotechnical Society, 2025, 40(4): 1117-1128.

[9] 於少林, 张兴, 王佳宁, 等. 分立器件并联型叠层母排均流分析及优化设计[J]. 电工技术学报, 2023, 38(8): 2086-2099.

Yu Shaolin, Zhang Xing, Wang Jianing, et al. The current balance analysis and optimization design of the laminated busbar with discrete devices in parallel[J]. Transactions of China Electrotechnical Society, 2023, 38(8): 2086-2099.

[10] 李东润, 宁圃奇, 康玉慧, 等. 采用大芯片的高功率密度SiC功率模块设计[J]. 电源学报, 2024, 22(3): 93-99.

Li Dongrun, Ning Puqi, Kang Yuhui, et al. Design of high power density SiC power module with large chips[J]. Journal of Power Supply, 2024, 22(3): 93-99.

[11] Husain I, Ozpineci B, Islam M S, et al. Electric drive technology trends, challenges, and opportunities for future electric vehicles[J]. Proceedings of the IEEE, 2021, 109(6): 1039-1059.

[12] Reimers J, Dorn-Gomba L, Mak C, et al. Automotive traction inverters: current status and future trends[J]. IEEE Transactions on Vehicular Technology, 2019, 68(4): 3337-3350.

[13] Li Helong, Zhao Shuang, Wang Xiongfei, et al. Parallel connection of silicon carbide MOSFETs: challenges, mechanism, and solutions[J]. IEEE Transa- ctions on Power Electronics, 2023, 38(8): 9731-9749.

[14] 张少昆, 孙微, 范涛, 等. 基于分立器件并联的高功率密度碳化硅电机控制器研究[J]. 电工技术学报, 2023, 38(22): 5999-6014.

Zhang Shaokun, Sun Wei, Fan Tao, et al. Research on high power density silicon carbide motor controller based on parallel connection of discrete devices[J]. Transactions of China Electrotechnical Society, 2023, 38(22): 5999-6014.

[15] 王来利, 赵成, 张彤宇, 等. 碳化硅功率模块封装技术综述[J]. 电工技术学报, 2023, 38(18): 4947- 4962.

Wang Laili, Zhao Cheng, Zhang Tongyu, et al. Review of packaging technology for silicon carbide power modules[J]. Transactions of China Electro- technical Society, 2023, 38(18): 4947-4962.

[16] 张缙, 刘智, 刘意, 等. 基于智能算法的双面散热SiC功率模块多目标优化设计[J]. 电工技术学报, 2023, 38(20): 5515-5529.

Zhang Jin, Liu Zhi, Liu Yi, et al. Research on multi-objective optimization design of double-sided cooling SiC power module based on intelligent algorithm[J]. Transactions of China Electrotechnical Society, 2023, 38(20): 5515-5529.

[17] Zhang Boyi, Wang Ruxi, Barbosa P, et al. Common source inductance compensation technique for dynamic current balancing in SiC MOSFETs parallel operations[C]//2023 IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 2023: 358-365.

[18] Zhu Ye, Li Han, Luo Cheng, et al. Influence of paralleled SiC MOSFET on turn-off gate voltage oscillation[C]//2020 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 2020: 683-689.

[19] Zhao Cheng, Wang Laili, Zhang Fan, et al. A method to balance dynamic current of paralleled SiC MOSFETs with kelvin connection based on response surface model and nonlinear optimization[J]. IEEE Transactions on Power Electronics, 2021, 36(2): 2068-2079.

[20] 陈宇, 周宇, 罗皓泽, 等. 计及芯片导通压降温变效应的功率模块三维温度场解析建模方法[J]. 电工技术学报, 2021, 36(12): 2459-2470.

Chen Yu, Zhou Yu, Luo Haoze, et al. Analytical 3D temperature field model for power module con- sidering temperature effect of semiconductor voltage drop[J]. Transactions of China Electrotechnical Society, 2021, 36(12): 2459-2470.

[21] Tang Lei, Jiang Huaping, Liao Ruijin, et al. Impact of the threshold dispersity evolution on the current sharing of parallel SiC MOSFETs[J]. IEEE Transa- ctions on Power Electronics, 2024, 39(5): 6312-6326.

[22] Neira S, Mathieson R, Parker M, et al. Investigation into current sharing of parallel SiC MOSFET modules using a gate-driver with sub-nanosecond time-skew capability[C]//2023 25th European Conference on Power Electronics and Applications (EPE'23 ECCE Europe), Aalborg, Denmark, 2023: 1-8.

[23] Li Helong, Munk-Nielsen S, Bęczkowski S, et al. Effects of auxiliary source connections in multichip power module[C]//2016 IEEE Applied Power Elec- tronics Conference and Exposition (APEC), Long Beach, CA, USA, 2016: 3101-3106.

[24] Zhao Cheng, Wang Laili, Zhang Fan. Effect of asymmetric layout and unequal junction temperature on current sharing of paralleled SiC MOSFETs with kelvin-source connection[J]. IEEE Transactions on Power Electronics, 2020, 35(7): 7392-7404.

[25] Lü Jianwei, Chen Cai, Liu Baihan, et al. A dynamic current balancing method for paralleled SiC MOSFETs using monolithic Si-RC snubber based on a dynamic current sharing model[J]. IEEE Transactions on Power Electronics, 2022, 37(11): 13368-13384.

[26] Wen Yang, Yang Yuan, Gao Yong. Active gate driver for improving current sharing performance of paralleled high-power SiC MOSFET modules[J]. IEEE Transactions on Power Electronics, 2021, 36(2): 1491-1505.

[27] He Yang, Wang Xun, Shao Shuai, et al. Active gate driver for dynamic current balancing of parallel- connected SiC MOSFETs[J]. IEEE Transactions on Power Electronics, 2023, 38(5): 6116-6127.

[28] Du Liyang, Du Xia, Zhao Shuang, et al. Digital close-loop active gate driver for static and dynamic current sharing of paralleled SiC MOSFETs[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2024, 12(2): 1372-1384.

[29] Gong Hongzhou, Wang Laili, Yang Junhui, et al. Effect of distributed decoupling capacitors in multi-chip SiC power modules on current sharing mechanism[C]// 2024 IEEE 10th International Power Electronics and Motion Control Conference (IPEMC2024-ECCE Asia), Chengdu, China, 2024: 2619-2624.

[30] Baker N, Iannuzzo F, Li Helong. Impact of Kelvin- source resistors on current sharing and failure detection in multichip power modules[C]//2018 20th European Conference on Power Electronics and Applications, Riga, Latvia, 2018: 1-7.

[31] 曾正, 邵伟华, 胡博容, 等. 基于耦合电感的SiC MOSFET并联主动均流[J]. 中国电机工程学报, 2017, 37(7): 2068-2081.

Zeng Zheng, Shao Weihua, Hu Borong, et al. Active current sharing of paralleled SiC MOSFETs by coupling inductors[J]. Proceedings of the CSEE, 2017, 37(7): 2068-2081.

[32] Miao Zichen, Mao Yincan, Lu Guoquan, et al. Magnetic integration into a silicon carbide power module for current balancing[J]. IEEE Transactions on Power Electronics, 2019, 34(11): 11026-11035.

[33] He Yang, Zhang Junming, Shao Shuai. Dynamic current balancing for paralleled SiC MOSFETs with circuit mismatches considering circulating current in drive circuit[J]. CPSS Transactions on Power Elec- tronics and Applications, 2024, 9(2): 219-229.

[34] 邵伟华, 冉立, 曾正, 等. 基于优化对称布局的多芯片SiC模块动态均流[J]. 中国电机工程学报, 2018, 38(6): 1826-1836, 1920.

Shao Weihua, Ran Li, Zeng Zheng, et al. Dynamic current sharing of multichip SiC module with optimal symmetric layout[J]. Proceedings of the CSEE, 2018, 38(6): 1826-1836, 1920.

[35] Zeng Zheng, Zhang Xin, Li Xiaoling. Layout- dominated dynamic current imbalance in multichip power module: mechanism modeling and comparative evaluation[J]. IEEE Transactions on Power Elec- tronics, 2019, 34(11): 11199-11214.

[36] Wang Miao, Luo Fang, Xu Longya. A double-end sourced wire-bonded multichip SiC MOSFET power module with improved dynamic current sharing[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2017, 5(4): 1828-1836.

[37] Bęczkowski S, Jørgensen A B, Li Helong, et al. Switching current imbalance mitigation in power modules with parallel connected SiC MOSFETs[C]// 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), Warsaw, Poland, 2017: P.1-P.8.

[38] Cittanti D, Iannuzzo F, Hoene E, et al. Role of parasitic capacitances in power MOSFET turn-on switching speed limits: a SiC case study[C]//2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 2017: 1387-1394.

Dynamic Current Balancing Method for Parallel SiC MOSFETs Based on Direct Source Interconnection Strategy

Abstract Driven by the increasing demand for high power, paralleling SiC MOSFETs emerge as a cost-effective and efficient solution to boost current capacity. Multichip SiC power modules with Kelvin-source connection are popular in applications requiring large capacity and high switching frequency, yet dynamic current imbalance persists as a prevalent challenge. As a result, the paralleled SiC MOSFET chips experience unbalanced losses and junction temperatures. In extreme cases, thermal runaway can occur, resulting in chip failure.

Existing dynamic current balancing methods will make the circuit more complex, difficult to design and implement, or increase costs. This paper proposes a method using direct source interconnection (DSI) between the source terminals of paralleled SiC MOSFET chips. By adjusting the DSI parameters, effective current balance can be readily attained. Compared to active methods, this method does not require complex sensors or processing circuits and remains fully compatible with traditional manufacturing techniques. Unlike conventional passive methods, it does not require additional passive components such as resistors, inductors, or capacitors, simplifying implementation and reducing costs. Moreover, it avoids the need for changes to the DBC layout and does not demand complex structural design or precise calculations.

The mechanism of dynamic current imbalance in paralleled SiC MOSFETs is derived through circuit modeling and mathematical analysis, considering both cases with and without the DSI method. The mechanism reveals the current coupling mechanism between the power loop and the drive loop of paralleled SiC MOSFETs under unbalanced power source parasitic inductance. Additionally, the differences in the drive loop and dynamic current caused by this coupling are obtained. In the derived mechanism, the key parameters affecting dynamic current imbalance are identified. The mechanism of action of the DSI dynamic current balancing method is explained. The DSI method effectively mitigates the current coupling between the power loop and the drive loop, thereby reducing differences in the drive loop and dynamic current. This results in a significant improvement in dynamic current imbalance. Furthermore, the method retains the benefits of the Kelvin-source connection, enhancing switching speed and reducing switching losses for the chips.

Simulations and experiments have verified the mechanism of dynamic current imbalance and the effectiveness of the proposed dynamic current balancing method. The results show that the proposed DSI method reduces the dynamic current difference and switching loss difference of paralleled SiC MOSFETs by at least 50%. Additionally, the method preserves the high efficiency of the power module, which features a Kelvin-source connection. Consequently, it provides the dual advantages of balanced current sharing and efficiency optimization.

Finally, the effectiveness of the DSI method is validated in the module with more parallel chips. The results show that in multichip parallel applications, the DSI method demonstrates significant performance advantages compared to the Kelvin-source connection. Moreover, the DSI method requires only a simple wire bonding process, without altering the power module layout or adding extra pins. Therefore, in high-power-density and high-frequency applications, the DSI method meets the dynamic current sharing requirements of multichip power modules while reducing implementation complexity and costs.

Keywords:Paralleled SiC MOSFETs, dynamic current imbalance, dynamic current balancing method, direct source interconnection (DSI), multichip SiC power modules

中图分类号:TM46; TN305

DOI: 10.19595/j.cnki.1000-6753.tces.250133

中国南方电网有限责任公司科技资助项目(GDKJXM20222550)。

收稿日期 2025-01-22

改稿日期 2025-03-22

陈浩斌 男,2000年生,硕士研究生,研究方向为宽禁带半导体功率器件封装与应用。

E-mail: chenhaobin@zju.edu.cn

闫海东 男,1981年生,博士,副研究员,研究方向为宽禁带功率器件新型封装技术。

E-mail: haidong_yan@zju.edu.cn(通信作者)

(编辑 陈 诚)