图1 功率模块封装结构截面

Fig.1 Cross-sectional of power module package

摘要 碳化硅功率器件凭借其优异的性能,成为传统硅器件有力的竞争者。然而,在封装过程中,因键合线以及引出端子等引入的额外寄生电感,致使封装后的碳化硅功率模块会产生较大的开关过冲与振荡,进而难以体现其理论上的优越性。为此,该文提出一种具有极低电感的多芯片整体式Clip互连碳化硅功率模块封装方法,将功率模块内部键合铝线替换成Clip互连,并通过规划陶瓷基板布局,使Clip电流流向与陶瓷基板线路电流相反,利用电流反向耦合效应降低功率模块内部寄生电感。同时,利用电容直连结构消除外部回路寄生电感。经仿真得到的功率模块内部寄生电感为3.8 nH,功率回路电感为5.0 nH。实验测试得到1 200 V/600 A样机功率回路电感为4.53 nH,换流回路总电感5.87 nH,与传统布局功率模块相比电感降低了44.6%。

关键词:碳化硅功率模块 寄生电感 整体式Clip互连 反向耦合 换流回路

功率半导体器件是电力电子变换器的核心部件,在能量转换过程中起着至关重要的作用。近些年,随着技术的快速发展,以碳化硅(Silicon Carbide, SiC)为代表的第三代半导体在轨道交通等中高功率场合的应用受到了广泛的关注。碳化硅器件因其优异的材料特性参数,相比于硅基器件具有高电压、高温工作能力,同时还具备了低导通电阻、高开关速度的特性,从而提高了电力电子变换器的效率和功率密度[1-4]。

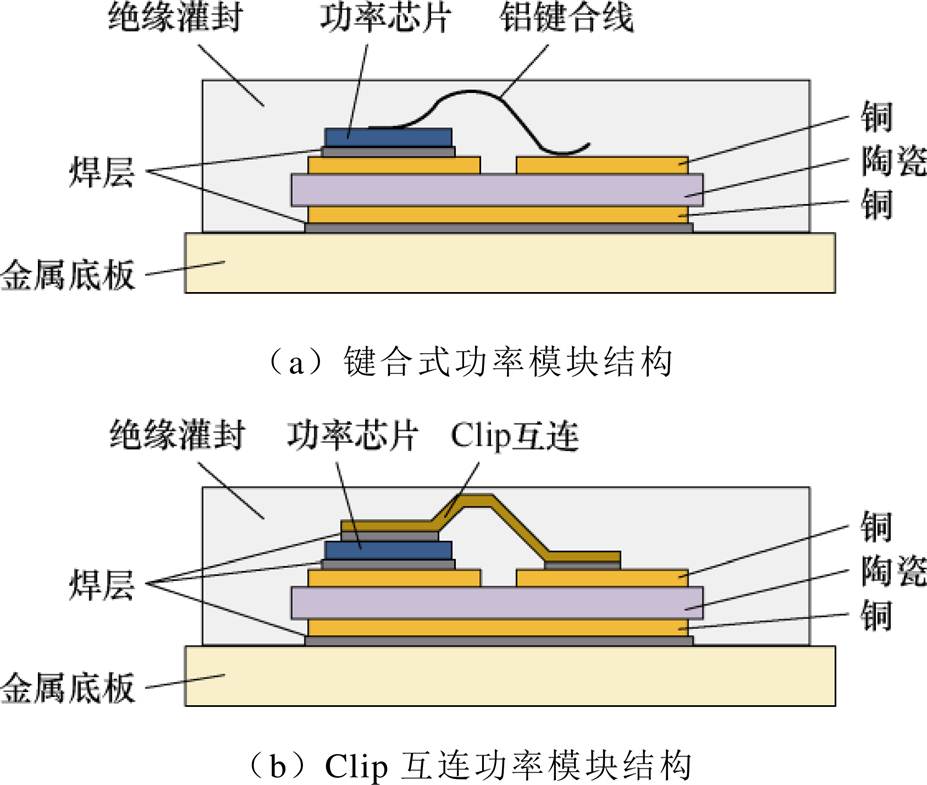

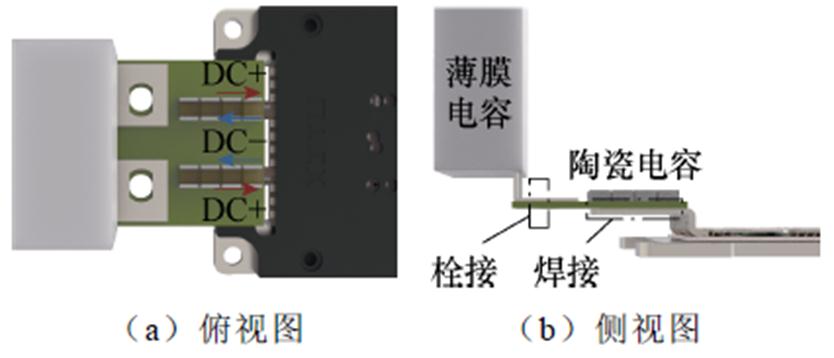

功率半导体芯片通过封装与外部电路进行连接,并将产生的热量耗散出去。在较大功率的电力电子变换器中,常将多个功率芯片封装为一个功率模块,组成半桥等电路拓扑进行使用。功率模块封装结构截面如图1所示。传统的键合功率模块封装结构如图1a所示,功率芯片下表面粘接在具有“铜-陶瓷-铜”的三层结构陶瓷基板上,上表面采用键合铝线完成电气连接。这种封装结构引入的寄生电感较大,直接应用在碳化硅功率模块封装时会因为碳化硅更快的开关速度给开关性能带来更多的负面影响,如增大电压过冲、引发振荡等,从而增大了开关损耗,降低了系统效率,影响电路的安全工作[5-7]。

图1 功率模块封装结构截面

Fig.1 Cross-sectional of power module package

针对这个问题,国内外的学者提出了多种新型封装方法来降低碳化硅功率模块的寄生电感。降低寄生电感的方式主要分为降低回路自感与利用电流反向耦合效应的负互感降低回路电感。降低回路自感一般从碳化硅芯片上表面的芯片互连(inter- connection)入手。传统功率模块封装采用铝键合线进行互连[8-10],这种互连方式会带来较大的寄生电感。为了改善互连结构的自感,学者们提出了多种新型互连方式,如键合铝带[11-12]、键合铜带[13]、混合铝-铜带[14]、铜夹扣(Clip)互连[15-18]等方法,通过增大互连面积的方式来减小回路的电感与电阻。其中,键合线与键合带的键合连接限制其连接形式为两点直接连接,而图1b中的Clip互连为焊接连接,可以包含更多的连接点,并可通过各连接点连通形成复杂线路,具有更高的设计自由度,并且可靠性随连接层的寿命提升而提升[19],具有更广泛的前景。然而,现有的Clip互连技术大多数是对键合线两点互连的直接替代,并没有充分发挥其高自由度的优势,使得采用Clip互连后的功率模块的寄生电感未能大幅降低。另有部分学者通过改进功率模块结构,利用端子之间的耦合效应[20-21]或是多层堆叠线路之间的耦合来降低端子处的寄生电感[22-24]。改进功率模块结构的方法通常可以大幅降低功率模块内部的寄生电感,但也经常会引入新的复杂工艺流程以及与现有系统难以适配的外部接口,这就给实际应用带来了困难。

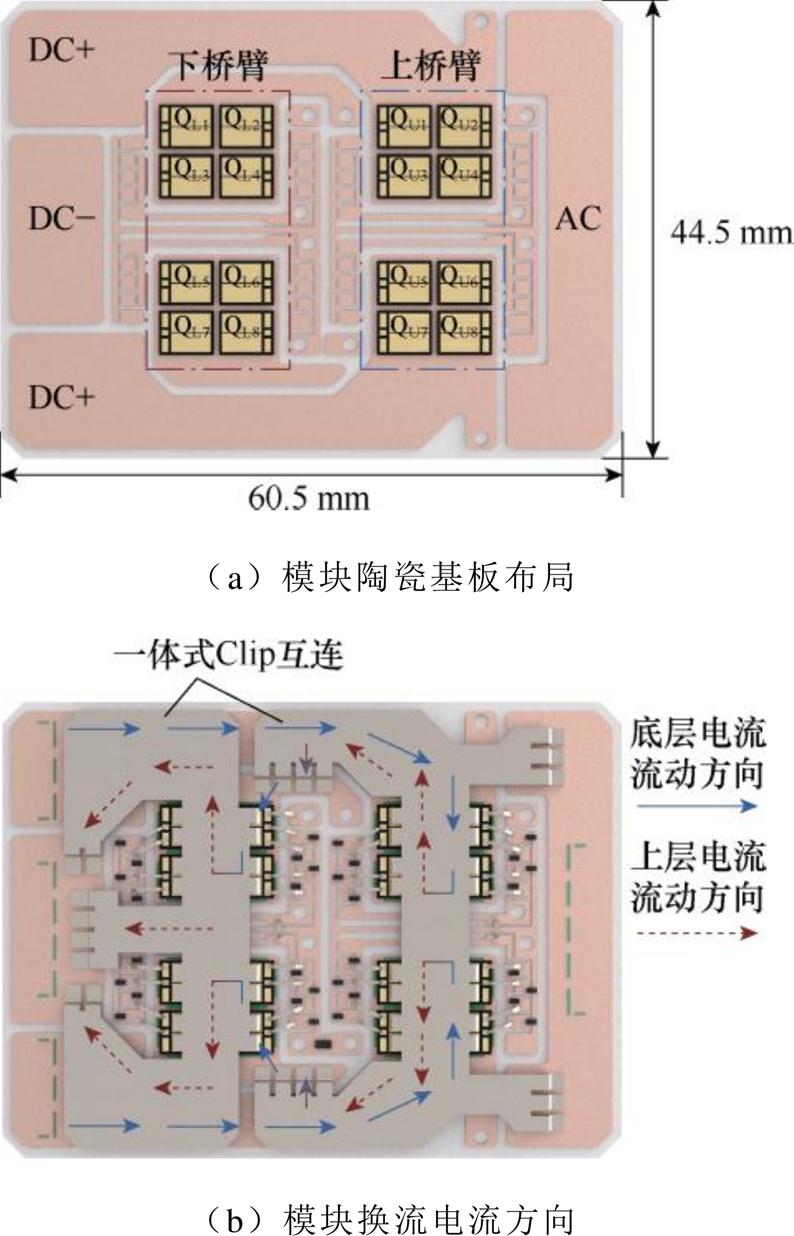

目前,电动汽车领域广泛采用的封装形式为HybridPACKTM Drive(HPD)封装,拓扑形式为三相全桥结构,最早由英飞凌公司提出并应用于IGBT功率模块[25],按照功率模块内同一桥臂的并联芯片排布方式可以分为矩阵布局[26-27]和线型布局[28-29]。其中,线型布局适合面积较大的硅IGBT芯片,而矩阵布局因可以并联更多数量的小面积芯片而适合碳化硅芯片。然而,在使用传统封装方式时,这种布局的功率模块内部换流回路总寄生电感仍较难优化至10 nH以下,在通过功率端子引出连接至外部电路电容时,换流回路总电感甚至会超过20 nH,这使得目前的HPD功率模块布局不利于碳化硅模块的高性能使用。

本文提出一种整体式Clip互连结构,基于矩阵型HPD功率模块布局,利用一个整体式Clip互连完成所有并联芯片的上表面互连。得益于Clip互连的高自由度,所设计的整体式Clip互连形成了独立于陶瓷基板的另一层导电回路,更充分地利用了电流反向耦合效应优化功率模块内部寄生电感,设计了具有极低寄生电感的1 200 V/600 A半桥多芯片碳化硅功率模块。同时,利用电容直连(Capacitor Direct Connection, CDC)结构替代端子栓接结构来消除功率模块外部的寄生电感,从而获得具有极低寄生电感的换流回路。最后,本文制作了所设计的功率模块样机并进行测试,验证了所提出的多芯片整体式Clip互连功率模块封装方法具有极低的寄生电感。

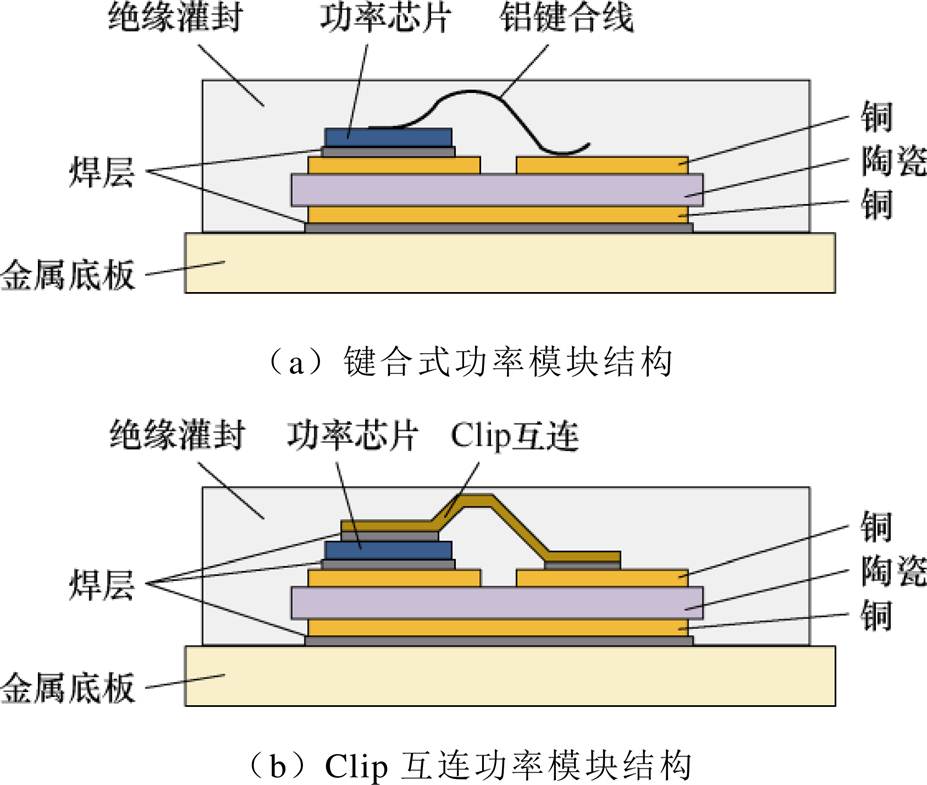

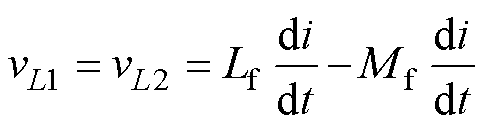

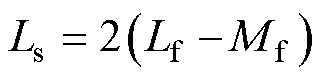

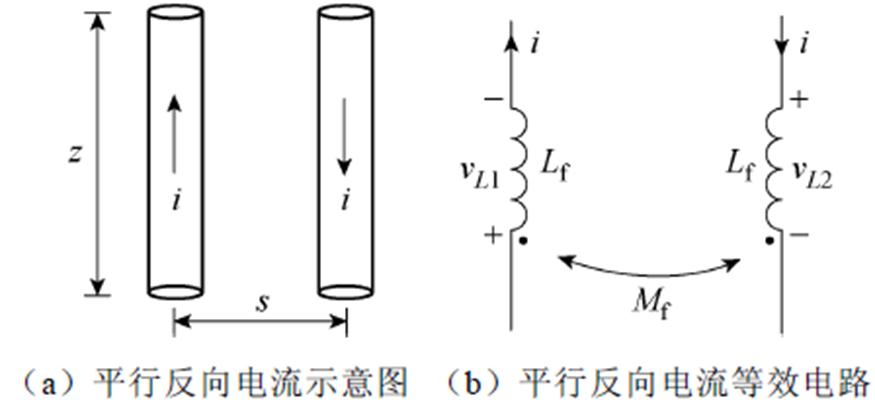

在功率模块内部,寄生电感来源于端子、电路布局与芯片互连三部分,在电流流过功率模块内部电路时,功率回路上固有的寄生电感Ls会在流通路径上产生压降,从而在开关过程中产生电压过冲,并降低开关速度。为了减小模块内部电感,通常采用减小自感与利用电流的反向耦合效应的方法。将功率模块中的电感在如图2所示的双线传输平行反向电流寄生电感模型中使用微元电流建模,具有平行反向电流的双传输线上的电感由导线自身的电感与电流产生的互感组成,其在导线上产生的压降vL1、vL2与功率回路电感Ls可分别表示为

(1)

(1)

(2)

(2)

式中,i为传输线上的电流;Lf与Mf分别为单根传输线上的自感与两根传输线间的互感。

图2 双线传输平行反向电流寄生电感模型

Fig.2 The parasitic inductance model of parallel current transmitted by two wires

式(1)与式(2)中的自感与互感可分别近似表示为

(3)

(3)

(4)

(4)

式中,m0为真空磁导率;rw为传输线半径;z为导线长度;s为两根传输线的距离。

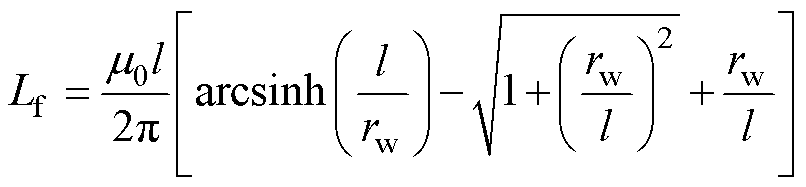

在功率模块中,用于通流的线路布局一般具有一定的长度和宽度,为了使寄生电感计算模型更加符合功率模块内部情况,设置长×宽×高为l×w×h的长方体导体,电流沿长度方向流动,并有l>w h。由此,建立如图3所示用于计算导体自感与互感的长方体导体寄生电感模型,并忽略导体厚度。

h。由此,建立如图3所示用于计算导体自感与互感的长方体导体寄生电感模型,并忽略导体厚度。

图3 长方体导体寄生电感模型

Fig.3 The parasitic inductance model of cuboid conductors

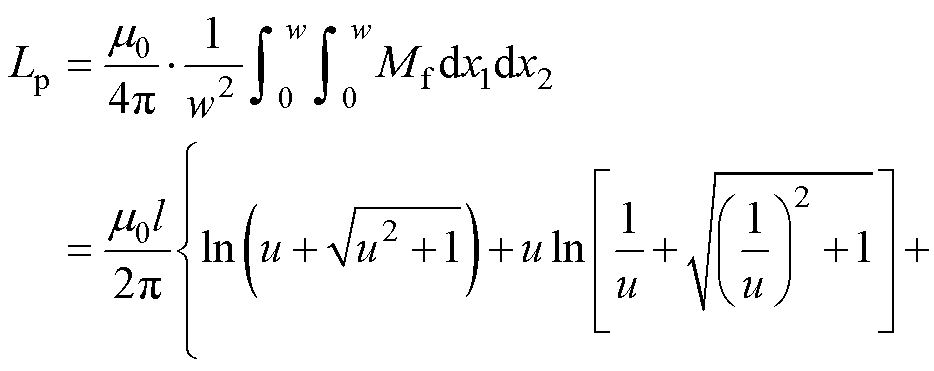

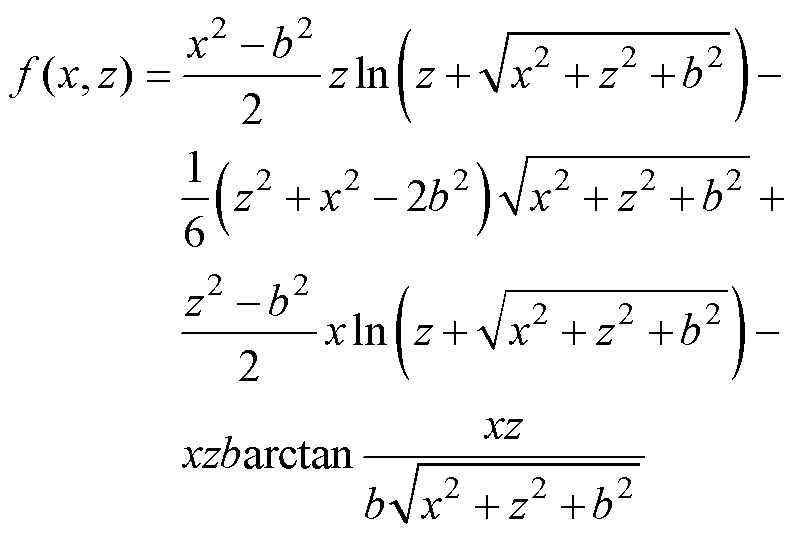

图3a中的长方体导体自感的计算通过对距离左边界分别为x1与x2的线电流的互感在整个宽度w上积分得到,所得到的自感Lp表示为

(5)

(5)

式中,u=l/w。

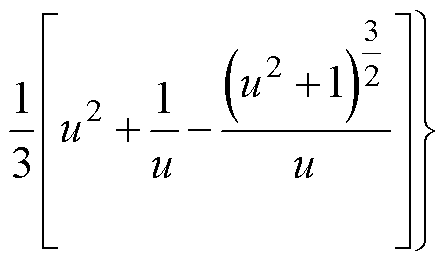

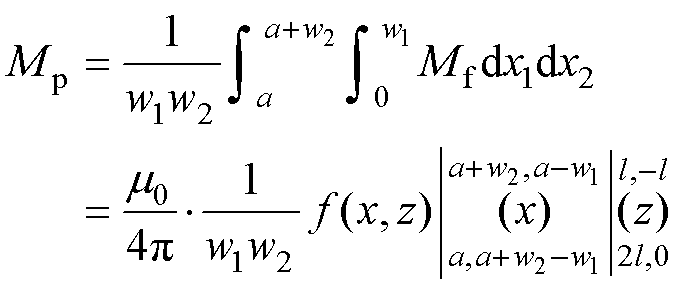

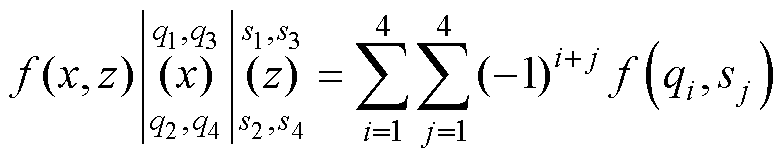

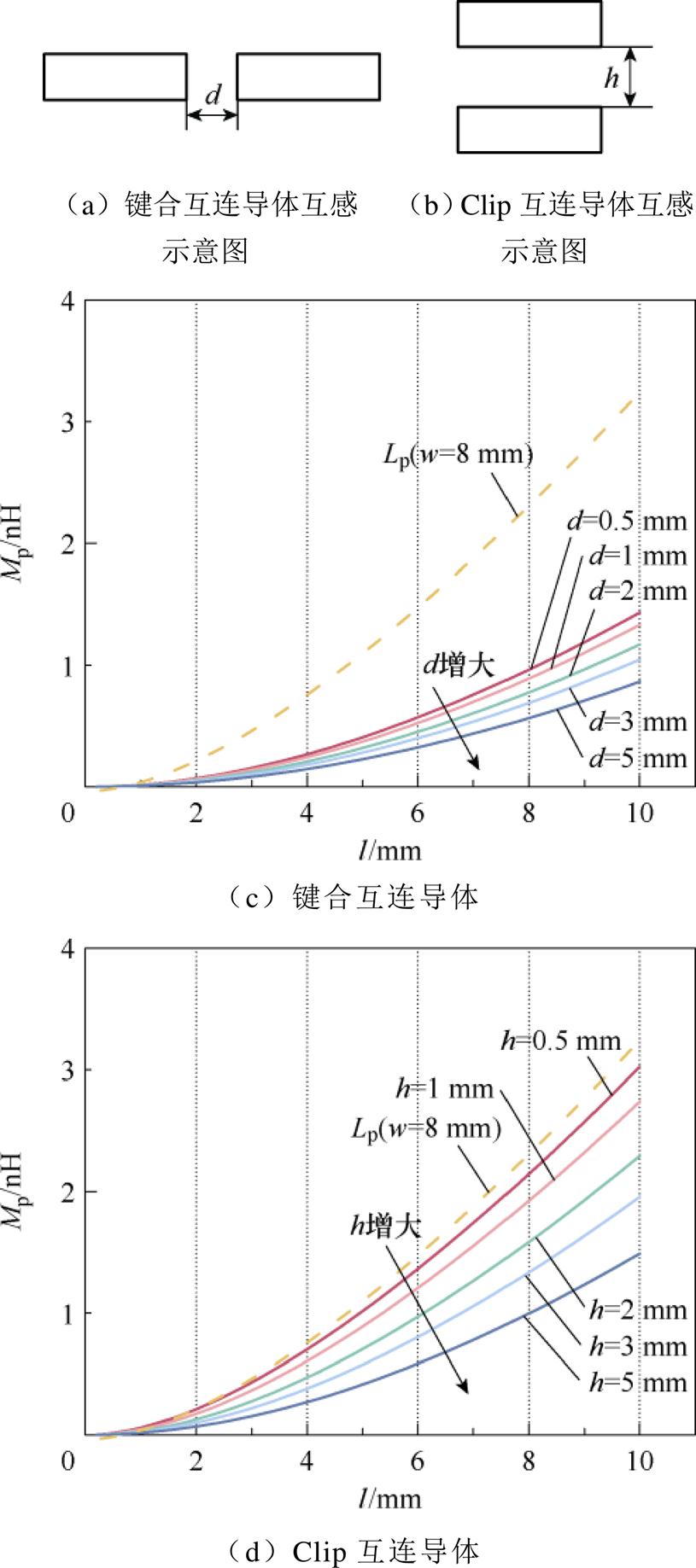

对于图3b中的长方体导体互感也用相同的积分方法计算,以下方宽度为w1的长方形导体左边界为原点,规定上方宽度为w2的长方形导体距离原点的水平与垂直距离分别为a与b。对下方距离原点水平距离x1与上方距离原点水平距离x2的线电流互感进行积分,所得到的互感Mp可表示为

(6)

(6)

其中

(7)

(7)

(8)

(8)

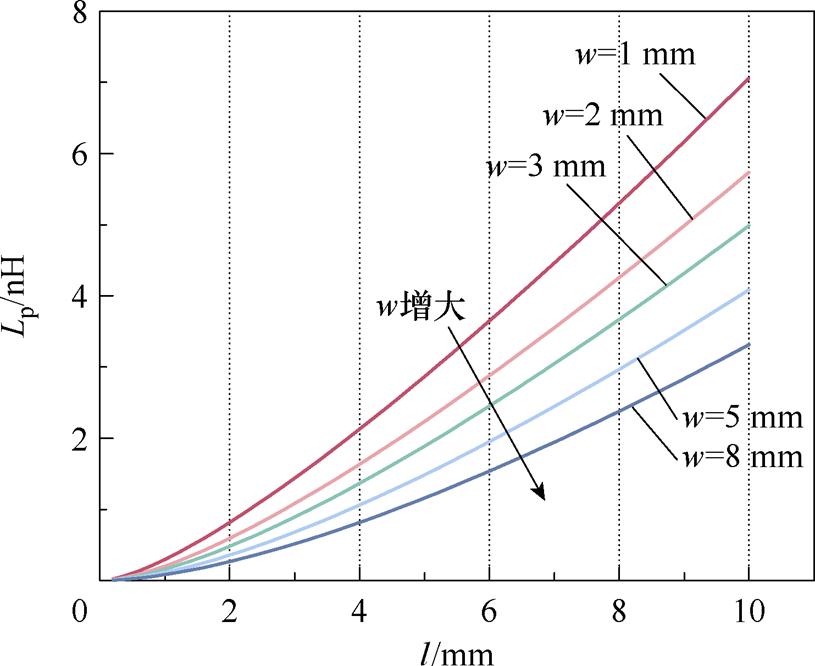

功率模块内部主要的寄生电感来源于线路布局。经过以上建模计算,可在一定程度上对功率模块内部的寄生电感进行量化。图4为长方体导体自感计算值随其尺寸变换的关系曲线,可以看出,导体自感Lp随长度l的增加而增加,并且Lb增加的斜率也随l的增加而缓慢上升;与之相反,随着宽度w的增加,Lp会逐渐降低,但增大导体宽度以降低自感的效率小于减小导体长度以降低自感的效率。另外,对于电感的考虑通常是在高频工作下,而高频下的趋肤效应会导致电流仅集中在较宽导体的两端,这更加削弱了通过调整导体尺寸来降低自感的效果。由此,在功率模块中首选的降低自感的方法为减小导体长度,并适当增加导体的宽度。但由于功率模块内部要形成特定的拓扑,保证一定的绝缘间隙,并在特定位置利用端子引出线路,这导致线路长度无法无限制地减小,使得减小自感的空间极为 有限。

图4 长方体导体自感随尺寸参数变化的关系曲线

Fig.4 The relationship curves of self inductance of cuboid conductor with dimension parameters

功率模块内部空间有限,各电流通路之间的距离较小,因此功率模块内部回路之间的电流耦合效应产生的互感也必须被纳入考虑。在传统的键合型功率模块内部,所有电流通路均在一个平面内,如图5a所示,所产生的电流耦合效应较弱;而采用如图1b所示的Clip互连可以将电流通路布置在陶瓷基板的导体上方,如图5b所示,从而产生较强的电流耦合效应。分别计算这两种放置方式的互感,在w1=w2=8 mm时,键合互连中平行放置导体与Clip互连中垂直放置导体的互感值Mp随导体尺寸和位置参数的变化关系分别如图5c与图5d所示。可以看出,导体间的互感随着导体长度的增加而增加,并随水平距离d或垂直距离h的增大而减小。值得注意的是,在图5c与图5d中,Clip互连的耦合效应要远大于键合互连中导体的耦合效应,并且Clip互连由耦合效应产生的互感在垂直距离h较小时与其本身自感非常接近。依据式(2),在Clip互连结构中,当距离极短的两段导体的电流方向相反时,其反向电流耦合效应可以将单位长度的导体寄生电感降至极低的程度,此时即使在较长的功率回路长度下也可以得到极低的电感。因此,Clip互连利用在功率模块内部通过规划电流路径,使功率回路上的电流更多地产生反向电流对,可以很大程度地降低总体环流回路的寄生电感。

图5 导体互感值随尺寸与位置参数的变化关系

Fig.5 The relationship of mutual inductance values of cuboid conductors with dimension and position parameters

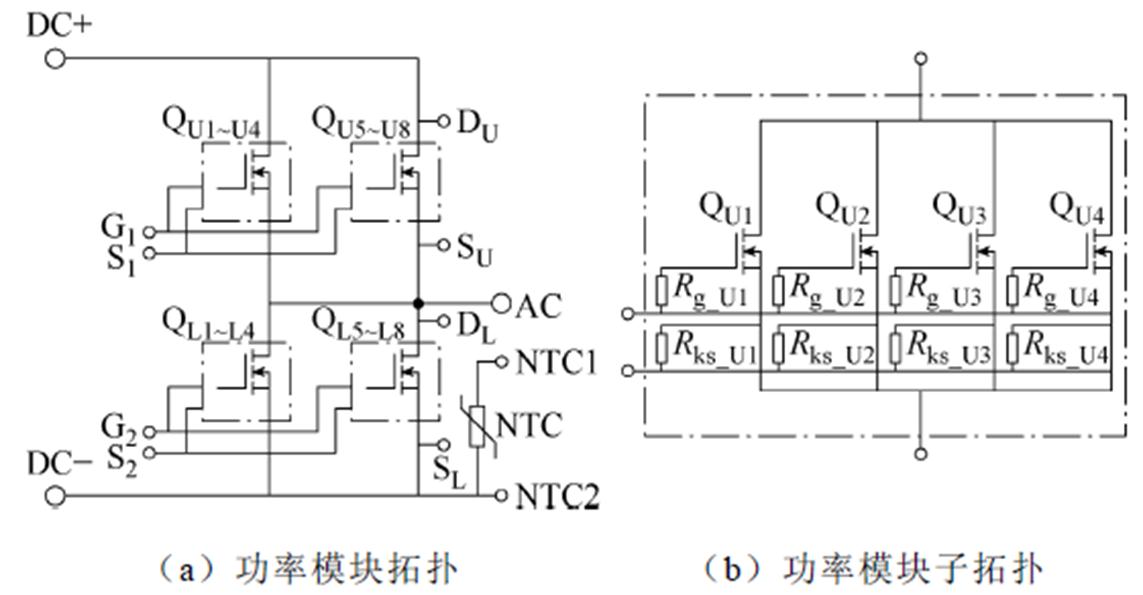

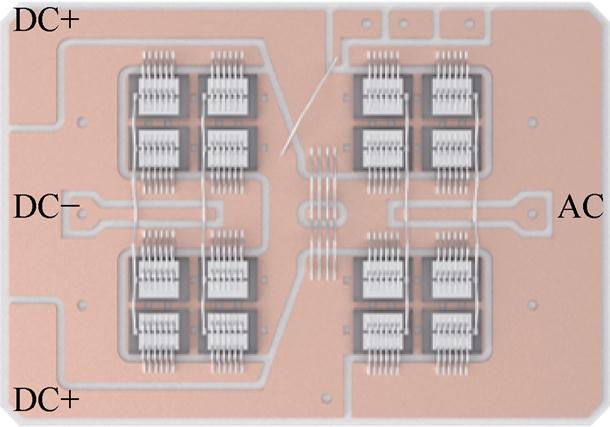

本节以矩阵型HPD的陶瓷基板布局为基础,提出8芯片并联的低电感碳化硅半桥功率模块,半桥同一侧的所有并联芯片上表面互连采用一个整体式Clip结构完成,其总体拓扑如图6a所示。本文所提出的半桥功率模块将每个桥臂分为两个如图6b所示的子拓扑,并引出对应的功率端子、驱动端子与测量端子。通过在功率模块内部集成分立驱动电阻,为每个并联芯片添加驱动电阻来减小驱动回路的振荡。最后在模块内集成负温度系数(Negative Temperature Coefficient, NTC)热敏电阻来间接测量功率模块内部功率芯片结温。

图6 多芯片整体式Clip互连碳化硅功率模块拓扑

Fig.6 Topology of multi-Chip silicon carbide power module with integral Clip bonding

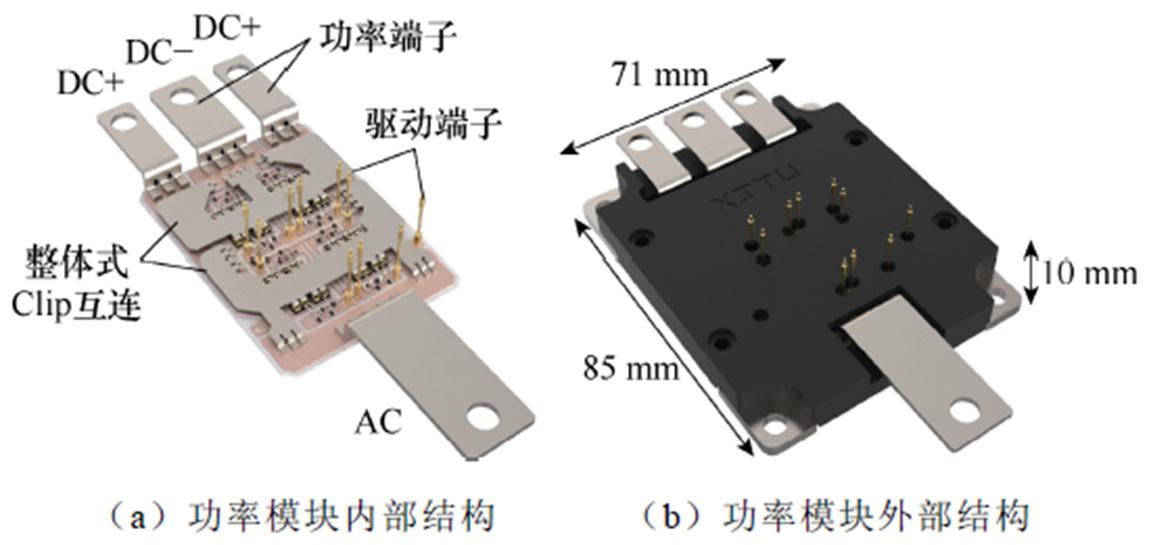

所提多芯片整体式Clip互连碳化硅功率模块结构如图7所示,内部不采用键合线互连,而是采用整体式Clip互连将同一桥臂的所有并联芯片同时连接,并实现高于陶瓷基板线路的另一层走线线路,从而构建距离接近的反向电流对。陶瓷基板采用氮化铝(Aluminum Nitride, AlN)活性金属钎焊(Active Metal Brazing, AMB)陶瓷基板,功率模块内部的对应电位由功率端子与驱动端子引出,在安装了金属底板与外壳后,金属底板尺寸为85 mm×71 mm,外壳与底板的总高度为10 mm。

图7 多芯片整体式Clip互连碳化硅功率模块结构

Fig.7 Structure of multi-chip silicon carbide power module with integral Clip bonding

根据热仿真,所设计的碳化硅功率模块在每个芯片损耗为250 W时,最高结温达到约150℃。设计采用的碳化硅MOSFET在常温下的额定等级为 1 200 V/14.7 mW。根据数据手册,在150℃时的导通电阻约为31 mW,计算可得导通电流约为90 A。考虑到计算时未纳入开关损耗,所以对计算的电流降额为额定电流,因此本文所设计的模块额定等级为1 200 V/600 A。

图8为一个传统矩阵型HPD布局的碳化硅半桥功率模块,通过陶瓷基板布局将每个桥臂分为对称的两组,并将DC+一侧的铜路布局对称化,从而达到较好的均流均温性能。但是,由于采用铝键合线互连,这种布局的反向电流对的路径并未垂直正对,其产生的反向耦合效应较弱,导致降低功率模块内部电感的效果较差,模块内部功率回路寄生电感Lin=6.0 nH,在使用螺栓连接功率端子与外部电路时Lin增大至18 nH。

图8 传统矩阵型HPD碳化硅功率模块布局

Fig.8 Layout of a conventional matrix HPD silicon carbide power module layout

基于2.1节的讨论,为了提出具有极低寄生电感的功率模块,需要利用整体式Clip互连构建一层额外的走线路径,并通过规划电流路径,利用反向电流对的反向耦合效应充分降低换流回路部分的寄生电感。同时为了最大程度地降低寄生电感,需要尽可地能增加陶瓷基板与整体式Clip上的铜路宽度,并减小铜路的走线长度,充分利用陶瓷基板的铜路与Clip互连之间的负互感来减小电感。

由此提出的碳化硅功率模块布局结构如图9所示。图9a中,与传统矩阵式布局相同的是,所提出的布局在同一桥臂并联的8颗芯片被分为两组,并对称地放置在两侧;与传统布局不同的是,本文提出的布局引入了如图9b所示的整体化Clip互连,这使芯片上表面互连部分的线路布置拥有了远超键合铝线的自由度,从而实现了本文提出的线路布局。首先,由于两个桥臂的源极互连部分被分配到上层回路,给陶瓷基板上的线路提供了更多的走线空间,使得DC+部分的回路宽度大幅增加,从而降低了此部分的自感。随后,规划功率模块内部电流流动路径如图9b,使得在换流过程中绝大部分的功率电流在底层陶瓷基板铜路和上层Clip铜路的电流方向均构成反向电流对,从而最大程度地增大反向电流耦合效应,降低回路整体寄生电感。经过优化后,在仿真中功率模块内部功率回路电感Lin减小至3.8 nH,相比原布局寄生电感减小36.7%。

图9 整体式Clip互连碳化硅功率模块布局结构

Fig.9 SiC MOSFET power module layout with integral Clip bonding

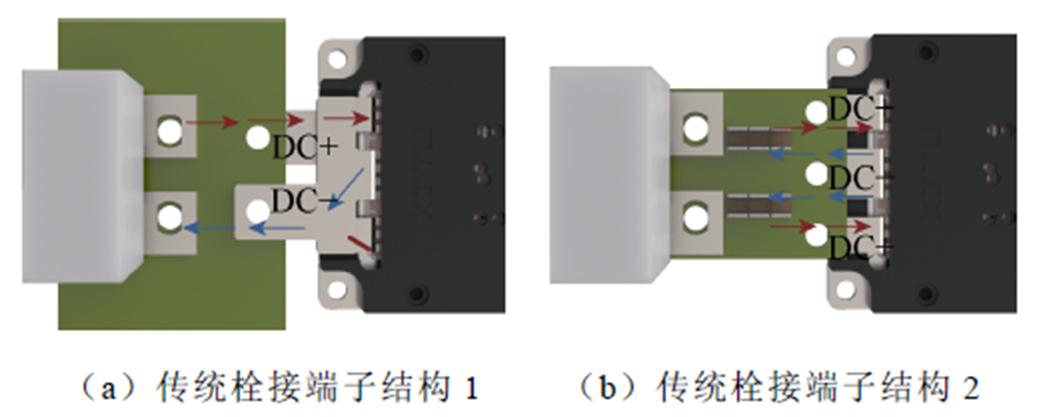

功率模块换流回路的寄生电感影响功率模块的开关过程,换流回路的路径由功率模块外部安装的电容出发,从DC+端子经过功率模块内部上下桥臂后从DC-至电容另一侧,构成一个完整的回路。换流回路寄生电感组成包括功率模块内部功率回路电感Lin、功率端子部分电感Lter、外部连接电路电感Lext、电容的等效串联电感(Equivalent Series Indu- ctance, ESL)LC。

传统功率模块的功率端子以及外部连接方式如图10a所示,在布局中分立为两部分的DC+端子利用引出功率端子合并,外部连接电路常采用叠层母排减小寄生电感,并采用栓接的方式连接外部电路与功率端子、薄膜电容等。在这种连接结构中,功率模块外部的功率端子难以利用反向耦合效应减小寄生电感,因此端子部分的寄生电感Lter常常较大(大于10 nH);同时,所采用薄膜电容也具有较大的电感(LC>5 nH),由于外部回路与薄膜电容产生的寄生电感远大于功率模块内部的寄生电感,使得通过优化功率模块内部电感的方式对功率模块整体开关性能的提升较小。因此,对功率模块外部电路电感进行优化,也是减小功率模块换流回路电感,提升功率模块性能的一个重要部分。在图10b中采用的栓接端子结构在分立的功率端子引出后立即利用螺栓与线路板连接,并放置ESL更小的陶瓷电容,缩短了回路长度。然而,因为栓接的关系,需要在外部电路为螺栓连接预留足够的空间与绝缘间距,这仍会增大外部连接电路寄生电感Lext,进而引入额外的电感。

图10 碳化硅功率模块传统栓接端子示意图

Fig.10 The structure of traditional bolted terminal in SiC power module

本文提出了如图11所示的碳化硅功率模块电容直连结构示意图。所提出的结构不采用端子栓接的方式,而是将线路板与引出的端子直接进行焊接连接,并在端子引出功率模块的位置就近放置陶瓷电容,完成功率模块与外部电路的解耦,将大部分功率端子的长度也划分至外部电路部分,最大限度地消除功率端子与外部连接电路电感对开关过程的影响,降低了换流回路上的总寄生电感。通过采用所提出的电容直连结构,几乎消除了外部连接电路引入的额外线路电感Lext,并大幅降低了功率端子部分电感Lter。经过电容直连结构的优化,图11中功率端子部分电感Lter仅为1.1 nH,约为传统端子连接结构寄生电感的10%,这是因为占据功率端子主体寄生电感部分的长度被解耦电容划分至外电路,在功率回路中仅剩余引出至外壳的长度。结合所提出的整体式Clip对内部电感Lin的优化与电容直连结构对外部电感Lter的优化,功率回路的总寄生电感Ls=Lin+Lter在仿真中约为5 nH。

图11 碳化硅功率模块电容直连结构示意图

Fig.11 The structure of capacitor direct connection in SiC power module

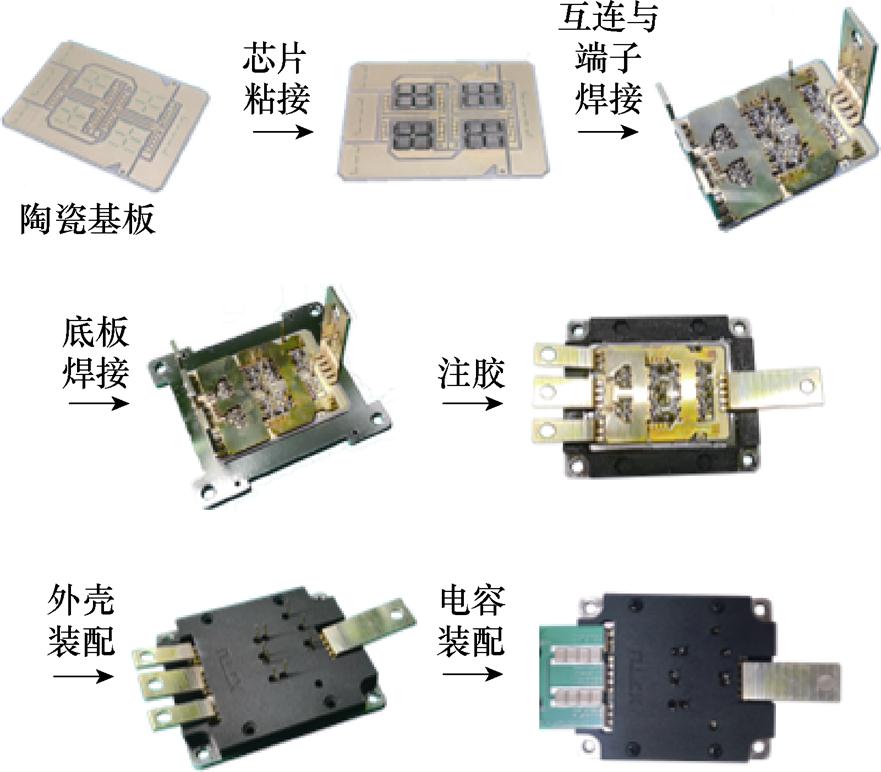

为了验证以上所设计的多芯片整体式Clip互连碳化硅功率模块具有极低的换流回路寄生电感值,本文进行了功率模块的样机制作与测试。样机制作流程如图12所示,所使用的材料与属性参数见表1。

图12 多芯片整体式Clip互连碳化硅功率模块样机制作流程

Fig.12 Fabrication of the multichip SiC MOSFET power module prototype with integral Clip bonding

功率模块的制作分为多步焊接,为了后序工艺不影响前序工艺,需要使用多种熔点的焊料完成工艺流程。

(1)芯片粘接,在陶瓷基板上印刷焊料Sn90/ Sb10(熔点约260℃),放置芯片后进行第一步回流焊接,回流焊接中的芯片需要使用阻焊层或使用额外的模具进行位置固定,防止发生芯片位置偏移。

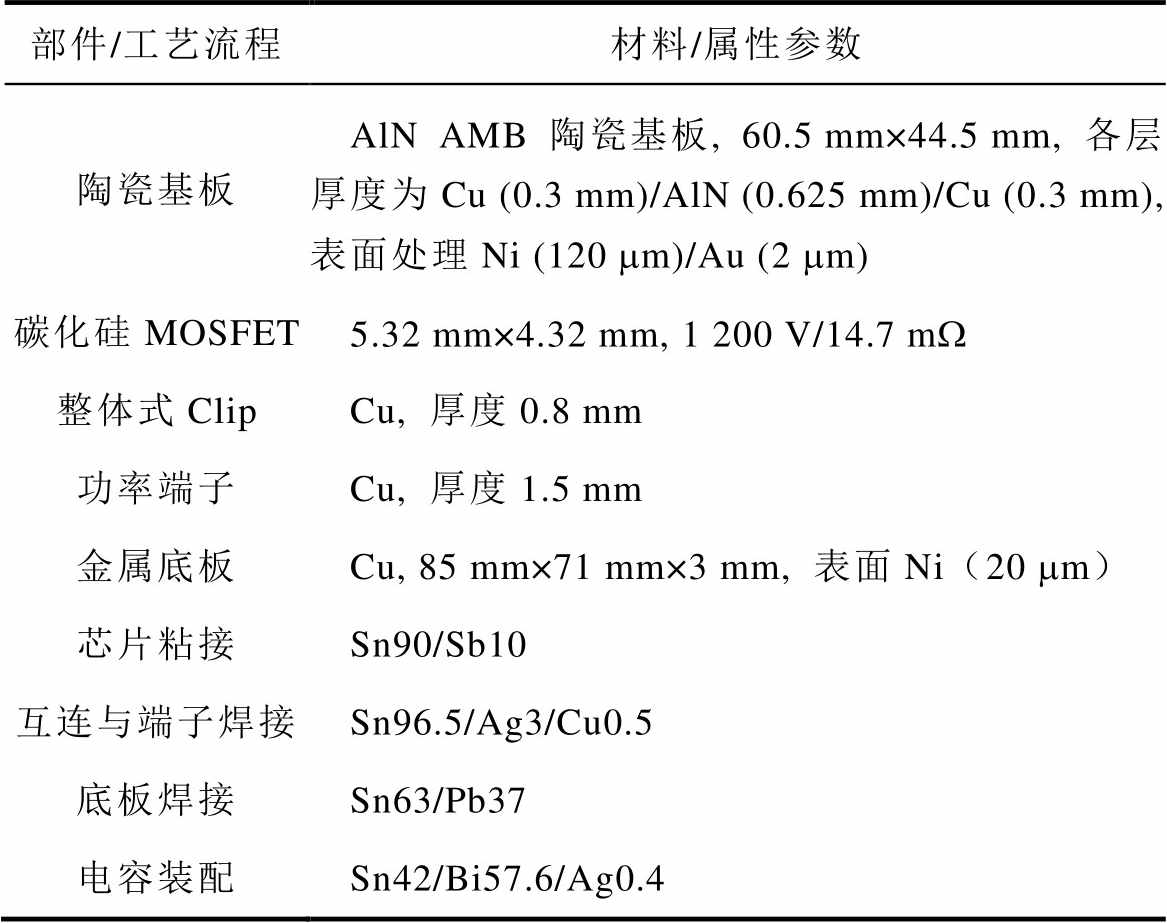

表1 碳化硅功率模块样机工艺流程材料属性参数

Tab.1 Material parameters of the SiC power module prototype in fabrication

部件/工艺流程材料/属性参数 陶瓷基板AlN AMB陶瓷基板, 60.5 mm×44.5 mm, 各层厚度为Cu (0.3 mm)/AlN (0.625 mm)/Cu (0.3 mm), 表面处理Ni (120 mm)/Au (2 mm) 碳化硅MOSFET5.32 mm×4.32 mm, 1 200 V/14.7 mW 整体式ClipCu, 厚度0.8 mm 功率端子Cu, 厚度1.5 mm 金属底板Cu, 85 mm×71 mm×3 mm, 表面Ni(20 mm) 芯片粘接Sn90/Sb10 互连与端子焊接Sn96.5/Ag3/Cu0.5 底板焊接Sn63/Pb37 电容装配Sn42/Bi57.6/Ag0.4

(2)焊接使用焊料Sn96.5/Ag3/Cu0.5(熔点约218℃),这一步需要完成模块内部的互连与模块端子的连接,模块内部芯片的整体式Clip、栅极与开尔文源极的驱动Clip、模块内部放置的NTC热敏电阻与栅极隔离电阻、栅极引出端子等均需要在这一步完成焊接。功率引出端子除在这一步焊接外,也可以在这一步焊接完成后采用超声焊接的方式进行连接。

(3)焊接将完成互连与端子焊接后的陶瓷基板与金属底板连接,连接采用焊料Sn63/Pb37(熔点约183℃)。连接好金属底板后,将底层外壳安装在底板上,注入配置好的灌封胶,等待灌封胶固化后装配顶部外壳,样机即制作完成。

出于方便,本文所提出的电容直连结构在样机中使用PCB与引出的DC+、DC-功率端子直接连接构成电容直连结构,在大功率的应用场景下应当使用耐受更高电流的叠层母排等厚铜线路板。所使用的PCB下表面与引出的功率端子的连接采用焊料Sn42/Bi57.6/Ag0.4(熔点约150℃)。为了方便组装,此处采用的焊料熔点较低,但由于端子处距离热源碳化硅芯片较远,在正常水冷工作散热条件下并不会达到过高的温度。电容直连结构的主体PCB下表面与引出功率端子连接后,上表面放置多个陶瓷电容,最大限度地减小换流回路的面积,同时减小由功率端子以及外部电容引入的寄生电感,从而得到极低的功率回路寄生电感。

表2展示了本文所提出的碳化硅功率模块样机与市面上商用功率模块的材料成本对比,本文所提出的封装结构在装配工艺上与传统封装结构相比,最大的区别在于芯片源极互连步骤。传统功率模块所需的源极引线键合步骤,被替换为本文整体式Clip的焊接。因为整体式Clip较高的精度定制要求,在较小规模制作时成本偏高,而在大批量制作时的规模效应可以将成本控制到极低的水平,仅略高于键合铝线,碳化硅功率模块中的主要材料成本仍是碳化硅芯片成本。因此,本文所提出的结构对功率模块封装成本上浮较小。

表2 碳化硅功率模块样品与商用模块材料成本对比

Tab.2 The material cost comparison between the proposed SiC power module prototype with commercial SiC power modules

样品材料成本 本文功率模块样品商用功率模块 碳化硅芯片约100CNY/pcs×16约100CNY/pcs×16 陶瓷基板约50CNY/pcs约50CNY/pcs 芯片互连整体式Clip 400CNY/套极低 端子与外壳约200CNY/套<50CNY/套

注:CNY表示人民币;pcs表示片。

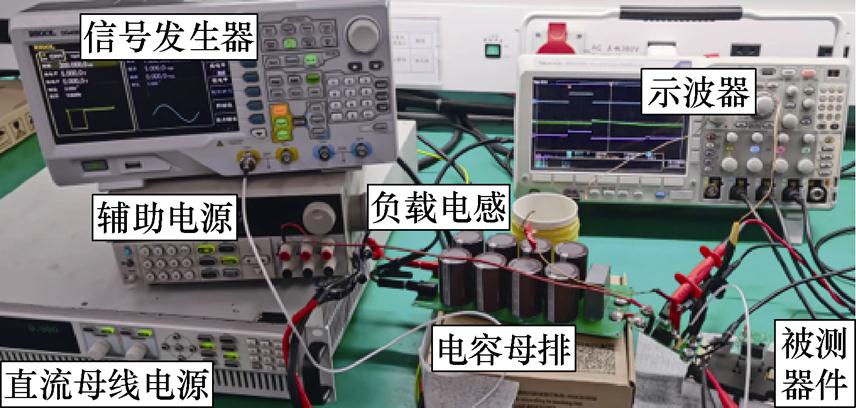

搭建如图13所示的实验平台对所制作的碳化硅功率模块样机进行性能测试。实验平台主要设备包括直流母线电源(1 200 V,5 A,3 kW)、辅助供电电源(30 V,3 A)、信号发生器(60 MHz,500 MSa/s)、示波器(500 MHz,2.5 GSa/s),由直流母线电源向功率回路供电,由辅助供电电源向驱动回路供电,信号发生器产生所需要的驱动脉冲波形,采用示波器读取、储存测量波形数据,测量器件两端电压采用差分探头(1 500 V,500 MHz),测量器件的电流采用罗氏线圈(3 000 A,20 MHz)。

图13 样机测试实验平台

Fig.13 The test platform for the prototype

测试平台的外部其他电路部分主要包含电容母排与负载电感。电容母排由电解电容组与薄膜电容组成,电解电容组(1 000 V,940 mF)由8个电解电容(500 V,470 mF)通过两组串联、四组并联构成,主要负责在快速的脉冲测试中稳定直流母线电压。薄膜电容(900 V,20 mF)相比电解电容来说具有较低的ESL,可以过滤电容母排较大的寄生电感产生的影响,降低低频电压振荡。负载电感采用空芯电感,电感值为22 mH。

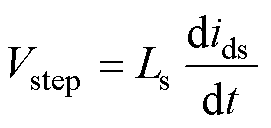

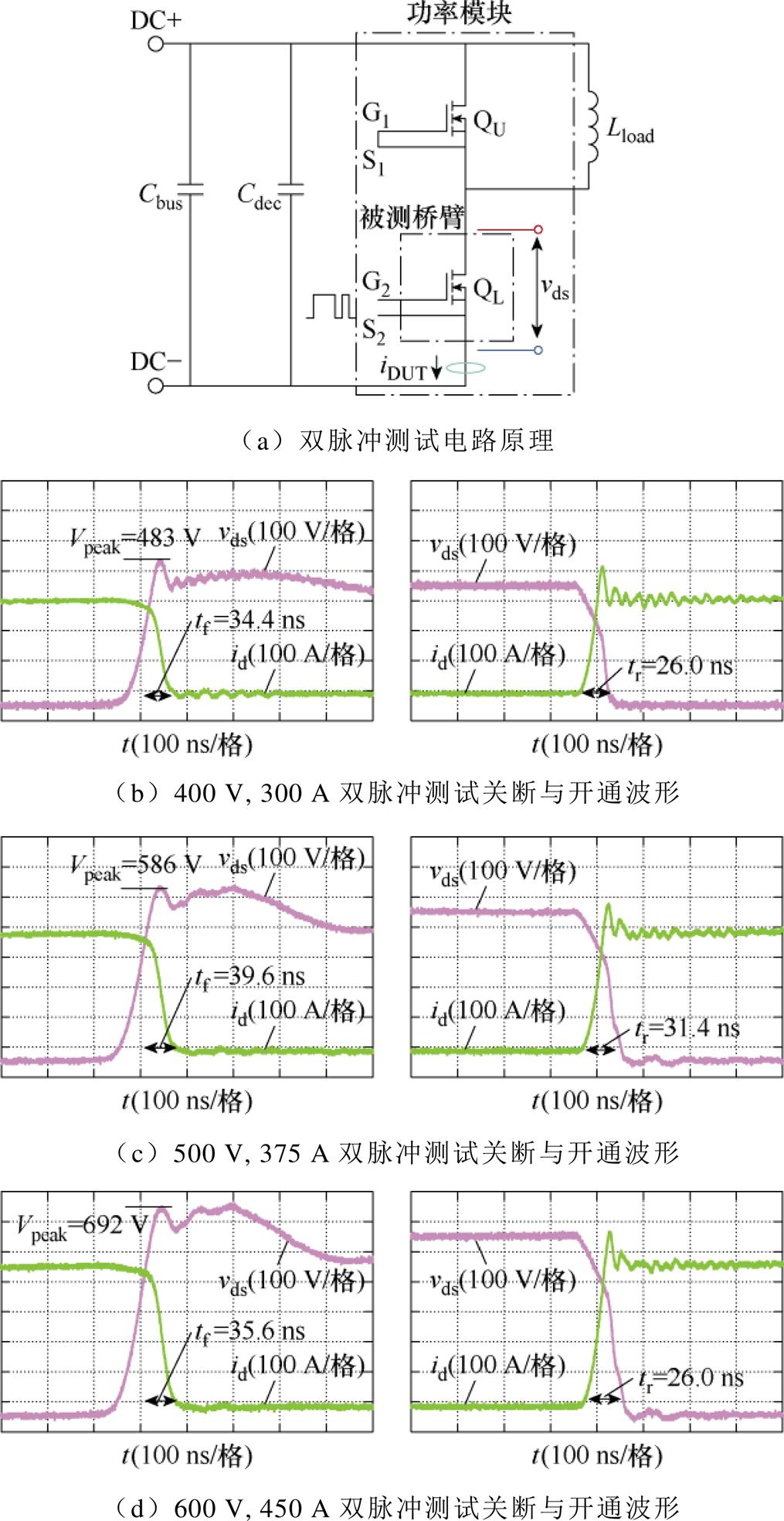

对所制作的功率模块样机进行两项测试,分别测试了功率模块的功率回路寄生电感Ls与开关性能。对功率模块的寄生电感测试参考IEC 60747-15中的功率器件电感测试方法[31],测试电路原理如图14a所示。其中,在电感测试中以所制作的功率模块为实验组,以图8中传统布局的功率模块为对照组同时进行测试,来对比优化前后的功率模块内部寄生电感。将被测器件上、下桥臂的栅极与源极均作短接处理,保证关断。在外部串联一个辅助开关管Qa,在被测器件两端并联负载电感Lload,向Qa输入长、短两个脉冲波形,长脉冲用于向负载电感充电,在长脉冲关断时,负载电感通过被测器件体二极管续流。在第二个短脉冲开通时,体二极管的电流以接近恒定的速率减小,此时电流的变化率会在被测器件两端形成一个跳变的电压平台,电压平台值表示为

(9)

(9)

式中,Vstep为第二个脉冲到来后被测器件两端电压的跳变值;ids为通过被测器件体二极管的电流值。

图14 碳化硅功率模块寄生电感测试波形

Fig.14 The waveforms of the parasitic inductance test for the SiC power modules

测试中的直流母线电压取200 V,长脉冲的长度为14 ms,计算可得负载电感上的电流值约为127 A。在第二个短脉冲开通时刻,测试所得对照组与实验组的波形分别如图14b和图14c所示。在辅助开关管Qa开通前,器件两端电压为体二极管压降;在辅助开关管Qa开通后,体二极管电流迅速下降,在电流变化率较为平稳的一个阶段测量电压跳变平台值可以求得器件功率回路寄生电感。在图14b中的传统布局功率模块电感测量波形中,跳变电压平台值Vstep=19.2 V,电流变化率di/dt=2.35 A/ns,求得传统布局的功率模块功率回路寄生电感Ls=8.17 nH;作为对比,在图14c中的整体式Clip功率模块电感测量波形中,跳变电压为12.0 V,电流变化率为2.65 A/ns,以此求得所制作的整体式Clip碳化硅功率模块样机功率回路寄生电感为4.53 nH,与传统布局的模块相比降低了44.6%,测试结果证明所提出的碳化硅功率模块整体具有极低的功率回路寄生电感。

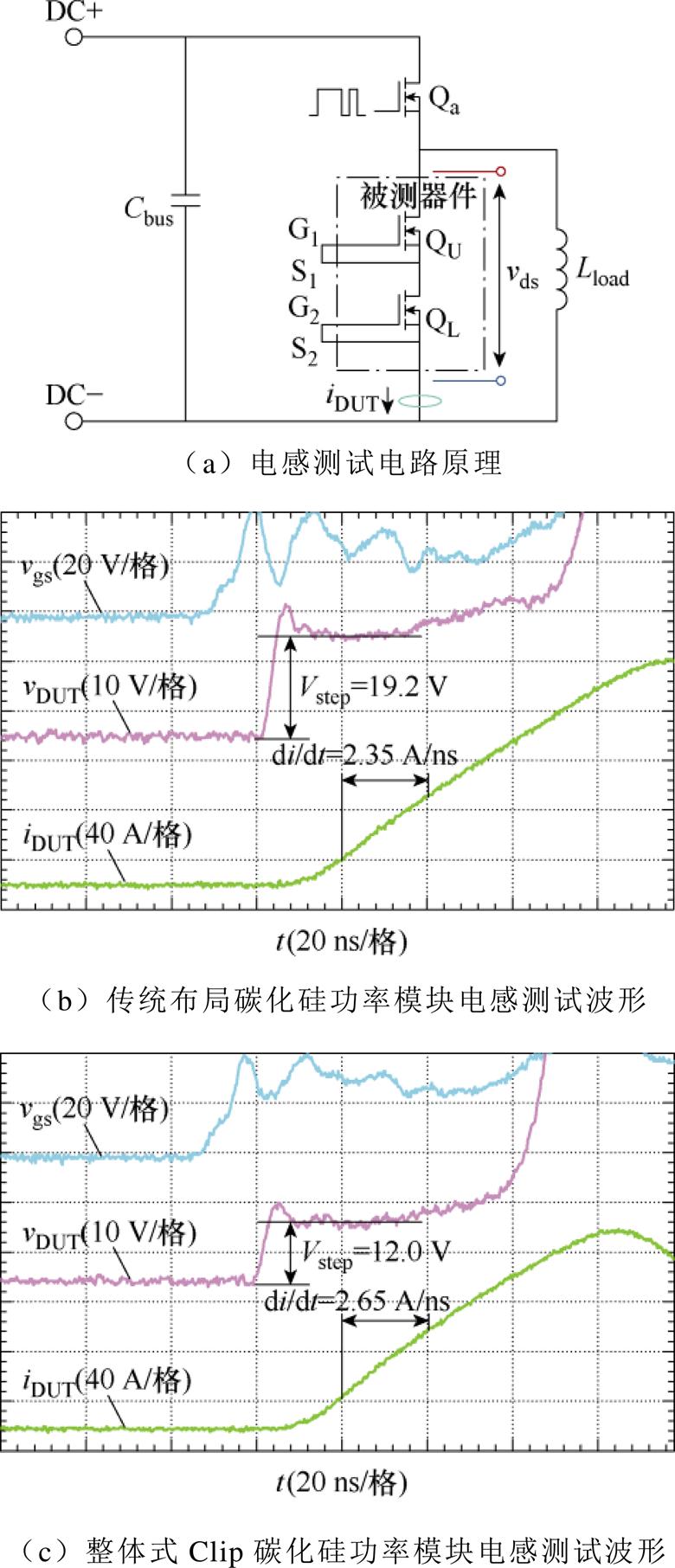

在通过图14的电路测试了所提出的碳化硅功率模块的换流回路寄生电感后,对制作的功率模块样机的开关特性进行测量,测量采用如图15a所示的双脉冲电路。在双脉冲电路中,测试下管的开关性能,将负载电感与上管并联,将上管的栅极与源极短接,利用体二极管进行续流。向下管的栅源极输入长、短两个脉冲,长脉冲用于向负载电感充电,在长脉冲关断时可以观察带载情况被测器件的关断性能;在短脉冲开通时可以观察带载情况下器件的开通性能,以此测试被测器件的开关性能。

在测试本文所提出的功率模块时,功率模块内部集成分立驱动电阻为5.1 W,外部公共驱动电路电阻为2.0 W。进行双脉冲测试前,在电容直连结构上装配的解耦电容规格为1 000 V/2.64 mF(8个1 000 V/ 330 nF陶瓷电容并联)。基于所制作样机的功率等级进行了三组双脉冲测试,电压/电流等级分别为400 V/300 A、500 V/375 A、600 V/450 A。测试所得开关波形如图15b~图15d所示。

图15 碳化硅功率模块样机双脉冲测试结果波形

Fig.15 The waveforms of the double pulse test for the commutation loop in the SiC power module prototype

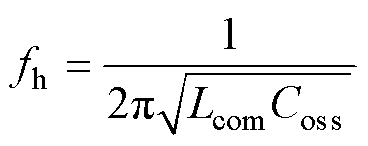

开通过程中,电流在稳定后发生高频振荡,在图15b中的400 V/300 A测试中,振荡频率fh= 43.9 MHz。这个振荡频率表示为

(10)

(10)

式中,Lcom为换流回路寄生电感;Coss为输出电容。

查阅碳化硅芯片手册可知,在测试电压400 V条件下,单芯片Coss约为280 pF,根据式(10)可计算得到换流回路总寄生电感Lcom=5.87 nH,为图15所测量功率回路电感Ls与集成解耦电容等效串联电感LC之和,与仿真及电感测试结果基本吻合。

在本文提出的整体式Clip碳化硅功率模块双脉冲测试的结果中,主要关注了功率模块的关断过程电压过冲。在400、500、600 V的测试条件,最大电流下降率均超过10 A/ns的极快开关速度下,电压过冲分别控制在20.8%、17.2%、15.3%。由于所提出的多芯片整体式Clip互连碳化硅模块与电容直连结构样机具有极低的换流回路寄生电感,在发挥碳化硅器件高开关速度的特性的同时,很大程度地抑制了开关过程中的电压过冲,在电路设计中更加充分地使用碳化硅器件的性能参数,减少降额造成的性能浪费。

本文提出了一种新型的多芯片整体式Clip互连多芯片碳化硅功率模块封装结构,实现了具有极低寄生电感的换流回路。通过在碳化硅功率模块引入整体式Clip互连结构,在同时完成所有并联芯片上表面互连的同时,构建出高于陶瓷基板的另一层线路布置空间,通过对陶瓷基板上的导电线路与一体式Clip的电流进行规划,使得功率模块内部Clip上的电流与陶瓷基板上的电流形成相反电流对,利用电流反向耦合效应形成的负互感减小了功率模块内部的寄生电感。此外,在功率模块端子外部提出电容直连结构,在功率引出端子处引出功率模块的临近区域布置解耦电容,消除外部回路中由引出端子、外部电路与母排电容的电感对换相过程造成的影响,大幅减小了换相回路的面积与寄生电感。

在仿真中,功率模块内部电感Lin降低至3.8 nH,功率回路的总电感Ls被控制在5 nH左右。实验测试结果显示,所制作的基于一体式Clip互连的1 200 V/600 A碳化硅功率模块样机功率回路电感Ls=4.53 nH,比传统布局的功率模块降低了44.6%,换相回路总寄生电感Lcom约为5.87 nH。所提出的功率模块封装结构具有极低的寄生电感与电压过冲,有利于减小碳化硅器件使用中的电压过冲与损耗,提高变换器的效率,并使器件工作在更接近额定值的工况,充分地发挥碳化硅器件的优异性能。

参考文献

[1] 王来利, 赵成, 张彤宇, 等. 碳化硅功率模块封装技术综述[J]. 电工技术学报, 2023, 38(18): 4947- 4962.

Wang Laili, Zhao Cheng, Zhang Tongyu, et al. Review of packaging technology for silicon carbide power modules[J]. Transactions of China Electro- technical Society, 2023, 38(18): 4947-4962.

[2] 盛况, 董泽政, 吴新科. 碳化硅功率器件封装关键技术综述及展望[J]. 中国电机工程学报, 2019, 39(19): 5576-5584, 5885.

Sheng Kuang, Dong Zezheng, Wu Xinke. Review and prospect of key packaging technologies for silicon carbide power devices[J]. Proceedings of the CSEE, 2019, 39(19): 5576-5584, 5885.

[3] 刘基业, 郑泽东, 李驰, 等. 电压自平衡碳化硅MOSFET间接串联功率模块[J]. 电工技术学报, 2023, 38(7): 1900-1909.

Liu Jiye, Zheng Zedong, Li Chi, et al. An indirect series-connected SiC MOSFET power module with voltage self-balance[J]. Transactions of China Elec- trotechnical Society, 2023, 38(7): 1900-1909.

[4] 张缙, 刘智, 刘意, 等. 基于智能算法的双面散热SiC功率模块多目标优化设计[J]. 电工技术学报, 2023, 38(20): 5515-5529.

Zhang Jin, Liu Zhi, Liu Yi, et al. Research on multi-objective optimization design of double-sided cooling SiC power module based on intelligent algorithm[J]. Transactions of China Electrotechnical Society, 2023, 38(20): 5515-5529.

[5] 王思媛, 梁钰茜, 孙鹏, 等. 基于3D封装的低感双向开关SiC功率模块研究[J]. 电源学报, 2024, 22(3): 87-92.

Wang Siyuan, Liang Yuxi, Sun Peng, et al. 3D packaging for low-inductance bidirectional switch of SiC power module[J]. Journal of Power Supply, 2024, 22(3): 87-92.

[6] 徐文凯, 朱俊杰, 聂子玲, 等. 全碳化硅功率模块开关瞬态特性及损耗研究[J]. 电机与控制应用, 2019, 46(5): 100-106, 119.

Xu Wenkai, Zhu Junjie, Nie Ziling, et al. Research on switching transient performance and loss of all silicon carbide power module[J]. Electric Machines & Control Application, 2019, 46(5): 100-106, 119.

[7] 张茂盛. 碳化硅功率模块高速开关及近场电磁特性研究[D]. 杭州: 浙江大学, 2021.

Zhang Maosheng. Studies on characteristics of fast switching and near-field electromagnetic emissions for silicon carbide power modules[D]. Hangzhou: Zhejiang University, 2021.

[8] (德)安德列亚斯·福尔克(Andreas Volke), (德)麦克尔·郝康普(Michael Hornkamp)著. 韩金刚译. IGBT模块: 技术、驱动和应用[M]. 北京: 机械工业出版社, 2016.

[9] Hou Fengze, Wang Wenbo, Cao Liqiang, et al. Review of packaging schemes for power module[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 223-238.

[10] Lee H, Smet V, Tummala R. A review of SiC power module packaging technologies: challenges, advances, and emerging issues[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 239-255.

[11] Luechinger C. Ribbon bonding-a scalable inter- connect for power QFN packages[C]//2007 9th Elec- tronics Packaging Technology Conference, Singapore, 2007: 47-54.

[12] 郑志强, 程秀兰, Frank Ta. 功率器件封装工艺中的铝条带键合技术[J]. 电子与封装, 2008, 8(11): 5-8, 11.

Zheng Zhiqiang, Cheng Xiulan, Frank Ta. Aluminum ribbon bonding technology in power device packaging[J]. Electronics & Packaging, 2008, 8(11): 5-8, 11.

[13] Xu Tao, Chen Raymond, Cionea C, et al. System considerations for large copper wire and ribbon bonding in mass production[C]//PCIM Europe 2022; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 2022: 497-505.

[14] Ling Jamin, Xu Tao, Chen R, et al. Cu and Al-Cu composite-material interconnects for power devices[C]// 2012 IEEE 62nd Electronic Components and Tech- nology Conference, San Diego, CA, USA, 2012: 1905-1911.

[15] Abdoulahad T, Emmanuel S, William S, et al. 3D-FE electro-thermo-magnetic modeling of automotive power electronic modules - wire-bonding and Copper clip technologies comparison[C]//2019 IEEE Inter- national Workshop on Integrated Power Packaging (IWIPP), Toulouse, France, 2019: 78-82.

[16] Li Kongjing, Wang Yangang, Morshed M. All-Cu- package (ACP) high-power GaN HEMT module platform for xEV traction inverter and high-speed DC charger[C]//PCIM Europe 2022; International Exhi- bition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 2022: 530-533.

[17] Zhang Xin, Gan Yongmei, Zhang Tongyu, et al. Dynamic current balancing optimization of Cu clip- bonded SiC power module based on layout-dominated parasitic inductance[C]//PCIM Asia 2024; Inter- national Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Shenzhen, China, 2024: 106-110.

[18] Zhu Qingwei, Forsyth A, Todd R, et al. Thermal characterisation of a copper-clip-bonded IGBT module with double-sided cooling[C]//2017 23rd International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Amsterdam, Nether- lands, 2017: 1-6.

[19] 廖林杰, 范益, 梅晓洋, 等. 基于铜夹互连的双芯片功率器件的热力机械性能研究[J]. 机车电传动, 2023(5): 101-106.

Liao Linjie, Fan Yi, Mei Xiaoyang, et al. Investi- gation of thermal-mechanical performance of dual- chip SiC power devices based on Cu clip inter- connection[J]. Electric Drive for Locomotives, 2023(5): 101-106.

[20] Zhang Chi, Huang Zhizhao, Chen Cai, et al. A 900A high power density and low inductive full SiC power module for high temperature applications based on 900V SiC MOSFETs[C]//2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 2020: 2777-2781.

[21] Watt G, Romero A, Burgos R, et al. Design of a compact, low inductance 1200 V, 6.5 mW SiC half- bridge power module with flexible PCB gate loop connection[C]//2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 2019: 2786-2793.

[22] Chen Hao, Wei Tiwei, Chen Yuxiang, et al. Feasibility design of tight integration of low inductance SiC power module with microchannel cooler[C]//2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 2022: 962-965.

[23] Hui Xiaoshuang, Ning Puqi, Fan Tao, et al. A novel multiple DBC-staked units package to parallel more chips for SiC power module[J]. CES Transactions on Electrical Machines and Systems, 2024, 8(1): 72-79.

[24] Chen Cai, Chen Yu, Li Yuxiong, et al. An SiC-based half-bridge module with an improved hybrid packaging method for high power density appli- cations[J]. IEEE Transactions on Industrial Elec- tronics, 2017, 64(11): 8980-8991.

[25] Infineon. FS05MR12A6MA1B[EB/OL]. [2022-09-01]. https://www.infineon.com/cms/cn/product/power/mosfet/ silicon-carbide/modules/fs05mr12a6ma1b/.

[26] Jakobi W, Uhlemann A, Thoben M, et al. Benefits of new CoolSiCTM MOSFET in HybridPACKTM Drive package for electrical drive train applications[C]// 10th International Conference on Integrated Power Electronics Systems, Stuttgart, Germany, 2018: 1-9.

[27] Sitta A, Mauromicale G, Giuffrida V, et al. Paralleling silicon carbide MOSFETs in power module for traction inverters: a parametric study[C]// 2021 22nd International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experi- ments in Microelectronics and Microsystems (EuroSimE), St. Julian, Malta, 2021: 1-5.

[28] Zhao Yushan, Deng Erping, Pan Maoyang, et al. Influence of thermal coupling on lifetime under power cycling test[J]. IEEE Transactions on Power Elec- tronics, 2022, 37(11): 13641-13651.

[29] Du Jiakun, Feng Yuxin, Chen Qian, et al. Tunnel magnetoresistance-based short-circuit protection for SiC MOSFET in HybridPACKTM drive package[C]// IECON 2022–48th Annual Conference of the IEEE Industrial Electronics Society, Brussels, Belgium, 2022: 1-5.

[30] Paul C R. Inductance: loop and partial[M]. Hoboken, New Jersey: John Wiley & Sons, Inc., 2010.

[31] IEC 60747-15, Semiconductor devices-discrete devices- part 15: isolated power semiconductor devices[S], Ed. 2.0, Geneva, Switzerland, 2010.

Multichip Integral Clip Bonding SiC Power Module Reverse Coupling Low Inductance Packaging Method

Abstract The silicon carbide (SiC) power device has emerged as a promising candidate for replacing the silicon power device in power converters. SiC exhibits extremely high blocking voltage, high switching speed, and low loss. However, when SiC devices are utilized as power modules, their performance is constrained by the packaging. The conventional aluminum (Al) wire bonding, power terminals, laminated busbars, and even film capacitors introduce unacceptable parasitic inductance into the commutation loop of the SiC power module, thereby resulting in high voltage overshoots, oscillations, and increased switching losses.Therefore, this paper proposes a low-inductance packaging method for multichip SiC power modules.

Firstly, a theoretical derivation of the parasitic inductance is presented, encompassing both the self- inductance and mutual inductance. The available space restricts the optimization of the self-inductance within the power module, as the size and number of the dies cannot be decreased. Moreover, the SiC MOSFETs require an additional conduction path to route the gate signal out of the power module, which also enlarges the size. Consequently, it is challenging to reduce the parasitic inductance without altering the packaging method of the power module. The optimized packaging method should place more emphasis on the mutual-inductance cancellation effect.

In this paper, the upper surface interconnection of the SiC MOSFET is substituted from Al wire bonding to Cu clip bonding. Cu clip bonding has a large cross-sectional area, enabling it to handle higher currents. More significantly, the integral Cu clip forms an additional layer for the arrangement of the circuit layout inside the power module. This extra layer provided by the integral Cu clip is co-designed with the layout of the ceramic substrate. The directions of the current flow on the Cu clip and the ceramic substrate are arranged to be opposite. The mutual inductance resulting from the opposite currents on the Cu clip and the ceramic substrate significantly reduces the parasitic inductance within the SiC power module. In the simulation, the parasitic inductance within the power module is decreased to 3.8 nH.

The switching performance of the SiC MOSFET is influenced by the parasitic inductance of the commutation loop, which includes the inductance within the power module and the inductance from the power terminal to the capacitor. The long path of the power terminal and the equivalent series inductance (ESL) of the film capacitor significantly increase the total inductance. To eliminate the influence of this part, this paper proposes a capacitor direct connection (CDC) structure. The CDC structure mounts decoupling capacitors close to the position where the terminals protrude from the power module. The main body of the CDC structure is directly connected to the power terminals using its lower surface. The capacitors are arranged on the upper surface. The electrical connections within the upper and lower surfaces of the CDC structure rely on a large number of vias. The parasitic inductance outside of the power module is decreased to 1.1 nH by using the CDC structure in simulation, resulting in a low-inductance power loop within 5 nH.

A 1 200 V/600 A prototype of the proposed power module has been constructed and tested. The experimental results demonstrate that the power loop inductance of the prototype SiC power module based on the integral Cu clip bonding is 4.53 nH, 44.6% lower than that of the conventional layout. The inductance of the commutation loop is measured as 5.87 nH. The proposed power module packaging method is conducive to reducing the voltage overshoot and loss when using silicon carbide devices, thereby improving the efficiency of the converter. It can also enable the SiC devices to operate closer to their rated conditions and fully utilize their excellent performance.

Keywords:SiC power module, parasitic inductance, integral Clip bonding, reverse coupling, commutation loop

中图分类号:TN305.94

DOI: 10.19595/j.cnki.1000-6753.tces.250153

国家自然科学基金国家杰出青年科学基金资助项目(52325705)。

收稿日期 2025-01-24

改稿日期 2025-04-23

张彤宇 男,1997年生,博士研究生,研究方向为碳化硅功率模块封装集成。

E-mail: zty598979175@stu.xjtu.edu.cn

王来利 男,1982年生,教授,博士生导师,研究方向为电力电子封装集成。

E-mail: llwang@mail.xjtu.edu.cn(通信作者)

(编辑 陈 诚)