(1)

(1)

摘要 为了提高SiC MOSFET的短路可靠性,在不同的母线电压、驱动电压、驱动电阻、主回路寄生电感以及栅极阈值电压参数下,对SiC MOSFET短路电流特性曲线进行测量,定量分析各个参数对短路电流的影响,为如何提高SiC MOSEFT的短路耐受时间提供解决思路。同时,由于SiC MOSFET的短路耐受时间决定着对其进行短路保护动作的最大时间,所以这些不同参数的设置直接影响着SiC MOSFET短路保护电路的设计。在传统SiC MOSFET短路保护策略中,利用开尔文源极与功率源极之间寄生电感产生的感应电压,配合RC滤波器进行短路保护,存在SiC MOSFET在硬开关短路和负载短路中,触发短路保护动作阈值不一致的问题,即导致短路保护失败。针对此问题,提出基于di/dt-PMOS的短路保护策略,保证了阈值的一致性。通过公式推导以及实验验证了基于di/dt-PMOS的SiC MOSFET短路保护策略的有效性。

关键词:SiC MOSFET 短路耐受时间 短路保护 开尔文源极 驱动电路

SiC MOSFET凭借其宽禁带、耐高温以及低开关损耗等诸多优点,在电力电子领域运用越来越广泛[1-6]。但由于SiC MOSFET高电流密度以及较小的芯片面积,造成SiC MOSFET短路耐受能力极差,严重阻碍了SiC MOSFET的应用[7-8]。SiC MOSFET短路类型主要分为两种:①硬开关短路(Hard Switching Fault, HSF);②负载短路(Fault Under Load, FUL)。以负载并联于上管的半桥电路为例,HSF为半桥电路中上管正常开通状态下,下管因故障突然开通,此时下管电流ids从0急剧上升至短路电流峰值,随着温度的升高,声子散射以及表面粗糙散射的增强,导致载流子迁移率降低[7],流过SiC MOSFET的电流减小,ids开始下降。下管的漏源电压vds始终为供电电压Vdc,但由于主回路寄生电感的存在,vds会在HSF开关时刻产生波动[8-10]。FUL与HSF则正好相反,其为下管正常导通状态下,上管突然开通,此时ids从正常工作电流ids(on)急剧上升,后因温度上升导致载流子迁移率下降,ids下降。vds从正常导通状态下的电压vds(on)上升至Vdc[11-13]。

相比IGBT,由于SiC MOSFET在短路期间更大的短路电流以及自身更小的芯片面积,造成其热应力较大,因而相应的短路耐受时间(Short Circuit Withstand Time, SCWT)更短,短路故障对SiC MOSFET威胁更大[14]。有研究表明,相同情况下IGBT的SCWT为10 ms,而SiC MOSFET仅为3 ms[15]。由于SiC MOSFET的SCWT主要与短路过程中产热大小有关,产热越大,SCWT越短,而产热的大小取决于短路过程中短路电流的大小,影响短路电流大小的因素主要有母线电压vdc、驱动电压vg、驱动电阻Rg、主回路寄生电感Ls、壳温Tc以及SiC MOSFET的栅极阈值电压vth。

在上述影响短路电流大小的各因素中,已有学者研究了部分因素。其中文献[16]利用Si基增强型MOSFET串接于SiC MOSFET源极,在导通电阻及开关损耗仅分别增加4.2%和13%情况下,短路耐受时间却增加了86%。然而Si MOSFETs的选择方法使得电路设计者在实际应用中,尤其是在大容量和高电流应用中难以实施。文献[17]从电感限制短路电流角度出发,改变封装结构,在SiC MOSFET短路期间切换至电感更大的路径,短路电流峰值降低了20.07%,短路过程中总发热量降低了30.04%,但该方法仅针对半桥模块,对于单管或并联模块并不适用。文献[18]从驱动电压角度出发,在SiC MOSFET短路过程中降低驱动电压,将SiC MOSFET的短路耐受时间提升至10 ms,但该方案在漏极和源极之间引入了额外的电阻和电容,影响了器件的开关性能。上述学者虽然提出了一些拓宽SiC MOSFET短路耐受时间的方法,但分析较局限,所以有必要对所有因素进行全面分析。分析各个因素影响程度大小,为如何拓宽SiC MOSFET的SCWT提供解决办法,并针对SiC MOSFET提出更快速、准确的短路保护策略。

SiC MOSFET的短路保护策略有很多,主要分为以下几大类。

(1)工业界运用最为广泛的为退饱和短路保护方案,其原理是在SiC MOSFET开通阶段,检测其vds大小作为是否发生短路的判据[19-20]。然而,退饱和短路保护方案为了避免受到dvds/dt造成的误触发,必须设置检测盲区。如Wolfspeed公司的PT62SCMD17的检测盲区时间为1 ms[21-22],检测盲区的存在致使该种方案无法做到短路保护的快速性,现市面成熟的退饱和短路保护方案芯片保护时间均在ms级。鉴于该缺点,Ouyang Wenyuan等利用SiC MOSFET开尔文源极与功率源极之间的寄生电感Lss在dids/dt产生的感应电压作为检测vds的前级条件,虽较好地避免了退饱和短路保护方案的缺陷[9],但此种策略应用范围较为受限,仅针对拥有开尔文引脚封装的SiC MOSFET。

(2)米勒平台的检测,由于在HSF时,SiC MOSFET开通过程中不存在米勒平台,即开通过程中驱动输入的电荷量更小,所以通过检测SiC MOSFET开通过程中的电荷量来判断米勒平台是否存在,进而判断是否发生HSF[23-24]。但此种方法无法判断FUL,同时由于电荷量差异较小,具体实现电路相当复杂,该种方法运用范围最窄。

(3)利用电流传感器直接监测SiC MOSFET的工作电流,当电流超过设置的保护阈值时,即可判断为发生短路。其中电流传感器最为常见的是PCB罗氏线圈[25-26]。然而,为了防止其他干扰,PCB罗氏线圈需要精心设计,并且PCB罗氏线圈的线圈匝数与测量带宽呈正相关,更多的匝数会严重影响其抗扰动性能,可能导致短路保护电路的误触发[23]。此外,PCB罗氏线圈的信号还原电路实现较为复杂,严重阻碍了该方法的应用。另外,独特的电流传感器为隧道磁阻(Tunnel Magnetoresistance, TMR),TMR的电阻随磁通密度变化而变化,所以可以通过使用环形TMR电流传感器来监测电流[27],但是这种方法仅局限于半桥或者全桥模块中,无法应用于单个的SiC MOSFET。

(4)di/dt检测方法,利用SiC MOSFET在正常开通过程和短路过程中,开尔文源极与功率源极之间Lss产生的感应电压vss的不同来判断短路事件的发生[28-29]。该方案对寄生电感引起的噪声特别敏感,所以通常会配合一组RC低通滤波电路使用(即di/dt-RC检测)[30],vss给低通滤波器中电容C充电,通过C的电压与所设的短路阈值电压相比较判断短路事件。但由于SiC MOSFET在正常工作时,C会放电,造成HSF和FUL在C的短路阈值电压不一致,即FUL触发短路保护动作时,短路电流会远大于HSF的短路电流,同时还需要为C设计繁琐的复位电路,这些缺陷严重限制了该种方案的推广使用。

受上述内容的启发,针对传统di/dt-RC存在的缺陷,本文提出一种基于di/dt-PMOS的SiC MOSFET短路保护策略,利用PMOS中寄生二极管的单向导电性,阻碍C在SiC MOSFET正常工作时放电,同时利用PMOS在栅极为负压时的导通特性,为电容进行复位操作,省去了繁琐的复位电路设计,降低了保护电路的复杂性。

本文首先对SiC MOSFET在不同的vdc、vg、Rg、Ls、Tc以及vth下短路电流特性进行测量和分析,为如何拓宽SCWT提供参考思路;其次对本文提出的di/dt-PMOS短路保护策略原理进行阐述,并对两种短路类型进行实测,对比di/dt-PMOS较传统di/dt- RC的优点;最后对全文进行总结。

影响SiC MOSFET短路电流特性因素主要包括vdc、vg、Rg、Tc、vth以及Ls。这些因素对短路电流特性影响程度存在差异,所以有必要对这些因素进行定量分析,以HSF为例,探究每个参数的变化率对ids影响程度大小。

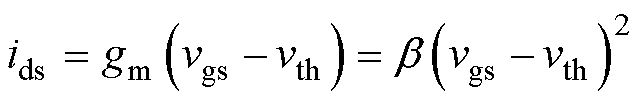

如果忽略了功率回路的寄生电感,vds近似等于总线电压,则电流变化过程可以近似为

(1)

(1)

式中,gm为SiC MOSFET的跨导,它与阈值电压vth和跨导系数 有关;vgs为SiC MOSFET栅源极电压。vth可表示为

有关;vgs为SiC MOSFET栅源极电压。vth可表示为

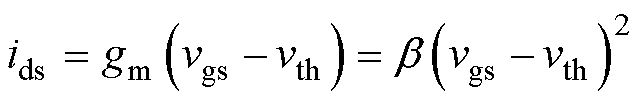

(2)

(2)

式中, 为介电常数;k为玻耳兹曼常数;T为开尔文温度;q为电子电荷;NA为掺杂浓度;ni为本征载流子浓度;Cox为氧化层电容;Qox为氧化层总有效电荷。vth主要由Qox、NA和Cox决定。其中Qox主要包括可移动离子电荷、氧化层陷阱电荷、固定氧化层电荷和界面态电荷。这些差异由阻挡氧化层厚度的Cox决定。

为介电常数;k为玻耳兹曼常数;T为开尔文温度;q为电子电荷;NA为掺杂浓度;ni为本征载流子浓度;Cox为氧化层电容;Qox为氧化层总有效电荷。vth主要由Qox、NA和Cox决定。其中Qox主要包括可移动离子电荷、氧化层陷阱电荷、固定氧化层电荷和界面态电荷。这些差异由阻挡氧化层厚度的Cox决定。

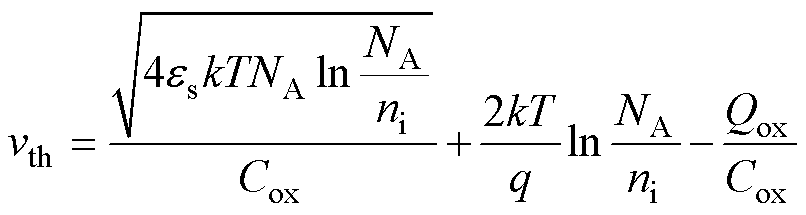

SiC MOSFET的vgs可表示为

(3)

(3)

式中,Ciss为输入电容。

SiC MOSFET的vgs还可表示为

(4)

(4)

尽管SiC MOSFET在不同短路故障下的短路特性存在差异,但短路特性分析方法较为相似,所以本文只对其中一种短路故障进行分析[7]。以HSF为例,本文选用Wolfspeed公司生产的型号为C3M0280090D(900 V/10.2 A)作为待测SiC MOSFET,其短路电流特性随不同参数的变化分析如下。

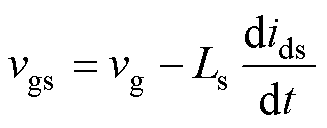

1)不同Ls下的SiC MOSFET短路电流特性

根据式(4)可知,Ls会影响SiC MOSFET的栅极电压大小,二者呈负相关。不同Ls对应的ids差异如图1所示。随着Ls的增加,ids峰值逐渐下降,其原因为电感对电流变化存在阻碍作用,较大的寄生电感会导致电流上升、时间延长,从而减小短路电流的峰值。另外寄生电感的增加,也会使其产生更大的感应电动势,该电动势的增加会降低器件漏源两端电压,进一步限制了电流峰值的增加。

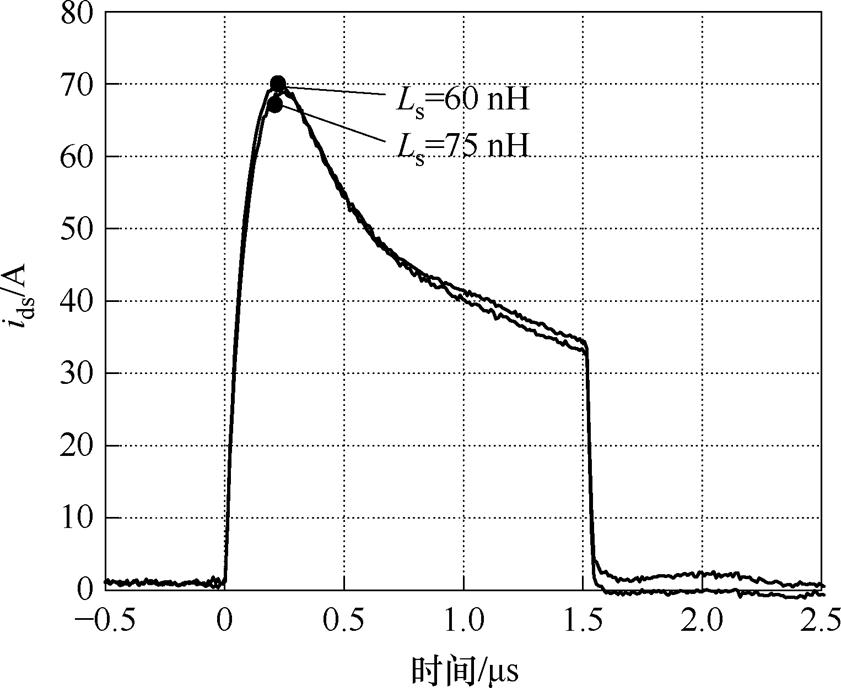

2)不同Rg下的SiC MOSFET短路电流特性

根据式(3)可知,Rg主要影响SiC MOSFET栅极电压vgs充放电速度,但由于该变量处于指数函数中,对vgs影响很小,所以根据式(1)可知ids几乎不受影响。不同Rg对应的ids差异如图2所示。随着Rg的增大,ids峰值会略微下降,其主要原因为Rg的增大会减小驱动电流,进而导致MOSFET的导通程度降低,阻碍ids的上升,但阻碍程度相当有限。

图1 不同Ls情况下ids差异(vg=20 V、vdc=600 V、Tc=25℃、vth=2.3 V、Rg=5 W)

Fig.1 Difference in ids under various Ls conditions (vg=20 V、vdc=600 V、Tc=25℃、vth=2.3 V、Rg=5 W)

图2 不同Rg情况下ids差异(vg=20 V、vdc=600 V、Tc=25℃、vth=2.3 V、Ls=60 nH)

Fig.2 Difference in ids under various Rg conditions (vg=20 V、vdc=600 V、Tc=25℃、vth=2.3 V、Ls=60 nH)

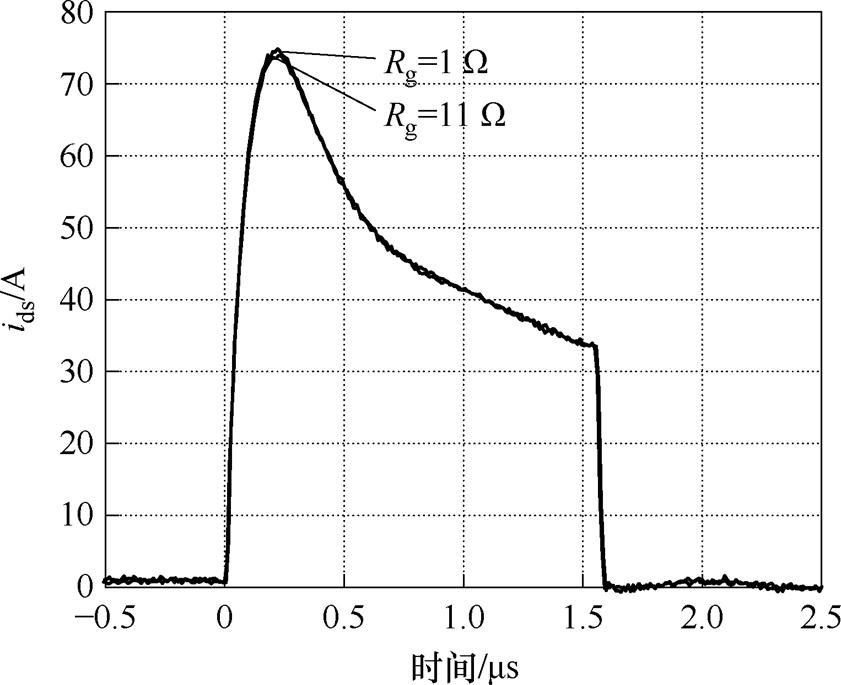

3)不同Tc下的SiC MOSFET短路电流特性

不同Tc对应的ids差异如图3所示。由图3可知,随着Tc的增加,ids峰值逐渐下降,这正是由于SiC MOSFET的导通电阻具有正温度特性,温度越高导通电阻越大,ids越小。

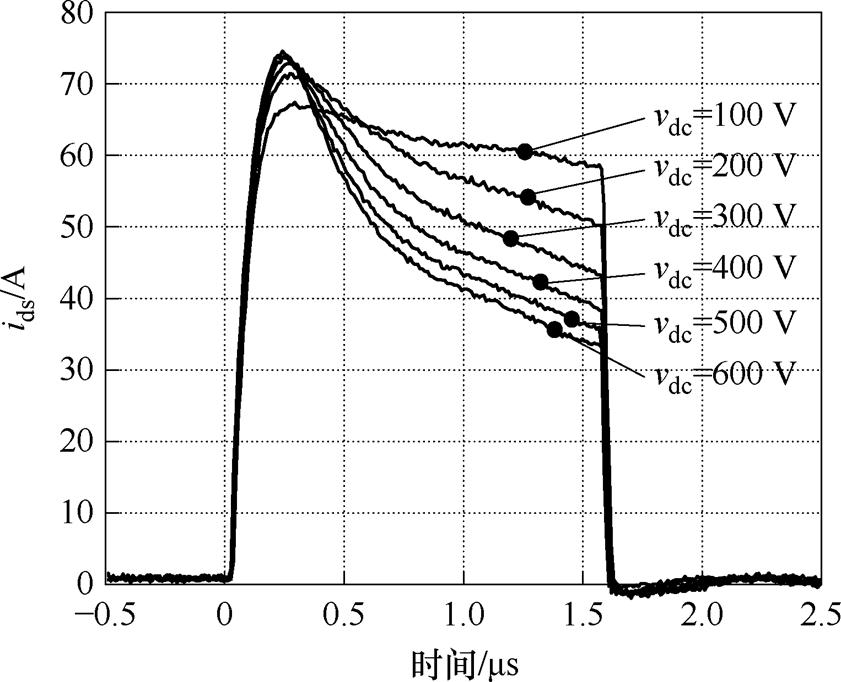

4)不同vdc下的SiC MOSFET短路电流特性

不同vdc对应的ids差异如图4所示。由图4可知,随着vdc的增加,ids峰值逐渐增加,这点很好理解,根据欧姆定律,电压越大,电流越大。

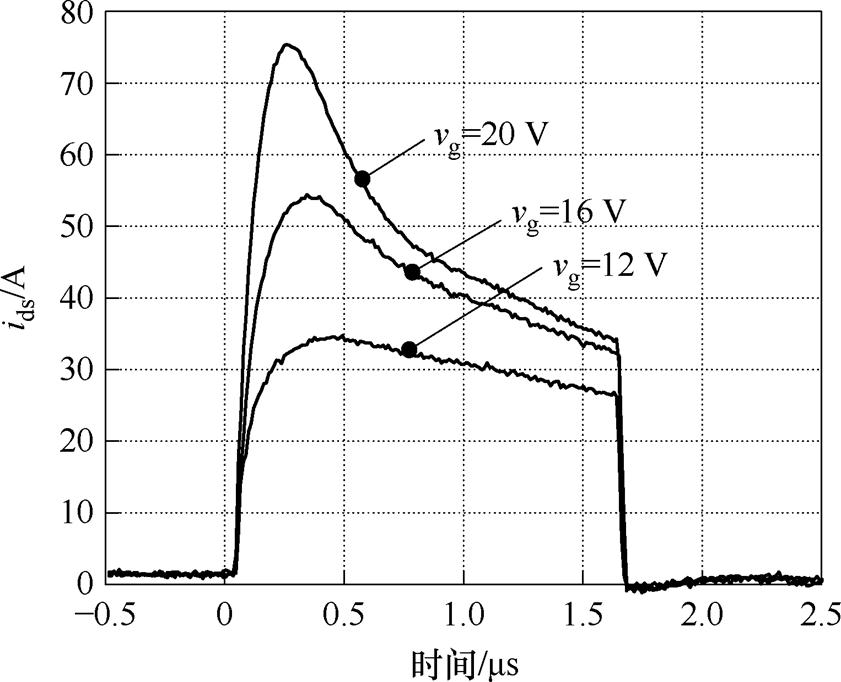

5)不同vg下的SiC MOSFET短路电流特性

同时根据式(1)和式(4)可知,ids与vg呈正相关性。不同vg对应的ids差异如图5所示,随着vg的增加,ids峰值逐渐增加。沟道宽度随着vg的增大而变宽,更宽的沟道意味着更小的导通电阻,从而允许更大的电流流过器件。

图3 不同Tc情况下ids差异(vg=20 V、vdc=600 V、Rg=5 W、vth=2.3 V、Ls=60 nH)

Fig.3 Difference in ids under various Tc conditions (vg=20 V、vdc=600 V、Rg=5 W、vth=2.3 V、Ls=60 nH)

图4 不同vdc情况下ids差异(vg=20 V、Tc=25℃、Rg=5 W、vth=2.3 V、Ls=60 nH)

Fig.4 Difference in ids under various vdc conditions (vg=20 V、Tc=25℃、Rg=5 W、vth=2.3 V、Ls=60 nH)

图5 不同vg情况下ids差异(vdc=600 V、Tc=25℃、Rg=5 W、vth=2.3 V、Ls=60 nH)

Fig.5 Difference in ids under various vg conditions (vdc=600 V、Tc=25℃、Rg=5 W、vth=2.3 V、Ls=60 nH)

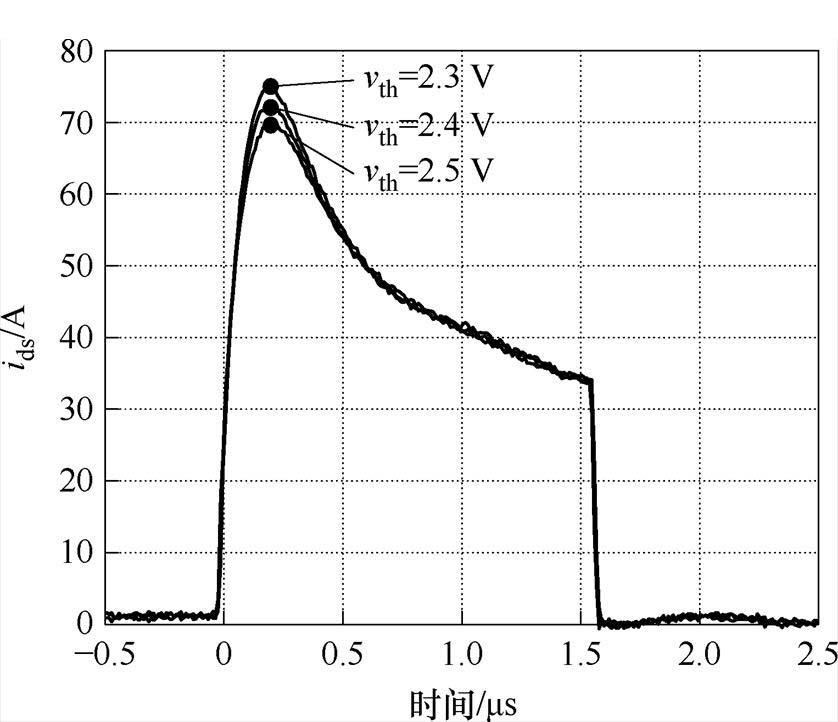

6)不同vth下的SiC MOSFET短路电流特性

选用同一型号但不同的vth的SiC MOSFET做对比,不同vth对应的ids差异如图6所示,定量层面解释见式(1),随着vth的增加,ids峰值逐渐减小。物理层面解释则为越高的vth意味着需要更高的vg才能使SiC MOSFET沟道打开,因此在相同的vg情况下,高的vth对应的SiC MOSFET沟道导通程度小于低的vth,即vth越大,ids峰值越小。

图6 不同vth情况下ids差异(vg=20 V、Tc=25℃、Rg=5 W、vdc=600 V、Ls=60 nH)

Fig.6 Difference in ids under various vth conditions (vg=20 V、Tc=25℃、Rg=5 W、vdc=600 V、Ls=60 nH)

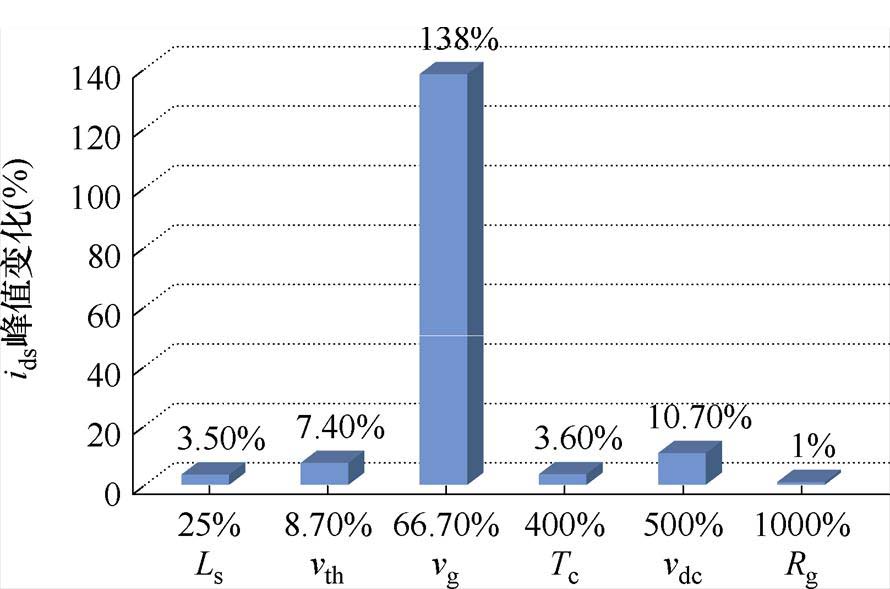

7)不同参数对ids影响程度大小

综上定量分析,各个参数变化量对ids峰值的影响程度如图7所示。从图7中可看出,在众多变量中,vg对SiC MOSFET短路电流影响程度最大,vg变化66.70%时,ids峰值变化138%,Rg影响最小;Rg变化1 000%时,ids峰值几乎无变化,这对如何增强SiC MOSFET的SCWT提供了解决思路,即在短路时减小vg,抑制ids的增大,进而增强SiC MOSFET的短路耐受时间。

图7 各参数变化量对ids峰值的影响程度

Fig.7 The impact of various parameters on the peak value of the ids

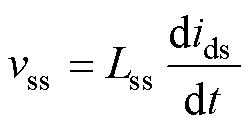

TO-247-4封装的SiC MOSFET由于引入了开尔文引脚,可以减小驱动回路的寄生电感,提高开关速度,减小栅极电压的波动,降低开关损耗。在开尔文源极与功率源极之间存在寄生电感Lss,该Lss在SiC MOSFET开通瞬态会产生相应的感应电压vss,传统基于di/dt-RC的短路保护策略正是利用了该感应电压来判断短路事件是否发生。

(5)

(5)

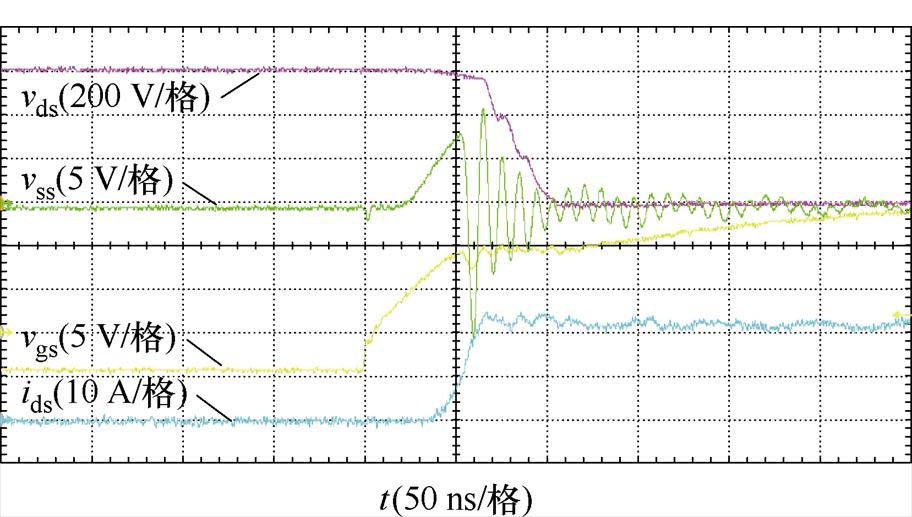

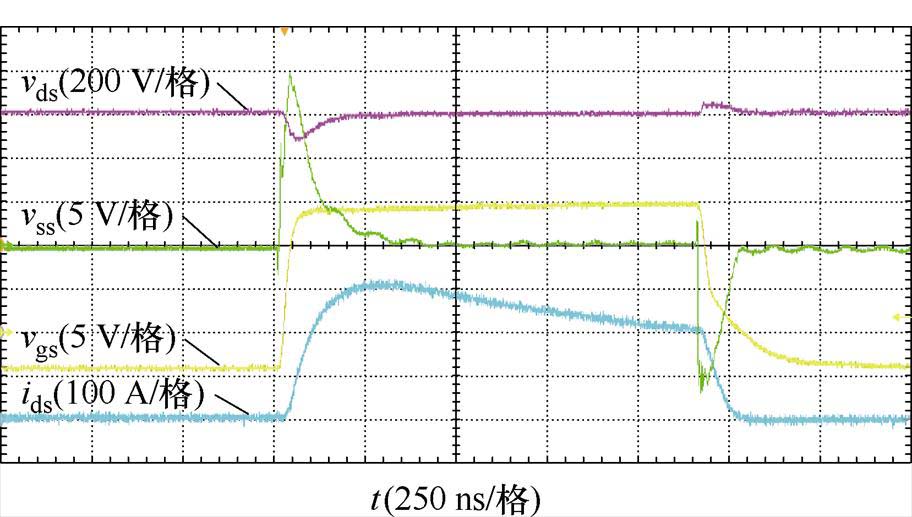

TO-247-4封装的SiC MOSFET正常开通状态波形、HSF波形以及FUL波形如图8~图10所示[9]。

图8 正常开通波形

Fig.8 The normal switching on waveforms

图9 HSF波形

Fig.9 The waveforms of HSF

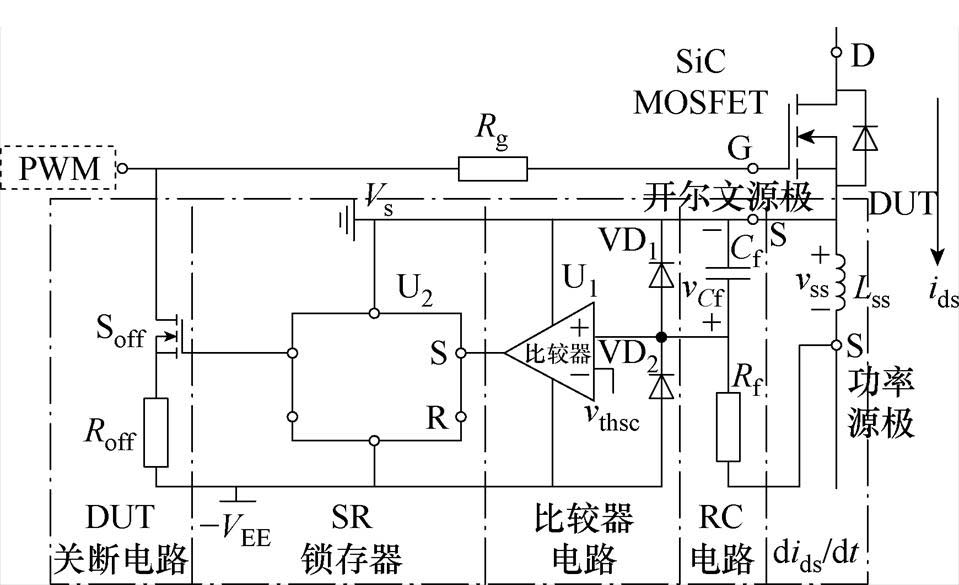

传统di/dt-RC短路保护策略电路如图11所示,主要包括待测器件(Device Under Test, DUT)、RC积分电路、比较器电路、SR锁存器电路以及DUT关断电路。

RC积分电路主要包括一个RC低通滤波器用于执行积分,目的是为了在短路故障期间,利用电容电压表征ids,由于SRfCf 1,所以此时高频传递函数可表示为

1,所以此时高频传递函数可表示为

图10 FUL波形

Fig.10 The waveforms of FUL

图11 传统di/dt-RC短路保护策略电路

Fig.11 Traditional di/dt-RC short-circuit protection circuit

(6)

(6)

式中,Rf、Cf、vCf(s)分别为阻值、容值、RC滤波器输出的电压。因而vCf(s)存储了ids(s)在短路状态中的值。当DUT发生短路时,vCf作为比较器电路的输入,与所设的短路阈值电压vthsc相比较,若vCf<vthsc,比较器输出相应的短路信号,该信号经SR锁存器电路锁存,控制Soff导通,PWM信号经Soff及Roff拉至-VEE,DUT关断,完成短路保护。

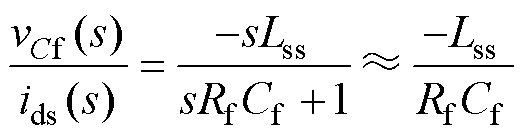

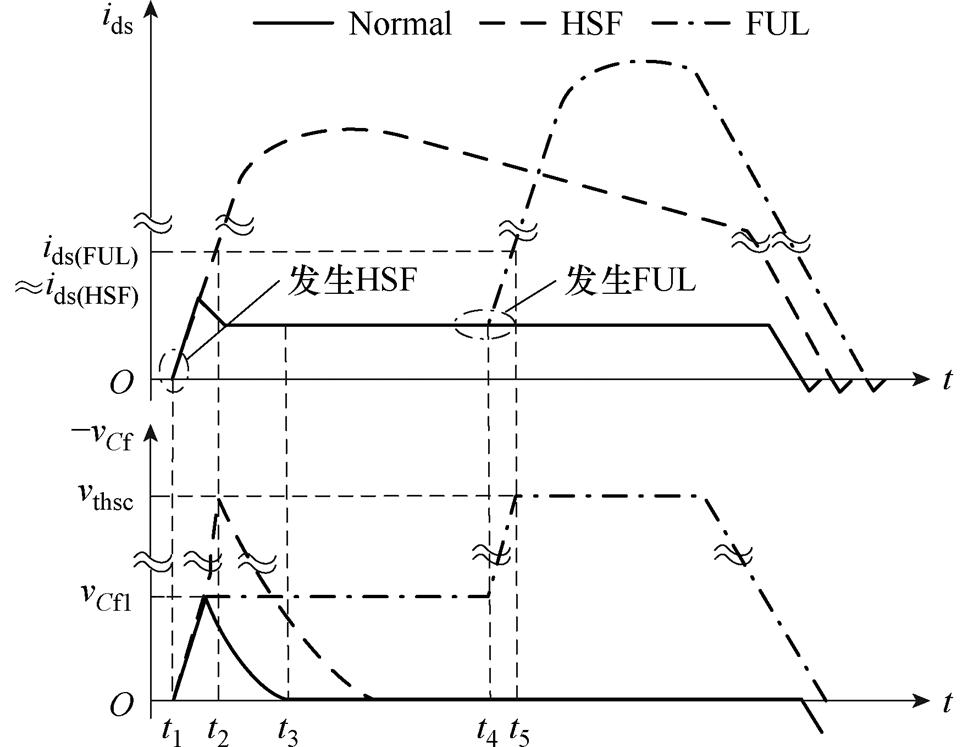

传统di/dt-RC理论波形如图12所示。传统di/dt-RC短路保护策略虽然可以将vss存储起来,并且根据vCf的大小推断出ids的值,但是该方法存在缺陷,即HSF和FUL两种状态下触发短路信号的阈值不一致。具体原因分析如下:

(1)HSF情况。t1:DUT发生HSF,ids急剧上升,巨大的dids/dt致使vCf急剧上升;t2:vCf=vthsc, ids=ids(HSF),比较器输出短路保护信号。

(2)FUL情况。t1:DUT正常开通,ids从0上升至正常工作电流ids(on),由于此时的dids/dt远小于短路状态,vCf虽急剧上升但峰值远未达到vthsc;t2:ids趋于平稳,Cf逐渐放电,vCf逐渐下降;t3:vCf下降至0;t4:发生FUL,ids从ids(on)急剧上升,vCf从0急剧上升;t5:vCf=vthsc, ids=ids(FUL),比较器输出短路保护信号。

图12 传统di/dt-RC理论波形

Fig.12 The theoretical waveforms of the traditional di/dt-RC protection strategy

从上述分析可知,由于DUT正常导通状态,Cf放电,致使FUL发生时,vCf从0上升至vthsc,造成ids(FUL)>ids(HSF)。

综上分析可知,传统di/dt-RC短路保护策略无法在HSF和FUL状态下,使得触发短路保护信号时ids(FUL)=ids(HSF),存在短路保护失效风险。针对该问题有两种解决办法:①针对HSF和FUL分别设置两个不同的短路保护阈值电压,即FUL的短路保护阈值电压要小于HSF状态时;②设计合理电路,阻碍Cf在正常工作状态下放电。设计两个不同的短路保护阈值意味着需要多个比较器及其配套的阈值电压电路,电路繁杂。所以本文所提出的di/dt-PMOS原理基于第②种方法。

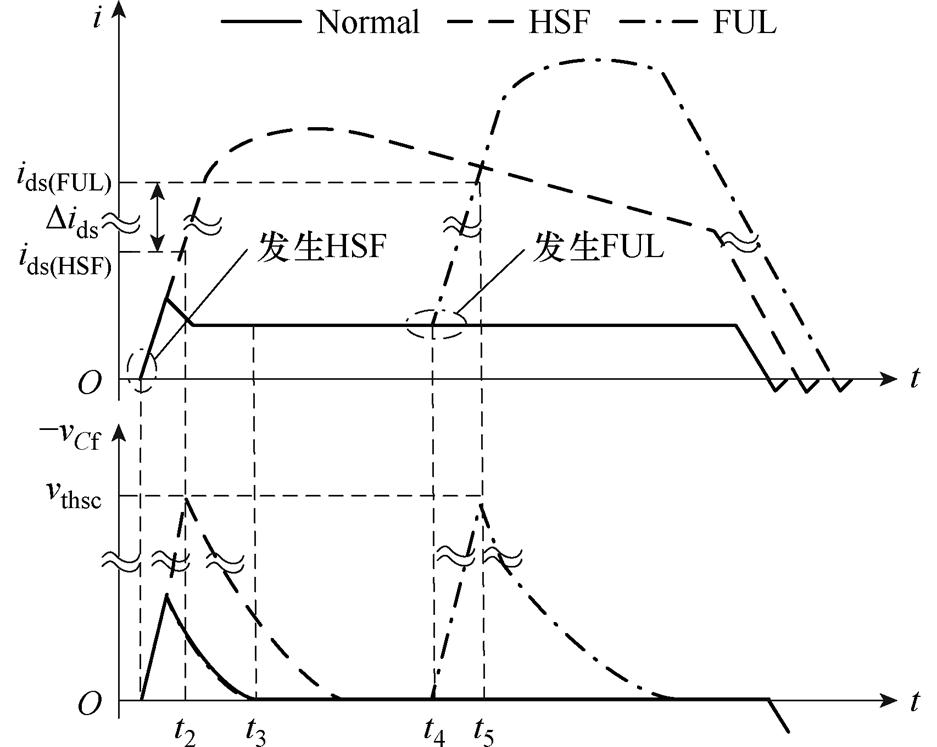

图13所示为本文所提出的di/dt-PMOS短路保护策略原理,其中主要包括DUT、RC积分电路、比较器电路、数字隔离、SR锁存电路以及DUT关断电路。其与传统di/dt-RC保护策略不同之处在于本策略在RC积分电路与Lss之间串联了一个PMOS器件Sp,利用PMOS中寄生二极管的单向导电性阻碍Cf的放电,并且在DUT处于关断状态时,DUT驱动为负压,PMOS导通对Cf进行放电复位。

本文所提出的di/dt-PMOS理论波形如图14所示。具体原理分析如下:

图13 di/dt-PMOS短路保护策略

Fig.13 The di/dt-PMOS short-circuit protection strategy

图14 di/dt-PMOS理论波形

Fig.14 The theoretical waveforms of the di/dt-PMOS

(1)HSF情况。t1:DUT发生HSF,ids急剧上升,巨大的dids/dt致使vCf急剧上升;t2:vCf=vthsc,ids=ids(HSF),比较器输出短路保护信号。

(2)FUL情况。t1:DUT正常开通,ids从0上升至正常工作电流ids(on),由于此时的dids/dt远小于短路状态,vCf虽急剧上升但峰值远未达到vthsc;t2:ids趋于平稳,由于PMOS管中寄生二极管的单向导电性Cf不放电,vCf=vCf1保持不变;t3:vCf保持不变;t4:发生FUL,ids从ids(on)急剧上升,vCf从vCf1急剧上升;t5:vCf=vthsc, ids=ids(FUL),比较器输出短路保护信号。

从上述分析可知,由于DUT正常导通状态,PMOS中寄生二极管阻碍了Cf放电,因而FUL发生时,vCf从vCf1上升至vthsc,使得ids(FUL)≈ids(HSF)。

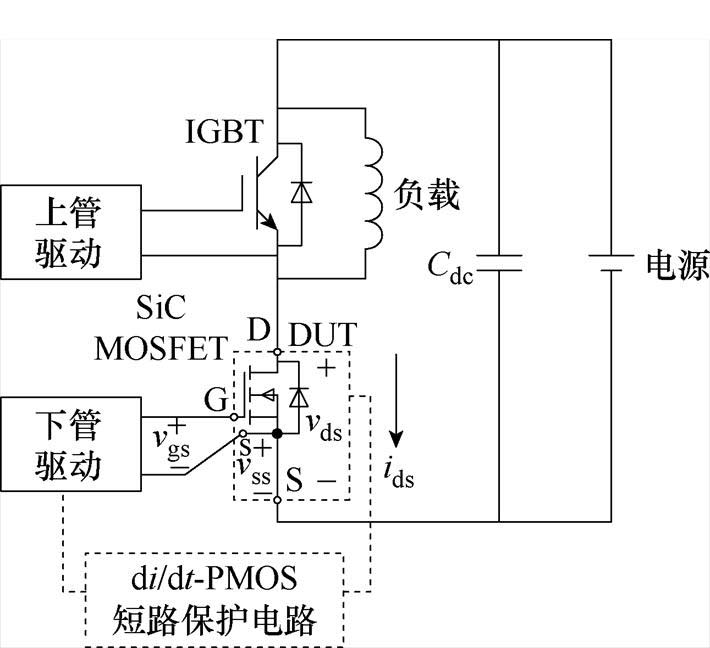

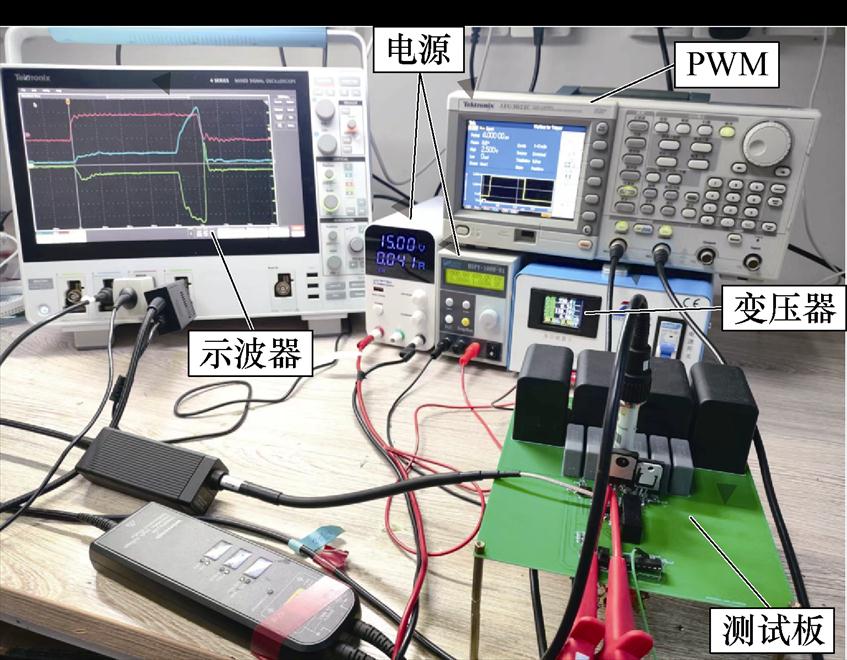

实验测试板结构框图如图15所示,为常见的半桥电路,Cdc为储能电容,下管为DUT,di/dt-PMOS保护策略作用于DUT上,为了保证安全且不影响DUT短路性能,上管选用额定电压及电流远大于DUT的IGBT。控制IGBT及DUT的开关时序即可模拟出HSF和FUL两种状态。测试平台如图16 所示。

图15 实验测试板结构框图

Fig.15 Experimental test board structure diagram

图16 测试平台

Fig.16 Test platform

本实验中各参数选择为Cf=470 pF,Rf=330 W,vthsc=-2 V。DUT选用Wolfspeed生产的型号为C3M0075120K(1 200 V/30 A),IGBT选用CRMICRO生产的型号为CRG40T120AK3S(1 200 V/80 A)。直流母线电压设置为600 V,SiC MOSFET初始结温设置为25℃。

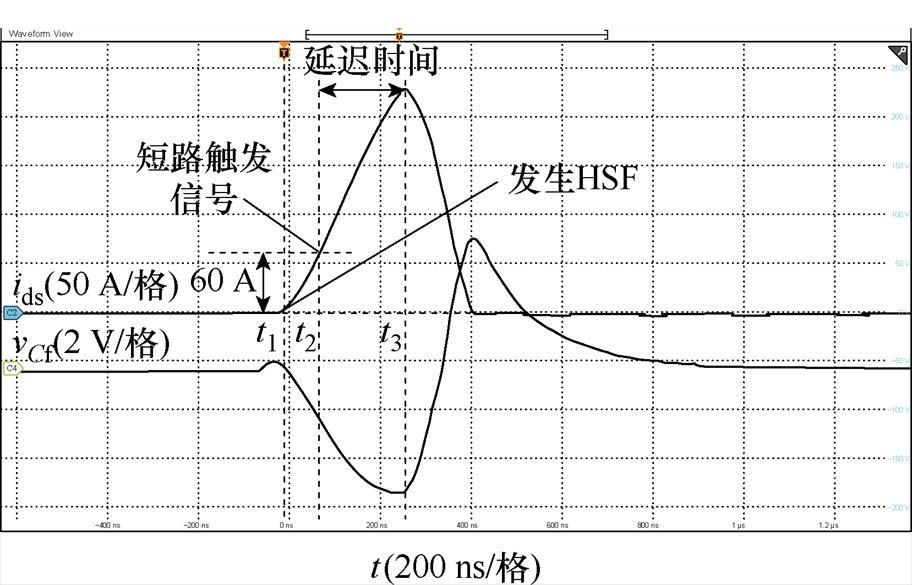

图17所示为传统di/dt-RC的HSF实测波形。t1时刻,发生HSF,ids急剧上升。t2时刻,vCf= -2 V,ids=55 A,此时比较器电路触发短路信号,该信号经数字隔离SR锁存电路以及DUT关断电路,造成一定的延时至t3时刻,DUT关断,短路保护完成。

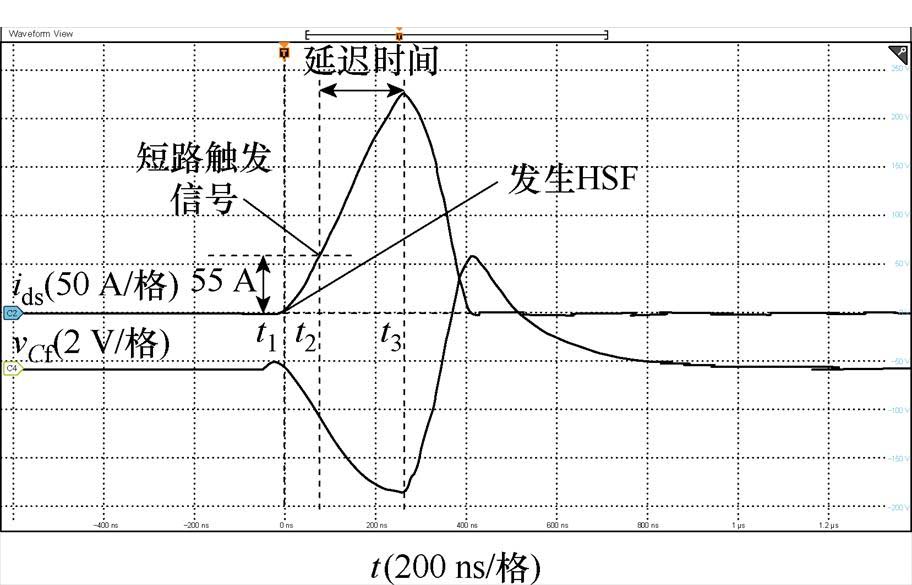

图18所示为di/dt-PMOS的HSF实测波形。当vCf=-2 V时,ids=60 A,保护过程与传统di/dt-RC一致。

图17 传统di/dt-RC的HSF实测波形

Fig.17 Traditional di/dt-RC HSF measured waveforms

图18 di/dt-PMOS的HSF实测波形

Fig.18 Measured waveforms of HSF for di/dt-PMOS

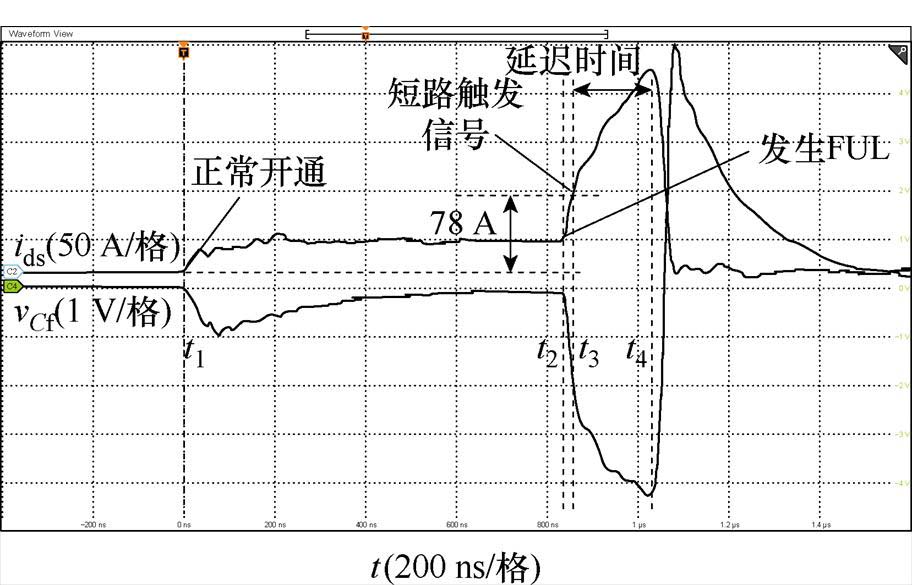

图19所示为传统di/dt-RC的FUL实测波形。t1时刻,DUT正常导通,ids从0上升至ids(on),vss给Cf充电,vCf从0下降为一定负值。经过很短时间后ids稳定于ids(on),vss=0,Cf放电,vCf逐渐趋于0。t2时刻发生FUL,ids从ids(on)急剧上升,vCf从0急剧下降。t3时刻,当vCf=-2 V时,ids=78 A,信号经数字隔离SR锁存电路以及DUT关断电路,造成一定的延时至t4时刻,DUT关断,短路保护完成。

图19 传统di/dt-RC的FUL实测波形

Fig.19 Traditional di/dt-RC FUL measured waveforms

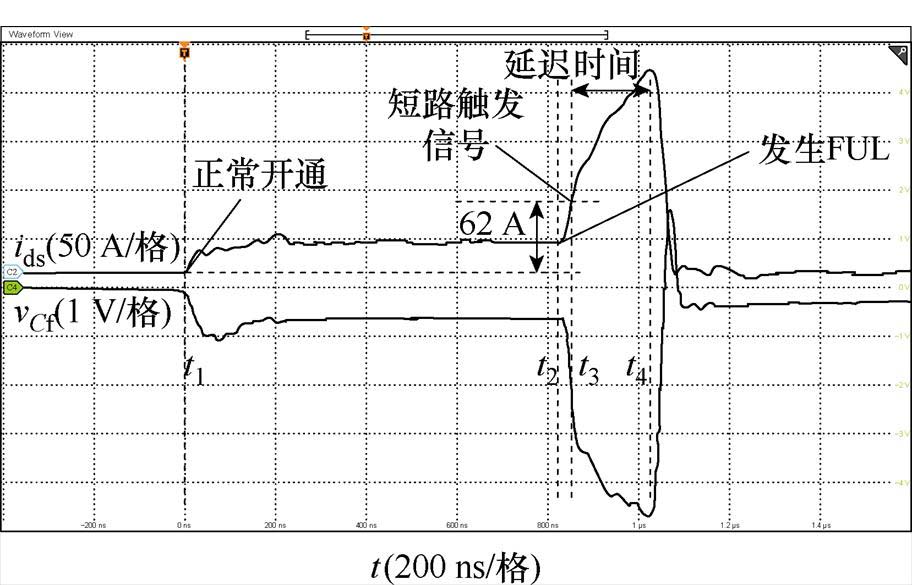

图20所示为di/dt-PMOS的FUL实测波形。t1时刻,DUT正常开通,ids从0上升至ids(on),vss给Cf充电,vCf从0下降为一定负值,但由于PMOS中寄生二极管的单向导电性,阻碍Cf放电,vCf保持不变。t2时刻,发生FUL,ids从ids(on)急剧上升,vCf急剧下降。t3时刻,vCf=-2 V时,ids=62 A。信号经数字隔离SR锁存电路以及DUT关断电路,造成一定的延时至t4时刻,DUT关断,短路保护完成。

图20 di/dt-PMOS的FUL实测波形

Fig.20 Measured waveforms of FUL for di/dt-PMOS

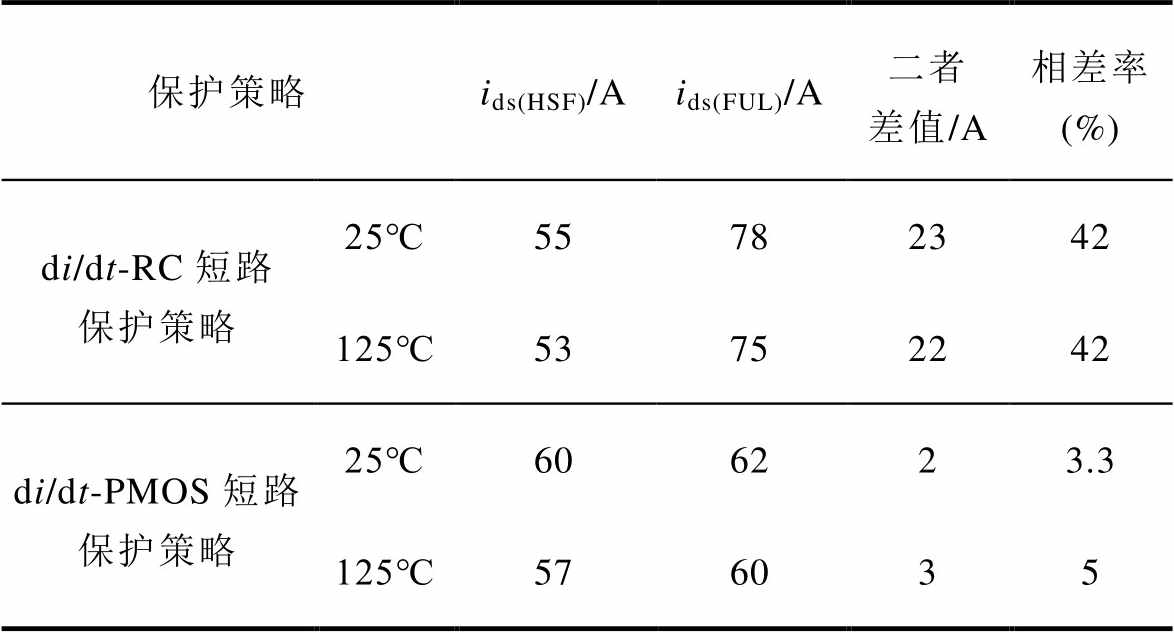

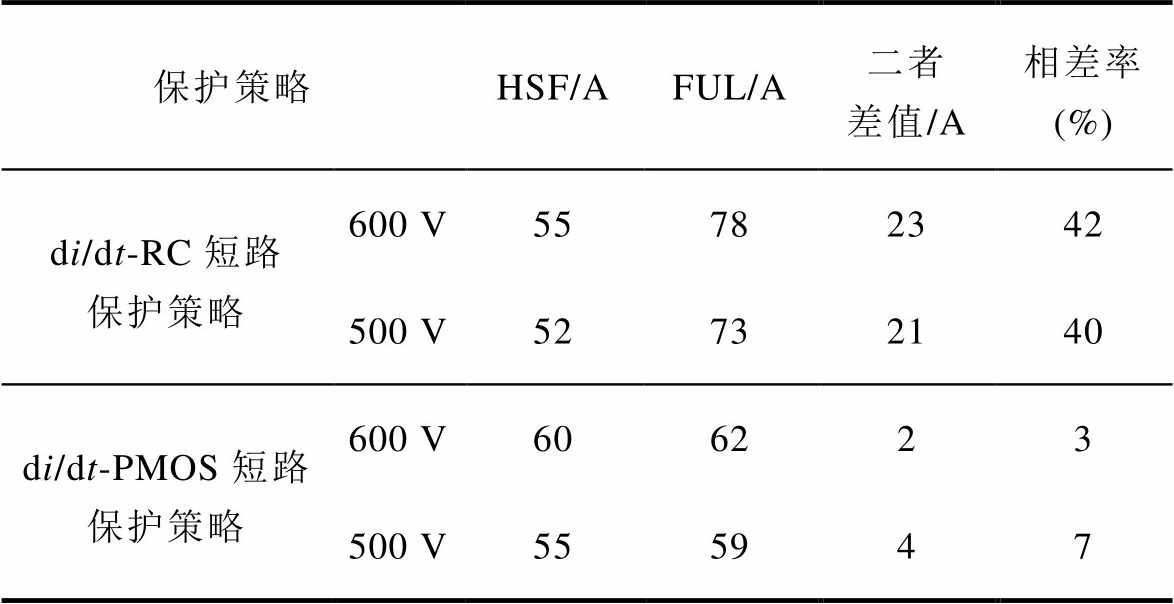

由上述实测结果分析可知,在直流母线电压为600 V,初始结温为25℃情况下,传统di/dt-RC短路保护策略中,HSF和FUL二者值相差23 A,相差率达42%,而本文提出的di/dt-PMOS短路保护策略在相同情况下,HSF和FUL二者差值仅为2 A,相差率也仅为3.3%。由于器件的导通及静态特性均受结温影响,考虑本文所提策略的普适性,将SiC MOSFET初始结温加热至125℃并再次进行实验,结果显示di/dt-RC保护策略相差率为42%,di/dt- PMOS保护策略为5%。对比可知,初始结温对di/dt- PMOS保护策略影响可忽略不计。不同初始结温下两种保护策略数据对比见表1。

表1 不同初始结温下两种保护策略数据对比

Tab.1 Data comparison of two protection strategies under different initial junction temperatures

保护策略ids(HSF)/Aids(FUL)/A二者差值/A相差率(%) di/dt-RC短路保护策略25℃55782342 125℃53752242 di/dt-PMOS短路保护策略25℃606223.3 125℃576035

初始结温设置为25℃,直流母线电压设置为500 V并再次进行实验,结果显示di/dt-RC保护策略相差率为40%,di/dt-PMOS保护策略为7%。对比可知,di/dt-PMOS短路保护策略性能远胜于传统di/dt-RC短路保护策略,且普适性强。不同直流母线电压下两种保护策略数据对比见表2。

表2 不同直流母线电压下两种保护策略数据对比

Tab.2 Data comparison of two protection strategies under different DC bus voltages

保护策略HSF/AFUL/A二者差值/A相差率(%) di/dt-RC短路保护策略600 V55782342 500 V52732140 di/dt-PMOS短路保护策略600 V606223 500 V555947

在极端HSF状况下,vss最大不超过10 V,Cf充放电峰值电流不超过30 mA,绝大多数PMOS都能承受这个量级的电压和电流。且在正常开关状态下vss更远小于10 V,对PMOS的危害可忽略不计。

本文首先研究了SiC MOSFET在不同vth、Rg、Tc、vg、Ls以及vdc参数下的短路电流特性,并通过实测定量分析了各个变量对ids的影响,这对如何提高SiC MOSFET的SCWT有着至关重要的参考作用;然后对SiC MOSFET传统di/dt-RC短路保护策略存在的问题进行了分析,针对该问题提出两种相应的解决思路;最后就其中一种解决思路创造性地提出了基于di/dt-PMOS的SiC MOSFET短路保护策略,利用PMOS管内寄生的二极管完美地解决传统di/dt-RC短路保护策略存在的问题,但di/dt- PMOS适用范围仅限于开尔文封装的SiC MOSFET。本文中所有实验表明:

1)诸多参数会影响SiC MOSFET的短路电流特性,其中vdc、vg与SiC MOSFET短路的ids峰值呈正相关,尤其vg对ids峰值的影响最大。因而在一些扩宽SiC MOSFET的SCWT策略中,常常使用在检测到短路发生后,降低vg的方案来抑制短路ids的上升,尽可能地增强SiC MOSFET短路耐受能力。

2)其余Ls、vth、Tc、Rg参数与SiC MOSFET短路ids峰值呈负相关,其中Rg的影响最小,几乎可以忽略不计。

3)基于di/dt-PMOS的SiC MOSFET短路保护策略可有效解决传统di/dt-RC存在的在HSF和FUL状态下不同短路保护阈值的问题。

参考文献

[1] 邹铭锐, 曾正, 孙鹏, 等. 基于变电阻驱动的SiC器件开关轨迹协同调控[J]. 电工技术学报, 2023, 38(16): 4286-4300.

Zou Mingrui, Zeng Zheng, Sun Peng, et al. Coordinated switching trajectory regulation of SiC device using variable resistance gate driver[J]. Transactions of China Electrotechnical Society, 2023, 38(16): 4286-4300.

[2] 王旭东, 朱义诚, 赵争鸣, 等. 驱动回路参数对碳化硅MOSFET开关瞬态过程的影响[J]. 电工技术学报, 2017, 32(13): 23-30.

Wang Xudong, Zhu Yicheng, Zhao Zhengming, et al. Impact of gate-loop parameters on the switching behavior of SiC MOSFETs[J]. Transactions of China Electrotechnical Society, 2017, 32(13): 23-30.

[3] 谭亚雄, 张梦洋, 刘元, 等. 一种连续函数描述的高精度SiC MOSFET模型[J]. 电工技术学报, 2024, 39(18): 5719-5731.

Tan Yaxiong, Zhang Mengyang, Liu Yuan, et al. A high-precision SiC MOSFET model described by continuous function[J]. Transactions of China Elec- trotechnical Society, 2024, 39(18): 5719-5731.

[4] 吴海富, 张建忠, 赵进, 等. SiC MOSFET短路检测与保护研究综述[J]. 电工技术学报, 2019, 34(21): 4519-4528.

Wu Haifu, Zhang Jianzhong, Zhao Jin, et al. Review of short-circuit detection and protection of silicon carbide MOSFETs[J]. Transactions of China Elec- trotechnical Society, 2019, 34(21): 4519-4528.

[5] Yang Yuan, Wen Yang, Gao Yong. A novel active gate driver for improving switching performance of high-power SiC MOSFET modules[J]. IEEE Transa- ctions on Power Electronics, 2019, 34(8): 7775-7787.

[6] 邵伟华, 冉立, 曾正, 等. SiC MOSFET短路特性评估及其温度依赖性模型[J]. 中国电机工程学报, 2018, 38(7): 2121-2131, 2227.

Shao Weihua, Ran Li, Zeng Zheng, et al. Short-circuit evaluation and temperature-dependent model of SiC MOSFET[J]. Proceedings of the CSEE, 2018, 38(7): 2121-2131, 2227.

[7] 康建龙, 辛振, 陈建良, 等. SiC MOSFET短路失效与退化机理研究综述及展望[J]. 中国电机工程学报,

2021, 41(3): 1069-1083.

Kang Jianlong, Xin Zhen, Chen Jianliang, et al. Review and prospect of short-circuit failure and degradation mechanism of SiC MOSFET[J]. Pro- ceedings of the CSEE, 2021, 41(3): 1069-1083.

[8] Boige F, Trémouilles D, Richardeau F. Physical origin of the gate current surge during short-circuit operation of SiC MOSFET[J]. IEEE Electron Device Letters, 2019, 40(5): 666-669.

[9] Ouyang Wenyuan, Sun Pengju, Xie Minghang, et al. A fast short-circuit protection method for SiC MOSFET based on indirect power dissipation level[J]. IEEE Transactions on Power Electronics, 2022, 37(8): 8825-8829.

[10] Wen Yang, Yang Yuan, Gao Yong. Active gate driver for improving current sharing performance of paralleled high-power SiC MOSFET modules[J]. IEEE Transactions on Power Electronics, 2021, 36(2): 1491-1505.

[11] An Junjie, Namai M, Yano H, et al. Investigation of robustness capability of -730 V P-channel vertical SiC power MOSFET for complementary inverter applications[J]. IEEE Transactions on Electron Devices, 2017, 64(10): 4219-4225.

[12] Nguyen T T, Ahmed A, Thang T V, et al. Gate oxide reliability issues of SiC MOSFETs under short-circuit operation[J]. IEEE Transactions on Power Electronics, 2015, 30(5): 2445-2455.

[13] Romano G, Fayyaz A, Riccio M, et al. A com- prehensive study of short-circuit ruggedness of silicon carbide power MOSFETs[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2016, 4(3): 978-987.

[14] 李腾, 辛振, 石亚飞, 等. 用于SiC MOSFET短路保护的平面型差分罗氏线圈建模与设计方法[J]. 电源学报, 2025, 23(1): 219-228.

Li Teng, Xin Zhen, Shi Yafei, et al. Modeling and designing method for planar differential rogowski coil for SiC MOSFET short-circuit protection[J]. Journal of Power Supply, 2025, 23(1): 219-228.

[15] Wang Heng, Zhao Jia, Zheng Ziqing, et al. Driving a silicon carbide power MOSFET with a fast short circuit protection[C]//2018 1st Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Xi’an, China, 2018: 260-265.

[16] Kanale A, Baliga B J. A new user-configurable method to improve short-circuit ruggedness of 1.2-kV SiC power MOSFETs[J]. IEEE Transactions on Power Electronics, 2021, 36(2): 2059-2067.

[17] 罗皓泽, 高洪艺, 朱安康, 等. 基于换流-短路双回路解耦的SiC MOSFET功率器件抗短路封装构型设计[J]. 中国电机工程学报, 2023, 43(7): 2781-2790.

Luo Haoze, Gao Hongyi, Zhu Ankang, et al. Anti- short-circuit packaging structure of SiC MOSFET power device with commutation-short circuit path decoupling[J]. Proceedings of the CSEE, 2023, 43(7): 2781-2790.

[18] Ouyang Wenyuan, Sun Pengju, Xie Minghang, et al. A gate voltage clamping method to improve the short-circuit characteristic of SiC MOSFET[C]//2023 IEEE 2nd International Power Electronics and Application Symposium (PEAS), Guangzhou, China, 2023: 287-292.

[19] 胡亮灯, 孙驰, 陈玉林, 等. 大功率IGBT的短路故障检测[J]. 电工技术学报, 2018, 33(11): 2592-2603.

Hu Liangdeng, Sun Chi, Chen Yulin, et al. Short- circuit fault detection for high-power IGBT[J]. Transactions of China Electrotechnical Society, 2018, 33(11): 2592-2603.

[20] Zhang Xuan, Li He, Brothers J A, et al. A gate drive with power over fiber-based isolated power supply and comprehensive protection functions for 15-kV SiC MOSFET[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2016, 4(3): 946-955.

[21] Ji Shiqi, Laitinen M, Huang Xingxuan, et al. Short-circuit characterization and protection of 10-kV SiC mosfet[J]. IEEE Transactions on Power Elec- tronics, 2019, 34(2): 1755-1764.

[22] 文阳, 杨媛, 宁红英, 等. SiC MOSFET短路保护技术综述[J]. 电工技术学报, 2022, 37(10): 2538-2548.

Wen Yang, Yang Yuan, Ning Hongying, et al. Review on short-circuit protection technology of SiC MOSFET[J]. Transactions of China Electrotechnical Society, 2022, 37(10): 2538-2548.

[23] Wang Jun, Mocevic S, Burgos R, et al. High- scalability enhanced gate drivers for SiC MOSFET modules with transient immunity beyond 100 V/ns[J]. IEEE Transactions on Power Electronics, 2020, 35(10): 10180-10199.

[24] Li Xinchang, Xu Dawei, Zhu Hongyue, et al. Indirect IGBT over-current detection technique via gate voltage monitoring and analysis[J]. IEEE Transa- ctions on Power Electronics, 2019, 34(4): 3615-3622.

[25] Wang Jun, Shen Zhiyu, Burgos R, et al. Integrated switch current sensor for shortcircuit protection and current control of 1.7-kV SiC MOSFET modules[C]// 2016 IEEE Energy Conversion Congress and Expo- sition (ECCE), Milwaukee, WI, USA, 2016: 1-7.

[26] 张经纬, 李晓辉, 谭国俊. 基于PCB罗氏线圈的SiC MOSFET短路保护研究[J]. 电力电子技术, 2017, 51(8): 26-29.

Zhang Jingwei, Li Xiaohui, Tan Guojun. The PCB rogowski coil based on short-circuit protection of SiC MOSFET[J]. Power Electronics, 2017, 51(8): 26-29.

[27] Shao Shuai, Yu Naipeng, Xu Xiaopeng, et al. Tunnel magnetoresistance-based short-circuit and over- current protection for IGBT module[J]. IEEE Transa- ctions on Power Electronics, 2020, 35(10): 10930- 10944.

[28] 杨媛, 文阳. 大功率IGBT驱动与保护技术[M]. 北京: 科学出版社, 2018.

[29] Maerz A, Bertelshofer T, Horff R, et al. Requirements of short-circuit detection methods and turn-off for wide band gap semiconductors[C]//9th International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 2016: 1-6.

[30] Wang Zhiqiang, Shi Xiaojie, Xue Yang, et al. Design and performance evaluation of overcurrent protection schemes for silicon carbide (SiC) power MOSFETs[C]// 2013 IEEE Energy Conversion Congress and Expo- sition, Denver, CO, USA, 2013: 5418-5425.

Analysis of Short-Circuit Withstand Time of SiC MOSFET and Short-Circuit Protection Based on di/dt-PMOS

Abstract The short-circuit tolerance of SiC MOSFETs is directly related to the heat generated during the short-circuit process, which is, in turn, directly related to the short-circuit current. Measuring short-circuit current characteristic curves under various parameters, including bus voltage, drive voltage, drive resistance, main circuit parasitic inductance, and gate threshold voltage, is essential. The impact of each parameter on the short-circuit current is analyzed to provide solutions for increasing the short-circuit withstand time (SCWT) of SiC MOSFETs. The drive voltage significantly influence the short-circuit current among these parameters, and lower gate voltage reduces the short-circuit current. Reducing the drive voltage can increase the SCWT of SiC MOSFETs. Additionally, the SCWT of SiC MOSFETs determines the maximum time for short-circuit protection actions. As a result, the settings of these different parameters directly affect the design of SiC MOSFET short-circuit protection circuits.

In traditional SiC MOSFET short-circuit protection strategies, the induced voltage generated by the parasitic inductance between the Kelvin source and power source, in conjunction with an RC filter, charges the capacitor (C) when the SiC MOSFET current changes, providing real-time feedback on the magnitude of the short-circuit current through the voltage across C. When the voltage across C exceeds a set value, the state of the SiC MOSFET is regarded as a short circuit. However, this traditional method has inconsistent short-circuit current thresholds for triggering short-circuit protection actions in hard switching faults (HSF) and fault under load (FUL), leading to the failure of short-circuit protection. Capacitor discharge is the main reason when the SiC MOSFET is normally turned on, resulting in a high short-circuit current threshold in the FUL state compared to the HSF state. Therefore, this paper proposes a short-circuit protection strategy based on di/dt-PMOS. This strategy places the PMOS's drain and source in series between the parasitic inductance and C. The unidirectional conductivity of the parasitic diode in the PMOS prevents the discharge of C when the SiC MOSFET is normally turned on, and the gate of the PMOS connecting to the SiC MOSFET's gate drive resets the discharge of C when the SiC MOSFET is turned off. It avoids complex discharge reset circuits for C and ensures the consistency of the short-circuit protection current threshold in both HSF and FUL states.

Practical measurements were conducted under different bus voltages and various initial junction temperatures. The proposed short-circuit protection strategy shows a minimum difference rate of only 3% in short circuits, while the traditional protection strategy exhibits a difference rate of 42%. The results demonstrate the effectiveness of the di/dt-PMOS-based short-circuit protection strategy for SiC MOSFETs.

Keywords:SiC MOSFET, short-circuit withstand time, short-circuit protection, Kelvin source, gate driver circuit

中图分类号:TM46

DOI: 10.19595/j.cnki.1000-6753.tces.241527

国家自然科学基金资助项目(52107179)。

收稿日期 2024-08-30

改稿日期 2024-11-22

谢佳明 男,1995年生,博士研究生,研究方向为第三代功率半导体器件的封装、驱动及其短路保护。

E-mail: xjm_phd@cqu.edu.cn

丰 昊 男,1991年生,副教授,博士生导师,研究方向为宽禁带功率半导体器件及应用。

E-mail: hfeng6@cqu.edu.cn(通信作者)

(编辑 陈 诚)