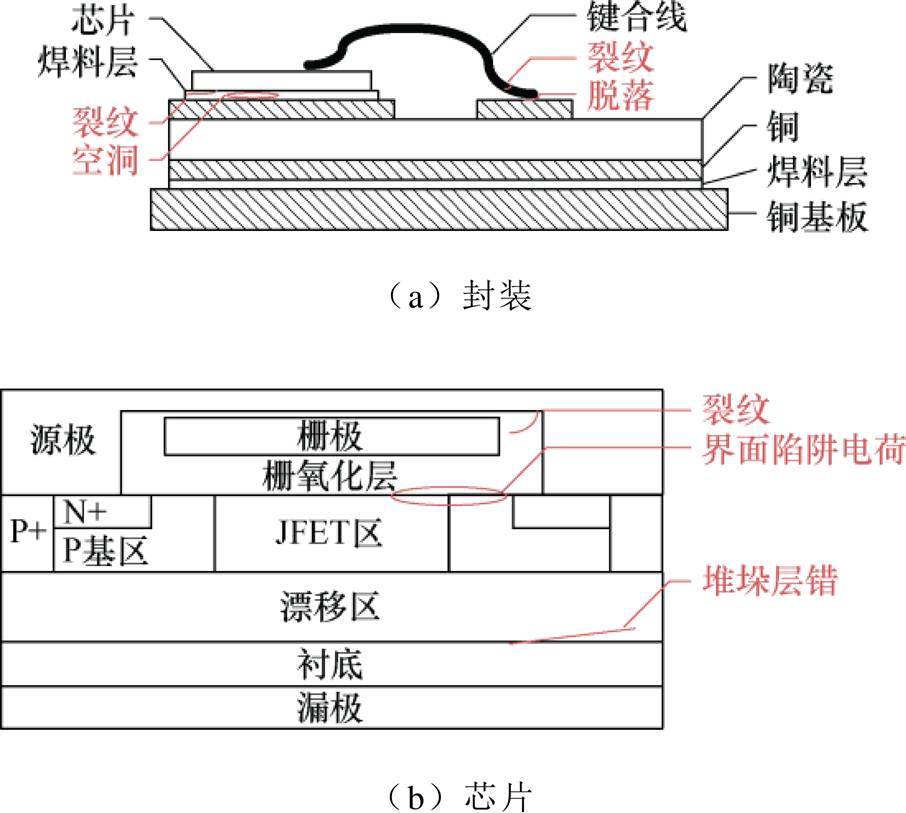

图1 SiC MOSFET的内部结构与失效模式

Fig.1 Internal structure and failure modes of SiC MOSFET

摘要 受寄生电感或串联器件分压不均影响,SiC MOSFET可能承受偶发的、安全工作区(SOA)外的短时过电压硬开关应力,造成参数退化或器件损坏,而现有的功率器件可靠性研究主要集中于SOA内的长期静态工况,导致预期寿命与实际寿命偏差较大。该文研究过电压硬开关应力作用下两种不同额定电压的SiC MOSFET退化机制,并与栅极开关应力和静态过电压应力测试结果进行对比。由于栅氧化层退化,工作在第一象限的器件阈值电压Vth和导通电阻RDS(on)减小,栅极漏电流IGSS和漏极截止电流IDSS增加。同时,受阈值电压和跨导变化的影响,器件动态特性产生变化。对于工作在第三象限的器件,堆垛层错扩大造成其体二极管正向压降增加。结合不同过应力工况下的实验结果和TCAD仿真,明确器件栅氧化层退化的主要机制为高电场应力导致的热载流子注入,且阈值电压退化规律主要与开关次数及漏源电压相关。该研究为器件在临界工况中的应用及变换器的裕量设计提供了理论支撑。

关键词:加速寿命测试 SiC MOSFET 栅氧化层退化 硬开关

碳化硅(Silicon Carbide, SiC)MOSFET在高压、高功率密度领域应用前景广阔。与硅(Silicon, Si)IGBT相比,SiC MOSFET在击穿电压、热导率、开关速度等方面具有显著优势[1-2]。然而,受限于更高的栅氧化层电场强度与氧化物电荷密度,SiC MOSFET的栅氧化层退化问题仍然是其应用范围扩大的一个潜在障碍[3]。

功率器件的可靠性评估主要基于安全工作区(Safe Operating Area, SOA)内的工况进行。通过500~1 000 h的静态或循环应力,激发SiC器件的半导体与封装失效[4]。其中,高温静态电应力测试主要应用于半导体可靠性评估,而循环的电热应力测试则更多地应用于封装可靠性评估[5]。针对SiO2/SiC界面较高的界面陷阱电荷密度,高温反偏(High Temperature Reverse Bias, HTRB)和高温栅偏(High Temperature Gate Bias, HTGB)测试分别在高温下对被测器件(Device Under Test, DUT)施加80%额定漏源电压VDS[6]或额定栅源电压VGS[7]。通过静态高温与高电场加速氧化物电荷的积累,并激发器件栅氧化层退化。针对SiC半导体较高的杨氏模量,功率循环(Power Cycling, PC)实验对DUT施加循环漏源电流IDS引起结温Tj的重复波动,进而模拟实际工况[8]。通过不同材料间热膨胀系数差异引起的机械应力,加速DUT键合线脱落等封装失效[9]。

除SOA内的可靠性评估外,器件的鲁棒性评估主要基于SOA外的极端工况进行。测试的应力时间从数微秒至数小时不等,器件失效机制集中于半导体内过电压、过电流产生的局部击穿与过热损坏。针对器件开关过程中偶发的雪崩击穿工况,非钳位感性开关(Unclamped Inductive Switching, UIS)测试通过电感的放电,施加超出DUT额定电压的VDS,并激发DUT的雪崩击穿。通过高温、高电压应力,引起器件局部热失控[10]或半导体退化。针对短路工况,短路测试对器件施加单次或重复短时过电流ISC。通过高电流密度与局部热应力,加速DUT半导体与封装的退化[11-12]。

图1 SiC MOSFET的内部结构与失效模式

Fig.1 Internal structure and failure modes of SiC MOSFET

针对MOSFET在变换器中面临的高频重复开关工况,开关测试对DUT施加SOA内的动态栅极电压VGS以及VDS、IDS应力,其应力时间约为数十小时。对应测试方法主要包括有VDS而无IDS应力的开关测试[13]、含IDS的开关测试[14]及基于Buck、功率因数校正(Power Factor Correction, PFC)等实际变换器和对应任务剖面的开关测试[15-16]等。相比于静态可靠性评估方法,动态的电、热应力加速了器件氧化物电荷的积累并极大地缩减了器件寿命,使其可靠性评估结果更接近实际应用。

然而,受串联器件分压不均和电路杂散电感等因素的影响[17],器件在实际应用中可能经历偶发的、SOA外的短时过电压硬开关应力工况。虽然其电压不足以引发器件雪崩击穿或瞬时热损坏,但是在动态高电压、电流应力及栅极开关应力的影响[18]下,基于静态工况的HTRB、HTGB,以及基于瞬时击穿工况的UIS等测试所得失效时间与器件的实际寿命存在较大偏差[14]。对于HTRB等静态测试,由于缺少开关过程的影响,过电压工况下的器件失效时间可达数百小时[19-20],远高于动态工况下所得结果,且其主要失效机制为静态高电压和漏电流产生的栅氧化层损伤与局部高温[21]。而动态UIS应力下,受雪崩击穿过程中高电场导致的热空穴注入及局部高温导致的封装退化的影响[22],器件失效时间仅为数千个开关周期[23],与实际寿命存在差异。此外,考虑到现有开关测试工况更多集中在SOA内,其评估结果同样难以直接用于描述过电压工况下的器件退化机制[24]。因此,器件在过电压开关工况下的参数退化规律及其失效机制有待进一步深入 研究。

为了准确评估器件在过电压开关应力下的可靠性,本文对过电压硬开关工况下的SiC MOSFET参数退化规律及其机理进行研究。首先介绍测试电路及其工作原理,并分析测试过程中的电、热应力;其次展示两种不同额定电压的SiC MOSFET在过电压开关工况下的静态、动态参数退化结果;再次对比静态过电压应力、栅极开关应力以及不同过电压开关应力对参数退化规律的影响;最后通过TCAD(technology computer-aided design)仿真研究器件的退化机制,并基于不同实验条件下所得参数退化结果分析VDS对Vth退化规律的影响。

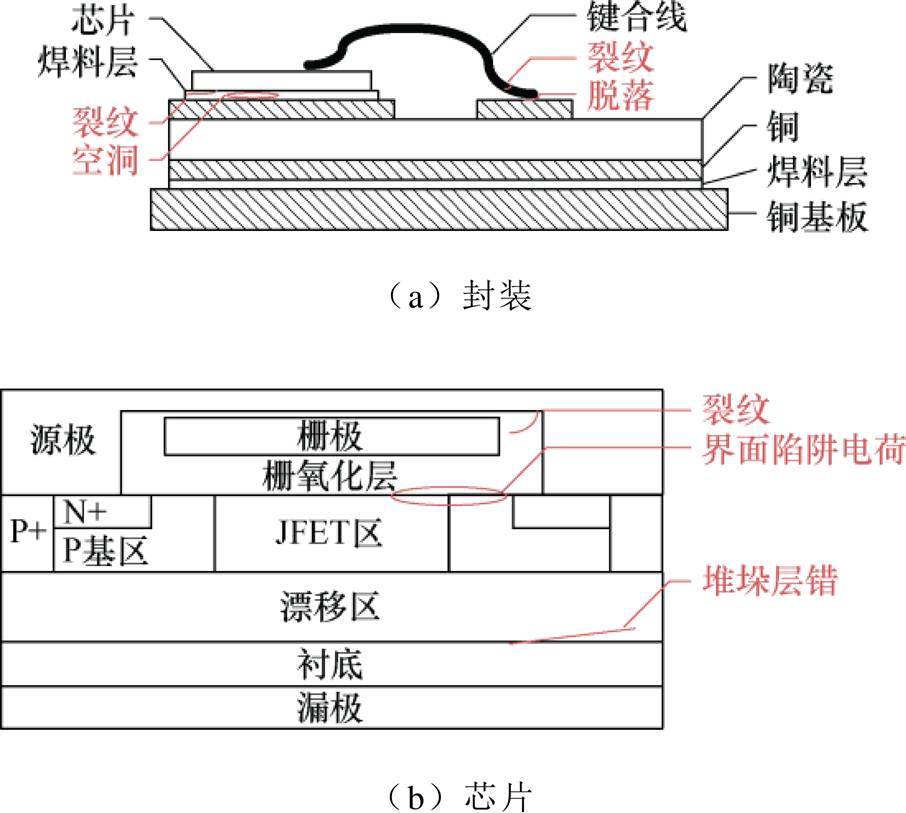

基于半桥电路搭建SiC MOSFET过电压硬开关应力测试电路,如图2所示。下管S2工作在开关状态,上管S1工作在截止状态并由体二极管续流,二者分别承受第一象限和第三象限的动态电、热应力。通过调节S2的占空比D2与直流输入电压VDC,可以控制器件的电压、电流及结温。当更换S1为肖特基二极管(Schottky Barrier Diode, SBD)、并设置S2栅极信号为双脉冲信号时,该测试电路也可以用于双脉冲测试(Double Pulse Test, DPT),对器件的动态特性进行测量。

图2 SiC MOSFET过电压开关应力测试装置

Fig.2 Overvoltage switching stress testing platform for SiC MOSFET

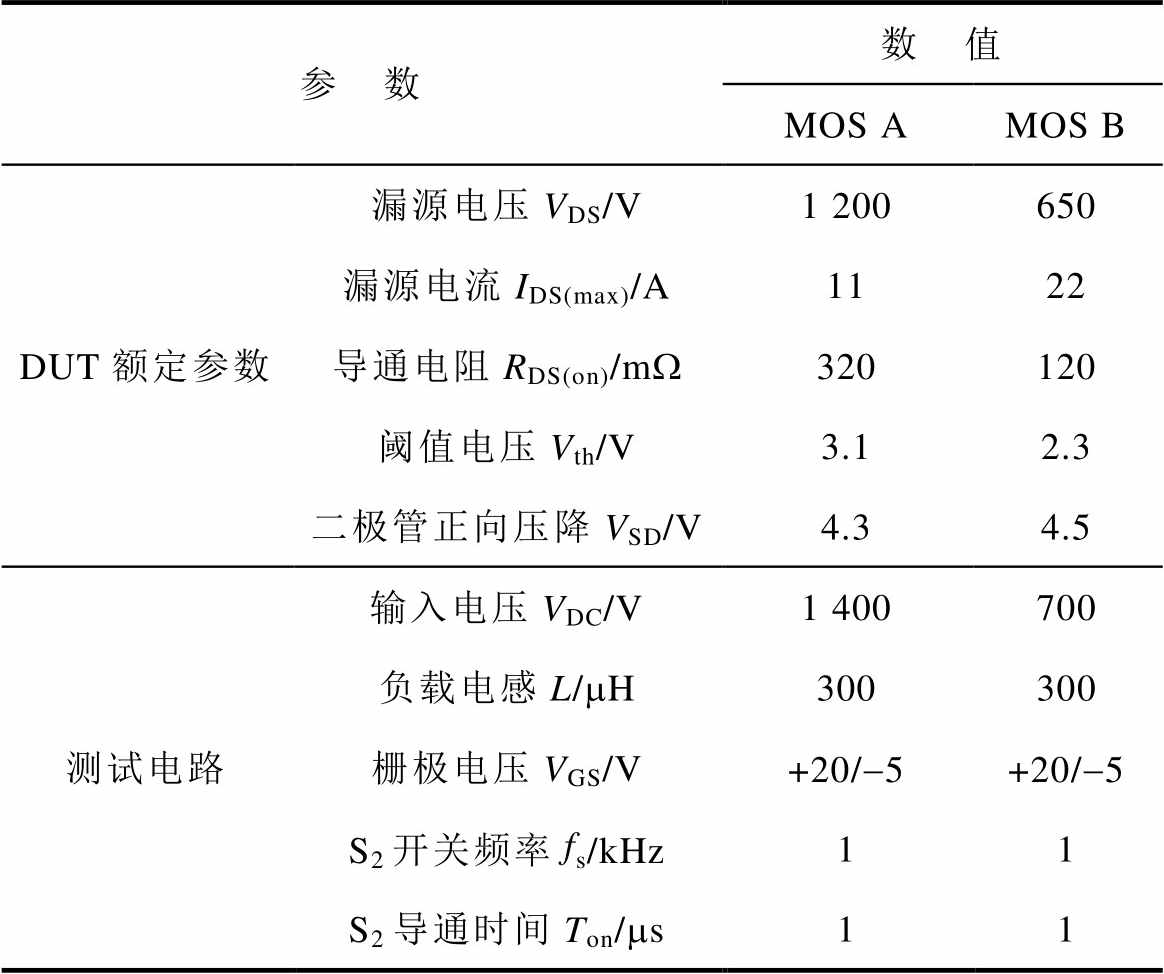

对两种不同额定电压的商用SiC VD-MOSFET的参数退化规律进行测试。其中,MOS A(C2M0280120D, 1 200 V)和MOS B(C3M012065D, 650 V)分别为Wolfspeed公司第二代和第三代SiC MOSFET,二者封装均为TO-247-3。

在室温(Ta=300 K)条件下对被测器件施加总计60 h的过电压硬开关应力。为避免开关过程中电压尖峰造成雪崩击穿,选择直流输入电压VDC为器件实际雪崩击穿电压V(BR)DSS的80%,即VDC= 1 400 V(MOS A)和VDC=700 V(MOS B)。设置S2导通时间Ton=1 ms、开关频率fs=1 kHz,以降低器件损耗并保持器件结温Tj接近环境温度Ta。同时,较低的占空比D2使得电感电流iL在S2截止状态期间可以下降至0。MOS A和MOS B详细参数与测试条件见表1。

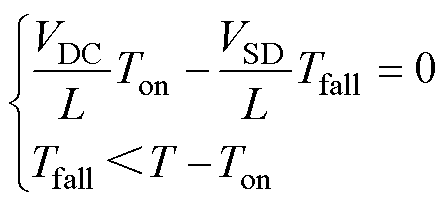

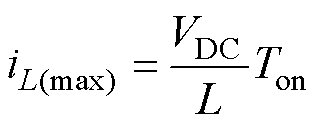

(1)

(1)

式中,VSD为二极管正向压降;Tfall为电感电流从峰值下降为0的时间;T为S2开关周期,T=1/fs。

表1 被测器件额定参数与过电压开关测试工况

Tab.1 Rated parameters of DUTs and overvoltage switching test conditions

参 数数 值 MOS AMOS B DUT额定参数漏源电压VDS/V1 200650 漏源电流IDS(max)/A1122 导通电阻RDS(on)/mW320120 阈值电压Vth/V3.12.3 二极管正向压降VSD/V4.34.5 测试电路输入电压VDC/V1 400700 负载电感L/mH300300 栅极电压VGS/V+20/-5+20/-5 S2开关频率fs/kHz11 S2导通时间Ton/ms11

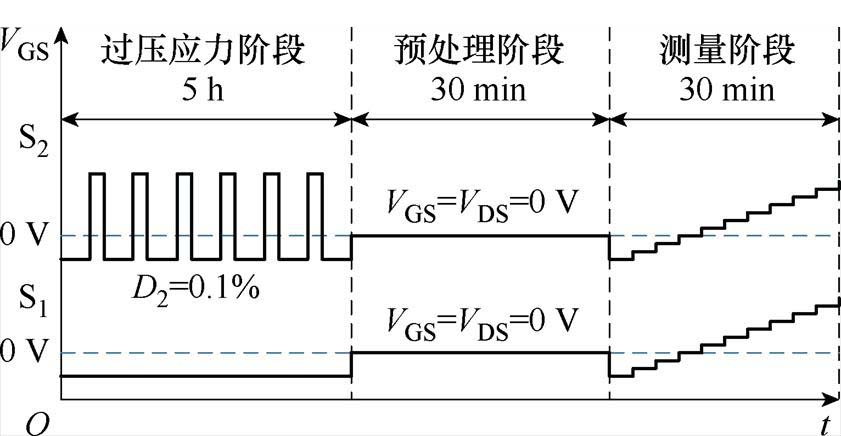

鉴于SiC MOSFET存在偏置温度不稳定等可恢复的参数退化[25],在应力阶段与测量阶段之间加入预处理阶段,以消除可恢复参数退化的影响。测试过程以6 h为一个周期,每个周期依次为持续5 h的过电压应力阶段、持续30 min的预处理阶段以及持续30 min的测量阶段,具体实验流程如图3所示。在预处理阶段,将MOSFET的各个电极短接,使得VGS和VDS均为0 V,进而减小因栅极偏置产生的可恢复漂移对阈值电压等参数测量结果的影响。

图3 含预处理阶段的实验流程

Fig.3 Experimental sequence with precondition stage

在测量阶段,基于动态和静态特性参数的变化对器件性能退化程度进行表征。其中,动态特性通过双脉冲测试进行测量,包括开通延迟td(on)和关断延迟td(off)、电压上升时间tr(v)和下降时间tf(v),以及开通损耗Eon和关断损耗Eoff。静态特性使用ITECH IT2801源测量单元(Source Measure Unit, SMU)进行测量,主要包括阈值电压Vth、导通电阻RDS(on)、转移特性、输出特性、栅极漏电流IGSS和漏极截止电流IDSS等。上述参数的定义及测量方法与器件数据手册保持一致。当发生以下异常状况时,测试中止:器件参数的偏移幅值超过初始值20%并造成器件结温异常升高;IDSS或IGSS大于1 mA;器件出现功能故障,如电极短路或器件断路等。

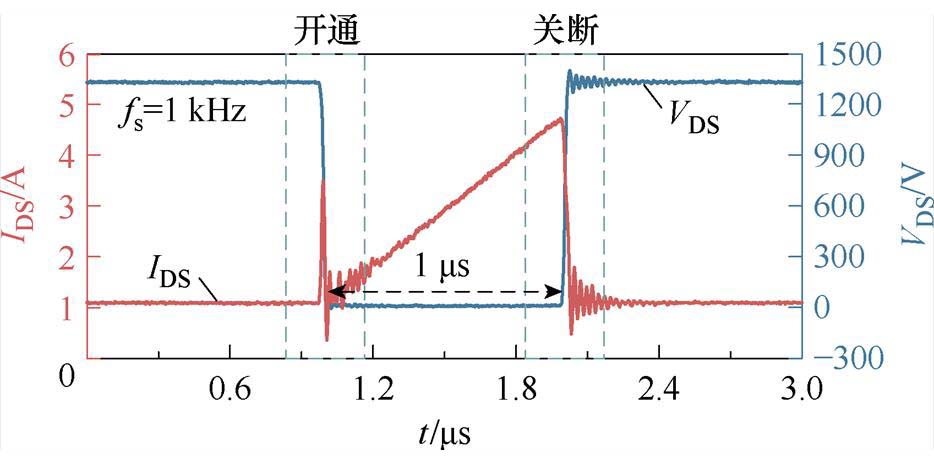

以MOS A为例,在图4中给出被测器件S2的VDS、IDS波形。当下管S2开通时,电感电流iL流经S2,并从0线性增加到最大值iL(max)=4.7 A。S2处于截止状态时,iL通过上管S1的体二极管VD1续流,并从峰值iL(max)线性下降为0。S2关断电压尖峰约为1 500 V,大于器件额定电压且小于其实际击穿电压。分析开关过程可知,S2承受第一象限的过电压硬开关应力,S1承受第三象限的过电压开通应力。

(2)

(2)

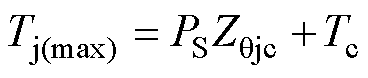

为了评估开关测试中温度应力对参数退化的影响,基于损耗与热阻估算器件结温。考虑到S2开关频率远高于功率循环所用频率,可以假设一定应力时间后其结温到达最大值Tj(max)且近似恒定。Tj(max)可以通过损耗PS和结-壳热阻Zqjc进行计算[26]。

(3)

(3)

图4 MOS A S2的VDS和IDS波形(VDS=1 400 V, IDS(max)=4.7 A)

Fig.4 VDS and IDS waveforms of MOS A S2 (VDS=1 400 V and IDS(max)=4.7 A)

式中,Tc为温度传感器所测的器件壳温;损耗PS通过VDSIDS计算;热阻Zθjc由器件的数据手册提供,并基于恒功率测试进行校正。对MOS A而言,S1的Tj(max)= 314.9 K,S2的Tj(max)=300.6 K;对于MOS B,S1和S2的Tj(max)分别为311.2 K和300.4 K。

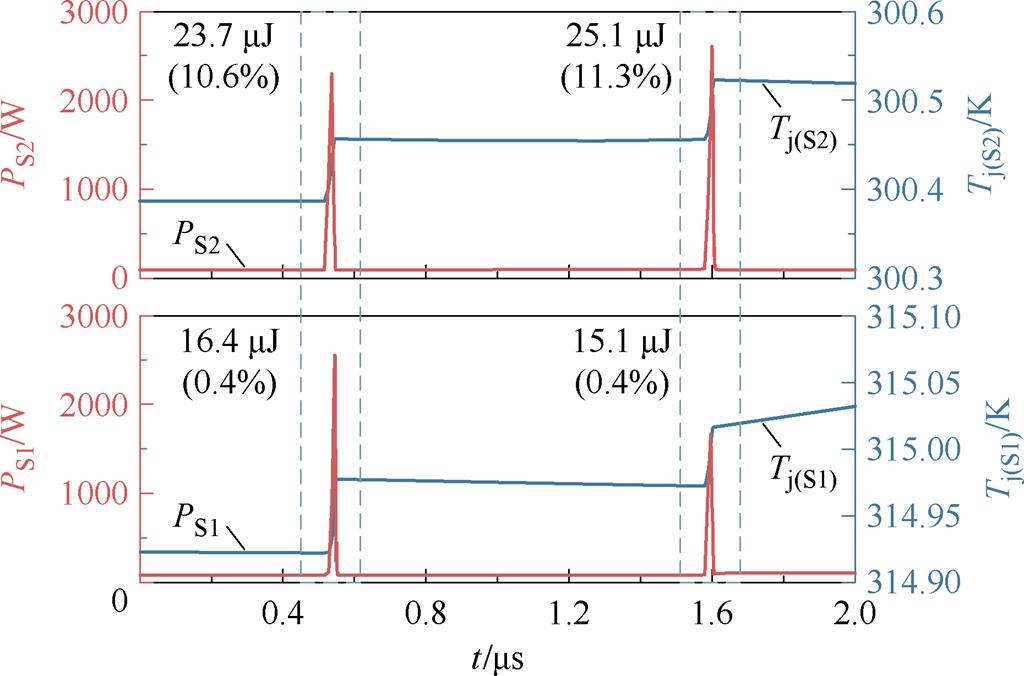

通过Spice仿真进一步分析和验证上述结温结果,MOS A S1和S2的仿真损耗和结温(VDS=1 400 V)如图5所示。单个开关周期内,对于MOS A,S2和S1的损耗分别为222.2 mJ和3.7 mJ,对应Tj(max)分别为300.5 K和316.2 K。被测器件的平均结温与结温变化幅值远小于功率循环测试,此外,较低的单次开关损耗也不足以引发UIS等测中与局部过热相关联的封装退化。因此,被测器件参数退化与热应力导致的封装退化关联较低,其更多受电应力导致的半导体退化的影响。

图5 MOS A S1和S2的仿真损耗和结温(VDS=1 400 V)

Fig.5 Simulation switching losses and junction temperature of MOS A S1 and S2 (VDS=1 400 V)

与HTRB测试中承受的静态应力不同,在过电压开关应力测试中,器件主要承受动态的电压、电流应力。对于静态的HTRB测试,器件损耗主要为IDSS产生的截止损耗;而在过电压开关测试下,S2的损耗主要为MOSFET开关过程中的开关损耗,S1则为体二极管的导通损耗。同时,过电压开关测试引入了器件栅极的开通、关断行为,在开关过程中对氧化物陷阱进行重复充、放电,加速了器件栅氧化层的退化。

基于三组不同批次的MOS A和MOS B进行过电压开关测试,以验证器件参数退化的可重复性。经历总计60 h的应力时间(对应开关次数Ncycle约为2.16×108)后,被测器件S1和S2的静态参数(Vth、RDS(on)等)和动态参数(Eon、Eoff等)存在显著变化,同时各组被测器件在测试中呈现出相似的参数退化趋势。下面分别对一组有代表性的MOS A和MOS B的测试结果进行分析。

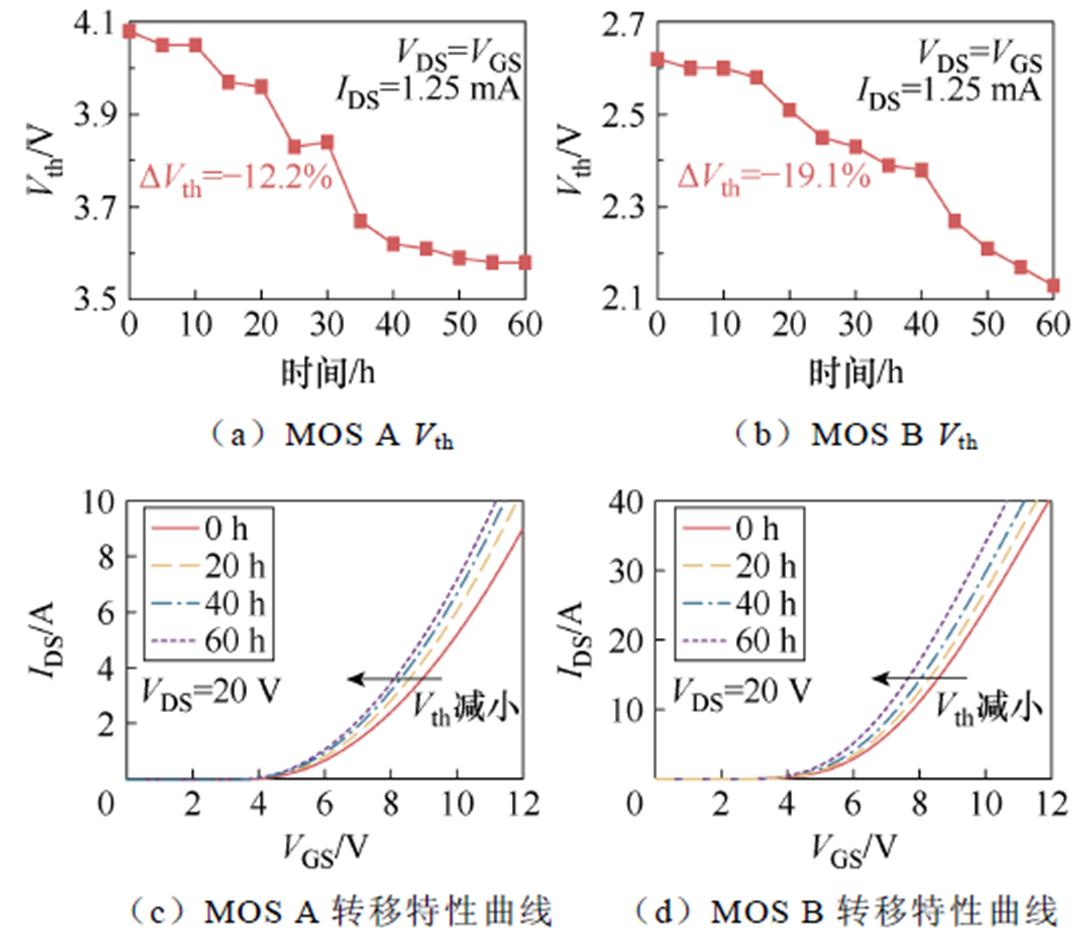

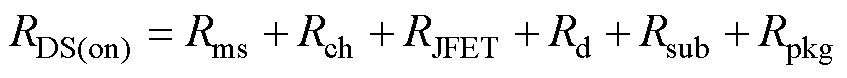

对于工作在第一象限的S2,随应力时间增加,其Vth减小、转移特性曲线左移,表明其退化可能发生在栅氧化层,过电压开关应力下S2Vth与转移特性的变化如图6所示。图6a、图6b给出了器件Vth的变化,经60 h的开关应力后,MOS A的Vth降低了0.5 V(-12.2%),MOS B的Vth降低了0.69 V(-19.1%)。从图6c、图6d可知,受栅氧化层退化及阈值电压降低的影响,器件的转移特性曲线左移。此外,MOS A的Vth降低在40 h后逐渐减缓,表明其栅氧化层退化在这一阶段趋于稳定。基于转移特性曲线计算可知,二者跨导gm的变化存在差异:MOS A的gm增加,而MOS B的gm减小。

图6 过电压开关应力下S2Vth与转移特性的变化

Fig.6 Changes of Vth and transfer characteristics of S2 under overvoltage switching stress

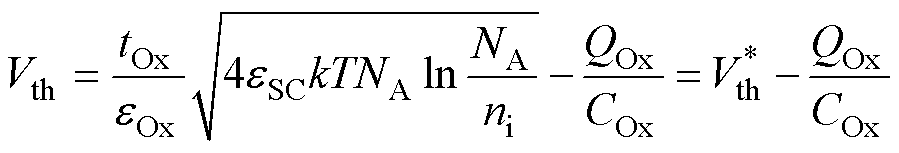

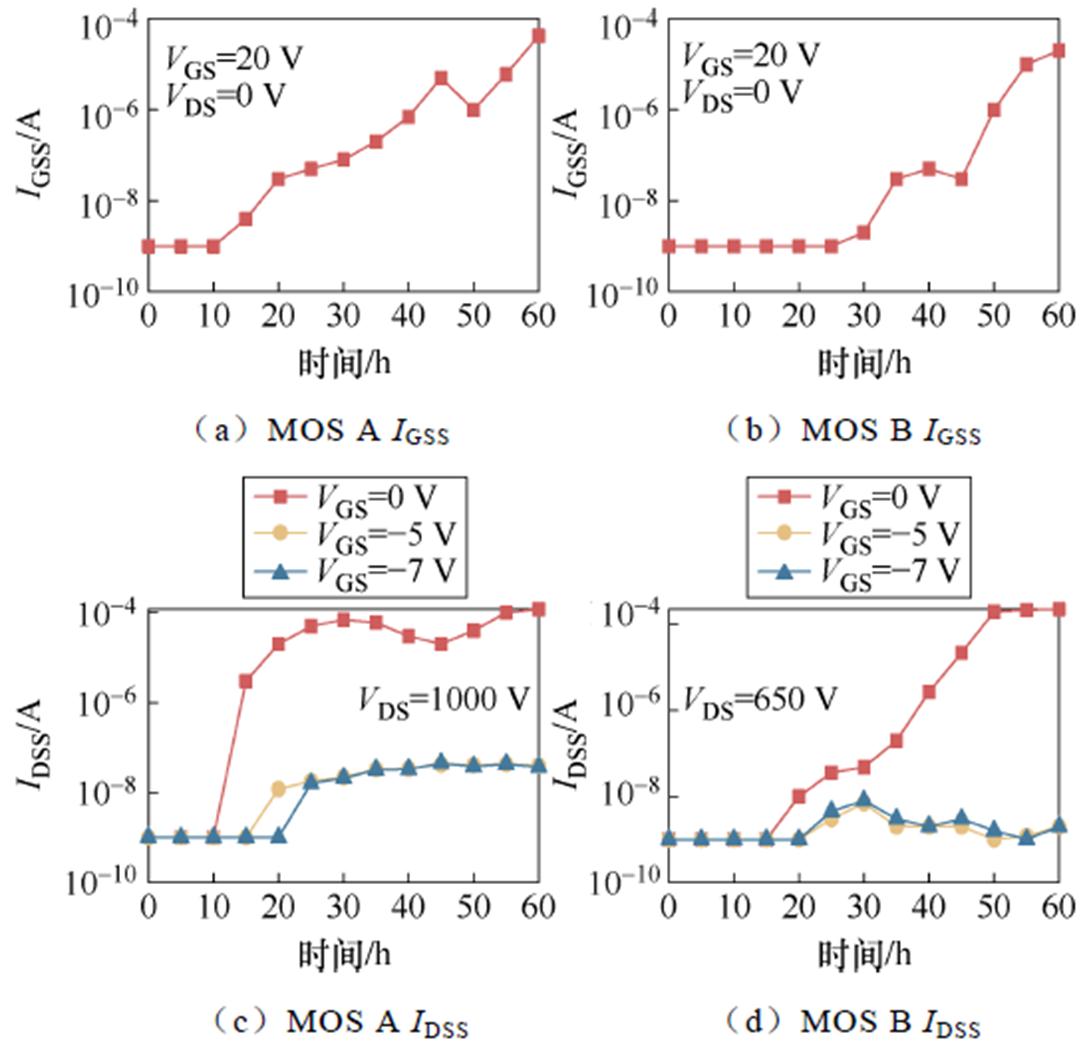

MOS A和MOS B的栅极漏电流IGSS分别如图7a、图7b所示,经60 h应力后,二者分别从1 nA增加至42 mA和20 mA,IGSS的增加进一步验证了器件的栅氧化层退化。栅氧化层的退化可能与高电场下存在的热载流子注入(Hot Carrier Injection, HCI)效应相关[5, 18]。受VDS及较强的沟道电场影响,器件载流子克服势垒并注入栅氧化层中,形成氧化物陷阱电荷,同时在SiO2/SiC界面形成界面陷阱电荷。将氧化物陷阱电荷与界面陷阱电荷等电荷等效为氧化物总电荷QOx,则该电荷可能引起能带弯曲并降低Vth,影响器件的导通电阻等特性。Vth与QOx的关系可以表示为

(4)

(4)

式中,tOx为栅氧化层厚度;εOx和εSC分别为SiO2和SiC的介电常数;k为玻耳兹曼常数;T为热力学温度;NA和ni分别为掺杂浓度和本征载流子浓度;COx为栅氧化层的比电容; 为不考虑氧化物电荷QOx影响的理想阈值电压。

为不考虑氧化物电荷QOx影响的理想阈值电压。

图7 过电压开关应力下S2IGSS和IDSS的变化

Fig.7 Changes of IGSS and IDSS of S2 under overvoltage switching stress

器件S2在不同VGS下测得的IDSS如图7c和图7d所示。VGS=0时,初始状态(Ncycle=0)下器件IDSS约为1 nA;经60 h开关应力后,MOS A和MOS B的IDSS均大于100 mA。IDSS的增加主要与器件栅氧化层退化,以及N型和P型半导体层构成的PN结退化相关[27]。将漏电流的变化值DIDSS表示为

(5)

(5)

式中,DIDch和DIDPN分别为沟道漏电流及半导体PN结反向电流的变化。

理想状态下,沟道漏电流IDch的幅值可以忽略,IDSS≈IDPN。由于界面陷阱电荷增加,当VGS=0 V时,沟道漏电流增加(DIDch>0),对应图7c和图7d中较大的IDSS。而当VGS=-5 V时,由于沟道完全关闭(IDch≈0),漏电流增加量DIDSS≈DIDPN,低于VGS=0 V时的测量结果。且VGS=-7 V和VGS=-5 V时,器件IDSS基本一致,验证了DIDSS存在不受沟道漏电流影响的分量DIDPN,使得DIDSS≈DIDPN。基于上述实验结果可知,除栅氧化层退化外,半导体PN结退化同样造成了IDSS的增加。

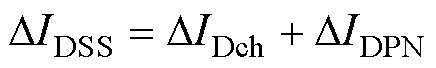

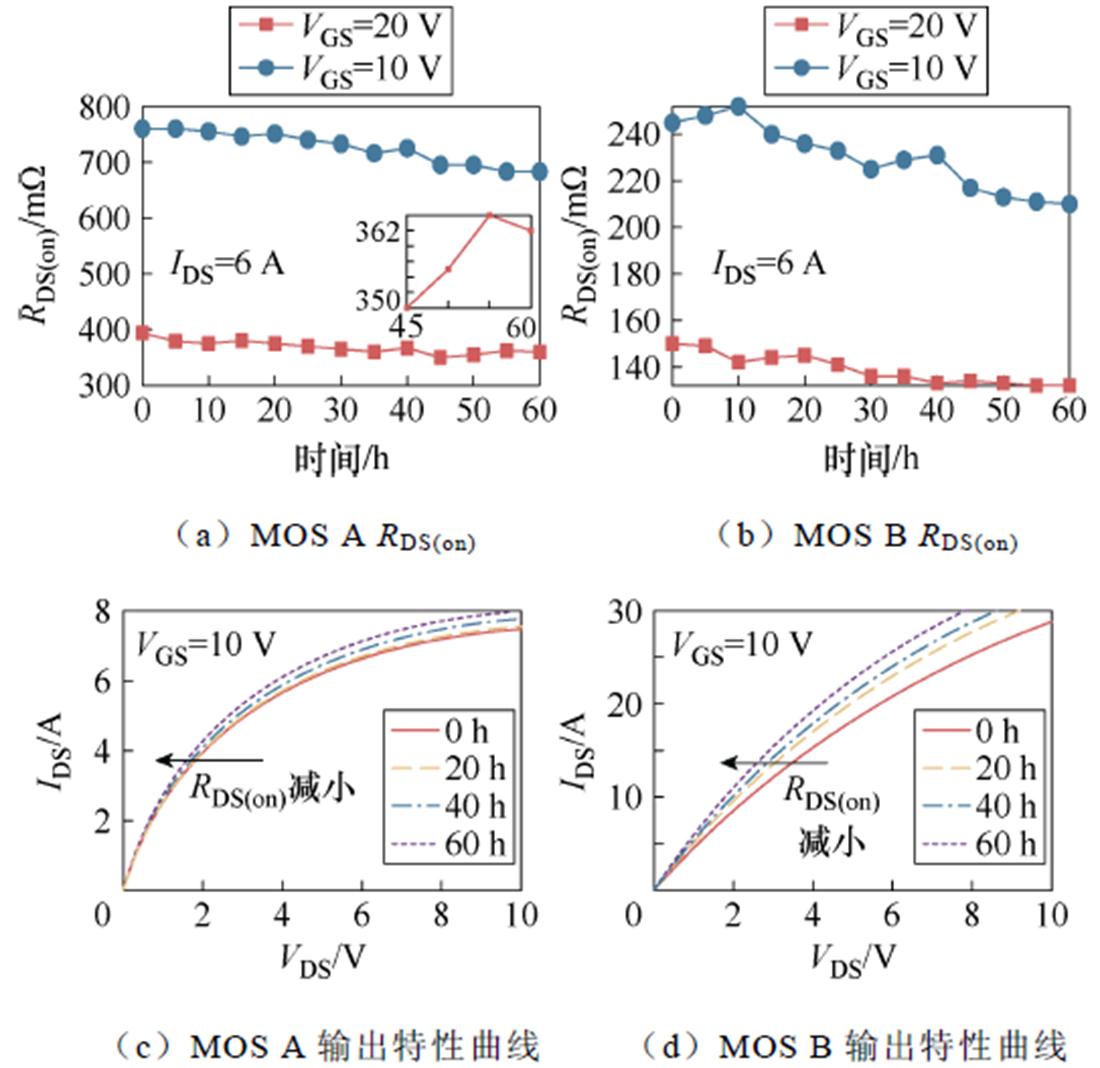

导通电阻RDS(on)与输出特性曲线随应力时间的变化如图8所示。MOS A和MOS B的RDS(on)在测试中均显著降低,对应器件输出特性曲线左移。此外,MOS A在40~60 h的测试期间RDS(on)略微增加且仍小于其初始值。基于式(6)和式(7)可知,器件导通电阻RDS(on)的降低与其栅氧化层退化相关,即Vth降低导致沟道电阻Rch降低[28]。与VGS=20 V下所得结果相比,VGS=10 V时测得的DRDS(on)的幅值增加。该现象主要是由于VGS较低时,Rch较大且在RDS(on)中的比例较高,对应其变化幅值DRch的增加,且封装退化等因素产生的电阻增加对RDS(on)的影响减小,最终造成了DRDS(on)幅值的增加。

(6)

(6)

式中,Rms为漏极、源极金属与半导体的接触电阻;Rch为沟道电阻;RJFET为JFET区电阻;Rd和Rsub分别为漂移区和衬底的电阻;Rpkg为含键合线电阻在内的封装电阻。Rch与Vth之间的关系可以表示为

图8 过电压开关应力下S2RDS(on)和输出特性的变化

Fig.8 Changes of RDS(on) and output characteristics of S2 under overvoltage switching stress

(7)

(7)

式中,Lch和Z分别为沟道的长度和宽度;mni为电子的反型层迁移率。

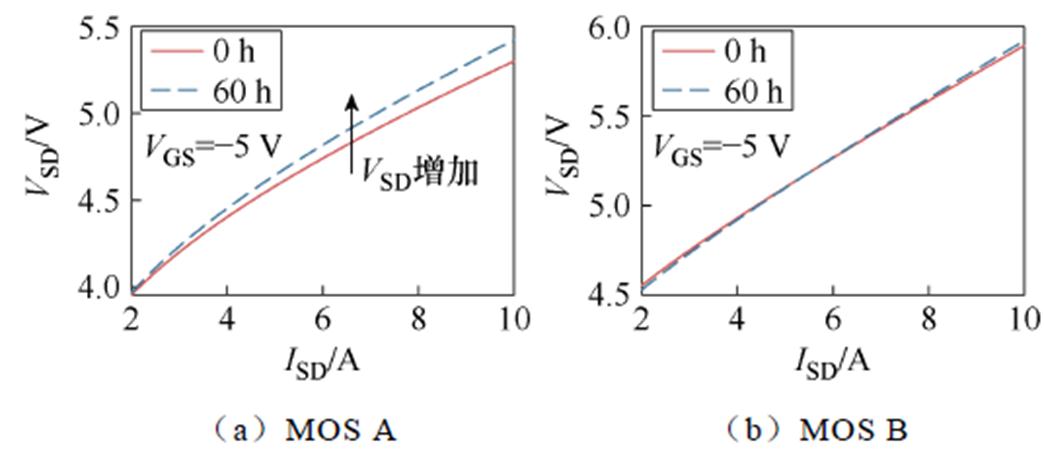

应力时间40 h后,MOS A的RDS(on)上升与其封装退化存在关联,即器件在这一阶段存在一定的封装退化,其体二极管正向压降VSD的增加验证了这一结论,过电压开关应力下S2VSD的变化如图9所示。相比器件MOS B,MOS A的DVSD/DISD增加,表明器件第三象限导通状态下的等效电阻增大,即被测器件的封装退化导致了Rms和Rpkg增加。

(8)

(8)

式中,Vf为器件半导体PN结的导通压降。

图9 过电压开关应力下S2VSD的变化

Fig.9 Changes of S2VSD under overvoltage switching stress

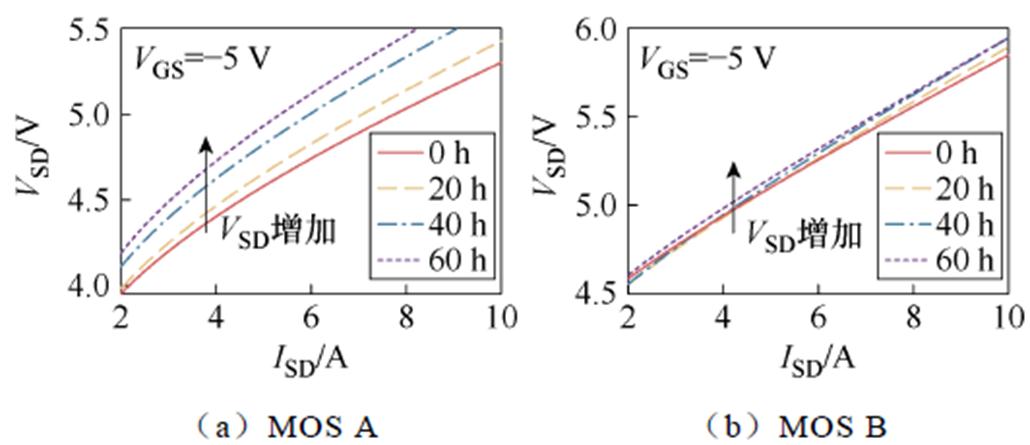

对于工作在第三象限的S1,随着应力时间增加,其VSD逐渐增加,如图10所示。同时,Vth基本保持恒定。VSD的增加可以通过半导体堆垛层错的扩大导致的半导体退化解释:经历第三象限电压、电流应力时,高电场促进了空穴向衬底区扩散,并在其附近或其内部与电子复合,而复合释放的能量造成半导体中堆垛层错的蔓延,减小器件的电流路径并导致体二极管的VSD增加[29]。结温变化引起的封装退化也可能造成等效电阻Rms+Rpkg增加,进而造成器件VSD增加。

图10 过电压开关开关应力下S1VSD的变化

Fig.10 Changes of S1VSD under overvoltage switching stress

基于图2所示测试平台开展双脉冲测试,以表征器件动态特性的退化。S1为SBD(C4D10120A, 1 200 V),直流输入电压VDC=600 V,开关状态下,漏极电流ID=6 A。使用50 W 电阻作为器件的栅极电阻RG,以降低开关速度并减小测量相对误差。此外,为了量化动态特性的退化程度,基于开关波形提取相应的特征参数进行分析,包括开通延迟td(on)和关断延迟td(off)、电压上升时间tr(v)和下降时间tf(v),以及开通损耗Eon和关断损耗Eoff。

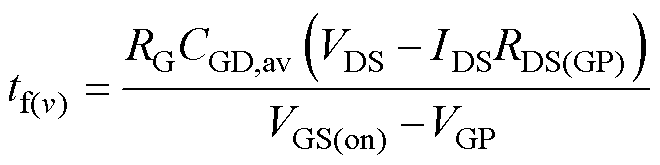

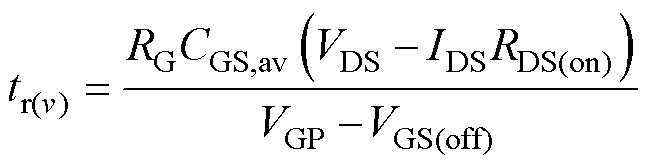

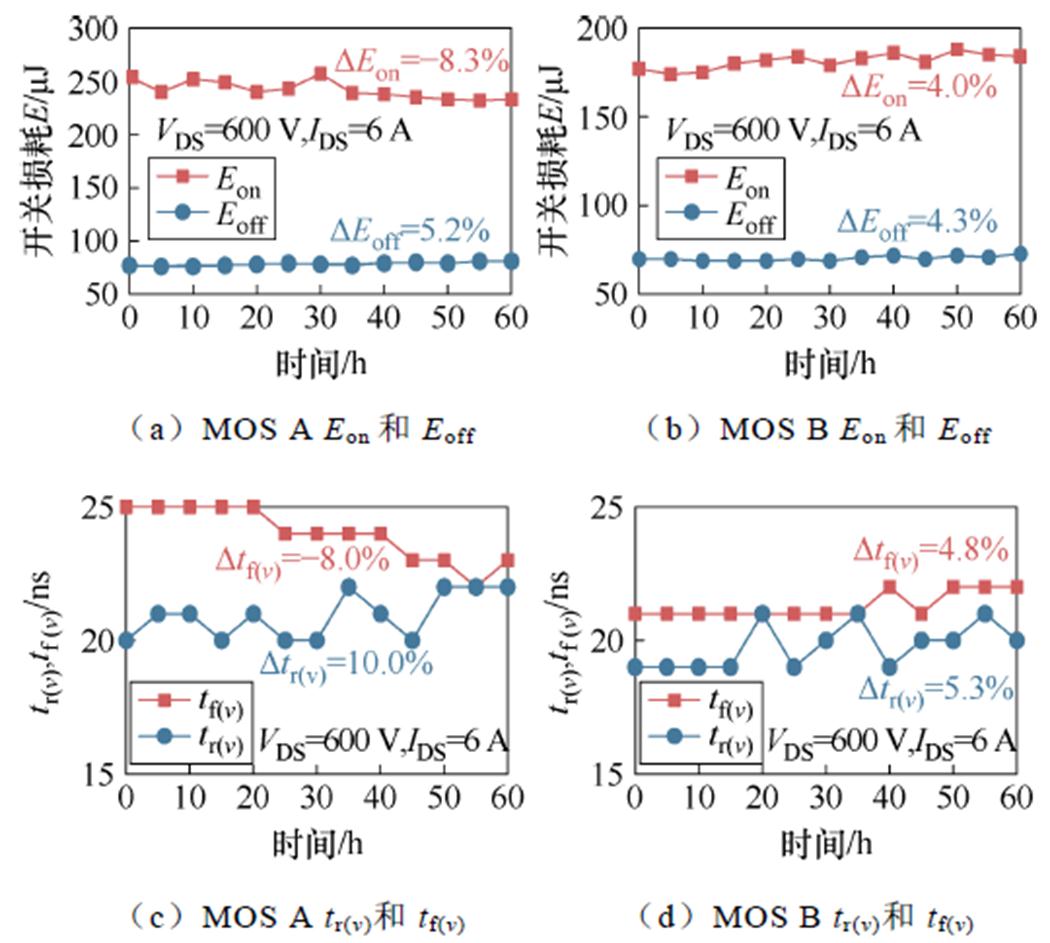

开关损耗和电压上升、下降时间的变化如图11所示。经60 h的开关应力,MOS A的Eon降低8.3%,Eoff增加5.2%;同时,tf(v)降低8.0%,tr(v)增加10%。与MOS A不同,MOS B的Eon增加4.0%,Eoff增加4.3%;tf(v)和tr(v)分别增加4.8%和5.3%。对比可知,tf(v)和tr(v)的变化是开关损耗变化的主要原因,二者可以分别表示为

(9)

(9)

(10)

(10)

图11 过电压开关应力下开关损耗和电压上升、下降时间的变化

Fig.11 Changes of switching losses and voltage rise and fall times under overvoltage switching stress

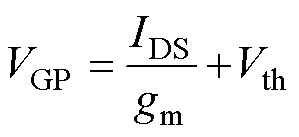

式中,VGP为米勒平台电压;CGD,av和CGS,av分别为开关过程中漏源电容CGD和栅源电容CGS的平均值;RDS(GP)为VGS=VGP时的器件电阻;VGS(on)和VGS(off)分别为栅极开通和关断电压。VGP可以基于gm和Vth表示为

(11)

(11)

器件MOS A和MOS B的电压上升、下降时间变化的不同主要与二者跨导gm和漏源电容CGD的不同变化相关。对于MOS A,由于gm增加且Vth降低,VGP降低,进而造成tf(v)降低、tr(v)增加。而由于MOS B的Vth降低且gm降低,二者最终造成VGP增加,且栅氧化层退化导致了CGD和CGS的增加,造成MOS B的tf(v)和tr(v)增加。

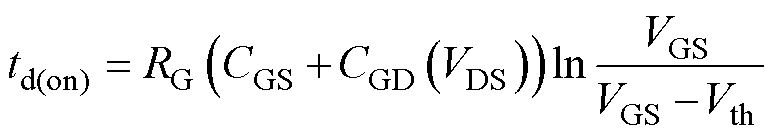

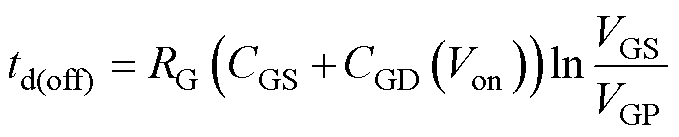

图12给出了器件开通延迟td(on)和关断延迟td(off)的变化。随应力时间增加,MOS A的td(on)降低7.9%,td(off)增加6.8%;而MOS B的td(on)增加8.2%,td(off)降低5.0%。将td(on)和td(off)分别表示为

(12)

(12)

(13)

(13)

式中,CGD(VDS)和CGD(Von)分别为器件截止和导通状态下的漏源电容。由于Vth和VGP减小,MOS A的td(on)降低、td(off)增加。对于MOS B,CGD增加是其td(on)增加的主要原因,而其td(off)的减小则与VGP增加相关。上述结果表明,gm和CGD的变化同样影响了器件的开关延迟。

图12 过电压开关应力下器件开关延迟的变化

Fig.12 Changes of switching delay times under overvoltage switching stress

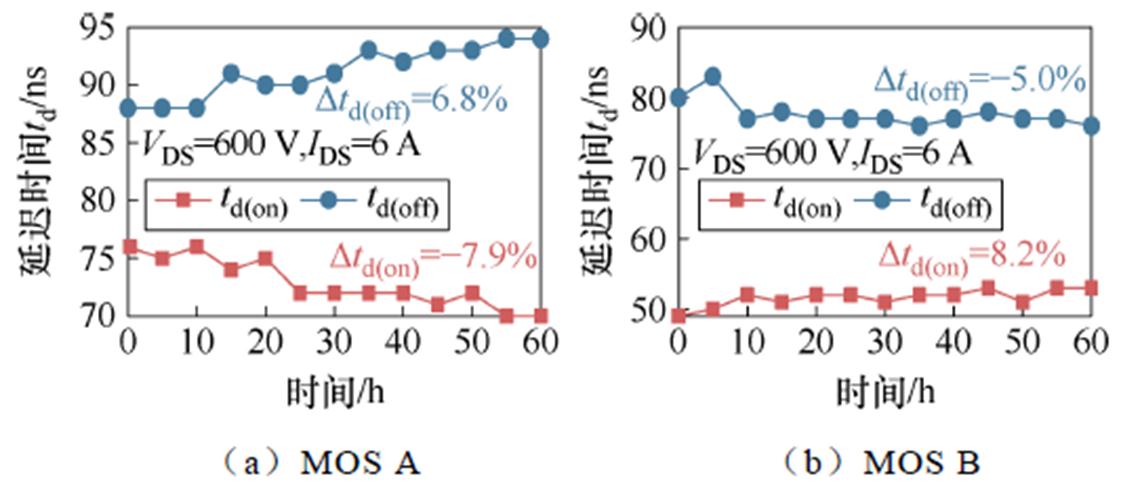

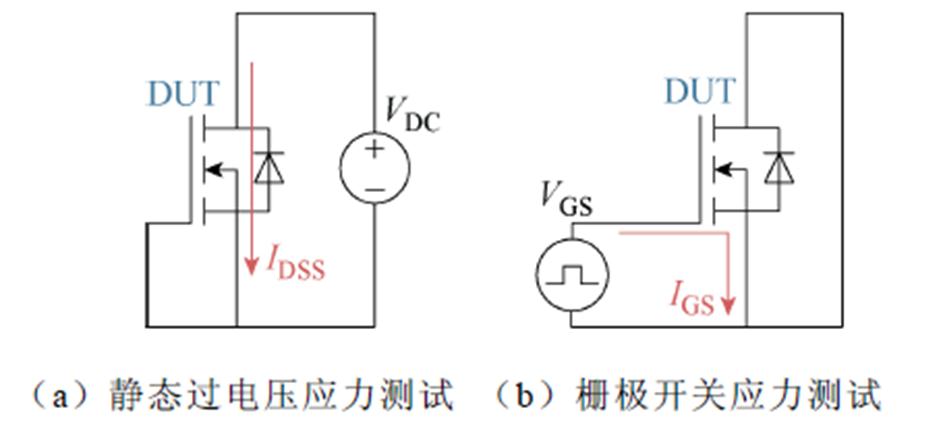

对MOS A和MOS B进行静态过电压应力测试、栅极开关应力测试及不同条件下的过电压开关应力测试,以研究过电压开关应力对器件退化的影响。通过更改图2所示电路的线路连接方式,得到图13中的静态过电压应力和栅极开关应力测试电路。其中,静态过电压应力测试在栅源极短路条件下,对器件施加恒定的VDS过电压应力;而栅极开关应力测试则在漏源极短路条件下,对器件施加动态VGS开关应力。

图13 静态过电压应力与栅极开关应力测试原理

Fig.13 Schematic diagram of static overvoltage stress testing and gate switch stress testing

与过电压开关应力测试相似,在常温下测试三组不同批次器件以验证结果的可重复性。测试应力时间为60 h,且VDC、VGS等电路参数与过电压开关应力测试保持一致,并对动态和静态参数进行测量。

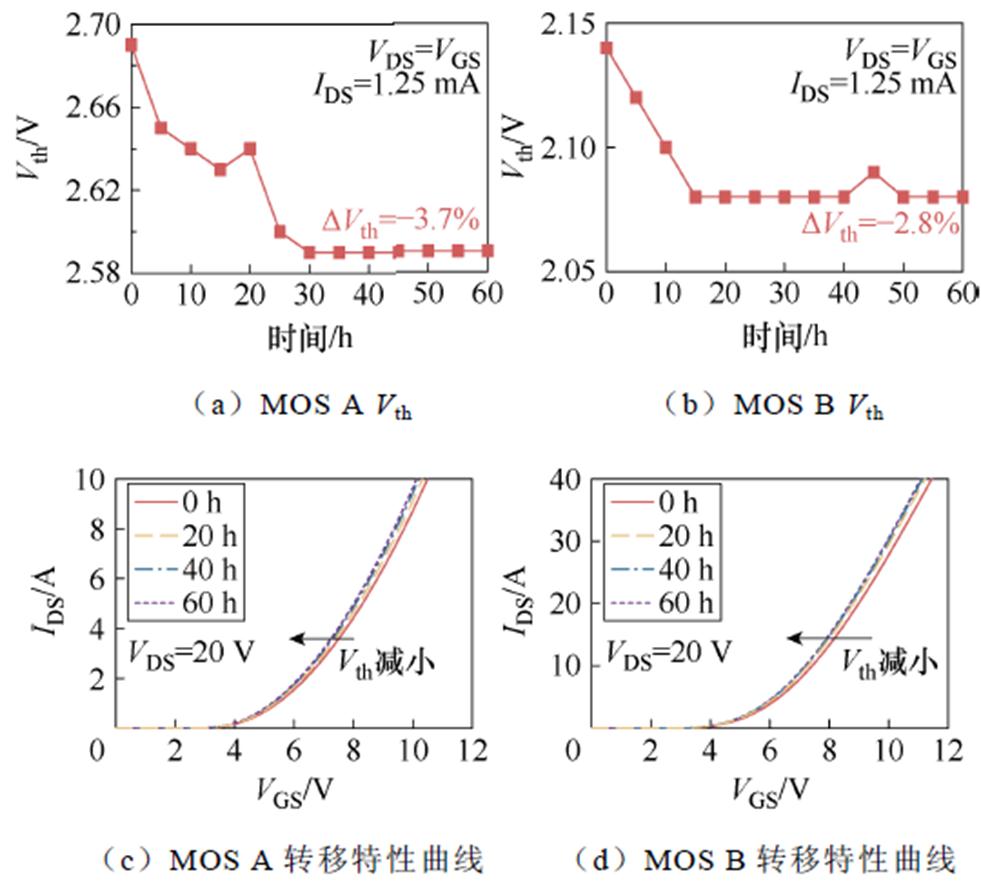

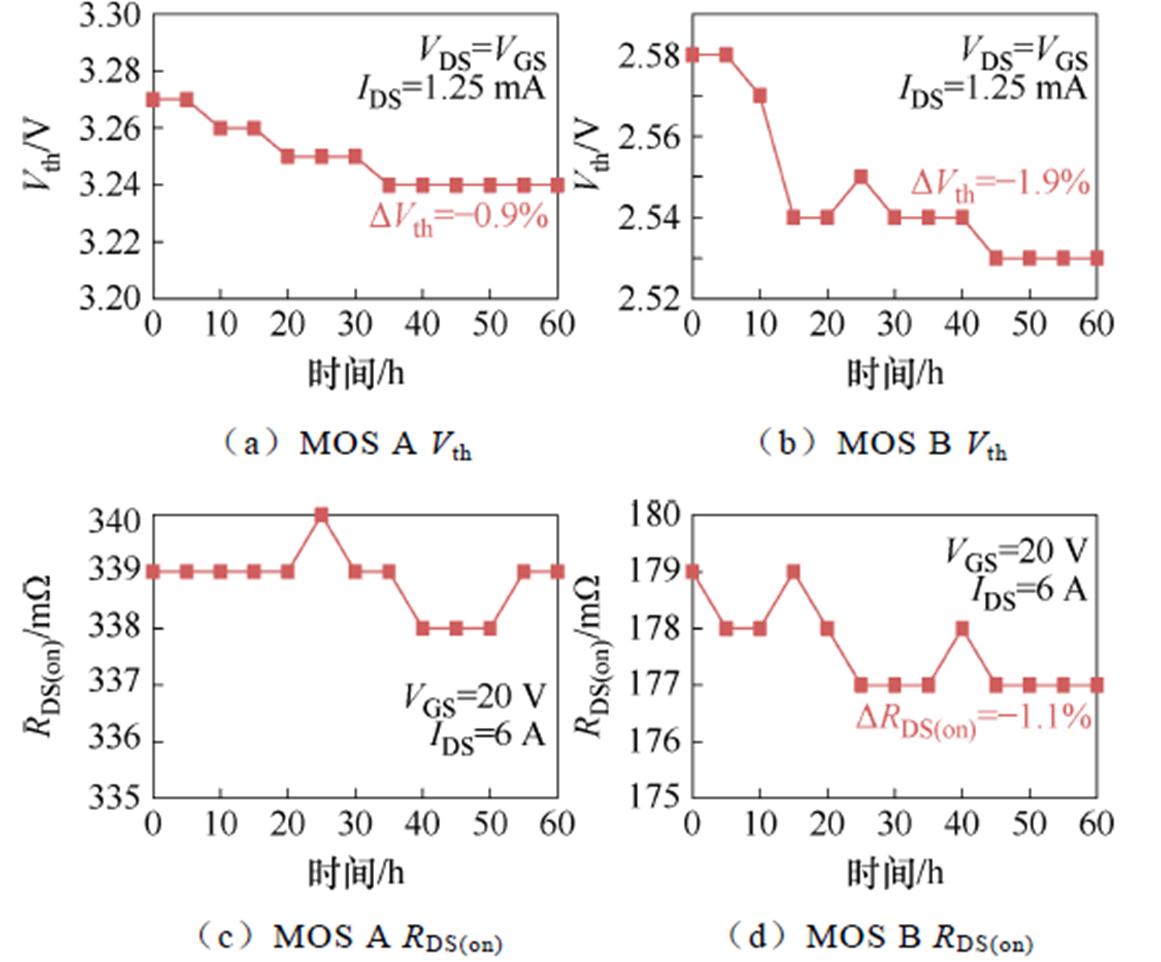

在静态过电压应力下,虽然器件参数变化幅值远小于过电压开关应力测试所得结果,但二者退化趋势基本一致。静态过电压应力下Vth与转移特性及RDS(on)的变化如图14和图15所示。静态过电压应力造成了器件转移特性左移,Vth及RDS(on)减小。

图14 静态过电压应力下Vth与转移特性的变化

Fig.14 Changes of Vth and transfer characteristics under static overvoltage stress

图15 静态过电压应力下RDS(on)的变化

Fig.15 Changes of RDS(on) under static overvoltage stress

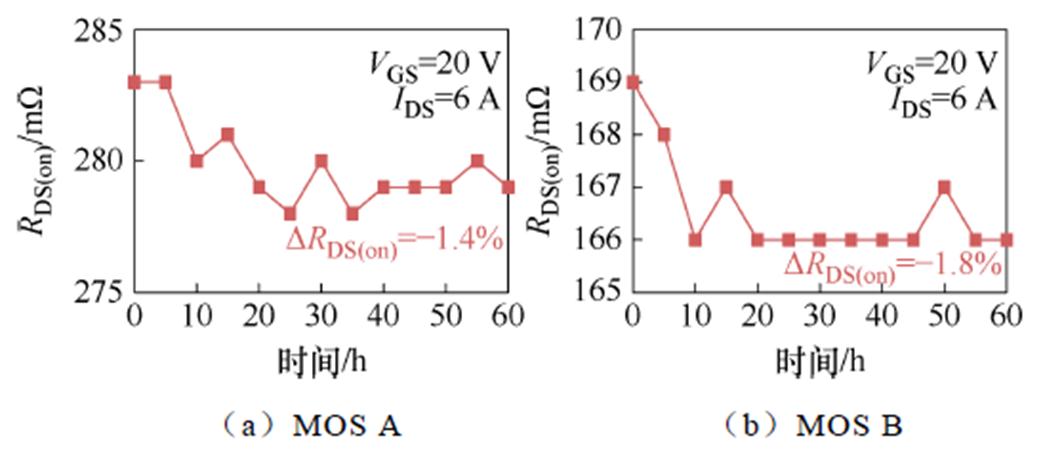

MOS A和MOS B的Vth分别降低0.1 V(-3.7%)和0.06 V(-2.8%);二者RDS(on)分别降低4 mW(-1.4%)和3 mW(-1.8%)。与2.1节相似,Vth和RDS(on)的变化与高电场下的器件栅氧化层退化相关。静态的栅氧化层高电场导致的F-N隧穿电流(Fowler-Nordheim tunneling current)加速了器件氧化物电荷的积累,并造成器件阈值电压等参数的退化。此外,如图16所示的静态过电压应力下IDSS和IGSS的变化中,MOS A与MOS B的漏电流IDSS增加,同样由栅氧化层退化引起。

图16 静态过电压应力下IDSS和IGSS的变化

Fig.16 Changes of IDSS and IGSS under static overvoltage stress

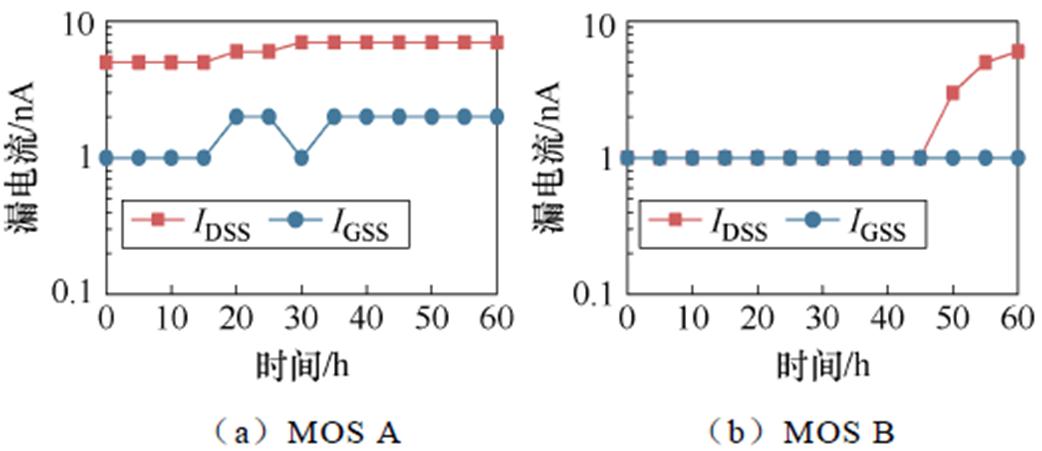

器件开关延迟和电压上升、下降时间等动态特性近似保持恒定,如图17所示。这主要与器件Vth和gm变化较小相关。与过电压开关测试相比,静态过电压应力下器件不受动态VGS、VDS及IDS应力的影响。静态应力下较小的参数退化幅值表明,过电压开关测试中的动态应力显著加速了栅氧化层退化,且对器件动态特性产生了更大的影响。

图17 静态过电压应力下动态特性变化

Fig.17 Changes of dynamic characteristics under static overvoltage stress

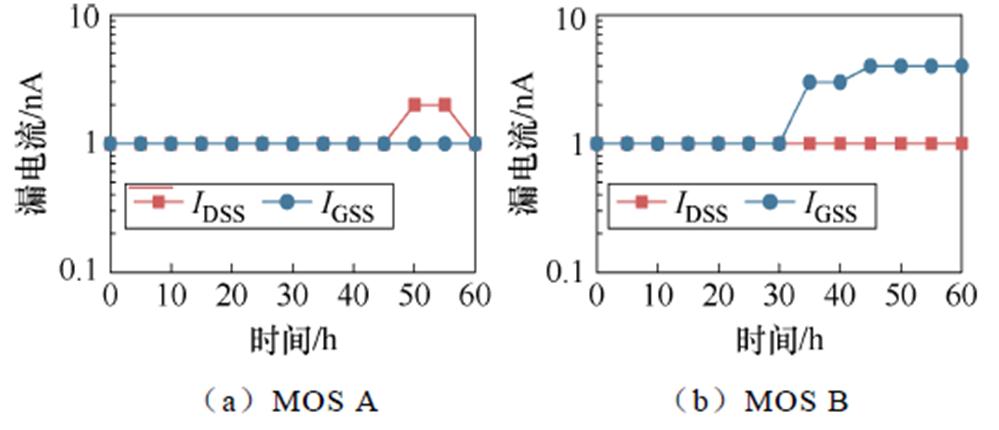

通过栅极开关应力测试研究动态VGS对器件参数的影响。测试使用+20 V/-5 V为器件栅极电压,除VDS=0 V外,其余测试条件与过电压开关应力测试保持一致。需要注意的是,MOS A中VGS的额定最大值为+25 V/-10 V,MOS B则为+19 V/-8 V,即MOS B的实际VGS超出其额定的最大值VGS(max),这可能对应着更高的栅氧化层电场,以及更快的器件参数退化速度。

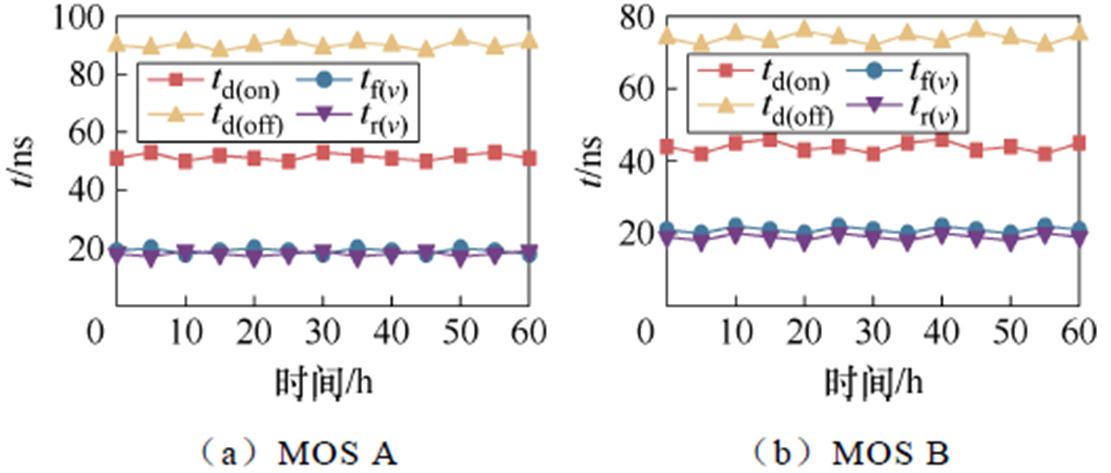

图18和图19分别给出了栅极开关应力下器件Vth、RDS(on)和漏电流的变化。对于MOS A,这些参数基本保持恒定;而对于器件MOS B,Vth与RDS(on)分别降低了1.9%和1.1%。结合栅极漏电流IGSS的增加可知,栅氧化层退化是MOS B上述参数变化的主要原因。

图18 栅极开关应力下Vth和RDS(on)的变化

Fig.18 Changes of Vth and RDS(on) under gate switching stress

图19 栅极开关应力下IDSS和IGSS的变化

Fig.19 Changes of IDSS and IGSS under gate switching stress

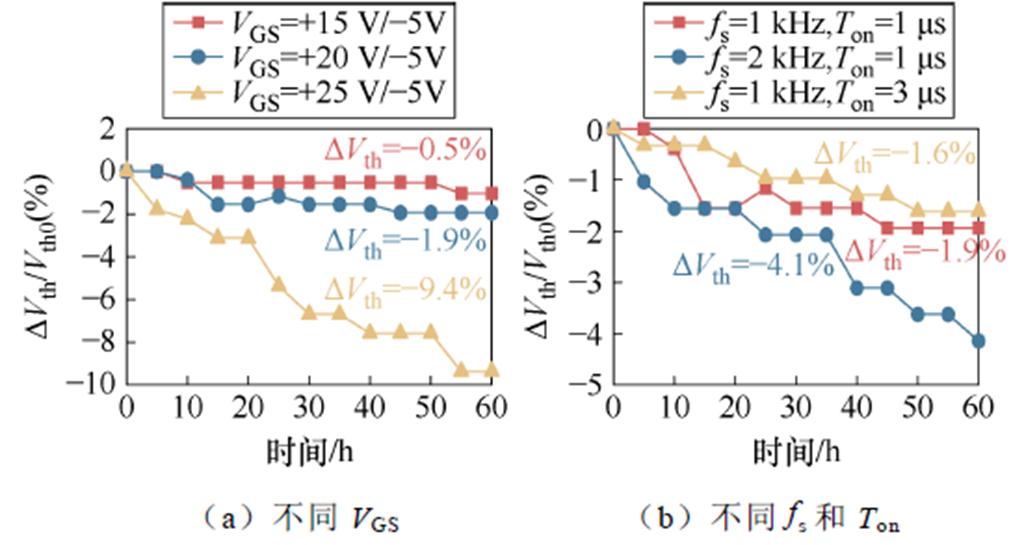

开展不同条件下的栅极开关测试,以研究栅极电压和开关过程的影响。不同VGS下MOS B的Vth变化在图20a中给出。随VGS的增加,相同应力时间下DVth幅值逐渐增加。此外,较低VGS(+15 V/-5 V)条件下Vth基本不变。相比MOS A,MOS B较大的参数退化与超出额定范围的VGS相关。高电场加速了氧化物电荷增加,并加速了器件参数退化。

图20 不同栅极开关应力下MOS B Vth的变化

Fig.20 Changes of MOS B Vth under different gate switching stresses

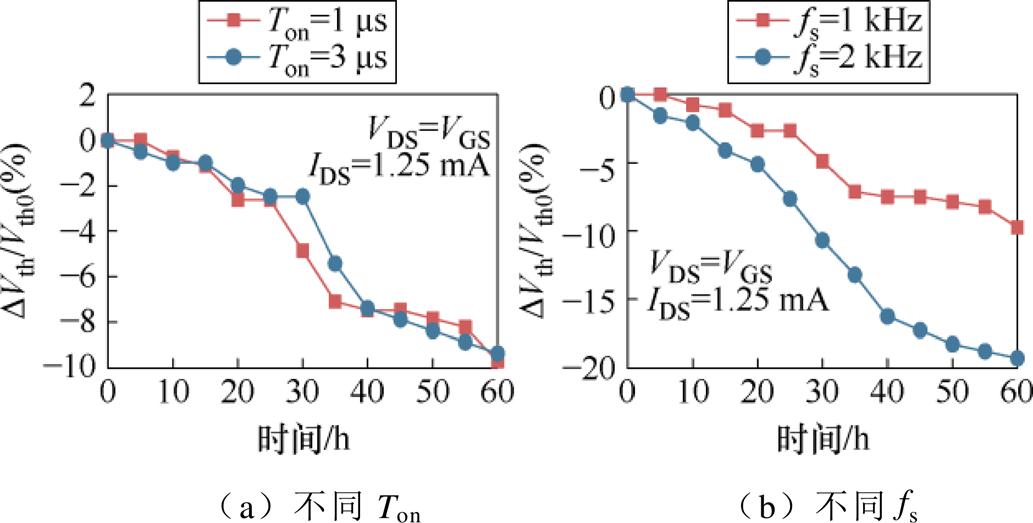

图20b给出了MOS B在不同开关频率和不同占空比下Vth的变化。由于损耗极小,被测器件结温基本保持一致。在相同应力时间下,fs=2 kHz的器件DVth幅值远大于fs=1 kHz器件所得结果,而Ton=3 ms的器件参数退化幅值与Ton=1 ms器件基本一致。基于上述结果,可知MOS B的参数退化主要与开关过程相关[30],而受占空比影响较小。

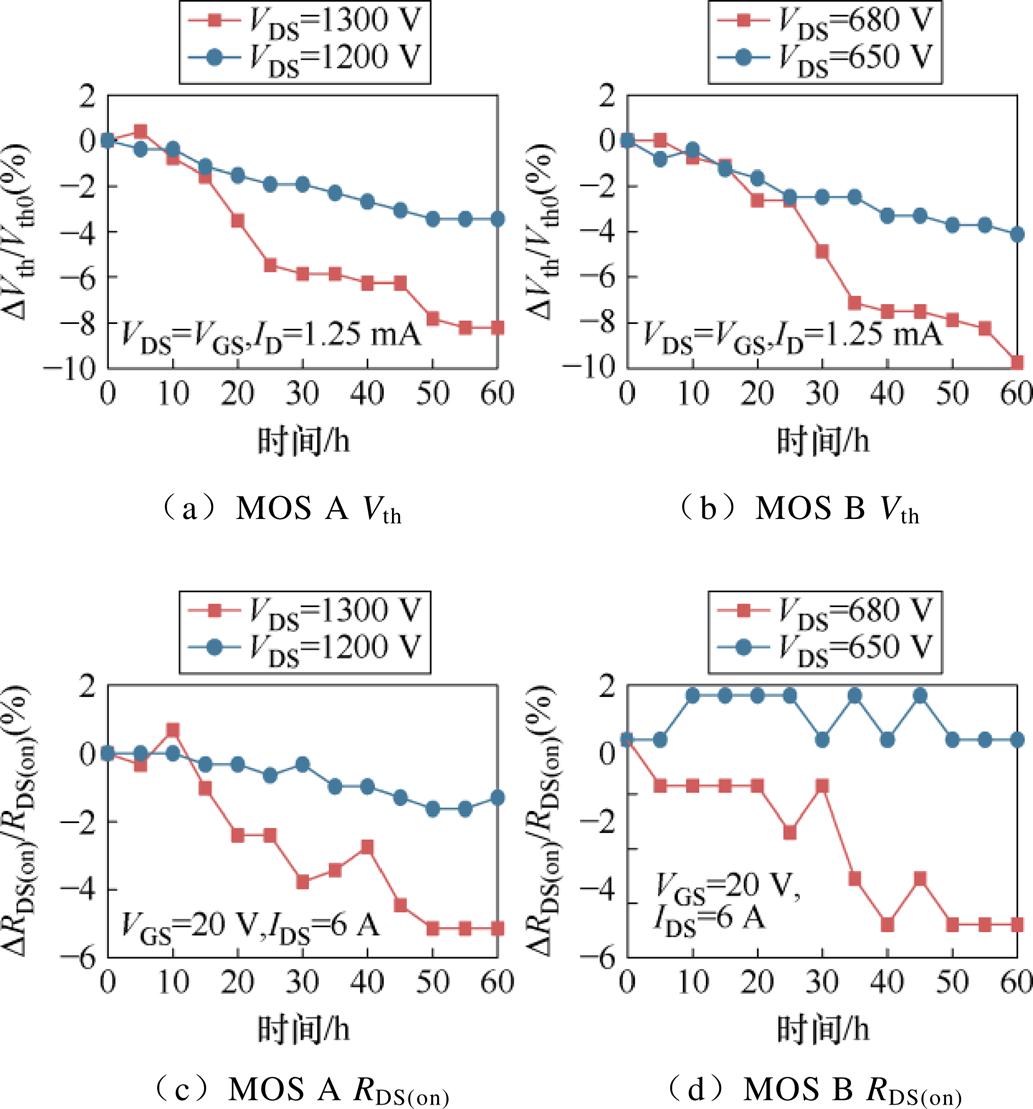

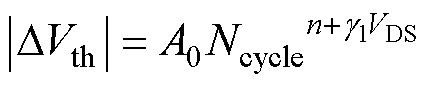

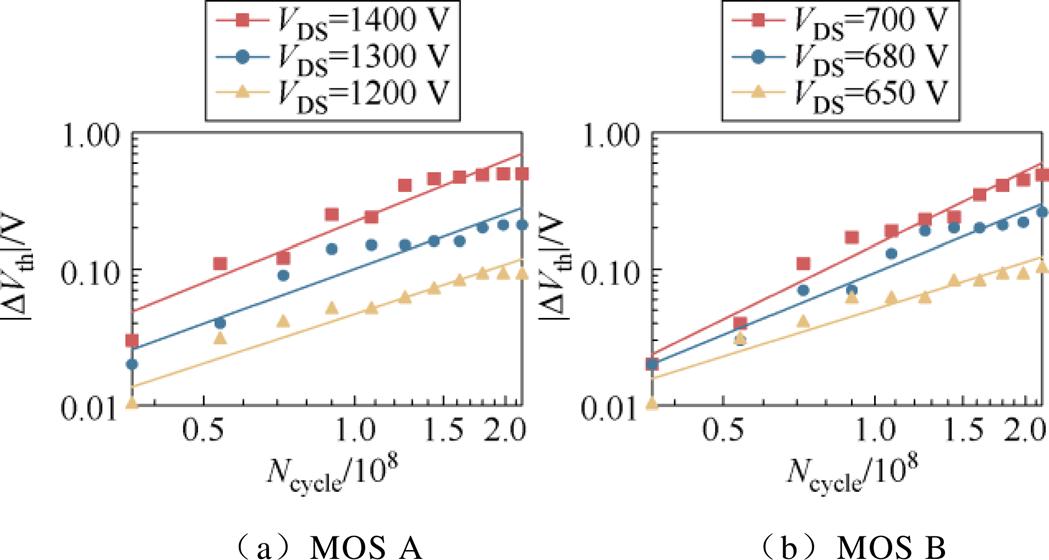

开展不同VDS下的过电压开关应力测试,以明确VDS幅值对参数退化的影响。基于实际击穿电压和数据手册选取测试VDS,即75%VBR(DSS)和额定最大电压。对于MOS A,上述电压分别为1 300 V和1 200 V,对于MOS B,则为680 V和650 V。

器件Vth和RDS(on)的变化如图21所示,二者均随应力时间增加而降低。结合80%VBR(DSS)条件下的测试结果进行对比,可知随着VDS的降低,器件Vth退化幅值减小。这一现象表明:随着VDS电压下降,栅氧化层与沟道电场降低,热载流子对氧化物电荷的影响降低。而栅氧化层退化速度的降低,导致了Vth和RDS(on)变化的减小。

图21 不同VDS过电压开关应力下Vth和RDS(on)的变化

Fig.21 Changes of Vth and RDS(on) under overvoltage switching stresses with different VDS

在不同开关频率和导通时间下对MOS B进行测试,如图22所示。通过调节电感L,使iL(max)基本一致。与栅极开关测试中所得结果相似,不同Ton下器件参数退化幅值基本一致,且DVth幅值随开关频率的增加而增加。上述结果证明器件参数退化基本不受占空比影响,而主要与开关过程,特别是开关次数相关。

图22 不同过电压开关应力下MOS B Vth的变化

Fig.22 Changes of MOS B Vth under different overvoltage switching stresses

结合不同测试条件下的参数变化特征可知,参数退化主要与开关过程中动态应力导致的栅氧化层退化相关。且随VGS、VDS及开关频率增加,Vth、RDS(on)的退化速度逐渐增加。同时,单一静态过电压应力或栅极开关应力产生的参数退化幅值远小于过电压开关应力所得结果。

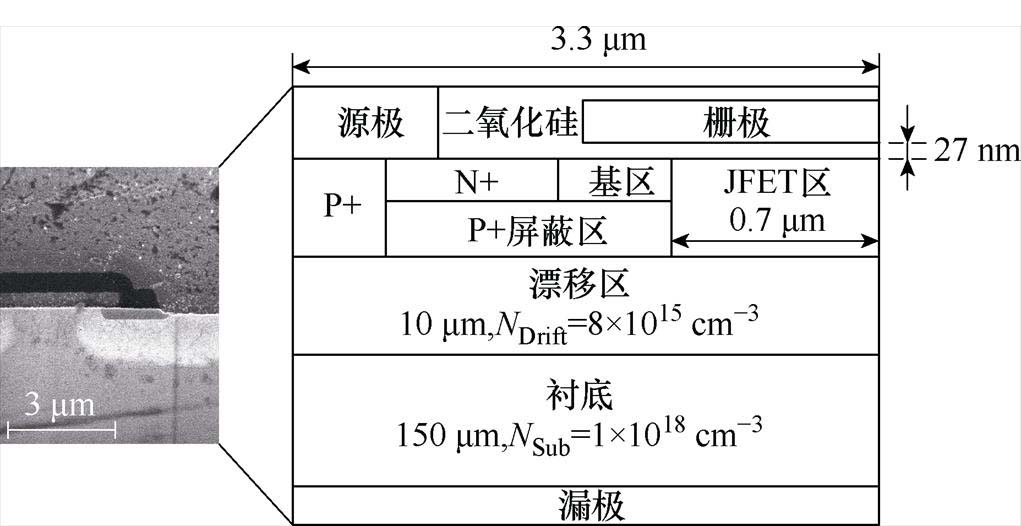

为了进一步分析SiC MOSFET在过电压开关应力下的参数退化机制,研究动态的VGS、VDS及IDS应力对器件栅氧化层及其参数的影响,通过TCAD对MOS A进行电、热应力仿真。基于扫描电子显微镜(Scanning Electron Microscope, SEM)所得的器件内部结构搭建器件TCAD仿真模型,如图23所示。同时,模型结构与掺杂浓度等参数也参考了相关研究[15, 28]。器件的N+区和JFET区的掺杂浓度分别为1×1020 cm-3和3×1016 cm-3。此外,沟道长度为0.5 mm,栅氧化层厚度为27 nm。模型的参数基于器件的数据手册与实际测量结果进行了校准,使其击穿电压V(BR)DSS、Vth和RDS(on)等参数与被测器件基本一致。

图23 1 200 V SiC MOSFET的内部结构(SEM图像)与TCAD仿真模型

Fig.23 Internal structure (SEM image) and TCAD simulation model of 1 200 V SiC MOSFET

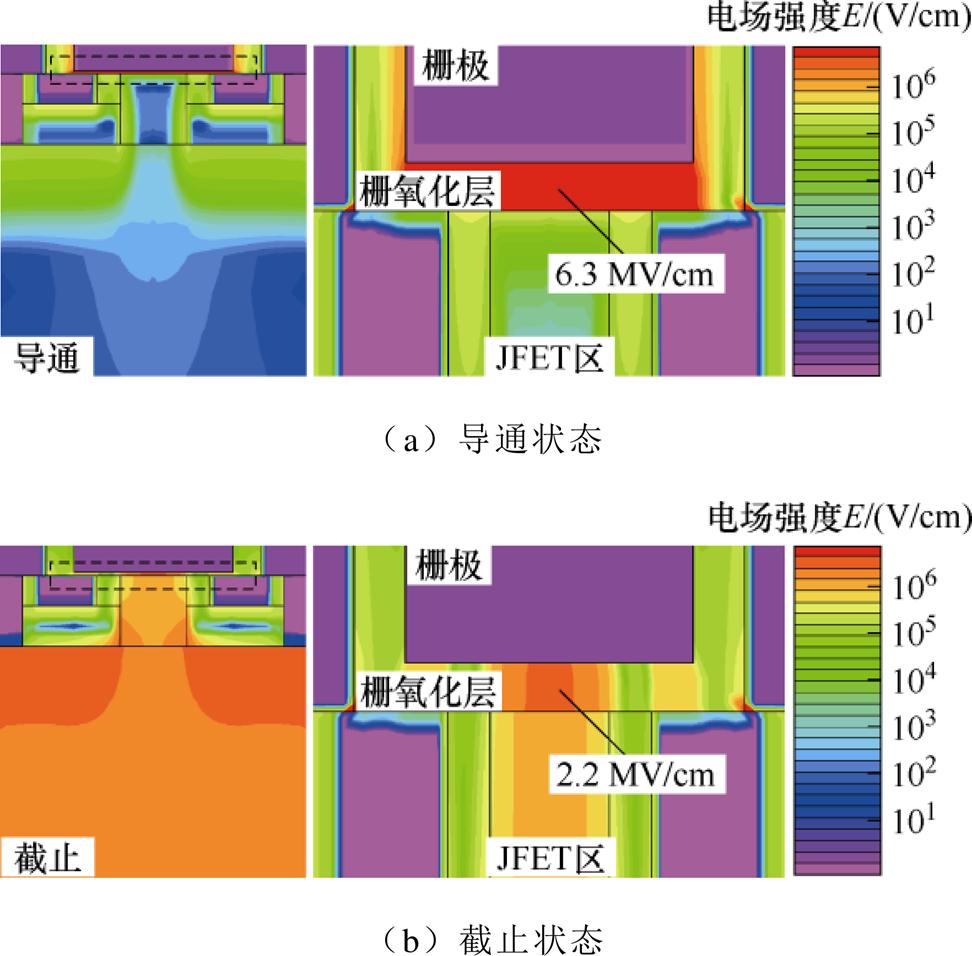

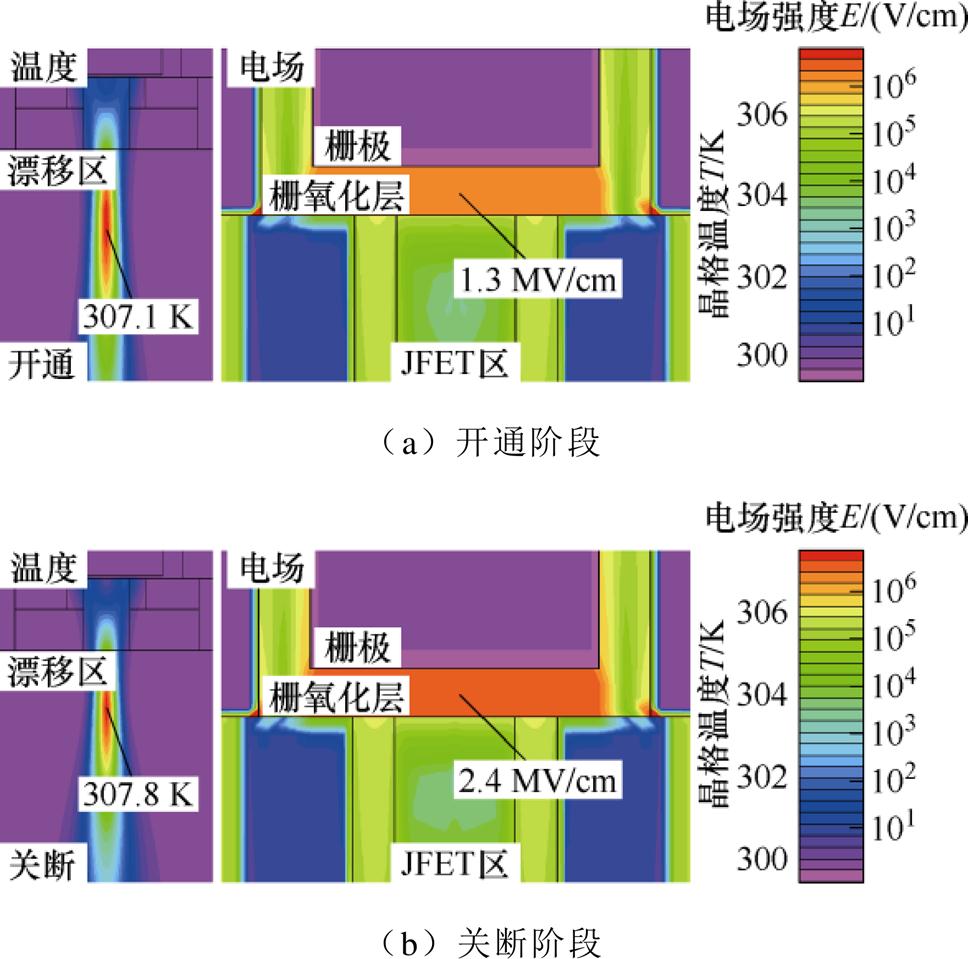

图24和图25分别给出了静态和动态条件下的SiC MOSFET内部的电场分布。在开关过程的不同阶段,器件的栅氧化层都承受最高的电场应力,这与栅氧化层退化主要受电场的影响相对应[29]。具体而言,除栅氧化层边界外,器件内部最高电场强度均位于JFET区域上方的栅氧化层部分,并沿着沟道向器件两侧逐渐降低。随器件工作状态的变化,其最高电场强度在1.3~6.3 MV/cm之间波动。较高的沟道电场加速载流子,并使其注入器件栅氧化层形成氧化物陷阱电荷,同时通过碰撞电离产生界面陷阱电荷。当氧化物电荷的变化整体等效为正电荷增加时,器件阈值电压Vth降低,如式(4)所示。同时,氧化物电荷也会影响器件RDS(on)、IGSS与开关特性等参数。

图24 导通和截止状态下器件内部电场

Fig.24 Simulated electric fields of SiC MOSFET in on and off states

图25 开通和关断过程中器件内部温度和电场

Fig.25 Simulated temperature and electric field of SiC MOSFET in turn-on and turn-off stages

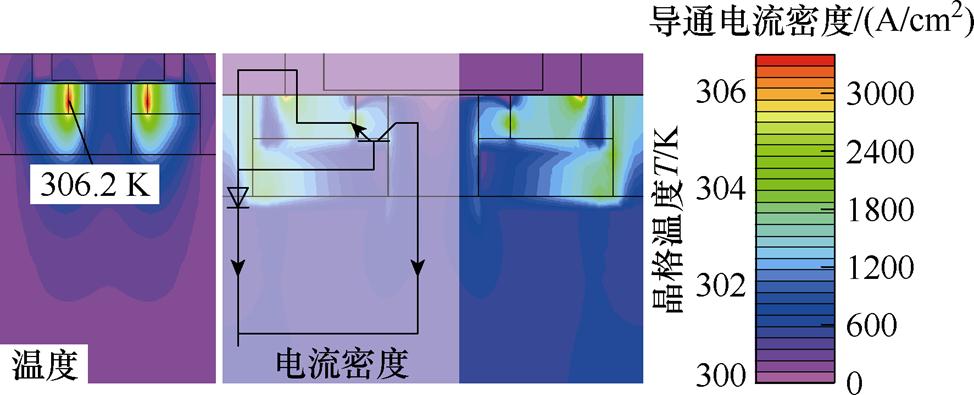

对于温度应力而言,仿真使用漏极外侧作为散热器接触面,并设置该接触面温度恒定为300 K,即器件始终散热良好。在导通和截止阶段,器件内部温度基本保持一致,且不存在局部高温。而开通和关断过程中器件内部温度如图25所示,器件最高晶格温度为307.8 K,出现在JFET区下方的Drift区,而栅氧化层温度基本不变。因此,器件栅氧化层的退化与高温关联较小。

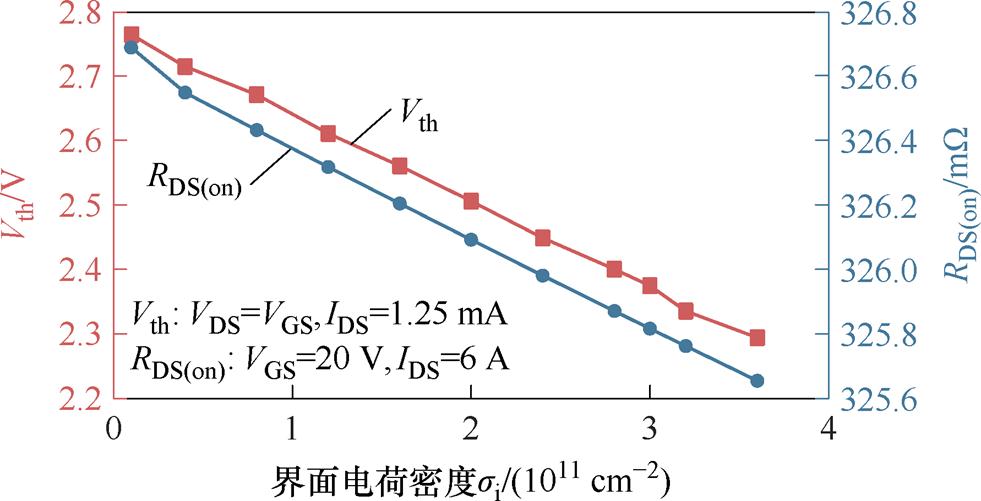

界面电荷密度si的变化与Vth、RDS(on)之间的关系如图26所示。假设栅氧化层始终存在正电荷QOx且主要位于SiO2/SiC界面,则界面电荷密度si的增加与氧化物电荷增加相对应[28]。随si增加,阈值电压Vth和导通电阻RDS(on)逐渐减小,二者退化趋势与测试结果相对应。上述结果验证了器件参数退化与氧化物电荷积累相关联。

图27展示了S1体二极管导通时的温度与电流密度分布。基于电流密度分布可知,器件内部有两个主要电流的路径:第一个是由P+区、P+屏蔽区和漂移区构成的PN结二极管;另一个是由基区、N+区和JFET区构成的NPN寄生晶体管[30]。第三象限导通损耗主要产生于器件晶体管部分,即Base区与N+区边界,而非器件内部的导通电阻或二极管正向压降。可知器件内部最高温度为306.2 K,表明热应力对其封装影响较小。结合图10中给出的参数退化结果可知,因堆垛层错扩大造成的电流路径减小是VSD增加的主要原因。

图26 Vth和RDS(on)随界面电荷密度si增加的变化

Fig.26 Changes of Vth and RDS(on) with increasing interface charge density

图27 SiC MOSFET第三象限工作时的内部温度与导通电流密度

Fig.27 Simulated temperature and current density of SiC MOSFET operating in third quadrant

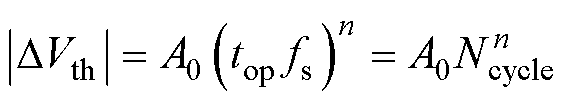

栅极开关应力下,幂律模型较好地描述了阈值电压变化量DVth与开关次数Ncylce之间的关联[31]。

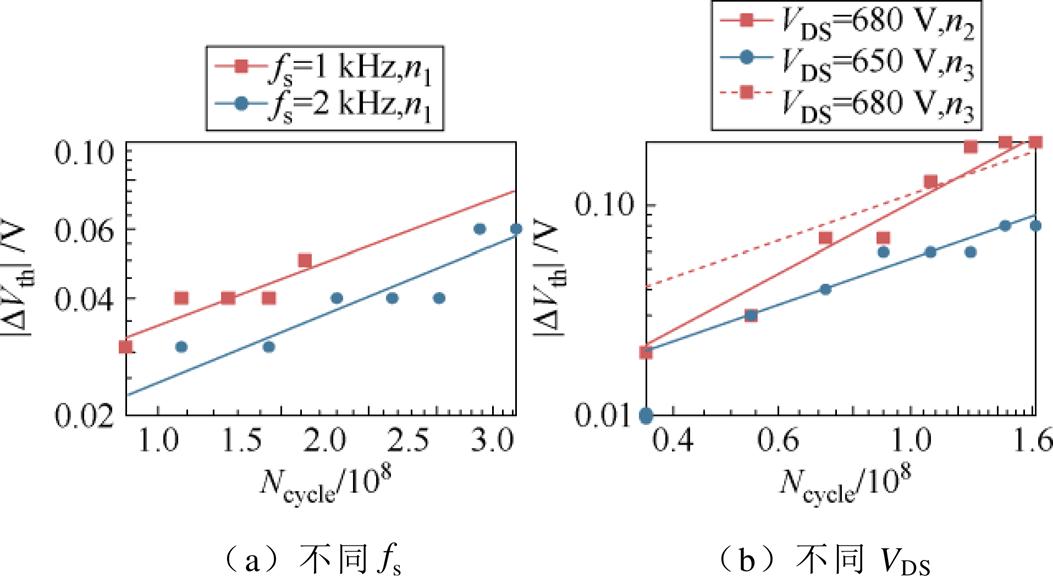

(14)

(14)

式中,A0和n为拟合所得常数;top为栅极开关应力时长。不同工况下幂律模型的拟合结果如图28所示。当VDS相同时,不同fs下的Vth退化结果可以使用相同幂指数n1较好的拟合;但VDS不同条件下的测试结果对应的幂指数n2和n3呈现较大差异。该差异的主要原因是幂律模型未考虑VDS对器件电场及栅氧化层退化的影响,进而无法准确描述不同VDS下的Vth退化。

与幂律模型相比,考虑栅氧化层退化机制的E模型描述了静态栅氧化层电场下的器件击穿时间tbd。但是基于3.1节可知,静态过电压应力下的参数退化远小于过电压开关应力,表明E模型对开关工况下的器件退化过程描述同样存在较大的偏差。

图28 MOS B 的阈值电压退化及幂律模型

Fig.28 Changes of MOS B Vth and power law model

(15)

(15)

式中,A为材料相关系数;DH0为活化能;g 为与器件结构及工况相关的常数;EOx为栅氧化层的电场强度。

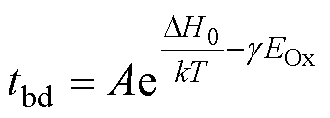

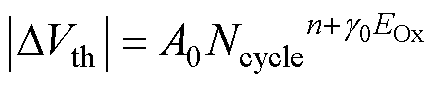

为了准确描述开关过程及VDS过电压应力对栅氧化层的影响,合并幂律模型和E模型并对测试结果进行分析。以DVth为器件退化指标,在式(14)的幂指数中引入电场加速因子g0EOx,可得

(16)

(16)

考虑到模型主要基于幂指数n描述开关过程对Vth退化规律的影响,为了进一步简化模型参数计算过程,将开关过程中动态的EOx简化为正比于静态VDS的恒定值,即EOx≈A2VDS。则式(16)可以基于VDS表示为

(17)

(17)

式中,g1为描述VDS电压应力影响的参数,g1=A2g0。

过电压开关应力下MOS A和MOS B的Vth退化结果及对应的模型参数分别如图29所示和见表2。对比MOS A和MOS B的退化结果可知,随着VDS增加,MOS B参数退化趋势的变化大于MOS A,即g1(MOS B)>g1(MOS A)。此外,对比不同电压下的Vth退化规律及模型参数可知,更高的VDS加速了器件的Vth退化,对应模型参数g1>0。需要注意的是,由于Vth的增加或降低方向受到了器件结构与实际工况的影响[32],模型未对这一特性进行描述。

如图29a所示,随着开关次数增加,MOS A的Vth的退化呈现不同的模式[31]。当VDS=1 400 V且Ncycle>1.5×108时,DVth的变化趋势逐渐平稳,对应模型参数n的减小。而更高的VDS加速了这一退化特征变化的产生,即模型参数n显著变化对应的开关次数Ncycle阈值与VDS相关。上述结果表明,当采用单一静态测试或栅极开关测试时,所得退化模式与模型参数可能与过电压开关工况下所得的结果存在较大差异。因此,需要采用过电压开关应力测试,为器件在过电压工况下的栅氧化层退化及参数变化提供更准确的退化模型。

图29 不同VDS下Vth变化与改进后的退化模型

Fig.29 Changes of Vth under different VDS and improved degradation model

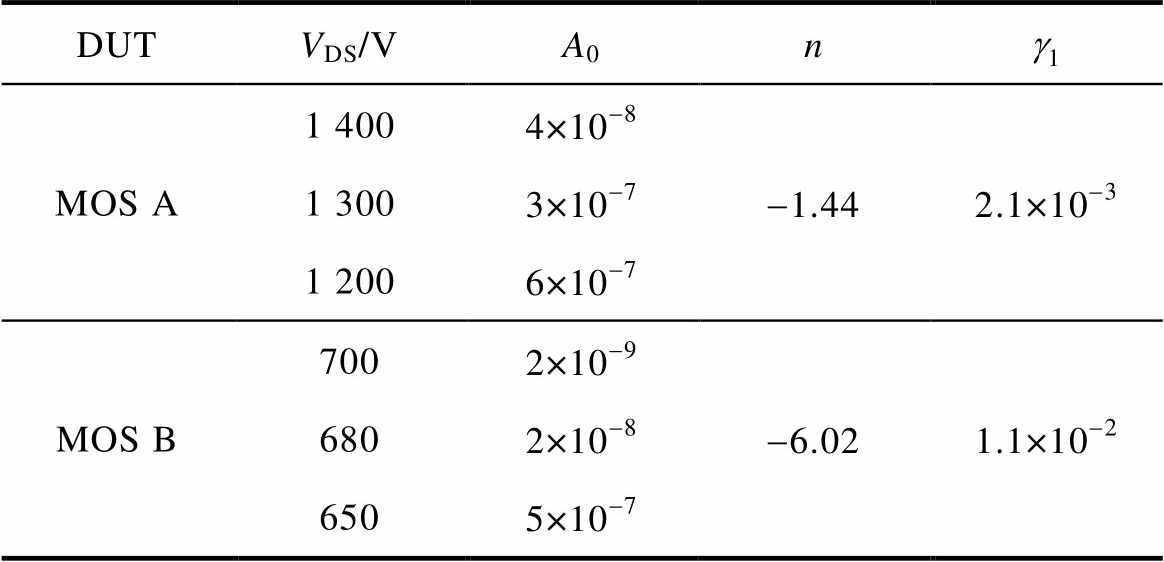

表2 不同VDS下的退化模型参数

Tab.2 Degradation model parameters under different VDS

DUTVDS/VA0ng1 MOS A1 4004×10-8-1.442.1×10-3 1 3003×10-7 1 2006×10-7 MOS B7002×10-9-6.021.1×10-2 6802×10-8 6505×10-7

本文研究了过电压硬开关工况下SiC MOSFET的参数退化规律。对多工况下器件的静态和动态特性变化进行分析,以研究其退化机制。主要结论概括如下:

1)过电压开关应力造成了器件的栅氧化层退化。经过60 h开关应力,器件的Vth和RDS(on)下降、IGSS和IDSS增加。同时,由于Vth和跨导变化,器件开关损耗等动态特性也产生显著变化。TCAD仿真表明,高电场引起的热载流子注入是栅氧化层退化的主要机制。对于工作在第三象限的器件,则存在由堆垛层错扩大引起的VSD增加。

2)动态电压、电流应力是器件参数加速退化的主要原因。静态过电压测试和栅极开关测试中,器件参数退化幅值远小于过电压开关测试所得结果。此外,受器件栅极应力及跨导变化不同的影响,两种被测器件呈现不同的静态和动态特性退化规律。

3)器件Vth的退化规律主要与开关次数和电压应力幅值相关。VDS显著加速了器件的Vth退化,而开关频率和占空比产生的影响较小。

研究表明,过电压开关应力下器件参数退化与传统测试方法下存在较大差异,有必要对该工况下的器件可靠性进行研究。未来拟研究不同电流及温度影响下的器件退化规律,以得出更完善的参数退化模型。

参考文献

[1] 任鹏, 涂春鸣, 侯玉超, 等. 基于Si和SiC器件的混合型级联多电平变换器及其调控优化方法[J]. 电工技术学报, 2023, 38(18): 5017-5028.

Ren Peng, Tu Chunming, Hou Yuchao, et al. Research on a hybrid cascaded multilevel converter based on Si and SiC device and its control optimization method[J]. Transactions of China Electrotechnical Society, 2023, 38(18): 5017-5028.

[2] 徐浩东, 罗嗣勇, 毕闯, 等. 基于SiC MOSFET同步Buck DC-DC变换器的宽频混合EMI滤波器设计[J]. 电工技术学报, 39(10): 3060-3069.

Xu Haodong, Luo Siyong, Bi Chuang, et al. Design of broadband hybrid EMI filter in synchronous Buck DC-DC converter with SiC MOSFETs[J]. Transa- ctions of China Electrotechnical Society, 2024, 39(10): 3060-3069.

[3] 胡嘉豪, 王英伦, 代豪豪, 等. SiC MOSFET 器件栅氧可靠性研究综述[J]. 电源学报, 2024, 22(4): 1-11.

Hu Jiahao, Wang Yinglun, Dai Haohao, et al. Review on gate oxide reliability of SiC MOSFET devices[J]. Journal of Power Supply, 2024, 22(4): 1-11.

[4] 龙海洋, 李辉, 王晓, 等. 纳米银烧结压接封装IGBT的长期可靠性研究[J]. 中国电机工程学报, 2020, 40(18): 5779-5787.

Long Haiyang, Li Hui, Wang Xiao, et al. Study on the long term reliability of nanosilver sintered press pack IGBT[J]. Proceedings of the CSEE, 2020, 40(18): 5779-5787.

[5] 王来利, 赵成, 张彤宇, 等. 碳化硅功率模块封装技术综述[J]. 电工技术学报, 2023, 38(18): 4947- 4962.

Wang Laili, Zhao Cheng, Zhang Tongyu, et al. Review of packaging technology for silicon carbide power modules[J]. Transactions of China Electro- technical Society, 2023, 38(18): 4947-4962.

[6] Jouha W, Masmoudi M, El Oualkadi A, et al. Physical study of SiC power MOSFETs towards HTRB stress based on C-V characteristics[J]. IEEE Transactions on Device and Materials Reliability, 2020, 20(3): 506- 511.

[7] Hayashi S I, Wada K. Accelerated aging for gate oxide of SiC MOSFETs under continuous switching conditions by applying advanced HTGB test[J]. Microelectronics Reliability, 2021, 126: 114213.

[8] 郑丹, 宁圃奇, 仇志杰, 等. 基于老化补偿的功率模块全生命周期在线结温监测方法[J]. 电工技术学报, 2024, 39(12): 3705-3717.

Zheng Dan, Ning Puqi, Qiu Zhijie, et al. Full life-cycle online junction temperature monitoring of power module based on aging compensation[J]. Transactions of China Electrotechnical Society, 2024, 39(12): 3705-3717.

[9] Li Yang, Liu Jinjun, Zhang Yan, et al. IGBT long- term forward bias safe operating area calibration considering aging-caused shrinkage[C]//2022 IEEE International Power Electronics and Application Conference and Exposition (PEAC), Guangzhou, Guangdong, China, 2022: 903-908.

[10] 徐晓筱. 高压碳化硅雪崩耐量测试[D]. 杭州: 浙江大学, 2020.

Xu Xiaoxiao. Avalanche tolerance test of high voltage silicon carbide[D]. Hangzhou: Zhejiang University, 2020.

[11] Ouyang Wenyuan, Sun Pengju, Xie Minghang, et al. A fast short-circuit protection method for SiC MOSFET based on indirect power dissipation level[J]. IEEE Transactions on Power Electronics, 2022, 37(8): 8825-8829.

[12] 文阳, 杨媛, 宁红英, 等. SiC MOSFET短路保护技术综述[J]. 电工技术学报, 2022, 37(10): 2538-2548.

Wen Yang, Yang Yuan, Ning Hongying, et al. Review on short-circuit protection technology of SiC MOSFET[J]. Transactions of China Electrotechnical Society, 2022, 37(10): 2538-2548.

[13] Fayyaz A, Castellazzi A. High temperature pulsed- gate robustness testing of SiC power MOSFETs[J]. Microelectronics Reliability, 2015, 55(9/10): 1724- 1728.

[14] Kozak J P, Zhang Ruizhe, Liu Jingcun, et al. Degradation of SiC MOSFETs under high-bias switching events[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2022, 10(5): 5027-5038.

[15] Jiang Xi, Wang Jun, Chen Jianjun, et al. Investigation on degradation of SiC MOSFET under accelerated stress in a PFC converter[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2021, 9(4): 4299-4310.

[16] Cai Yumeng, Sun Peng, Chen Cong, et al. Investi- gation on gate oxide degradation of SiC MOSFET in switching operation[J]. IEEE Transactions on Power Electronics, 2024, 39(8): 9565-9578.

[17] 王莉娜, 马浩博, 袁恺, 等. SiC MOSFET半桥电路开关瞬态过电流、过电压建模与影响因素分析[J]. 电工技术学报, 2020, 35(17): 3652-3665.

Wang Lina, Ma Haobo, Yuan Kai, et al. Modeling and influencing factor analysis of SiC MOSFET half- bridge circuit switching transient overcurrent and overvoltage[J]. Transactions of China Electrotech- nical Society, 2020, 35(17): 3652-3665.

[18] Guo Chunsheng, Cui Shaoxiong, Li Yumeng, et al. Study of the influence of different gate oxide traps on threshold voltage drift of SiC MOSFET based on transient current[J]. IEEE Transactions on Power Electronics, 2024, 39(8): 9629-9637.

[19] Cai Jinhao, Peng Yongjie, Fan Jianfeng, et al. The reverse bias reliability of SiC MOSFET under different conditions and failure analysis[C]//2024 25th International Conference on Electronic Packaging Technology (ICEPT), Tianjin, China, 2024: 1-5.

[20] Mengotti E, Bianda E, Baumann D, et al. Industrial approach to the chip and package reliability of SiC MOSFETs (invited)[C]//2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2023: 1-6.

[21] Ren Min, Liang Shiqi, Zhou Tong, et al. Gate oxide failure mechanisms of SiC MOSFET related to electro-thermomechanical stress under HTRB and HTGB test[C]//2024 36th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Bremen, Germany, 2024: 208-211.

[22] Mao Hua, Qiu Guanqun, Jiang Xiaofeng, et al. Investigation on the degradations of parallel- connected 4H-SiC MOSFETs under repetitive UIS stresses[J]. IEEE Transactions on Electron Devices, 2022, 69(2): 650-657.

[23] Deng Xiaochuan, Huang Wei, Li Xu, et al. Investi- gation of failure mechanisms of 1200 V rated trench SiC MOSFETs under repetitive avalanche stress[J]. IEEE Transactions on Power Electronics, 2022, 37(9): 10562-10571.

[24] 李鑫, 罗毅飞, 史泽南, 等. 一种基于物理的SiC MOSFET改进电路模型[J]. 电工技术学报, 2022, 37(20): 5214-5226.

Li Xin, Luo Yifei, Shi Zenan, et al. An improved physics-based circuit model for SiC MOSFET[J]. Transactions of China Electrotechnical Society, 2022, 37(20): 5214-5226.

[25] Yang Liao, Bai Yun, Li Chengzhan, et al. Gate oxide instability of 4H-SiC p-channel MOSFET induced by AC stress at 200℃[J]. IEEE Transactions on Electron Devices, 2023, 70(1): 379-382.

[26] 崔曼, 胡震, 张腾飞, 等. 基于壳温信息的功率器件可靠性分析[J]. 电工技术学报, 2023, 38(24): 6760-6767.

Cui Man, Hu Zhen, Zhang Tengfei, et al. Reliability analysis of power device based on the case temperatures[J]. Transactions of China Electro- technical Society, 2023, 38(24): 6760-6767.

[27] Qiu Leshan, Bai Yun, Dong Zewei, et al. Degradation under low drain bias induced by heavy ion in SiC MOSFETs[J]. IEEE Transactions on Nuclear Science, 2024, 71(11): 2377-2385.

[28] Baliga B J. Fundamentals of Power Semiconductor Devices[M]. Cham: Springer International Publishing, 2019

[29] Karki U, González-Santini N S, Peng F Z. Effect of gate-oxide degradation on electrical parameters of silicon carbide MOSFETs[J]. IEEE Transactions on Electron Devices, 2020, 67(6): 2544-2552.

[30] Tang Lei, Jiang Huaping, Zhong Xiaohan, et al. Investigation into the third quadrant characteristics of silicon carbide MOSFET[J]. IEEE Transactions on Power Electronics, 2023, 38(1): 1155-1165.

[31] Salmen P, Feil M W, Waschneck K, et al. Gate- switching-stress test: electrical parameter stability of SiC MOSFETs in switching operation[J]. Micro- electronics Reliability, 2022, 135: 114575.

[32] Jiang Huaping, Qi Xiaowei, Qiu Guanqun, et al. A physical explanation of threshold voltage drift of SiC MOSFET induced by gate switching[J]. IEEE Transa- ctions on Power Electronics, 2022, 37(8): 8830-8834.

Abstract In practical converters, Silicon carbide (SiC) MOSFETs may experience short-term, repetitive overvoltage and hard-switching stresses that exceed their safe operating area (SOA). These stresses can result from uneven voltage distribution in series configurations and parasitic inductances. However, current SiC MOSFET reliability studies focus on the effects of long-term and static stress within the SOA on device parameters, and discrepancies exist between the predicted and actual device lifetimes. This paper investigates the degradation of device parameters under overvoltage and hard-switching conditions. Tests are performed on two SiC MOSFETs with different voltage ratings to analyze static and dynamic parameter changes. The degradation mechanisms of device parameters are clarified through static overvoltage and gate-switching tests.

Overvoltage and hard-switching tests at 80% of the actual breakdown voltage cause degradation of the gate oxide in the devices. After 60 hours of stress, the threshold voltage and on-resistance decrease, while the output and transfer characteristics shift to the left. Additionally, both gate leakage current and zero-gate-voltage drain current increase. For dynamic parameters, variations in transconductance and the Miller plateau voltage cause the two devices under test (DUTs) to exhibit different changes in switching characteristics. These characteristics mainly include turn-on and turn-off delay times and losses. Furthermore, in devices operating in the third quadrant, the expansion of stacking faults leads to an increase in the forward voltage drop of the body diode.

Tests under static overvoltage and gate-switching conditions show that device parameter degradation is primarily due to dynamic overvoltage and current stress. At the same drain-source voltage, degradation in static characteristics from static overvoltage stress is much smaller than that from overvoltage switching stress, with dynamic characteristics remaining largely unaffected. Similarly, parameter changes in the gate-switching stress test are significantly reduced. Gate-switching and overvoltage hard-switching stress tests at different voltages reveal that higher gate- and drain-source voltage accelerate parameter degradation. Tests conducted at varying on-state times and switching frequencies show that threshold voltage degradation is mainly related to the number of switching cycles, with minimal impact from switching frequency and on-state times.

Technology computer-aided design (TCAD) simulations verify the gate oxide degradation mechanism and analyze threshold voltage degradation. The electric field and temperature distribution in devices operating in the first quadrant show that the switching process accelerates gate oxide degradation. Changes in oxide charge simulate threshold voltage and on-resistance degradation. The temperature and current density distribution in devices operating in the third quadrant are also studied, confirming that parameter degradation is primarily due to semiconductor degradation, particularly stacking faults. A power-law model based on switching cycles is developed, incorporating the drain-source voltage to better describe the threshold voltage degradation under varying voltages. The accuracy of the degradation model is validated through experimental results under different operating conditions.

Overvoltage and hard-switching stress accelerate the degradation of SiC MOSFET parameters, such as threshold voltage and on-resistance. These changes are primarily attributed to gate oxide degradation, which is accelerated by hot carrier injection under high electric fields. The drain-source voltage and the number of switching cycles influence threshold voltage variation. This research provides theoretical support for device applications under critical conditions and for selecting margins in converter design.

Keywords:Accelerated life testing, SiC MOSFET, gate oxide degradation, hard switching

中图分类号:TM464

DOI: 10.19595/j.cnki.1000-6753.tces.241872

国家重点研发项目(2021YFB2601503)和国家自然科学基金项目(52177193)资助。

收稿日期 2024-10-21

改稿日期 2024-11-18

张 岩 男,1983年生,副教授,博士生导师,研究方向为电力电子器件及系统可靠性、分布式电源系统变流器建模及控制理论、高频高功率密度谐振变换器软开关拓扑及其数字控制技术等。

E-mail: zhangyanjtu@xjtu.edu.cn(通信作者)

薛少鹏 男,1998年生,博士研究生,研究方向为宽禁带功率半导体可靠性等。

E-mail: sp.xue@stu.xjtu.edu.cn

(编辑 陈 诚)