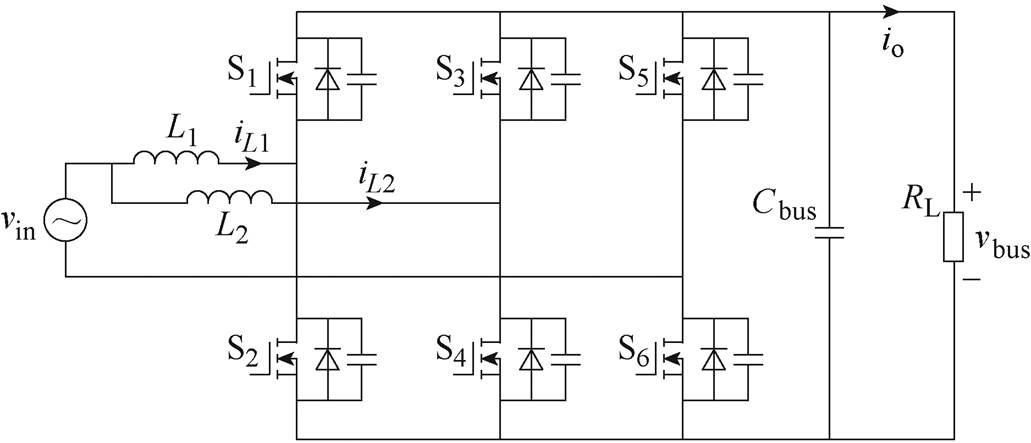

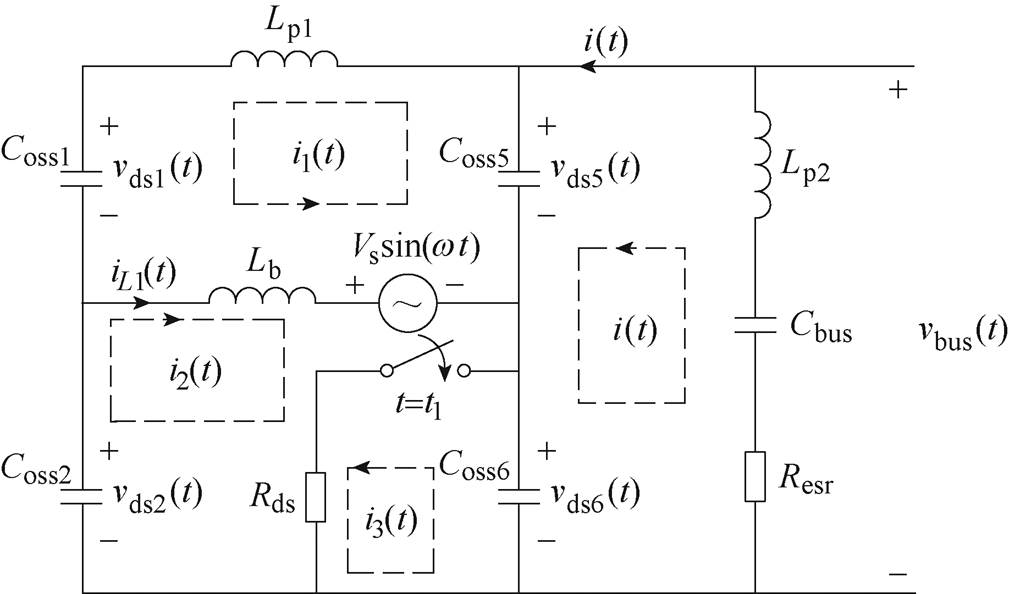

图1 交错并联图腾柱无桥PFC拓扑

Fig.1 Interleaved totem-pole bridgeless PFC topology

摘要 工作于临界电流模式下的图腾柱无桥功率因数校正(PFC)电路因其无整流桥损耗、电感体积小、易于实现软开关而得到广泛关注。然而,在输入电压过零点处,工频管之间的换相时刻,电感会与工频管的结电容产生谐振,相应地,电感电流和直流母线电压因此会存在高频振荡。电感电流振荡会加剧输入电流畸变程度,而母线电压上的高频尖峰由于振荡频率高,后级DC- DC变换器难以抑制而传递至负载,导致敏感负载无法正常工作。该文分析线性开关在主动栅极电路中抑制振荡的工作原理,基于线性开关的特性提出三电平驱动方式来抑制图腾柱无桥PFC换相谐振,降低输入电流总谐波畸变率(THD)的同时实现对直流母线的高频尖峰的抑制,在2 kW满载工况下,将输入电流THD降低1%,母线电压尖峰高频分量峰值由2.83 V减小至0.01 V以下。实验结果表明,该文所提出的三电平驱动方式可以有效抑制临界电流模式图腾柱无桥PFC的换相谐振。

关键词:图腾柱无桥功率因数校正(PFC) 换相谐振 线性开关 三电平驱动 母线电压尖峰抑制

离网电力电子变换装置的非线性特性会产生大量谐波,直接接入电网会污染电力环境,影响电网的安全运行。故许多国家和国际组织对用户设备在不同功率等级下的各次谐波电流进行了限值,如IEC/EN 61000-3-2、IEC 555-2、GJB-181B等标 准[1-2]。为了减小输入电流谐波,提高功率因数,需要在电网侧和后级DC-DC变换器之间加入功率因数校正(Power Factor Correction, PFC)电路。

图腾柱无桥PFC因为不存在整流桥,相比传统Boost PFC在每个开关周期中少流经一个功率管,具有较小的通态损耗。临界导通模式(Critical Conduction Mode, CRM)的图腾柱无桥PFC相较连续导通模式(Continuous Conduction Mode, CCM)可以实现零电压开通(Zero Voltage Switching, ZVS),克服了CCM下硬开关损耗大的问题,提高了工作频率,减小了电感体积,适用于中小功率的应用场合[3-4]。为了提升功率等级,常采用两相交错并联的PFC,通过一定的控制策略实现电感电流移相,抵消输入电流纹波,减小输入电流总谐波畸变率(Total Harmonics Distortion, THD)[5]。交错并联的图腾柱无桥PFC拓扑如图1所示。

同时以碳化硅(Silicon Carbide, SiC)和氮化镓(Gallium Nitride, GaN)为代表的第三代宽禁带半导体器件的广泛应用,使得电力电子变换器可以在更高的电压、温度和频率下稳定高效地工作[6-7]。但是与高压高频的开关应用相伴的则是更高的电压电流变化率(dv/dt和di/dt),由此产生的高电磁干扰(Electromagnetic Interference, EMI)、串扰、振荡等一系列问题影响了SiC MOSFET的开关性能,增大了损耗,并且会影响外部电路的正常工作[8-11]。CRM图腾柱无桥PFC工频桥臂开关切换的过程中,电路中的电感会与母线电容以及开关管输出结电容发生谐振,导致电感电流换相处和母线电压的二次纹波过零点产生较大的振荡尖峰。前级滤波器无法完全滤除电感电流换相处的尖峰,因此尖峰同样会对输入电流产生影响,导致其THD增大。文献[12]考虑了软硬件信号延时造成的输入电流畸变,提出了零电流检测(Zero-Current-Detection, ZCD)延迟补偿控制策略来减小电流THD,但实验结果中电感电流在二倍工频换相处的尖峰仍然存在,输入电流在过零处的畸变因此加剧。同时由于母线电压尖峰为高频分量且会叠加在母线电压的二次纹波之上,将直接传导给后级的DC-DC变换器。带宽的大小会影响系统动态响应速度,通常的DC-DC变换器带宽设计在开关频率的10%~20%之间[13],故无法对该高频噪声进行有效的抑制。

图1 交错并联图腾柱无桥PFC拓扑

Fig.1 Interleaved totem-pole bridgeless PFC topology

目前,针对上述开关器件动作带来的EMI、串扰、振荡等常见问题的解决方案,主要集中于优化MOSFET的驱动电路上,即采用主动栅极驱动(Active- Gate-Driver, AGD)电路。MOSFET工作在开关状态下时,在截止区和可变电阻区之间来回切换,切换过程中会经过线性区,此时通过改变栅极电阻[14-17]、多电平切换[18-20]等控制策略,可以改变传统驱动电路的工作方式,增大开关瞬间的阻尼,优化开关轨迹,克服高dv/dt和di/dt对电路产生的不利影响。

文献[17]针对低于10 ns开关瞬变时间的高速氮化镓功率器件,设计了一款可编程主动栅极驱动器,在开关瞬态期间可激活在0.12~64 W 之间几乎任意序列的栅极电阻。它的主动栅极驱动控制带宽足够高,足以实现氮化镓器件在开关过程中的轨迹优化。但是该驱动器最大只能实现5 V供电,无法满足SiC MOSFET通常所需的驱动电压要求。针对这个问题,文献[20]提出一种多级驱动拓扑,通过4个栅极驱动串联,在SiC MOSFET开关瞬间提供不同电压等级的驱动信号,可以在ns级别内优化开关轨迹。但是由于驱动电路结构复杂,若同时打开所有栅极驱动,栅源极的电压可能会由于AGD输出阻抗的不同而偏离预期,降低驱动的可靠性,且对PCB布局有极高的要求,最终实验结果相比传统驱动方案只将输出电压的扰动降低了30%。文献[18]提出一种自适应AGD策略,可根据SiC器件在不同工作情况下自动生成中间驱动电平,但是其只对关断瞬态进行了设计,且驱动电压在进行电平切换时存在很大的振荡,降低了控制精度和可靠性。文献[19]也是在ns级别实现多电平的驱动控制,但对于振荡的抑制也很有限。

对于CRM图腾柱无桥PFC工频换相谐振引起的电感电流和母线电压尖峰问题,不需要在ns数量级进行控制,且为了减小母线电压高频尖峰对后级负载的影响,需要将振荡抑制在较低的范围内。针对以上分析,结合线性开关在AGD的应用原理,本文提出了三电平混合驱动的控制策略,利用线性开关独特的电气性能在工频管开通的瞬态过程中减缓驱动电压对栅漏极电容的充电速度,优化开关轨迹、减小输入电流畸变、抑制母线电压尖峰。并将其和传统增大栅极电阻的方法进行对比,从损耗和控制精度等角度分析,最后选取三电平混合驱动控制作为最优的换相谐振方法。最终,搭建了一台2 kW的交错并联图腾柱无桥PFC样机,验证所提控制策略的有效性。

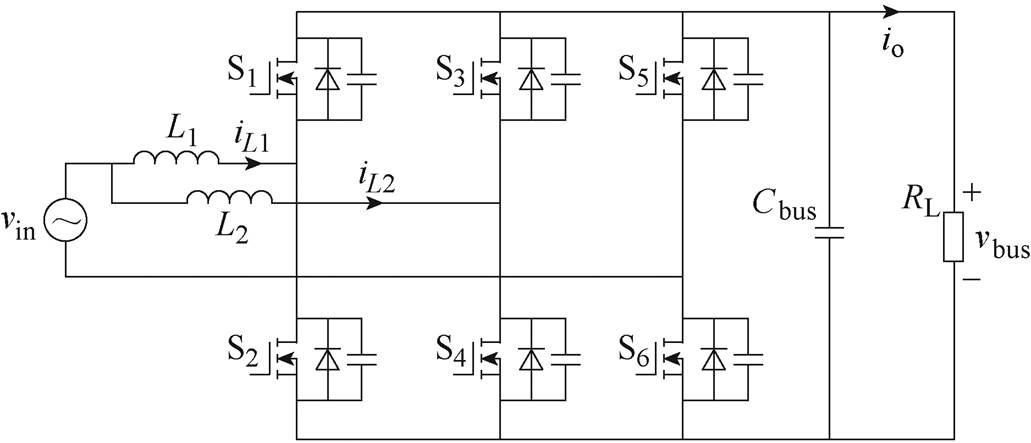

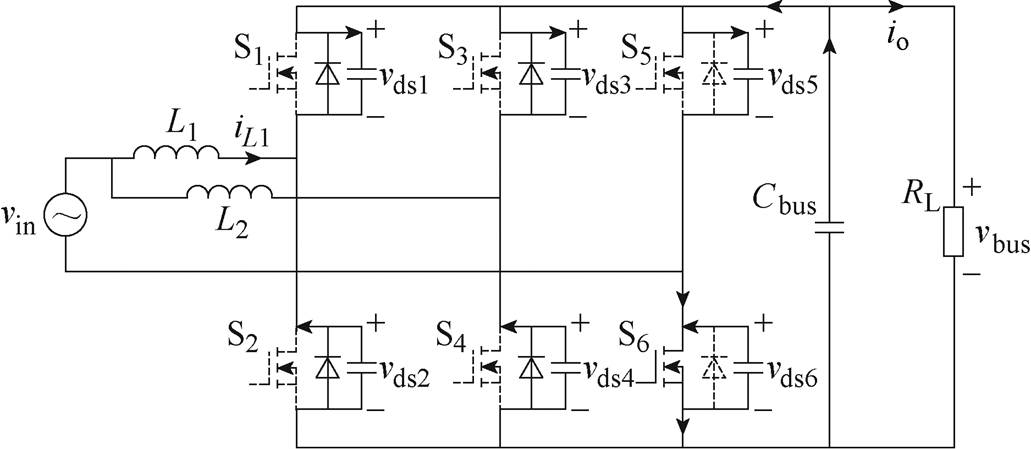

在存在桥臂切换的变换器中为了防止开关管直通造成短路,会在互补管子的驱动信号之间设置一段死区时间。交错并联的CRM图腾柱无桥PFC变换器在死区结束的瞬间,由于线路中寄生电感和器件相关寄生参数之间发生谐振,较高的dv/dt和di/dt会对电感电流和母线电压产生影响。t1时刻开通工频管S6电路如图2所示。电感电流和母线电压尖峰示意图如图3所示。

以图2所示换相情况为例,图中,vin为输入交流电压,S1~S4为高频开关管,S5、S6为工频管,L1、L2为升压电感,Cbus为输出母线电容,vbus为母线电压,iL1和io分别为电感L1流过的电流和输出电流,vds1~vds6为对应管的漏源极电压。t0时刻之前,输入电压小于零,S5保持导通,S6保持关断,在输入电压由负到正过零点附近,高频管先于工频管关断,高频管全部关断后S5所在回路中几乎无电流,故t0时刻关断S5,电路中的电流向其寄生电容Coss充电极为缓慢,t0~t1死区期间工频管S5和S6的电压基本保持不变,不会产生谐振现象。t1时刻开通S6管,vds6迅速下降,此时电感电流iL1和母线电压vbus将由于谐振产生尖峰,其示意图如图3所示,其中vgs5和vgs6分别为工频管5、6的栅极驱动信号。电感电流尖峰流经前级EMI滤波器反射至输入侧导致输入电流THD加剧;母线电压尖峰高频分量叠加在二次纹波上,经过后级的DC-DC变换器施加于负载,将会影响一些敏感设备的正常工作,故需从源头上对该尖峰进行抑制。对于输入电压由正到负的换相情况,原理与上述分析类似。

图2 t1时刻开通工频管S6电路

Fig.2 Circuit of open power frequency S6 at t1 moment

图3 电感电流和母线电压尖峰示意图

Fig.3 Diagram of inductor current and DC bus voltage spike

为了分析S6开通后的瞬态过程,以L1所在电路为例,将未开通的开关管均等效为一个结电容Coss,将S6开通的瞬间等效为一个电阻Rds以并联形式接入其结电容Coss6,来模拟S6导通瞬间的阻尼效果。Lp1为回路杂散电感,Lp2为回路杂散电感和母线电容等效寄生电感之和,忽略负载对于母线电容的影响,图2可以等效成一个全响应电路,如图4所示,图中,i(t)、i1(t)~i3(t)分别为对应位置的网孔电流。

t1时刻前电路已经达到稳态,母线初始电压Vbus0=380 V,vds1和vds5的初始电压为1 V,vds2和vds6的初始电压为379 V,结电容Coss=200 pF,升压电感Lb=36 mH,升压电感和寄生电感的初始电流均为0。输入交流电压峰值Vs=311 V,母线电容Cbus= 600 mH,Lp1=120 pF,Lp2=200 pF,母线电容寄生电阻Resr=0.2 W。

图4 图腾柱无桥PFC换相等效全响应电路

Fig.4 Totem-pole bridgeless PFC commutation equivalent complete response circuit

在t1时刻由于引入了Rds,S6的结电容将会迅速放电,母线电容迅速给S5的结电容充电,这个过程中电感Lp2和结电容Coss5、Coss6之间会发生谐振现象,此时母线电压将会产生大幅的振荡,同时Lp1也会与结电容Coss5、Coss6发生谐振,在母线电压中引入更高频的小幅振荡,但对其振荡峰值几乎没有影响。随着vds6迅速降低,由于输入电压处在过零点附近,高频管S1和S2之间也由于KVL定律发生结电容充放电现象,Coss2的电压迅速下降,Coss1的电压迅速上升,这个过程中主要为电感Lb和结电容Coss1、Coss2之间发生明显的谐振现象,导致电感电流出现振荡。

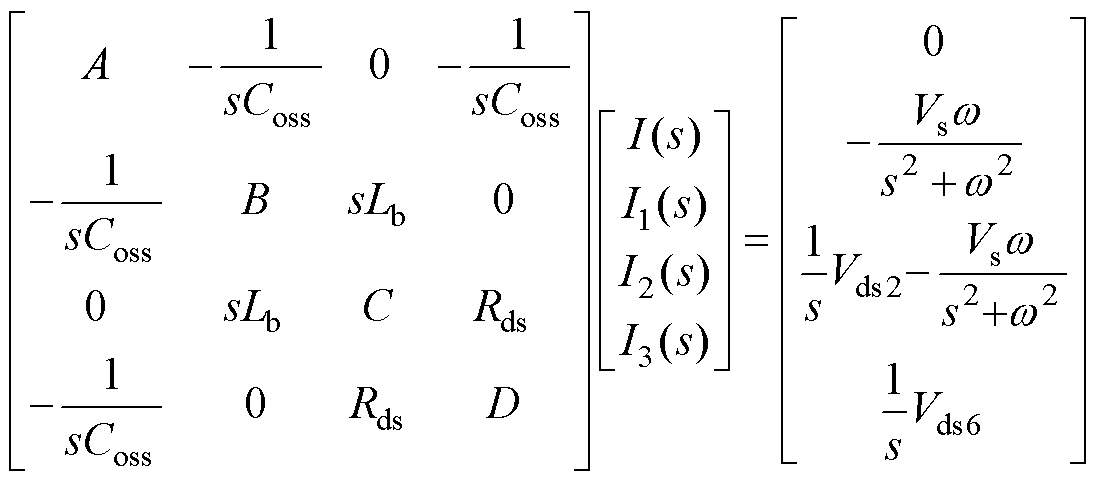

将等效全响应电路进行拉普拉斯变换后列出节点电压和网孔电流方程,如式(1)~式(3)所示,将方程求解后即可得到电感电流IL1和母线电压Vbus的s域传递函数。

(1)

(1)

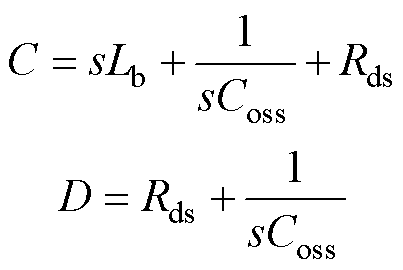

其中

(2)

(2)

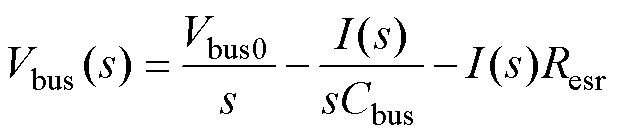

(3)

(3)

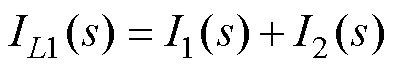

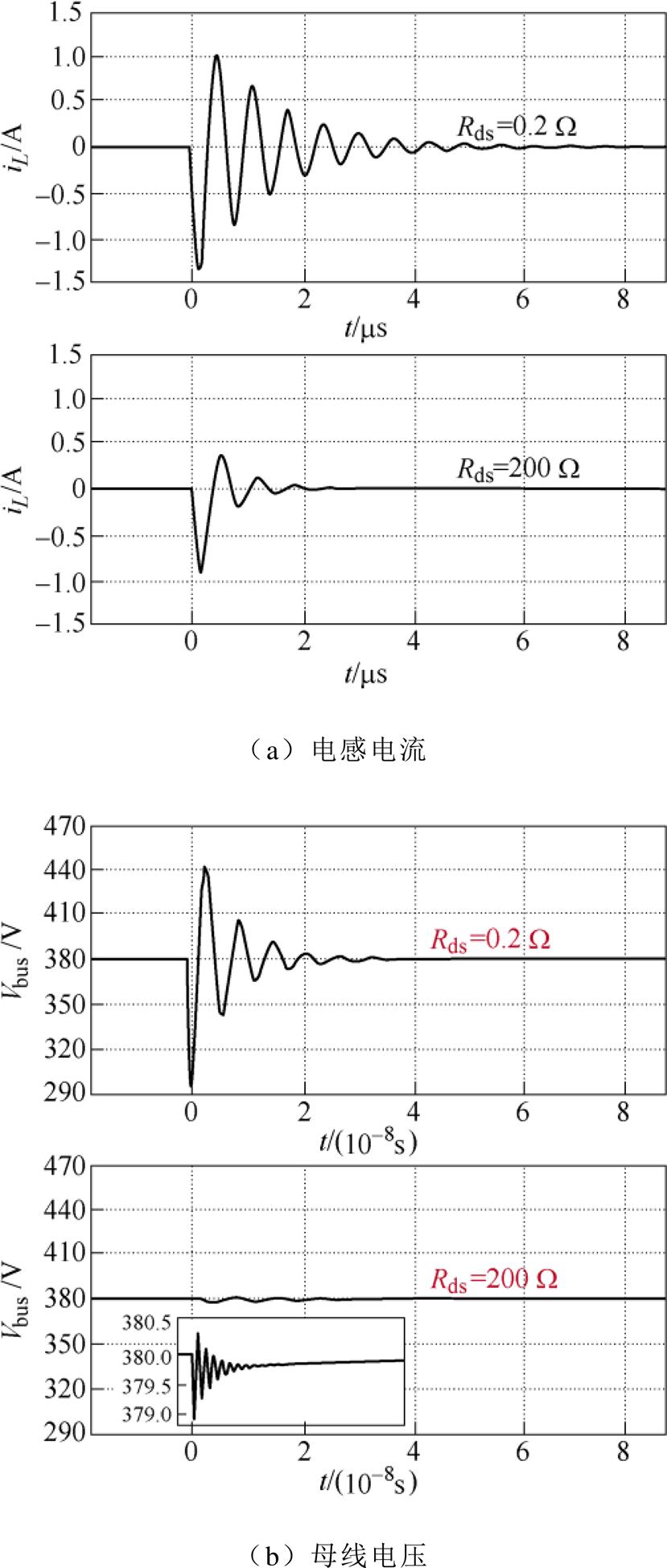

将该传递函数进行拉普拉斯反变换可以得到时域下的母线电压和电感电流表达式(详见附录式(A1)、式(A2))。图5为不同导通电阻Rds下的电感电流和母线电压波形。图6为电感电流和母线电压振荡幅值随Rds变化趋势。

图5 电感电流和母线电压波形

Fig.5 Waveforms of inductor current and DC bus voltage

图6 电感电流和母线电压振荡幅值随Rds变化趋势

Fig.6 The variation trend of inductance current and bus voltage oscillation amplitude with Rds

可以看出,S6开通的瞬间对电流的阻尼越大,电感电流iL1和母线电压vbus产生的尖峰越小,当Rds增加至100 W 时,iL1的振荡幅度减小至1 A以下;当Rds增加至100 W 时,母线电压的振荡幅度减小至1 V以下。

由第1节的分析可知,CRM图腾柱无桥PFC工频桥臂换流时工频管开通瞬间的阻抗对电感电流和母线电压尖峰的抑制效果显著,因此,通过改进驱动策略来优化工频管MOSFET的初始导通的阻抗可有效实现对上述振荡的抑制。

线性开关近年来被大量用于主动栅极驱动电路,处理高频高压的应用场合下MOSFET引起的EMI、串扰、振荡等问题。本文将基于开关管的线性工作的电气特性实现对MOSFET开通时刻的阻抗调节,从而达到抑制电感电流和母线电压尖峰的目的。

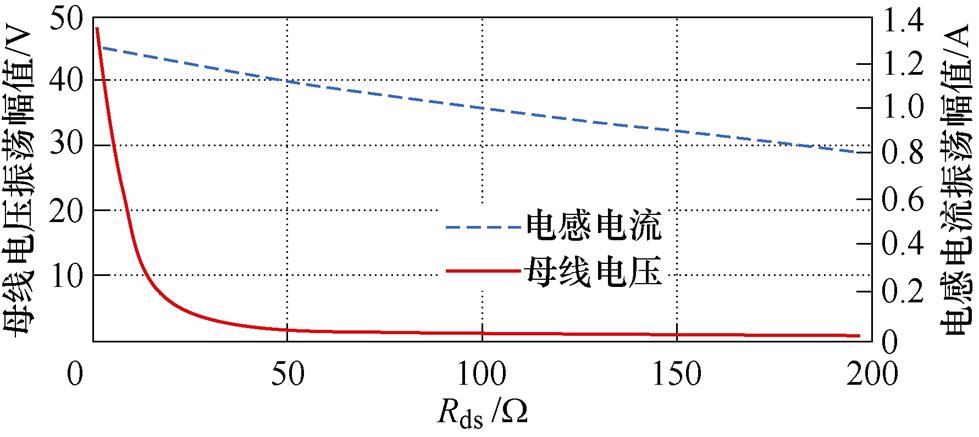

图7为N沟道场效应晶体管线性工作模式下的内部结构,源极S与衬底B直接相连,Rd为漏极串接电阻。

图7 线性工作模式下的MOSFET结构

Fig.7 MOSFET structures in linear operating modes

假设MOSFET初始处于关断状态,栅极驱动电压vgs小于门槛电压Vth,漏源极间不存在导电沟道,故MOSFET中没有电流流过,此时漏源极间承受的电压为vds,MOSFET处于截止区。

若继续提升vgs,则P型半导体中大量的受主原子呈电离态,形成耗尽层,同时大量的自由电子被吸引到表面,电子浓度超过表面电荷浓度,形成反型层沟道。但由于漏极的电位较高,反型层中的电子将不断流入漏极n+区,导致附近的反型程度减弱,沟道在漏极发生夹断,MOSFET进入线性区。这个过程中,反型层两端承受的电压值保持在饱和电压Vsat=vgs-Vth,夹断区两端承受的电压为vds-Vsat,在vds下降到等于Vsat之前,夹断区始终存在。夹断区处于弱反型,其中的电荷数量|QI|很小,载流子以超高速通过该区域,流过沟道的电流id=Isat,即饱和漏极电流。由于vds带来的夹断的长度远小于反型沟道的长度,故可以假设沟道长度不变,同时沟道两端承受电压不变,则沟道中流过的电流始终为Isat[21]。

若进一步提升vgs,被吸引到表面的电子浓度继续增加,vds下降到小于饱和电压Vsat,MOSFET进一步开通,完全开通后漏源两端通过沟道直接相连,该过程中漏极电流为iDN,MOSFET处于可变电阻区。

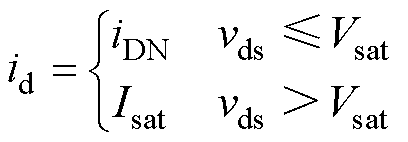

综上所述,MOSFET在不同工作状态下漏极电流id可以表示为

(4)

(4)

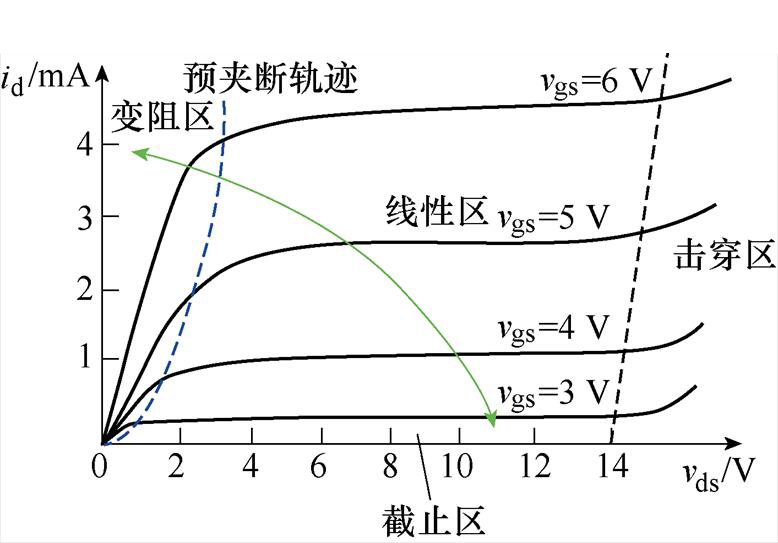

显然,当MOSFET进入线性区后,漏极电流由于导电沟道夹断而维持在饱和漏极电流这一恒定值。此时流过MOSFET的电流是可控的,漏极电流几乎不受vds变化的影响,漏源极间相当于一个只受vgs控制的恒流源[21]。而处在开关工作状态的MOSFET在截止区和可变电阻区之间切换的过程中会经过线性区,MOSFET输出特性曲线如图8所示。本文所述线性开关的应用就是将后者应用于开关瞬态中来增加阻尼,达到对振荡的抑制。

图8 MOSFET输出特性曲线

Fig.8 MOSFET output characteristic curves

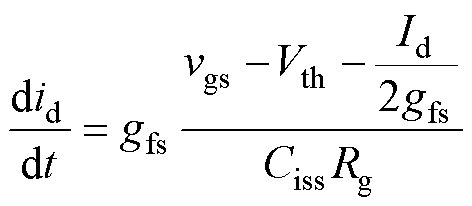

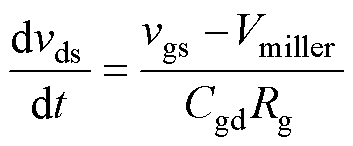

宏观分析,开启过程中的漏极电流随时间的变化率did/dt可以近似表示为

(5)

(5)

式中,gfs为跨导;Ciss=Cgs+Cgd为MOSFET输入电容;Rg为开通过程中的栅极电阻;Id为开关管完全开通后的漏极电流大小。

漏源电压随时间的变化率dvds/dt可以表示为

(6)

(6)

式中,Cgd为栅漏极电容;Vmiller为开关管米勒平台电压。从式(5)、式(6)可以看出,在开关经过线性区期间,增加栅极电阻Rg或减小驱动电压Vgs都可以降低能量转换速度,延长开关处于线性区的过程,减小di/dt和dv/dt,使得id和vds更加可控。

基于以上分析,针对CRM图腾柱无桥PFC电路,传统增加栅极电阻的驱动方法和本文提出的三电平混合驱动的控制策略,都是通过大幅延长其开通时线性区持续的时间,增加开通阶段回路中的等效阻尼,从而限制MOSFET沟道形成过程中的电流变化率,抑制或避免电感电流和母线电压振荡尖峰。

图9为传统增大栅极电阻的两电平驱动方法,通过增大MOSFET的栅极电阻Rg,减缓vgs的上升速度,从而阻尼漏极电流的振荡,即在开通瞬间大幅增加了第1节中所提的导通电阻Rds。根据CREE C3M0065090D器件手册关于外部栅极驱动电阻和开通时间的关系曲线可知,增加驱动电阻对vgs上升时间的延长相当有限,当驱动电阻从5 W 增加至20 W 时,上升时间tr只增加了8 ns,想要对MOSFET开启过程中的输出特性进行精准的控制以达到明显的振荡抑制效果比较困难。

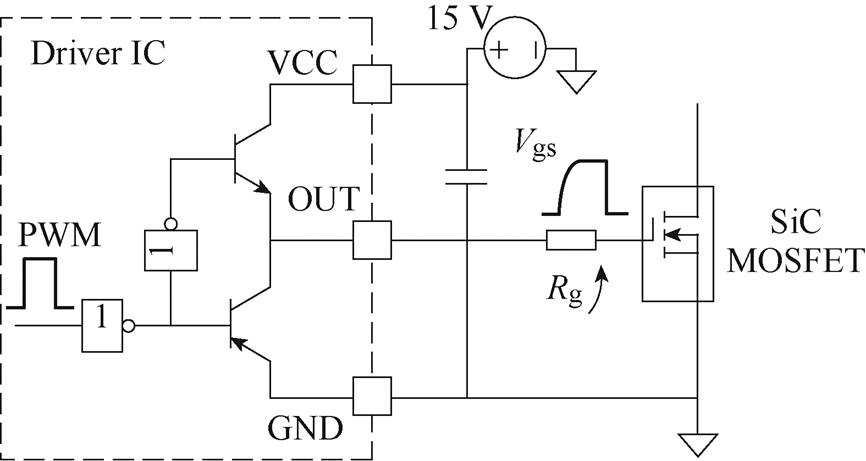

图9 传统增大栅极电阻的两电平驱动方式

Fig.9 Traditional two-level drive method with increased gate resistance

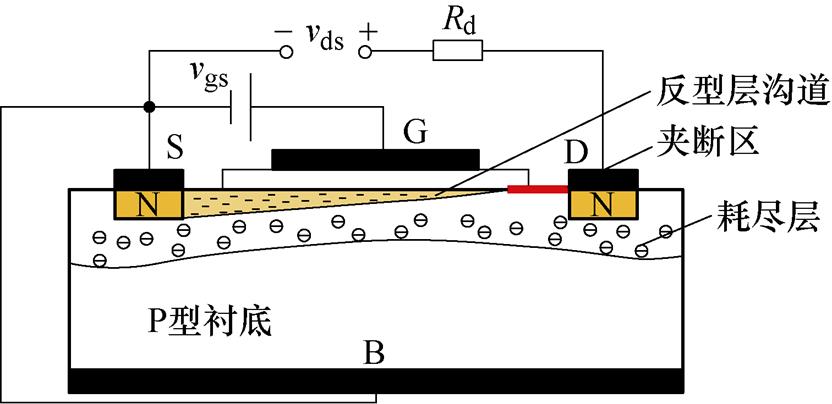

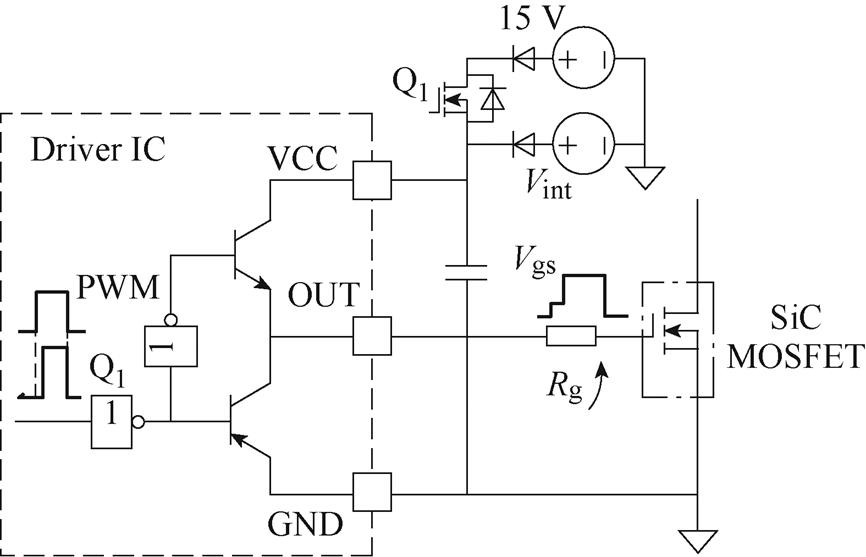

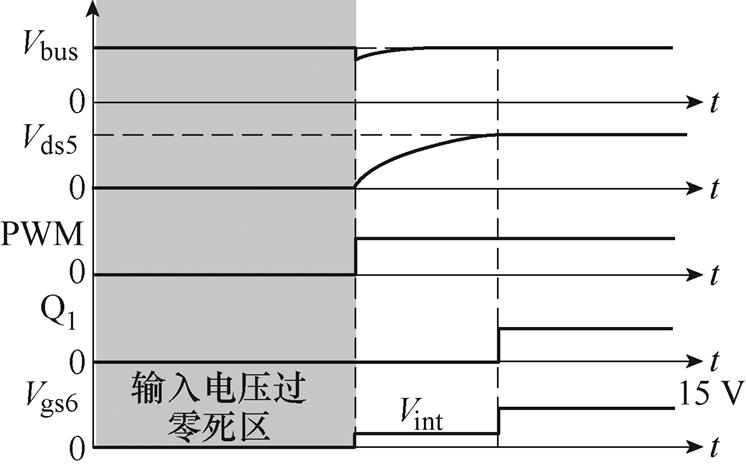

增加开通时刻的阻抗本质上要延长MOSFET处于线性区内的时间,由上述分析可知,直接增大电阻的方式虽然能有一定的改善效果,但是受诸多因素制约,这种方法对线性区的延长并不可控。为避免其对稳态性能的影响,本文提出一种增加线性工作时间的三电平混合驱动策略,如图10所示。该驱动策略在工频信号到来时,先通过较低的中间驱动电平Vint使MOSFET稳定工作在线性区,此时辅助管Q1截止,当另一工频管的电压上升至母线电压,电路达到稳定后,Q1开通,驱动信号切换至正常的驱动电平15 V,MOSFET完全开通,控制信号的时序如图11所示。显然,合理分配PWM与辅助管驱动信号到来的时刻就可以实现受控的线性工作时间。

图10 三电平混合驱动策略

Fig.10 Three-level hybrid drive strategy

图11 三电平混合驱动的控制时序

Fig.11 Control timing of three-level hybrid drive

由于MOSFET开启过程中线性工作区的时间被可控延长,此时MOSFET的沟道处于夹断状态,漏极电流饱和,故母线电容的放电电流得到了限制。由式(5)可知,选取合适的中间电平可以将电路中的阻尼控制在理想水平,使得电感电流和母线电压尖峰得到有效抑制,两路交错并联的高频管和工频管都使用CREE公司的SiC MOSFET C3M0065090D,该型号的门槛电压为2.5 V。

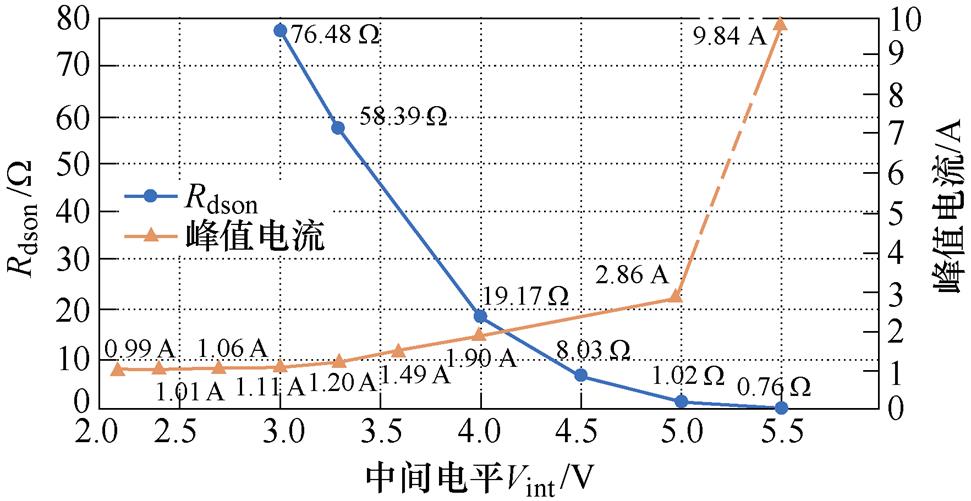

由于采用数字控制方法,实际CRM图腾柱无桥PFC使用的中间电平的持续时间设为中断周期的整数倍,本文采用主频100 MHz的DSP,中断周期设置为30 ms,中间电平的持续时间选择一个中断周期。利用CREE提供的C3M0065090D Ltspice模型搭建开通瞬态下的仿真模型,基于此可得到不同中间电平下漏极电流的振荡峰值,结合实测的不同中间电平下导通电阻Rdson作为开通阻抗的参考,不同中间电平对应开通电阻和峰值电流分布如图12所示。传统的两电平驱动方式开通瞬间漏极电流振荡峰值为9.84 A,此时实际的Rdson=0.76 W;采用三电平混合驱动,在开通时刻能对谐振产生明显的抑制效果,当电压为3.3 V时漏极电流峰值减小至1.11 A,此时实际的Rdson=58.39 W。为保证MOSFET有效开通,Vint必须大于门槛电压,同时为了获得较好的阻尼效果,最后取Vint=3.3 V。

图12 不同中间电平对应导通电阻和峰值电流分布

Fig.12 Distribution of Rdson and peak current corresponding to different intermediate levels

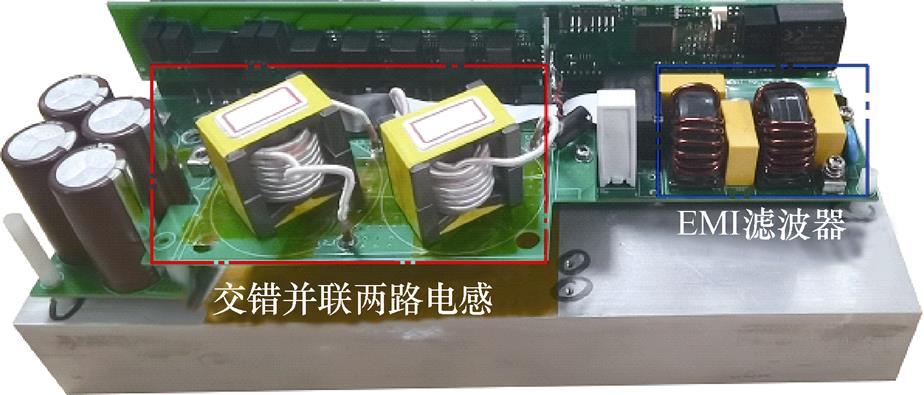

为了验证所提出的驱动策略,实验室搭建了一台2 kW的交错并联CRM图腾柱无桥PFC样机,如图13所示。两路交错并联的高频管和工频管都使用CREE公司的SiC MOSFET,具体型号为C3M0065090D。样机详细参数见表1。

图13 2 kW图腾柱无桥PFC样机

Fig.13 Prototype of 2 kW totem-pole bridgeless PFC

功率因数校正控制采用文献[12]中第1节的控制策略,在此基础上通过三电平混合驱动策略抑制母线电压和电流振荡。为了保证样机的可靠性,工频管和高频主管先于同步整流管开通,在工频管处于线性区期间,输入电压处在过零点附近,能量交换较小。在同步整流管开始工作后,对应相位的工频管已进入可变电阻区正常工作,所以三电平驱动不会影响高频桥臂工作之后的功率因数校正效果和效率。

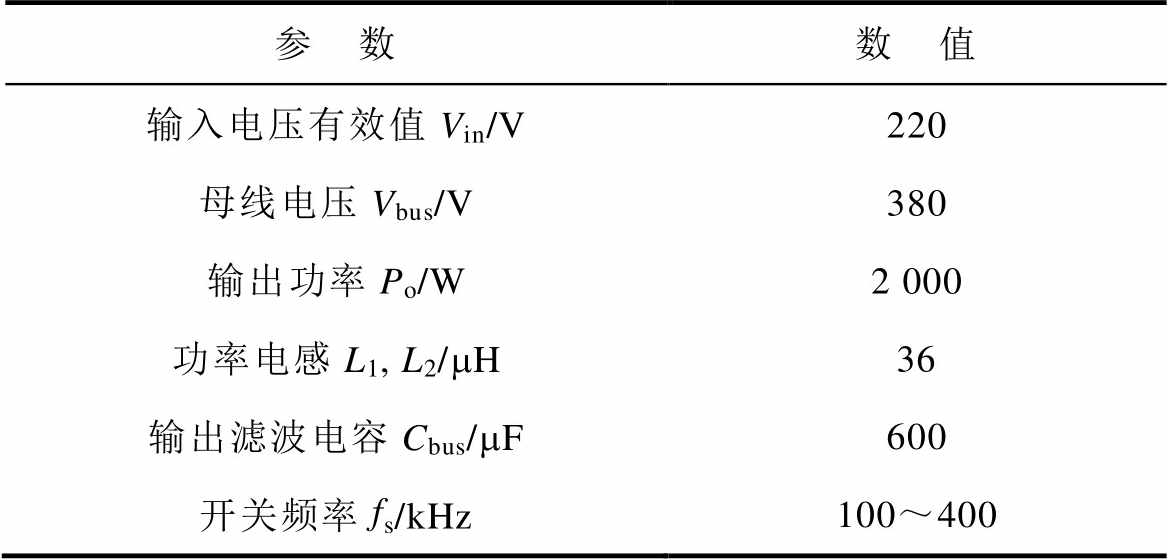

表1 CRM图腾柱无桥PFC变换器电路参数

Tab.1 Circuit parameters of CRM totem-pole bridgeless PFC converter

参 数数 值 输入电压有效值Vin/V220 母线电压Vbus/V380 输出功率Po/W2 000 功率电感L1, L2/mH36 输出滤波电容Cbus/mF600 开关频率fs/kHz100~400

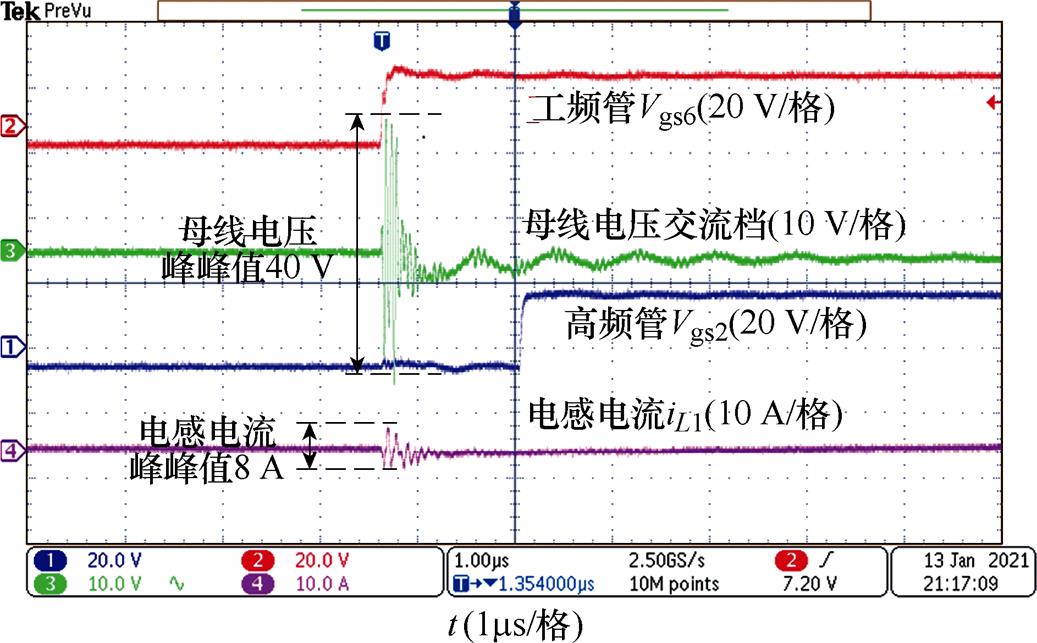

图14为传统两电平驱动方式下的实验波形,栅极电阻为8 W。在输入电压换相处,电感电流的振荡幅值为8 A,母线电压振荡幅值为40 V,满载时输入电流THD为4.3%。

图14 传统两电平驱动波形

Fig.14 Waveforms of traditional two-level driving

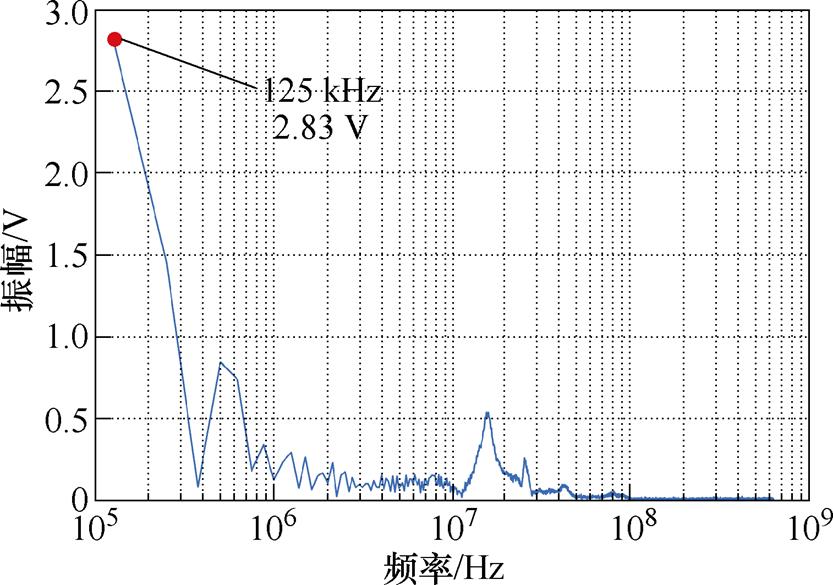

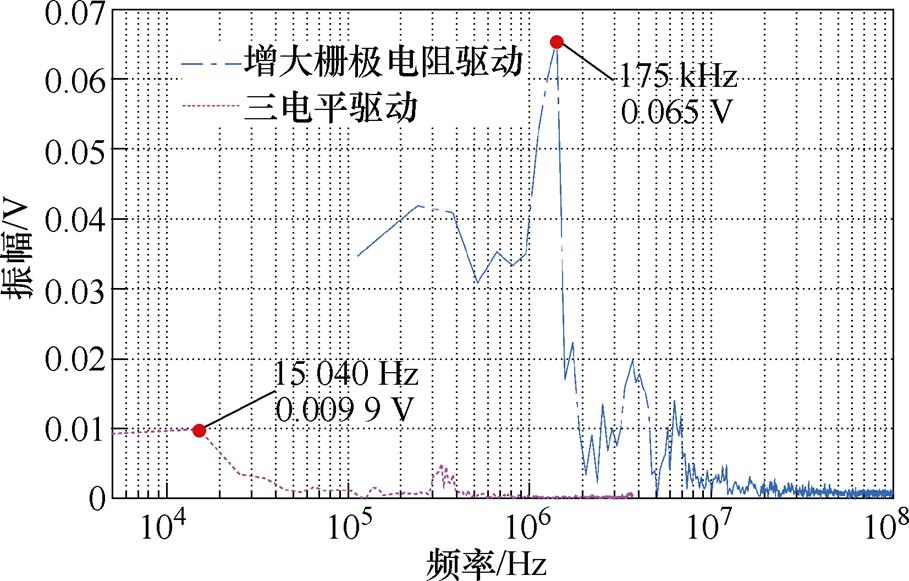

对尖峰波形进行快速傅里叶变换分析,图15为其归一化后的单边振幅谱,可以看出,尖峰振荡中较大的高频分量超过125 kHz,而后级DC-DC变换器的截止频率一般要小于这个值,控制环无法实现对该频段的抑制,该噪声会直接施加于敏感负载,将对设备的正常工作产生不利影响。

图15 母线电压尖峰快速傅里叶分析

Fig.15 Fast Fourier analysis of bus voltage spike

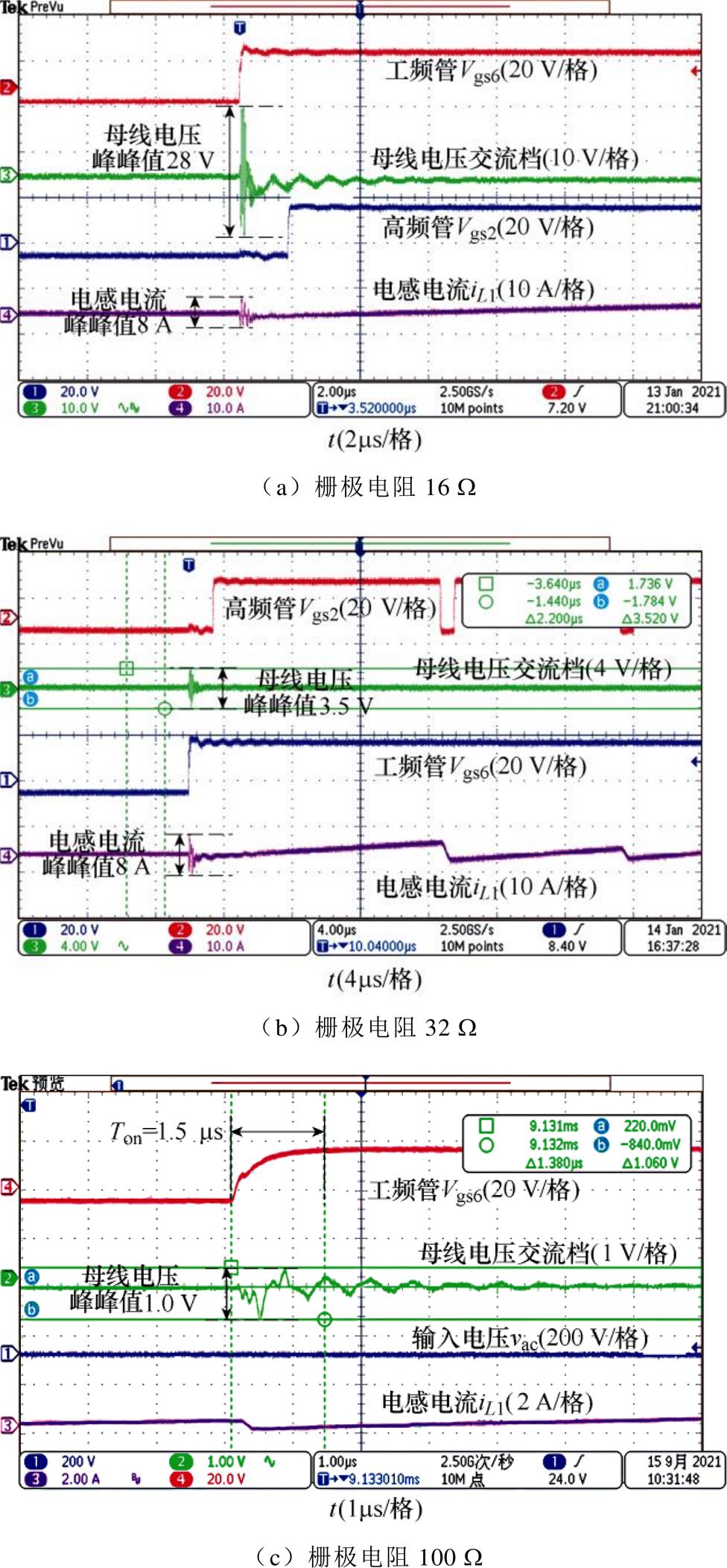

图16a~图16c分别为栅极电阻16 W、32 W 和100 W时,输入电压为220Vac、单路功率为1 kW条件下的实验波形。可以看出,当栅极电阻为16 W 时,母线电压尖峰为28 V,振荡幅值减小;当栅极电阻增加至32 W 时,母线电压尖峰下降至3.5 V,电感电流振荡峰值基本不变;当栅极电阻增加至100 W 时,电感电流振荡基本消失,符合正常功率因数校正波形,母线电压尖峰下降至1 V。不足的是继续增加栅极电阻对MOSFET线性区延长的时间有限,振荡尖峰的抑制效果不甚明显,想实现精确而又灵活的控制比较困难。

图16 增大栅极电阻驱动策略实验波形

Fig.16 Experimental waveforms of driving strategy for increasing gate resistance

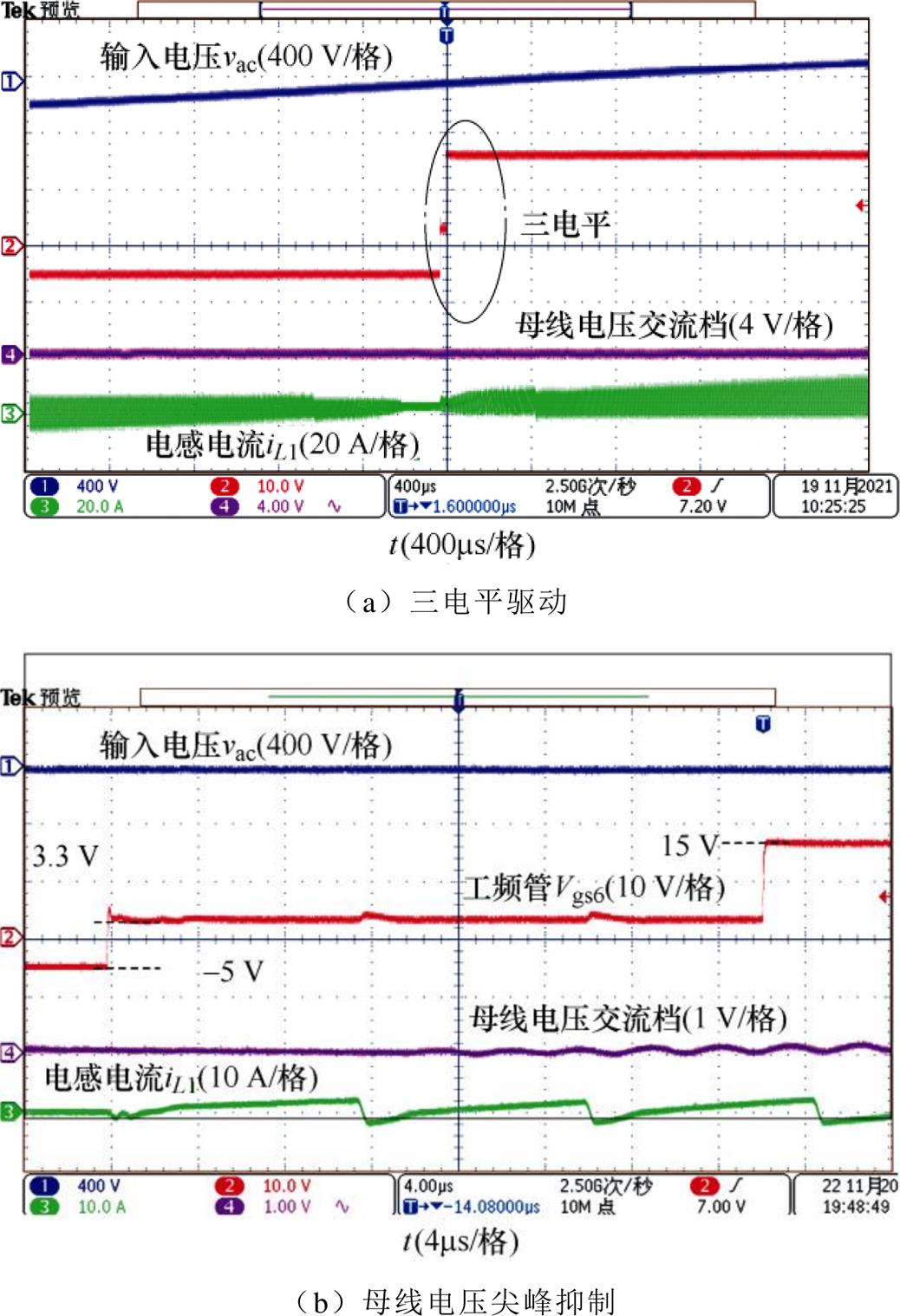

图17为应用三电平驱动策略的实验波形,这里中间电平设置为3.3 V。使用AMS公司的AMS1117- 3.3,辅助管Q1使用DIODES公司的2N7002-7-F,封装为SOT-23,导通电阻为3 W,但由于MOSFET的驱动电流较小,不会对三电平驱动信号的发生产生影响。相比增大栅极电阻的方法,能实现更好的尖峰抑制效果,电感电流波动和母线电压尖峰几乎完全消失,同时由于开通过程中电感电流很小,不会带来额外的导通损耗,且针对不同的应用场合可以选取不同的中间电平及其作用时间,具有更高的控制精度和应用价值。

图17 三电平驱动策略实验波形

Fig.17 Experimental waveforms of three-level driving strategy

对图16c和图17b中的母线电压波形进行快速傅里叶分析,图18为其归一化后的单边振幅谱,其中增大栅极电阻策略的母线电压高频振荡分量下降到0.065 V以下,三电平驱动的控制策略下降到0.01 V以下,基本可以忽略其传递给后级所造成的影响。

图18 优化后母线电压尖峰快速傅里叶分析

Fig.18 Fast Fourier analysis of bus voltage spike after optimization

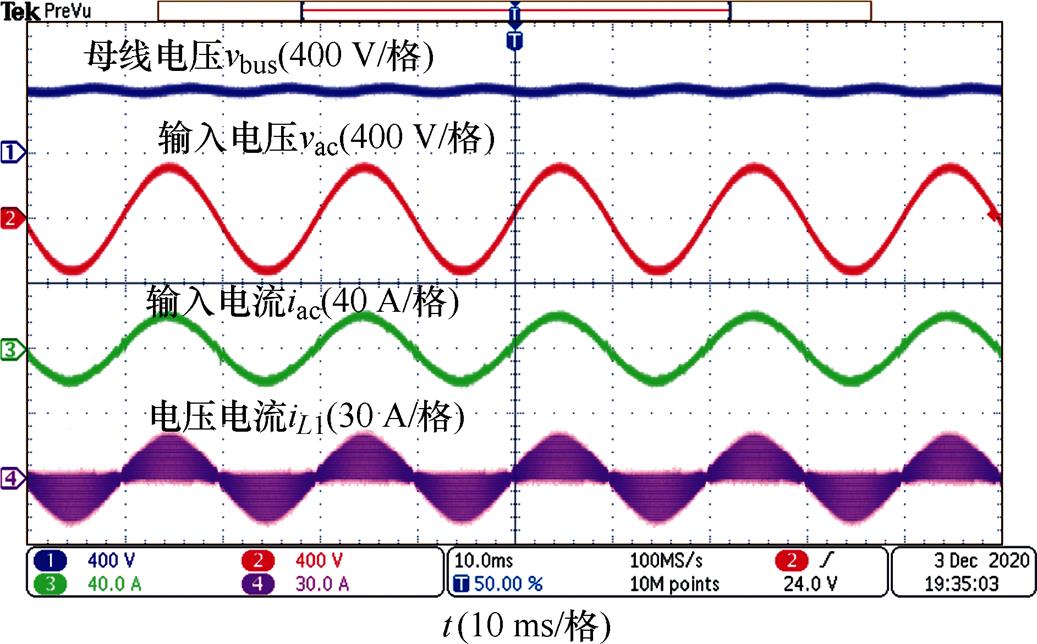

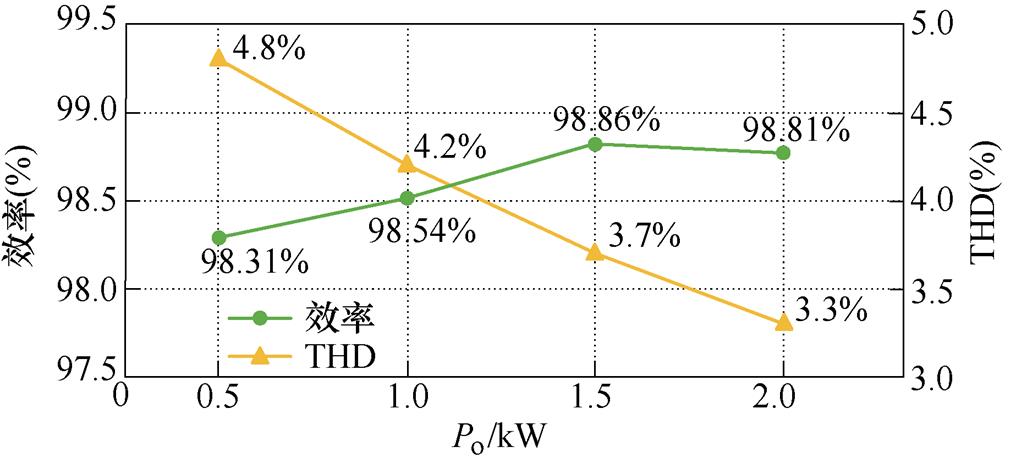

图19为2 kW工况下图腾柱无桥PFC的功率因数校正波形。对该样机在不同功率点下进行测试,情况如图20所示,样机满载效率为98.81%,峰值效率为98.86%,满载时输入电流THD为3.3%,比传统两电平驱动减小1%。综上所述,采用三电平控制策略的CRM图腾柱无桥PFC依然能达到良好的电气性能,同时实现降低输入电流THD值,明显抑制母线电压尖峰的效果。

图19 2 kW工况下PFC效果验证波形

Fig.19 Waveforms of PFC effect verification under 2 kW working condition

图20 不同功率点下CRM图腾柱无桥PFC样机参数

Fig.20 Parameters of CRM totem-pole bridgeless PFC prototype at different power points

本文针对CRM图腾柱无桥PFC电路在输入电压换相时刻出现的电感电流和母线电压尖峰问题,提出了一种利用线性开关特性的三电平混合驱动电路。对工频换相处的暂态电路模型进行分析,通过增大工频管开启瞬间对电流的阻尼可以有效抑制谐振,阻尼越大、抑制效果越好。分析了线性开关在主动栅极驱动电路中优化开关轨迹的原理,通过增大栅极电阻和改变驱动电压的方式,可以利用线性区的特性来控制MOSFET在开关瞬态中电压和电流的变化率。搭建2 kW CRM图腾柱无桥PFC样机,将这两种方法应用于工频管驱动控制中,对比分析其对换相处尖峰的抑制效果,最终选择三电平混合驱动策略实现电感电流和母线电压的尖峰抑制,将输入电流THD降低了1%,同时减小传递给后级变换器的电压高频分量,峰值效率为98.86%。

附 录

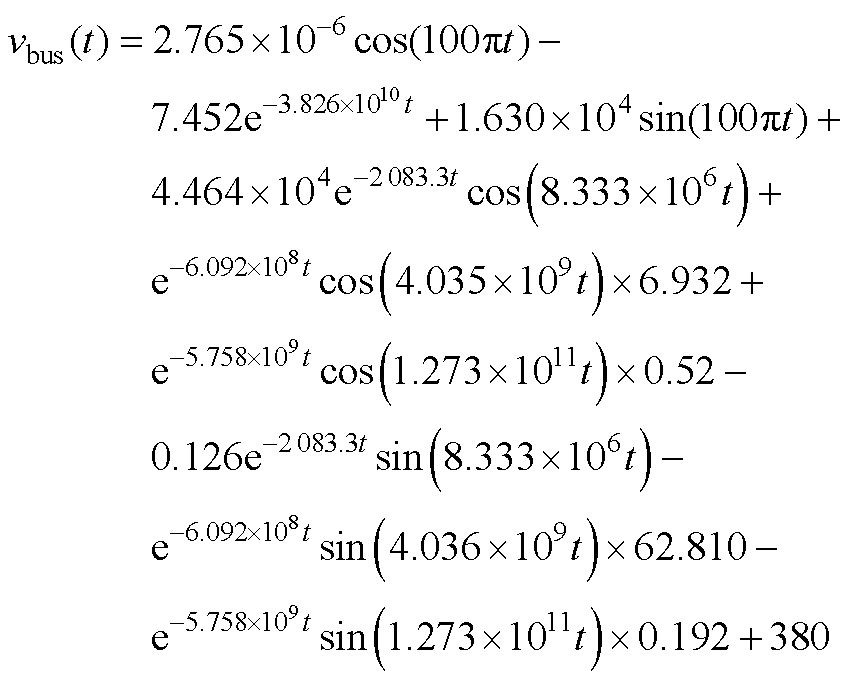

母线电压随时间变化的数学表达式为

(A1)

(A1)

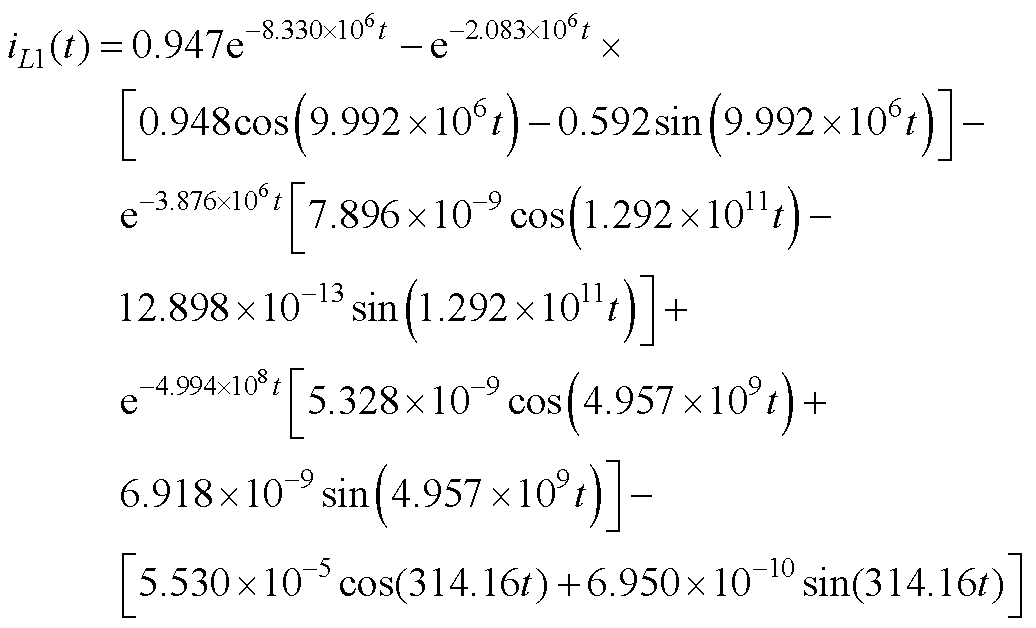

电感电流随时间变化的数学表达式为

(A2)

(A2)

参考文献

[1] 孙凯, 贲洪奇, 孟涛, 等. 一种具有宽输出调压范围与低电压应力的单级无桥隔离型PFC变换器[J]. 电工技术学报, 2022, 37(8): 1991-2005.

Sun Kai, Ben Hongqi, Meng Tao, et al. A single-stage bridgeless isolated PFC converter with wide output voltage range and low voltage stress[J]. Transactions of China Electrotechnical Society, 2022, 37(8): 1991- 2005.

[2] 王兆安, 刘进军, 王跃. 谐波抑制和无功功率补偿[M]. 3版. 北京: 机械工业出版社, 2016.

[3] 邹军, 吴红飞, 刘越, 等. 基于低高度平面电感的GaN-Si混合型图腾柱无桥功率因数校正器[J]. 电工技术学报, 2021, 36(20): 4265-4273.

Zou Jun, Wu Hongfei, Liu Yue, et al. Hybrid totem- pole bridgeless power factor corrector converter with GaN HEMT and Si diode based on low profile planar inductor[J]. Transactions of China Electrotechnical Society, 2021, 36(20): 4265-4273.

[4] Liu Zhengyang, Huang Zhengrong, Lee F C, et al. Digital-based interleaving control for GaN-based MHz CRM totem-pole PFC[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2016, 4(3): 808-814.

[5] Xu Xiaojun, Huang A Q. A novel closed loop interleaving strategy of multiphase critical mode Boost PFC converters[C]//2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition, Austin, TX, USA, 2008: 1033-1038.

[6] 王宁, 张建忠. 基于开关轨迹优化的SiC MOSFET有源驱动电路研究综述[J]. 电工技术学报, 2022, 37(10): 2523-2537.

Wang Ning, Zhang Jianzhong. Review of active gate driver for SiC MOSFET with switching trajectory optimization[J]. Transactions of China Electro- technical Society, 2022, 37(10): 2523-2537.

[7] 梁美, 郑琼林, 可翀, 等. SiC MOSFET、Si CoolMOS和IGBT的特性对比及其在DAB变换器中的应用[J]. 电工技术学报, 2015, 30(12): 41-50.

Liang Mei, Zheng Qionglin, Ke Chong, et al. Perfor- mance comparison of SiC MOSFET, Si CoolMOS and IGBT for DAB converter[J]. Transactions of China Electrotechnical Society, 2015, 30(12): 41-50.

[8] 李国文, 杭丽君, 童安平, 等. 串扰有源抑制型SiC MOSFET驱动方法[J]. 中国电机工程学报, 2021, 41(11): 3915-3923.

Li Guowen, Hang Lijun, Tong Anping, et al. The driver design of SiC MOSFET with active crosstalk suppression[J]. Proceedings of the CSEE, 2021, 41(11): 3915-3923.

[9] Liu Tianjiao, Ning Runtao, Wong T T Y, et al. Modeling and analysis of SiC MOSFET switching oscillation[J]. IEEE Journal of Emerging & Selected Topics in Power Electronics, 2017, 4(3): 747-756.

[10] Zhou Hao, Ye Chunxian, Zhan Xubiao, et al. Designing a SiC MOSFETs gate driver with high dv/dt immunity and rapid short circuit protection for xEV drivetrain inverter[C]//2019 22nd International Conference on Electrical Machines and Systems (ICEMS), Harbin, China, 2019: 1-5.

[11] 钱照明, 陈恒林. 电力电子装置电磁兼容研究最新进展[J]. 电工技术学报, 2007, 22(7): 1-11.

Qian Zhaoming, Chen Henglin. State of art of electromagnetic compatibility research on power electronic equipment[J]. Transactions of China Electrotechnical Society, 2007, 22(7): 1-11.

[12] 王生东, 李浩然, 顾占彪, 等. 便携式充电CRM图腾柱PFC过零检测延迟与交错相位误差补偿控制[J]. 电工技术学报, 2022, 37(1): 12-23.

Wang Shengdong, Li Haoran, Gu Zhanbiao, et al. Compensation control of zero current detection delay and interleave phase error for CRM totem-pole power factor correction in portable charging[J]. Transactions of China Electrotechnical Society, 2022, 37(1): 12-23.

[13] 张卫平. 开关变换器的建模与控制[M]. 北京: 机械工业出版社, 2020.

[14] Camacho A P, Sala V, Ghorbani H, et al. A novel active gate driver for improving SiC MOSFET switching trajectory[J]. IEEE Transactions on Indu- strial Electronics, 2017, 64(11): 9032-9042.

[15] Nayak P, Hatua K. Active gate driving technique for a 1200 V SiC MOSFET to minimize detrimental effects of parasitic inductance in the converter layout[J]. IEEE Transactions on Industry Applications, 2018, 54(2): 1622-1633.

[16] Zhang Zheyu, Dix J, Wang F F, et al. Intelligent gate drive for fast switching and crosstalk suppression of SiC devices[J]. IEEE Transactions on Power Elec- tronics, 2017, 32(12): 9319-9332.

[17] Dymond H C P, Wang Jianjing, Liu Dawei, et al. A 6.7-GHz active gate driver for GaN FETs to combat overshoot, ringing, and EMI[J]. IEEE Transactions on Power Electronics, 2017, 33(1): 581-594.

[18] Zhao Shuang, Dearien A, Wu Yuheng, et al. Adaptive multi-level active gate drivers for SiC power devices[J]. IEEE Transactions on Power Electronics, 2020, 35(2): 1882-1898.

[19] Yang Yuan, Wen Yang, Gao Yong. A novel active gate driver for improving switching performance of high-power SiC MOSFET modules[J]. IEEE Transa- ctions on Power Electronics, 2019, 34(8): 7775- 7787.

[20] Dymond H C P, Liu Dawei, Wang Jianjing, et al. Multi-level active gate driver for SiC MOSFETs[C]// IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 2017: 5107-5112.

[21] 希维迪斯. MOS晶体管的工作原理及建模[M]. 西安: 西安交通大学出版社, 1989.

Abstract Totem-pole bridgeless power factor correction (PFC) circuit operating in critical conduction mode (CRM) has a low on-state loss, easy implementation of soft switching, and high power density. However, at the commutation time between the power frequency switches, the inductance in the circuit can resonate with the bus capacitance and the output junction capacitance of the switches. As a result, a large oscillation peak exists when the input current commutates and the secondary ripple of the bus voltage crosses the zero point. The oscillation of inductance current causes an increase in input current total harmonics distortion (THD). Meanwhile, the oscillation spike superimposed on the bus voltage’s secondary ripple includes high-frequency components directly applied to the load through the subsequent DC-DC converter, causing the sensitive load to work improperly. Therefore, it is necessary to suppress the commutation resonance effectively.

Through the analysis of the totem-pole circuit, the greater the impedance of the power frequency switch at its opening moment, the better the suppression effect of the oscillation. This paper proposes a three-level hybrid driving strategy for power frequency switches. Based on the characteristics of the linear switch, the adverse effects of high dv/dt and di/dt in the circuit can be overcome by changing the working mode of traditional driving circuits, increasing the damping of switching instants and optimizing switching trajectories. This strategy is to extend the time of the MOSFET operating in a linear region through a lower intermediate level Vint at the moment when the power frequency switch is turned on. When the voltage of another power frequency switch rises to the bus voltage and the circuit reaches stability, the driving signal reverts to the normal high level. The switching of the intermediate level is achieved through the auxiliary tube Q1. The input voltage is close to the zero-crossing point during commutation, and the input current oscillation is suppressed by the proposed control strategy. Therefore, the reliability of the system can be guaranteed, and the impact of the three-level hybrid drive strategy on efficiency can be ignored.

To verify the proposed driving strategy, a 2 kW interleaved parallel CRM totem-pole bridgeless PFC prototype is built, and both the high-frequency switches and the power frequency switches use the C3M0065090D SiC MOSFET of CREE. An intermediate level of 3.3 V was selected according to simulations and conduction resistance comparisons of the MOSFET under different driving voltages. The results show that the three-level hybrid drive strategy can suppress power frequency commutation resonance. Under the 2 kW full load condition, the input current THD is reduced by 1%, and the peak value of the high-frequency component of the bus voltage spike is reduced from 2.83 V to below 0.01 V. Compared with the traditional method, a better oscillation suppression effect can be achieved with almost complete disappearance of inductance current oscillation and bus voltage spike. The prototype’s efficiency under the full load condition is 98.81%, and different intermediate levels and their action time can be selected for different application scenarios, which has higher control accuracy than the traditional method.

keywords:Totem-pole bridgeless power factor correction (PFC), commutation resonance, linear switch, three-level drive, DC bus voltage spike suppression

DOI: 10.19595/j.cnki.1000-6753.tces.230419

中图分类号:TM461

国家自然科学基金资助项目(52177181)。

收稿日期 2023-04-06

改稿日期 2023-05-30

黄 帆 女,2000年生,硕士,研究方向为AC-DC变换器拓扑与控制技术、宽禁带器件应用技术。E-mail: huangfan@nuaa.edu.cn

任小永 男,1979年生,博士,教授,研究方向为高频/超高频功率电子变换技术、宽禁带器件应用技术、储能与控制、无线充电技术以及高功率密度集成。E-mail: renxy@nuaa.edu.cn(通信作者)

(编辑 陈 诚)