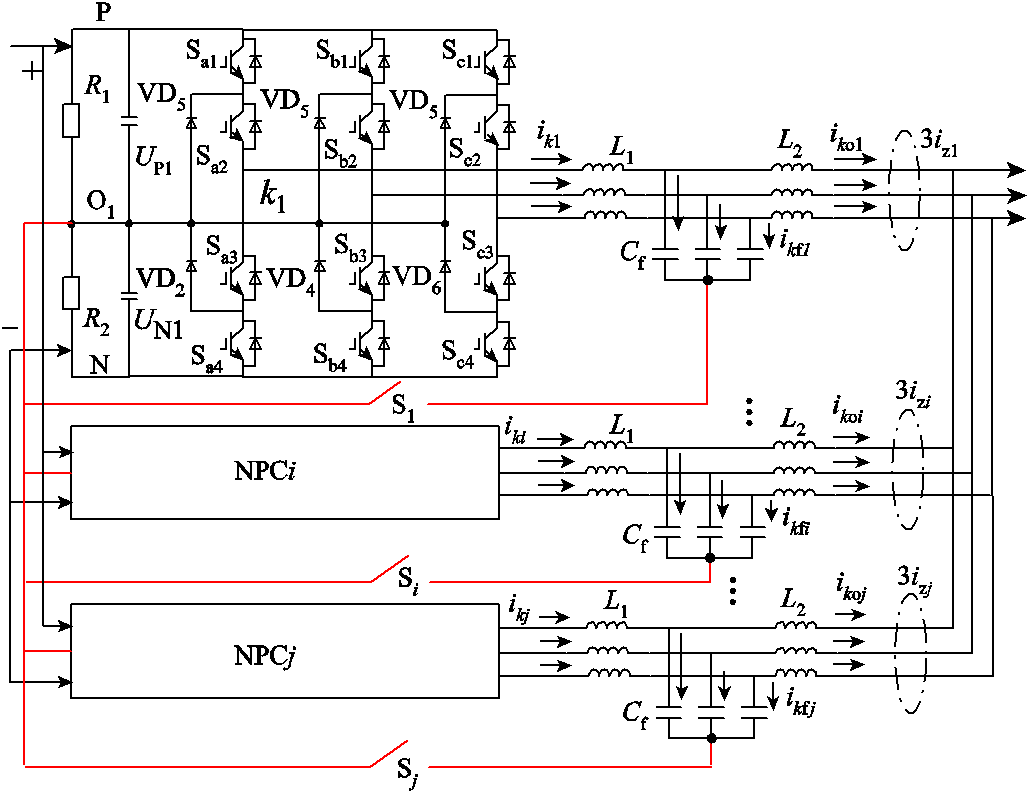

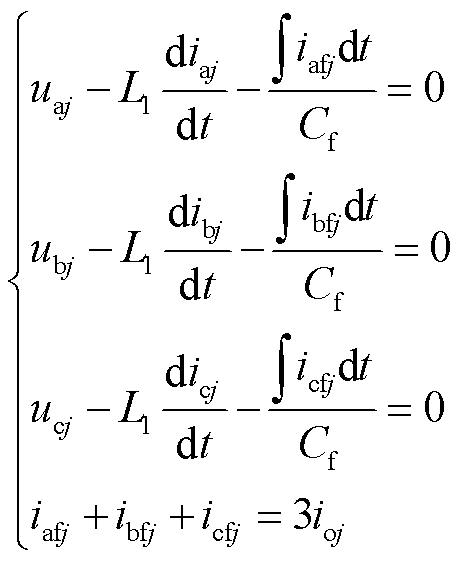

图1 三电平模块化逆变器系统

Fig.1 Three level modular inverter system

摘要 针对中点钳位型(NPC)三电平逆变器并联系统内普遍存在的零序环流问题,该文首先分析模块间环流的通路,建立零序环流的电路和数学模型。根据等效模型阐述零序环流各成分的产生机制,并对零序环流进行定量分析。定义零序环流的三类具体成分:通态零序环流、开关零序环流及混合零序环流。对于不同类别的零序环流,提出共享直流侧中线和改进型LCL滤波器的硬件措施及准比例积分谐振(PIR)控制器的软件措施去抑制对应环流成分的高频、低频分量;另外,针对改进型LCL滤波器中交流滤波电容中点和直流侧电容中点连接电缆上有较大高频电流的缺陷,提出载波移相控制下模块共用滤波电容的优化方案,在保证环流抑制效果的同时将奇数次开关频率的高频纹波转移到共用电容上,实现奇数纹波分量的自动抵消,使连接电缆上的电流减小近50%;最后,仿真与实验结果验证了所提环流抑制策略的可行性。

关键词:三电平中点钳位型逆变器 逆变器并联系统 零序环流抑制 准比例积分谐振控制 模块共用滤波电容 载波移相控制

近年来,全面推广可再生能源并网发电已成为我国能源转型和实现“双碳”目标的重要技术手段。脉冲宽度调制(Pulse Width Modulation, PWM)的逆变器在新能源并网中能可靠实现与外部电网之间可控的能量交换。然而,受限于开关器件功率、温度阈值的影响,单台逆变器可提供的功率有限,难以应用于有大容量要求的并网系统或大电源系统中,多台逆变器并联运行成为增加系统容量、提高功率等级的一种主要措施[1-3]。

多逆变器并联系统具有高功率、高灵活性和高可靠性等优势,但其稳定性往往面临着更严峻的挑战。多机系统中任意一台逆变器的功率扰动都有可能影响整个系统,加之每台逆变器的LCL滤波器固有的谐振尖峰,多机并联系统更容易出现谐振失稳问题[4-5]。与此同时,共交直流母线的多逆变器并联系统会产生零序环流问题,一方面会增加器件应力从而造成额外的损耗且引发保护误动作;另一方面引起输出电流畸变进而威胁并联系统的稳定性[6-8]。

中点钳位(Neutral Point Clamped, NPC)型三电平逆变器由于开关管数与输出电平数增加,其环流路径和环流成分相较两电平逆变器更为复杂,加之其固有的中点电位不平衡问题,NPC逆变器并联系统的环流抑制更具挑战性,有必要采取综合软件和硬件措施加以抑制。文献[6]设计一种环流谐振控制器的方法来抑制环流;此外优化的调制策略能抑制甚至消除逆变器的共模电压以达到减少环流含量和改善并联系统电磁特性的目的[7-10]。文献[11]从光伏系统共模漏电流的分析出发,在此基础上建立了模块化并联三电平逆变器系统环流模型,分析了各频率成分环流的交互影响,提出了无谐振的环流控制方法。文献[12]提出基于比例-积分+精准前馈的协调控制策略抑制低频环流。文献[13]比较了不同类型的控制器后提出了采用准比例积分谐振(Proportional-Integral-Resonant, PIR)控制器抑制低频谐波电流,为低频零序环流的抑制提供了参考。文献[14-15]指出相间环流流通路径且环流的主要成分为零序环流,环流与各个模块之间的功率分配呈强相关。文献[14]还进一步提出一种改进的数字控制策略,适用于各并联模块阻抗不匹配、电网电压不平衡等工况的相间环流抑制。在应用各类不同软件调制控制措施的同时,出于经济性的考虑及控制器带宽的限制,大量硬件措施也被广泛用于抑制零序环流。文献[15]的研究对象是共享直流侧中线的逆变器并联系统。现有最直接有效的消除零序环流的方法是添加隔离变压器和独立采用直流源,这两种硬件方法分别切断了并联逆变器交流侧和直流侧的环流回路,能完全抑制零序环流。然而随着并联模块数量的增加,每个模块均采用隔离变压器及独立直流源,增加了系统的整体成本和体积;另外,还有些低成本的硬件方法能抑制特定成分的零序环流,如连接各模块直流侧中点形成共享中线、采用星形联结的滤波电容时连接交直流电容中点形成改进型LCL滤波器[15-20],这些方法易于实现但也有不足之处,如改进型LCL中的连接电缆上电流过大,会引入额外的纹波干扰。现有文献大多从软件控制策略上研究和改进零序环流的抑制措施,以追求控制效果和算法复杂度的兼顾平衡,而对于硬件措施的使用,沿袭传统方案来抑制相应类别的零序环流是常见的选择,少有研究去完善优化传统的硬件措施。

针对多NPC逆变器并联系统零序环流问题,本文在分析环流回路的基础上,建立了环流的数学模型并借助开关函数对环流进行分类,使用傅里叶分解对环流进行了量化分析,针对不同类别的零序环流,提出对应的抑制方法来控制多逆变器并联系统中的零序环流,同时优化了传统改进型LCL的连接方式,形成载波移相控制下的模块共用电容方案。对比传统的改进型LCL,连接电缆上具有更小的电流纹波,装置元器件的工作环境得到了改善。最后通过仿真和实验证明相关措施的可行性与有效性。

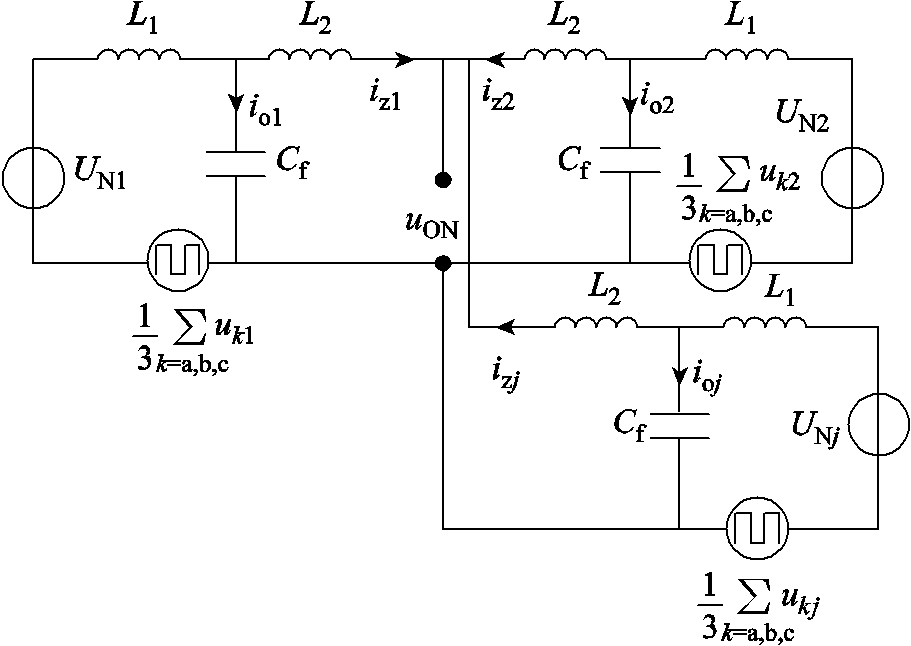

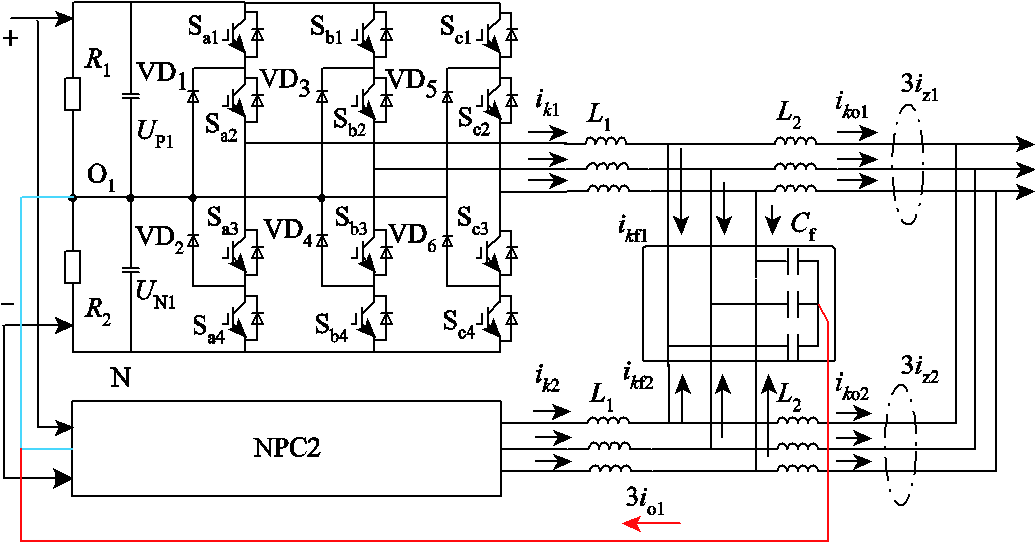

三电平模块化逆变器系统如图1所示,R1、R2为均压电阻,L1、L2为滤波电感,Cf为滤波电容。对由M个逆变器并联的系统中的逆变器j(1≤j≤M),UPj和UNj分别为其直流侧上、下电容电压,Oj为直流中性点,Sa1~Sa4为A相桥臂的4个IGBT,Sb1~Sb4为B相桥臂的4个IGBT,Sc1~Sc4为C相桥臂的4个IGBT,VD1~VD6为钳位二极管,kj为k相桥臂输出端口,k=a, b, c,ikj为k相电感电流,ikfj为k相电容电流,ikoj为k相输出电流。由于逆变器直流侧共享正负母线P、N和交流母线,逆变器模块间会产生环流,由于控制环节及滤波环节的存在,环流的成分主要为零序环流izj,以逆变器j和i为例,来分析零序环流的通路。

图1 三电平模块化逆变器系统

Fig.1 Three level modular inverter system

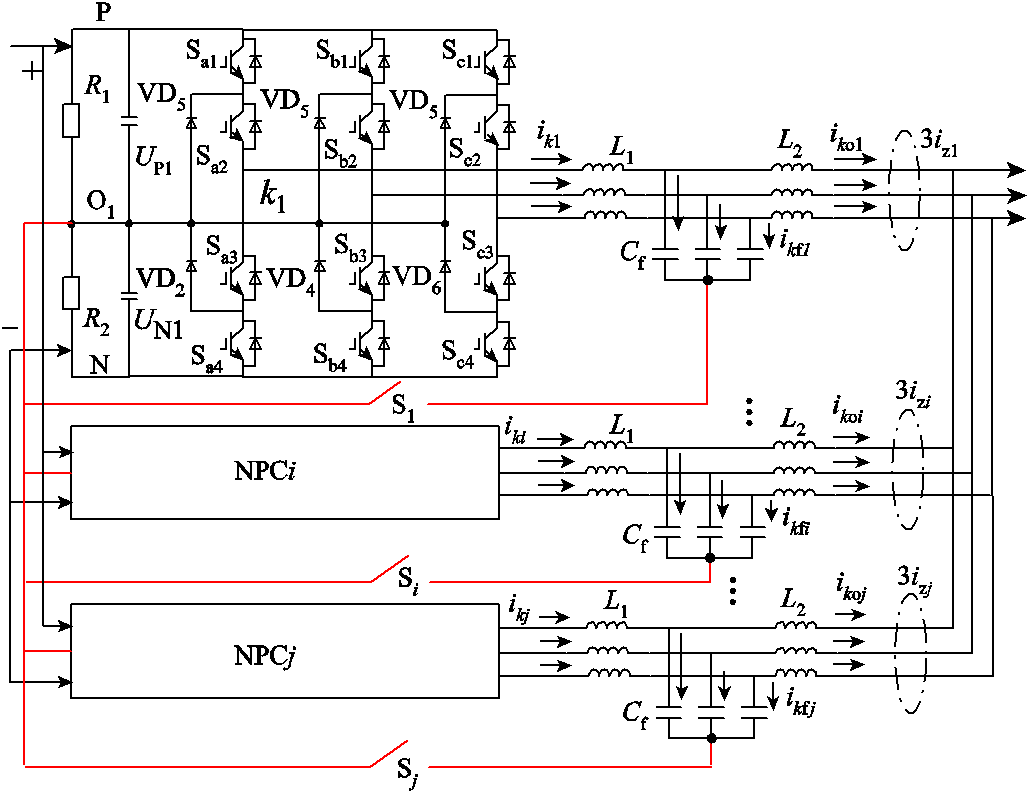

由于各逆变器每相桥臂有三种不同的开关状态,那么逆变器j和i并联时,每相桥臂将形成32=9种零序环流的环路。定义逆变器j的开关函数为Skj且假设环流从逆变器j流出。可列举各个零序回路见表1。

表1 零序环流激励源和路径

Tab.1 Excitation source and path of zero sequence circulation

环路路径SkjSki激励源 1P-kj-L1-L2-L2-L1-ki-P110 2P-kj-L1-L2-L2-L1-ki-Oi-P10UPi 3P-kj-L1-L2-L2-L1-ki-N-P1-1Udc 4P-Oj-kj-L1-L2-L2-L1-ki-P01UPj 5PP-Oj-kj-L1-L2-L2-L1-ki-Oi-P00UPi-UPj 5NN-Oj-kj-L1-L2-L2-L1-ki-Oi-N00UNj-UNi 6N-Oj-kj-L1-L2-L2-L1-ki-N0-1UNj 7N-kj-L1-L2-L2-L1-ki-P-Oi-N-11Udc 8N-kj-L1-L2-L2-L1-ki-Oi-N-10UNi 9N-kj-L1-L2-L2-L1-ki-N-1-10

从表1可以看出,有些环路虽然存在物理上的路径,但由于没有激励源,所以不会产生零序环流,如回路1和9;相应地,有激励源的回路大部分都是由于开关状态不一致导致的。需要指出的是,当两个模块的同一桥臂开关状态都是0时,存在2个零序环流的流通路径,如图2所示。此时的激励源与并联逆变器的中点电位差异有关,与开关状态差异无关。此外,电感L1、L2均包含在零序环流环路中,会影响到零序环流的幅值,电容Cf并未包含在零序环流环路中,不会对零序环流造成影响。

图2 环路5P和5N

Fig.2 Loop 5P and 5N

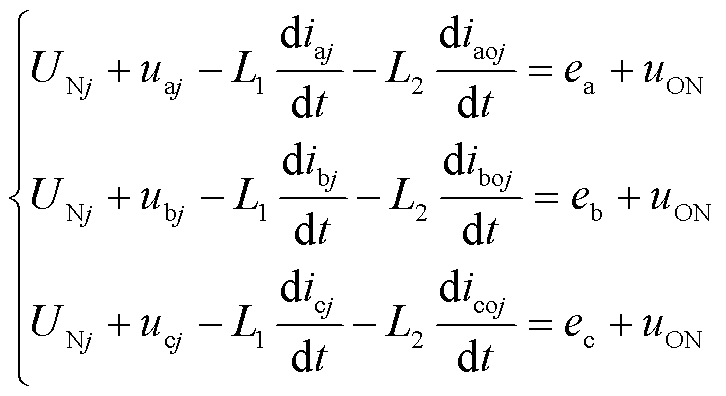

在图1所示的模块化三电平逆变器系统中,忽略开关管动态过程、电感和电容的等效电阻,根据基尔霍夫电压定律,建立NPC三电平逆变器的三相回路方程为

(1)

(1)

式中,ukj为逆变器j的k相桥臂输出对直流侧中点Oj的输出PWM电压;ek为电网或负载电压;uON为电网或负载中性点对负母线N的电压差。

根据零序环流的定义,此时izj可表示为

在电网或负载电压三相平衡时,式(1)中的各式分别相加,并代入式(2),可以得到

![]() (3)

(3)

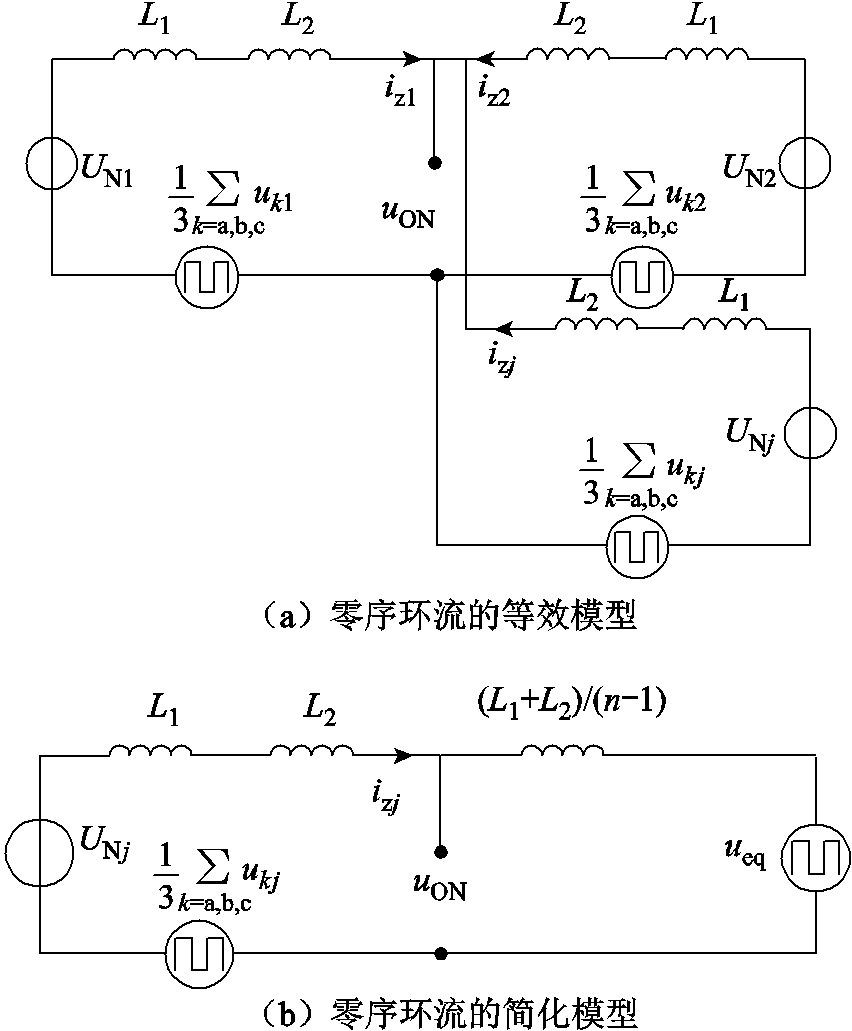

根据式(3)并运用基尔霍夫电压定律以及戴维南定理可以得到模块化NPC逆变器并联系统的零序环流电路模型,如图3所示。

图3 零序环流的电路模型

Fig.3 Circuit model of zero-sequence circulating current

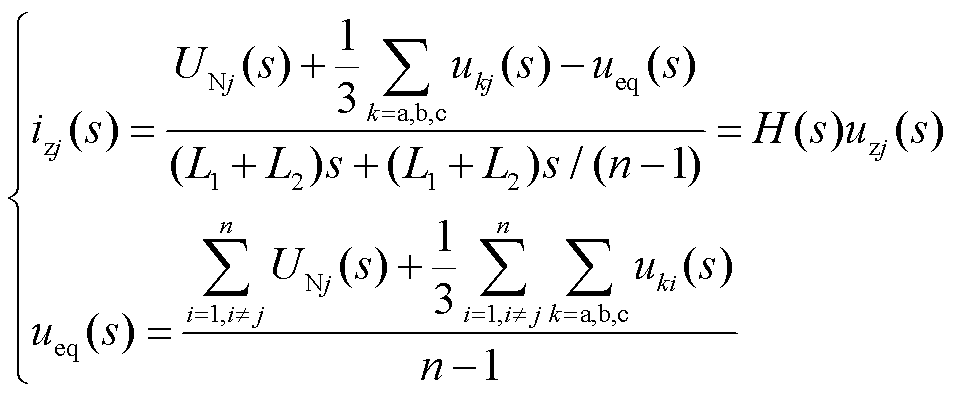

根据图3,逆变器j的零序环流可表示为

(4)

(4)

式中,H(s)为逆变器j的零序环流传递函数;uzj(s)为零序环流激励源的复频域表达式,即

(5)

(5)

从式(4)和式(5)可以看出,逆变器j的零序环流传递函数H(s)为一阶函数,且其衰减能力只与电感有关,电容不会影响零序环流的幅值,这与1.1节中分析环路时得到的结论相符。另外,从零序环流激励源的复频域表达式uzj(s)可看出,其激励源为各模块中点电位的差异和桥臂输出电压的差异,与1.1节中的分析相符。

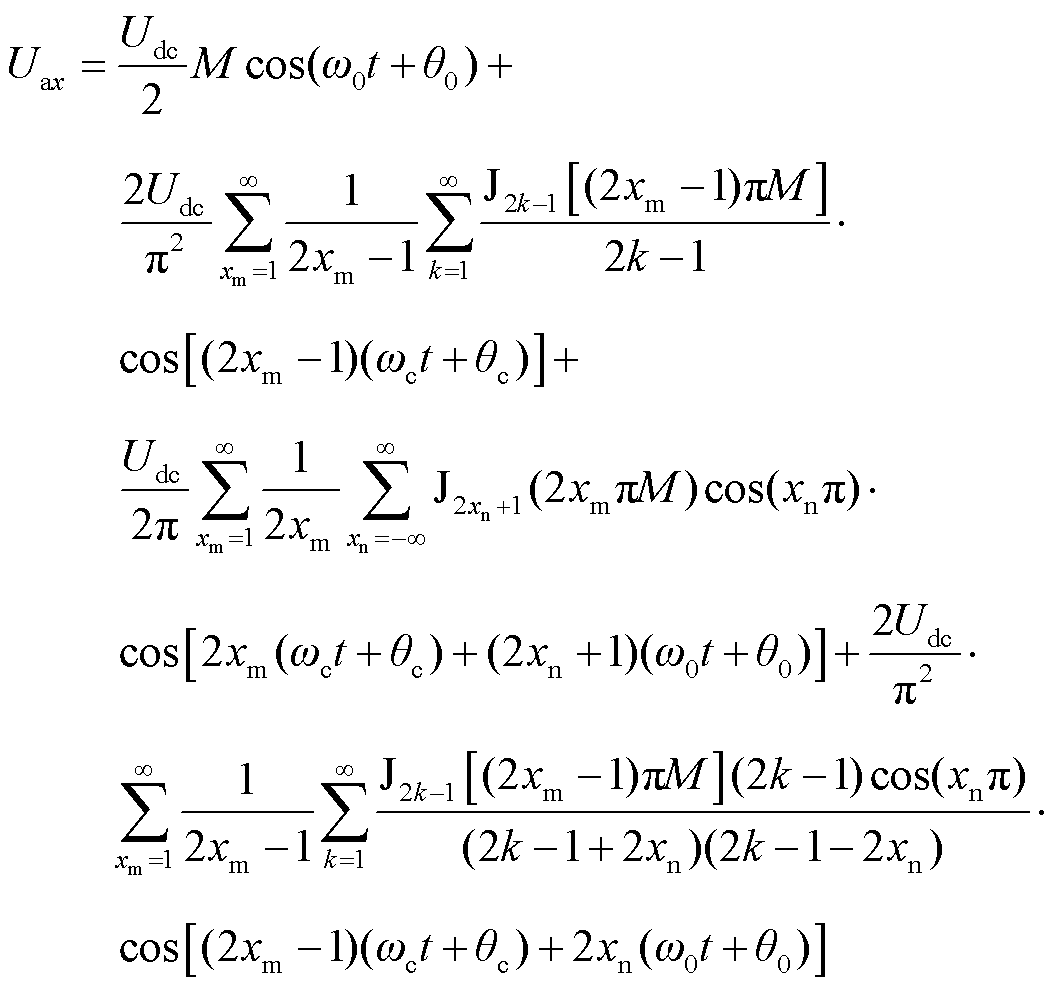

在各个逆变器模块共享中线的情况下,针对由于各模块桥臂输出电压差异引入的零序环流,可以进一步借助傅里叶变换分析桥臂的输出电压特性,从而量化零序环流。以两台载波同相层叠调制的逆变器为例,使用解析法可得逆变器j的A相桥臂输出PWM电压表达式Uax[18]为

(6)

(6)

式中,M为调制度;xm、ωc和θc分别为载波频次、载波信号角频率和相位偏移量;xn、ω0和θ0分别为基波频次、基波信号角频率和相位偏移量;Jn为第一类n阶贝塞尔函数,表达式为

![]() (7)

(7)

若同一相并联两桥臂载波相位差180°,则由式(6)可以求得A相桥臂输出电压差Uah,经过推导得到Uah为

(8)

(8)

其余两相类似。利用求得的桥臂电压差除以环路的阻抗,结合式(5),便得到某一频率下环流分量的幅值大小,即

![]() (9)

(9)

借助式(9)便可分析和量化不同频率成分的零序环流。

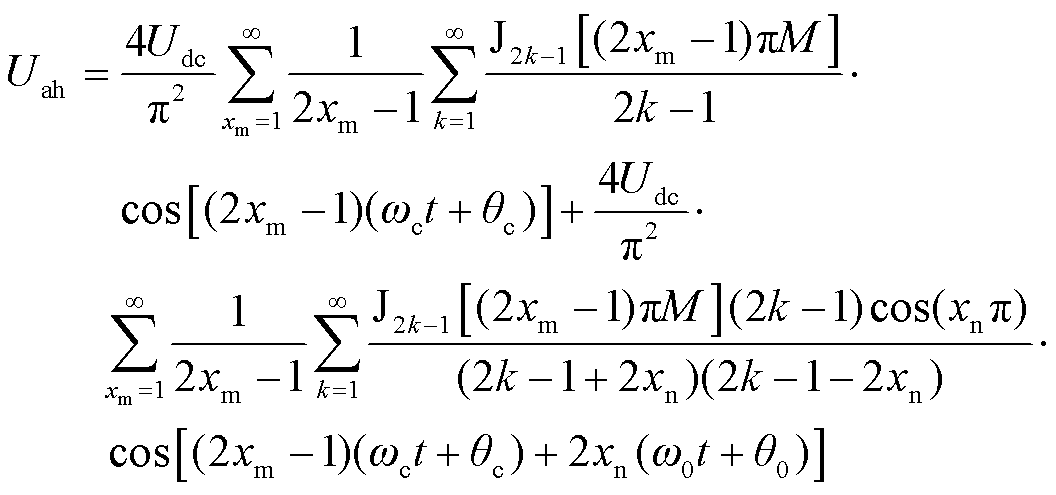

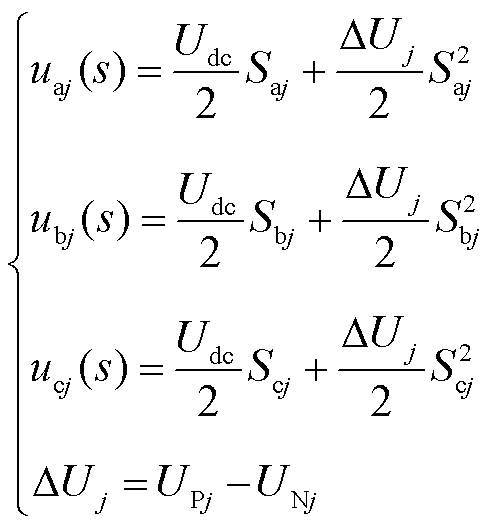

从式(4)和式(5)表示的零序环流模型中无法获得三电平零序环流的具体成分,因此引入开关函数进一步变换[17-18]为

(10)

(10)

根据式(5)和式(10),可得三电平逆变器j零序环流激励源的具体表达式为

(11)

(11)

由式(11)可知,零序环流存在的因素主要有以下三类:模块间中点电位差导致的Ⅰ类零序环流(通态零序环流)、模块间开关状态差异导致的Ⅱ类零序环流(开关零序环流)及模块间中点电位和开关状态差异导致的Ⅲ类零序环流(混合零序环流)。

2.1.1 通态零序环流

通态零序环流表达式为![]() ,这部分激励与各三电平逆变器间的中点电位之差有关,中点电位的波动与差异集中在低频,其对应环路5。在正常工作时,各模块具有基本相同的调制度和功率因数,因此中点电位基本一致,此时通态零序环流激励接近。然而当部分逆变器进行模式切换或者投切负载时,其调制度和功率因数会发生突变,从而产生瞬间的动态零序环流冲击。

,这部分激励与各三电平逆变器间的中点电位之差有关,中点电位的波动与差异集中在低频,其对应环路5。在正常工作时,各模块具有基本相同的调制度和功率因数,因此中点电位基本一致,此时通态零序环流激励接近。然而当部分逆变器进行模式切换或者投切负载时,其调制度和功率因数会发生突变,从而产生瞬间的动态零序环流冲击。

2.1.2 开关零序环流

开关零序环流表达式为![]() ,这部分零序环流的产生是由于并联逆变器的开关状态不一致,对应的环路为环路2~4和环路6~8。对于各逆变器模块,开关状态序列的不同,是高频载波信号和低频调制波信号不严格一致导致的结果,这种不同步使由载波与调制波交点而决定的开关管动作时刻存在差别,进而促使此部分零序环流的产生,表现为与三电平逆变器的共模电压差异相关。因此开关零序环流含有低频分量和高频分量。低频分量主要分布在基频的整数倍,可以通过控制方法抑制;高频分量分布在开关频率整数倍及其附近的边带频率,较难通过有限带宽的控制器来解决。

,这部分零序环流的产生是由于并联逆变器的开关状态不一致,对应的环路为环路2~4和环路6~8。对于各逆变器模块,开关状态序列的不同,是高频载波信号和低频调制波信号不严格一致导致的结果,这种不同步使由载波与调制波交点而决定的开关管动作时刻存在差别,进而促使此部分零序环流的产生,表现为与三电平逆变器的共模电压差异相关。因此开关零序环流含有低频分量和高频分量。低频分量主要分布在基频的整数倍,可以通过控制方法抑制;高频分量分布在开关频率整数倍及其附近的边带频率,较难通过有限带宽的控制器来解决。

2.1.3 混合零序环流

混合零序环流表达式为![]()

![]() ,可以看出,这部分的环流激励是由于开关状态不完全一致以及中点电位的综合影响产生的,这部分环流与开关零序环流类似,同样分为低频和高频分量。

,可以看出,这部分的环流激励是由于开关状态不完全一致以及中点电位的综合影响产生的,这部分环流与开关零序环流类似,同样分为低频和高频分量。

通过2.1节的分析可知,并联三电平NPC逆变器零序环流的成分较为复杂,包括通态零序环流、开关零序环流和混合零序环流。后两者还分为低频和高频分量。为了更好地抑制各类零序环流,有必要在硬件以及软件两方面分别对其进行抑制。

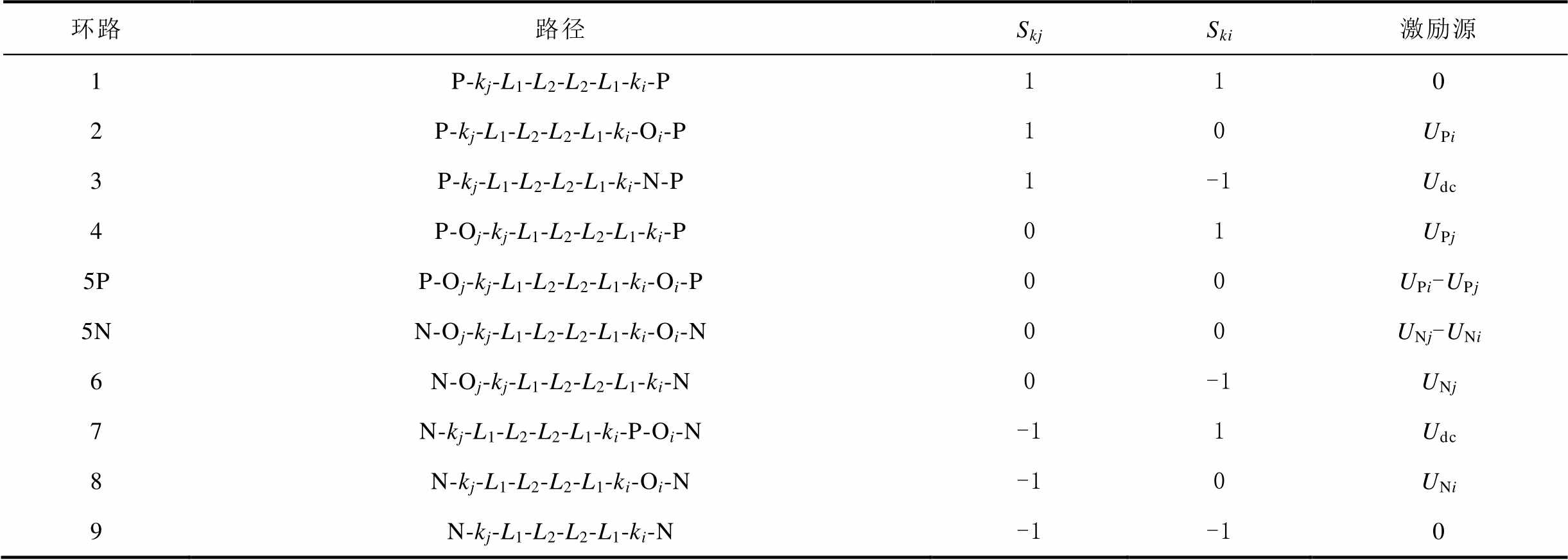

2.2.1 通态零序环流的抑制

通态零序环流是三电平模块化逆变器特有的零序环流,它与并联逆变器的开关状态无关,是并联的三电平逆变器的中点电位之差引起的。为了抑制此类零序环流,可以将各个模块的直流侧电容中点连接起来,形成共享中线,如图2b所示。

对比图2a、图2b可以看出,共享中线的措施影响了通态零序环流的路径:共享中线前,环路5经过正负母线形成回路;共享中线后,环路5直接经由连接的中点形成了闭合回路。同时,由于各模块直流侧中点相连,各逆变器中点电位相等,从而有

由式(11),此时通态零序环流激励为0,虽然环路路径存在,但激励源却被消除,此时的环路5只作为续流路径存在。因此共享中线是一种简易的、不需复杂控制的消除通态零序环流的措施。

2.2.2 开关零序环流和混合零序环流的抑制

保持共享中线后,混合零序环流中由中点电位引起的环流也可被消除,因此所有环流中只剩下由于开关状态不一致所导致的高频和低频分量。

高频分量出现的主要原因是载波不同步,虽然载波交错移相能改善输出波形,然而却增加了高频零序环流的大小,实际工程中也存在载波信号延时,因此高频的零序环流普遍存在。受限于控制器的带宽,此类高频分量很难通过控制策略来抑制。为了抑制高频的开关零序环流,一般采用一种将交流侧滤波电容中点连接到直流侧中性点的改进型LCL滤波器的方案,即将图1中开关S1~Sj闭合。

此时每个逆变器会多出一条在自身内部流通的路径Oj-kj-L1-Cf-Oj。需要指出的是,这部分路径的电流不在两个逆变器间流通,不被算作环流。

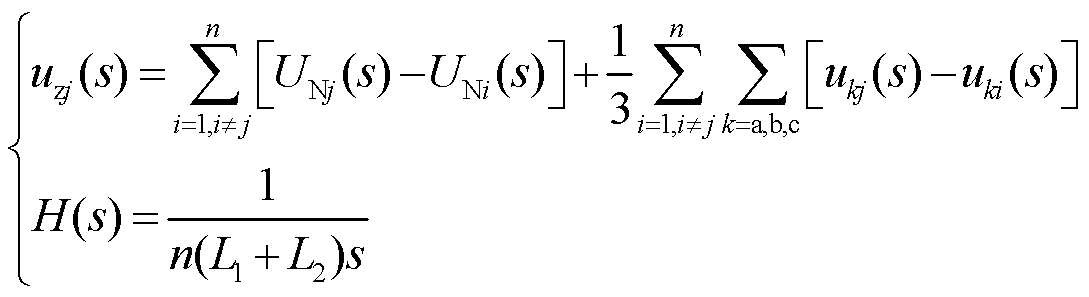

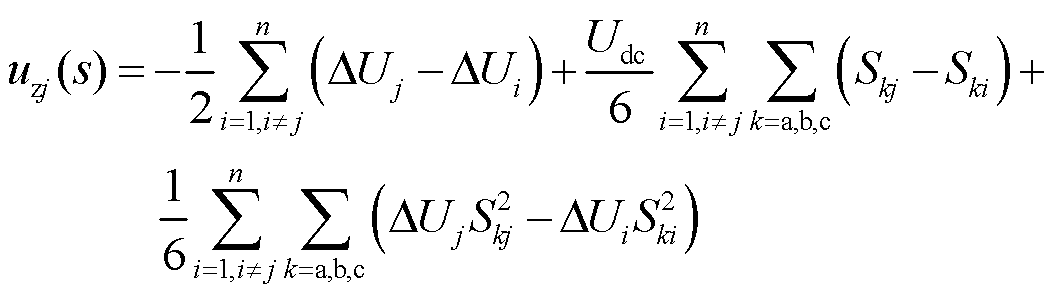

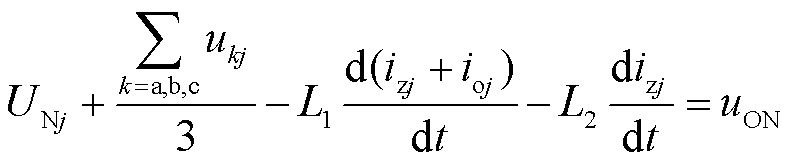

针对闭合开关S1~Sj后的图1,列写逆变器j新增路径的基尔霍夫电压定律方程为

(13)

(13)

由于此时新增了包含滤波电容的路径,因此逆变器j的零序环流式(2)需要重新定义为

![]() (14)

(14)

同样在电网或负载电压三相平衡时,式(1)中各式分别相加,并代入式(14),可以得到

(15)

(15)

根据戴维南定理,可以得到改进型LCL的零序环流电路模型如图4所示。

图4 基于改进型LCL滤波器的零序环流等效电路模型

Fig.4 Zero sequence circulation equivalent circuit model based on improved LCL filter

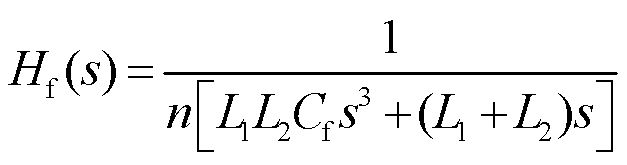

类似地,此时逆变器j的零序环流传递函数Hf(s)为

(16)

(16)

对比式(5)和式(16),采用改进型LCL滤波器后零序环流传递函数由一阶变成三阶。这是由于添置连接电缆后,形成的电容支路为高频零序环流提供了一条低阻旁路,从而提高了对零序环流高频分量的衰减能力。输出侧原有的高频零序环流被分流至这条电容支路上,抑制输出侧零序环流的同时却增大了电容支路连接电缆的电流应力,引入了额外的高频纹波干扰,因此本文对传统改进型LCL进行了改善和优化,提出载波移相控制下的模块共用滤波电容方案,具体分析将在3.2节论述。

对于基频及其整数倍的低频分量,可采用零序环流控制器抑制,结合比例-积分与比例-谐振控制器的优点,本文采用准PIR控制器抑制零序环流中的直流分量和三倍频分量,其传递函数为

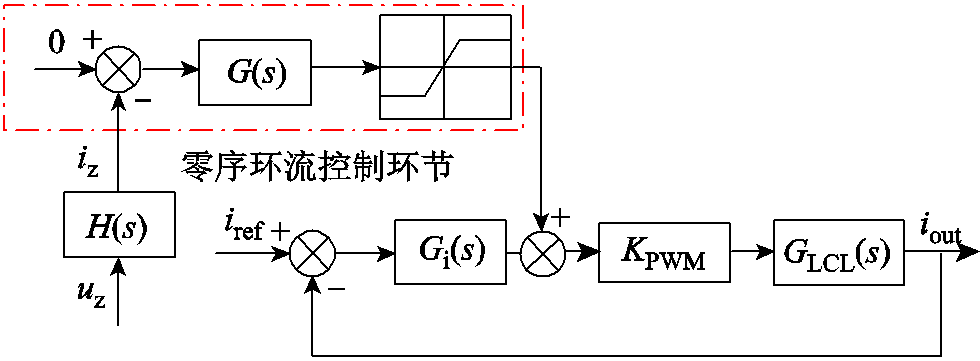

式中,Kp、Ki、Kr3分别为比例系数、积分系数和3次谐振系数;ωc3、ω03分别为谐振环节的截止角频率和谐振角频率。其控制框图如图5所示。其中,H(s)为零序环流的环路传递函数,G(s)、Gi(s)、GLCL(s)分别为零序环流控制器传递函数、电流控制器传递函数以及LCL滤波器传递函数,KPWM为逆变器传递函数。

图5 零序环流控制框图

Fig.5 Zero sequence circulating current control block diagram

根据系统稳定裕度的要求可以设计出准PIR控制器的参数[13]:Kp=5.5,Ki=20,Kr3=20,ωc3=15 rad/s,ω03=942 rad/s。此时的控制器在三倍频处有较大的开环增益,能更有效地抑制含有基频整数倍的低频零序环流。

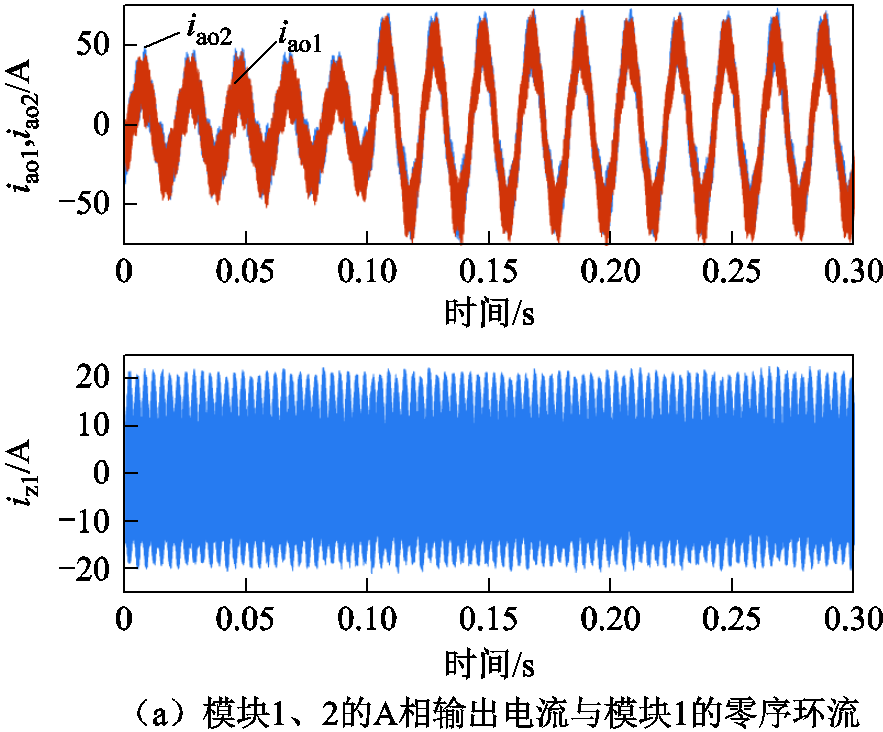

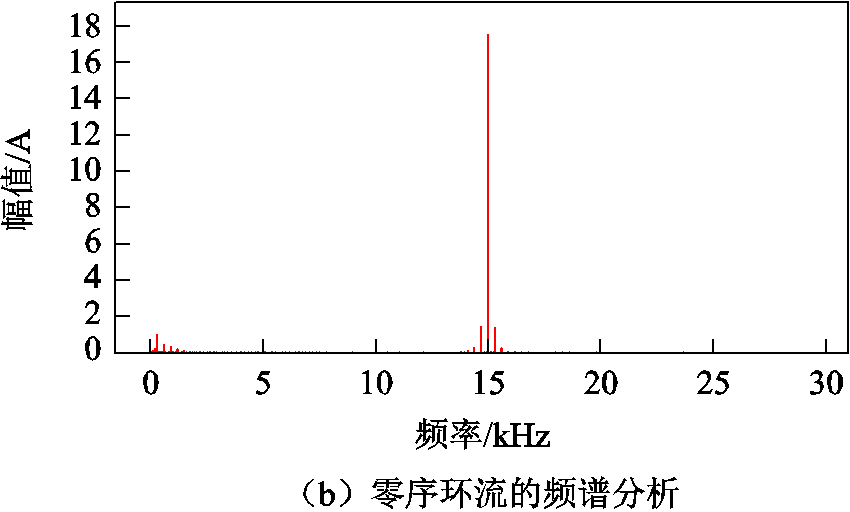

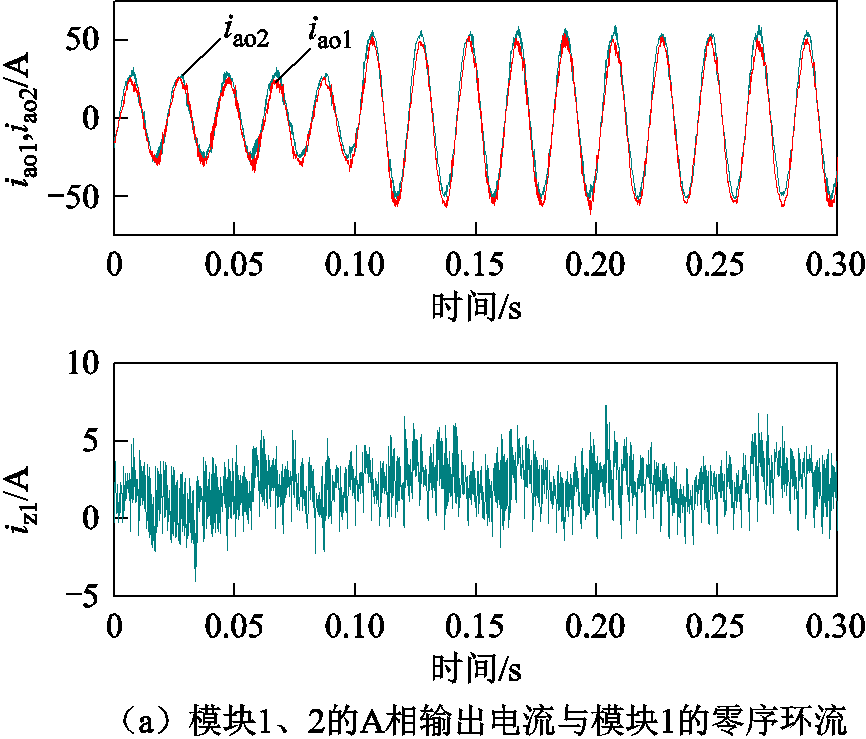

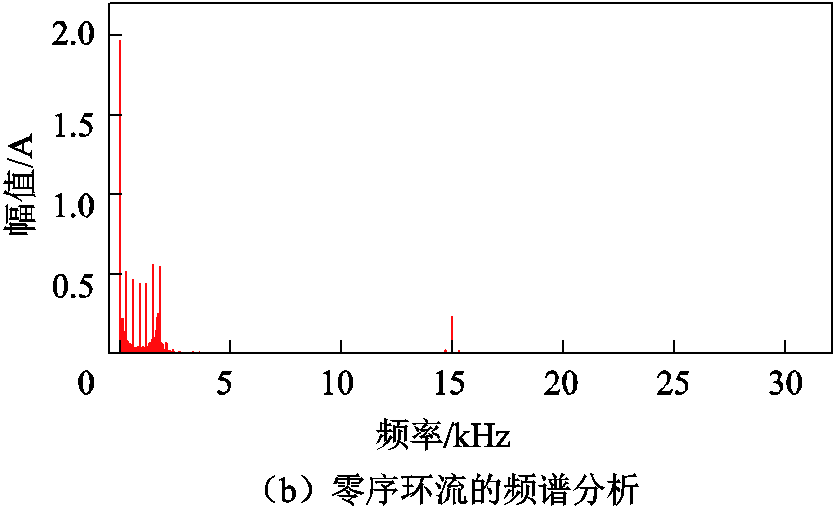

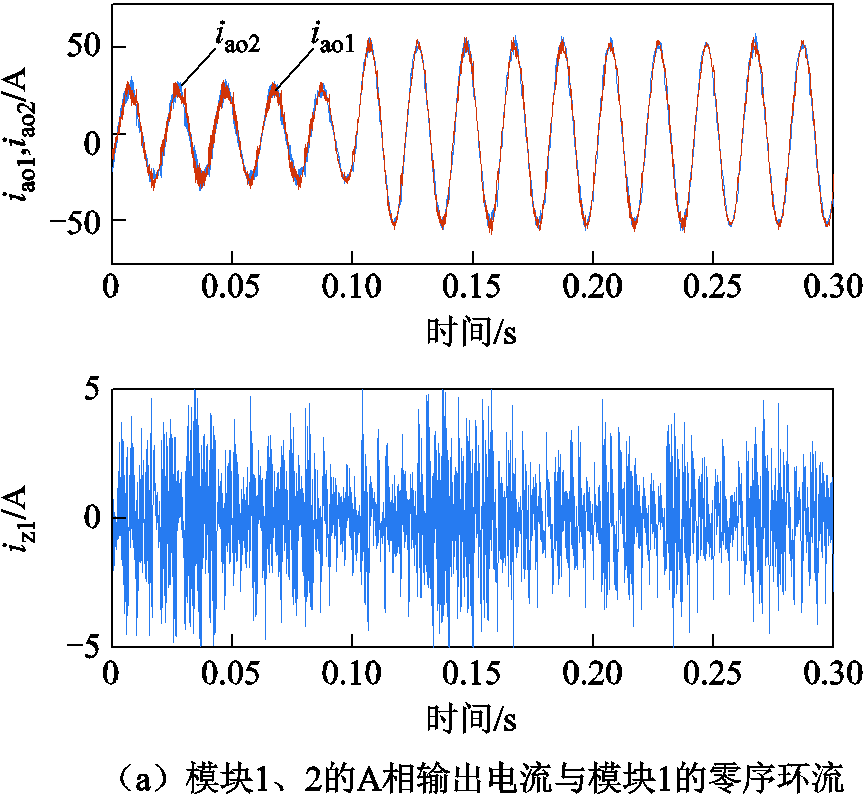

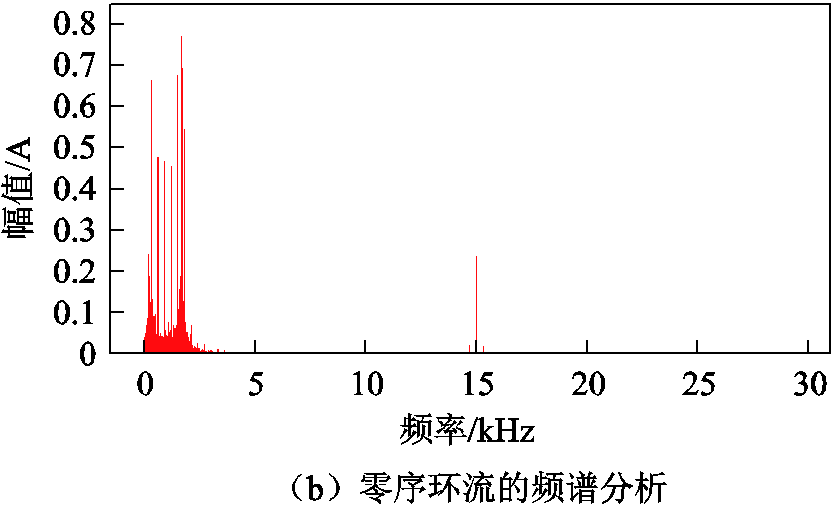

本文提出了共享直流侧中线方法,使用改进型LCL滤波器的硬件措施以及使用低频环流准PIR控制的软件措施,验证所提策略的有效性,现对比三种方案下的零序环流以及模块A相输出电流波形与频谱情况。方案一:无任何措施;方案二:只采取硬件措施;方案三:采取硬件+软件措施。仿真参数见表2,仿真中使用了2台NPC逆变器交错并联,载波相差180°以模拟零序环流最恶劣的情况。采用三种方案的仿真波形如图6~图8所示。

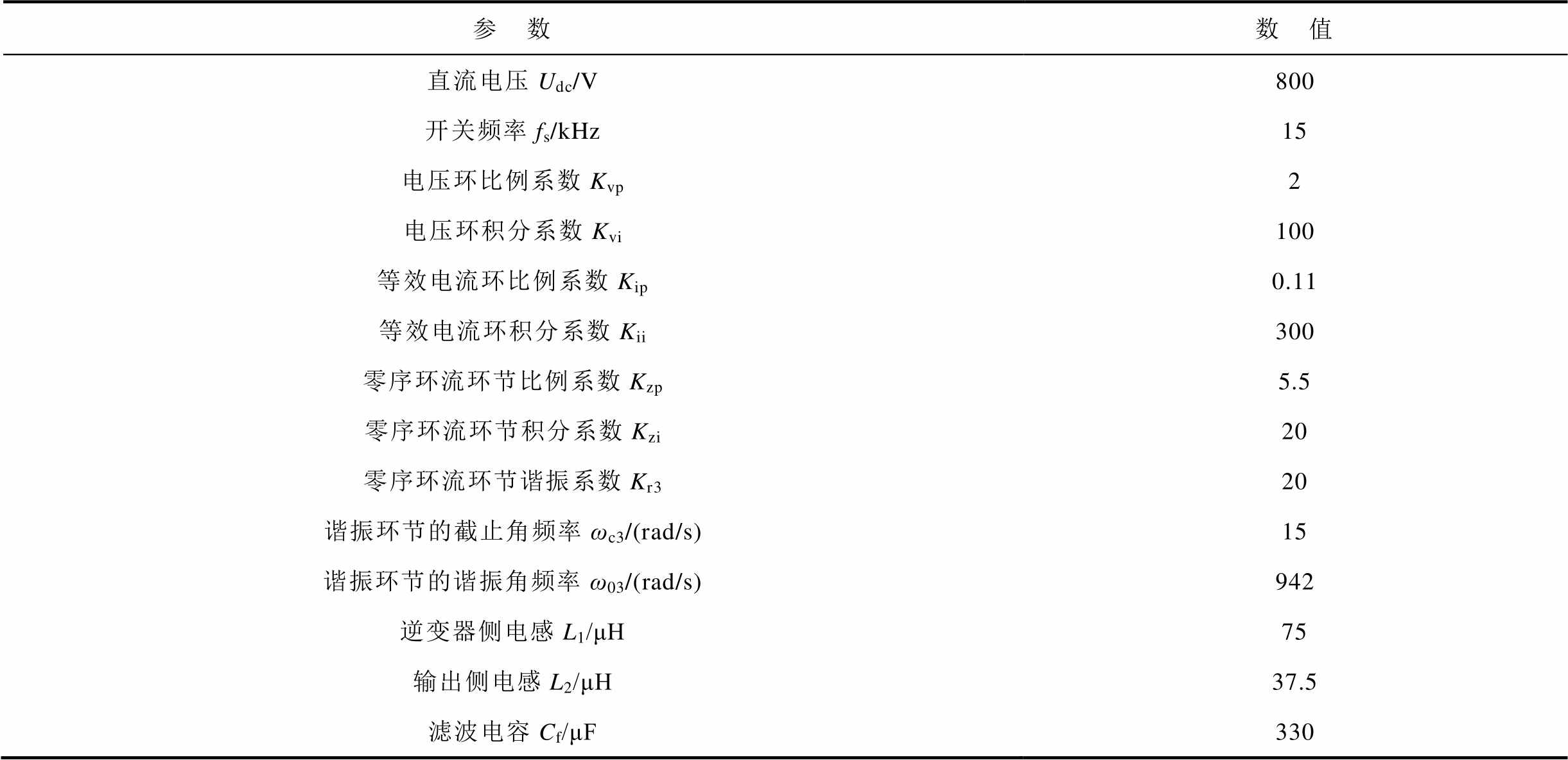

表2 模块化三电平逆变器仿真参数

Tab.2 Simulation parameters of modular three-level inverter

参 数数 值 直流电压Udc/V800 开关频率fs/kHz15 电压环比例系数Kvp2 电压环积分系数Kvi100 等效电流环比例系数Kip0.11 等效电流环积分系数Kii300 零序环流环节比例系数Kzp5.5 零序环流环节积分系数Kzi20 零序环流环节谐振系数Kr320 谐振环节的截止角频率ωc3/(rad/s)15 谐振环节的谐振角频率ω03/(rad/s)942 逆变器侧电感L1/μH75 输出侧电感L2/μH37.5 滤波电容Cf/μF330

对比各方案输出侧零序环流及电流的波形与频谱,方案一中零序环流幅值较大且含有低频分量和高频分量;采用方案二后,零序环流幅值得到限制且高频分量被抑制;采用方案三后,低频零序环流幅值减小,输出电流波形质量得到进一步改善。

图6 采用方案一时的仿真波形

Fig.6 The simulation waveforms with Scheme 1

图7 采用方案二时的仿真波形

Fig.7 The simulation waveforms with Scheme 2

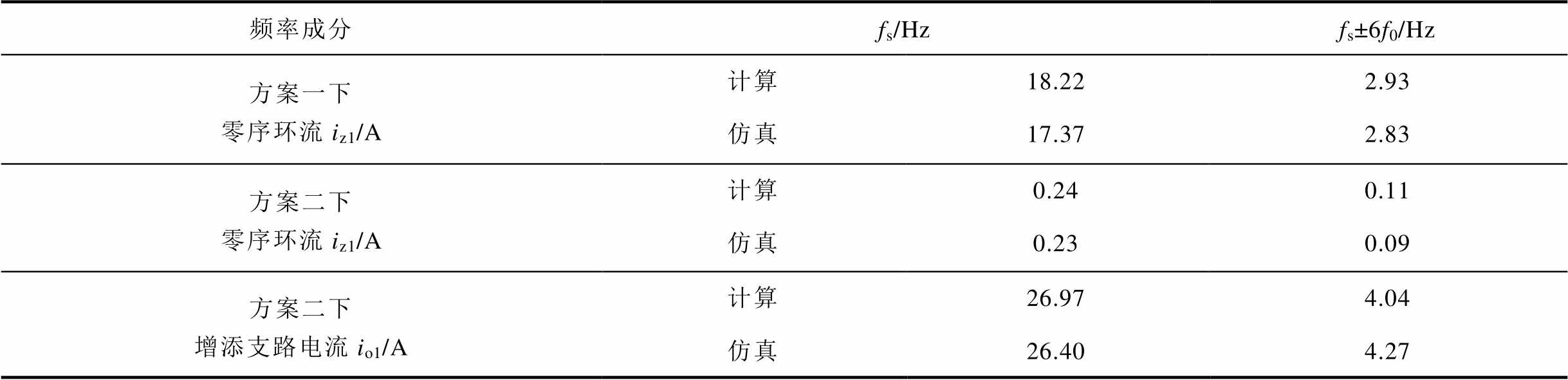

同时由式(8)、式(9)、图3、图4及对应支路分流关系,利用Matlab计算不同方案下开关频率次数附近的零序环流及增添支路电流幅值大小,与对应条件下的仿真结果对比,见表3。

图8 采用方案三时的仿真波形

Fig.8 The simulation waveforms with Scheme 3

表3 模块化三电平逆变器开关频率零序环流含量

Tab.3 Zero-sequence circulating current amplitude of switching frequency of modular three-level inverter

频率成分fs/Hzfs±6f0/Hz 方案一下零序环流iz1/A计算18.222.93 仿真17.372.83 方案二下零序环流iz1/A计算0.240.11 仿真0.230.09 方案二下增添支路电流io1/A计算26.974.04 仿真26.404.27

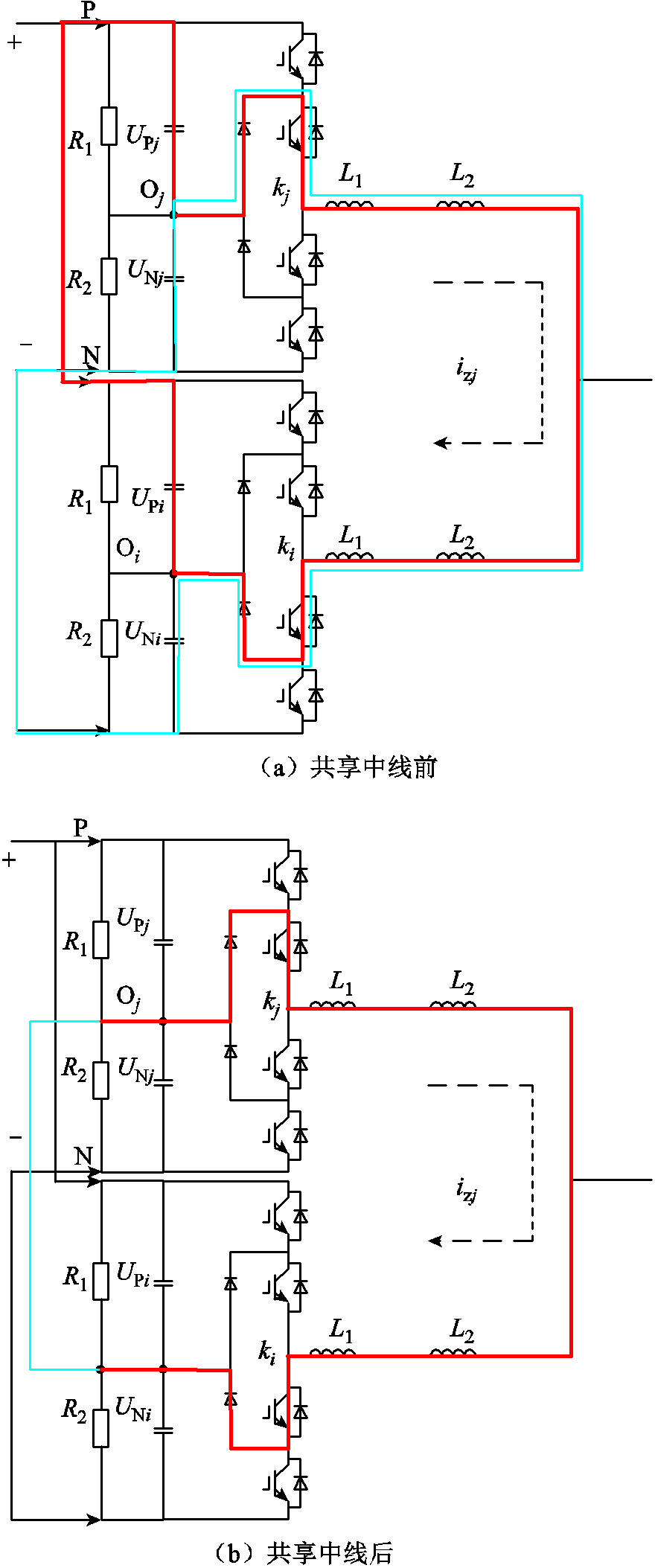

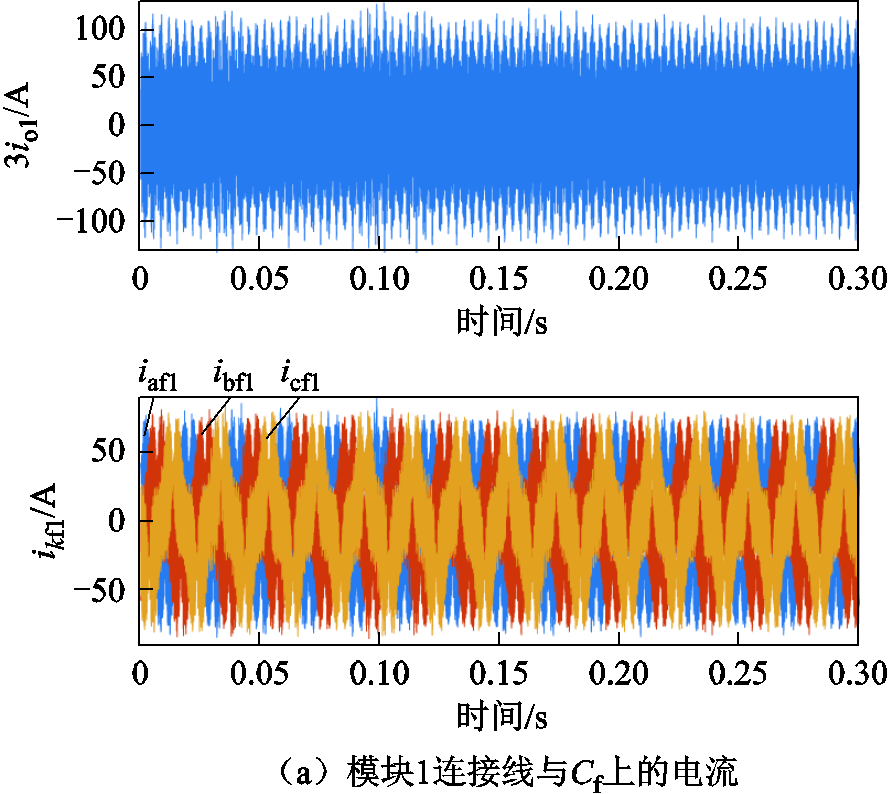

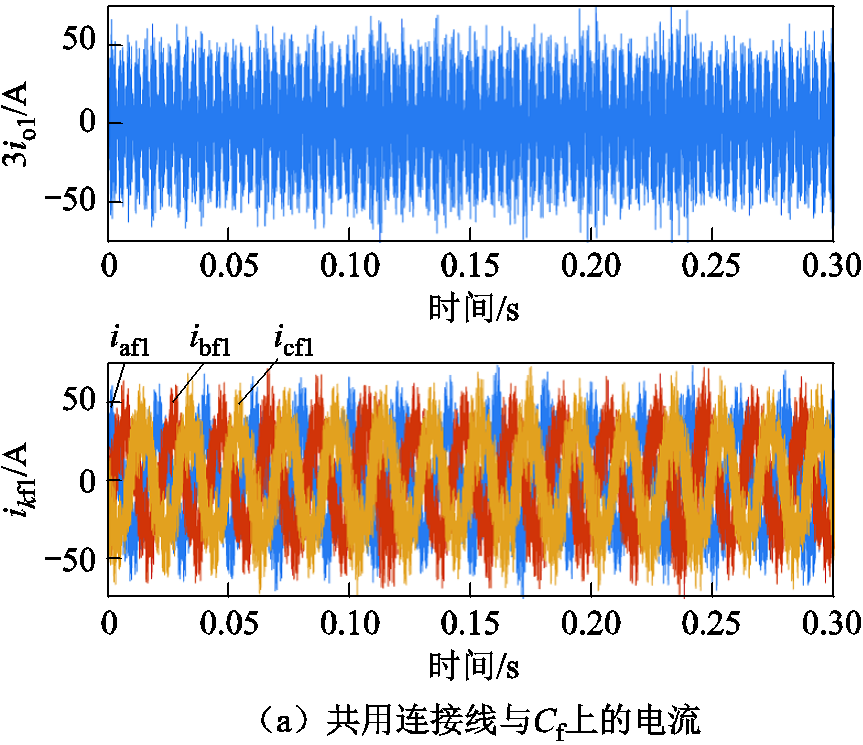

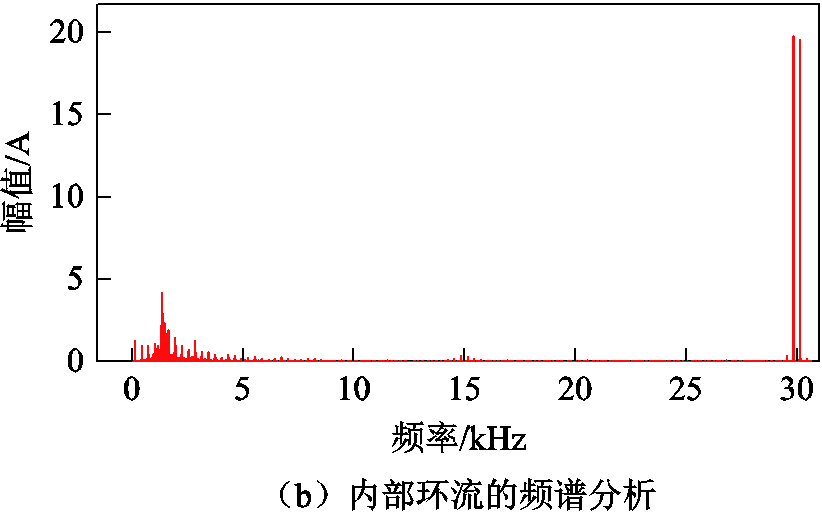

需要指出的是,3.1节提出的方案二和方案三均需采用传统改进型LCL滤波器:低成本的简易硬件操作对于输出侧的零序环流的改善具有显著作用。然而,这种方法将会使大量的开关纹波流过交流侧滤波电容以及连接电缆,传统硬件方案下内部环流与滤波电容电流仿真波形如图9所示。

由图9,并结合2.2.2节的分析可知,连接电缆使滤波电容进入了零序环流的等效电路中,为零序环流的高频分量提供了一条低阻通路,因此连接线上的电流主要为开关频率倍数次的高频分量。

考虑到载波移相控制下各模块间开关频率分量的特性,能以恰当的连接方式转移并抵消部分高频开关纹波。在保证对输出侧零序环流旁路作用生效及输出电流质量改善的基础上,以减小传统改进型LCL连接电缆电流为目的,提出一种模块共用交流侧滤波电容的改进方案,其原理如图10所示。

图9 传统硬件方案下内部环流与滤波电容电流仿真波形

Fig.9 Simulation waveforms of internal circulating current and filter capacitor current under traditional hardware scheme

图10 两模块共用电容时的改进型LCL方案

Fig.10 An improved LCL scheme for two modules sharing capacitance

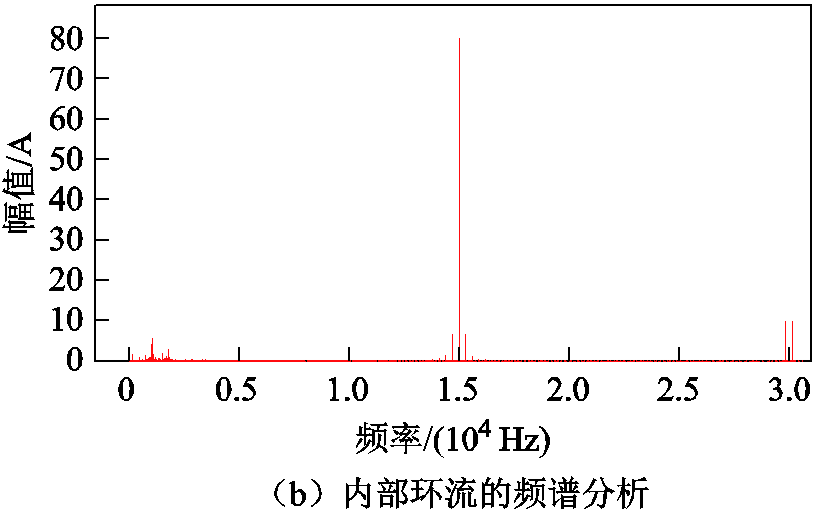

共用电容是使两个模块与一组电容并联,节省了一组电容器的消耗,在载波移相控制下,模块共用电容中转移并注入的奇数次开关频率纹波电流由于方向相反会被抵消。共用电容时内部环流与滤波电容电流仿真波形如图11所示。

图11 共用电容时内部环流与滤波电容电流仿真波形

Fig.11 Simulation waveforms of internal circulating current and filter capacitor current with improved sharing capacitance scheme

对比图9、图11,相较于传统的改进型LCL硬件方案,连接电缆上的电流(即内部环流)中原有的奇数次开关频率分量已被抵消,方向相同的偶数次开关频率的分量依旧存在且变为原来的2倍,但总体电流的幅值降低了近50%,有效地降低了高频纹波干扰。电容元件数量的减少为装置的成本尺寸优化提供了可能,对电容器组的可靠性提出了一定要求,但流经各个滤波电容的电流有一定程度的降低。因此共用电容方案能有效降低元件的电流应力,在降低连接电缆上高频电流纹波的同时保证了传统改进型LCL能滤除零序环流高频分量,减少其发热损耗的同时提高了元器件的使用寿命。

对于依旧存在的偶数次开关频率分量,则可以添加额外的LC陷波支路进行补偿[21]。

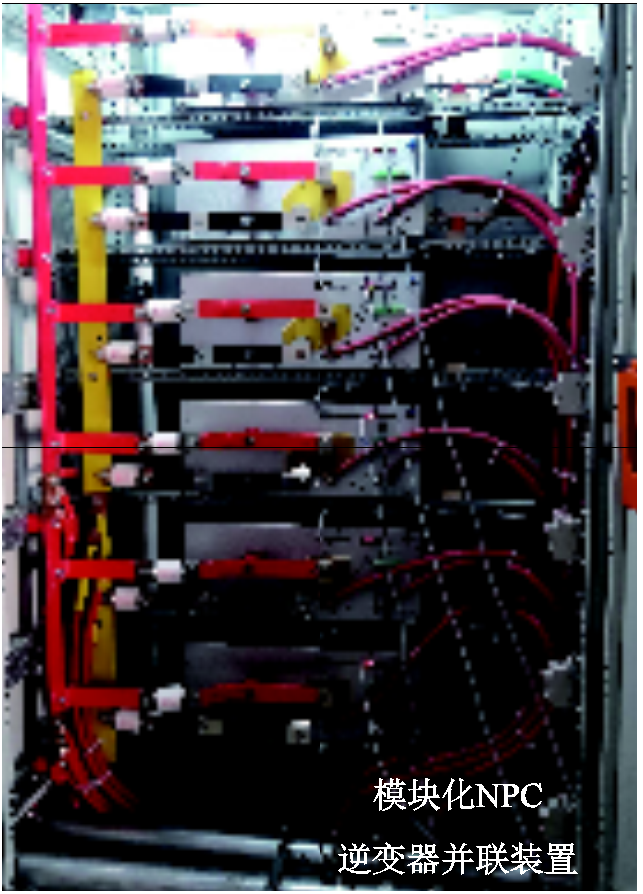

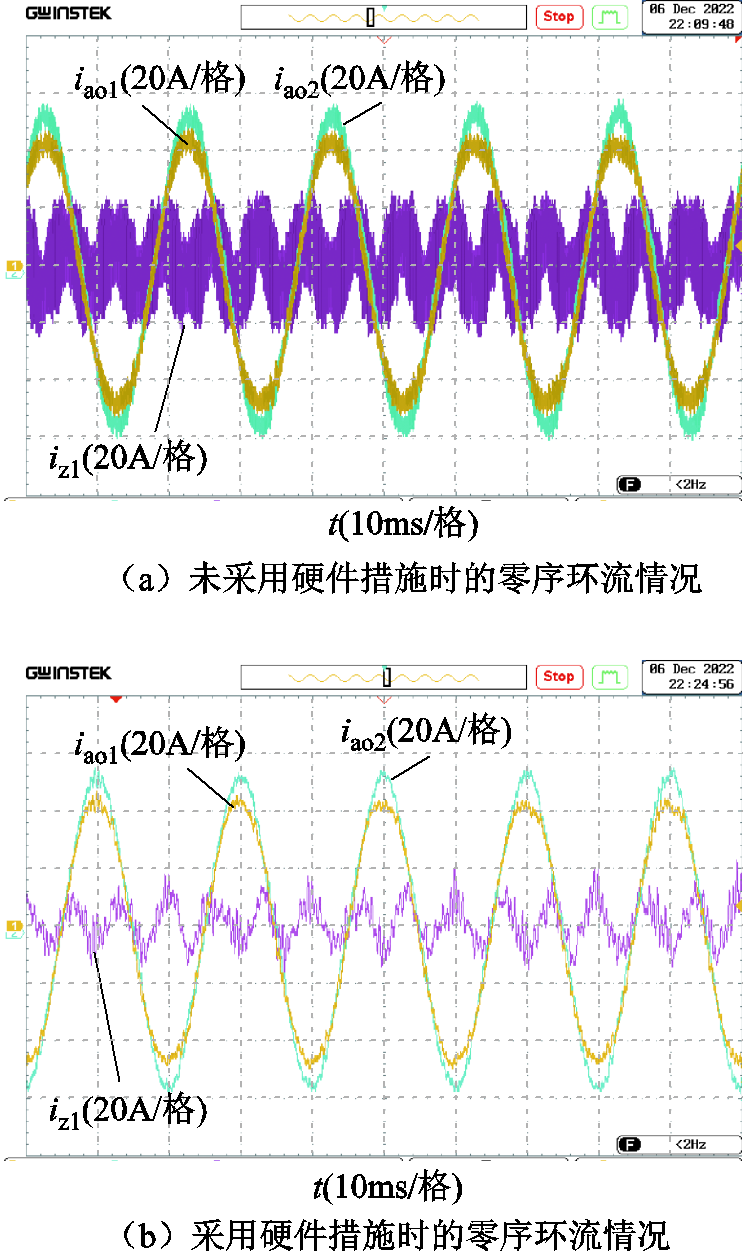

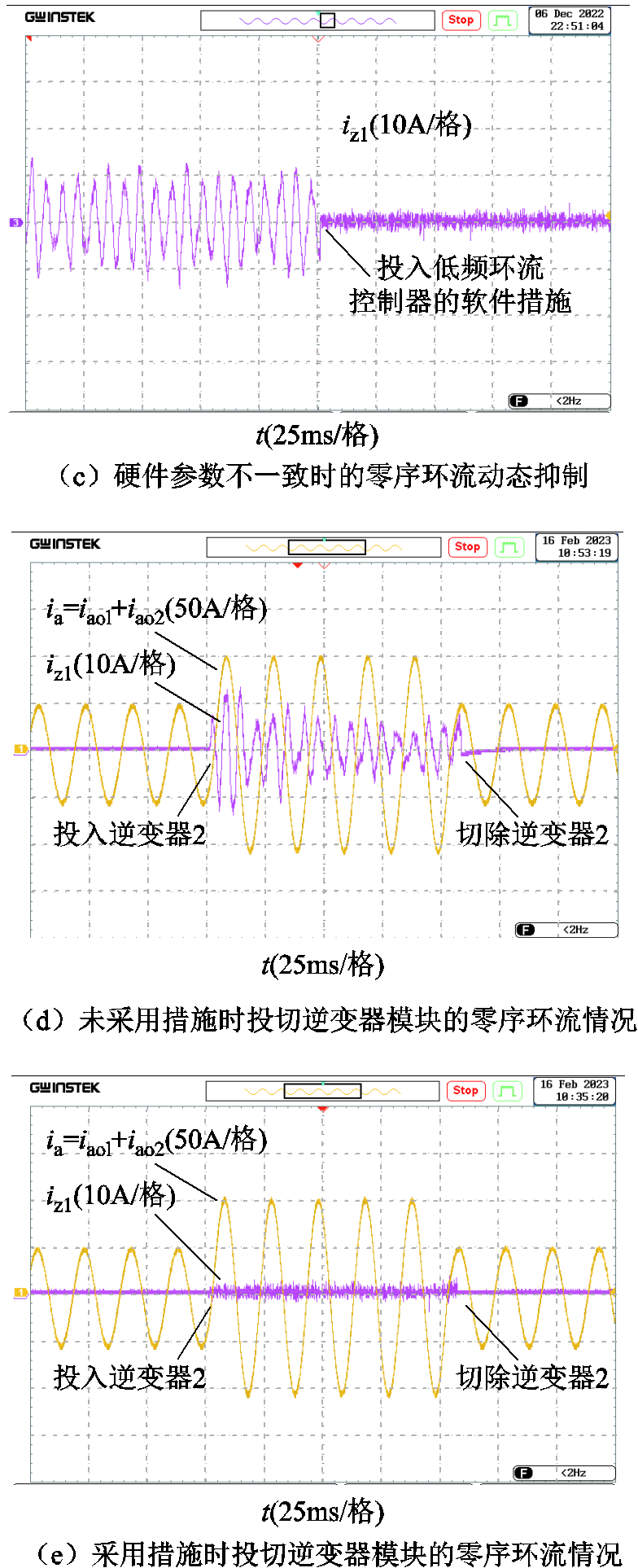

搭建了如图12所示的模块化NPC三电平逆变器并联系统实验样机,使用两模块进行实验验证。对比了采用本文所提硬件措施前后两模块输出电流及零序环流,证明了采取硬件措施能简单经济地消除零序环流中的高频分量,改善输出电流的波形质量,如图13a、图13b所示;另外,由于元器件工艺以及线路长度等因素,逆变器并联系统中各模块之间的硬件参数不一致是实际工程中的常见现象,通过投入使用本文所提出的软件措施,零序环流的幅值从10 A被限制为2 A,具有良好的动态抑制效果,如图13c所示;最后,逆变器并联系统中常常会由于不同应用场合所需功率容量的差异而投切模块,根据2.1.1节的分析,这时的零序环流的频率成分是低频的,主要是Ⅰ类的通态零序环流。在各个逆变器模块正常运行时,各模块中点电位的差异很小可以忽略不计,此时产生的Ⅰ类零序环流很小;然而,当部分逆变器模块投切时,考虑到电容、均压电阻等硬件参数不一致的影响,处于不同状态模块的中点电位存在很大差异,模块间的均流不能快速达到较为理想的效果,那么在投切后就会产生零序环流。采取本文提出的共享中线和软件控制措施,投切逆变器模块所引入的动态零序环流冲击得到了较好地抑制,如图13d、图13e所示。

图12 模块化NPC三电平逆变器并联系统样机

Fig.12 Modular NPC three-level inverter parallel system prototype

图13 零序环流抑制实验波形

Fig.13 Experimental waveforms of zero sequence circulating current suppression

本文建立了NPC型三电平逆变器并联系统的零序环流等效模型,分析了零序环流的具体成分及形成机制。分别提出共享中线和改进型LCL滤波器等硬件抑制措施及准PIR调节的软件抑制措施,同时,针对采用传统改进型LCL滤波器后有较大高频分量流经连接交直流电容中点电缆的缺陷,提出了一种载波移相控制下模块共用滤波电容的优化方案。最后通过仿真与实验证明了本文提出的各类零序环流抑制策略及载波移相下模块共用滤波电容解决方案的有效性。通过本文的研究,可以得到以下结论:

1)针对模块化NPC三电平逆变器并联系统中更为复杂的零序环流,需要综合采用本文所提的硬件和软件措施以更有效可靠地抑制零序环流。

2)与传统改进型LCL相比,载波移相控制下模块共用滤波电容方案在保持原有的零序环流抑制效果的同时,实现了奇数次开关频率纹波分量转移与抵消,使连接电缆上的高频纹波减小近50%。

3)载波移相控制下的模块共享滤波电容方案节省了电容元件的消耗,降低了元件线路的电流应力与发热损耗,为样机的高功率密度设计提供了可能。

参考文献

[1] 辛业春, 王延旭, 李国庆, 等. T型三电平并网逆变器有限集模型预测控制快速寻优方法[J].电工技术学报, 2021, 36(8): 1681-1692. Xin Yechun, Wang Yanxu, Li Guoqing, et al. Finite control set model predictive control method with fast optimization based on T-type three-level grid-connected inverter[J]. Transactions of China Electrotechnical Society, 2021, 36(8): 1681-1692.

[2] 陈杰, 章新颖, 闫震宇, 等. 基于虚拟阻抗的逆变器死区补偿及谐波电流抑制分析[J]. 电工技术学报, 2021, 36(8):1671-1680. Chen Jie, Zhang Xinyin, Yan Zhenyu, et al. Dead-time effect and background grid-voltage harmonic suppression methods for inverters with virtual impedance control[J]. Transactions of China Electrotechnical Society, 2021, 36(8): 1671-1680.

[3] 李杨, 帅智康, 方俊彬, 等. 基于阻抗测量的多逆变器系统稳定性校验方法[J]. 电力系统自动化, 2021, 45(11): 95-101. Li Yang, Shuai Zhikang, Fang Junbin, et al. Stability check method for multi-inverter system based on impedance measurement[J]. Automation of Electric Power Systems, 2021, 45(11): 95-101.

[4] 张占俊, 李建文, 董耀, 等. 弱电网下多逆变器并网谐振失稳分析方法[J]. 电气技术, 2020, 21(10): 21-28. Zhang Zhanjun, Li Jianwen, Dong Yao, et al. Method of resonance instability analysis of multiple grid-connected inverters in weak grid[J]. Electrical Engineering, 2020, 21(10): 21-28.

[5] 涂春鸣, 邹凯星, 高家元, 等. 基于不对称正负反馈效应的PQ功率控制并网逆变器稳定性分析[J]. 电工技术学报, 2023, 38(2): 496-509. Tu Chunming, Zou Kaixing, Gao Jiayuan, et al. Stability analysis of grid-connected inverter under PQ power control based on asymmetric positive-negative-feedback effects[J]. Transactions of China Electrotechnical Society, 2023, 38(2): 496-509.

[6] 郭寅远, 王龙, 李宗原, 等. 多模块三电平逆变器并联系统环流谐振抑制[J]. 电力电子技术, 2020, 54(11): 121-124. Guo Yinyuan, Wang Long, Li Zongyuan, et al. Circulating resonance suppression of multi module three-level inverter parallel system[J]. Power Electronics, 2020, 54(11): 121-124.

[7] Shen Zewei, Jiang Dong, Chen Jianan, et al. Circulating current reduction for paralleled inverters with modified zero-CM PWM algorithm[J]. IEEE Transactions on Industry Applications, 2018, 54(4): 3518-3528.

[8] Tcai A, Kwon Y, Pugliese S, et al. Reduction of the circulating current among parallel NPC inverters[J]. IEEE Transactions on Power Electronics, 2021, 36(11): 12504-12514.

[9] Xing Xiangyang, Li Xiaoyan, Qin Changwei, et al. An optimized zero-sequence voltage injection method for eliminating circulating current and reducing common mode voltage of parallel-connected three-level converters[J]. IEEE Transactions on Industrial Electronics, 2020, 67(8): 6583-6596.

[10] Jiang Dong, Shen Zewei, Wang Fei. Common-mode voltage reduction for paralleled inverters[J]. IEEE Transactions on Power Electronics, 2018, 33(5): 3961-3974.

[11] 李晓艳. 非隔离型三电平光伏并网逆变器安全高效控制技术研究[D]. 济南: 山东大学, 2020.

[12] Chen Alian, Zhang Zicheng, Xing Xiangyang, et al. Modeling and suppression of circulating currents for multi-paralleled three-level T-type inverters[J]. IEEE Transactions on Industry Applications, 2019, 55(4): 3978-3988.

[13] 张馨予, 张钢, 钱江林, 等. 具有低次谐波抑制能力的PIR控制器设计[J]. 电工技术学报, 2016, 31(增刊2): 19-27. Zhang Xinyu, Zhang Gang, Qian Jianglin, et al. Design of PIR controller with the ability of low harmonic damping[J]. Transactions of China Electrotechnical Society, 2016, 31(S2): 19-27.

[14] Ren Biying, Sun Xiangdong, Yu Majing, et al. Circulating current analysis and the improved D-Σ digital control strategy for multiparalleled three-level T-type grid-connected inverters[J]. IEEE Transactions on Industrial Electronics, 2020, 67(4): 2810-2821.

[15] 姚修远, 金新民, 杨捷, 等. 三电平逆变器并联系统的零序环流抑制技术[J]. 电工技术学报, 2014, 29(增刊1): 192-202. Yao Xiuyuan, Jin Xinmin, Yang Jie, et al. The technology of zero-sequence circulating current reduction for the parallel system of three-level inverters[J]. Transactions of China Electrotechnical Society, 2014, 29(S1): 192-202.

[16] Sun Kai, Lin Xiang, Li Yunwei, et al. Improved modulation mechanism of parallel-operated T-type three-level PWM rectifiers for neutral-point potential balancing and circulating current suppression[J]. IEEE Transactions on Power Electronics, 2018, 33(9): 7466-7479.

[17] 邵章平. 三电平光伏并网逆变器的模块化控制研究[D]. 合肥: 合肥工业大学, 2015.

[18] 陈甜甜. 交错并联三电平逆变器环流及中点平衡控制研究[D]. 合肥: 合肥工业大学, 2020.

[19] Li Xiaoyan, Xing Xiangyang, Zhang Chenghui , et al. Simultaneous common-mode resonance circulating current and leakage current suppression for transformerless three-level T-type PV inverter system[J]. IEEE Transactions on Industrial Electronics, 2019, 66(6): 4457-4467.

[20] Jiang Changpeng, Quan Zhongyi, Zhou Dehong, et al. A centralized CB-MPC to suppress low-frequency ZSCC in modular parallel converters[J]. IEEE Transactions on Industrial Electronics, 2021, 68(4): 2760-2771.

[21] 李林, 郭源博, 张晓华.双陷波开关频率滤波器LCLDT的设计[J]. 电工技术学报, 2017, 32(8): 256-263. Li Lin, Guo Yuanbo, Zhang Xiaohua. Design of a double-trap switching frequency harmonics filter LCLDT[J]. Transactions of China Electrotechnical Society, 2017, 32(8): 256-263.

Abstract Parallel operation of inverters is the most common and direct means to improve power capacity and power level. However, in parallel inverter system, zero-sequence circulating current (ZSCC) occurs because of the common AC and DC bus. This will lead to distortion of output current and additional device loss, which seriously threatens the stability of the parallel system. The ZSCC of neutral-point-clamped (NPC) three-level inverter parallel system studied in this paper is more complex than that of the two-level parallel inverters, and it is necessary to take both hardware and software measures to suppress it. Most of the existing studies focused on software control strategies to suppress ZSCC. For the use of hardware measures, following the traditional scheme was a common choice. Few studies have been done to improve the traditional hardware measures. This paper optimizes the connecting pattern of the improved LCL, which is a traditional hardware measure commonly used to suppress ZSCC, and forms a module shared capacitance scheme under carrier phase-shifting control. Compared with the traditional improved LCL, the added connection cable has smaller current ripple.

Firstly, the loop of circulating circuit is analyzed according to the switch state of the bridge-leg, and the mathematical and circuit model of ZSCC are established. The circulating current is also quantified by Fourier decomposition. Then, a switch function is introduced to further refine the category of ZSCC. For different types of ZSCC, the generation mechanism is explained, and hardware measures of sharing DC side midline and improved LCL and software measures of quasi-proportional-integral-resonance controller are proposed to suppress the corresponding ZSCC. Simulations and experiments show the validity of the proposed measures. At the same time, experiments show that the proposed methods are also feasible when hardware parameters of each inverter are inconsistent and the inverter modules are put in or removed.

In addition, it should be noted that there is a large high frequency current on the connection cable between the AC filter capacitor midpoint and the DC side capacitor midpoint in the traditional improved LCL. Its overall amplitude is around 100A during the simulation verification, which contains both odd switching frequency ripple with the amplitude of 80A and even switching frequency ripple with the amplitude of 20A. Therefore, an optimization scheme of module common filter capacitance under carrier phase-shifting control is proposed, which transfers the high frequency ripple at odd switching frequency to the common capacitance with no extra circuit. Since the current ripple at odd switching frequency is opposite under carrier phase-shifting control, the auto-cancellation of current ripple component at odd switching frequency is achieved and current ripple component at even switching frequency is doubled, but in general the total current on the connection cable is reduced by nearly 50% to about 50A.

The following conclusions can be drawn from the analysis: (1) For different types of ZSCC, the combined use of hardware and software measures mentioned in this paper can effectively and reliably suppress the ZSCC in the parallel system of NPC three-level inverters. (2) The module shared filter capacitance scheme under carrier phase-shifting control has smaller high frequency ripple on the connection cable and better electromagnetic performance of the device than traditional improved LCL hardware measures while the original effect of ZSCC suppression is maintained. (3) The module shared filter capacitance scheme under carrier phase-shifting control saves the consumption of capacitive components, reduces the current stress of components, which provides the possibility for the high power density design of the prototype.

Keywords:Neutral-point-clamped (NPC) three-level inverter, parallel inverters system, zero-sequence circulating current suppression, quasi-proportional-integral-resonant (PIR) controller, filter capacitor shared by modules, carrier phase-shifting control

DOI: 10.19595/j.cnki.1000-6753.tces.L10022

中图分类号:TM464

国防科工局稳定支持项目(6142217200403)和国家自然科学基金项目(52177191)资助。

收稿日期 2023-01-13

改稿日期 2023-02-16

徐 畅 男,1998年生,硕士研究生,主要研究方向为三电平逆变器并联系统,高功率密度电力电子技术。E-mail:changxu0825@whu.edu.cn

宫金武 男,1981年生,博士,副教授,主要研究方向为电能质量分析与治理、高效率高功率密度电力电子变换技术等。E-mail:gongjinwu@whu.edu.cn(通信作者)

(编辑 陈诚)