0 引言

随着可再生能源和储能系统的接入[1],以及船舶直流电力系统[2-3]、直流输电和直流电网[4]等相关技术的发展,系统容量越来越大,电压等级也越来越高,电力电子变换器通常由多个标准子模块通过串、并联组合而成。在对功率密度要求比较高的场合,需要利用开关速度更快、耐压更高的器件搭建电压等级更高的子模块,以减小变换器无源器件的体积,减少子模块数量,提高变换器的功率密度。

目前,Si IGBT 电压等级已经达到了6.5kV,但受限于开关损耗,其开关频率一般在几kHz 范围内。以碳化硅MOSFET 为代表的宽禁带半导体器件在开关损耗、高温特性、导通电阻等方面具有更优良的性能,被认为是新一代电力电子器件[5-6]。然而,受限于更高的工艺要求,目前常见的商用器件最高耐压等级为1.7kV,高压器件(>10kV)仅为少量实验室样片[7]。而通过将多个低电压等级的器件串联使用来提高电压等级,具有更低的成本,在经济上更有优势,更利于推广应用,且相比于单个器件,在导通电阻、电流容量等方面更具优势[8]。串联器件的关键在于如何避免器件承受的电压出现不均,而造成部分器件发生过电压击穿。

通过直接将低压器件首尾相连,并且所有器件同时开通和关断,可以提高等效耐压水平,此种方法的难点在于,如何实现串联器件在开关暂态的电压均衡[9]。为此,现有解决方案可分为两类,且各有其局限性[10]:①无源缓冲电路[11],通过吸收过电压脉冲能量实现电压基本均衡,是一种简单的解决方案,但会增加额外开关损耗,限制了其在高频高效场合的应用;②有源门极驱动[12-13],通过控制驱动电压以改变开关瞬态特性实现电压平衡,基本无额外开关损耗,但通常需要多个高精度、高带宽检测电路,增加了系统的成本和复杂度,此外,开关过程的非线性特性也对控制性能提出很大挑战。

不同于以上方法,结合不同拓扑结构构建通用的功率单元,利用电容电压对器件承受的电压进行钳位,避免开关暂态电压不均衡,是另一种提高器件等效耐压等级的手段。拓扑中器件顺序开关而非同时开关,以平衡电容电压,降低开关暂态的dv/dt,该方法在本文中称为间接串联方法。该方法多采用含有钳位电路的拓扑或者多电平拓扑。代表研究如ABB 公司利用类模块化多电平变换器结构设计的高压器件单元[14]、瑞士苏黎世联邦理工学院利用飞跨电容拓扑构建“super-switch”功率模块[15]、西安交通大学利用新型主动钳位电路构建的SiC MOSFET 串联半桥电路[16]等。间接串联方法的优点在于器件的开关暂态电压被电容电压钳位,从而提高了可靠性。但该方法的难点在于如何保证拓扑中的电容电压均衡,为此通常需要多个传感器来检测电容电压和负载电流,并配合闭环控制方法动态调整器件开关顺序。

鉴于此,本文提出一种二极管-电容混合钳位拓扑和准两电平调制方法构成的间接串联功率模块,其保留了间接串联方法的优点,同时还可实现拓扑中电容电压自均衡,避免了电压电流传感器和控制算法。此外,拓扑需要的电容容值很小,陶瓷贴片电容即可满足要求,因此整个拓扑被封装到一个功率模块中,并设计了一个集成驱动保护电路,二者一起构成了一个通用的中压功率模块,可应用于交流-直流电能变换和直流-直流电能变换等多种应用场合,具有体积小、集成度高等优点。损耗测试结果表明,每个器件的开关损耗相同,总损耗相较于其他串联方法甚至单个中压器件更小。

1 二极管-电容混合钳位拓扑分析

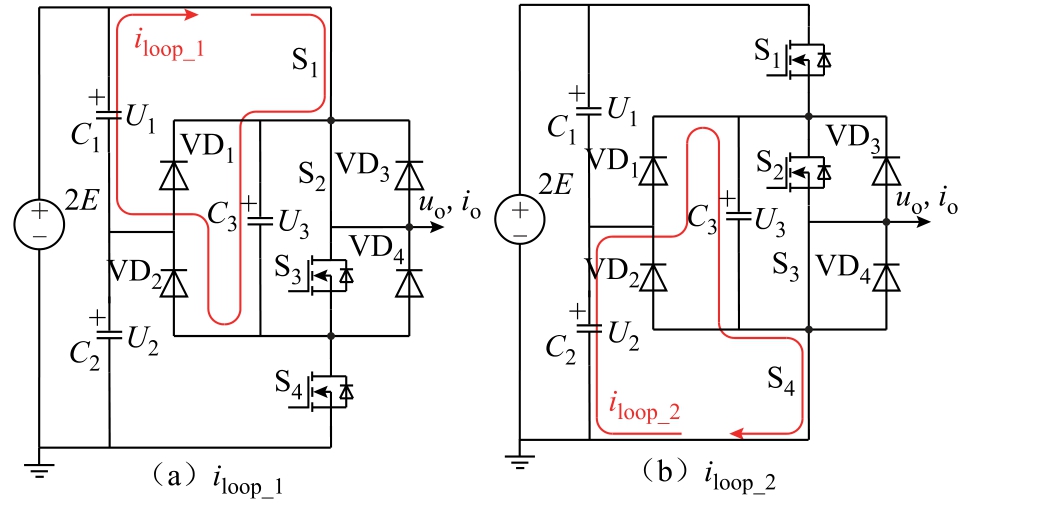

本文提出的双管串联和三管串联的二极管-电容混合钳位拓扑分别如图1a、图1b 所示,该拓扑可以看成文献[17]的改进型拓扑。为简化分析,首先以双管串联拓扑为例进行分析。MOSFET 器件S1~S4和二极管VD1~VD4的等效输出结电容记为Coss_Si和Coss_Di(i=1,2,3,4),且可以认为输出结电容远小于C1~C3。电压U1~U3 在稳态条件下可认为是恒定值。若直流电压为2E,U1~U3 均保证为E,则每个半导体器件承受的最大电压也不超过E,保证了器件在开关暂态不会发生过压击穿。当S1~S4 以准两电平方式顺序开关时,整个拓扑对外即可等效为一个母线电压为2E 的半桥单元。

图1 双管串联和三管串联的二极管-电容混合钳位拓扑

Fig.1 Diode-capacitor hybrid clamp topology with two and three series-connected switches

该拓扑采用准两电平调制,大部分时间模块输出电压为正母线电压或者负母线电压,如图2 所示,此时拓扑中各个电容电压不随负载电流发生变化。图2 中,当S1、S2 导通,输出电压uo 为2E 时,存在图2a 中的电流回路iloop_1,因此有

式中,Udson_S1 和Uon_D2 分别为S1 和VD2 的导通压降。忽略器件压降则有U1=U3。类似地,如图2b,有U2=U3。当uo 在0V 和2E 之间不断切换时,两种状态交替出现,则可自动实现U1=U2=U3。但需注意的是,若要存在iloop_1、iloop_2,需保证C3 在换流过程中不被充电,否则会造成U3>U1 或者U3>U2,导致iloop_1 或者iloop_2 被VD1 或VD2 阻断,进而失去电压平衡。为实现上述目标,本文设计一种准两电平开环调制方法,以保证C3 在任意负载电流条件下都不会在换流过程中被充电。

图2 电压自平衡原理

Fig.2 The principle of voltage self-balance

2 准两电平开环调制方法研究

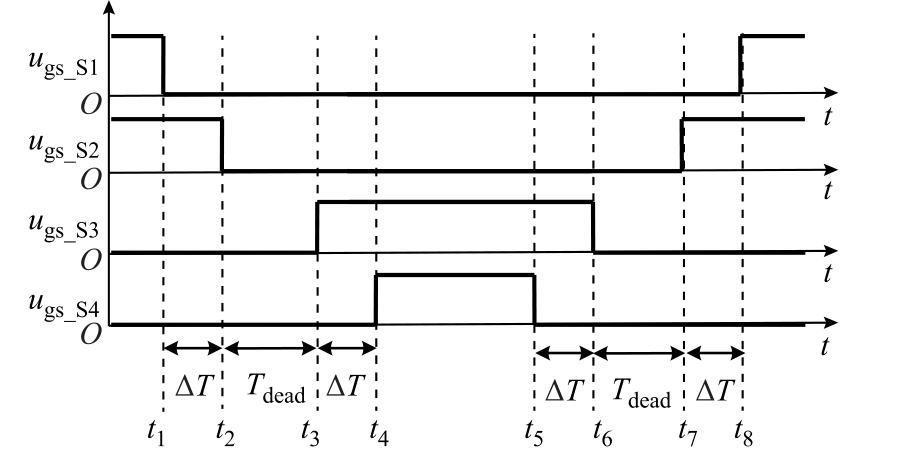

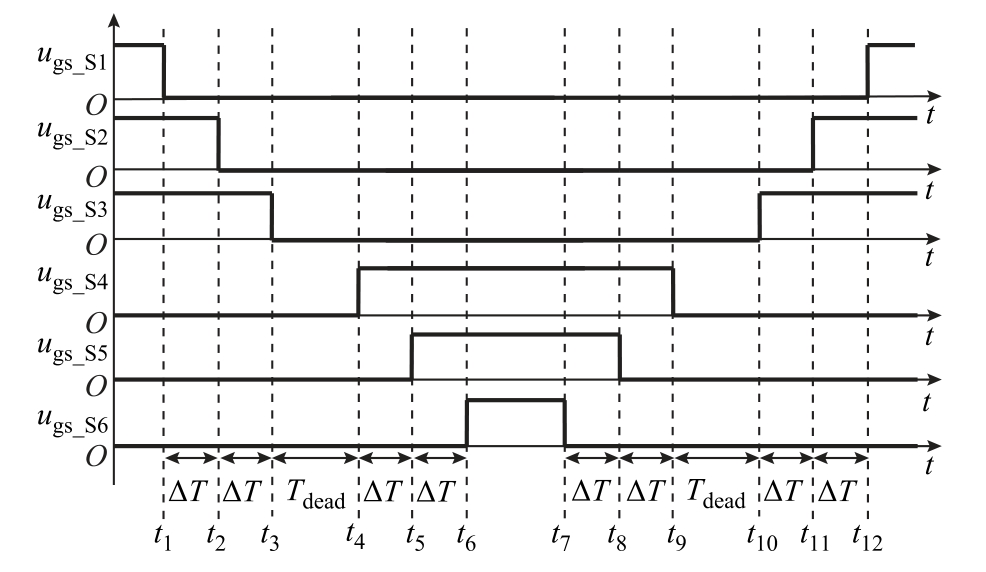

本文提出的准两电平开环调制方法如图3 所示。其中,ugs_Si 是MOSFET 的驱动信号,ΔT 是S1 与S2,及S3 和S4 的开关延迟时间,大约几十ns,其存在可生成准两电平的电压输出波形,Tdead 是上下桥臂之间的死区时间。

图3 准两电平开环调制方法

Fig.3 Modulation strategy for two-switch seriesconnected topology

尽管在不同应用场合和实际工况中负载电流形式各不相同,但考察换流过程,在每一个开关周期内均含有两个换流过程,且两个过程类似。因此本文以第一个换流过程,即换流过程发生t1~t4时间内,进行分析。根据换流瞬态负载电流大小不同,可分为两种换流情况,且C3 不会在换流过程中被充电。需要指出的是,由于换流暂态时间很短,分析中假设负载电流io 保持不变,并且假设此时拓扑已经达到了稳态,有U1=U2=U3=E。

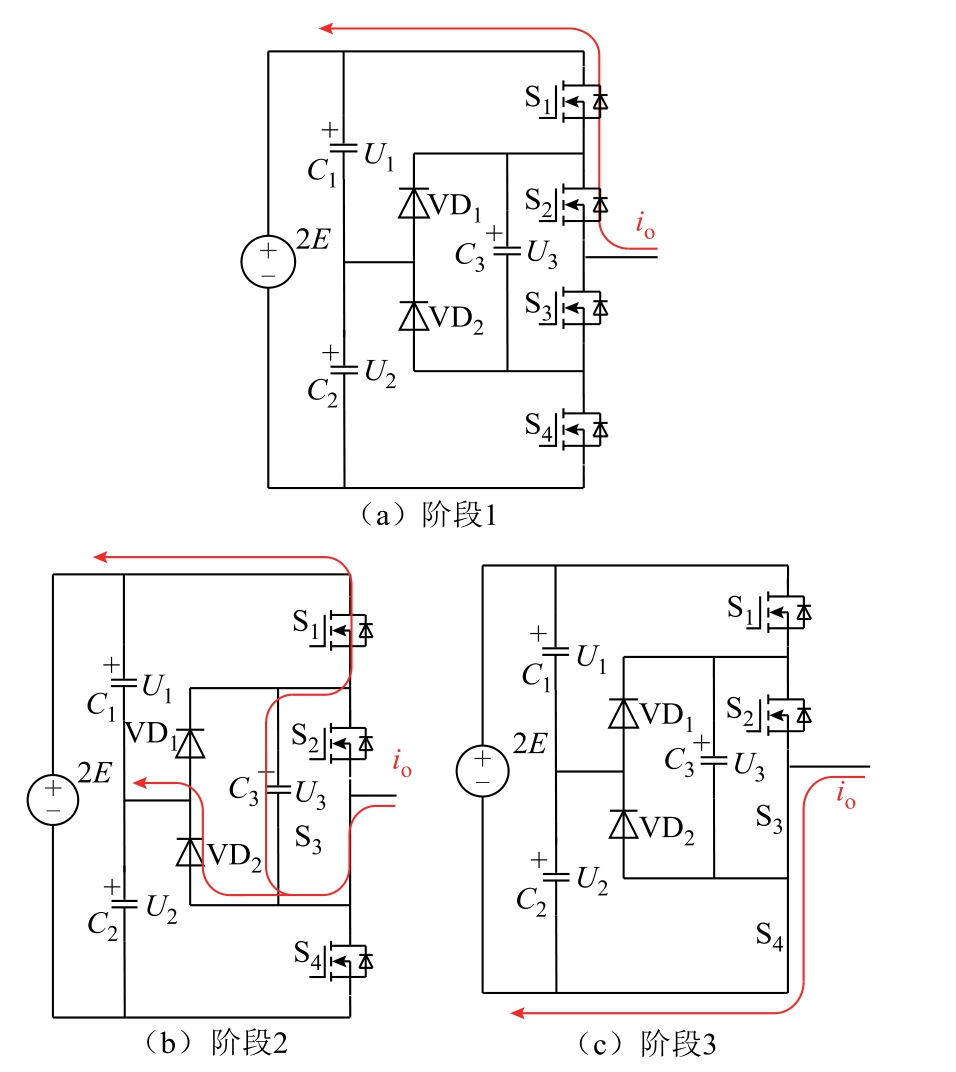

情况1:若io 足够大,使得在ΔT 时间器件结电容能够充放电完全,则C3 的充放电行为主要受io 影响,MOSFET 器件和二极管的输出结电容可以忽略。由于VD3、VD4 分别与S2、S3 的体二极管并联,此时同样可以被忽略。根据换流过程的不同阶段和io的方向,可分为六种电路状态,如图4、图5 所示。

图4 开关电流较大且流出模块时的换流阶段

Fig.4 Intervals duirng commutation process with large swithing current flowing out of the module

当io 流出间接串联拓扑时共有三种电路状态,如图4。其中图4a、图4c 中io 流经正负母线,C3 被旁路,既不充电也不放电。图4b 中根据U2 和U3 的大小关系不同,io 存在两条可能的路径,其中一条C3 被旁路,另一条对C3 放电。当io 流入拓扑时同样有三种状态,如图5 所示,C3 在图5a、图5c 中被旁路,在图5b 中有可能被放电。

图5 开关电流较大且流入模块时的换流阶段

Fig.5 Intervals duirng commutation process with large swithing current flowing into the module

综上所述,在情况1 的换流过程中,C3 仅有可 能被负载电流放电。

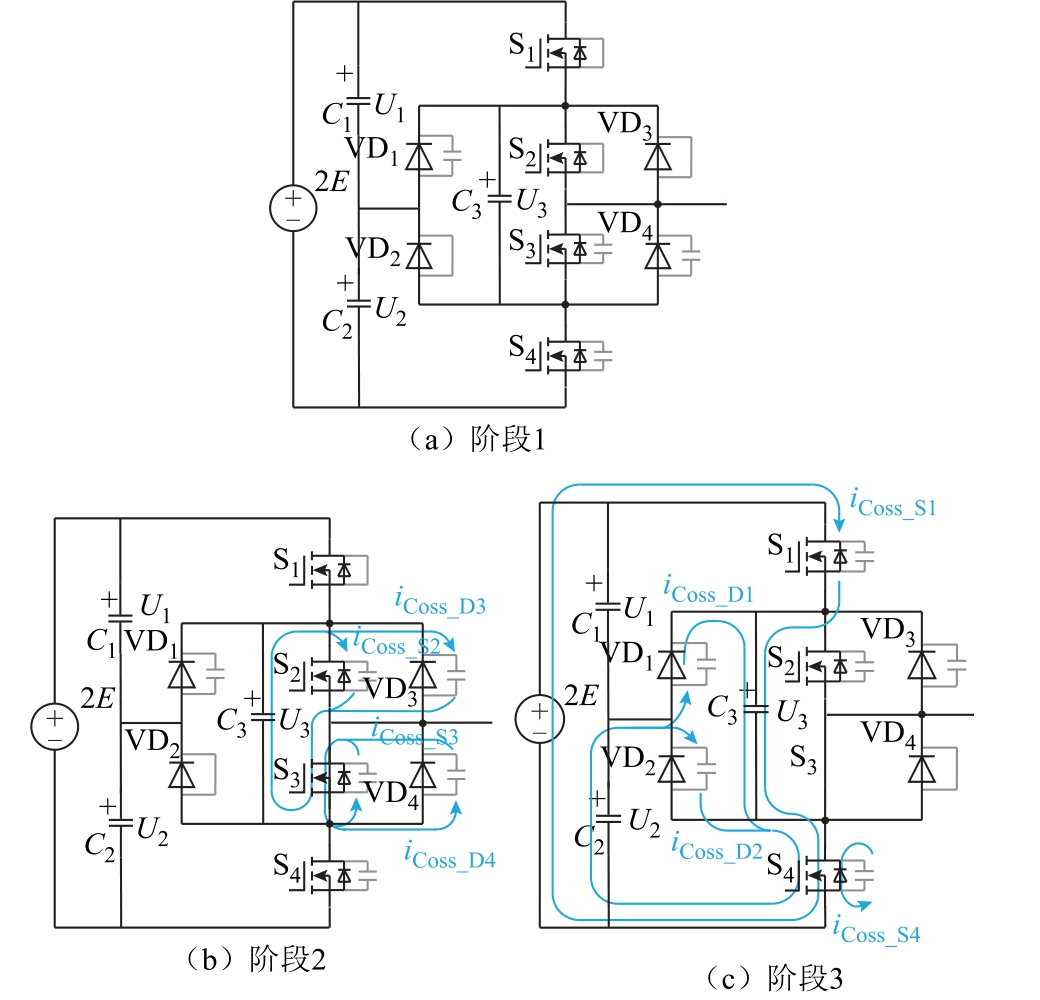

情况2:若io 较小,在ΔT 时间器件结电容无法完全充放电,则C3 的充放电行为主要受器件结电容的充放电电荷影响,此时器件结电容不可忽略。考虑最极端情况,当io 为0 时,共有三种电路状态,如图6 所示。

图6 开关电流为0 时的换流阶段

Fig.6 Intervals duirng commutation process with zero swithing current

在t3 前,无论S1、S2 处于导通还是阻断状态,S1、S2、VD2、VD3 的结电容电压均为0,S3、S4、VD1、VD4 的结电容电压均为E,如图6a 所示。当S3 开通时,S3、VD4 结电容储存的电荷通过S3 释放,同时S2、VD3 结电容的充电电流对C3 放电,放电电荷为(Coss_S2+Coss_D3)E,如图6b 所示。当S4 开通时,S4、VD2 结电容储存的电荷通过S4 释放,同时S1、VD1结电容的充电电流流过C3,对C3 充电,充电电荷为(Coss_S1+Coss_D1)E。综合整个过程,C3 净充电电荷为

因此C3 既不会被充电也不会被放电。

综合上述两种情况,当采用如图3 所示的调制方法时,C3 不会在上述换流过程中被充电,保证了图2 中iloop_1 和iloop_2 的存在,进而保证了电容电压的自平衡。需要指出的是,准两电平的调制方法并不唯一,但图3 是最为简单、且能够保证电压自平衡的调制方法,因此简化了后文外围电路如模块驱动等电路的设计制作。

此外,当需要更多器件串联时,可遵循相同的原理设计调制方法。图7 给出了三管串联拓扑的调制方法,同样外侧器件先于内侧器件关断,而晚于内侧器件导通。

图7 三管串联拓扑的调制方法

Fig.7 Modulation strategy for three-switch seriesconnected topology

3 驱动保护电路设计

本节根据前文调制方法,以图1b 和图7 三管串联方案为例,设计适配驱动电路,发出符合时序的准两电平驱动信号。同时设计故障检测和保护电路,进行故障逻辑处理,在组成模块的单个器件发生故障时能够及时地封锁所有器件。

3.1 驱动电路设计

脉冲宽度调制(Pulse Width Modulation,PWM)信号生成示意图如图8 所示,S1~S6 的驱动电路分别通过六个隔离直流-直流驱动电源供电,源极电位互不相同。为发出与图7 所示相同时序的PWM 信号,本文利用多个4 路信号隔离器逐级传递驱动信号的方式,构建驱动电路,以减小驱动电路体积。以上管S1、S2、S3 的驱动信号为例,光纤隔离的驱动输入信号PWM_P 最先传输到S3 电位区,当没有故障发生(即FLT/_P1、FLT/_P2、FLT/_P3 信号均为高电平),并且下管光纤驱动信号PWM_N 为低电平时,驱动信号经过信号隔离器P1、信号隔离器P2,经过隔离器本身延时后逐次将信号传递到S2、S1 电位区,随后,再以相反的顺序再次反向传回至S2、S3 电位区。每个器件的实际驱动信号为正向传递的信号和反向传递的信号做“或”运算以后,再经过推挽放大后得到的信号,如此即可实现图7 所示的调制方法。而图7 中的延时时间ΔT 即等于信号隔离器的信号传输延迟时间。下管S4~S6 的驱动信号生成方式与上管类似,不再重复。

图8 PWM 信号生成示意图

Fig.8 Schematic diagram of PWM signal generation

值得注意的是,信号隔离器P-N 将下管PWM_N信号传递至S3 电位区作为PWM_P 信号的使能端,仅在PWM_N 信号为低电平时PWM_P 信号才有可能逐级向上传递,如此即确保了模块不会出现S1~S6直通的故障情况,在一定程度上起到了保护作用。

3.2 故障保护电路设计

故障检测与保护电路包括两个方面。第一方面,每个器件都会通过退保和检测电路[18]检测本地器件是否发生故障。退保和检测基本原理如图9 所示。

图9 故障保护电路示意图

Fig.9 Schematic diagram of protection circuit

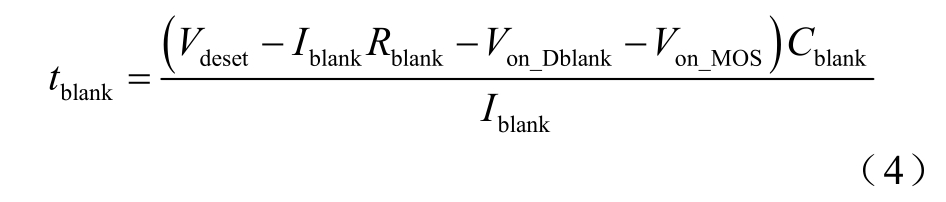

当驱动信号为高电平时,器件Sx (x=1,…,6)若正常导通,则漏极-源极之间的压降较小,则Iblank 电流流过Sx,比较器输出为低电平。当发生过电流故障或者开路故障时,漏极-源极压降将满足

式中,Vdeset 为比较器参考值;Von_Dblank 为二极管VDblank 的管压降。Iblank 首先转向Cblank 充电,Cblank的充电时间可以按式(4)估算,其中 Von_MOS 为MOSFET 正常导通时的压降。

Cblank 充电至电压大于Vdeset 时,比较器输出变为高电平,经逻辑处理电路处理并锁存后,FLT/_Sx输出变为低电平,上报故障。

第二方面,本地器件发生故障时,能够通过信号隔离器快速地封锁其他器件的PWM 信号。如图8 所示,以S2 器件为例,当故障信号FLT/_S2 变为低电平时,其通过“与”运算首先阻断PWM_P 信号向S2 和S1 电位区传递,可封锁器件S2、S1。其次FLT/_S2 与经信号隔离器P2 隔离后的FLT/_S3 信号做“与”运算后,经信号隔离器P1 传递到S3 电位区,同样可以封锁器件S3。

得益于上述两个方面的保护逻辑,保护电路能够在任意一个器件发生过电流故障或者开路故障时,及时将模块的其他器件封锁,实现模块的保护功能。

4 中压半桥模块设计与制作

本节根据图 1b 的拓扑结构,设计并封装三管串联中压半桥模块,配合第3 节的驱动保护电路,构造一款通用的耐压等级为3 600V 的中压功率模块。

模块选用的MOSFET 裸片为深圳基本半导体公司的BC1M160120,其额定参数为1 200V/20A。模块中的二极管仅在延迟时间ΔT 内和死区时间内导通电流,时间为μs 级别,相比MOSFET 主功率器件电流导通时间极短,因此二极管的电流等级选择为MOSFET 的1/10 即可满足要求[19]。本文中选择二极管为深圳基本半导体公司的BCD10120,其额定值为1 200V/10A。

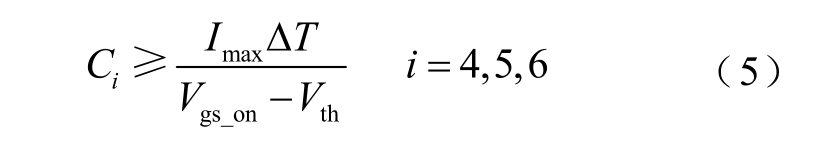

根据第2 节的研究,钳位电容C4~C6 需要在开关暂态过程中钳位MOSFET 器件的漏极-源极电压并放电,在换流完成后被母线电容重新充电,其行为与开关电容变换器行为相同。根据文献[20]的研究结果,在电容充电时应保证器件过程保持在线性电阻区以减小损耗,若记模块的最大开关电流为Imax,导通状态下驱动电压的最大值为Vgs_on,则钳位电容值应该满足

式中,Vth 为MOSFET 器件的导通阈值电压。

延迟时间ΔT 需略大于MOSFET 开通暂态的电压下降时间,如此一方面可以降低开关暂态的等效dv/dt,以减小无源器件的绝缘压力和电磁干扰;另一方面也可保证在器件特性、驱动延时等存在不一致的前提下,保证第2 节中的器件开关顺序。在满足上述前提下延迟时间ΔT 越小越好,以减小对钳位电容的要求。

本文中设置延迟时间ΔT 为40ns,选择钳位电容C4~C6 为0.25μF。

中压半桥模块的制造过程如图10 所示。DBC陶瓷基板选用0.635mm 厚的氧化铝双层敷铜陶瓷基板,采用SAC305 焊膏对焊盘进行喷涂,利用回 流焊机对SiC MOSFET 裸片进行焊接。随后对基板清洗后采用0.38mm 直径铝丝焊接机对裸片进行键合,利用Sn63Pb37 含铅焊膏将电容等无源器件、厚镀镍散热基板、功率端子焊接到DBC 陶瓷基板上。最后安装封装外壳并采用硅胶进行灌封。封装后中压模块尺寸为11cm×10cm×3.5cm。

图10 模块制作过程

Fig.10 Fabrification process of the power module

本文设计的中压功率模块驱动保护电路如图11 所示,其中隔离驱动电源采用MGJ2D242005SC,信号隔离器采用ISO7842,驱动芯片采用NCP51705。整个中压功率模块与驱动保护电路的参数见表1。

图11 中压功率模块与驱动电路

Fig.11 Medium-voltage power module and driver

表1 中压功率模块元件参数

Tab.1 The parameters of medium-voltage power module

5 实验验证

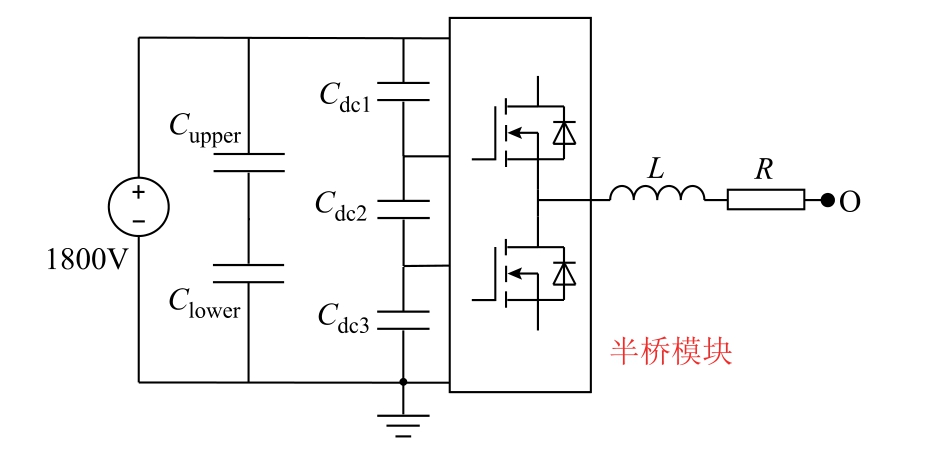

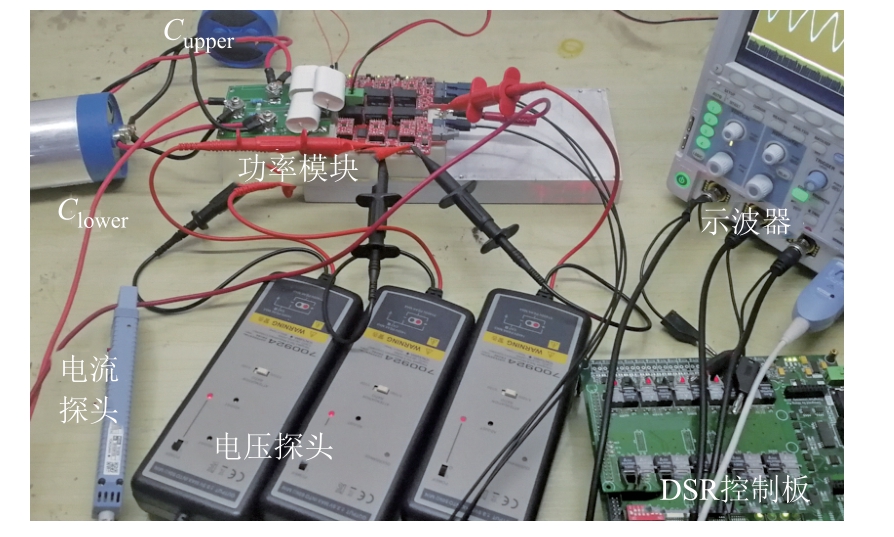

为验证本文研究设计的中压半桥功率模块,搭建一台用于测试模块电压均衡的半桥实验平台,拓扑结构如图12 所示。直流电源为构造的半桥模块提供1 800V 直流电,Cdc1~Cdc3采用EACO 公司的STD-850-2.5-44 电容,其分别与模块内部的电容C1~C3 并联,直流母线通过EACO 公司的SHP-1200-150-FS电容Cupper 和Clower 分出直流母线中点。半桥模块的交流输出端连接电阻、电感负载,通过将端子O 连接到直流母线“地”或者直流母线中点,发出不同形式的负载电流,以验证中压模块在不同负载电流条件下的电压平衡效果。实验装置如图13 所示。

图12 实验拓扑

Fig.12 Topology of the experiment

图13 实验装置

Fig.13 Experimental setup

5.1 电压平衡效果验证

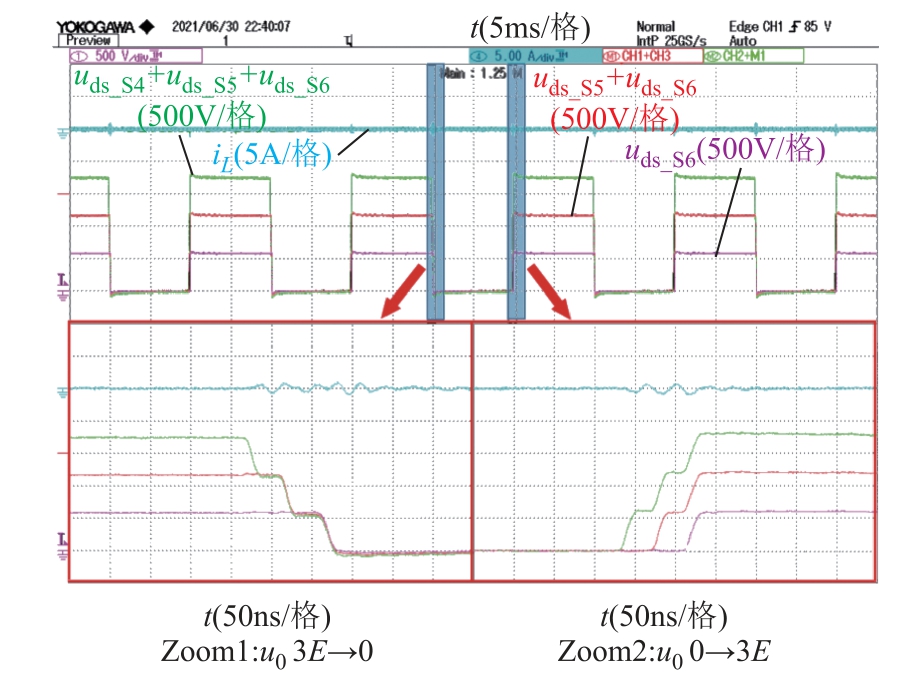

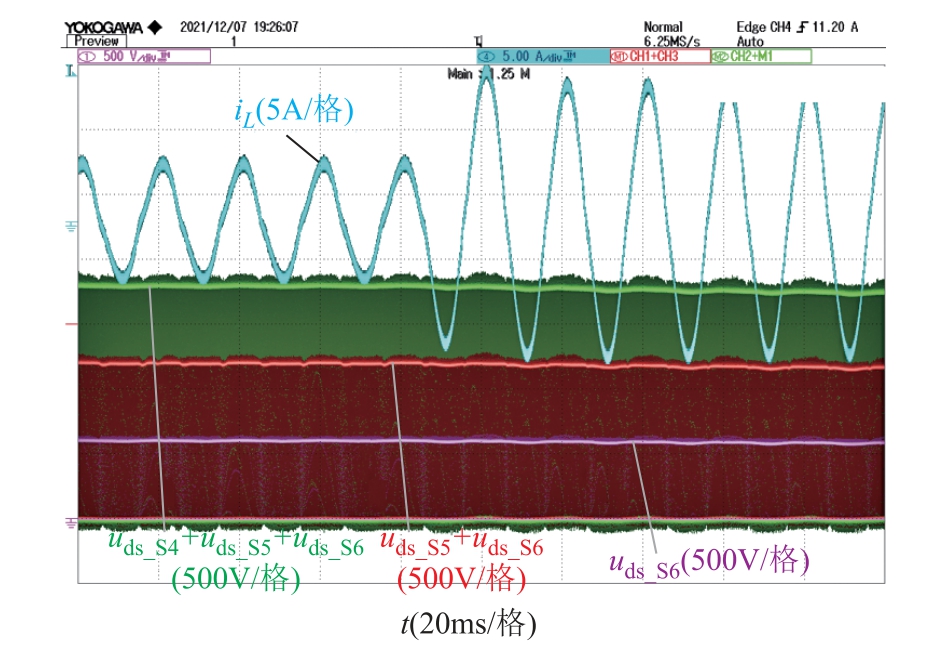

功率模块在单极性负载电流、双极性负载电流、50Hz 正弦负载电流和空载条件下的电压平衡效果如图14~图17 所示,可见在不同形式的负载电流条件下,器件S4~S6 漏极-源极电压都能够良好地平衡,验证了所提出模块的电压平衡效果。由于中压模块采用图7 的调制方法,当负载电流恒为正的单极性时,单极性电流电压平衡效果如图14 所示,在开通暂态,S4~S6 漏-源极电压下降的顺序为S4、S5、S6;在关断暂态,漏极-源极电压上升的顺序为S6、S5、S4。当负载电流为正负交替的双极性时,双极性电流 电压平衡效果如图15 所示。S4~S6 漏极-源极电压的变化取决于S1~S3 的关断行为,因此图15 中S4~S6 漏-源极电压变化顺序为S6、S5、S4。当模块空载时,零电流电压平衡效果如图17 所示。S4~S6 漏-源极电压的变化取决于S4~S6 的开通行为,因此漏-源极电压变化先后顺序为S4、S5、S6。

图14 单极性电流电压平衡效果

Fig.14 Voltage self-balance with unipolar load current

图15 双极性电流电压平衡效果

Fig.15 Voltage self-balance with bipolar load current

图16 正弦电流电压平衡效果

Fig.16 Voltage self-balance with sinusoidal load current

图17 零电流电压平衡效果

Fig.17 Voltage self-balance with zero load current

除了上述稳态过程外,本文还进行了模块在单极性电流、双极性电流和正弦电流条件下,负载增加的动态过程电压平衡效果的实验,结果如图18~图20 所示。可见,在负载变化的过程,模块依然能够保持良好的电压平衡效果,这与前文分析一致。

图18 单极性电流负载增加时的电压平衡效果

Fig.18 Voltage self-balance with step-up unipolar current

图19 双极性电流负载增加时的电压平衡效果

Fig.19 Voltage self-balance with step-up bipolar current

图20 双极性电流负载增加时的电压平衡效果

Fig.20 Voltage self-balance with step-up sinusoidal current

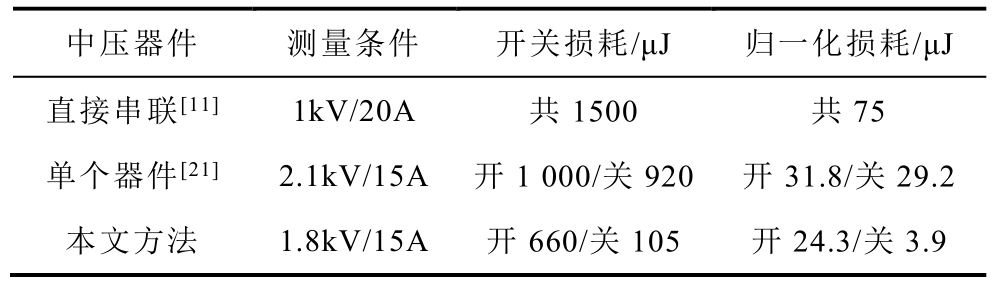

5.2 开关损耗验证

类比中压两电平半桥功率模块,本文提出的间接串联模块开关损耗,等于各个低压器件的单次开关损耗之和。为了测量功率模块的开关损耗,在实验室利用相同布局的PCB 板构建了一个测试平台,并用SSDN-010 型电流同轴分流器对S4~S6 的漏极电流进行测量。测试平台拓扑同图13,将端子O 连接至直流电源“地”,S4~S6 发出多个脉冲,并改变负载电阻,来获得不同的负载电流。测量得到的波形如图21 所示。将器件的漏-源极电压与漏极电流在开关暂态时间内进行积分,可得开关损耗如图22所示。

图21 开关波形

Fig.21 Switching waveforms

图22 开关损耗测量结果

Fig.22 Measured switching losses

式中,Esw 为开关损耗;tsw 为开关时间;id 为漏极电流;vds 为漏极-源极电压。

如图22 所示,构成中压模块的各个器件开通损耗和关断损耗基本一致,整个模块的开关损耗与单个器件的开关损耗呈现简单的倍数关系。模块的开通损耗相比关断损耗要大得多,这与器件的特性一致。进一步,本文将提出的功率模块的开关损耗与其他文献中方法构成的中压器件的开关损耗进行了对比,对比结果见表2。由于不同文献中的器件测量条件不同,为排除此因素的影响,本文将开关损耗归一化为每kV·A 后再进行比较。本文与文献[11]均采用器件串联方案,其主要功率半导体MOSFET数量相同,可预见的是二者成本也相当,但采用缓冲吸收电路直接进行器件串联的方案每kV·A 总开关损耗为75μJ,要比本文方案大得多。而文献[21]中单个3.3kV 中压器件的开关损耗虽然小于直接串联方案,但依然大于本文提出的模块,且根据文献[8]可预见其成本将远大于本文提出的模块。综上所述,本文提出的模块在开关损耗以及经济上更有优势。

表2 开关损耗对比

Tab.2 Comparison results of switching losses

6 结论

本文提出了一种二极管-电容混合钳位拓扑及和准两电平调制方法,用于构成SiC MOSFET 间接串联中压功率模块。该拓扑中MOSFET 功率器件承受的电压被电容钳位,避免了器件直接串联时的开关暂态电压不均衡。拓扑中的电容容值要求比较小,陶瓷电容即可满足要求。同时本文提出的准两电平调制方法保证了拓扑中电容电压的自均衡,避免使用电压、电流传感器以及电容电压平衡控制算法。基于此,本文利用 MOSFET 裸片设计了一款3600V/20A 的中压功率模块,并设计了一款与之配套的驱动保护电路,进行了相关的实验验证与测试。测试结果表明所提出的功率模块能够在任意形式的负载电流下实现电压平衡,从而保证了器件的安全运行。最后,本文还对功率模块的开关损耗进行了测量,结果表明构成模块的每个器件的开关损耗基本相同,模块整体损耗相比于采用缓冲吸收电路的直接串联器件甚至是单个中压SiC MOSFET 器件的开关损耗更具有优势。

[1]Adam G P,Gowaid I A,Finney S J,et al.Review of DC-DC converters for multi-terminal HVDC transmission networks[J].IET Power Electronics,2016,9(2): 281-296.

[2]张勤进,张博,刘彦呈,等.基于低频电流注入的船舶直流微电网线路阻抗检测[J].电力系统保护与控制,2020,48(8): 134-140.Zhang Qinjin,Zhang Bo,Liu Yancheng,et al.A line impedance detection of a ship DC microgrid based on low frequency current injection[J].Power System Protection and Control,2020,48(8): 134-140.

[3]吴本祥,张晓锋,张超,等.六相整流发电机接地方式对船舶中压电力系统谐波影响[J].电力系统保护与控制,2019,47(23): 92-99.Wu Benxiang,Zhang Xiaofeng,Zhang Chao,et al.Influence of grounding mode of 6-phase generator with rectifier-load on harmonics in shipboard medium voltage power system[J].Power System Protection and Control,2019,47(23): 92-99.

[4]王思华,赵磊,王军军,等.基于MMC 的直流输电系统双极短路故障保护策略研究[J].电力系统保护与控制,2021,49(11): 9-17.Wang Sihua,Zhao Lei,Wang Junjun,et al.Research on protection strategy of a bipolar short circuit fault in an HVDC transmission system based on MMC[J].Power System Protection and Control,2021,49(11): 9-17.

[5]邵天骢,郑琼林,李志君,等.基于干扰动态响应机理的SiC MOSFET 驱动设计[J].电工技术学报,2021,36(20): 4204-4214.Shao Tiancong,Zheng Qionglin,Li Zhijun,et al.SiC MOSFET gate driver design based on interference dynamic response mechanism[J].Transactions of China Electrotechnical Society,2021,36(20): 4204-4214.

[6]吴海富,张建忠,赵进,等.SiC MOSFET 短路检测与保护研究综述[J].电工技术学报,2019,34(21): 4519-4528.Wu Haifu,Zhang Jianzhong,Zhao Jin,et al.Review of short-circuit detection and protection of silicon carbide MOSFETs[J].Transactions of China Electrotechnical Society,2019,34(21): 4519-4528.

[7]Johannesson D,Nawaz M,Ilves K.Assessment of 10kV,100A silicon carbide MOSFET power modules[J].IEEE Transactions on Power Electronics,2018,33(6): 5215-5225.

[8]Bolotnikov A,Losee P,Permuy A,et al.Overview of 1.2kV-2.2kV SiC MOSFETs targeted for industrial power conversion applications[C]//2015 IEEE Applied Power Electronics Conference and Exposition (APEC),Charlotte,2015: 2445-2452.

[9]Lin Xiang,Ravi L,Zhang Yuhao,et al.Analysis of voltage sharing of series-connected SiC MOSFETs and body-diodes[J].IEEE Transactions on Power Electronics,2021,36(7): 7612-7624.

[10]周野,王旭,鲜亮,等.基于门极放电补偿的串联IGBT 有源驱动电路[J].电工技术学报,2021,36(18): 3934-3945.Zhou Ye,Wang Xu,Xian Liang,et al.Active gate drive with discharge compensation for seriesconnected IGBT[J].Transactions of China Electrotechnical Society,2021,36(18): 3934-3945.

[11]Kopacz R,Peftitsis D,Rabkowski J.Experimental study on fast-switching series-connected SiC MOSFETs[C]//2017 19th European Conference on Power Electronics and Applications,Warsaw,2017: 1-10.

[12]Wang Tao,Lin Hua,Liu Shengsheng.An active voltage balancing control based on adjusting driving signals time delay for series-connected SiC MOSFETs[J].IEEE Journal of Emerging and Selected Topics in Power Electronics,2020,8(1): 454-464.

[13]Marzoughi A,Burgos R,Boroyevich D.Active gatedriver with dv/dt controller for dynamic voltage balancing in series-connected SiC MOSFETs[J].IEEE Transactions on Industrial Electronics,2019,66(4): 2488-2498.

[14]Aeloiza E,Canales F,Burgos R.Power converter having integrated capacitor-blocked transistor cells: US 14/814914[P].2015-07-31.

[15]Czyz P,Papamanolis P,Guillod T,et al.New 40kV/ 300kVA quasi-2-level operated 5-level flying capacitor SiC “super-switch” IPM[C]//2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019-ECCE Asia),Busan,2019: 813-820.

[16]Zhang Fan,Ren Yu,Yang Xu,et al.A novel active voltage clamping circuit topology for seriesconnection of SiC-MOSFETs[J].IEEE Transactions on Power Electronics,2021,36(4): 3655-3660.

[17]Bum-Seok Suh,Dong-Seok Hyun.A new n-level high voltage inversion system[J].IEEE Transactions on Power Electronics,1997,44(1): 107-115.

[18]Wang Zhiqiang,Shi Xiaojie,Xue Yang,et al.Design and performance evaluation of overcurrent protection schemes for silicon carbide (SiC) power MOSFETs[J].IEEE Transactions on Industrial Electronics,2014,61(10): 5570-5581.

[19]Soeiro T B,Mengotti E,Bianda E,et al.Performance evaluation of the body-diode of SiC mosfets under repetitive surge current operation[C]//IECON 2019 -45th Annual Conference of the IEEE Industrial Electronics Society,Lisbon,2019: 5154-5159.

[20]Wong Y C,Zhou Wei,El-Rayis A O,et al.Practical design strategy for two-phase step up DC-DC Fibonacci Switched-Capacitor converter[C]//2011 20th European Conference on Circuit Theory and Design (ECCTD),Linköping,2011: 817-820.

[21]Bolotnikov A,Losee P,Matocha K,et al.3.3kV SiC MOSFETs designed for low on-resistance and fast switching[C]//2012 24th International Symposium on Power Semiconductor Devices and ICs,Bruges,2012: 389-392.