图1 脉冲电压边沿处的波形

Fig.1 The waveform measured at the edge of pulse voltage

摘要 电力电子器件在运行过程中会产生应力波,该信号可以表征器件的内部信息和工作状态,可用于器件的在线监测。该文首先从测量绝缘内部空间电荷的电声脉冲法原理出发,从封装绝缘的角度对脉冲边沿时刻应力波的形成机理进行了深入探讨,发现绝缘材料中空间电荷在脉冲边沿处的振动可能是应力波的发射源之一。在此基础上,设置具有单一的界面缺陷和老化缺陷的试样,进行脉冲边沿时刻的应力波检测,并将其与正常状态下的应力波进行对比,探究不同缺陷类型对应力波参数的影响。结果显示,界面缺陷会使得应力波在高频处产生新的峰,而老化缺陷则会导致应力波的频域分量向低频处集中,不同的缺陷类型与应力波的时域和频域检测结果存在良好的对应关系。该研究可为建立电力电子器件缺陷状态与应力波参数之间的关联关系奠定基础。

关键词:电力电子器件 应力波 状态监测 界面缺陷 老化状态

现代电力系统中,以IGBT、MOSFET为代表的电力电子器件具有体积小、作用灵活、使用方便等优点,在直流输电、新能源并网等领域得到了广泛的应用[1-2]。然而,电力电子器件的可靠性却难以满足现代电力系统的需求。调查报告显示,电力系统中发生的绝大多数故障都是由于电力电子器件的失效导致的[3]。一方面,电力电子器件在工作过程中所承受的温度、电压等外界条件变化十分剧烈,加快了材料的疲劳失效,使得器件应对外界条件变化的能力变弱;另一方面,对性能的过分追求导致器件的裕量通常设计得很低,这也增加了运行过程中故障发生的可能性[4-5]。因此,监测电力电子器件的工作状态,对保障电力系统的正常运行具有重大意义。

国内外学者对电力电子器件的失效机理进行了许多研究,发现失效是在电-热-应力场的共同作用下导致的[6-7]。传统的电力电子器件监测方法,主要建立在对器件工作过程中电、磁、热等信息参数的提取上[8-11]。基于电信息的监测方法主要是对器件工作过程中关键位置的电气量进行提取,并通过机械学习、建立模型等方法,分析电气量与器件状态之间的对应关系[12-15]。基于磁信息的监测方法则是利用巨阻磁效应,借助于器件内部的磁场传感器,来获得器件内部的结构信息[16]。基于温度信息的监测方法主要是利用传感器,对器件的内部结温、表面温度等热力学量进行提取,然后借助软件对数据进行处理量化,将结果与正常工作状态下得到的结果进行比较,从而判断器件的工作状态[17-18]。上述方法都可以对电力电子器件的工作状态进行有效的监测与评估,然而由于器件的内部结构太过复杂,所以目前的绝大多数研究局限于通过物理量来表征器件的工作状态,而不能确定具体的故障类型。因此,需要探寻其他能够表征器件工作状态的物理量,对电力电子器件的监测方法进行扩展。

局部能量的快速释放会产生应力波,该信号能够表征发射源内部缺陷及其物理性质,因而可用于发射源状态的评估[19]。该方法具有快速、实时、非侵入等特点,符合电力电子设备在线监测的需求,因此在近几年得到了国内外学者的广泛关注[20]。芬兰拉普兰塔理工大学的T. J. Kärkkäinen等首次观察到功率半导体模块的通断瞬间会发射声信号[21]。波兰什切青海事大学的R. Gordon等对IGBT器件连续开断释放的应力波进行了分析,发现器件的开断是应力波产生的主要原因[22]。德国开姆尼茨工业大学的S. Müller在频域范围内对老化器件释放的应力波进行了分析,发现老化使得应力波信号在主频率处的幅值增大,在谐振频率处的幅值减小[23]。湖南大学的何赟泽等对电力电子器件在工作过程中释放的应力波的产生机理及影响因素进行了深入研究,并对应力波信号中的不同频域分量进行分析,得到了不同工作条件下应力波参数与电气参数之间的关系[24-26]。

上述文献对电力电子器件开断过程中释放应力波的影响因素进行了探究。然而,现有文献主要针对器件整体开展应力波检测。研究显示,在器件内部存在多个应力波发射源,不同发射源产生的应力波信号掺杂在一起,给器件内部状态分析带来了很大的困难[27]。此外,这种方法对于器件内部状态的界定不明确,很难建立具体的缺陷类型与状态同应力波的直接关联关系。因此,需要尝试研究特定的发射源在确定的缺陷类型下的机械应力波特性。

本课题组近年来开展了脉冲电场下绝缘材料电荷行为及响应特性的研究,前期研究已发现聚酰亚胺(Polyimide, PI)、有机硅等器件封装材料在脉冲上升沿和下降沿时刻的电荷振动现象,通过压电传感器检测到脉冲边沿时刻的应力波信号,并从电荷受力平衡的角度对应力波产生机理进行了阐述[28]。通过与现有的电力电子器件应力波检测的研究结果比较分析,发现绝缘封装中的电荷振动现象可能是脉冲时刻器件应力波的来源之一,即器件内部的半导体或绝缘材料中的界面或空间电荷,在脉冲电场力作用下发生快速位移,并带动束缚电荷的分子或晶体结构发生振动,进而形成应力波。通过实验室制作的封装绝缘模型,可以获得明确的材料和结构条件下的应力波,便于探讨应力波产生的物理机制。更为方便的是,可以人为设置不同的绝缘缺陷类型,研究缺陷形式与应力波特性的直接关联关系,进而映射到实际的器件缺陷检测中。因此,本文提出研究人为设置缺陷的实验室模型的应力波特性的方法,可以作为器件应力波检测技术研究的新思路。

本文首先从微观的角度,对电力电子器件在运行过程中产生应力波的机理进行了分析。然后基于电力电子器件在运行过程中常见的封装绝缘故障形式,设置了不同材料界面和绝缘老化两种缺陷类型,对不同缺陷状态下的应力波进行了探测。并且分别在时域和频域内,将存在缺陷时的应力波与正常状态下的应力波进行了对比分析。最后总结了不同缺陷下器件应力波的参数特征。

在现代电力电子领域中,为了使得到的波形变得平滑,器件通常工作在较高通断频率的状态下,这使得其承受高重复频率和高电压上升率的方波脉冲电压[29]。由此推断,长期承受高频、高幅值、陡上升沿和下降沿的脉冲电压的冲击作用,是高压电力电子装备的普遍工况。

由于外加电场和极化的影响,降低了电子逸出电极的势垒,从电极发射的电子在外加电场的作用下产生迁移,在迁移过程中被介质中的陷阱所捕获,从而形成空间电荷。空间电荷的存在会导致局部电场的畸变,进而影响材料的绝缘性能。目前较为常用的空间电荷检测方法为电声脉冲(Pulsed Electro-Acoustic, PEA)法,其基本原理为:给试样施加一个微扰场脉冲,破坏空间电荷原本的平衡状态,由于电荷与原子核或分子单元之间的强耦合作用,电荷会带动分子振动并产生应力波[30]。根据电声脉冲法的原理,带电分子会在窄场脉冲的作用下发生振动,考虑到电力电子器件在工作过程中始终受到高频率、陡上升下降沿的方波脉冲电压的影响,脉冲的上升和下降时间均处于ns范围内,其频率分量与电声脉冲法所施加的微扰场脉冲所包含的频率分量相近。据此推测,在正常工况下,电力电子器件绝缘与半导体材料中的分子或晶格结构会由于脉冲上升下降沿的激励作用发生振动,并产生应力波。

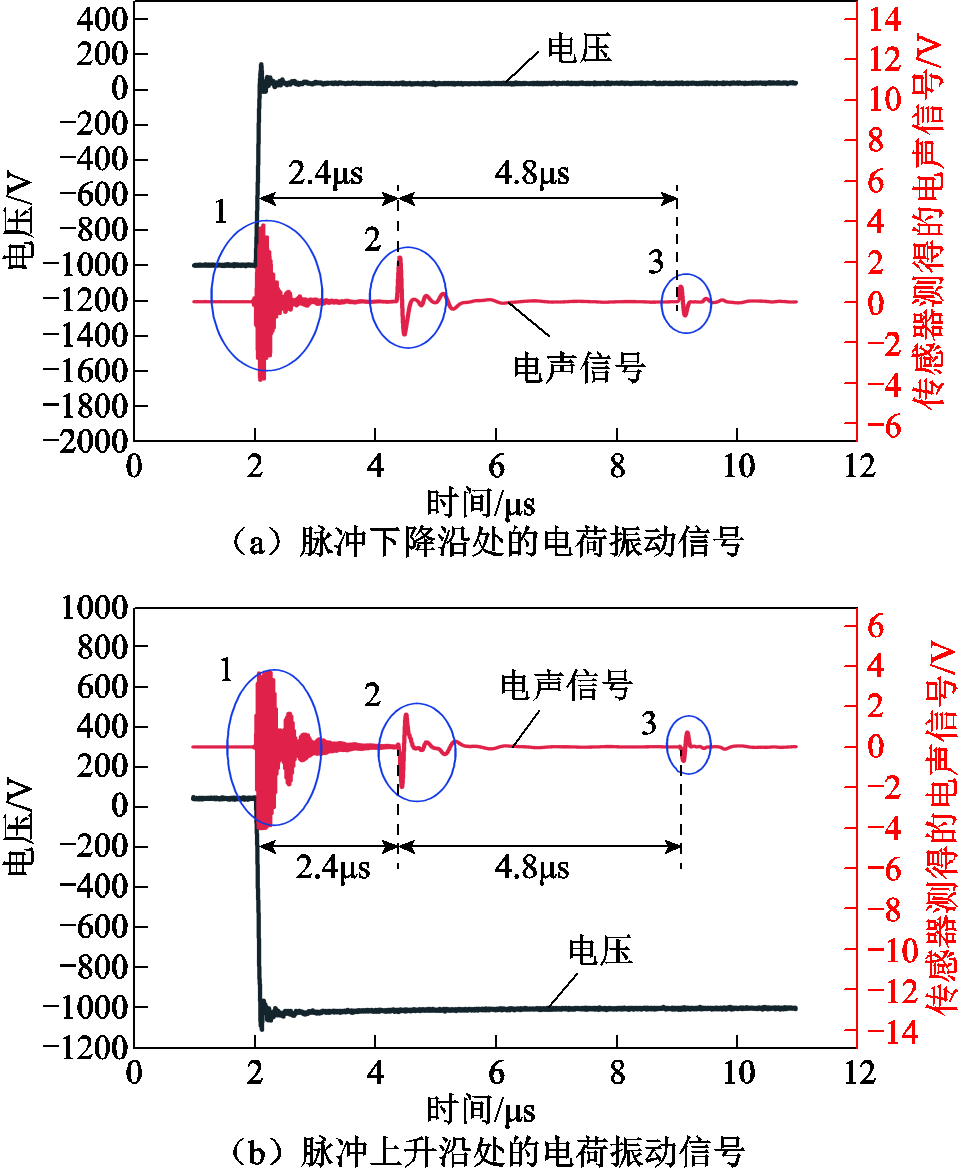

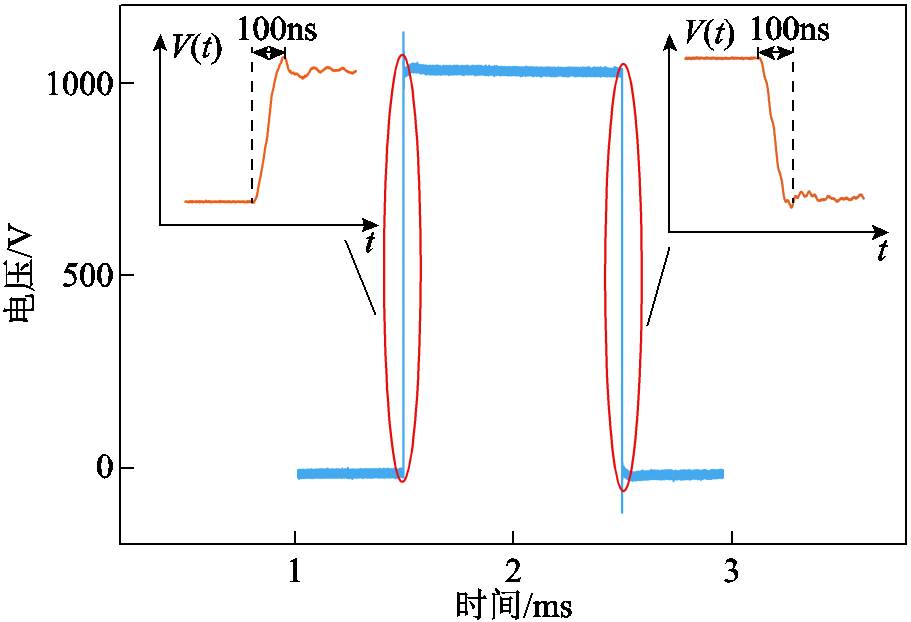

在先前的研究中[28],以聚酰亚胺为研究对象,对脉冲电场上升沿和下降沿处分子的行为进行了研究,发现在脉冲的上升沿和下降沿处,分子的确发生了振动,并检测到了振动产生的应力波,如图1所示。其中脉冲电压幅值为-1kV,脉冲的上升和下降时间均为100ns。应力波可以分为三部分。由于试样与传感器之间存在铝电极板,并不直接接触,因此分子振动所产生的应力波被传感器接收要经过一定的延时。此装置中铝电极的厚度为15mm,铝中的声速约为6 300m/s,可以计算出应力波从产生到被传感器接收所经过的延时约为2.4µs。由此可以判断,图中第二部分即为分子振动所产生的应力波。第一部分信号的传播时延为0,这说明第一部分信号是由于在脉冲边沿时刻电压突变所产生的电磁信号,由于电磁波传播速度极快,约为光速,因此在其产生的瞬间便被传感器所捕获。第三部分信号和第二部分信号之间的时间间隔为4.8µs,是在铝板中传播时间的两倍,且幅值与第二段波形相比具有明显衰减。因此,第三部分信号是第二部分信号的反射波形。

图1 脉冲电压边沿处的波形

Fig.1 The waveform measured at the edge of pulse voltage

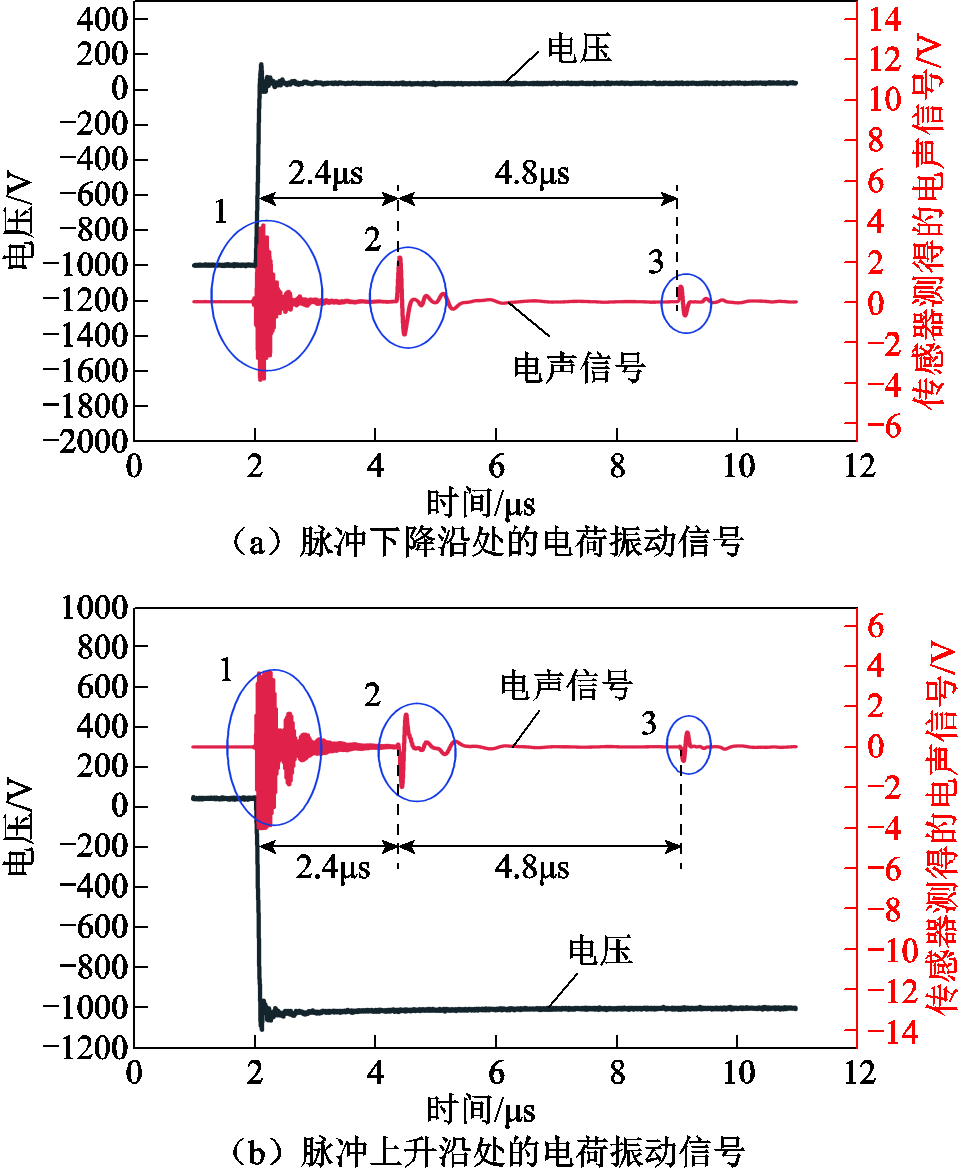

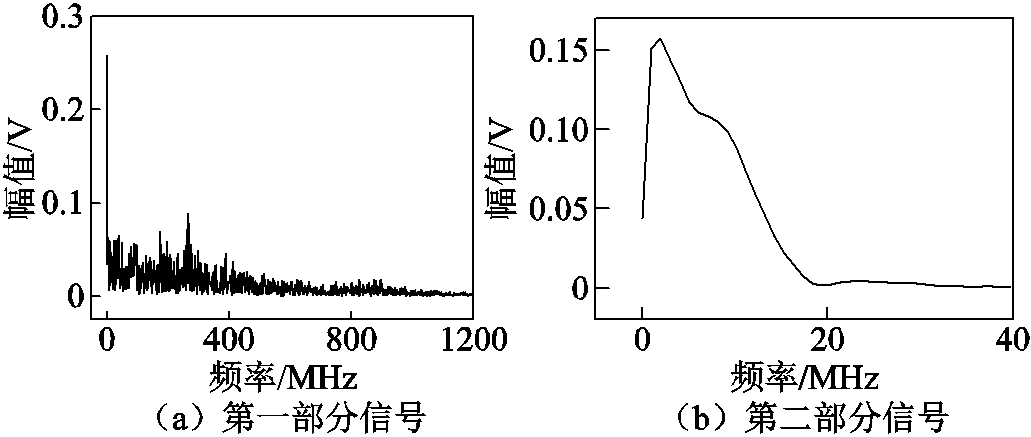

对第一部分和第二部分信号进行傅里叶分解(由于第三部分信号是第二部分信号的反射波形,其所包含的频域分量与第二部分基本一致,因此不进行分析),得到脉冲边沿处分子振动信号的频谱图如图2所示。发现第二部分信号的频域分量主要集中在0~20MHz范围内,属于低频分量;第一部分信号的上限截止频率高达1 000MHz,属于高频分量。在其他学者的研究中也发现了类似的现象。湖南大学的何赟泽等对功率MOSFET在通断过程中发射的应力波的成分进行了分析,发现由低频分量和高频分量两部分组成,低频信号与高频信号之间存在时延,如图3所示[24]。

图2 脉冲边沿处分子振动信号的频谱图

Fig.2 Spectrum of molecular vibration signal at the edge of pulse

图3 MOSFET通断时产生的应力波信号

Fig.3 Stress wave signal generated during MOSFET on-off

关于应力波的来源,目前主流的观点是器件通断时刻剧烈变化的电磁场使带电粒子和晶格发生振动,从而释放应力波。T. J. Kärkkäinen、何赟泽、李孟川等从电磁应力的角度出发,认为器件关断时刻内部的电流会急剧变化,在周围空间中产生剧烈变化的电磁场,带电粒子由于电磁力的作用发生振动并释放应力波[21,24-25]。耿学峰等则从能量的角度入手,认为电流变化的瞬间会产生瞬时脉冲功率并释放热量,热量进入芯片薄层后会使材料晶格动能增加,导致晶格振动并释放应力波[31]。由此可见,国内外学者普遍从电流的角度,对应力波的产生机理进行了深入剖析,而关于通断时刻剧烈变化的电场对应力波的产生是否有影响,目前还没有明确的结论。本课题组基于电声脉冲法的基本原理,同时考虑到电力电子器件运行过程中的实际工况,从电场的角度对应力波的成因进行了解释:器件开断时刻内部电场急剧变化,破坏了带电粒子的受力平衡,导致带电粒子振动并产生应力波。这几种观点分别从电场、磁场、能量的角度,对电力电子器件通断过程中应力波的产生机理进行了阐述,可以互为补充。

综上所述,应力波由低频分量和高频分量组成。其中,低频信号是由于器件内部分子振动而产生,同内部结构紧密相关,其所反映的器件工作状态信息更加准确。且低频信号与高频信号相比,不但波形更为简洁,所包含的频域分量也更少,还可以通过低通滤波器对其进行提取,分析过程更为简便。因此本文主要对应力波的低频分量,即分子振动所产生的信号进行研究。当器件出现故障时,由于内部结构以及物理性质发生变化,应力波的参数也会发生变化。因此,可以通过对应力波进行提取和分析,来评估电力电子器件的工作状态。

电力电子器件的失效类型,可以根据失效部位分为两大类:芯片失效和封装失效[32]。芯片失效是指电力电子器件的集成芯片在运行过程中出现功能异常等问题,通常是由电、热、应力等因素共同导致的。由于芯片具有结构复杂、密封性好等特点,迄今为止并没有研发出比较好的针对芯片失效的在线监测方法。封装失效是指除了芯片外的其他结构出现异常的现象,常见的类型有键合线失效、焊料层疲劳等[33-34]。封装失效并非偶发性故障,而是由于运行过程中缺陷的长期积累所致,如裂缝等局部缺陷及材料的老化疲劳等。通常情况下,器件内部的缺陷会导致内部结构及材料性质发生变化,应力波信号的参数也会发生改变。本文即面向封装失效缺陷中的界面缺陷和材料老化缺陷,设置单一缺陷实验模型,来探究器件内部缺陷对应力波参数的影响。

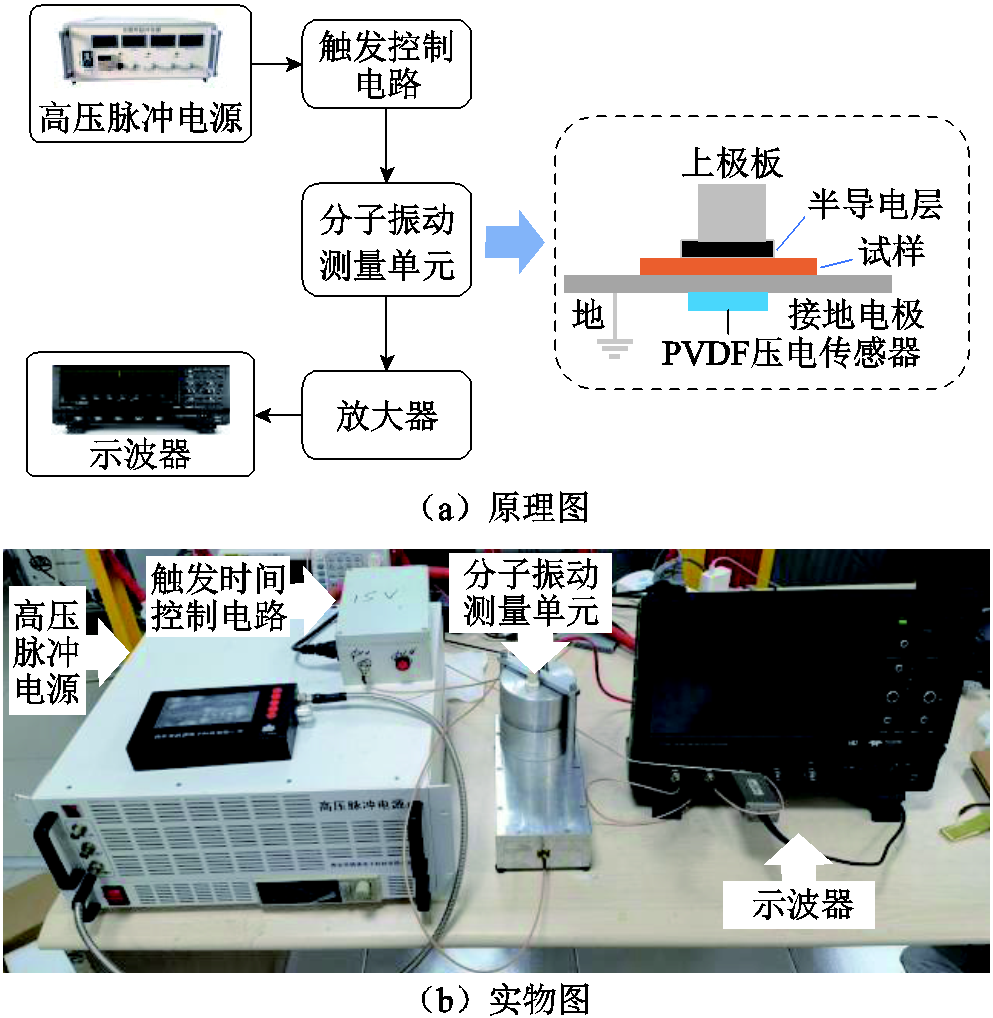

实验装置的整体原理及实物如图4所示,该系统主要由高压脉冲电源、分子振动测量单元、触发控制电路、放大器、示波器组成。其中,高压脉冲电源可以产生纳秒级别上升下降时间的方波脉冲电压,用来模拟电力电子器件在运行中的实际工况。方波脉冲电压的波形如图5所示,其上升沿和下降沿时间均为100ns。触发控制电路可以控制触发时间,从而实现脉冲边沿处分子行为的测量。分子振动测量单元由高压电极、半导电层、待测试样、接地电极、聚偏二氟乙烯(Polyvinylidene Fluoride, PVDF)压电传感器、放大器组成。PVDF压电传感器接收到待测试样中分子振动发出的声信号,会由于受到压力的作用发生形变,产生声电反应,从而将微弱的声信号转换为电信号。电信号经放大器放大后被示波器所接收。半导电层放置在高压电极和试样之间,作用是改善高压电极周围的电场分布,防止闪络现象的发生。

图4 分子振动信号测试平台

Fig.4 Molecular vibration signal test platform

图5 方波脉冲电压波形

Fig.5 Square wave pulse voltage waveform

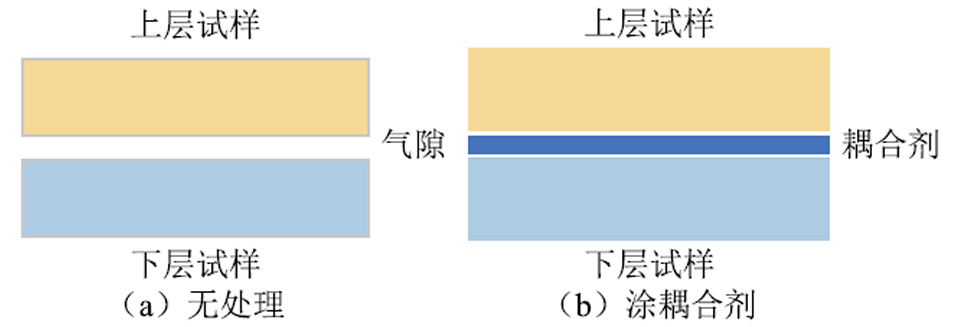

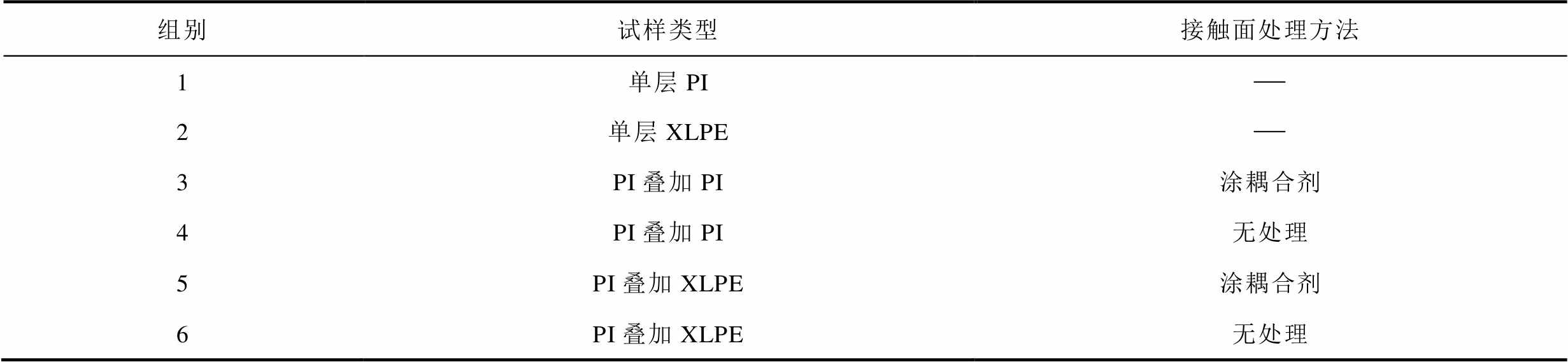

电力电子器件在运行过程中,剧烈变化的电场、温度场、应力场会对材料的微观结构造成损伤,在局部形成气隙。例如局部畸变的电场会对绝缘材料的分子链产生破坏,在绝缘层内部形成电树枝。过高的温度场会加剧焊料层承受的不均匀热应力,导致焊料层中出现空洞、裂纹、分层。气隙的存在会破坏分子取向、结构、物理性质的连续性,导致界面的产生。由于界面两侧的物理性质存在差异,以及界面之间声阻的存在,应力波在界面传播时会发生衰减和畸变。此外,界面处由于电导率和介电常数等参数不连续,会积累大量界面电荷,因此脉冲边沿时刻界面两侧分子振动十分剧烈。基于界面缺陷的上述性质,本实验中,通过试样叠放的方式来模拟器件内部的界面缺陷,如图6所示。通过改变叠放的试样类型(相同试样叠放/不同试样叠放)来改变界面两侧的物理性质,通过在两片试样的接触面处涂抹耦合剂来改变界面处的声阻。聚酰亚胺由于具有极佳的耐高温性能、机械性能和介电性能,成为电力电子领域最常用的材料之一[35]。而交联聚乙烯(Cross-Linked Polyethyline, XLPE)由于其优良的环境耐受性能以及绝缘性能,在高压领域得到了广泛的应用。因此,本实验以交联聚乙烯和聚酰亚胺作为研究对象。具体的界面缺陷设置情况见表1。

图6 界面缺陷示意图

Fig.6 Schematic diagram of interface defects

表1 界面缺陷设置

Tab.1 Interface defect setting

组别试样类型接触面处理方法 1单层PI— 2单层XLPE— 3PI叠加PI涂耦合剂 4PI叠加PI无处理 5PI叠加XLPE涂耦合剂 6PI叠加XLPE无处理

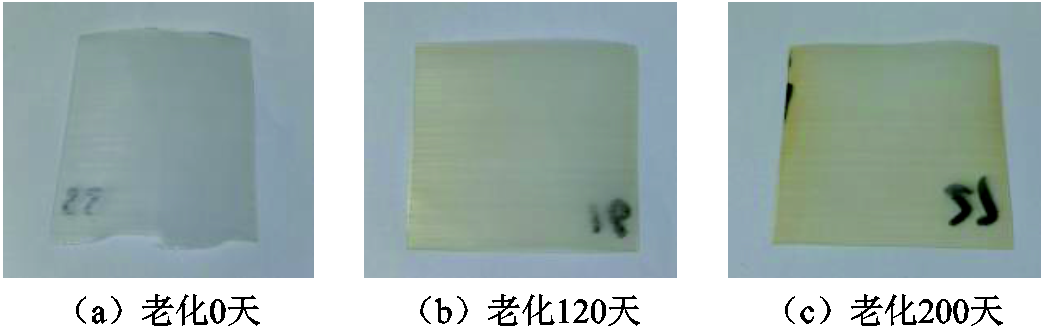

在电力电子器件的运行过程中,严苛的温度及电场环境会加剧器件的老化损伤,使其性能发生劣化。电力电子器件的老化主要可以分为两类:①长期的电热应力作用导致的金属疲劳,主要包括金属疲劳裂纹的产生以及焊点的脱落[36];②局部放电和高温对高分子材料中分子结构造成的损伤,比如分子链的断裂、分子的裂解等[37-38]。相较于金属材料,高分子材料中声信号发射的现象更加明显。R. Khazaka等对高温下聚酰亚胺薄膜的老化特性进行了研究,发现聚酰亚胺材料的机械及电气特性受老化的影响较小[39],因此以交联聚乙烯为研究对象,探究老化对应力波信号参数的影响。考虑到电力电子器件的老化是在电-热耦合场的共同作用下导致的[40],本实验通过将试样放置在高温、强电场环境中的方法,来加快试样的老化速度。研究表明,114℃是XLPE试样晶区达到解列峰值的温度,因此,试样老化环境的温度和电压分别设置为114℃和30kV。根据老化效果,老化时间分别设置为0天、120天、200天。不同老化时间下的老化试样如图7所示。

图7 XLPE老化试样

Fig.7 XLPE aging sample

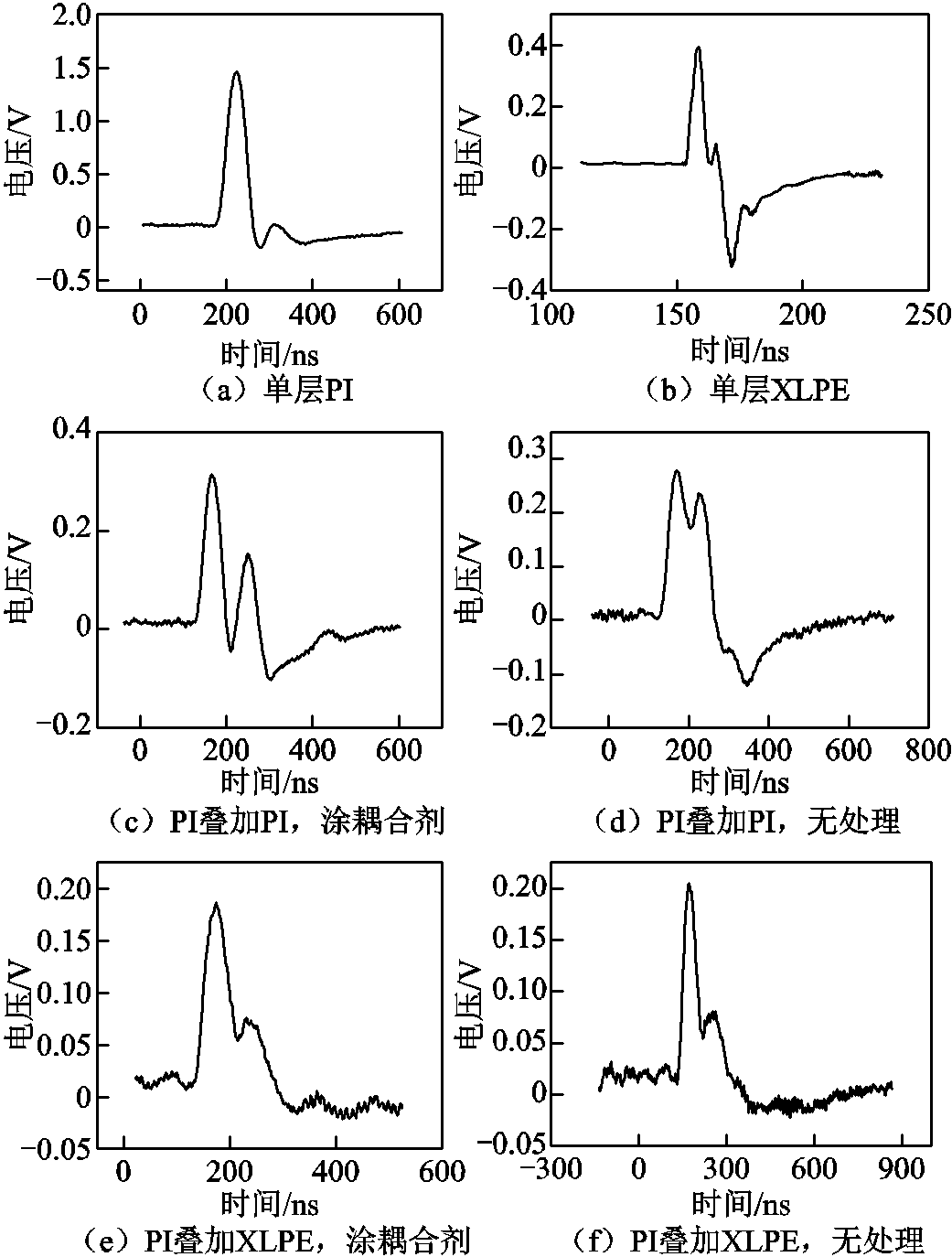

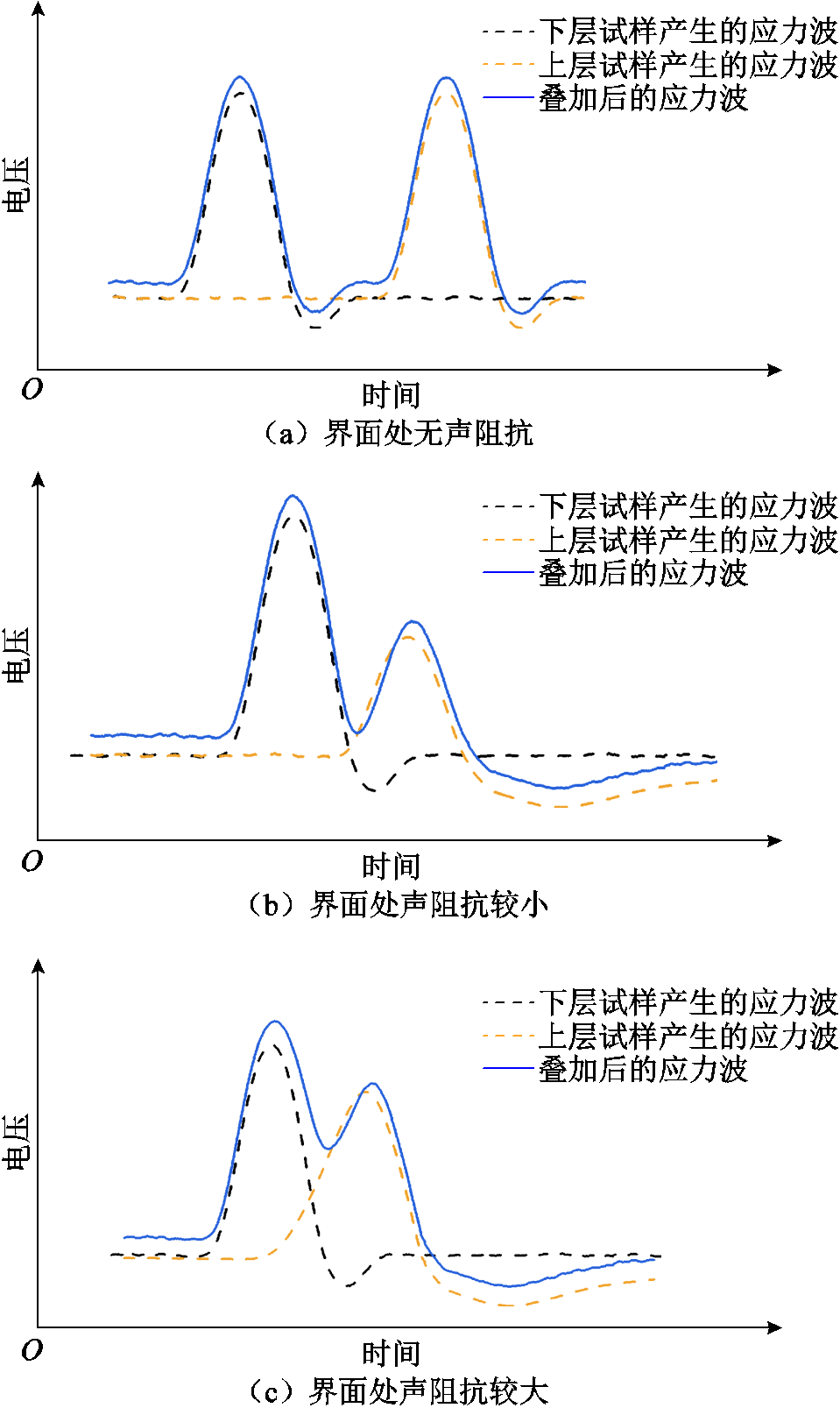

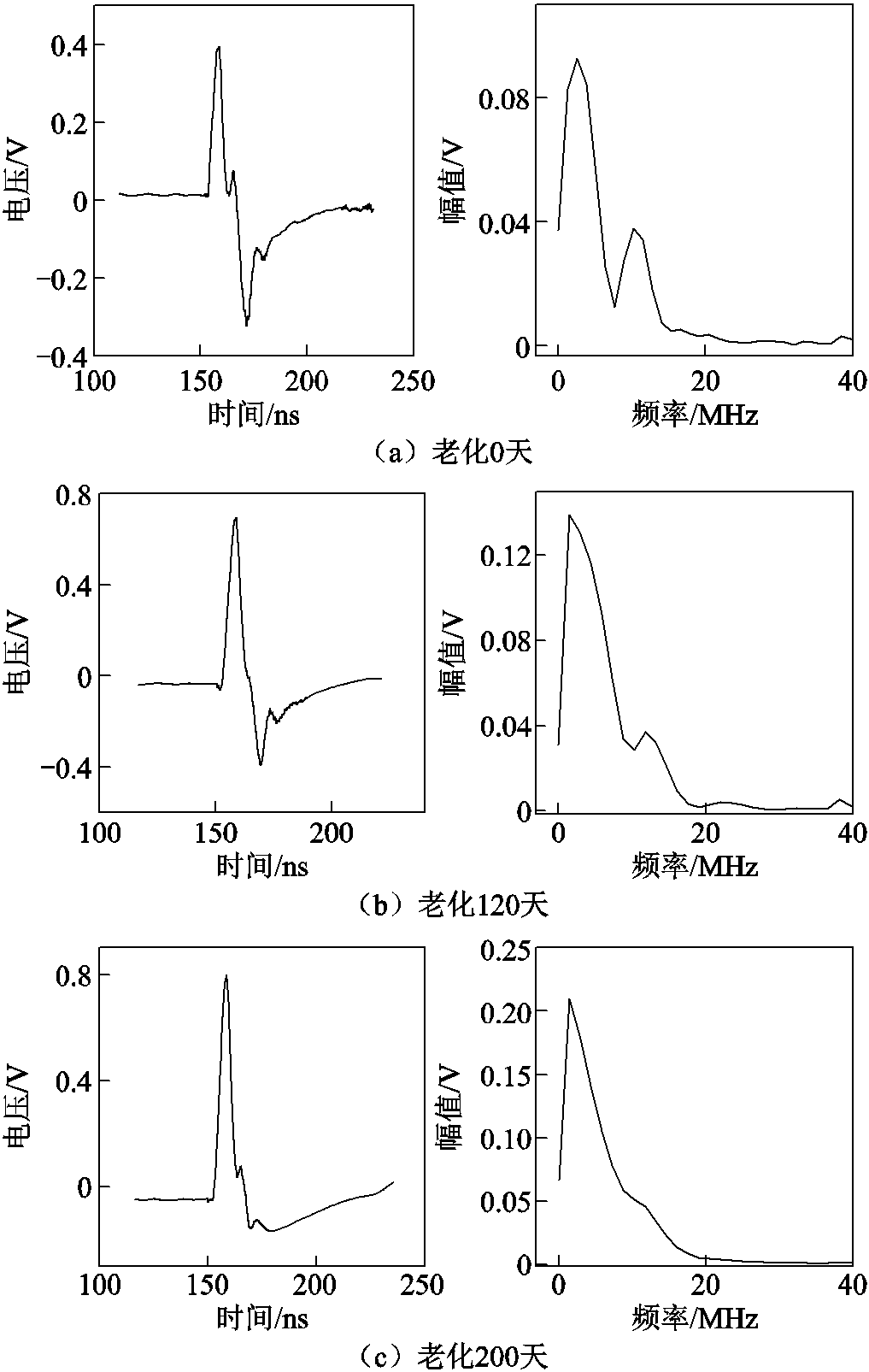

不同界面缺陷下应力波时域波形如图8所示,不同界面声阻抗下应力波的叠加和界面对应力波传播的影响分别如图9和图10所示。完全理想状态下,由于两片试样和PVDF压电传感器之间的距离不同,因此PVDF压电传感器应该先检测到靠近下电极的试样产生的应力波,随后检测到靠近上电极的试样产生的应力波,示波器上应连续显示两个单层试样产生的应力波,且两个信号之间没有相互干扰,如图9a所示。然而,由于介质内部的弛豫现象,以及界面两侧介质不同,应力波在界面处传播时存在损耗和色散,这会导致应力波在经过界面时波形的畸变,具体表现为波形的峰值减小,宽度变宽,且出现拖尾现象,如图10所示。下层试样产生的应力波在到达PVDF压电传感器之前,只需经过试样与下极板形成的界面,因此PVDF压电传感器接收到的波形不会发生较为严重的失真。而上层试样产生的应力波在传播时,除了需要经过下层试样与下极板形成的界面外,还需要经过上层试样和下层试样之间形成的界面,这导致上层试样产生的应力波在传播过程时的衰减和色散更为严重。因此,两片试样产生的应力波存在相互重叠的区域,导致示波器上显示的波形发生畸变,如图9b所示。接触面不涂耦合剂的情况与涂有硅油的情况相比,界面处的声阻更大,发生的损耗和色散更加严重,应力波信号的拖尾也更加严重,这会导致应力波重合的区域更大,波形的畸变也更加严重,如图9c所示。

图8 不同界面缺陷下应力波时域波形

Fig.8 Time domain waveforms of stress wave under different interface defects

由于PI和XLPE的聚合单元的结构以及数目不同,产生的应力波信号的时域波形存在较大的差异。对比图8a和图8b可知,在激励源固定的情况下,PI产生的应力波的正峰值为1.5V,负峰值为0.2V,且整体波形较为平滑;而XLPE产生的应力波的正峰值仅有0.4V,远小于PI产生的应力波对应的峰值,且XLPE产生的应力波在峰值过后还存在电压过冲。因此,PI叠加XLPE界面产生的应力波与PI叠加PI界面产生的应力波相比,两个正电荷峰之间的幅值差距较大。此外,由于界面两侧的物理性质差距更大,在界面处传播时发生的损耗和色散也更加严重,因此与相同试样叠加发射的应力波相比,不同试样叠加产生的应力波存在更严重的拖尾现象,且波形中的毛刺也更加明显。

图9 不同界面声阻抗下应力波的叠加

Fig.9 Superposition of stress wave under different interface acoustic resistances

图10 界面对应力波传播的影响

Fig.10 Effect of interface on stress wave propagation

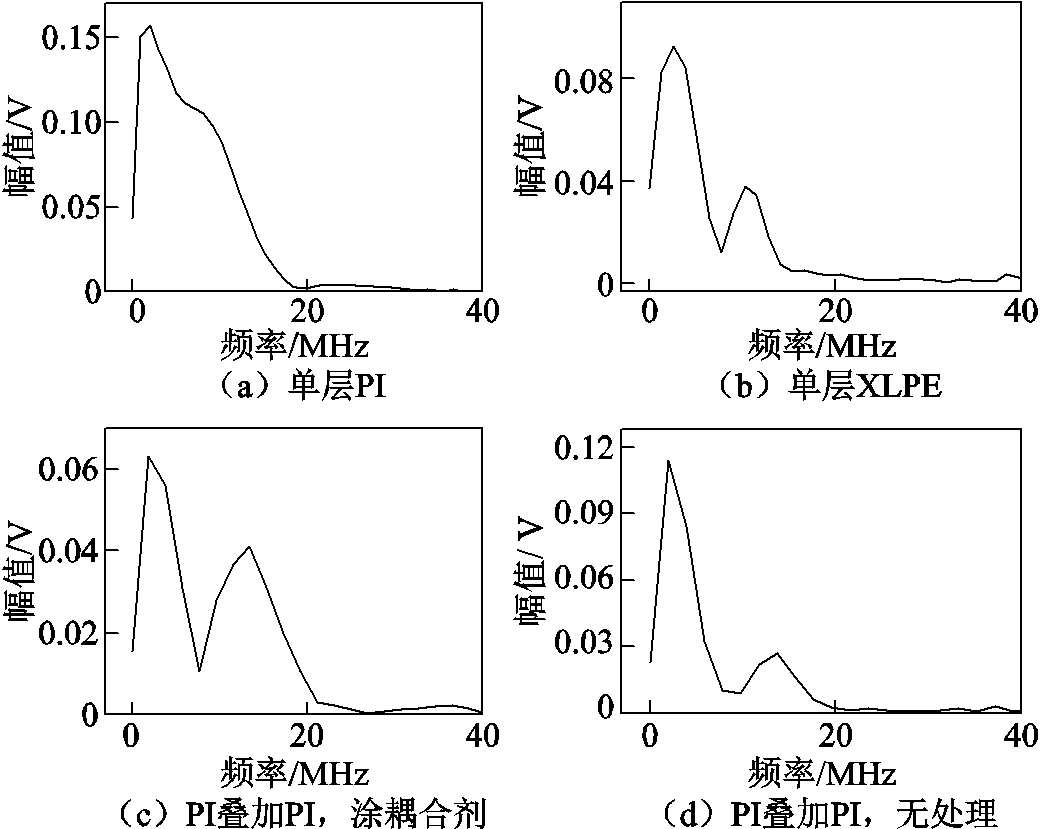

根据上述分析可知,界面的存在会使应力波产生畸变,畸变的程度与界面两侧的物理性质以及界面处的声阻大小有关。应力波是能量在介质中传播产生的机械波,其本质是一种能量释放现象,而频谱图可以直观地反映各个频段内能量的分布情况。为了更直观地分析界面情况对应力波的影响,对实验结果进行傅里叶分解,得到不同界面情况下应力波的频谱如图11所示。

实验结果显示,应力波的频域分量主要集中在0~20MHz的范围内。不同界面情况下,应力波频谱图的尖峰频域段及其幅值各不相同。单层PI试样产生的应力波仅在2MHz处存在尖峰;单层XLPE试样产生的应力波,分别在2MHz与10MHz处存在尖峰。相同试样叠加产生的应力波,除了在2MHz处存在尖峰外,在13MHz处也存在一个峰值更小的尖峰。相同试样叠加且界面处涂有硅油的情况下,13MHz处的峰值与2MHz处的峰值之比为0.67;而界面处不涂硅油的情况下,13MHz处的峰值与2MHz处的峰值之比为0.23。这表明界面的存在会使得应力波的频谱产生额外的峰,该峰与主峰的比值随着界面耦合程度的增加而增加,这种现象出现的原因可能是上下层试样产生的应力波的频域分量不同导致的。通过3.1节中对应力波的时域波形分析可知,存在界面时的应力波可以看做上下层试样单独产生的应力波的叠加。在理想情况下,上下层试样产生的应力波完全相同,所包含的频域分量也相等。然而由于界面的存在,上层试样产生的应力波发生色散,这使得其包含的频域分量发生变化,因此在频域内产生了新的频谱峰。耦合剂属于黏性材料,其存在会改变界面两侧分子振动的弹性系数,从而加剧了应力波频谱的畸变。因此,与界面不作处理的情况相比,涂有耦合剂时高频处的频谱峰与主频谱峰的比值更大。对于不同试样叠加产生的应力波,由于XLPE产生的应力波的强度小于PI产生的应力波的强度,因此其对频域的影响更小。在实验结果中表现为:PI与XLPE叠加的情况下,除了在2MHz处存在尖峰外,在10MHz附近并没有产生新的频谱峰,而是形成了一段较为平坦的结构。

图11 不同界面缺陷下应力波频谱图

Fig.11 Spectrum of stress wave under different interface defects

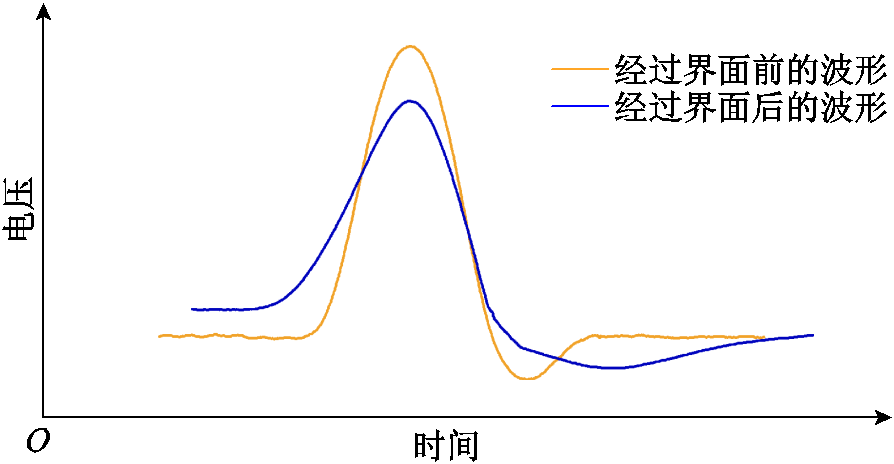

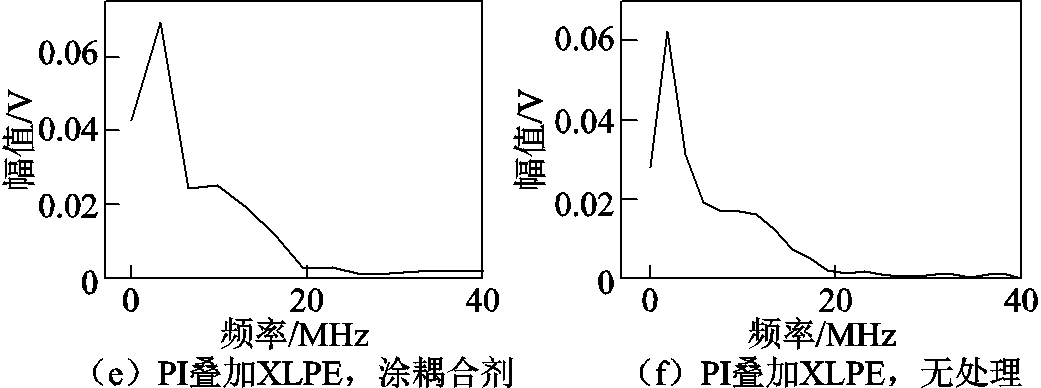

不同老化阶段的试样所产生应力波的时域及频域图如图12所示。时域结果显示,应力波的拖尾程度随着试样老化程度的增加而增大。而从频谱图中可以看出,频域分量主要集中在0~20MHz的范围内。未经老化的XLPE试样产生的应力波,分别在2.6MHz和10.8MHz处存在频谱峰。在114℃、30kV的条件下老化120天的试样产生的应力波,同样在1.7MHz和11.7MHz处存在两个频谱峰。与未老化的试样相比,其频域分量主要集中在低频范围内,高频处的频域分量明显减弱。在114℃、30kV的条件下老化200天的试样产生的应力波,频域分量集中在低频处的现象更加明显,仅在1.4MHz处存在一个频谱峰。

图12 老化试样的应力波时域及频谱图

Fig.12 Time domain and frequency spectrum of stress wave in aged specimen

实验结果显示,老化会使得试样产生的应力波信号的频域分量发生变化。随着老化程度的增加,频域分量逐渐向低频范围内集中。这种现象是由于材料分子的内部结构变化导致的。分子之间的结合力主要是电磁力,其大小与分子之间的相对位置有关,且作用机理表现为与分子所受到的形变力相对抗,可以看作弹性力。因此在受到微扰时,分子会在外力与弹性力的共同作用下发生振动,并产生应力波。应力波的频率与分子的振动频率有关,而分子的振动频率则受到分子之间耦合程度的影响。耦合越剧烈,振动频率越大。而在老化状态下,由于分子结构遭到破坏,彼此之间的耦合程度降低,这会导致分子的振动频率降低。因此,随着老化程度的增加,试样产生的应力波信号的高频分量逐渐减少,低频分量逐渐增加。

本文从微观尺度下分子振动的角度,对电力电子器件在工作过程中产生应力波的现象进行了分析,发现急剧变化的电场会导致绝缘材料中的空间电荷振动并产生应力波,进而推测电力电子器件的封装绝缘部分可能是应力波的来源之一。并通过实验的方法,探究了界面缺陷和老化缺陷两类缺陷对应力波参数的影响。主要结论如下:

1)电力电子器件的通断会引起本身承受的电场急剧变化,导致封装绝缘中带电粒子的受力平衡被打破,使其振动并产生应力波。而器件中的缺陷会导致内部结构发生变化,进而导致应力波参数的变化。因此,通过对器件在工作过程中产生的应力波信号进行监测,可以获知器件的工作状态。

2)界面缺陷对应力波的影响主要体现在产生机理和传播过程两方面。界面处产生的应力波可以看作相邻两个试样界面积累的表面电荷所产生的应力波的叠加。由于信号会在界面处存在衰减和色散,其包含的频域分量发生变化,这使得合成后的信号在高频处产生新的峰。此外,耦合剂会使得部分分子间的弹性系数发生变化,因此存在耦合剂时,高频峰的峰值比不存在耦合剂时的峰值更大。

3)老化会使得分子之间的耦合程度降低,这导致分子振动产生的应力波所包含的低频分量增加,高频分量减少。这种现象随着试样老化程度的增加而愈加明显。因此,通过对电力电子器件发射的应力波进行频域分析,可获知器件的老化程度。

本文对电力电子器件封装绝缘中产生的应力波进行分析,得到了不同缺陷类型对应力波的影响因素。不过,所设置的缺陷模型较为简单,尚不能全面反映器件内部的各种缺陷状态。在后续工作中,将考虑器件结构、封装布局等因素对声信号传播造成的影响,对应力波信号参数与故障类型之间的关系进行进一步的深入探究。

参考文献

[1] 张逸成, 叶尚斌, 张佳佳, 等. 电力电子设备传导噪声抑制措施研究综述[J]. 电工技术学报, 2017, 32(14): 77-86.

Zhang Yicheng, Ye Shangbin, Zhang Jiajia, et al. Review of conducted noise suppression method for power electronic and electrical equipment[J]. Transactions of China Electrotechnical Society, 2017, 32(14): 77-86.

[2] 蔡旭, 杨仁炘, 周剑桥, 等. 海上风电直流送出与并网技术综述[J]. 电力系统自动化, 2021, 45(21): 2-22.

Cai Xu, Yang Renxin, Zhou Jianqiao, et al. Review on offshore wind power integration via DC transmission[J]. Automation of Electric Power Systems, 2021, 45(21): 2-22.

[3] 王学梅, 张波, 吴海平. 基于失效物理的功率器件疲劳失效机理[J]. 电工技术学报, 2019, 34(4): 717-727.

Wang Xuemei, Zhang Bo, Wu Haiping. A review of fatigue mechanism of power devices based on physics-of-failure[J]. Transactions of China Electrotechnical Society, 2019, 34(4): 717-727.

[4] Choi U M, Blaabjerg F, Lee K B. Study and handling methods of power igbt module failures in power electronic converter systems[J]. IEEE Transactions on Power Electronics, 2015, 30(5): 2517-2533.

[5] 何东欣, 张涛, 陈晓光, 等. 脉冲电压下电力电子装备绝缘电荷特性研究综述[J]. 电工技术学报, 2021, 36(22): 4795-4808.

He Dongxin, Zhang Tao, Chen Xiaoguang, et al. Research overview on charge characteristics of power electronic equipment insulation under the pulse voltage[J]. Transactions of China Electrotechnical Society, 2021, 36(22): 4795-4808.

[6] 汪波, 罗毅飞, 张烁, 等. IGBT极限功耗与热失效机理分析[J]. 电工技术学报, 2016, 31(12): 135-141.

Wang Bo, Luo Yifei, Zhang Shuo, et al. Analysis of limiting power dissipation and thermal failure mechanism[J]. Transactions of China Electrotecnical Society, 2016, 31(12): 135-141.

[7] 彭英舟, 周雒维, 张晏铭, 等. 基于键合线等效电阻的 IGBT 模块老化失效研究[J]. 电工技术学报, 2017, 32(20): 117-132.

Peng Yingzhou, Zhou Luowei, Zhang Yanming, et al. Study of IGBT module aging failure base on bond wire equivalent resistance[J]. Transactions of China Electrotechnical Society, 2017, 32(20): 117-132.

[8] 李武华, 陈玉香, 罗皓泽, 等. 大容量电力电子器件结温提取原理综述及展望[J]. 中国电机工程学报, 2016, 36(13): 3546-3557.

Li Wuhua, Chen Yuxiang, Luo Haoze, et al. Review and prospect of junction temperature extraction principle of high power semiconductor devices[J]. Proceedings of the CSEE, 2016, 36(13): 3546-3557.

[9] 李辉, 胡玉, 王坤, 等. 考虑杂散电感影响的风电变流器 IGBT 功率模块动态结温计算及热分布[J]. 电工技术学报, 2019, 34(20): 4242-4250.

Li Hui, Hu Yu, Wang Kun, et al. Thermal distribution and dynamic junction temperature calculation of IGBT power modules for wind turbine converters considering the influence of stray inductances[J]. Transactions of China Electrotechnical Society, 2019, 34(20): 4242-4250.

[10] 吴海富, 张建忠, 张进, 等. SiC MOSFET 短路检测与保护研究综述[J]. 电工技术学报, 2019, 34(21): 4519-4528.

Wu Haifu, Zhang Jianzhong, Zhao Jin, et al. Review of short-circuit detection and protection of silicon carbide MOSFETs[J]. Transactions of China Electrotechnical Society, 2019, 34(21): 4519-4528.

[11] 姚芳, 胡洋, 李铮, 等. 基于结温监测的风电 IGBT 热安全性和寿命耗损研究[J]. 电工技术学报, 2018, 33(9): 2024-2033.

Yao Fang, Hu Yang, Li Zheng, et al. Study on thermal safety and lifetime consumption of IGBT in wind power converters based on junction temperature monitoring[J]. Transactions of China Electrotechnical Society, 2018, 33(9): 2024-2033.

[12] 姚陈果, 李孟杰, 余亮, 等. 基于脉冲耦合响应的IGBT故障检测方法[J]. 电工技术学报, 2020, 35(15): 3235-3244.

Yao Chenguo, Li Mengjie, Yu Liang, et al. A condition detecting method for the IGBT module based on pulse coupling response[J]. Transactions of China Electrotechnical Society, 2020, 35(15): 3235-3244.

[13] 赵子轩, 陈杰, 邓二平, 等. 负载电流对IGBT器件中键合线的寿命影响和机理分析[J]. 电工技术学报, 2022, 37(01): 244-253.

Zhao Zixuan, Chen Jie, Deng Erping, et al. The influence and failure mechanism analysis of the load current on the IGBT lifetime with bond wire failure[J]. Transactions of China Electrotechnical Society, 2022, 37(01): 244-253.

[14] Brown D W, Abbas M, Ginart A, et al. Turn-off time as an early indicator of insulated gate bipolar transistor latch-up[J]. IEEE Transactions on Power Electronics, 2012, 27(2): 479-489.

[15] Liu Jingcun, Zhang Guogang, Chen Qian, et al. In situ condition monitoring of IGBTs based on the miller plateau duration[J]. IEEE Transactions on Power Electronics, 2019, 34(1). 769-782.

[16] 王磊, 李兵, 董超跃, 等. 城轨牵引变流器功率开关器件的双向加速老化测试与在线损伤预测[J]. 电工技术学报, 2019, 34(增刊1): 224-234.

Wang Lei, Li Bing, Dong Chaoyue, et al. Bidirectional accelerated aging test and online damage prediction of power switch devices in urban traction converter[J]. Transactions of China Electrotecnical Society, 2019, 34(S1): 224-234.

[17] 万萌, 应展烽, 张伟. 分立型功率MOSFET结温估计的非线性热网络模型和参数辨识方法[J]. 电工技术学报, 2019, 34(12): 2477-2488.

Wan Meng, Ying Zhanfeng, Zhang Wei. Nonlinear thermal network model and parameter identification method for junction temperature estimation of discrete power MOSFET[J]. Transactions of China Electro-technical Society, 2019, 34(12): 2477-2488.

[18] 丁雪妮, 陈民铀, 赖伟, 等. 多芯片并联IGBT模块老化特征参量甄选研究[J]. 电工技术学报, 2022, 37(13): 3304-3316, 3340.

Ding Xueni, Chen Minyou, Lai Wei, et al. Selection of aging characteristic parameter for multi-chips parallel IGBT module[J]. Transactions of China Electrotechnical Society, 2022, 37(13): 3304-3316, 3340.

[19] 李孟川, 孟志强, 胡毅, 等. 电力电子器件机械应力波的试验研究[J]. 湖南大学学报(自然科学版), 2019, 46(4): 74-79.

Li Mengchuan, Meng Zhiqiang, Hu Yi, et al. Experimental study of mechanical stress wave in power electronics device[J]. Journal of Hunan University (Natural Sciences), 2019, 46(4): 74-79.

[20] 李孟川, 何赟泽, 孟志强, 等. 基于声发射检测技术的电力电子器件/模块机械应力波综述[J]. 电工技术学报, 2021, 36(22): 4773-4783.

Li Mengchuan, He Yunze, Meng Zhiqiang, et al. An overview of mechanical stress wave in power electronics device/module based on acoustic emission testing technology[J]. Transactions of China Electrotechnical Society, 2021, 36(22): 4773-4783.

[21] Karkkainen T J, Talvitie J P, Kuisma M, et al. Acoustic emission in power semiconductor modules-first observations[J]. IEEE Transactions on Power Electronics, 2014, 29(11): 6081-6086.

[22] Kozak M, Gordon R. Experimental investigations of monolithic IGBT transistor acoustic emission phenomena[J]. Poznan University of Technology Academic Journals, 2019, 99: 19-28.

[23] Müller S, Drechsler C, Heinkel U, et al. Acoustic emission for state-of-health determination in power modules[C]//13th International Multi-Conference on Systems, Signals & Devices (SSD), Leipzig, 2016: 468-471.

[24] 何赟泽, 邹翔, 李孟川, 等. 30V条件下功率MOSFET器件应力波理论与试验研究[J]. 中国电机工程学报, 2021, 41(16): 5683-5693.

He Yunze, Zou Xiang, Li Mengchuan, et al. Theoretical and experimental study on stress wave of power MOSFET under 30 volts[J]. Proceedings of the CSEE, 2021, 41(16): 5683-5693.

[25] Li Mengchuan, He Yunze, Meng Zhiqiang, et al. Acoustic emission based experimental analysis of mechanical stress wave in IGBT device[J]. IEEE Sensors Journal, 2020, 20(11): 6064-6074.

[26] Bai Yun, Shen Haoning, He Yunze, et al. Analysis of the stress-wave influence parameters of silicon MOSFET under 300V drain source voltage[J]. IEEE Sensors Journal, 2021, 21(18): 20107-20118.

[27] Karkkainen T J, Talvitie J P, Kuisma M, et al. Acoustic emission caused by the failure of a power transistor[C]// 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, 2015: 2481-2484.

[28] Zhang Tao, He Dongxin, Wei Junyu, et al. Charge vibration behaviour in polyimide under the pulse voltage with different rise and fall times[J]. High Voltage, 2022, 7(1): 64-74.

[29] 张崇兴, 吴文杰, 谢佳成, 等. 中压变换器关键部件绝缘设计与评估方法研究[J]. 高电压技术, 2020, 46(10): 3407-3417.

Zhang Chongxing, Wu Wenjie, Xie Jiacheng, et al. Insulation design and assessment of critical components in MV power converter[J]. High Voltage Engineering, 2020, 46(10): 3407-3417.

[30] Li Y, Yasuda M, Takada T, et al. Pulsed electroacoustic method for measurement of charge accumulation in solid dielectrics[J]. IEEE Transactions on Dielectrics and Electrical Insulation, 1994, 1(2): 188-195.

[31] Geng Xuefeng, He Yunze, Zeng Chenghao, et al. Analysis of influence parameters of stress wave at the turn-off moment in IGBT device based on differential AE sensor[J]. IEEE Sensors Journal, 2022, 22(3): 2259-2270.

[32] 王莉娜, 邓洁, 杨军一, 等.Si和SiC功率器件结温提取技术现状及展望[J]. 电工技术学报, 2019, 34(4): 703-716.

Wang Lina, Zheng Jie, Yang Junyi, et al. Junction temperature extraction methods for Si and SiC power devices—a review and possible alternatives[J]. Transactions of China Electrotechnical Society, 2019, 34(04): 703-716.

[33] 李亚萍, 周雒维, 孙鹏菊, 等. 基于特定集电极电流下饱和压降的IGBT模块老化失效状态监测方法[J]. 电工技术学报, 2018, 33(14): 3202-3212.

Li Yaping, Zhou Luowei, Sun Pengju, et al. Condition monitoring for IGBT module aging failure on VCE(on) under certain IC conditions[J]. Transactions of China Electrotechnical Society, 2018, 33(14): 3202-3212.

[34] 惠苏新, 王鹏, 吴琦, 等. 重复脉冲占空比对环氧树脂电树生长特性影响研究[J]. 中国电机工程学报, 2020, 40(16): 5383-5392.

Hui Suxin, Wang Peng, Wu Qi, et al. Study of the influence of repetitive impulse voltage duty cycle on the treeing characteristics of epoxy resin[J]. Proceedings of the CSEE, 2020, 40(16): 5383-5392.

[35] 佟辉, 臧丽坤, 徐菊. 导热绝缘材料在电力电子器件封装中的应用[J]. 绝缘材料, 2021, 54(12): 1-9.

Tong Hui, Zang Likun, Xu Ju. Application of thermally conductive insulating materials in power electronics packaging[J]. Insulating Materials, 2021, 54(12): 1-9.

[36] Van de Wal B J, Kendall G, Sammakia B, et al. Acoustic emission analysis for fatigue prediction of lap solder joints in mode two shear[J]. International Journal of Damage Mechanics, 2001, 10(3): 256-276.

[37] 王浩宇, 赵志斌, 付鹏宇, 等. 压接型IGBT器件封装结构中PEEK框架的绝缘特性分析[J]. 绝缘材料, 2019, 52(6): 60-66.

Wang Haoyu, Zhao Zhibin, Fu Pengyu, et al. Insulating properties of PEEK frame in pressed IGBT device[J]. Insulating Materials, 2019, 52(6): 60-66.

[38] Wang Peng, Hui Suxin, Akram S, et al. Influence of repetitive square voltage duty cycle on the electrical tree characteristics of epoxy resin[J]. Polymers, 2020, 12(10): 2215.

[39] Khazaka R, Locatelli M L, Diaham S, et al. Effects of mechanical stresses, thickness and atmosphere on aging of polyimide thin films at high temperature[J]. Polymer Degradation and Stability, 2013, 98(1): 361-367.

[40] 李洁, 赖伟, 汪纪锋, 等. IGBT的加速老化试验方法研究[J]. 电力电子技术, 2018, 52(8): 73-76.

Li Jie, Lai Wei, Wang Jifeng, et al. Study on accelerated ageing methods for IGBT[J], Power Electronics, 2018, 52(8): 73-76.

Abstract Power electronic devices generate stress wave during operation. This signal can reveal the internal information and working state of the devices, and can be used for on-line monitoring of power electronic devices. It is found that there are many stress wave emission sources in the devices. However, the existing research mainly focuses on the stress wave generated by the whole device, but ignores the correlation between the specific defect types and the stress wave. To solve this problem, this paper proposes a stress wave research method based on artificially set defects to explore the direct relationship between defect form and stress wave characteristics.

Firstly, from the phenomenon that space charge generates acoustic signals after being disturbed by pulsed electric field, the formation mechanism of stress wave is analyzed from the perspective of packaging insulation. It is found that the vibration of space charge at the edge of pulse in insulating material may be one of the emission sources of stress wave. Then the samples with single interface defects and aging defects were set, and the stress wave was detected. In the time domain and frequency domain, the stress wave generated by the defective samples are compared with those generated by the normal samples, to explore the influence of different defect types on stress wave parameters.

The experimental results show that the stress wave generated by the sample with interface defects can be regarded as the dislocation superposition of the stress wave generated by the sample under two normal conditions, and the waveform is related to the physical properties on both sides of the interface and the acoustic resistance at the interface. The reason for this phenomenon is that space charges will accumulate on both sides of the interface, and the stress wave generated by its vibration will interfere with the original stress wave. In addition, the acoustic resistance at the interface will also make the stress wave attenuate and disperse in the propagation process, resulting in the distortion of time-domain waveform. The spectrum analysis results show that the frequency domain components of stress waves are mainly concentrated in the range of 0~20MHz. In the case of interface, the frequency spectrum of stress wave will produce additional peaks at high frequencies, its position and amplitude are related to the interface conditions. The experimental results of aging samples show that with the increase of aging degree, the frequency domain component of stress wave gradually concentrates to the low frequency range. The reason is due to the internal structure changes of material molecules. The interaction force between molecules can be regarded as elastic force, and its vibration frequency is affected by the degree of coupling between molecules. The stronger the coupling, the greater the vibration frequency. In the aging state, due to the destruction of the molecular structure, the degree of coupling between them decreases, which leads to the reduction of the molecular vibration frequency.

Through the study of the stress wave generated by the sample under the interface and aging defects, the following conclusions can be drawn: ①Defects in power electronic devices lead to changes in the internal structure, which result in changes in the stress wave parameters. ②The influence of interface defects on stress wave is mainly reflected in the generation mechanism and propagation. The existence of the interface will distort the time-domain waveform of the stress wave and produce new spectral peaks at high frequencies. ③Aging defects reduce the coupling degree between molecules, which leads to the increase of the low-frequency component and the decrease of the high-frequency component of the stress wave generated by molecular vibration. This phenomenon becomes more obvious with the increase of the aging degree of the sample.

keywords:Power electronic devices, stress wave, condition monitoring, interface defect, aging state

DOI:10.19595/j.cnki.1000-6753.tces.221282

中图分类号:TM930

国家自然科学基金(51907105,U1966209)和山东省自然科学基金(ZR2019QEE013)资助项目。

收稿日期 2022-06-30

改稿日期 2022-07-22

何东欣 男,1990年生,硕士生导师,研究方向为电力电缆等电气设备在线监测与故障诊断、电气绝缘空间电荷理论及其应用。E-mail:hdx@sdu.edu.cn

李清泉 男,1969年生,教授,博士生导师,研究方向为高电压技术、电力变压器内绝缘状态在线监测、绝缘劣化机理和输配线路防雷技术等。E-mail:lqq@sdu.edu.cn(通信作者)

(编辑 李冰)