图1 4.5 kV弹性压接型IGBT器件的结构[26]

Fig.1 Structure of 4.5 kV compliant press-pack IGBT device[26]

摘要 压接型绝缘栅双极型晶体管(IGBT)是支撑柔性直流装备研制的核心器件,弹性压接型IGBT能更好地实现器件中各并联芯片的压力均衡,在电网应用场景中前景广阔。然而,器件内部的绝缘问题是高压器件研制过程中面临的主要挑战之一,因此,有必要在实际工况下分析器件绝缘结构中的瞬态电场分布,以指导绝缘设计。该文针对弹性压接型IGBT器件内部的复合绝缘结构,采用时域边界电场约束方程法,分别计算了单次关断工况和重复性导通关断工况下弹性压接型IGBT器件子模组封装绝缘结构中的瞬态电场分布。结果表明两种工况下,封装绝缘结构中最大电场强度均出现在芯片/聚酰亚胺(PI)钝化层界面上,且由于介质分界面两侧的绝缘材料介电常数和电导率参数不匹配,分界面上将会积累电荷。界面电荷密度随着时间逐渐增大,并影响电场分布,使得子模组中最大电场强度的模值和位置随时间发生变化。同时,单次关断工况下,最大电场强度的模值会更大。此外,该文提出通过改变器件中使用的绝缘材料,提高界面处的材料参数匹配程度,可以实现对子模组内电场分布的改善。该文所提方法能显著降低器件内部最大电场强度的模值,可为弹性压接型IGBT器件的封装绝缘结构设计和优化提供参考。

关键词:弹性压接型IGBT 时域有限元法 电准静态场 单次关断工况 重复性导通关断工况 电场调控方法

随着柔性直流输电技术的不断发展,高压大功率绝缘栅双极型晶体管(Insulated Gate Bipolar Transistor, IGBT)被广泛应用在各类大容量电力换流和控制装备中,成为直流电网中不可或缺的核心部件[1-7]。高压大功率IGBT器件有焊接型封装和压接型封装两种主要封装形式。相比于焊接型IGBT器件,压接型IGBT器件具有失效短路、易于串联、易于驱动等优点,适合高可靠性的电网应用场景,逐渐成为电网应用的主要封装形式[8]。压接型IGBT器件又有刚性压接型和弹性压接型两种形式[8-11],相比于刚性压接型器件,弹性压接型IGBT器件加入了碟形弹簧组件调控压力,因而模块中并联芯片的压力分布更为均匀,器件内部压力差对并联芯片特性的影响会更小。此外,弹性压接型IGBT器件填充有机硅凝胶作为主要绝缘材料,绝缘性能比用高压氮气作为主要绝缘材料的刚性压接型器件更为优越。因此,弹性压接型封装形式在电网中的应用前景更加广阔[10]。

弹性压接型IGBT器件的应用工况复杂,器件的工作电压不再是传统的直流或交流电压。在混合型直流断路器的正常运行状态下,主回路上的IGBT器件长期处于导通状态,转移支路上的器件关断;故障时,转移支路上的器件导通,而主回路上的IGBT器件关断。因此,直流断路器中的IGBT器件工作在单次关断或导通工况,其电压可以看成具有一定上升沿的非理想阶跃电压[12-13]。而在高压直流换流阀中,IGBT器件工作处于重复导通和关断状态,其工作电压为正极性重复方波电压[14-15]。同时,由于IGBT器件的封装绝缘结构通常采用由多种材料组合而成的复合绝缘结构[16],在瞬态电压激励下,绝缘结构中的介质交界面将出现电荷聚集现象[17-18],导致复合绝缘结构中的局部电场加强,可能引发器件的局部放电、绝缘劣化和击穿现象[19],造成器件绝缘失效问题。因此,为了提升弹性压接型IGBT器件的绝缘性能,需要掌握实际工况下器件内瞬态电场的准确分布。

现有对高压IGBT器件封装绝缘结构的电场研究相对较少,通常在静电场[15,20-21]或恒定电场[22]下进行,没有考虑实际工况下电场的瞬态特性。文献[23-24]分别在单次关断和重复性导通关断工况下研究了刚性压接型IGBT子模组中封装绝缘结构的瞬态电场分布,并提出了瞬态电场的调控方法,算法的有效性通过了具有电场解析解的绝缘结构算例的验证,为刚性压接型器件封装绝缘结构的优化设计提供了指导[25]。然而,对于弹性压接型IGBT器件而言,其内部封装绝缘结构与刚性压接型器件存在显著差异,绝缘材料的选择也不相同,在实际工况下的瞬态电场分布也存在一定差异,因此,需要在实际工况下研究弹性压接型IGBT器件封装绝缘结构中电场的瞬态特性。

为此,本文建立弹性压接型IGBT器件在单次关断与重复性导通关断电压工况下瞬态电场计算的数学模型,确定初值-边值问题,采用文献[25]中的瞬态边界电场约束方程法,系统地研究弹性压接型IGBT器件在单次关断和重复导通关断工况下的电场分布,获得器件封装绝缘结构中电场的瞬态特性。对比分析两种工况下弹性压接型IGBT器件各主要复合绝缘结构界面电场与界面电荷的瞬态变化规律,在此基础上提出改变钝化层材料以提高绝缘介质间参数匹配程度的方法实现对器件内部电场的改善。计算发现该方法使得器件内的最大电场强度大大降低,为弹性压接型IGBT器件内部结构绝缘设计提供了新的思路。

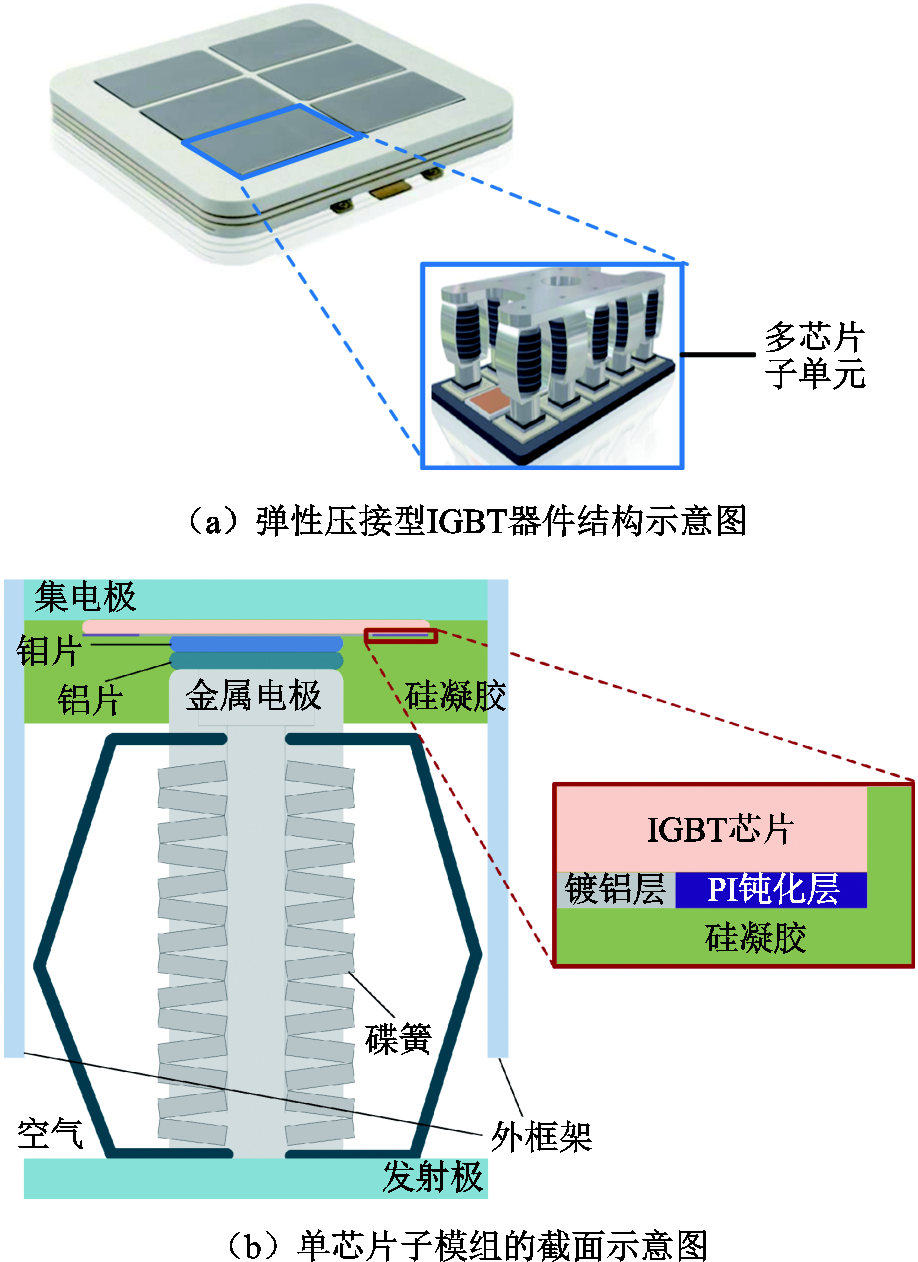

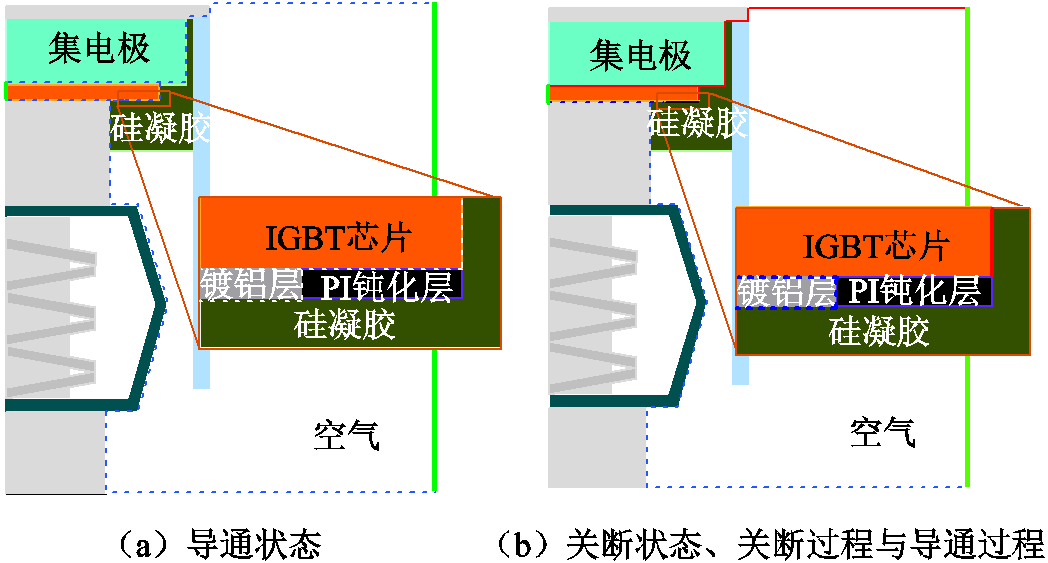

弹性压接型IGBT器件(后文简称器件)是将一定数目的IGBT子单元并联在一起,以提升器件的通流能力。而一个子单元由数个IGBT子模组和快恢复二极管(Fast-Recovery Diode, FRD)子模组构成[26]。图1给出了4.5 kV器件的结构,其中图1a为整个器件的结构示意图,蓝色实线框中为包含多个IGBT芯片的子单元;图1b为单芯片子模组(后文简称子模组)内部封装绝缘结构放大后的截面示意图。需要说明的是,因商业保密原因,本文不便给出器件结构的具体尺寸。

图1 4.5 kV弹性压接型IGBT器件的结构[26]

Fig.1 Structure of 4.5 kV compliant press-pack IGBT device[26]

从图1b中可以看出,单芯片子模组从上到下依次为集电极、IGBT芯片、钼片、铝片、金属电极、碟簧、发射极。IGBT芯片底部为芯片发射极,镀有一层金属铝,与金属电极接触,并通过导流片与下方器件的发射极实现电气连接。芯片终端涂有钝化层,起保护芯片和提高芯片耐受电压的作用[27]。整个结构放在一个外框架中,芯片周围灌封有机硅凝胶,在提高封装结构绝缘性能的同时,还能起到保护芯片、密封防潮的作用[28]。

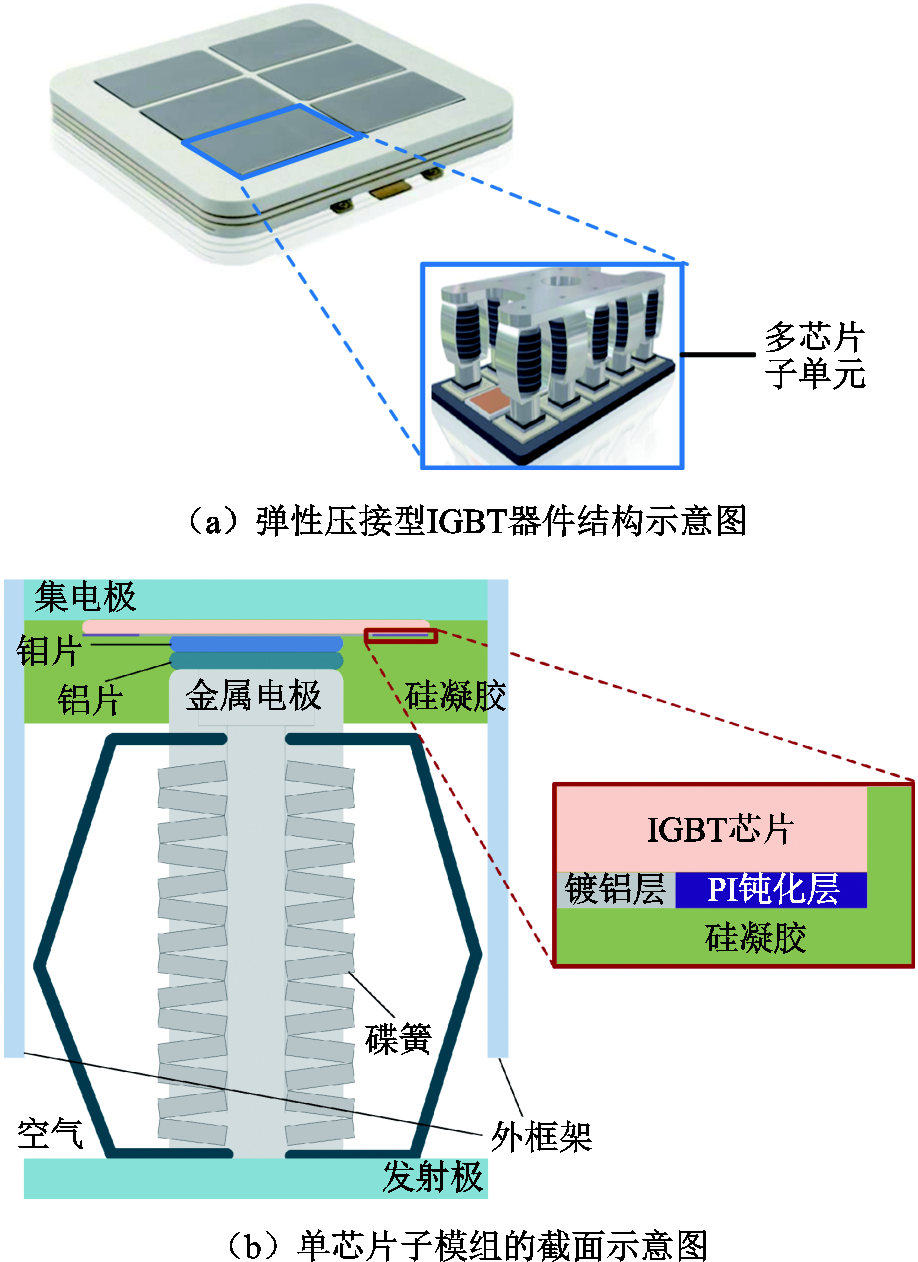

在单次关断工况下,器件的工作电压为带有一定上升沿的非理想阶跃电压,其电压波形如图2所示。图2中Um为非理想阶跃电压的幅值,tr为非理想阶跃电压的上升时间,即关断过程持续的时间。

图2 单次关断工况的非理想阶跃电压

Fig.2 Nonideal step voltage under single turn-off condition

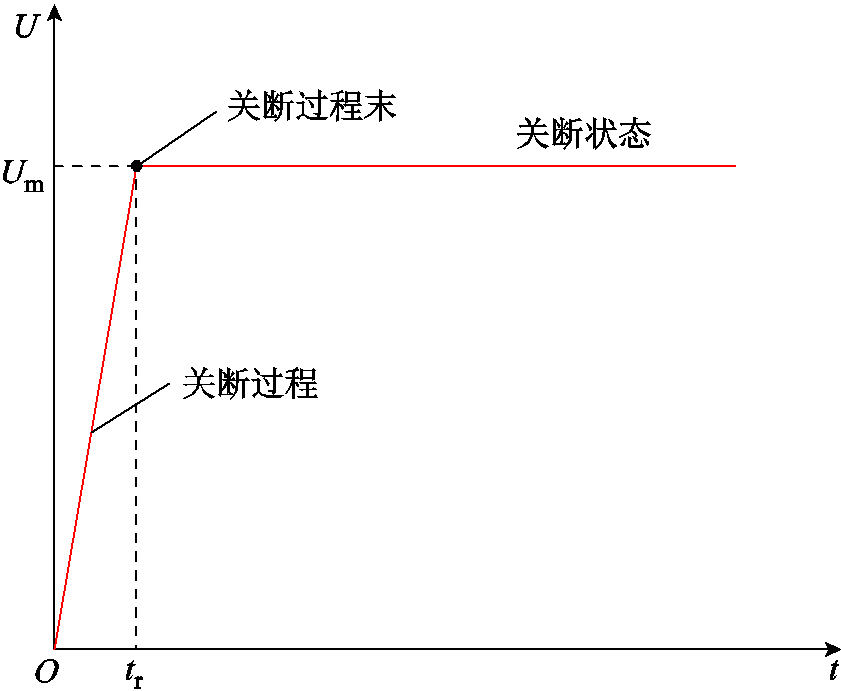

在重复性导通关断工况下,器件的工作电压为正极性重复方波电压,如图3所示。在导通过程中,器件中并联的IGBT芯片瞬间开通,在μs级的时间内,芯片中电压迅速降为零;在导通状态下,器件流通电流,不承受电压。反之,在μs级的关断过程中,IGBT芯片瞬间关断,芯片两端电压从零瞬间上升到高电压;在关断状态下,器件不流通电流,稳定承受高电压。图3中,Um为正极性周期方波电压us(t)的幅值,T为方波周期,α为方波的占空比;tr为方波的上升时间,是指电压从零上升到Um的时间,也就是器件关断过程持续的时间;tf为方波的下降时间,是指电压从Um下降到零的时间,也就是器件导通过程持续的时间。

图3 重复性导通关断工况的正极性重复方波电压[24]

Fig.3 Positive polarity repeated square wave voltage under repeatable turn-on and turn-off condition[24]

在计算弹性压接型器件的瞬态电场时,由于感应电场远远小于库伦电场[29],满足电准静态条件,因此瞬态电场的控制方程为电准静态场瞬态电场的控制方程。用标量电位表示的瞬态电场的初值-边值问题可写为

(1)

(1)

式中,e和g分别为材料的介电常数和电导率;t为时间;j为电位;Γ1为第一类高压边界,此时电位为u(t),在单次关断工况下,u(t)为图2所示非理想阶跃电压,在重复导通关断工况下,u(t)为图3所示正极性重复方波电压;Γ2为第一类低压边界,电位为0 V;Γ3为第二类齐次边界,边界上电位的法向导数为0;j|t=0为初始时刻的电位值,在计算中设置为0V。

由于子模组关于中间轴线呈左右对称,因此本文中将子模组的三维结构简化为二维,选择截面的右半边作为计算模型,具体的边界条件如图4所示。

图4 弹性压接子模组的二维数学模型及边界条件

Fig.4 2-D numerical model and boundary condition of compliant press-pack IGBT submodule

如图4a所示,当IGBT芯片处于导通状态时,芯片流通电流,可近似认为芯片的导通压降为0 V,芯片相当于导体。子模组的集电极、IGBT芯片、镀铝层、金属电极、导流片和发射极的电位设为0 V,属于第一类低压边界条件,即式(1)中的边界Γ2,在图中用虚线标注。子模组的左侧为对称轴,电场的法向分量为0;同时认为电场只集中在器件内部,故右边界的电场强度的法向分量也为0,均为第二类齐次边界,即式(1)中的边界Γ3,用绿色实线表示。

器件在关断状态、关断过程和导通过程时,边界条件如图4b所示。此时IGBT芯片未导通,持续承受高电压。子模组的集电极与芯片上表面为高电位;通过芯片内部电场仿真可知,芯片外边沿也为高压边界[30],属于迪利克雷边界,即式(1)中的边界Γ1,在图4中用红色实线标出。发射极、镀铝层、金属电极、导流片电压为0 V,为迪利克雷边界,用蓝色虚线表示。

整个计算区域为各个边界包围起来的闭合区域,共包含五种绝缘材料。在器件封装绝缘结构的电场计算中,通常将芯片简化成材料硅[21-22],本文沿用了这一简化。芯片终端的钝化层为聚酰亚胺(Polyimide, PI),外框架材料为尼龙6。模型中涉及材料的基本参数见表1。

表1 弹性压接子模组计算模型中材料的基本参数

Tab.1 Basic parameters of materials in compliant press-pack IGBT subunit

材料相对介电常数电导率/(S/m) 硅凝胶2.781.04×10−12 PI2.964.00×10−14 硅11.702.50×10−4 空气1.001.00×10−11 尼龙64.001.67×10−12

表1中,硅凝胶和PI的相对介电常数和电导率来自本课题组的实测数据[31];硅的相对介电常数和电导率采用文献[22]中的参数;空气为混合物,电导率和介电常数没有固定数值,但是由于空气中大部分是氮气,因此采用文献[22]中氮气的参数;尼龙6的参数来自文献[32]。

采用加权余量法,利用Lagrange乘子法施加边界条件,式(1)中控制方程所对应弱形式[33]为

(2)

(2)

式中,N为权函数;Ω为整个计算区域。

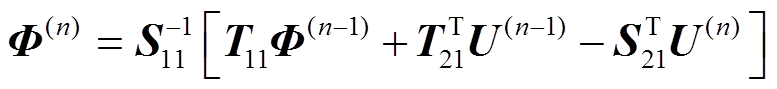

为了能够准确计算界面的电场强度,采用文献[20]中的瞬态边界电场约束方程法进行计算,计算中采用有限元法和时间差分,分别对式(2)进行空间和时间离散,再对场域内的所有节点编号重新排序[25]。时域有限元方程可以分解成两个方程,分别求解瞬态电位和边界上电场强度法向分量,即

(3)

(3)

(4)

(4)

式中,Φ为待求解的节点电位列向量;En为边界节点的法向电场列向量;Δt为计算时间步长;上标n-1和n分别表示第n-1个和第n个时刻;系数矩阵S、T、K和H中各元素的表达式见文献[25]。

相邻两种介质的分界面上的电荷密度可以表示为

(5)

(5)

式中,ε为介质的介电常数;En为介质边界上的电场法向分量,下标1、2区分两种介质,界面上的法向量的参考方向为介质1指向介质2。

计算中,选用一阶线性三角形单元对场域进行剖分。为了避免由于电压激励的剧烈变化引起的数值振荡[34],在时间差分上选用后向欧拉法。需要强调的是,本计算方法已被证明在器件内部电场计算方面具有极高的精度[25]。

在单次关断工况计算中,子模组承受的电压为图2所示的非理想阶跃电压,硅基器件的关断过程一般为2~5 μs,因此电压的上升时间tr = 5 μs,幅值Um=4 500V,计算总时间为2 500s,第一个计算时刻为t = 5 μs,对应图2中的关断过程末,之后的计算时间步长为1s。

在重复导通关断工况下,子模组承受的电压u(t)为图3所示正极性重复方波电压。为保证精度,每个周期选取4个点计算,分别为关断过程末、关断状态末、导通过程末、导通状态末。方波电压的幅值Um=4500V,占空比α=0.5,方波电压的上升时间tr和下降时间tf与单次关断工况的上升时间相同。根据文献[24]的仿真结果,方波电压的频率对于器件封装绝缘结构的电场分布影响不大,因此,计算时方波电压的频率f=1Hz,计算总周期数为2 500。

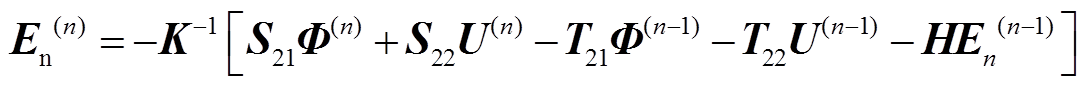

为分析子模组内电场和电荷随时间的变化,选择芯片/PI钝化层界面上横坐标为x=6.66 mm的一点,分别在单次关断和重复导通关断工况下,绘制PI钝化层侧的电场强度模值和界面电荷密度随时间的变化如图5所示。

图5 界面电场强度和界面电荷密度随时间的变化

Fig.5 The changes of interfacial electric field and interfacial charge with time

在芯片/PI钝化层界面上,根据式(5)可知,界面上法向量的正方向从PI钝化层指向芯片,界面电荷的极性为负极性。单次关断工况下子模组持续承受高压。根据麦克斯韦-瓦格纳极化效应,由于介质分界面两侧的介电常数和电导率存在差异,界面上将会积累电荷[35]。因此,随着阶跃电压的作用时间增加,界面上积累的电荷逐渐增大,界面电荷对电场起增强作用,导致界面上的电场强度也会逐渐变大[23]。随着时间的推移,界面电荷密度大小逐渐稳定,界面电场强度也随之趋于稳定。

在重复导通关断工况下,外施电压为正极性重复方波电压,关断过程和导通过程的持续时间达μs级,界面电荷在这两个阶段内来不及变化;在关断状态下,子模组承受高电压,与单次关断工况相同,界面电荷逐渐积累;在导通状态下,子模组不承受电压,界面电荷逐渐消散,因此界面电荷波形为三角波形。然而关断状态积累的电荷无法在导通状态时完全消散,因此一个周期内积累的净电荷不为零,进而导致随着时间推移,界面电荷量逐渐增大,直至达到稳定。界面电场强度的变化波形与方波电压的波形类似,在关断状态下,界面电场强度逐渐增大;在导通状态下,虽然外施电压变为0 V,但由于界面电荷的存在,子模组内的电场强度不为零。

接下来针对两种工况下子模组内的电场和电荷的分布特性进行研究。需要注意的是,对于重复导通关断工况,如图5b所示,在一个周期内关断状态末时刻的界面电荷密度和电场强度最大,有可能发生绝缘击穿和局部放电,有必要分析此时子模组的电场特性;此外,导通状态末的电场主要受界面电荷影响,也需要关注该时刻的电场特性。因此在重复导通关断工况下,选择图3中每个周期的导通状态末和关断状态末两个时刻,分析子模组中的电场和电荷特性。

2.2.1 子模组中电场分布随时间的变化

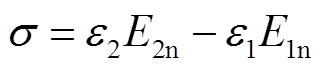

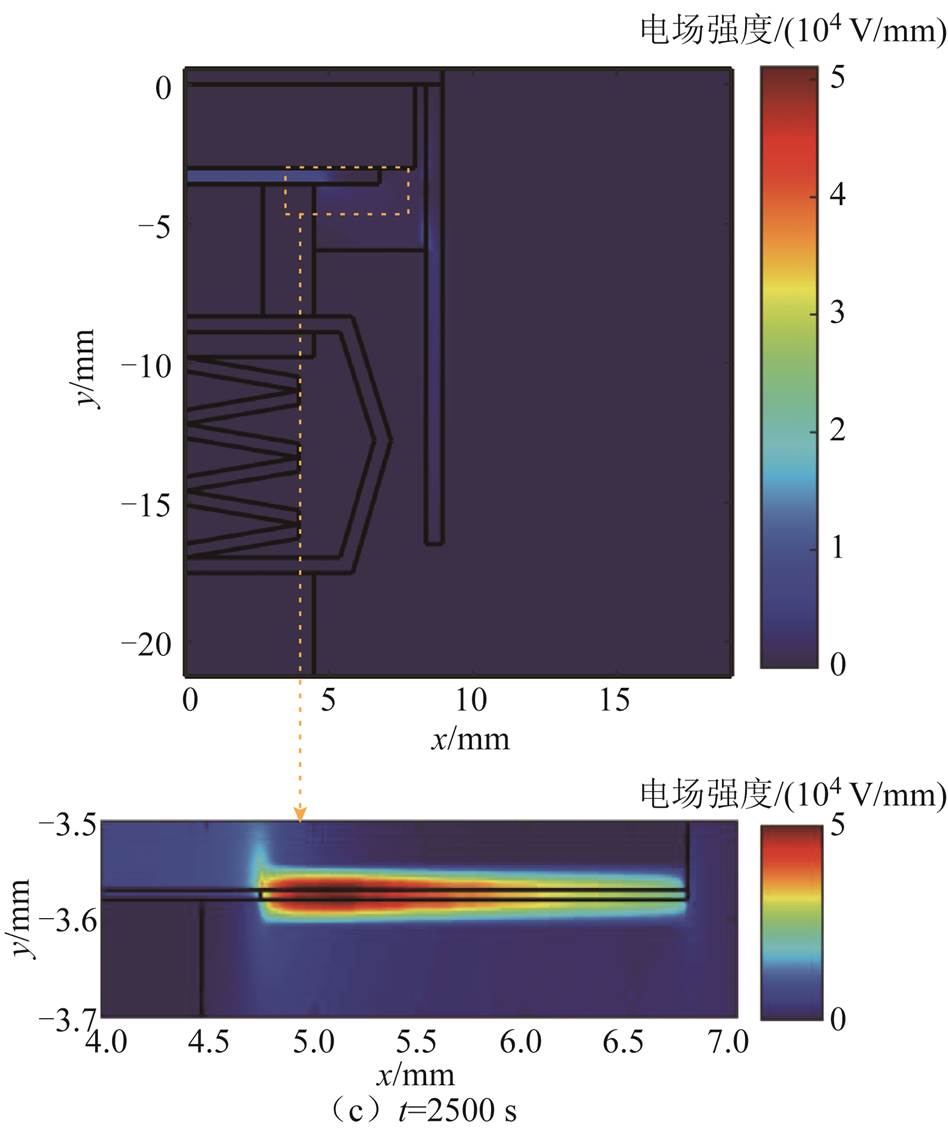

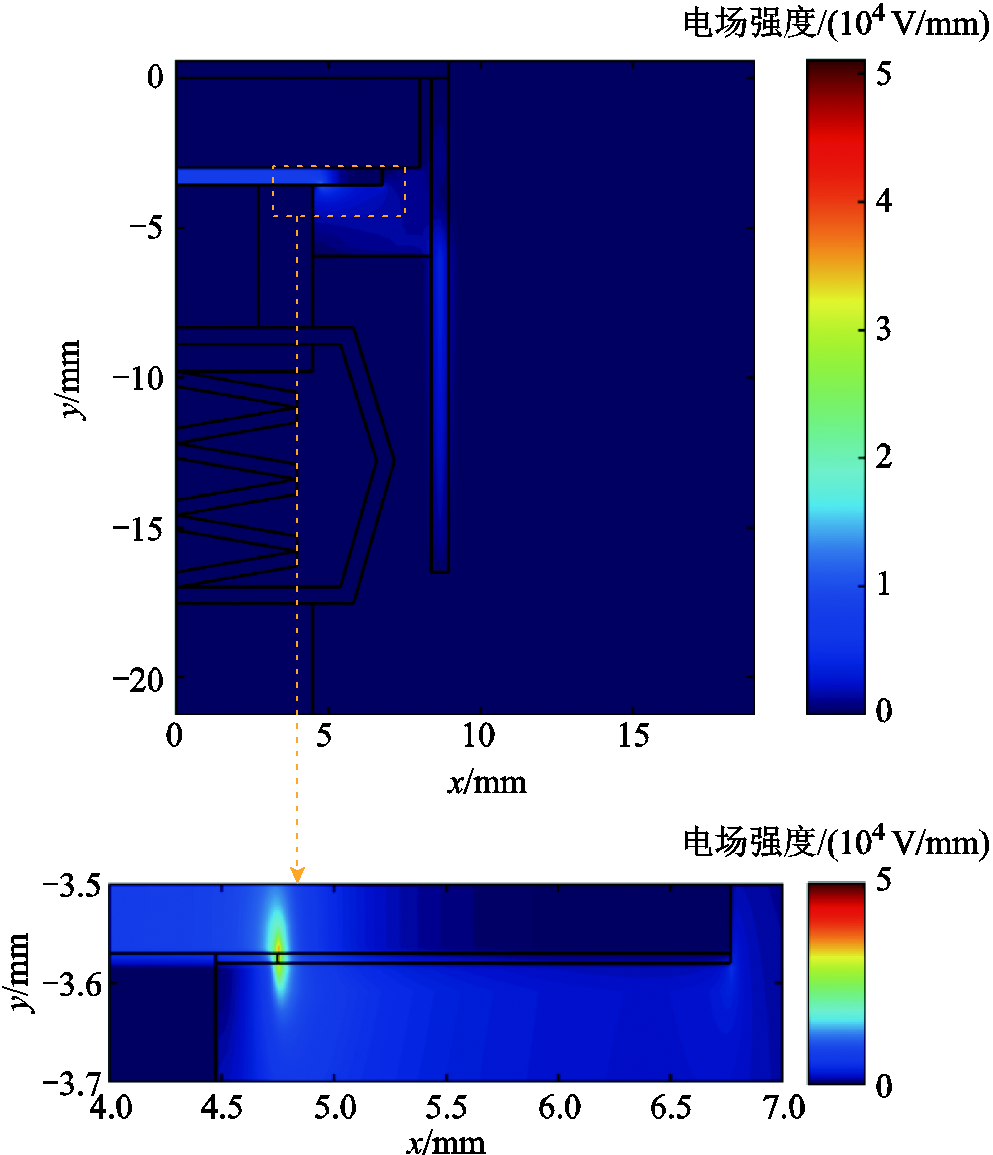

为了展示在单次关断工况下,器件封装绝缘结构的瞬态电场分布,图6给出了不同时刻下器件封装绝缘结构中的电场分布云图。

图6 电场分布云图随时间的变化

Fig.6 The variation of electric field distribution with time

如图6a所示,当t = 5 μs时,子模组刚刚关断,在外施电压的作用下,电场分布云图中芯片/镀铝层/PI钝化层结合处电场局部加强,这是由于三结合点处的介电常数和电导率不连续造成的,而此时子模组中的介质分界面来不及积累电荷,子模组中其他部分的电场强度很小;随着时间推移,如图6b所示,当t = 500 s时,由于芯片/PI钝化层界面(后文简称界面1)和PI钝化层/有机硅凝胶界面(后文简称界面2)上开始积累电荷,界面电荷调控电场,使得PI钝化层内部、芯片和有机硅凝胶中的电场强度逐渐变大。此外,由于电荷的作用,子模组的外框架中电场强度也逐渐增大;当t = 2 500 s时,界面电荷积累更多,PI钝化层内部、芯片和有机硅凝胶中的电场强度进一步变大。综上所述,单次关断工况下PI钝化层、界面1和界面2处的电场强度较大,需要重点关注。

2.2.2 子模组中最大电场强度的分布情况

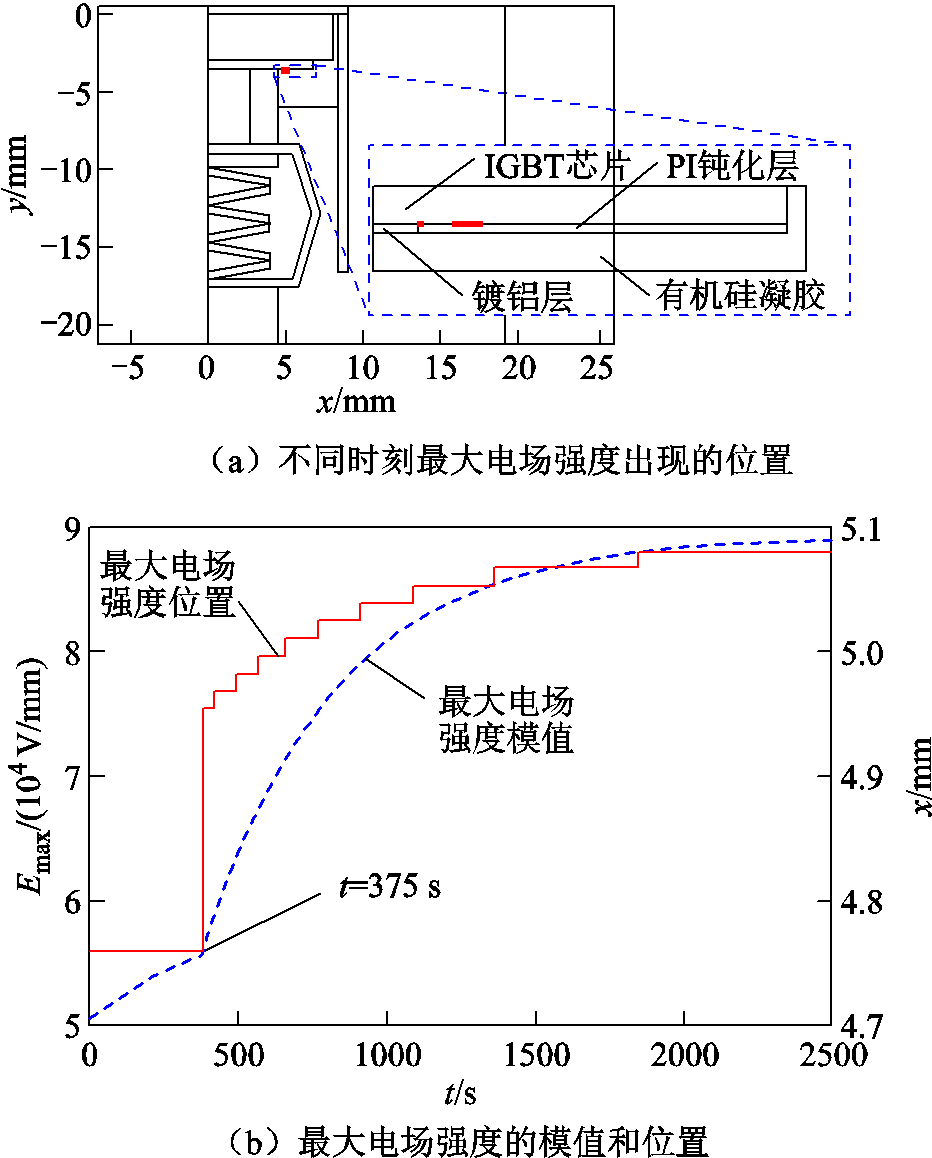

为研究单次关断工况下弹性压接型IGBT子模组中最大电场强度随时间的变化,图7给出了最大电场强度的位置和模值随时间的变化,其中图7a为每个计算时刻下最大电场强度出现的位置的叠加,红点即为最大电场强度出现的位置。可见,子模组中最大电场强度出现的位置始终位于同一界面上,即芯片/PI钝化层界面,因此可用横坐标的变化来表示位置的变化。

由图7b可知,子模组内最大电场强度的模值随时间逐渐增大。当t<375 s时,最大电场强度位于界面1的左侧x = 4.76 mm处,该点为芯片/镀铝层/PI钝化层三结合点,由于介电参数不匹配,该点的电场局部加强;当t = 375 s时,最大电场强度出现的位置突然沿+x轴方向移动到界面1上x = 4.95 mm处;当t>375 s时,最大电场强度出现的位置沿+x轴方向呈阶梯状移动,这是由于界面1上的电荷对电场起增强作用,随着积累电荷逐渐增多,界面1上的电场强度逐渐变大。根据2.1节得出的结论,随着时间的推移,界面电荷分布将会逐渐稳定,导致最大电场强度出现的位置随时间的变化逐渐缓慢,即最大电场强度出现的位置也会逐渐稳定不变。

图7 最大电场强度分布

Fig.7 The variation of maximum electric field with time

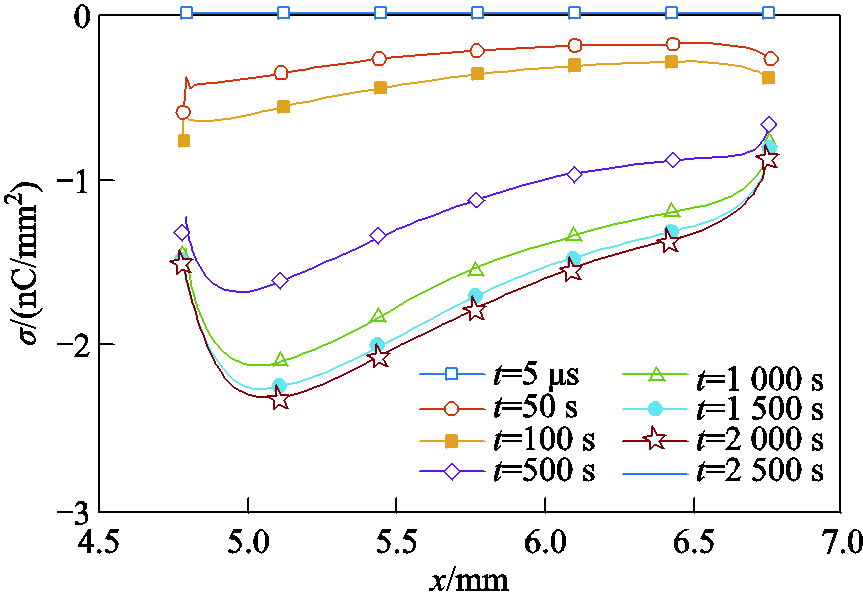

2.2.3 界面电荷分布特性

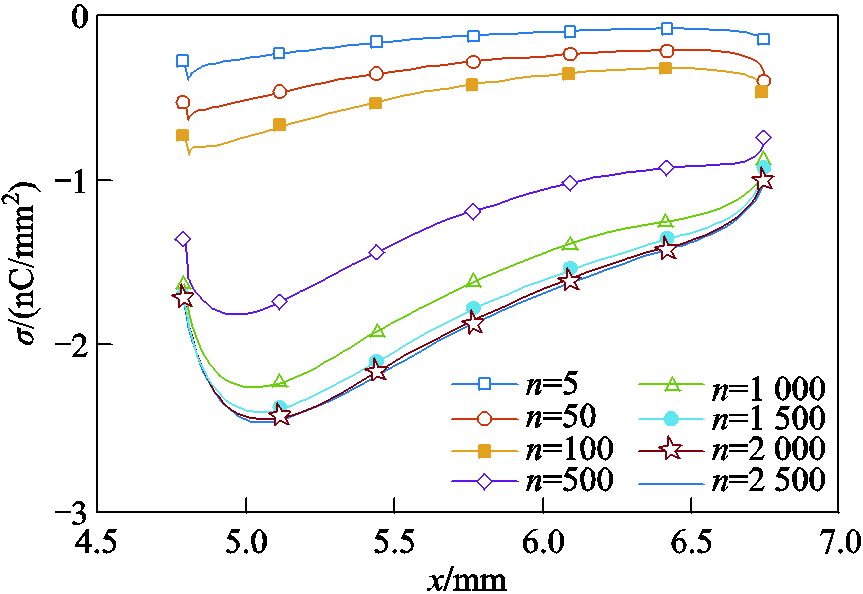

由2.1节的分析可知,随着时间的推移,子模组内的绝缘介质分界面上会不断积累电荷,导致电场的瞬态变化,因而需要关注界面上电荷密度的变化。因为最大电场强度出现在界面1上,因此提取该界面上的界面电荷进行分析。界面上法向量的参考方向为PI钝化层指向芯片。随着时间的增加,界面1上的电荷密度分布如图8所示。

由图8可知,随着时间的推移,界面1积累的电荷量逐渐增大。在初始阶段,当t<100 s时,界面电荷积累较少,界面1的最大电荷密度出现的位置为界面最左侧端点,即三结合点附近;当t>500 s时,界面1上最大电荷密度出现的位置逐渐向+x轴方向移动,并逐渐趋于稳定,这与图7b中实线的变化规律相同。

图8 单次关断工况芯片/PI钝化层界面(界面1)的电荷密度分布

Fig.8 Charge density at the interface of the chip /PI passivation layer (interface 1) under the single turn-off condition

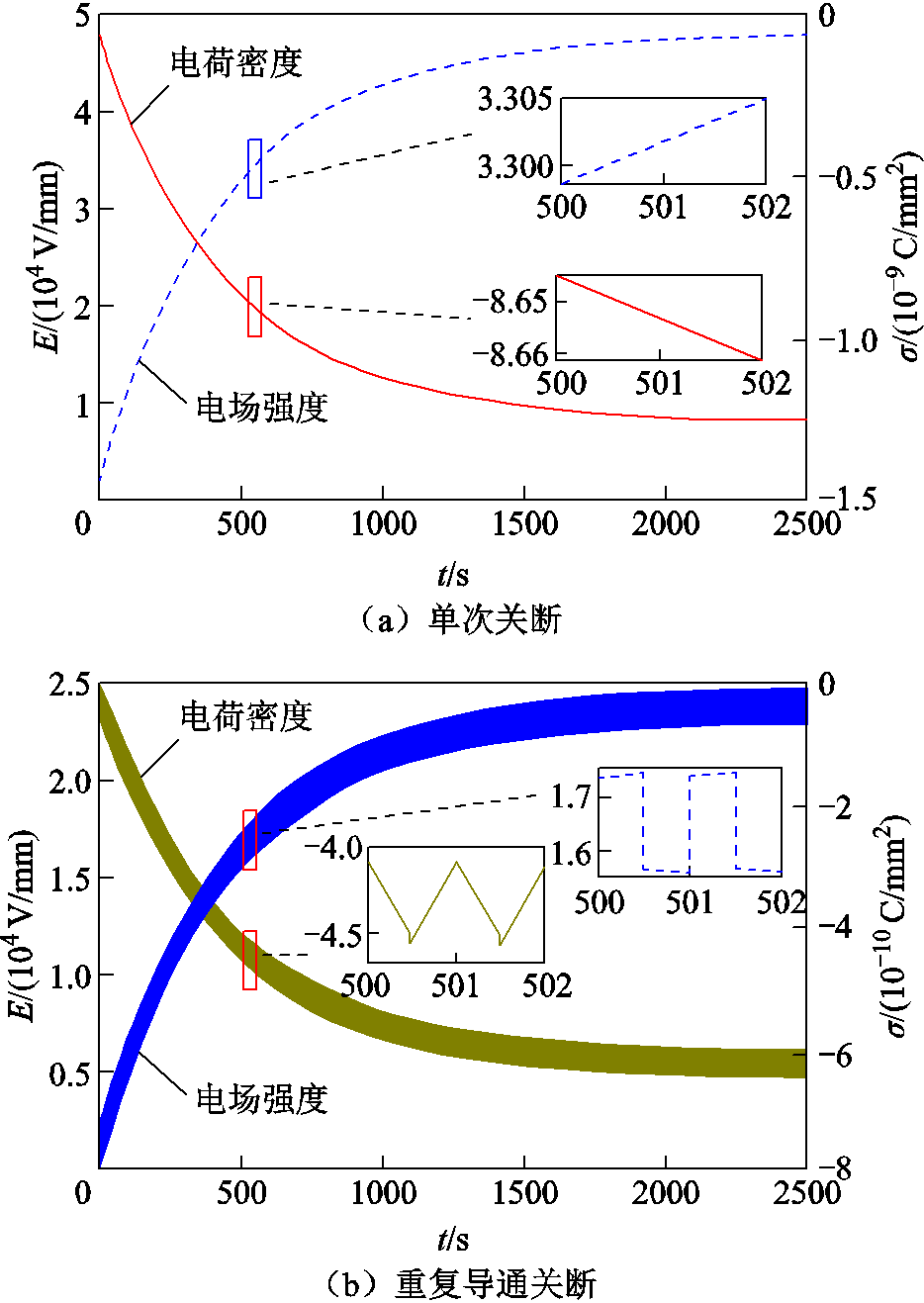

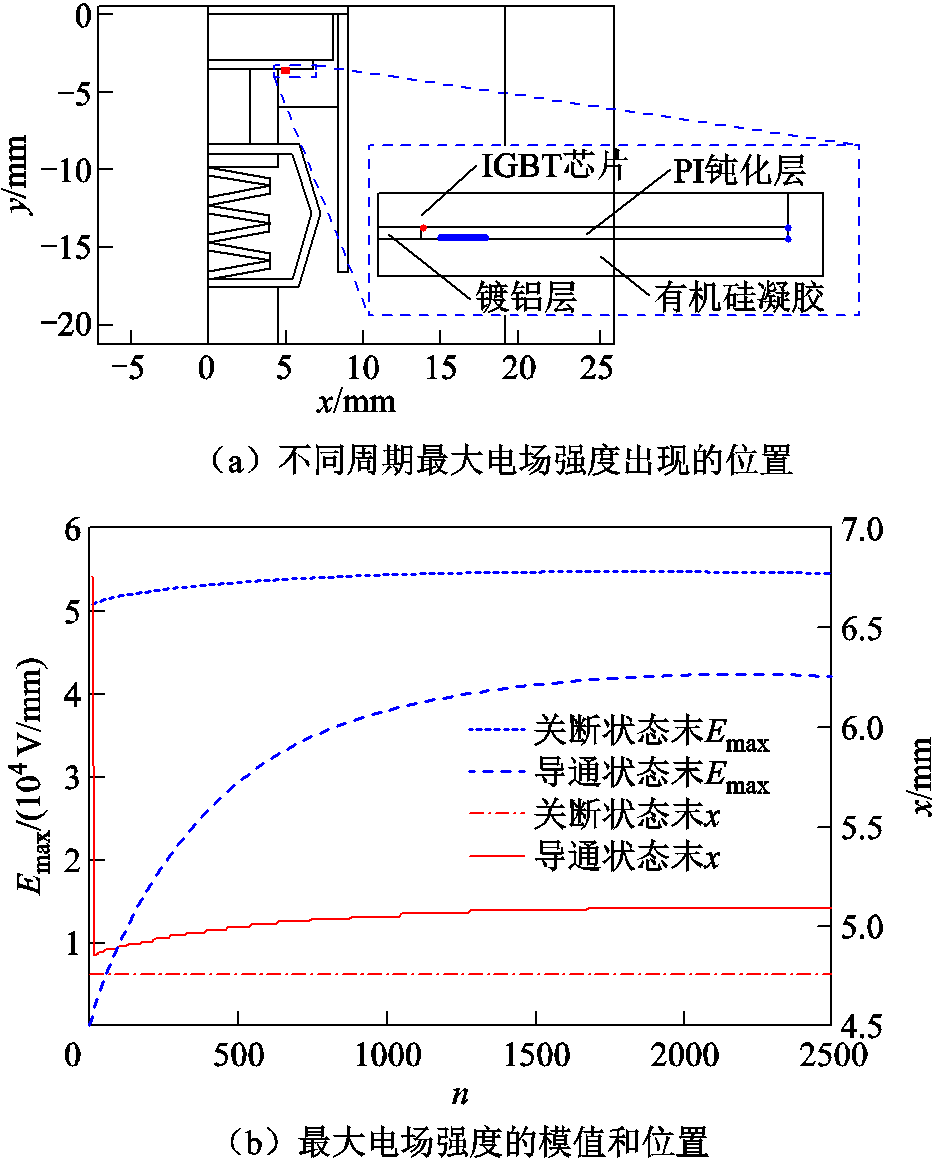

2.3.1 子模组中最大电场强度随时间的变化

根据2.1节分析,本节选择每个周期的导通状态末和关断状态末两个时刻,分析子模组中的电场和电荷分布特性。图9给出了重复导通关断工况下子模组内最大电场强度随周期数的变化情况。图9a中不同周期关断状态末的电场强度最大值出现的位置用红色点标出,导通状态末的电场强度最大值出现的位置用蓝色点标出。由图9a可知,不同周期关断状态末,子模组内的最大电场强度出现在界面1,即芯片/PI钝化层界面;导通状态末子模组内最大电场强度则主要出现在界面2,即PI钝化层/有机硅凝胶界面。

图9 最大电场强度的分布

Fig.9 The distribution of maximum electric field

在图9b中,实线表示关断状态末最大电场强度出现位置的横坐标随周期数的变化。结果表明在不同周期关断状态末,最大电场强度始终出现在界面1的左侧x = 4.76 mm处,即三结合点处,没有发生转移。而点画线则说明子模组在导通状态末的最大电场强度最开始出现在界面2的最右侧x=6.75 mm处,紧接着突然转移至x= 4.85 mm处,随着周期数逐渐增加,沿+x轴方向逐渐右移。

同时从图9b中可以看出,在外施电压和界面电荷的共同作用下,关断状态末子模组内的最大电场强度保持一个较高的数值;而在导通状态下,子模组不承受电压,内部的电场分布主要由子模组内的介质分界面积累的电荷决定。如导通状态末最大电场强度模值曲线所示,在第一个周期内,界面电荷几乎为零,最大电场强度也为零,随着电荷逐渐积累,最大电场强度也逐渐增大。由于导通状态末的最大电场强度模值总是小于关断状态末,因此关断状态末的子模组电场和电荷分布对于绝缘结构设计具有更重要的参考意义。

由图9和图7对比可知,单次关断工况和重复导通关断工况下,子模组内的最大电场强度总是出现在芯片/PI钝化层界面上,且单次关断工况下,最大电场强度的模值更大,出现的位置也会随着时间发生转移,对器件的绝缘性能要求更高。因此在进行器件的绝缘设计的时候需要考虑具体的应用工况。

2.3.2 界面电荷分布特性

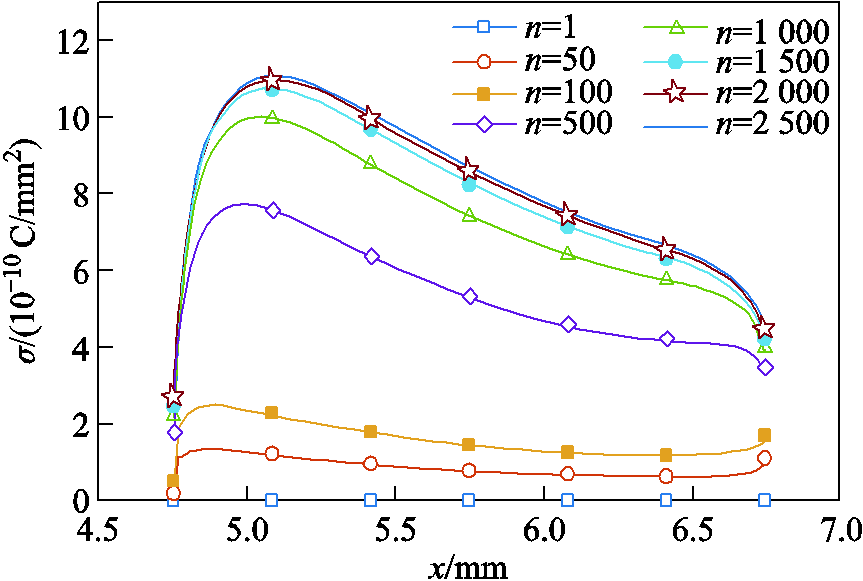

由2.3.1节分析可知,在重复导通关断工况下,子模组中界面1和界面2上的电场强度很大,需要关注两个界面上的电荷密度变化。不同周期关断状态末芯片/PI钝化层界面上电荷密度如图10所示。

图10 关断状态末芯片/PI钝化层界面(界面1)的电荷密度

Fig.10 Charge density at the interface of the chip /PI passivation layer (interface 1)at the end of turn-off state

由图10和图8对比可知,重复导通关断工况下界面1的电荷密度的变化规律与单次关断工况下相同,但是单次关断工况下的电荷密度数值更大,这与2.3.1节描述的子模组内最大电场模值的大小关系相同。导通状态末最大电场强度出现的位置位于界面2,随着时间的增加,界面2上的电荷密度分布如图11所示。其中,该界面的法向量的参考方向从有机硅凝胶指向PI钝化层。两个界面的电荷密度变化规律相似。

图11 导通状态末PI钝化层/有机硅凝胶界面(界面2)的电荷密度

Fig.11 Charge density at the interface of PI passivation layer/organosilicon gel (interface 2) at the end of turn-on state

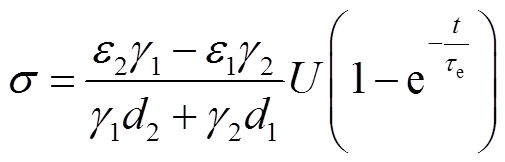

为降低子模组内的最大电场,可以采用优化子模组内绝缘材料介电常数和电导率的匹配程度的方法。根据文献[36]可知,对于双层介质的平行板电容器结构,当两种介质形状规则且厚度已知的情况下,对其施加阶跃电压时,介质分界面上将会出现电荷弛豫过程,参考文献[36]中给出的电荷弛豫表达式为

(6)

(6)

式中,界面上的法向量以介质1侧指向介质2侧为正;ε、γ分别为介质的介电常数和电导率;d为与介质形状相关的具有长度量纲的常数;下标1、2区分两种介质;U为施加直流电压;τe为电荷弛豫时间常数,其大小不会对稳态电荷分布造成影响。由式(6)可知,当ε2γ1−ε1γ2≠0即ε2/γ2−ε1/γ1≠0时,界面上积累电荷,积累的电荷极性与这一差值的正负有关;这一差值越大,界面两侧介质的参数匹配程度越差,积累的电荷量越多。因此,界面两侧介质ε2/γ2−ε1/γ1的大小,可以表征稳态条件下界面电荷的聚集程度。

IGBT芯片终端的PI钝化层能够有效地保护硅芯片[37],但是本文的仿真结果表明,由于芯片和PI钝化层界面的介电参数不匹配,即界面上ε2/γ2−ε1/γ1差值过大,界面上会积累较多电荷,使得局部电场强度过大,可能造成绝缘问题。通过2.3.1节的分析可知,单次关断工况下子模组内的最大电场强度模值大于重复导通关断工况的最大电场强度模值。因此,本节针对弹性压接型子模组的单次关断工况,采用改进钝化层材料方法来调控子模组的最大电场。

经调研发现,一种名为氮氧化硅(SiOxNy)的薄膜材料能够有效提高器件的阻断电压。另外,氮氧化硅能够抵抗湿气,有很好的力学、化学、电学特性和热稳定性,也适宜用作高压器件的顶层钝化层材料[38]。本节选用氮氧化硅材料作为钝化层对单次关断工况下子模组电场进行重新计算,计算条件与2.2节的单次关断工况条件相同。PI材料和氮氧化硅材料的基本参数对比见表2。其中,氮氧化硅的参数来自文献[39-40]。

表2 PI材料和氮氧化硅材料的基本参数

Tab.2 Basic parameters of PI material and silicon nitride material

材 料相对介电常数电导率/(S/m) 氮氧化硅4.001.0×10−9 PI2.964.0×10−14

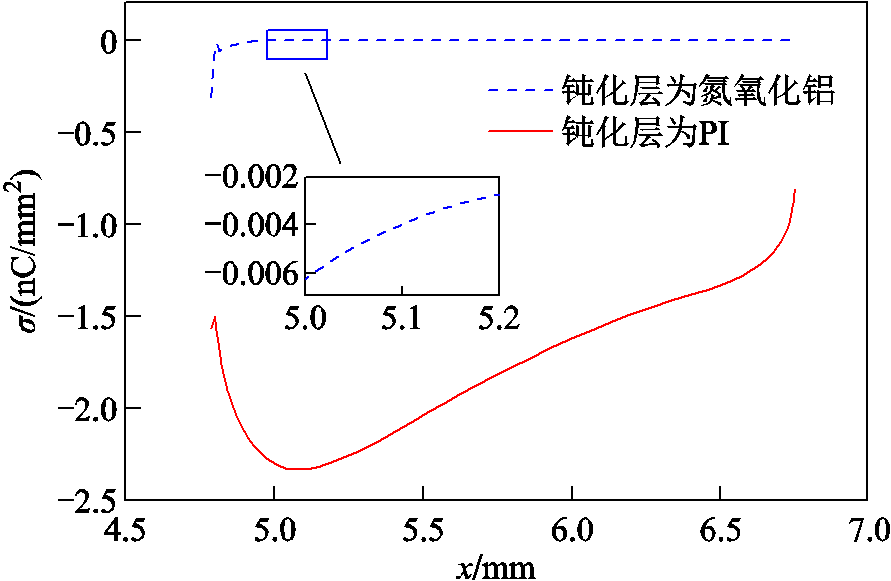

由表1和表2可知,相比于PI材料,氮氧化硅作为钝化层材料时,电导率更大,芯片与钝化层的界面上,ε2/γ2−ε1/γ1差值更小,稳态条件下界面上积累的电荷也会变小。图12给出了钝化层材料改进前后t=2 500 s时芯片与钝化层界面上的电荷密度分布。

图12 改进材料后芯片/钝化层界面(界面1)电荷密度

Fig.12 Charge density at the interface of the chip/passivation layer (interface 1) after material improvement

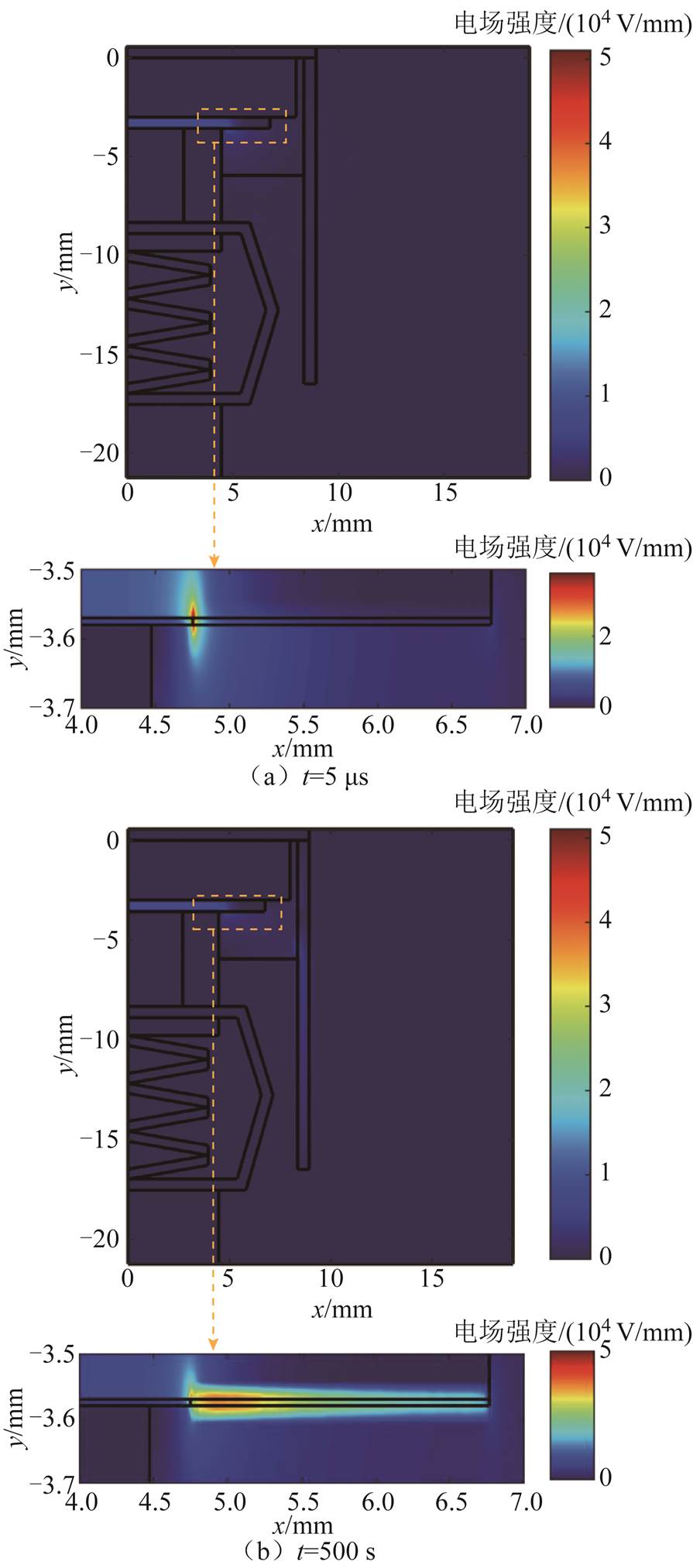

由图12可知,当采用氮氧化硅材料作为钝化层时,界面上的电荷密度下降3个数量级,这一结果与预期相符。当钝化层材料改变后,t=2 500 s时子模组内电场分布云图如图13所示。

图13 改进材料后子模组的电场分布云图

Fig.13 Electric field cloud of subunit after material improvement

由图13和图5c可知,当计算时间t=2 500 s时,子模组的电场分布达到稳定状态,最大电场强度出现在芯片/钝化层/镀铝层的三结合点处上,并没有像采用PI材料作为钝化层时,最大电场强度随着时间发生变化。此外,根据电场计算的结果可知,采用氮氧化硅作为钝化层材料时,最大电场强度模值相比于PI作为钝化层时降低了42.7%。这是由于氮氧化硅的电导率更大,与芯片硅材料参数的匹配程度更好造成的。因此,合理选择钝化层材料,使得绝缘材料和芯片的介电常数更好地配合,有利于降低子模组封装绝缘结构中的最大电场强度,从而降低放电及绝缘击穿的风险。在此,需要指出选用氮氧化硅作为钝化层材料时,其具体的实现工艺还有待进一步研究。

本文从弹性压接型IGBT子模组结构出发,采用时域有限元法,计算了子模组在单次关断工况和重复导通关断工况下,封装绝缘结构的电场分布,主要结论如下:

1)单次关断工况和重复导通关断工况的瞬态过程中,子模组内介质分界面存在电荷聚集,导致电场局部增强。需要说明的是,在重复导通关断工况的导通状态下,虽然外施电压为0,但由于界面电荷的存在,子模组内仍具有一定的电场强度。在两种工况下,子模组内的最大电场强度均出现在芯片/PI钝化层界面上,最大电场强度模值随着时间逐渐增大,出现的位置逐渐向芯片外边沿方向移动。

2)在不同工况下,芯片/PI钝化层界面上相同位置的电荷密度大小顺序为单次关断>重复导通关断工况的关断状态末>导通状态末。因此子模组内最大电场强度数值也呈现类似顺序。这表明单次关断工况下,器件发生绝缘问题的风险更大,需要重点关注处于单次关断工况的弹性压接型IGBT器件。

3)在单次关断工况下,采用改变钝化层材料的电场调控方法,通过提高绝缘材料的匹配程度,大大降低介质分界面上积累的电荷,使得子模组内的最大电场强度降低42.7%,为弹性压接型IGBT器件封装绝缘结构的优化提供一种有效的可借鉴的方法。

参考文献

[1] Zhan Cao, Zhu Lingyu, Liu Chenshuo, et al. Condition monitoring of high voltage press-pack igbt with on-state collector-emitter voltage[C]// Proceedings of the 21st International Symposium on High Voltage Engineering, Budapest, Hungary, 2020: 949-957.

[2] 赵子轩, 陈杰, 邓二平, 等. 负载电流对IGBT器件中键合线的寿命影响和机理分析[J]. 电工技术学报, 2022, 37(1): 244-253. Zhao Zixuan, Chen Jie, Deng Erping, et al. The influence and failure mechanism analysis of the load current on the IGBT lifetime with bond wire failure[J]. Transactions of China Electrotechnical Society, 2022, 37(1): 244-253.

[3] 李辉, 刘人宽, 王晓, 等. 压接型IGBT器件封装退化监测方法综述[J]. 电工技术学报, 2021, 36(12): 2505-2521. Li Hui, Liu Renkuan, Wang Xiao, et al. Review on package degradation monitoring methods of press-pack IGBT modules[J]. Transactions of China Electrotechnical Society, 2021, 36(12): 2505-2521.

[4] 彭程, 李学宝, 张冠柔, 等. 压接型IGBT芯片动态特性实验平台设计与实现[J]. 电工技术学报, 2021, 36(12): 2471-2481. Peng Cheng, Li Xuebao, Zhang Guanrou, et al. Design and implementation of an experimental platform for dynamic characteristics of press-pack IGBT chip[J]. Transactions of China Electrotechnical Society, 2021, 36(12): 2471-2481.

[5] 王琦, 杨张斌, 彭代晓, 等. 柔性直流输电阀控及子模块控制全接入试验系统设计[J]. 电气技术, 2022, 23(2): 40-47. Wang Qi, Yang Zhangbin, Peng Daixiao, et al. Design of full access test system for valve control and sub-module control of flexible direct current transmission[J]. Electrical Engineering, 2022, 23(2): 40-47.

[6] 贺之渊, 陆晶晶, 刘天琪, 等. 柔性直流电网故障电流抑制关键技术与展望[J]. 电力系统自动化, 2021, 45(2): 173-183. He Zhiyuan, Lu Jingjing, Liu Tianqi, et al. Key technologies and prospect of fault current suppression in flexible DC power grid[J]. Automation of Electric Power Systems, 2021, 45(2): 173-183.

[7] Zhang Jianjia, Shao Shuai, Li Yucen, et al. Arm voltage balancing control of modular multilevel resonant converter[J]. CES Transactions on Electrical Machines and Systems, 2020, 4(4): 303-308.

[8] Li Yan, He Zhipeng, Guo Weili, et al. FEM simulation and lifetime prediction of press-pack IGBT: a review[C]//2020 4th International Conference on HVDC, Xi'an, China, 2020: 355-361.

[9] Filsecker F, Alvarez R, Bernet S. Comparison of 4.5-kV press-pack IGBTs and IGCTs for medium-voltage converters[J]. IEEE Transactions on Industrial Electronics, 2013, 60(2): 440-449.

[10] Simpson R, Plumpton A, Varley M, et al. Press-pack IGBTs for HVDC and FACTs[J]. CSEE Journal of Power and Energy Systems, 2017, 3(3): 302-310.

[11] Deng Erping, Ren Bin, Li Anqi, et al. An integrated packaging structure of press pack for high power IGBTs[C]//2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 2019: 243-246.

[12] 张翀, 邱清泉, 张志丰, 等. 直流混合型断路器与直流故障限流器的匹配研究[J]. 电工电能新技术, 2016, 35(9): 21-28. Zhang Chong, Qiu Qingquan, Zhang Zhifeng, et al. Study on coordination of DC hybrid circuit breaker and DC fault current limiter[J]. Advanced Technology of Electrical Engineering and Energy, 2016, 35(9): 21-28.

[13] 吕玮, 方太勋, 杨浩, 等. 基于电弧电压的混合型直流断路器[J]. 电力系统自动化, 2015, 39(11): 83-87, 102. Lü Wei, Fang Taixun, Yang Hao, et al. Hybrid DC breaker based on arc voltage[J]. Automation of Electric Power Systems, 2015, 39(11): 83-87, 102.

[14] 袁清云. HVDC换流阀及其触发与在线监测系统[M]. 北京: 中国电力出版社, 1999: 263.

[15] Fu Pengyu, Zhao Zhibin, Li Xuebao, et al. Partial discharge measurement and analysis in PPIs[J]. IET Power Electronics, 2019, 12(1): 138-146.

[16] 付鹏宇, 赵志斌, 崔翔. 压接型IGBT器件绝缘研究: 问题与方法[J]. 电力电子技术, 2018, 52(8): 38-40, 62. Fu Pengyu, Zhao Zhibin, Cui Xiang. Study of the electrical insulation of press pack IGBT: problems and methodologies[J]. Power Electronics, 2018, 52(8): 38-40, 62.

[17] 何东欣, 张涛, 陈晓光, 等. 脉冲电压下电力电子装备绝缘电荷特性研究综述[J]. 电工技术学报, 2021, 36(22): 4795-4808. He Dongxin, Zhang Tao, Chen Xiaoguang, et al. Research overview on charge characteristics of power electronic equipment insulation under the pulse voltage[J]. Transactions of China Electrotechnical Society, 2021, 36(22): 4795-4808.

[18] 杜伯学, 张莹, 孔晓晓, 等. 环氧树脂绝缘电树枝劣化研究进展[J]. 电工技术学报, 2022, 37(5): 1128-1135, 1157. Du Boxue, Zhang Ying, Kong Xiaoxiao, et al. Research progress on electrical tree in epoxy resin insulation[J]. Transactions of China Electrotechnical Society, 2022, 37(5): 1128-1135, 1157.

[19] Fu Pengyu, Zhao Zhibin, Cui Xiang, et al. Partial discharge measurement and analysis in high voltage IGBT modules under DC voltage[J]. CSEE Journal of Power and Energy Systems, 2018, 4(4): 513-523.

[20] Fabian J H, Hartmann S, Hamidi A. Analysis of insulation failure modes in high power IGBT modules[C]//Fourtieth IAS Annual Meeting. Conference Record of the 2005 Industry Applications Conference, Hong Kong, China, 2005: 799-805.

[21] Fu Pengyu, Zhao Zhibin, Cui Xiang, et al. Electrical field analysis of press-pack IGBTs[C]//2017 Sixth Asia-Pacific Conference on Antennas and Propagation (APCAP), Xi'an, China, 2017: 1-3.

[22] Li Jinyuan, Chen Zhongyuan, Tang Xinling, et al. Study on the issue of electric field concentration in submodule of press pack IGBT[J]. IOP Conference Series: Earth and Environmental Science, 2018, 189: 052072.

[23] 文腾, 崔翔, 李学宝, 等. 压接型IGBT子模组在关断过程中的电场瞬态特性分析与调控[J]. 中国电机工程学报, 2022, 42(6): 2298-2308. Wen Teng, Cui Xiang, Li Xuebao, et al. Transient characteristics analysis and modification of electric field for press-packed IGBT submodule during turn-off process[J]. Proceedings of the CSEE, 2022, 42(6): 2298-2308.

[24] Wen Teng, Cui Xiang, Liu Sijia, et al. Characterization of electric field distribution within high voltage press-packed IGBT submodules under conditions of repetitive turn-on and turn-off[J]. CSEE Journal of Power and Energy Systems, 2022, 8(2): 609-620.

[25] Wen Teng, Cui Xiang, Li Xuebao, et al. Time-domain finite element method for transient electric field and transient charge density on dielectric interface[J]. CSEE Journal of Power and Energy Systems, 2020, 8(1): 143-154.

[26] 刘招成, 崔翔, 李学宝, 等. 弹性压接型IGBT器件封装结构对芯片内部电场的影响研究[J]. 中国电机工程学报, 2023, 43(1): 274-284. Liu Zhaocheng, Cui Xiang, Li Xuebao, et al. Influence analysis of packaging on electric field of chip in elastic press-pack IGBT device[J]. Proceedings of the CSEE, 2023, 43(1): 274-284.

[27] Trost J R, Ridley R S, Khan M K, et al. The effect of charge in junction termination extension passivation dielectrics[C]//11th International Symposium on Power Semiconductor Devices and ICs. ISPSD'99 Proceedings (Cat. No.99CH36312), Toronto, ON, Canada, 1999: 189-192.

[28] 章坚, 叶全明. 双组分加成型硅橡胶电子灌封料的制备[J]. 有机硅材料, 2009, 23(1): 31-35. Zhang Jian, Ye Quanming. Preparation of two-part addition cure potting silicone rubber[J]. Silicone Material, 2009, 23(1): 31-35.

[29] 王泽忠, 全玉生, 卢斌先. 工程电磁场[M]. 2版. 北京: 清华大学出版社, 2011: 329.

[30] Sweet M, Sankara Narayanan E M, Steinhoff S. Influence of cassette design upon breakdown performance of a 4.5kV press-pack IGBT module[C]//8th IET International Conference on Power Electronics, Machines and Drives (PEMD 2016), Glasgow, UK, 2016: 1-6.

[31] 翟宾. PEEK材料介电特性及其影响因素研究[D]. 北京: 华北电力大学(北京), 2020.

[32] 罗宏昌. 静电灾害及其分析[M]. 北京: 人民交通出版社, 1988.

[33] 王泽忠. 简明电磁场数值计算[M]. 北京: 机械工业出版社, 2011.

[34] Cao X, Kurita A, Yamanaka T, et al. Suppression of numerical oscillation caused by the EMTP-TACS interface using filter interposition[J]. IEEE Transactions on Power Delivery, 1996, 11(4): 2049-2055.

[35] 解希顺. 多层介质极化的Maxwell—Wagner效应[J]. 电声技术, 1994, 18(4): 7-9.

[36] Wen Teng, Cui Xiang, Li Xuebao, et al. Transient electric field of the combined insulation structure under positive periodic square waveform voltage: analytical analysis and application[J]. High Voltage, 2022, 7(5): 877-889.

[37] Stockmeier T, Roggwiller P. Novel planar junction termination technique for high voltage power devices[C]//Proceedings of the 2nd International Symposium on Power Semiconductor Devices and Ics, Tokyo, Japan, 1990: 236-239.

[38] 卞铮, 李冰. 高压高可靠性VDMOS功率器件钝化膜工艺研究[J]. 微电子学, 2008, 38(4): 497-501. Bian Zheng, Li Bing. Research on SiON passivation process for high breakdown voltage and high reliability VDMOS device[J]. Microelectronics, 2008, 38(4): 497-501.

[39] 沈莉莉, 夏钟福, 周涛, 等. 化学表面处理对微型化的氮氧化硅驻极体层电荷储存性能的影响[J]. 功能材料与器件学报, 2007, 13(1): 13-17. Shen Lili, Xia Zhongfu, Zhou Tao, et al. Influence of chemical surface treatment on charge storage stability for miniature Si3N4/SiO2 electret film[J]. Journal of Functional Materials and Devices, 2007, 13(1): 13-17.

[40] 杜姣龙. Si2N2O基透波陶瓷材料的制备及性能研究[D]. 郑州: 郑州大学, 2019.

Abstract With the development of flexible DC transmission technology, high-voltage and high-power IGBT (Insulated Gate Bipolar Transistor) has become an indispensable core component in DC power grid. Compliant press-pack IGBT has a wide application prospect in power grid because of its uniform pressure distribution and superior insulation performance. The calculation of the electric field distribution inside the device is an important step to improve its insulation performance. However, the transient electric field distribution under actual working conditions were not analyzed in previous studies. Therefore, the electric field distribution of the device under two working conditions is simulated, and a method to improve the matching degree of parameters between the insulating media is proposed in this paper, which can reduce the maximum electric field intensity in the device.

Firstly, based on the actual working conditions of the device, the 2D finite element model is established, and the governing equations and boundary conditions of the submodule are determined. Secondly, by using the weighted residual method, the weak form of the governing equation is obtained, which is discretized in space and time. Then all nodes in the field are reordered, and the equation is decomposed into two to solve the transient potential and the normal component of the electric field intensity on the boundary respectively. Thirdly, the electric field distribution in the IGBT device is calculated under the conditions of single turn-off and repeatable turn-on and turn-off condition. Finally, a method of improving the matching degree of dielectric constant and electrical conductivity of the insulating material in the submodule is proposed to reduce the maximum electric field.

The results show that the maximum electric field intensity in the submodule always appears at the interface of chip/PI passivation layer. Because the dielectric parameters of the insulating materials on both sides of this interface do not match, charges will accumulate. The interfacial charge affects the electric field distribution, causing the value and position of the maximum field intensity to change with time. In addition, the maximum electric field intensity under the single turn-off condition is larger than that under the repeated turn-off and turn-off conditions. Therefore, specific application conditions should be considered in the insulation design of devices. The silicon nitrous oxide material (SiOxNy) is proposed as the passivation layer to recalculate the electric field of the submodule under single turn-off condition. The results of recalculation show that the maximum electric field appears at the joint point of chip/passivation layer/aluminized layer and does not change with time. The maximum electric field intensity of SiOxNy as the passivation layer is 42.7% lower than that of PI as the passivation layer. This is due to the greater conductivity of SiOxNy, which better matches the silicon parameters of the chip.

The following conclusions can be drawn from the analysis: (1) In the transient process of single turn-off and repeatable turn-on and turn-off condition, there is charge aggregation on the dielectric interface in the sub-module, which leads to local enhancement of the electric field. (2) There is a greater risk of insulation problems in the single-turn off condition, so it is crucial to pay more attention to the compliant press-pack IGBT devices in this condition. (3) By changing the passivation layer material, the matching degree of insulation material can be improved, which can reduce the maximum field intensity in the submodule.

Keywords:Compliant press-pack IGBT, time domain finite element method, electric quasi-static field, single turn-off condition, repeatable turn-on and turn-off condition, electric field control method

DOI: 10.19595/j.cnki.1000-6753.tces.221474

中图分类号:TM211

国家自然科学基金面上项目资助(52077073)。

收稿日期 2022-07-30

改稿日期 2022-09-07

刘思佳 女,1997年生,硕士研究生,研究方向为高压大功率电力电子器件的封装绝缘技术,电磁场数值计算。E-mail:Liusijia@ncepu.edu.cn

李学宝 男,1988年生,副教授,博士生导师,研究方向为高压大功率电力电子器件封装。E-mail:lxb08357x@ncepu.edu.cn(通信作者)

(编辑 李冰)