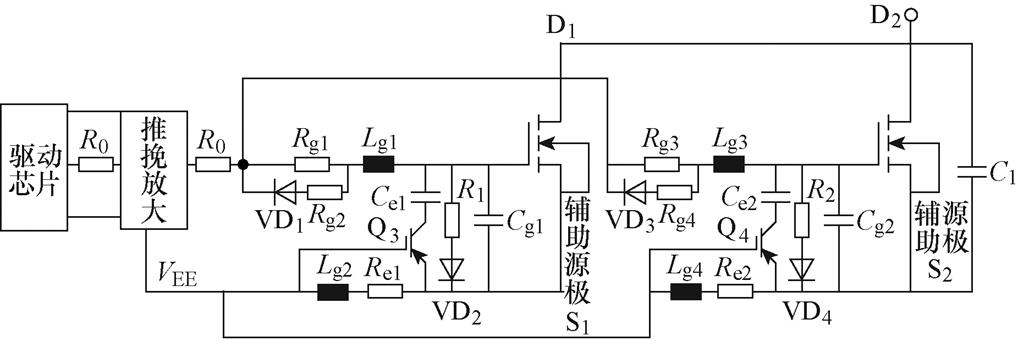

图1 控制器主回路原理

Fig.1 The schematic diagram of the main circuit of the controller

摘要 新能源车用的电机控制器通常通过大功率模块来完成,但大功率模块一般成本比较高,体积比较大,资源也有限。该文基于SiC MOSFET分立器件并联设计了一种高功率密度电机控制器,为了从电气和散热角度最大程度地提升材料和空间利用率,实现高功率密度以及分立器件的良好动静态均流,设计了一种新型的电子系统结构,并提出了一种能动态平衡并联MOSFET电流的高抗扰驱动电路以及可实现低寄生电感、大电流以及高散热的适合分立器件并联应用的新型印制电路板(PCB)叠层母排设计方法。提出的电路及方法既有利于实现并联器件的动静态均流,又可以减小寄生电感造成的影响,还可以有效抑制负向串扰电压。对基于上述研究成果开发出的碳化硅电机控制器,经过双脉冲及功率实验,结果表明,设计的分立器件并联控制器并联均流效果好、散热好、功率密度高,在风冷的条件下,实现了效率最高为99.5%,功率密度为60 kW/L,可应用到新能源整车系统中。

关键词:SiC MOSFET 分立器件并联 高功率密度 印制电路板(PCB)叠层母排

近年来,碳化硅(Silicon Carbide, SiC)作为一种优良的新型器件,已经被大量地应用到电动汽车、航空航天、新能源等领域[1-4]。它的出现不仅显著地改善了整个系统的性能,而且还显著地减少了变换器的制造、装配以及后面出现的维修等问题。随着功率密度的提升,SiC MOSFET的优势日益凸现,可以大大减少电力电子设备的体积,并能够极大地改善电气性能,提升电气系统的运行效率[2-4]。SiC MOSFET相比于传统的功率器件Si IGBT,击穿与阻断电压高、开关速度快、耐温能力强,而且,关断过程没有拖尾电流,能够大大减少开关损耗[4-5],极大地加快其运行,从而为电气控制领域带来了新的发展方向。随着技术的进步,SiC MOSFET已经可以满足电气传动、新能源等高效的电气传输需求,它的通流能力也可以达到几十安培,因此,其已经被认定为未来的最佳电气传输设备。“定制化”的功能模块的销售数量有限,而且封装方式存在差异,销售渠道也相对比较单一。此外,SiC模块的售价过高,这阻碍了开发更加经济实惠的电力驱动系统。与传统的功率模块不同,分离器件的制造技术更加先进,其制造精度更高,而且生产效果更好,这使得它们在单位时间内的制造费用要低得多[6]。另外,采用分离器件的并联技术,不仅可以灵活增加或减少器件的数量,还可以根据需要调整器件的参数,从而提供更加灵活的功率拓扑[7-9]。

但是,并联电路回路中寄生参数比较复杂,分布难免出现不对等的现象。SiC MOSFET的开关速度较高,因而极易在开关过程中电压与电流产生振荡比较严重的现象,而相比于IGBT来说,会给系统带来更严重的电流负载不均衡问题[10-11]。当输出负载不均衡时,将会形成各种损耗、应力和短路问题,不仅会严重干扰系统的正常工作,还可能会增加系统故障的风险,因此缩短了其实际使用期 限[12-13]。为了解决这一问题,学术界开始关注器件本身的情况,并探讨了器件的导流能力、阈值电压以及其他因素等对元件的动、静态电流均衡的影响。另外,器件的封装管脚除了可能会导致漏极、共源极等附加更多的寄生电感外,也会使并联器件的电流的分布状况受到影响[14-15]。文献[16]对器件特性参数是否影响SiC MOSFET的静动态均流进行了相关研究,并指出耦合电容对SiC MOSFET器件的并联静动态均流影响比较小,尤其是在器件间耦合电容差异不大的情况下,影响更小[16]。文献[17]经过研究也指出,寄生电容的分散性对并联电流分配几乎没有影响。在目前的大多数文献中,针对器件并联后可能出现的动静态电流不均衡的问题,通常会考虑优化印制电路板(Printed Circuit Board, PCB)布局的方法,降低并联回路寄生电感[18],进而可以有效减小回路杂感不同带来的开关过程中的电压及电流不均衡的问题。但是,采用已有的方法,如靠布局优化,不能完全解决电流不均衡问题,有时还会加重原来的不均衡现象[19-21]。文献[19]使用了一种耦合电感,以控制并联器件间的不平衡电流。文献[20]基于对源极电感进行补偿,以降低不同并联回路间的寄生参数的差异,改善均流性能。文献[21]通过控制MOSFET管的开通与关断时刻,采用主动补偿的方法来改善并联管的均流性能。但是,以上方法均需要额外增加一些部件,增大了系统复杂度的同时,降低了系统的可靠性,而且不能进行大规模的推广使用。

另外,在中大功率SiC逆变器中,叠层母排设计也被广泛应用,其架构可以将母线电容和功率器件紧密相联,从而实现了逆变器的高性能运行。目前,关于SiC功率模块的叠层母排如何进行结构设计见文献[22-24]。文献[22]提出一种新型的叠层母排的设计方法,采用了双层叠层,大大减小了整个系统母排的杂感。文献[23]对一款全SiC功率器件的母排架构进行了多方面优化,以得到更小的寄生电感值。文献[24]则研究了根据不同结构布置的电感元件对变流器特性的影响,并提出了一种更有利于抑制冲击电流的母排设计的结构布置方法。然而,适用于分立SiC MOSFET器件并联的叠层母排的设计方法,还没有详细的文献研究。基于分立器件并联的叠层母排的设计,除了考虑降低回路的杂感以外,各并联回路之间的阻抗对称也是需要重点考虑的要素。这是因为叠层母排如果结构不对称,必然会带来寄生阻抗的不对称,进而使并联器件之间电流不均衡[19]。不均衡的电流会出现各种损耗、应力以及短路问题,迫使整个系统降额运行。

综上所述,分立式的SiC MOSFET器件并联设计需要克服的主要问题为大功率元件并联均流、低杂感的叠层母排设计、大输出电流的负载及大功率的散热问题等。本文采用SiC MOSFET分立元件设计完成了一种高功率密度电机控制器,并克服了这些主要难题,设计出了一个全新的高集成度电子系统结构,不但可以减少强弱电干扰,还可以做到并联连接功率回路和控制回路的对称布局,便于均流。为了进一步实现并联器件良好的工作,还设计了一种能动态平衡并联MOSFET电流的高抗扰驱动电路,不仅有利于实现并联器件的动静态均流,减小寄生电感造成的影响,还可以有效抑制负向串扰电压。围绕低寄生电感、大电流以及高散热等目标,设计了一种新型的适合分立器件并联应用的PCB叠层母排,并通过仿真以及实验验证了所提设计方法的有效性。基于上述研究成果,开发出基于分立器件并联的碳化硅电机控制器,并联均流效果好、散热好、结构紧凑、功率密度高、成本低,可用于新能源整车系统中。

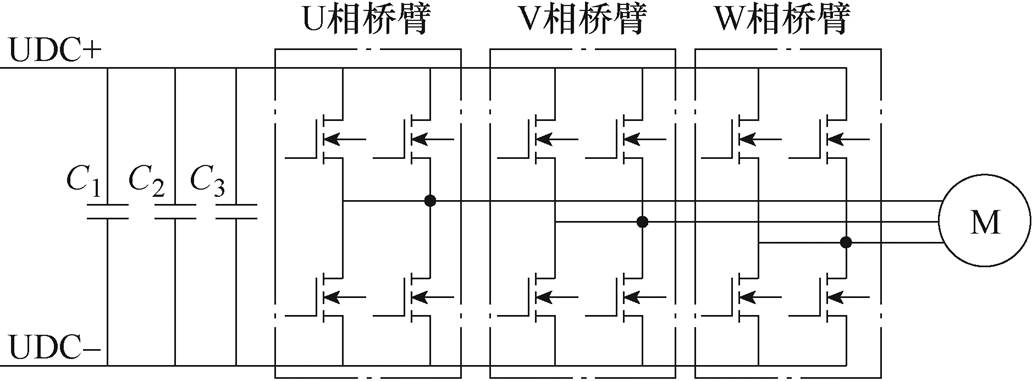

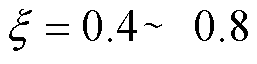

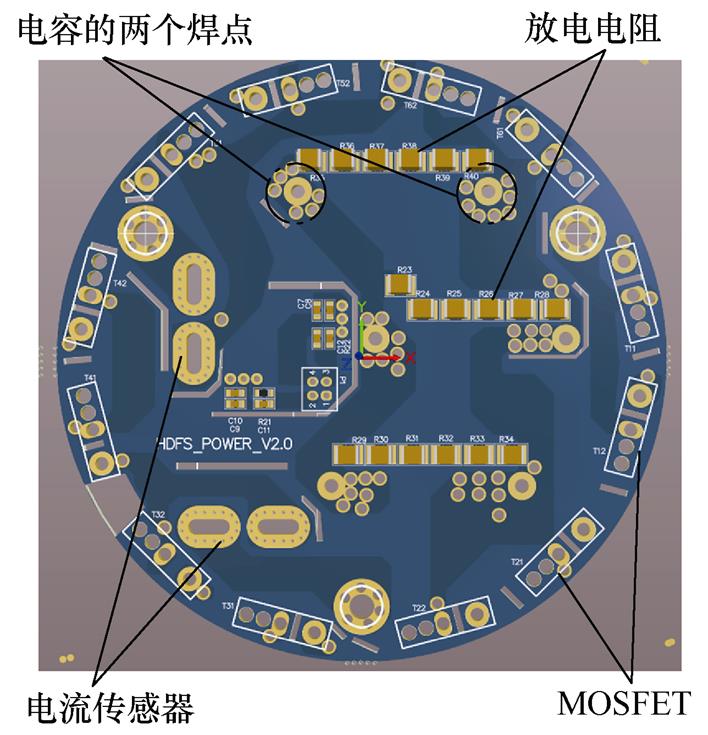

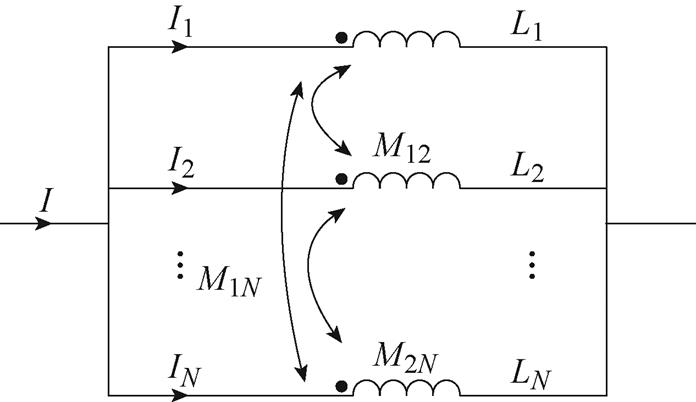

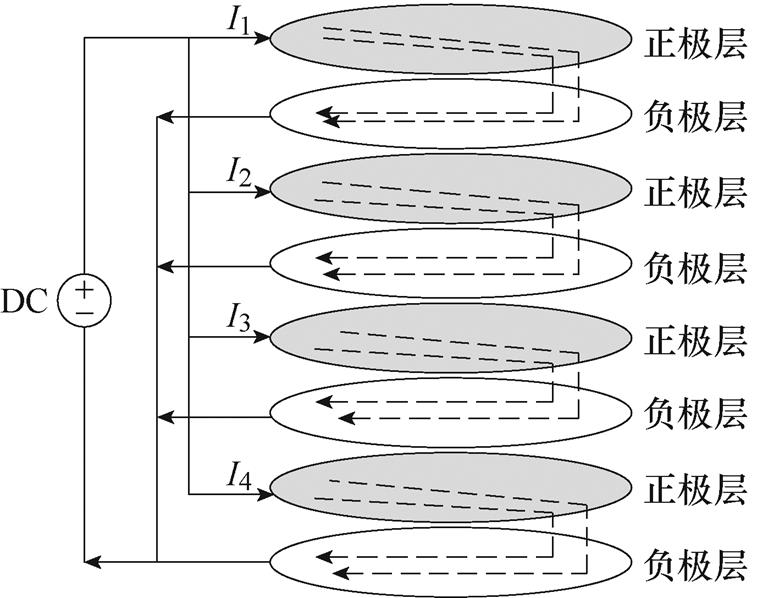

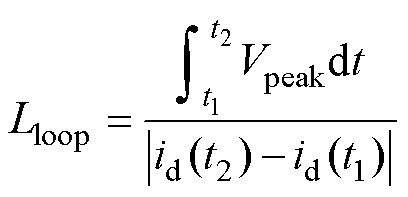

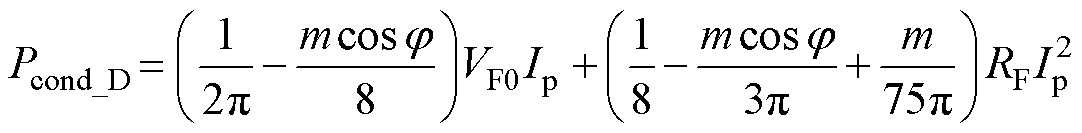

该系统选择了SiC MOSFET双管并联的方法,主回路原理如图1所示。采用的是常用的三相全桥的电路结构拓扑,为了扩大通流能力,6路开关管均采用了SiC MOSFET管并联的形式,并联的管子数量为2,封装为TO247-4。整个系统共采用了12只SiC MOSFET管。母线电压正极UDC+与母线电压负极UDC-所在回路上并联了3个小体积的薄膜电容C1、C2与C3,以利于实现高功率密度。

图1 控制器主回路原理

Fig.1 The schematic diagram of the main circuit of the controller

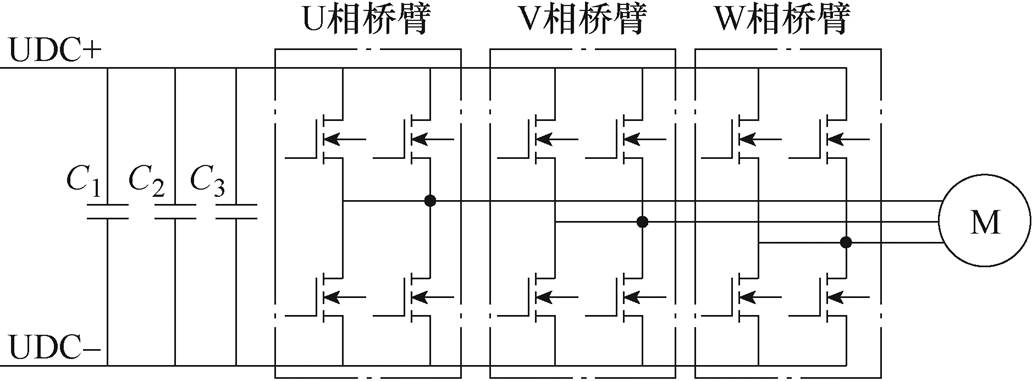

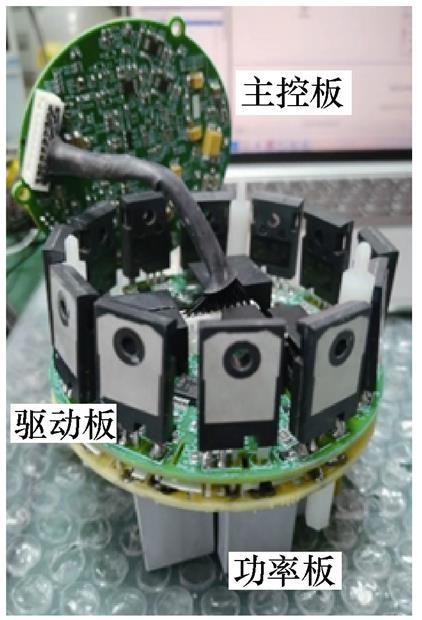

设计的控制器电子系统包括控制模块、驱动模块及功率模块三部分。为了实现最小的电流回路,并减小功率回路与驱动回路之间的相互干扰,主功率板和驱动电路板分别用两个PCB实现,SiC MOSFET的开尔文引脚在电流方面将功率回路与驱动回路分开,门极G与开尔文源极S1管脚焊接在驱动板上,功率源极S2与漏极VD管脚焊接在功率板上,除了有助于防止高压侧瞬变信号对栅极电压的反馈带来的干扰,降低动态损耗,还有利于实现并联SiC MOSFET管功率回路到驱动回路的对称布局。控制电路板、驱动电路板以及功率电路板均为圆形,并且是上下三层的结构,主控板的直径只有72 mm,驱动板、功率板直径均为88 mm,板子形状为圆形,有利于分立器件的对称布局,遵循最简单的物理对称原则,进一步有利于均流。在功率回路设计上,为了减小功率回路的耦合电容与杂散电感,并实现并联器件对称的功率回路,采用了多叠层的圆形PCB结构来实现低感叠层母排。控制器电子系统结构如图2所示,设计的电子系统结构布局,不仅可以减小电机控制器的整体体积,进而增强控制器的集成度以及功率密度,还可以达到节省成本的目的。

图2 控制器电子系统结构

Fig.2 The controller electronic system structure

为了从电气和散热角度最大程度地提升材料和空间利用率,整个系统实现了功率模块、驱动电路、电容与母排的协同设计。直流侧支撑电容采用多只并联形式,焊接在功率板上,通过覆铜层连接到各个并联功率模块的相应管脚上,以减小等效电感和等效电阻;功率板与电机三相交流输出端采用铜柱连接,实现电气和机械结构复用,同时起到支撑电路板的作用;为了节省空间,采用了PCB级电流传感器,且传感器位于功率板上;功率模块均匀布置于圆筒形铝壳内壁加工出的凸台上,通过螺钉与安装面固定并进行散热。最终设计的分立器件的高功率密度控制器的电气结构布局如图3所示。控制电路板、驱动电路板和功率电路板均设置为了圆形,控制板的直径只有72 mm,驱动板与功率板直径相同,均为88 mm,高功率密度的电路板增强了整个电子系统的集成度,最终提升了控制器的效率。

图3 控制器电气结构布局

Fig.3 The electrical structure layout of the controller

1.2.1 模块选型设计

当使用电力电子设备进行功率管模块的选型时,首先要确定其能够承受的最高电流,并且要综合分析其所处的环境条件,如超负荷、电压变化、开关故障、温差变化以及其他可能影响使用寿命的因素,以确定合适的功率管。在进行器件的选型时,必须考虑到各种使用场景,并且要求其能够承受足够的能量消耗。因此,需进行热阻核算,必须确保其最高结温低于预设的标准,这样可选择较小的功率管模块来通过更大的电流,更加有效地利用功率管。

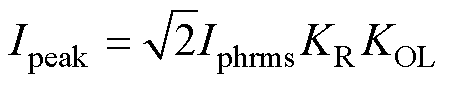

功率开关器件的电流为

(1)

(1)

式中, 为开关器件的峰值电流;

为开关器件的峰值电流; 为电流脉动系数;

为电流脉动系数; 为最大过载系数;

为最大过载系数; 为相电流有效值。

为相电流有效值。

相电流有效值按峰值工况计算, =1.0,

=1.0, = 1.2。由此可以计算得到

= 1.2。由此可以计算得到 =122 A。

=122 A。

分立器件并联的系统控制器的大功率开关管通常是由几个分立的开关管并联而得到的,但按照整个系统的电压等级和一个分立元件的电压级别,可选择由2~6个甚至更多个分立元件并联。基于控制器的功率以及体积,本文采用了两个分立的SiC MOSFET管并联的方案,因单只峰值功率应大于61 A,选用了CREE的1 200 V/115 A的TO247-4封装的SiC MOSFET 模块,整个功率单元的三相桥臂共采用了12只。

1.2.2 直流侧支撑电容设计

直流侧电容在控制器的设计过程中一直承担着很重要的角色,为感性负载供给无功功率,以及保证直流电压平稳的关键作用。同时,直流侧电容器也是车用电源驱动系统中非常重要的无源器件,是影响车辆驱动功率密度、稳定性及效率的关键部件之一。

在新能源汽车使用中,驱动的直流电源大部分由蓄电池组件供给,在此前提下,直流侧电容器组件主要起着与无功功率补偿和解耦的功能,以便保证驱动输入端直流电压稳定,而且不受负载影响。蓄电池组输出的电压理想状态下是近乎于平滑直流,而直流侧电容的电流则是脉动电流,也就是直流侧电容器需要吸收由功率开关管不停开关而产生的脉动电流,因此平稳的输出电压也可以增加蓄电池组件的使用寿命。

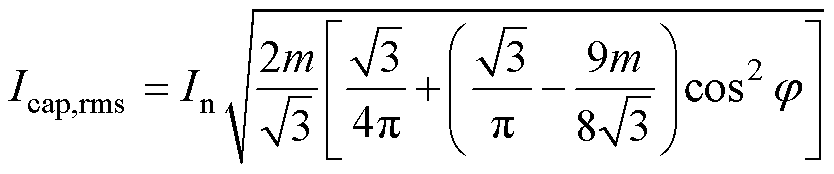

对于电容 的计算公式[25]为

的计算公式[25]为

(2)

(2)

式中, 为调制比;

为调制比; 为相电流幅值;

为相电流幅值; 为开关周期;

为开关周期; 为母线电压的最大纹波;

为母线电压的最大纹波; 为功率因数。

为功率因数。

对于电容纹波电流 的计算公式[25]为

的计算公式[25]为

(3)

(3)

可以得出,电容容量 、调制比

、调制比 、开关周期Ts和相电流幅值In影响直流电压脉动,直流电压脉动值在本设计中按母线电压的2%计算,根据各种工况,不同电压电流下的参数代入式(2)和式(3),最终求得的电容容值应不小于30 mF,电容纹波电流不小于32 A。选用3只Vishey的MKP1848612704K膜电容并联作为母线支撑电容。

、开关周期Ts和相电流幅值In影响直流电压脉动,直流电压脉动值在本设计中按母线电压的2%计算,根据各种工况,不同电压电流下的参数代入式(2)和式(3),最终求得的电容容值应不小于30 mF,电容纹波电流不小于32 A。选用3只Vishey的MKP1848612704K膜电容并联作为母线支撑电容。

1.3.1 驱动电源设计

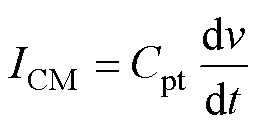

在电源中,使用变压器通过磁场传输电源能量。变压器的输入与输出之间存在寄生电容。在该电容 两端出现的高

两端出现的高 将在高电压功率转换器侧和低电压控制器侧之间产生位移电流

将在高电压功率转换器侧和低电压控制器侧之间产生位移电流 ,即

,即

(4)

(4)

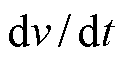

过高的位移电流可能对电磁干扰(Electro Magnetic Interference,EMI)性能产生不利影响。除了控制信号失真之外,由于高共模信号导致的不可预测的行为也有可能给控制器带来严重损害。寄生电容越低,对于特定的 产生的位移电流就越低,有助于系统克服这些问题。同时,也可以实现更高的开关速度、更高的效率、更小的体积和更低的系统成本。因此,变压器上的寄生电容Cpt越低,高压侧和低压侧之间耦合的共模噪声电流的阻抗就越高,如图4所示,图中,Cgd、Cgs与Cds为MOSFET管的极间耦合电容。

产生的位移电流就越低,有助于系统克服这些问题。同时,也可以实现更高的开关速度、更高的效率、更小的体积和更低的系统成本。因此,变压器上的寄生电容Cpt越低,高压侧和低压侧之间耦合的共模噪声电流的阻抗就越高,如图4所示,图中,Cgd、Cgs与Cds为MOSFET管的极间耦合电容。

图4 高低压侧共模电流耦合示意图

Fig.4 The schematic diagram of common mode current coupling on high and low voltage sides

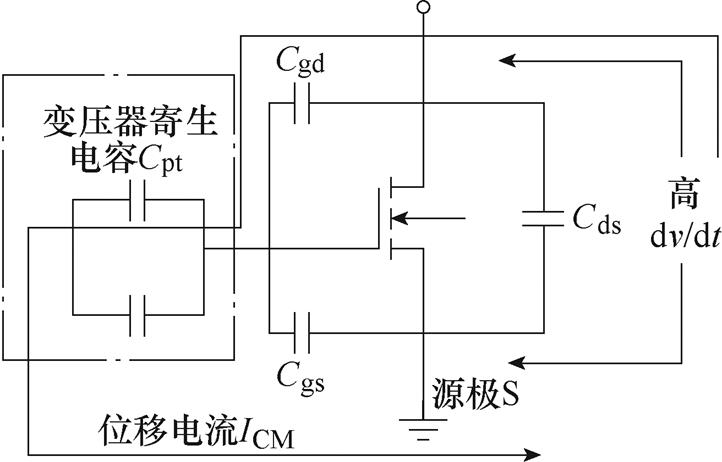

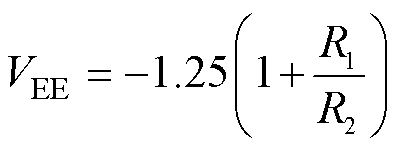

驱动电源采用了一种极其紧凑的反激拓扑结构,最大输出功率可达到4 W,原理框图如图5所示,隔离变压器采用低耦合电容设计,绕组间电容只有7 pF,有助于实现高的共模瞬态抗扰度,从而适应SiC MOSFET的快速开关。此外,变压器二次侧采用了隔离反激式转换器U2,型号为LT8302,可以通过直接在一次侧回扫波形来采样隔离侧的输出电压,无需第三绕组或反馈光隔离器件进行调节,可输出+15 V和-4 V的两个隔离电源,为了满足不同的SiC MOSFET芯片的需求,变压器负压输出后端还安装了电压调节芯片U3,型号为LM337,它可以通过调节电阻R1和R2的阻值来实现不同的负压输出,负电压VEE为

(5)

(5)

图5 驱动电源原理框图

Fig.5 The schematic diagram of driving power

可调节的负压可以适应不同类型的SiC MOSFET模块的需求,也有利于防止桥臂之间的管子在相互开通时给对管带来的直通风险。

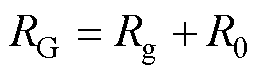

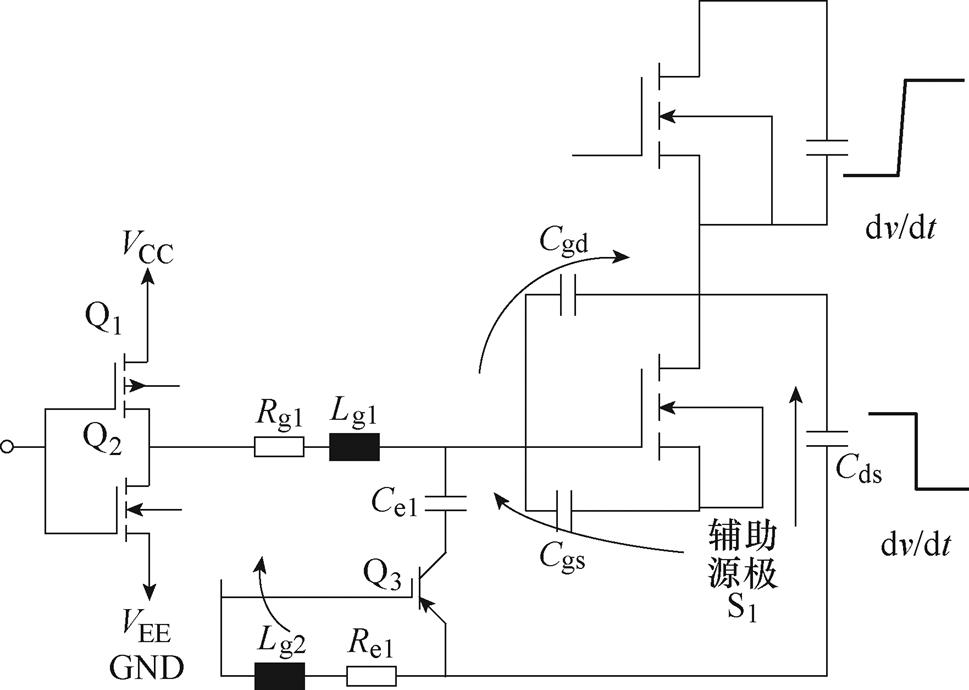

1.3.2 并联驱动电路设计

并联驱动电路原理框图如图6所示。为了实现并联均流,两并联的SiC MOSFET管共用一个驱动芯片和推挽放大电路,除了共用一个门极驱动电阻R0以外,每个SiC MOSFET管还有各自独立的开通电阻Rg1(Rg3)与关断电阻Rg2(Rg4),使每个SiC MOSFET管的门极电压可以独立地开通与关断,保证了在每个SiC MOSFET管的门极阈值电压有差异的情况下也可实现同时开关。

图6 并联驱动电路原理框图

Fig.6 The principle block diagram of parallel drive circuit

兼顾面积、功率、散热等因素,选择了采用磁性元件平衡回路阻抗特性的方法,保证并联等效阻抗相同。因此,在并联SiC MOSFET管的开通电阻与关断电阻的后面分别串联了一个铁氧体磁珠Lg1与Lg3,同时也可以抑制SiC MOSFET栅极回路中快速开关引起的振铃。磁珠特有的高频电阻和低频感抗特性,可以很好地捕捉和消除高频噪声,但其存在的微小电感量对脉冲前沿有一定的影响。阻抗值大的铁氧体磁珠对信号的高次谐波抑制作用好,但对脉冲信号的上升沿延迟却较大。为了实现脉冲上升沿延迟小并且高频抑制作用强,可按电感的暂态特性来计算选择所需磁珠的阻抗值,这里以MLCB2B3216系列磁珠为例,给出磁珠阻抗选取的理论依据,实际取值可根据实验结果微调。

磁珠的阻抗由100 MHz时的阻抗确定,因此阻抗值与电感量关系满足

(6)

(6)

式中, 为磁珠的电感;

为磁珠的电感; 为磁珠阻抗。

为磁珠阻抗。

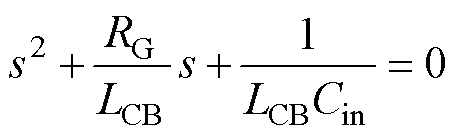

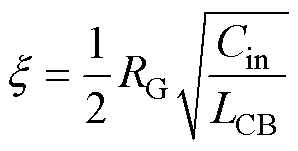

电感 与门极总驱动电阻

与门极总驱动电阻 (

( )及MOSFET门极输入电容

)及MOSFET门极输入电容 组成了RLC串联二阶系统,二阶系统阶跃响应传递函数为

组成了RLC串联二阶系统,二阶系统阶跃响应传递函数为

(7)

(7)

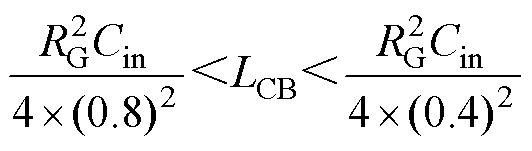

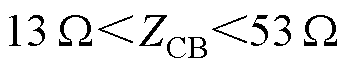

系统阻尼系数为 满足

满足

(8)

(8)

由控制理论可知,二阶系统的阶跃响应时间受阻尼系数影响,欠阻尼系统中,为保证系统动态性能,通常取 。

。

由此可得

(9)

(9)

电路中每个MOSFET管的总驱动电阻 值相同,为3 W,MOSFET输入电容

值相同,为3 W,MOSFET输入电容 ,值为6 nF,由式(6)和式(9)可得

,值为6 nF,由式(6)和式(9)可得

(10)

(10)

因门极回路的寄生振荡通常在50~200 MHz的范围内,因此在门极驱动开关频率为10 kHz且最大驱动电流不超过3 A的情况下,根据式(10)选取MLCB2B3216系列的30 W 左右的铁氧体磁珠,磁珠的频率与阻抗的关系曲线如图7所示。图7中, 为总阻抗,

为总阻抗, 为电阻,

为电阻, 为电感,在噪声频率50~200 MHz的范围内具有高阻抗,在10 kHz开关频率下具有超小阻抗,且由理论分析可知,其表现的电感特性对上升沿影响比较小,因此可以在噪声频率下更大限度地提高电阻分量以消散尽可能多的能量,同时更大限度地降低开关频率下的总体阻抗,以防止不必要的损耗并减少对脉冲上升沿的牺牲。可以说,该系列下30 W 阻抗的磁珠足以抑制SiC MOSFET栅极回路中的振铃并保持开关性能相对不变。当该磁珠与小驱动电阻串联使用时,门极寄生振荡会下降,同时最大限度地减少开关损耗。并联MOSFET管的门极上各串联一个铁氧体磁珠,可以实现在同样的驱动电压下,对每个SiC MOSFET管开通与关断回路上因不同参数产生的高频振荡选择不同阻抗的磁珠单独进行幅值的抑制,有利于并联MOSFET管的动态均流,也可以减小每个MOSFET管由于高频振荡带来的开关损耗。

为电感,在噪声频率50~200 MHz的范围内具有高阻抗,在10 kHz开关频率下具有超小阻抗,且由理论分析可知,其表现的电感特性对上升沿影响比较小,因此可以在噪声频率下更大限度地提高电阻分量以消散尽可能多的能量,同时更大限度地降低开关频率下的总体阻抗,以防止不必要的损耗并减少对脉冲上升沿的牺牲。可以说,该系列下30 W 阻抗的磁珠足以抑制SiC MOSFET栅极回路中的振铃并保持开关性能相对不变。当该磁珠与小驱动电阻串联使用时,门极寄生振荡会下降,同时最大限度地减少开关损耗。并联MOSFET管的门极上各串联一个铁氧体磁珠,可以实现在同样的驱动电压下,对每个SiC MOSFET管开通与关断回路上因不同参数产生的高频振荡选择不同阻抗的磁珠单独进行幅值的抑制,有利于并联MOSFET管的动态均流,也可以减小每个MOSFET管由于高频振荡带来的开关损耗。

图7 铁氧体磁珠频率与阻抗曲线

Fig.7 The curves of ferrite bead frequency vs. impedance

此外,在每个SiC MOSFET管的开尔文源极上均增加了一个源极电阻Re与一个铁氧体磁珠,该源极电阻Re的阻值取为1 W,有利于消除相互并联的SiC MOSFET管上源极杂感的不同而形成的环流,并可以形成良性负反馈,降低开关较快的SiC MOSFET管的开关速度,提高开关较慢的SiC MOSFET管的开关速度,使电路运行取得平衡。这里利用铁氧体磁珠的高频特性,与源极电阻串联,可消除存在于环路中的高频干扰和尖峰干扰,有利于减小并联MOSFET管源极杂感不同导致的电压差,进一步减小环流,同步门极信号。另外,在每个SiC MOSFET管的门极上增加了一个三极管 和电容Cex的串联电路,配合开尔文源极电阻Re可减小对每个SiC MOSFET管关断时产生的负向串扰电压。串扰抑制原理如图8所示,当桥臂上管的SiC MOSFET管关断时,上管的

和电容Cex的串联电路,配合开尔文源极电阻Re可减小对每个SiC MOSFET管关断时产生的负向串扰电压。串扰抑制原理如图8所示,当桥臂上管的SiC MOSFET管关断时,上管的 急剧上升,下管的

急剧上升,下管的 急剧下降,这导致Cgd开始放电,放电电流沿着图8中实线箭头方向,耦合电流会从开尔文源极S1流向开尔文源极电阻Re1,这样能够使三极管Q3开启,将串联的电容Ce1连接到门极GS上,为耦合电流提供一个低阻抗通路,有效地抑制了负向串扰,避免了SiC MOSFET管的门极由于负向串扰而承担过高的负向电压,导致的门极绝缘层损坏。

急剧下降,这导致Cgd开始放电,放电电流沿着图8中实线箭头方向,耦合电流会从开尔文源极S1流向开尔文源极电阻Re1,这样能够使三极管Q3开启,将串联的电容Ce1连接到门极GS上,为耦合电流提供一个低阻抗通路,有效地抑制了负向串扰,避免了SiC MOSFET管的门极由于负向串扰而承担过高的负向电压,导致的门极绝缘层损坏。

图8 串扰抑制原理

Fig.8 The crosstalk suppression principle

每个SiC MOSFET管的门极GS上均加了一个电阻与二极管的串联电路,分别为图6中的R1与VD2、R2与VD4的组合,该电路是为了增加驱动门极的抗干扰能力。

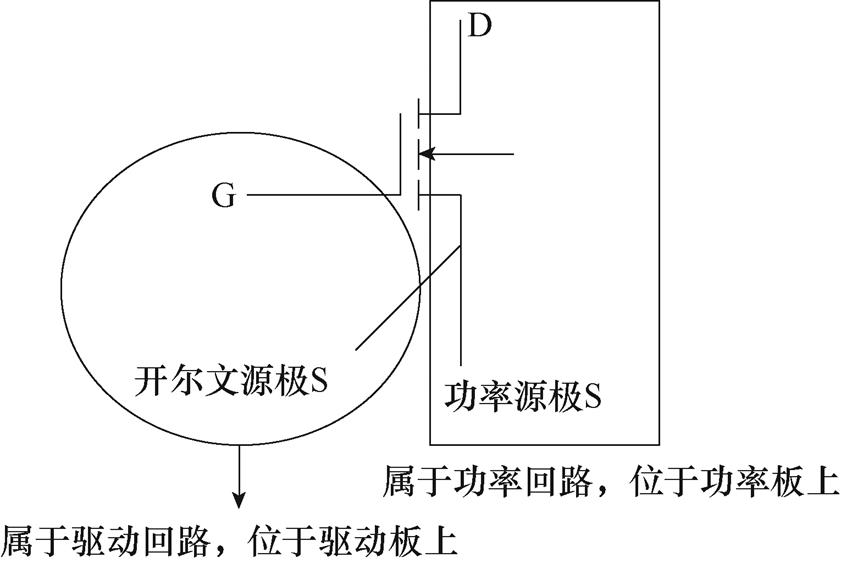

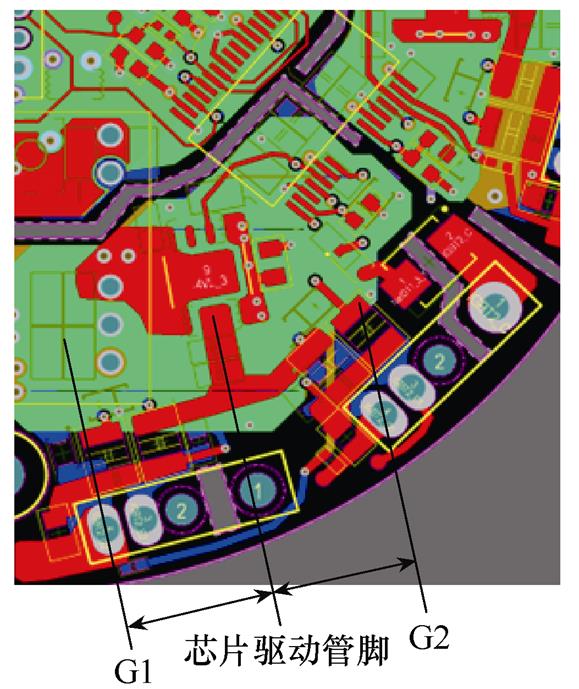

1.3.3 并联驱动电路PCB设计

为了减小门极驱动环与功率环之间的耦合与影响,将门极回路与功率回路分别放在了不同的PCB上。PCB设计结构原理如图9所示,SiC MOSFET的门极G与开尔文源极S焊接在驱动板上,漏极D与功率源极S通过驱动板上的无电气连接的通孔单独焊接到下层的功率板上。

图9 PCB设计结构原理

Fig.9 The principles of PCB design structure

除了在电路上采取均流的措施外,驱动回路布局上也采用了物理上减小并联杂感的方法,最终的驱动板PCB布局如图10所示,12个MOSFET管均匀地分布于圆形的驱动板上,两个并联的MOSFET管在布局时均满足从每个管的栅极到驱动器(驱动芯片加推挽芯片)的输出以及从栅极返回到驱动器的路径严格做到对称,并且驱动器应放置位于两个并联MOSFET管的栅极引脚中心,如图11所示,而不是放在两个并联MOSFET的物理位置的中间。此外,门驱动器距离两个并联MOSFET管的距离越近越好,以减小门极驱动回路上的电感。

图10 驱动板PCB布局

Fig.10 Layout diagram of drive board PCB

图11 并联驱动PCB设计要点

Fig.11 The key points of parallel drive PCB design

1.4.1 母排结构设计

为了实现控制器的高功率密度,PCB母排上实现了并联MOSFET管、电流传感器、放电电阻、直流电容以及交直流端子的一体化设计。不同PCB母排形状、器件连接方式以及电容布局的差异性,均会产生不同的叠层母排结构。图12为设计的新型PCB母排结构示意图,真正实现了小型化、高功率密度与布局对称。

图12 PCB母排结构

Fig.12 The PCB busbar structure diagram

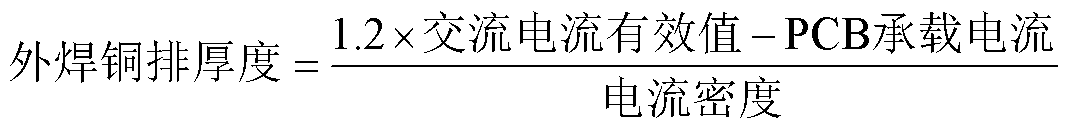

该设计从减小母排总自感、增大母排总互感,具有最大功率密度及物理均流特性的角度出发,实现了一种新型的PCB叠层母排结构。PCB母排形状为直径8 cm的圆形,极小的尺寸有利于减小母排的自感,圆形的布局可以更好地保证元器件的对称性,有利于均流。PCB母排由垂直多回路的多组PCB叠层组成,单组叠层由母线正与母线负组成,该结构有利于增大互感,减小杂感。母排的顶层和底层均具有直流和交流走线的金属开窗,如图13所示。可以焊接不同厚度的不规则形状的金属片或金属条,既起到扩流、满足承载最大电流的同时,又可以达到良好的散热效果。外焊铜片的厚度需要根据母排承载的电流进行计算,为了留有裕度,母排最终承载电流按实际需要电流的1.2倍进行计算,外焊铜排的厚度(mm)计算公式如式(11)所示。其中铜厚1盎司,宽度1 mm可以走1 A的电流,也就是电流密度为7 A/mm2。

(11)

(11)

图13 PCB母排实物

Fig.13 The physical diagram of PCB busbar

功率回路上的12个功率开关器件,均匀排布在圆形母排的周边上,构成了三相全桥结构。将PCB母排形状做成圆形,不仅可以更好地保证元器件的对称性,保障均流效果,在承载尽可能大电流的前提下,功率密度也可以做到最高,同时这种紧凑型的设计也节约了原材料成本。此外,为了节约控制器的空间,采用了两路PCB级电流传感器,传感器的输入与电机交流点相连,输出与上下并联管的中点相连。3个交流连接点处可以外焊铜柱直接与电机相连,实现可靠连接。直流电容位于PCB母排的中间位置,与每组单相桥的功率开关器件并联。

为了确保电路的稳定运行,在每个直流电容的正负极之间都安装了放电电阻,这样即使在电源变化的情况下,电容也能够保持充放电状态。

1.4.2 母排低杂感设计

在新能源驱动器中,因为功率回路上寄生电感的影响,导致功率元件在关断后形成超过耐压范围的暂态尖峰,从而致使功率元件击穿损坏[26]。通过对功率回路中寄生电感的构成分析,SiC MOSFET功率模块内寄生电感和直流支撑电容等效寄生电感在出厂时就固定不变,唯一可进行设计控制的就是直流母排的电感。

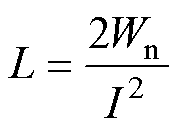

一个最基本的叠层母排结构由导体层(正极层、负极层)和中间的绝缘层组成,电流从正极层流入,从负极层流出。对于单个电流回路,能量存储在空间中的磁场中,环路电感可以根据存储的磁能来确定,其计算公式为

(12)

(12)

式中, 为回路电感;

为回路电感; 为存储在空间中的磁能;

为存储在空间中的磁能; 为回路电流。

为回路电流。

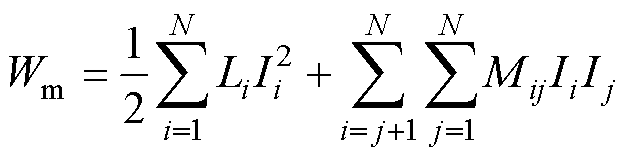

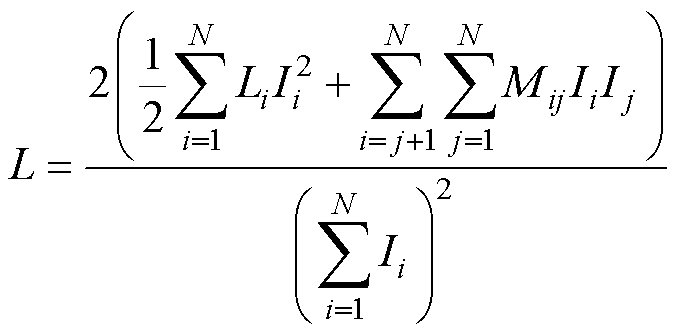

对于由多个并联电流回路组成的系统,每个回路中都有自感磁能,电流回路之间也有互感磁能。总磁能 为

为

(13)

(13)

式中, 为第

为第 个回路的电流;

个回路的电流; 为第

为第 个回路的电流;

个回路的电流; 为第

为第 个回路的自感;

个回路的自感; 为第

为第 和第

和第 个回路之间的互感;

个回路之间的互感; 为电流回路的数量。如果电流回路并联连接,等效电路如图14所示。

为电流回路的数量。如果电流回路并联连接,等效电路如图14所示。

图14 并联电流等效电路

Fig.14 The parallel current equivalent circuit

总回路电感可表示为

(14)

(14)

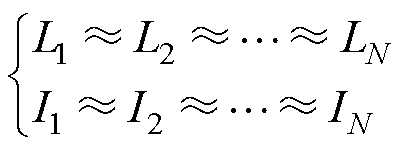

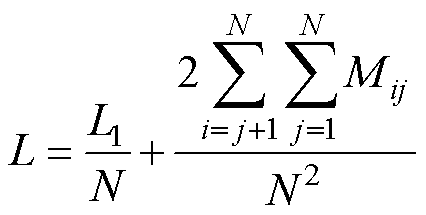

根据式(14)可以看出,减小回路互感可以减小回路总磁能,进而减小总回路电感。

如果并联电流回路阻抗相同,各个回路的自感也相同,那么每个回路电流大致相等,即

(15)

(15)

根据式(15)可以将式(14)化简为

(16)

(16)

当相邻回路的电流方向相反时,互感为负值,有

(17)

(17)

式中,L1为单个电流回路上的电感。

因此,并联电流回路上的电感可以通过减小互感来减小总回路上的电感,当并联回路相邻回路电流方向相反时,电感会随着回路数的增多而降低。

在器件的换流过程中,因为回路中信号的频率比较高,所以输出电流也可作为高频电流。文献[27]指出,叠层母排结构包括导体层(正极层、负极层)以及内部的绝缘间隙层。双层叠层母排自感分别为 和

和 ,互感为

,互感为 ,则有

,则有

(18)

(18)

式中, 为磁导率;

为磁导率; 为母排的长度;

为母排的长度; 为母排的宽度;

为母排的宽度; 为导体层厚度。

为导体层厚度。

由式(18)可知,叠层母排的总杂散电感不仅取决于导体层的自身特性,也受到导体层与其他层之间的互感影响。减小母排的长度以及正负极之间的距离,可以增大互感,减小总阻抗。通过分析可发现,当PCB相邻层之间的电流方向是相反的,而且它们之间的距离也比较近,能够显著减少由于层之间的电磁感应而造成的电感值。

基于以上原理,利用垂直方向上方向相反的电流在最小的环路面积上有最小的寄生电感的原理,设计的PCB母排直径只有8 cm,在板子厚度只有2 mm的情况下,单层铜厚可做到4盎司、层数为8的最大通流能力设计。低感叠层母排结构示意图如图15所示,板子共有4组PCB叠层,每组PCB叠层均由正母线层与负母线层组成,每组PCB叠层形成一个回路,且正母线层和负母线层中流过的电流大小相等、方向相反。四回路的PCB叠层,又可以进一步降低母排回路的杂散电感,避免功率开关器件在高速开关的过程中承受较大的电压过冲,从而降低功率损耗,提升系统效率。

图15 低感叠层母排结构示意图

Fig.15 The schematic diagram of low inductance stacked busbar structure

1.4.3 低感叠层母排电感测试

采用双脉冲的测试方法,对母排的杂散电感进行了测试。母排回路电感 也可通过关断电流的斜率

也可通过关断电流的斜率 和关断电压的电压尖峰

和关断电压的电压尖峰 求得[3],有

求得[3],有

(19)

(19)

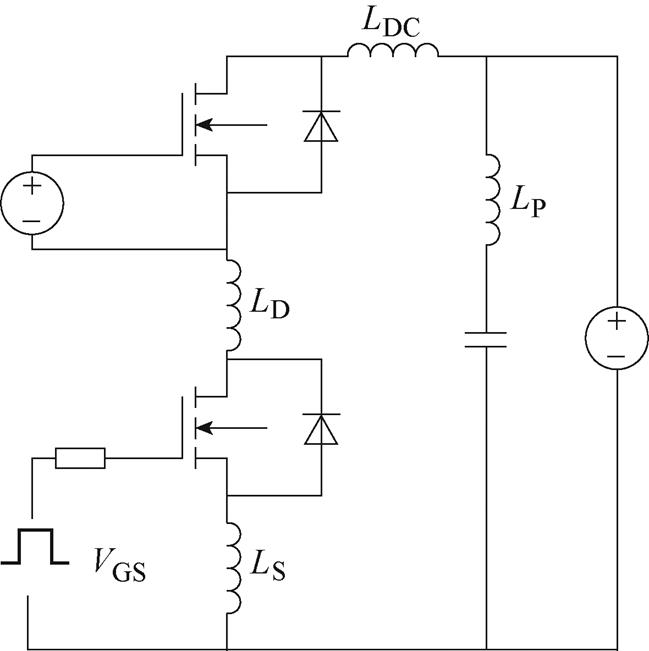

双脉冲功率回路电感组成如图16所示,主要包括母线电容上寄生电感LP、直流母排电感LDC、MOSFET上源极电感 和漏极电感

和漏极电感 四部分[3]。

四部分[3]。

图16 双脉冲功率回路电感

Fig.16 The inductance diagram of dual pulse circuit

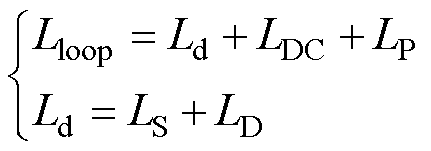

母排回路电感 满足

满足

(20)

(20)

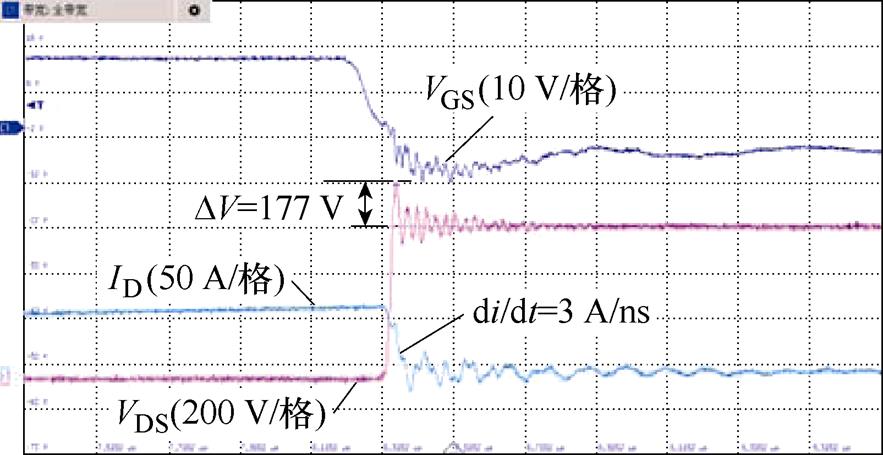

为了测量尽量准确,使用差分电压探头测量SiC MOSFET的开通电压VDS以及门极电压VGS,使用罗氏线圈测量漏极电流 。图17为600 V/120 A工况下双脉冲实验波形,图中DV为关断电压尖峰

。图17为600 V/120 A工况下双脉冲实验波形,图中DV为关断电压尖峰 的值,利用该过程计算母排电感。

的值,利用该过程计算母排电感。

图17 回路双脉冲测试波形

Fig.17 The loop double pulse test waveforms

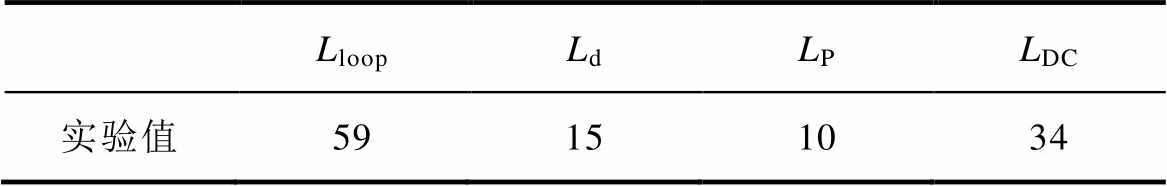

经过研究发现,由于电压、电流的测量误差以及电流变化率选取时段的误差,可能会导致电感测量值与实际值存在一定的偏差。表1统计了600 V/ 120 A工况下功率回路中各部分杂散电感的提取结果。在计算叠层母排电感时,功率回路电感采用双脉冲实验的测量值,从双脉冲波形可以看到关断电压过冲为177 V,电流变化斜率为3 A/ns,因此回路电感大概为59 nH。SiC MOSFET上寄生电感 采用阻抗分析仪的测量值,母线电容寄生电感

采用阻抗分析仪的测量值,母线电容寄生电感 采用数据手册值。最终得到的PCB母排上的杂散电感值为34 nH。由于母排上存在电流传感器、三相交流引出柱等,考虑绝缘,正负母排并未完全重合,母排杂感值并非理想中那么小。

采用数据手册值。最终得到的PCB母排上的杂散电感值为34 nH。由于母排上存在电流传感器、三相交流引出柱等,考虑绝缘,正负母排并未完全重合,母排杂感值并非理想中那么小。

表1 回路各部分电感

Tab.1 Inductance of each part of the circuit(单位: nH)

LloopLdLPLDC 实验值59151034

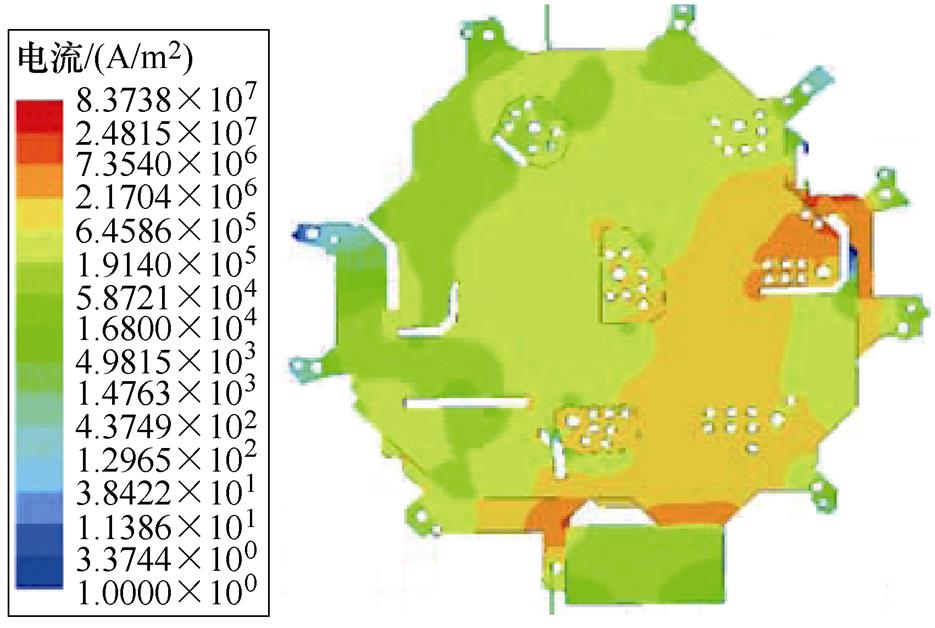

为了验证实验测量PCB母排杂散电感的正确性,通过Ansys Q3D对叠层母排进行了仿真。PCB母排在Q3D中的仿真电流分布如图18所示。仿真中,使用10 MHz的交流电源进行分析,最终获得的主回路总寄生电感值为30 nH。通过表2里的数据对比,可以发现两种不同的提取方式产生的母排的电感值存在一定的偏差,但在误差范围内。

图18 Q3D 母排仿真电流分布

Fig.18 Q3D busbar simulation current distribution

表2 仿真与实验杂感对比

Tab.2 Comparison of inductance simulation and experiment(单位: nH)

获取方式LDC 实验值34 Q3D仿真值30

1.5.1 损耗计算

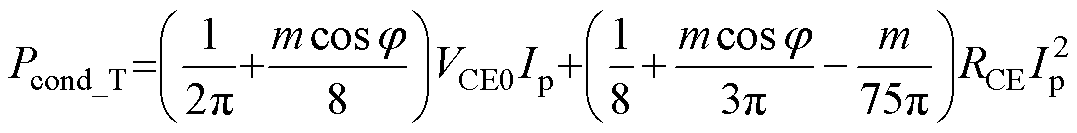

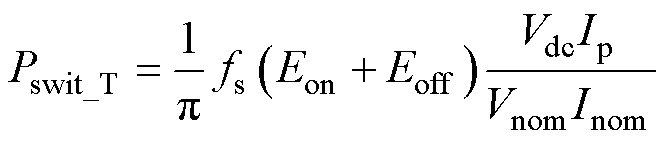

SiC MOSFET功率器件在工作过程中产生的功率损耗占功率回路总损耗的主要部分,因此,为了有效地降低损耗,必须采用有效的散热技术,并且通过精确的数值计算,来确定最佳的散热方案,才能有助于降低损耗,确保控制系统的正常运转。SiC功率器件在电机控制器功率回路中的损耗主要分为开关损耗与静态损耗,其中开关损耗分为开通损耗与关断损耗,静态损耗分为导通损耗与截止损耗。

控制器采用TO247封装的SiC MOSFET分立器件作为功率器件。MOSFET正向导通时,其并联的二极管处于关断状态,与IGBT模块相同。特别地,当二极管导通时,MOSFET也会反向导通,但由于它的导通电阻远小于二极管的导通电阻,故二者并联的总电流基本流入MOSFET,流经二极管的电流很小。计算时增加了MOSFET反向导通损耗。MOSFET管正、反向导通损耗公式分别为

(21)

(21)

(22)

(22)

式中, 为MOSFET正向导通损耗;

为MOSFET正向导通损耗; 为MOSFET正向导通电压电流曲线的截距;

为MOSFET正向导通电压电流曲线的截距; 为功率模块输出电流幅值;

为功率模块输出电流幅值; 为MOSFET正向导通电阻;

为MOSFET正向导通电阻; 为MOSFET反向导通损耗;

为MOSFET反向导通损耗; 为MOSFET反向导通电压电流曲线的截距;

为MOSFET反向导通电压电流曲线的截距; 为MOSFET反向导通电阻。

为MOSFET反向导通电阻。

MOSFET及其并联二极管的开关损耗分别为

(23)

(23)

(24)

(24)

式中, 为开关频率;

为开关频率; 为MOSFET在额定电流、额定电压下的开通损耗;

为MOSFET在额定电流、额定电压下的开通损耗; 为MOSFET在额定电流、额定电压下的关断损耗;

为MOSFET在额定电流、额定电压下的关断损耗; 为二极管关断损耗;

为二极管关断损耗; 为模块直流母线输入电压;

为模块直流母线输入电压; 、

、 分别为测量开关损耗时的电压和电流。

分别为测量开关损耗时的电压和电流。

1.5.2 散热结构设计

由文献[28]可知,环境温度不同对于静态电流和动态电流间的均衡也有影响,而环境温度不同又会影响器件的寄生参数,造成并联器件电流分布不均,进而可能影响到器件的安全运行范围,或者导致器件的电流损伤。为此,在控制器结构设计时对并联SiC MOSFET管进行了均温设计,以降低并联元件的温度差异对均流的影响。

由于电机控制器采用风冷方式散热,设计时将主要发热器件SiC MOSFET均匀安装在了圆形壳壁的柱段壳体上,通过热传导方式直接将热量传递到外壁面。驱动电路与控制电路发热较小,且均采用了高温125℃器件,通过壳体内部空气的自然对流散热,不需要额外散热,对模块散热没有影响。控制系统一共采用了12只TO247-4封装的SiC MOSFET模块,而单只模块的安装表面宽度约为16 mm,预留一定安装间隙,每个器件需要安装并散热的平面边长最大值约为23 mm,则需要的散热器的圆周长不少于276 mm。为了12只模块散热均匀,在壳体内部取f90 mm的内接正十二边形平台作为12只模块的安装台,考虑到固定器件的螺纹深度不小于6 mm,因此起到安装和散热作用的圆柱壳体外径选为f100 mm。另外,根据设计要求,散热圆柱壳体不能有外部肋片或凸起,因此对应模块安装面的壳体外壁加工3条深1 mm、宽5 mm的凹槽以加强扰动,同时增大对流换热面积,如图19所示。

图19 控制器散热结构设计

Fig.19 The design of controller heat dissipation structure

因SiC MOSFET模块与壳体进行安装的面为带电漏极,因此在模块与壳壁进行安装时需考虑绝缘处理,既起到散热作用又不影响电气性能,这里通过在模块和壳体之间增加绝缘陶瓷片的方式来实现电气隔离,且陶瓷片的尺寸需大于模块安装面的尺寸。12只SiC MOSFET的共地部分位于功率板上,3个桥臂的3个下管的功率管的功率源极S管脚焊在功率板上且均与母线负极进行连接,3个上管的漏极管脚D也均焊接在功率板上,且均与母线正极进行连接。

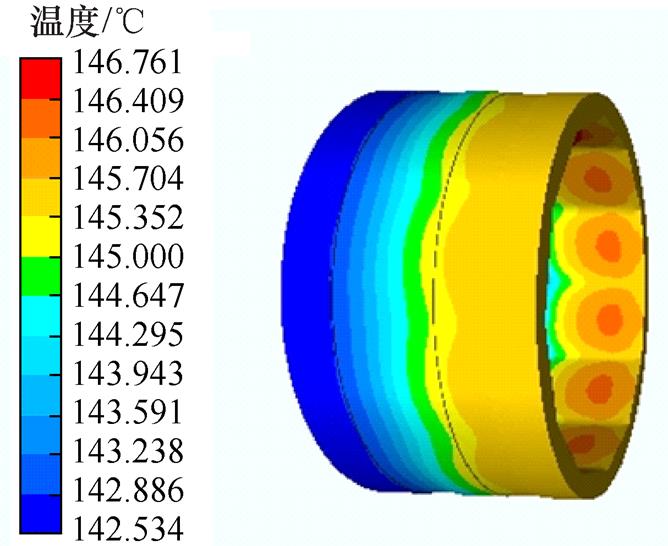

热流仿真使用ICEPAK和CFDesign软件,仿真设置如下:

(1)热源。假设损耗均匀分布于模块上,根据损耗计算结果赋值。

(2)边界条件。控制器采取风冷散热方式,近壳壁处风速为25 m/s。通过ICEPAK仿真先提取出壁面处的平均对流换热系数为158 W/m2,再将其作为第Ⅲ类边界条件赋值,空气温度不高于40℃。

峰值工况下的控制器温度场如图20所示。从图20的仿真结果可知,壳体内壁稳态最高温度为147℃。考虑到器件结壳热阻和陶瓷绝缘垫片热阻,根据式(25)推算MOSFET的结温不大于175℃,满足器件安全运行要求。

图20 峰值工况下的控制器温度场

Fig.20 Controller temperature field under peak operating conditions

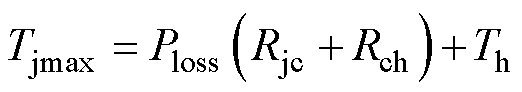

(25)

(25)

式中, 为芯片最高结温;

为芯片最高结温; 为模块损耗;

为模块损耗; 为模块结壳热阻;

为模块结壳热阻; 为陶瓷绝缘片热阻;

为陶瓷绝缘片热阻; 为控制器壳壁最高温度。

为控制器壳壁最高温度。

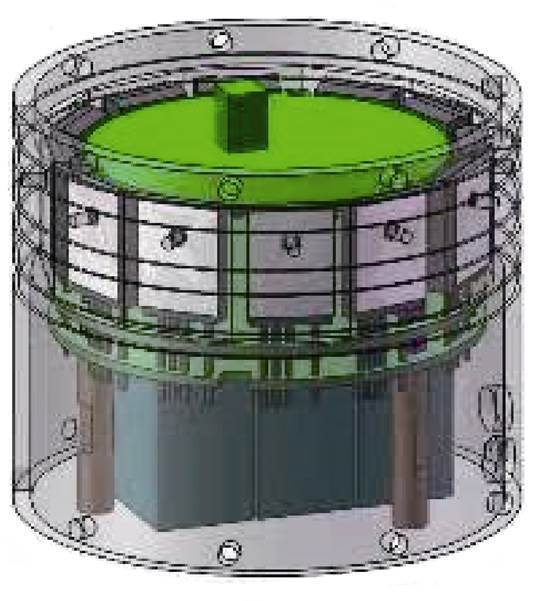

采用第1节所述的SiC MOSFET分立器件并联控制器关键部件设计方法,设计并加工了分立器件并联高功率密度SiC控制器样机,设计输入电压为600 V,输出峰值功率为40 kW,控制器体积为0.66 L,最终功率密度达到60 kW/L。控制器外观如图21所示,体积与常用的平口喝水杯差不多,功率密度比较高。控制器由圆形控制电路板、驱动电路板以及功率电路板组成的上下三层的电子系统结构,如图22所示。主控板的直径只有72 mm,驱动板、功率板直径均为88 mm,板子形状为圆形,有利于分立器件的对称布局,进一步有利于均流。小体积的电路设计节省了系统空间的同时,也有利于降低驱动回路寄生电感。

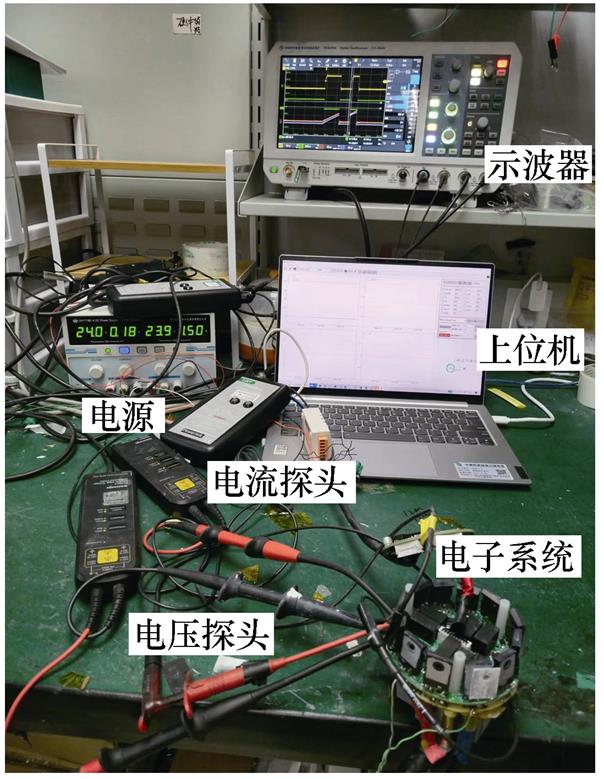

为了验证系统的均流特性以及在母线电压600 V下的开关性能,对电子系统进行了双脉冲测试。测试条件为母线电压600 V,最大负载电流120 A,驱动电阻2 W,负载电感45 mH。双脉冲实验平台如图23所示。电压探头采用了两个差分探头,型号为TT-SI 8071,带宽为200 MHz,测量并联MOSFET管的其中一个的VGS电压与VDS电压。电流探头采用两个罗氏线圈,带宽为100 MHz,分别测量并联MOSFET管的两个漏极电流。尽管与同轴分流器相比,100 MHz带宽的电流探头由于时间延迟,对于损耗计算可能不精确,但该探头可以揭示电流波形的细节。双脉冲测试整体波形如图24所示,图中浅蓝色线为驱动VGS电压信号,红色线为MOSFET被测管VDS电压,深蓝色与黑色线分别为罗氏线圈测量两个并联管的ID电流。由测试波形可知,该并联系统在600 V/120 A的工况下可以可靠地开通与关断,满足高功率密度控制器的最大工况要求,并且从并联MOSFET管的电流波形可以看出系统的动静态均流效果良好。

图21 分立器件并联控制器样机

Fig.21 The discrete device parallel controller prototype

图22 电子系统实物

Fig.22 The physical diagram of electronic system

图23 双脉冲实验平台

Fig.23 The double pulse experimental platform

图24 并联器件600 V/120 A下均流测试波形

Fig.24 The current sharing test waveforms for parallel devices at 600 V/120 A

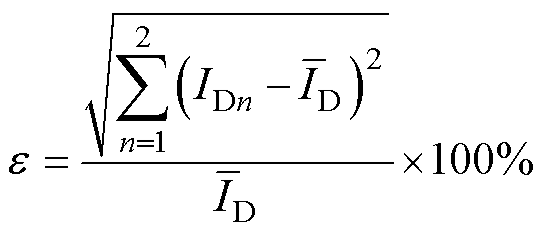

电流不平衡度的计算公式为

(26)

(26)

式中, 为第n个并联管的电流;

为第n个并联管的电流; 为所有并联MOSFET管漏极电流的平均值。

为所有并联MOSFET管漏极电流的平均值。

表3列出了两个并联管在静态、开通与关断不同时刻的电流瞬时值 与

与 ,根据电流不平衡度的计算公式,可以求出系统电流的不平衡度小于3%。

,根据电流不平衡度的计算公式,可以求出系统电流的不平衡度小于3%。

表3 并联管不同时刻的电流瞬时值

Tab.3 Instantaneous current values of parallel tubes at different times(单位: A)

过程ID1ID2 静态57.455.9 开通61.562.9 关断47.846.3

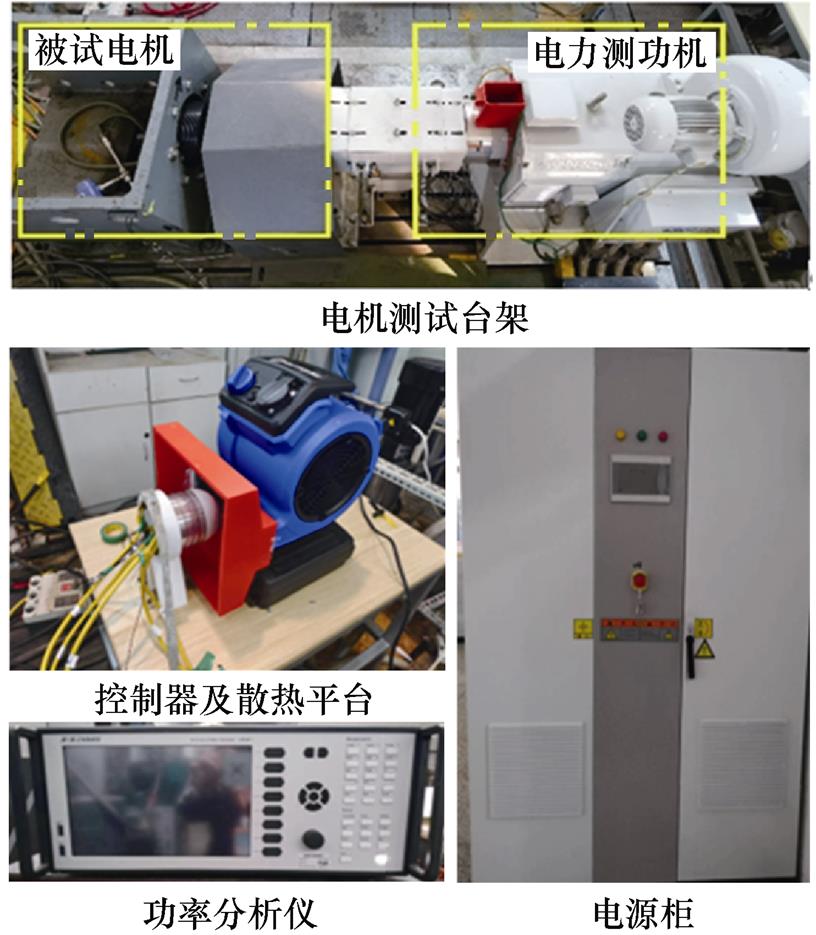

功率实验中,负载电机转速由电力测功机控制,转矩由SiC控制器控制,系统效率及各工况电气参数由功率分析仪测量得到。直流电源采用850 V电源柜,具有恒压限流功能。控制器采用风冷强制对流方案,控制器外壁附近实测风速分别约为:上方9 m/s、下方6 m/s、两侧13 m/s。分立器件并联SiC 控制器在风冷、600 V母线条件下,匹配一台最高转速10 000 r/min、额定转速5 000 r/min、额定功率40 kW、峰值功率80 kW的电机实现了输出峰值功率40 kW、输出电流有效值62 A的实验工况,控制器的功率密度达到了60 kW/L。图25为并联SiC MOSFET控制器功率实验平台。控制器主体固定在支架上,支架用螺栓固定在实验桌上,以防倒塌。控制器迎风端安装半球形导流壳,便于壳体散热。

图25 控制器功率实验平台

Fig.25 The controller power experimental platform

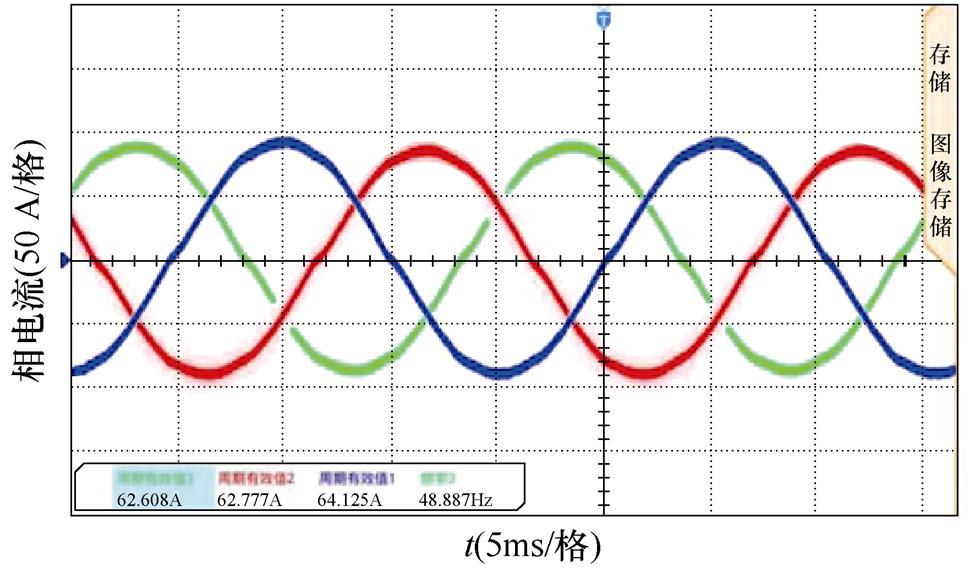

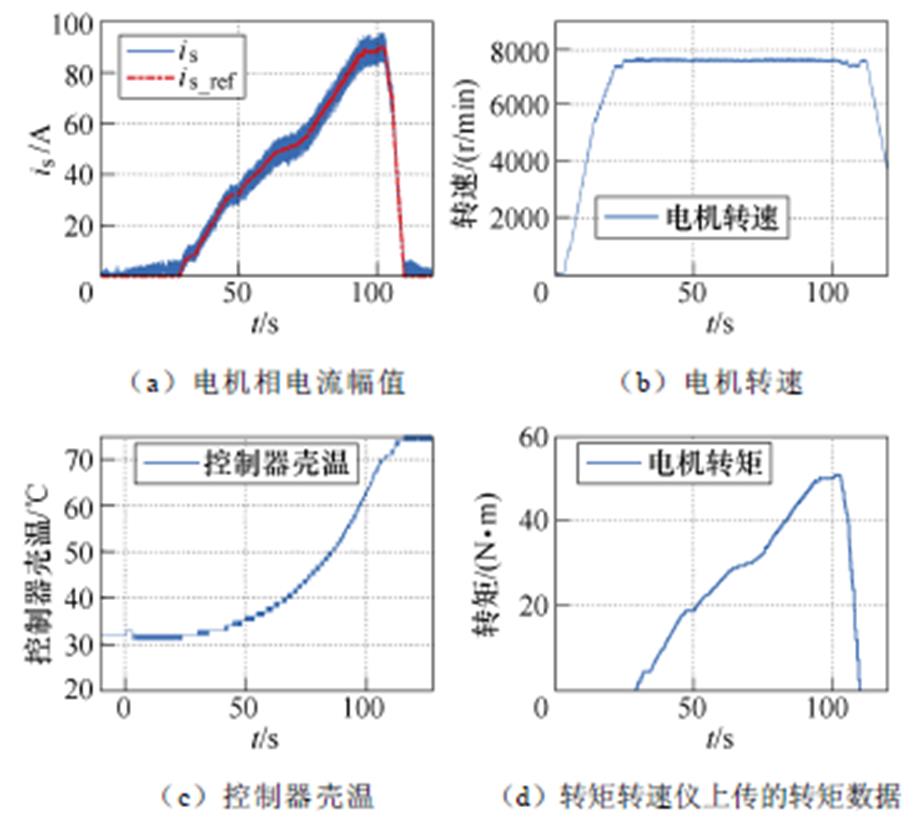

图26为40 kW实验时的稳态相电流波形。由波形可看到,三相交流电流幅值相等,均达到88 A,平衡度比较好,控制器运行良好。图27为上位机与功率分析仪存储下来的一些数据波形,其中包括电机相电流幅值给定值与实际值波形、转速波形、控制器壳温以及电机输出转矩的波形。从数据波形可以看到,交流电流峰值达到了88 A,转速达到了7 600 r/min,转矩达到了50 N·m。工况持续运行3 min以上时,内壁温度基本达到热平衡状态,内壁最终温度为76℃,此时估算MOSFET管结温约为100~110℃,满足设计要求。这里壳温为固定在控制器壳体内壁靠近MOSFET模块处的PT1000测得,由上位机直接读取温度值。

图26 40 kW实验稳态相电流

Fig.26 The 40 kW experimental steady-state phase current

图27 40 kW实验数据

Fig.27 The 40 kW experimental data

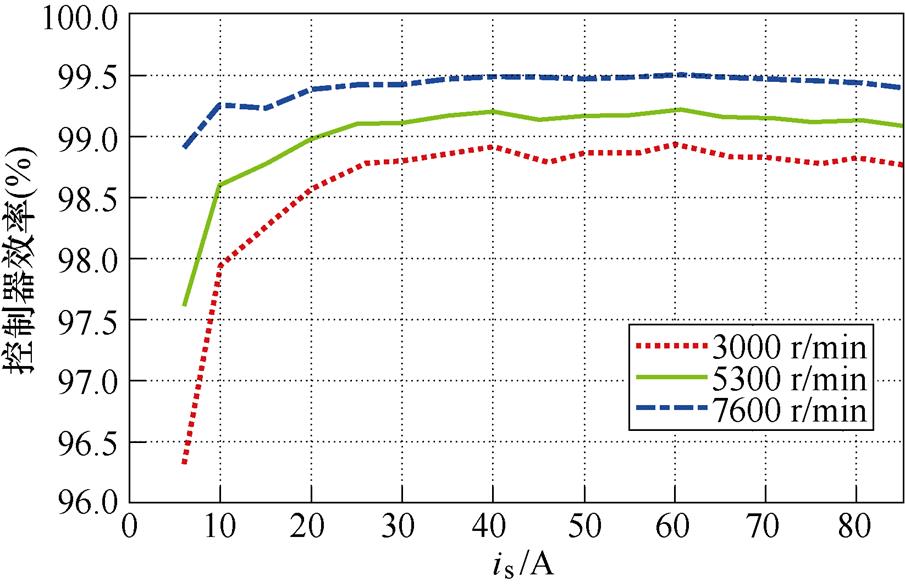

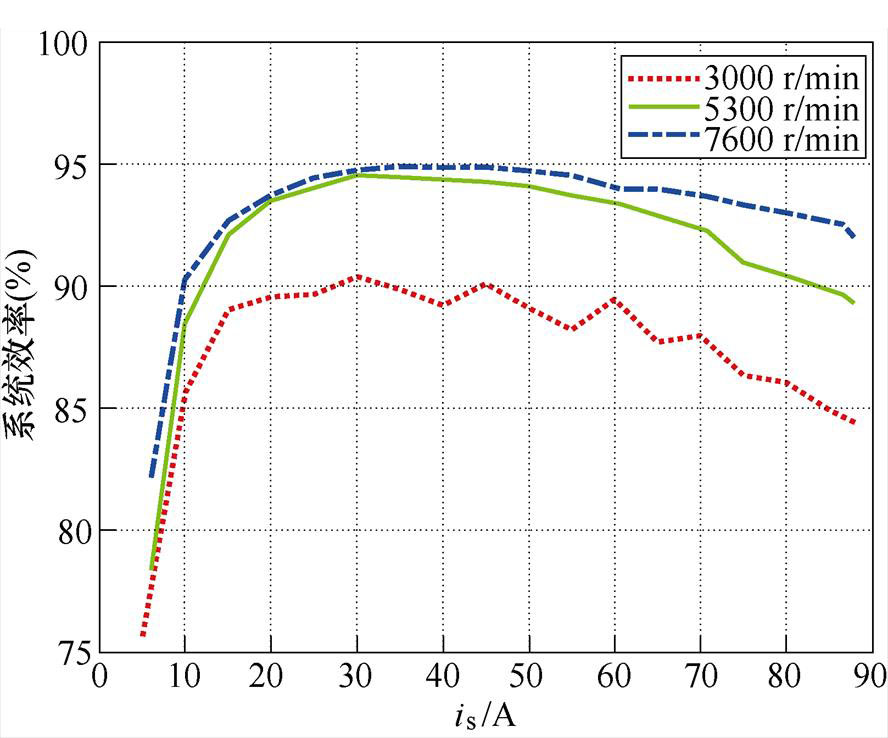

在风冷强制对流散热、母线电压600 V和开关频率10 kHz条件下测量了控制器在不同转速(3 000~7 600 r/min)、不同峰值电流(0~88 A)下的效率曲线,其中最高转速7 600 r/min下控制器达到了峰值功率40 kW。控制器的效率曲线如图28所示,控制器最高效率达到99.5%,这表明控制器在不同转速、不同功率下表现优异,能够高效率运行,也让整个控制器电机系统达到了95%的高效率,效率数据曲线如图29所示。

图28 控制器的效率曲线

Fig.28 The contour plot of controller efficiency

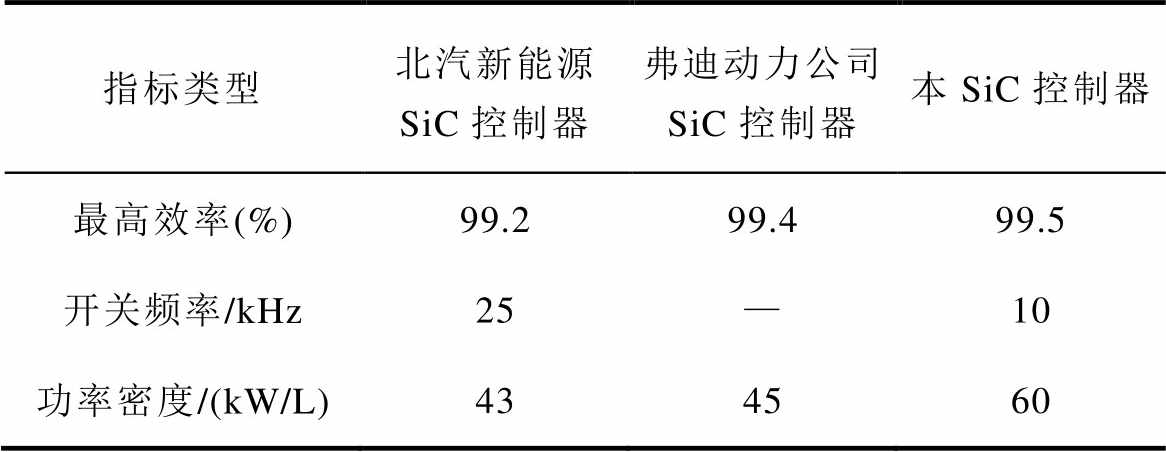

表4列出了研制的SiC控制器与近几年著名企业研制的控制器的指标对比,无论与北汽新能源SiC控制器相比还是与弗迪动力公司SiC控制器相比,功率密度都近1.33倍,而且效率都比两个公司的要高。

图29 系统的效率曲线

Fig.29 The contour plot of system efficiency

表4 本控制器与其他公司控制器指标对比

Tab.4 Comparison of controller indicators between this controller and other companies

指标类型北汽新能源SiC控制器弗迪动力公司SiC控制器本SiC控制器 最高效率(%)99.299.499.5 开关频率/kHz25—10 功率密度/(kW/L)434560

本文基于SiC MOSFET分立器件并联设计实现了一种高功率密度电机控制器,为了从电气和散热角度最大程度地提升材料和空间利用率,实现高功率密度以及分立器件的良好动静态均流,设计了一种新型的电子系统结构,并提出了一种能动态平衡并联MOSFET电流的高抗扰驱动电路以及可实现低寄生电感、大电流以及高散热的适合分立器件并联应用的新型PCB叠层母排设计方法。提出的电路及方法既有利于实现并联器件的动静态均流,又可以减小寄生电感造成的影响,还可以有效抑制负向串扰电压。对根据这些研究结果开发出来的碳化硅电机控制器,进行了双脉冲及功率实验,结果显示,新设计的分立器件并联控制器,均流性能好、散热性能强、功率密度大,并在风冷的条件下,达到了效率最高为99.5%、总功率密度为60 kW/L,为中国的新能源汽车及电机驱动器应用领域,积累了大量具有竞争力的生产技术和宝贵的开发经验。

在下一阶段的工作中,将深入研究并联器件在更大功率密度下的均流电路设计,研究进一步降低PCB母排杂感的优化设计方法,并且深入研究在更紧凑空间环境下的电子系统和母排间的电气互联系统的高效散热措施。

参考文献

[1] 刘平, 陈梓健, 苗轶如, 等. 基于开关瞬态反馈的SiC MOSFET有源驱动电路[J]. 电工技术学报, 2022, 37(17): 4446-4457.

Liu Ping, Chen Zijian, Miao Yiru, et al. Active gate driver for SiC MOSFET based on switching transient feedback[J]. Transactions of China Electrotechnical Society, 2022, 37(17): 4446-4457.

[2] 李鑫, 罗毅飞, 史泽南, 等. 一种基于物理的SiC MOSFET改进电路模型[J]. 电工技术学报, 2022, 37(20): 5214-5226.

Li Xin, Luo Yifei, Shi Zenan, et al. An improved physics-based circuit model for SiC MOSFET[J]. Transactions of China Electrotechnical Society, 2022, 37(20): 5214-5226.

[3] 刘博, 刘伟志, 董侃, 等. 基于全碳化硅功率组件的变流器母排杂散电感解析计算方法[J]. 电工技术学报, 2021, 36(10): 2105-2114.

Liu Bo, Liu Weizhi, Dong Kan, et al. Analytical calculation method for stray inductance of converter busbar based on full silicon carbide power module[J]. Transactions of China Electrotechnical Society, 2021, 36(10): 2105-2114.

[4] 余宝伟, 郭希铮, 部旭聪, 等. 全碳化硅辅助变流器功率回路振荡问题[J]. 电工技术学报, 2021, 36(增刊2): 619-626.

Yu Baowei, Guo Xizheng, Bu Xucong, et al. Oscillation of power circuit of full SiC auxiliary converter[J]. Transactions of China Electrotechnical Society, 2021, 36(S2): 619-626.

[5] Jahdi S, Alatise O, Ortiz G J A, et al. Temperature and switching rate dependence of crosstalk in Si- IGBT and SiC power modules[J]. IEEE Transactions on Industrial Electronics, 2016, 63(2): 849-863.

[6] Yu Shaolin, Wang Jianing, Zhang Xing, et al. The potential impact of using traction inverters with SiC MOSFETs for electric buses[J]. IEEE Access, 2021, 9: 51561-51572.

[7] 王学梅. 宽禁带碳化硅功率器件在电动汽车中的研究与应用[J]. 中国电机工程学报, 2014, 34(3): 371-379.

Wang Xuemei. Researches and applications of wide bandgap SiC power devices in electric vehicles[J]. Proceedings of the CSEE, 2014, 34(3): 371-379.

[8] Williamson S S, Rathore A K, Musavi F. Industrial electronics for electric transportation: current state- of-the-art and future challenges[J]. IEEE Transactions on Industrial Electronics, 2015, 62(5): 3021-3032.

[9] 钟华, 刘志强, 宋佳茵, 等. 分立器件电机控制器功率单元设计与实现[J]. 汽车文摘, 2021(1): 42-47.

Zhong Hua, Liu Zhiqiang, Song Jiayin, et al. Design and implementation of intelligent power unit for dis- crete device motor controller[J]. Automotive Digest, 2021(1): 42-47.

[10] Li Helong, Munk-Nielsen S, Wang Xiongfei, et al. Influences of device and circuit mismatches on paralle- ling silicon carbide MOSFETs[J]. IEEE Transactions on Power Electronics, 2016, 31(1): 621-634.

[11] Hu Ji, Alatise O, Ortiz Gonzalez J A, et al. Robust- ness and balancing of parallel-connected power devices: SiC versus CoolMOS[J]. IEEE Transactions on Industrial Electronics, 2016, 63(4): 2092-2102.

[12] 於少林, 张兴, 王佳宁, 等. 分立器件并联型叠层母排均流分析及优化设计[J]. 电工技术学报, 2023, 38(8): 2086-2099.

Yu Shaolin, Zhang Xing, Wang Jianing, et al. The current balance analysis and optimization design of the laminated busbar with discrete devices in parallel[J]. Transactions of China Electrotechnical Society, 2023, 38(8): 2086-2099.

[13] Peftitsis D, Baburske R, Rabkowski J, et al. Challenges regarding parallel connection of SiC JFETs[J]. IEEE Transactions on Power Electronics, 2013, 28(3): 1449-1463.

[14] Tiwari S, Rabiei A, Shrestha P, et al. Design considerations and laboratory testing of power circuits for parallel operation of silicon carbide MOSFETs[C]//17th European Conference on Power Electronics and Applications, Geneva, Switzerland, 2015: 1-10.

[15] Wang Gangyao, Mookken J, Rice J, et al. Dynamic and static behavior of packaged silicon carbide MOSFETs in paralleled applications[C]//IEEE Applied Power Electronics Conference and Exposition-APEC, Fort Worth, TX, USA, 2014: 1478-1483.

[16] 孙鹏, 魏昌俊, 柯俊吉, 等. 器件特性参数对SiC MOSFET静动态均流影响的实验研究[J]. 智能电网, 2017, 5(8): 757-764.

Sun Peng, Wei Changjun, Ke Junji, et al. Experi- mental investigations of the influences of characte- ristic parameters on static and dynamic current sharing of SiC MOSFET[J]. Smart Grid, 2017, 5(8): 757-764.

[17] Abuogo J. Influence of device parameters spread on current distribution of paralleled silicon carbide MOSFETs[J]. Journal of Power Electronics, 2019, 19(4): 1054-1067.

[18] Ning Puqi, Wang Fei, Ngo K D T. Automatic layout design for power module[J]. IEEE Transactions on Power Electronics, 2013, 28(1): 481-487.

[19] 曾正, 邵伟华, 胡博容, 等. 基于耦合电感的SiC MOSFET并联主动均流[J]. 中国电机工程学报, 2017, 37(7): 2068-2081.

Zeng Zheng, Shao Weihua, Hu Borong, et al. Active current sharing of paralleled SiC MOSFETs by coupling inductors[J]. Proceedings of the CSEE, 2017, 37(7): 2068-2081.

[20] Sadik D P, Colmenares J, Peftitsis D, et al. Experi- mental investigations of static and transient current sharing of parallel-connected silicon carbide MOSFETs[C]//15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2013: 1-10.

[21] Xue Yang, Lu Junjie, Wang Zhiqiang, et al. Active current balancing for parallel-connected silicon carbide MOSFETs[C]//IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 2013: 1563-1569.

[22] Mehrabadi N R, Cvetkovic I, Wang Jun, et al. Busbar design for SiC-based H-bridge PEBB using 1.7 kV, 400 a SiC MOSFETs operating at 100 kHz[C]//IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 2017: 1-7.

[23] 朱俊杰, 原景鑫, 聂子玲, 等. 基于全碳化硅功率组件的叠层母排优化设计研究[J]. 中国电机工程学报, 2019, 39(21): 6383-6394.

Zhu Junjie, Yuan Jingxin, Nie Ziling, et al. Optimum design of planer busbar based on all-silicon carbide power module[J]. Proceedings of the CSEE, 2019, 39(21): 6383-6394.

[24] 董玉斐, 罗皓泽, 杨贺雅, 等. 1.2MV·A混合钳位五电平变流模块的结构布局优化和叠层母排设计[J]. 电工技术学报, 2016, 31(8): 11-18.

Dong Yufei, Luo Haoze, Yang Heya, et al. Engin- eering design for structure and bus bar of 1.2MV·A hybrid clamped five-level converter module[J]. Transactions of China Electrotechnical Society, 2016, 31(8): 11-18.

[25] Solero L, Serrao V, Taglioni P, et al. Low-voltage power electronics building block for automotive applications[C]//Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition, TX, USA, 2006: 7.

[26] 王宁, 张建忠. 基于开关轨迹优化的SiC MOSFET有源驱动电路研究综述[J]. 电工技术学报, 2022, 37(10): 2523-2537.

Wang Ning, Zhang Jianzhong. Review of active gate driver for SiC MOSFET with switching trajectory optimization[J]. Transactions of China Electro- technical Society, 2022, 37(10): 2523-2537.

[27] Deng Xin, Huo Y, Wang Qing, et al. Development of a compact 60kW three-phase asymmetry half-bridge power convertor with specifically designed busbar for switched reluctance machines[C]//IEEE NW Russia Young Researchers in Electrical and Electronic Engineering Conference, St Petersburg, Russia, 2015: 311-316.

[28] 范迦羽, 郑飞麟, 王耀华, 等. 计及热阻与发射极电感匹配的并联IGBT芯片稳态结温均衡方法[J]. 电工技术学报, 2022, 37(12): 3028-3037.

Fan Jiayu, Zheng Feilin, Wang Yaohua, et al. Steady temperature equalization method for the parallel IGBTs considering the thermal resistance and the matching emitter parasitic inductance[J]. Transactions of China Electrotechnical Society, 2022, 37(12): 3028-3037.

Abstract The motor controllers for new energy vehicles are generally realized by high-power modules, but the high-power module is high cost, large volume, and limited in resources. This paper proposes a high-power density motor controller based on the parallel design of SiC MOSFET discrete devices, which maximizes material and space utilization from the perspectives of electrical and heat dissipation.

In order to achieve high power density, three circular circuit boards with a minimum diameter of only 72 mm, consisting of an upper and lower three-layer structure, were used to design the control circuit, driving circuit, and power circuit. The system has a circular structure and uses the Kelvin source of SiC MOSFET to separate the power and drive circuits. The power circuit uses the power source located on the power board, and the drive circuit uses the Kelvin source located on the drive board. It can prevent the interference of the high-voltage side transient signal on the grid voltage feedback and reduce the dynamic loss, allowing for a symmetrical layout of the parallel tube power circuit to the drive circuit.

In the circuit design, taking into account the area, power, heat dissipation, and other factors, the method of using magnetic components to balance the impedance characteristics of the circuit is selected to realize parallel current sharing. A high anti-interference driving circuit is proposed to dynamically equilibrium the current of parallel MOSFETs. A calculated impedance ferrite magnetic bead is connected in series behind the on and off resistors of each SiC MOSFET tube, ensuring that the parallel equivalent impedance is the same while suppressing ringing caused by rapid switching in the SiC MOSFET gate circuit. In addition, the series connection of source resistance and ferrite bead is added to the Kelvin source pole, which can further synchronize the gate signal and realize current sharing. The anti-crosstalk circuit designed using source resistance achieves dual use of one resistor, enhancing the circuit's anti-interference performance.

A new design of PCB stacked busbar, suitable for parallel application of discrete devices, has been achieved with a focus on the goals of low parasitic inductance, high current, and high heat dissipation. The busbar realizes the integrated design of parallel MOSFET tubes, current sensors, discharge resistors, DC capacitors, and AC-DC terminals. When the opposite direction of current in the vertical direction has the smallest parasitic inductance on the smallest loop area and adjacent circuits have opposite current directions, the inductance decreases with the increase of the number of circuits. Accordingly, a low-noise PCB busbar with multiple sets of stacked PCBs is designed. The top and bottom layers of the busbar both have metal windows for DC and AC wiring, which can weld irregularly shaped metal sheets or strips of different thicknesses to expand the current. Hence, it meets the requirements of carrying maximum current, provides good heat dissipation, and achieves long-term operation with a maximum peak current of 120 A.

Dual pulse and power experiments show that the designed discrete device parallel controller can achieve a maximum efficiency of 99.5% and a power density of 60 kW/L at the highest bus voltage of 600 V, suitable for new energy vehicle systems.

Keywords:SiC MOSFET, discrete device parallel, high power density, printed circuit board (PCB) stack bus

张少昆 女,1986年生,硕士研究生,研究方向为电力电子系统硬件设计及开发。E-mail: zhangshaokun@mail.iee.ac.cn

范 涛 男,1981年生,博士,研究员,研究方向为高功率密度电机及其控制器系统。E-mail: fantao@mail.iee.ac.cn(通信作者)

中图分类号:TM614

DOI: 10.19595/j.cnki.1000-6753.tces.230545

十四五国家重点研发计划资助项目(2022YFB2502800)。

收稿日期 2023-04-27

改稿日期 2023-07-07

(编辑 崔文静)