图1 基于双脉冲测试电路的SiC MOSFET开关轨迹

Fig.1 Switching trajectory of SiC MOSFET based on double pulse test

摘要 得益于优异的电-热性能,SiC器件在新能源变流器中得到了越来越多的应用。然而,相对于Si器件,SiC器件的开关速度更快、安全裕度更低、电磁干扰更大,制约了其安全可靠运行。基于栅极驱动电阻的动态切换,该文提出一种四阶段变电阻的SiC MOSFET器件开关轨迹调控方法,实现开关速度、损耗、过冲、振荡、串扰、延迟等多项性能的协同优化,建立驱动电阻对SiC器件开关轨迹定量调控的数学模型,发现开关性能量化指标与开关轨迹不同阶段之间的解耦规律,提出分阶段变电阻的驱动方法,实现开关轨迹中多个控制目标之间的协同优化,给出驱动电阻取值的通用设计方法,提出驱动电阻切换的交错时序逻辑,对比传统驱动方法,采用大量实验结果,验证了所提模型方法的有效性。

关键词:SiC MOSFET器件 主动栅极驱动 四阶段变电阻 开关轨迹调控 多目标协同

在新能源发电、电动汽车、轨道交通等领域,高效率、高功率密度SiC逆变器,可以降低功率损耗和系统成本,提升行驶里程和有效载荷,是“双碳”目标的关键技术支撑[1-3]。相对于传统Si IGBT器件,新兴的SiC MOSFET器件具有开关速度快、开关损耗低等优异性能,可以有效提升逆变器的开关频率和功率密度,从而得到了快速应用[4]。然而,SiC逆变器面临热管理和电磁兼容两大难题[5]。SiC器件的高dv/dt和di/dt,虽然会在一定程度上降低开关损耗,但是也会导致严重的过冲、振荡、串扰等副作用[6-7],限制了SiC逆变器功率密度的进一步提升。因此,如何在开关损耗和电磁干扰方面寻求折中,定量调控SiC器件的开关轨迹,提升SiC逆变器的功率密度,具有重要的研究价值和应用前景。

针对SiC器件的开关轨迹调控,已有部分研究,主要集中在可控性建模、无源电路调控和栅极电路调控三个方面。在开关轨迹建模方面,为了准确刻画SiC器件的开关行为,掌握器件开关轨迹的可观性,分析开关损耗、dv/dt、di/dt等的影响规律[8-10],可以考虑器件的等效电路模型和结电容效应[11-13],计及器件封装和印制电路板(Printed Circuit Board, PCB)布线的寄生参数[14-15],基于数据手册,建立SiC器件的解析模型或行为模型[16-17],并采用双脉冲实验进行验证。然而,开关轨迹的特征量还缺乏基础模型表征,开关轨迹的可控性还缺乏定量评估。在无源电路调控方面,通常在漏-源极、栅-源极或栅-漏极之间,添加RC缓冲吸收电路[18-20],或在直流母线引入RCD缓冲吸收电路[21],调控器件的开关行为。此外,也可以采用PCB上的变压器耦合[22-24],在功率回路植入阻尼电阻,转移器件的暂态能量,抑制开关振荡。然而,吸收电路在降低器件开关过冲和振荡的同时,会降低器件开关速度,增加开关损耗[25]。在栅极电路调控方面,由于栅极驱动回路可以为SiC MOSFET器件的开关行为提供多个调控自由度[26],从驱动侧调节并优化开关轨迹,越来越受到关注与研究。为抑制开关过冲、振荡和串扰,最直接的方法是增加栅极电阻。单纯地增加栅极电阻,虽然可以削弱过冲、振荡和串扰,但是也会大幅增加开关损耗和开关延迟,牺牲了SiC 器件的高速性能,得不偿失[27-28]。近年来,主动栅极驱动(Active Gate Driver, AGD)技术因其较高的灵活性,得到了快速发展[29-32]。根据调控变量的不同[26],AGD可以分为变电压、变电流、变电阻等不同类型。变电压AGD在器件开关过程中输出多个驱动电平,调节开关轨迹,能有效降低开关损耗[33-34]。输出电平数越多,控制自由度越高,效果越好;但是,驱动电路和隔离电源的设计复杂度也大幅增加[33]。变电流AGD通过调节驱动输出电流或附加注入电 流[35-36],抑制器件的开关过冲和振荡。但是,电流控制电路的结构更复杂、成本更高,电流注入在抑制振荡和过冲的同时,会牺牲器件的开关速度和损耗。变电阻AGD通过改变栅极电阻来调节器件的开关过程,结构简单、控制容易、成本较低[37-39]。然而,现有变电阻AGD的可调阶段数少,调节能力有限,还无法实现对开关轨迹中多个特征参量的协同调控,此外,阻值的选择依赖工程经验,缺乏理论模型指导。可见,如何通过栅极驱动电路,优化开关轨迹的各个特征参量,降低开关损耗、开关振荡、电磁干扰,仍然面临技术挑战。综上所述,现有研究建立了SiC器件的开关行为表征模型,从无源缓冲电路和栅极驱动电路的角度,给出了开关轨迹的调控方法。主动的或智能的栅极电路调控方法,是SiC器件开关轨迹调控的发展趋势。然而,基于主动栅极驱动的开关轨迹调控方法,可控目标与控制变量之间的关系还缺乏模型指导,栅极电阻的优化选择还缺乏定量设计,多个调控目标之间还缺乏协同优化,亟待技术创新。

针对主动栅极驱动缺乏调控分析模型、定量设计方法、多目标协同优化等技术难题,本文详细研究了一种四阶段变电阻的SiC器件开关轨迹调控方法。本文建立了刻画SiC器件开关轨迹的特征量模型,分析了栅极电阻对开关轨迹的调控规律,基于SiC器件开通或关断的四阶段模型。定量设计了各个阶段的最佳栅极电阻,提出了一种四阶段变电阻的栅极驱动电路,实现对速度、损耗、过冲、振荡和串扰等开关轨迹特征量的协同优化,并给出了交错切换的变电阻时序控制逻辑。采用对比实验结果,验证了所提模型和方法的有效性,为SiC MOSFET器件开关轨迹的多目标协同调控,提供模型方法和技术支撑,为降低SiC逆变器的开关损耗和电磁干扰,提供了有益参考。

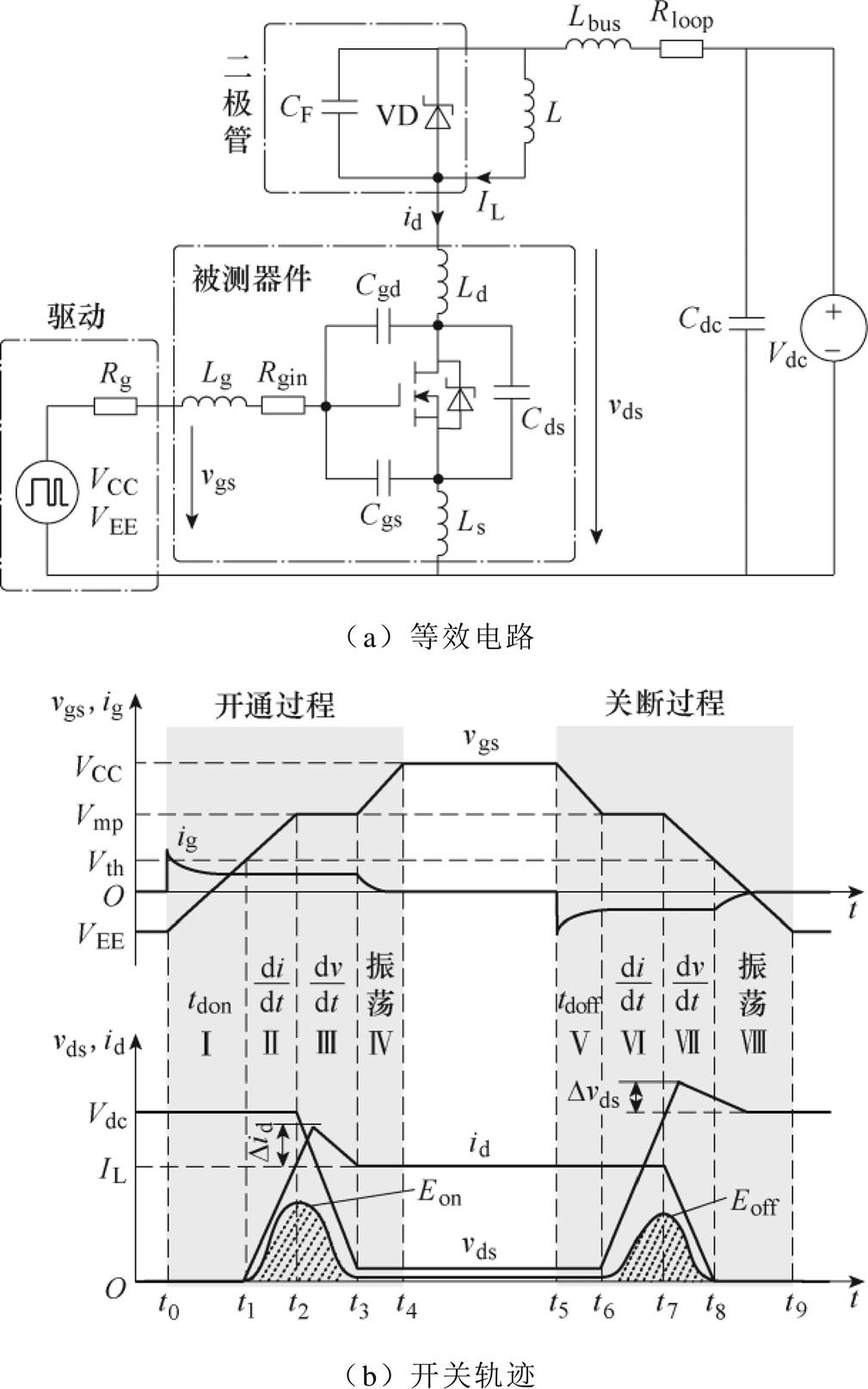

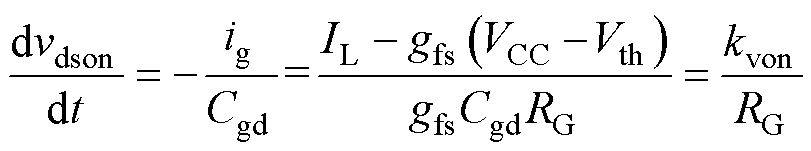

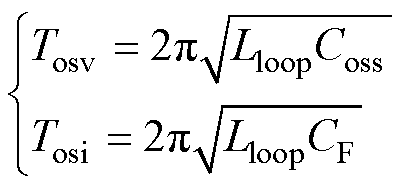

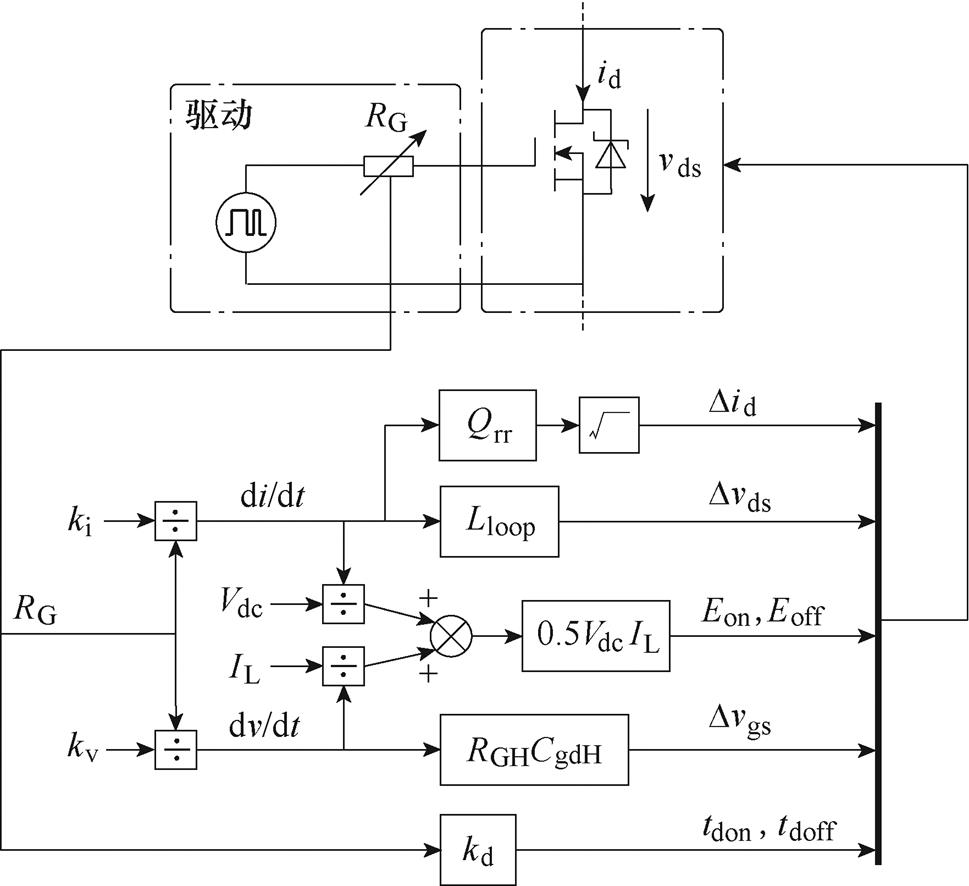

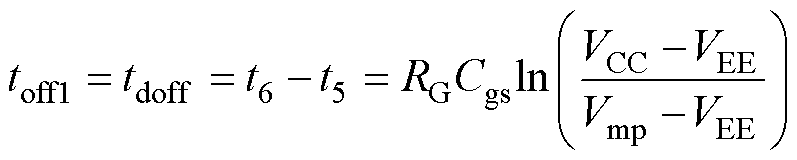

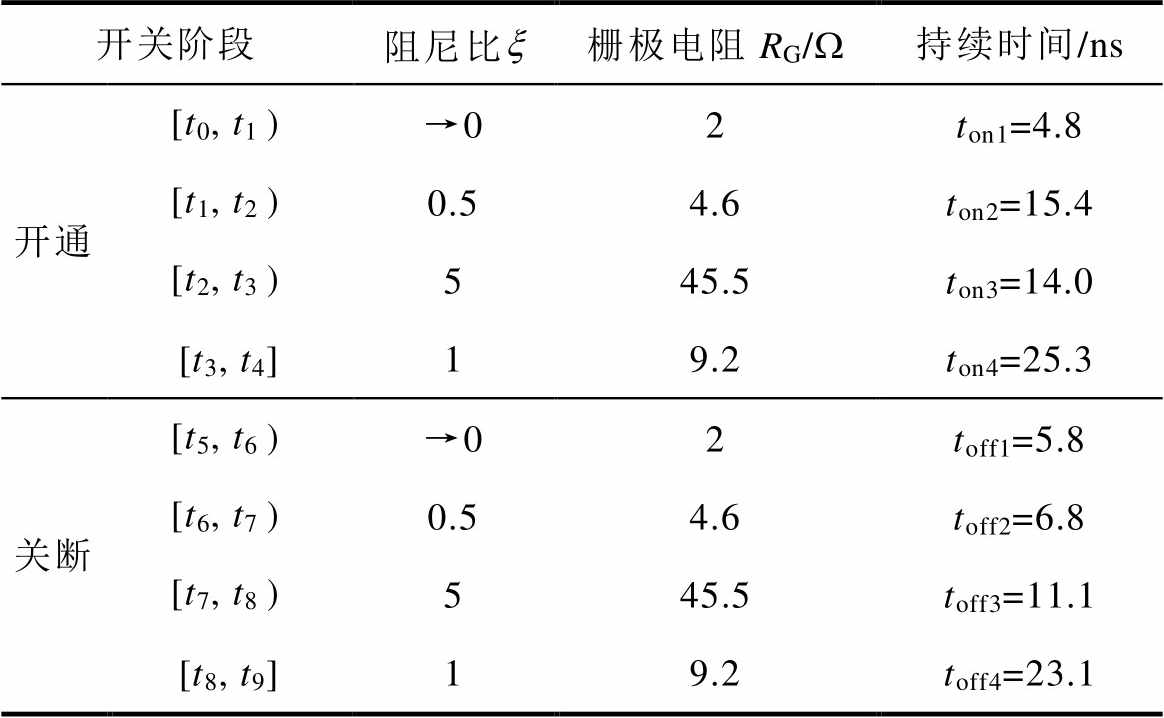

电感钳位双脉冲测试是评估SiC MOSFET器件开关特性的常用方法,基于双脉冲测试电路的SiC MOSFET开关轨迹如图1所示。图中,Vdc和Cdc分别为母线电压和母线电容,Lbus为母线寄生电感,Rloop为功率回路寄生电阻,L和IL分别为负荷电感和负荷电流,CF为二极管VD的结电容,vds和id分别为器件的漏-源极电压和漏极电流,vgs和ig分别为器件的栅-源极电压和栅极电流,Cgs、Cgd和Cds分别为器件的栅-源电容、栅-漏电容(米勒电容)和漏-源电容,VCC和VEE分别为栅极驱动电路的正压和负压,Rg为栅极驱动电阻,Rgin为器件的栅极内电阻,Lg、Ld和Ls分别为器件的栅极、漏极和源极寄生电感。Vth和Vmp分别为SiC MOSFET器件的阈值电压和米勒平台电压,Did和Dvds分别为器件的开通电流过冲和关断电压过冲,Eon和Eoff分别器件的开通损耗和关断损耗。

图1 基于双脉冲测试电路的SiC MOSFET开关轨迹

Fig.1 Switching trajectory of SiC MOSFET based on double pulse test

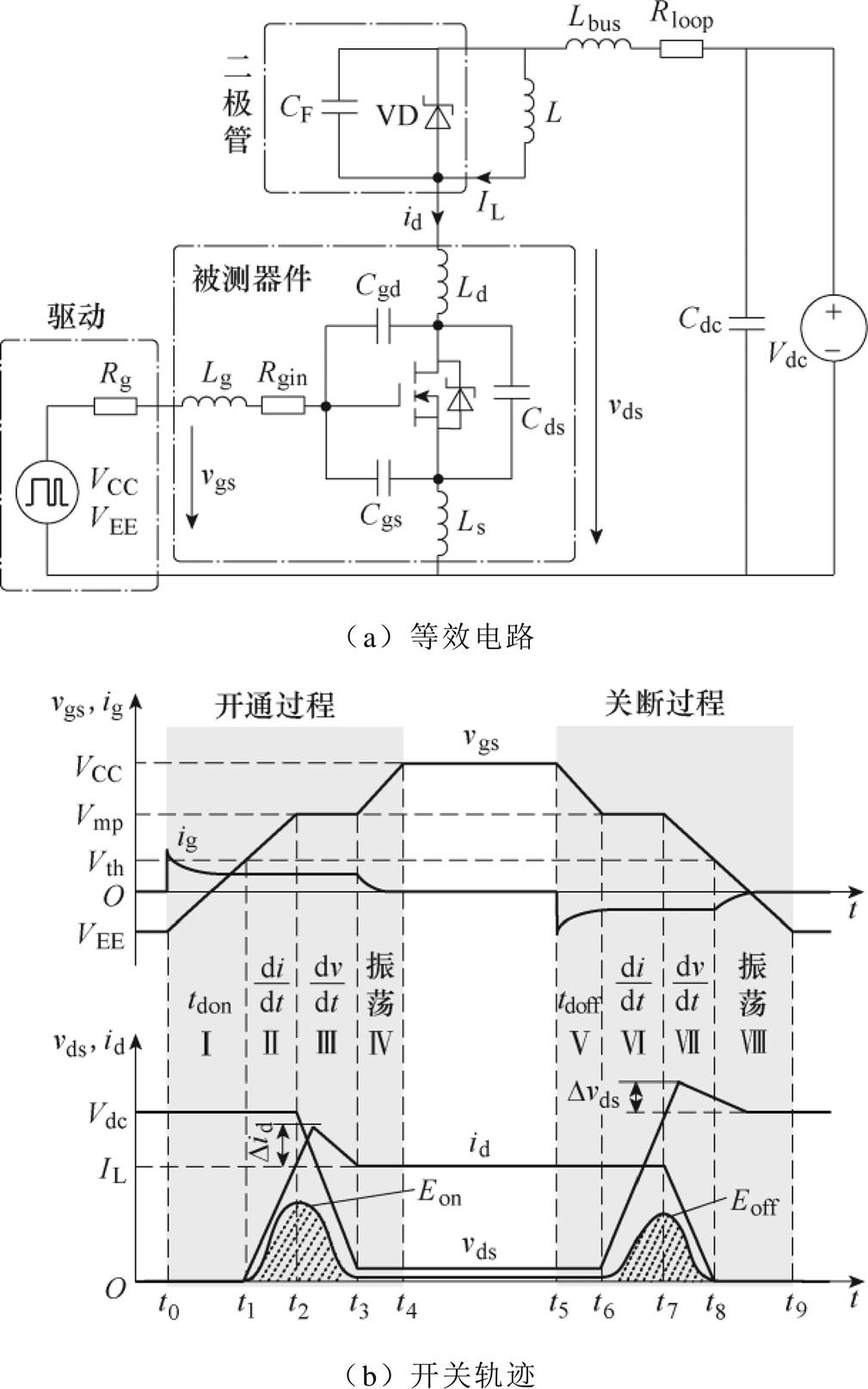

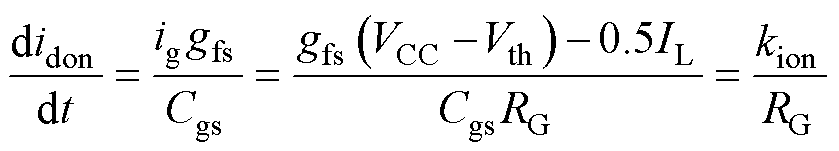

基于双脉冲测试方法,可以定量分析驱动电路对开关轨迹各特征量的影响规律。为主动驱动的设计,以及开关轨迹的精细化调控,提供理论依据。功率器件的开关轨迹与变流器的电-热设计息息相关,功率器件开关轨迹与变流器应用之间的映射关系见表1。在变流器的应用中,通常考虑6个关键特征参量,来描述功率器件的开关轨迹,包括:损耗、过冲、振荡、串扰、电压/电流变化率、延迟时间,分别对应8个开关阶段,突出解耦。

表1 功率器件开关轨迹与变流器应用之间的映射关系

Tab.1 Map between switching trajectory of power device and optimal design of power converter

编号开关轨迹特征量变流器应用 1开关损耗热设计与热管理可靠性设计 2电压/电流过冲有源和无源器件的电应力设计 3开关振荡功率器件的选型设计缓冲吸收电路设计 4开关串扰串扰抑制电路设计 5电压/电流变化率EMI滤波器设计低感直流母排设计 6开关延迟死区时间设计开关频率设计

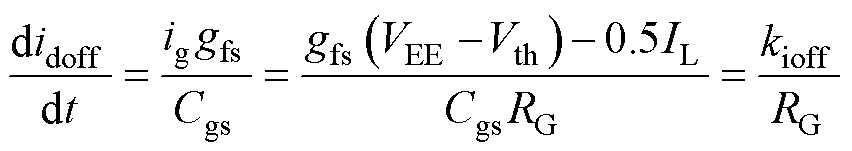

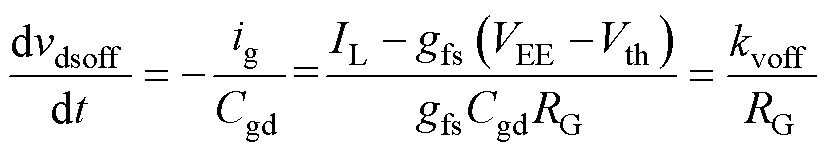

电压变化率dvds/dt和电流变化率did/dt直接决定器件的损耗、过冲、振荡、串扰等特征量。在简化的开关轨迹模型中,开关过程的电压、电流变化率模型分析如下。

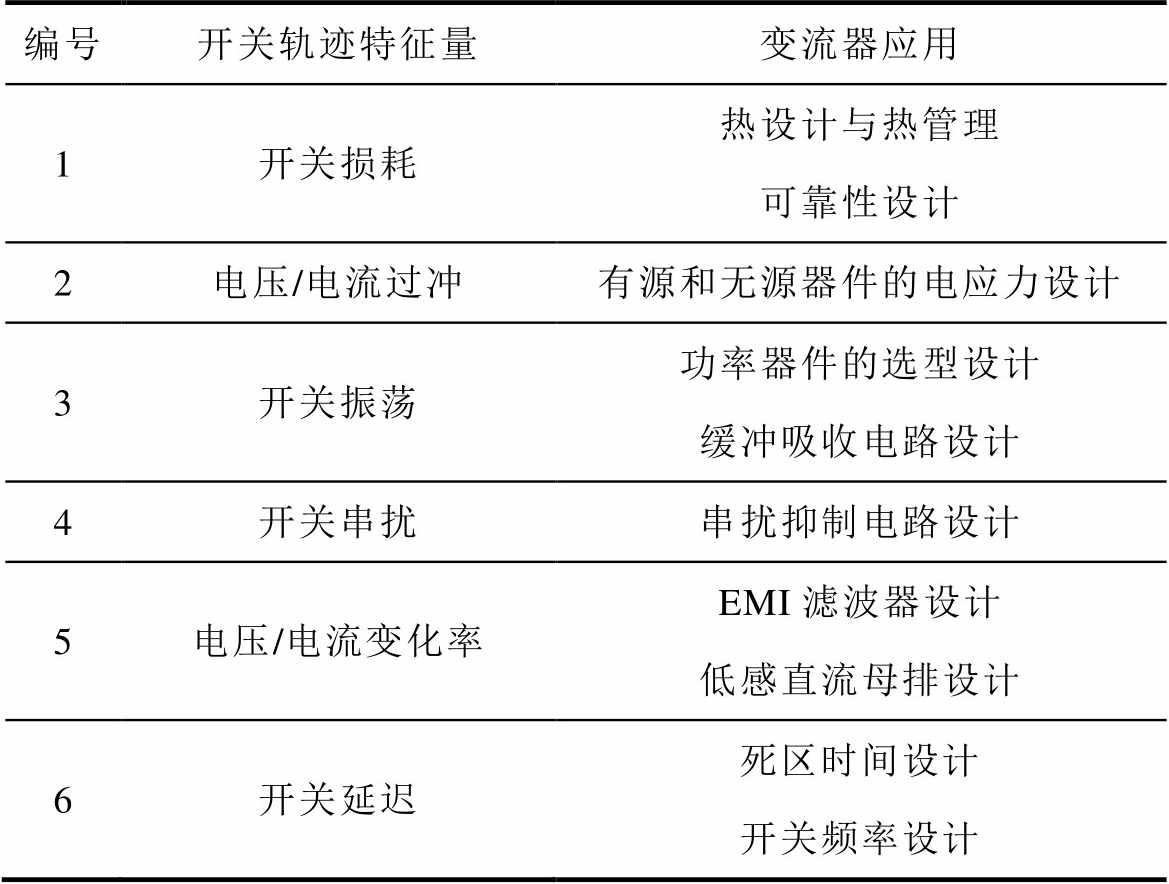

对于开通过程,电流id的上升发生在开通阶段Ⅱ[t1, t2 。在该阶段,vds≈Vdc,vgs从Vth上升至Vmp。开通阶段电流变化率didon/dt可以表示为

。在该阶段,vds≈Vdc,vgs从Vth上升至Vmp。开通阶段电流变化率didon/dt可以表示为

(1)

(1)

式中,RG为栅极回路的总电阻,RG=Rg+Rgin;gfs和Vth分别为器件的跨导和阈值电压;kion为常数。类似地,电压vds的下降发生在开通阶段Ⅲ [t2, t3 。该阶段近似有id≈IL,输入电容Ciss=Cgd+Cgs,而ig主要为米勒电容Cgd充电,vgs维持在米勒平台电压Vmp。开通阶段电压变化率dvdson/dt可以表示为

。该阶段近似有id≈IL,输入电容Ciss=Cgd+Cgs,而ig主要为米勒电容Cgd充电,vgs维持在米勒平台电压Vmp。开通阶段电压变化率dvdson/dt可以表示为

(2)

(2)

式中,kvon为常数。

对于关断过程,电流id的下降发生在关断阶段Ⅶ [t7, t8 ,关断阶段电流变化率didoff /dt可以表示为

,关断阶段电流变化率didoff /dt可以表示为

(3)

(3)

式中,kioff为常数。电压vds的上升发生在关断Ⅵ阶段[t6, t7 ,关断阶段电压变化率dvdsoff/dt可以表示为

,关断阶段电压变化率dvdsoff/dt可以表示为

(4)

(4)

式中,kvoff为常数。

综上所述,根据式(1)~式(4),开关过程中的dvds/dt和did/dt均与栅极电阻RG成反比,改变RG即可实现对dvds/dt和did/dt的有效调控。

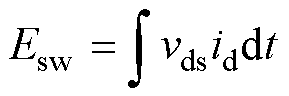

开关损耗是SiC MOSFET开关行为的重要量化指标,直接影响变流器的效率和热设计。开关损耗定义为开关过程中vds和id的交叠面积,即

(5)

(5)

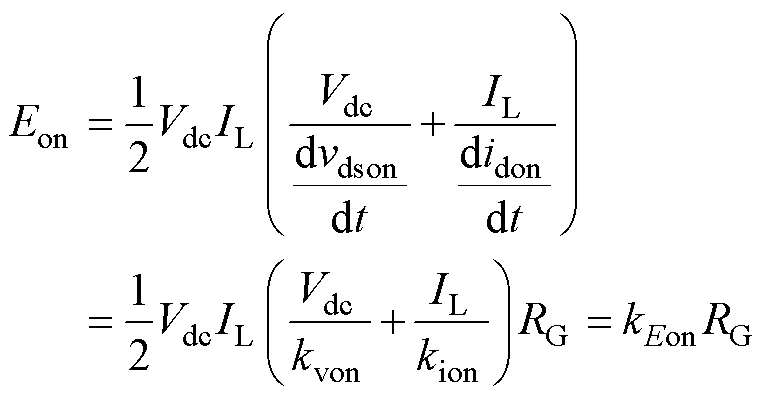

器件开关过程中的电压和电流近似呈线性变化,可以得到开关损耗的解析模型。对开通损耗Eon,有

(6)

(6)

式中,dvdson/dt和didon/dt分别为开通过程中,vds和id的变化率;kEon为常数。

类似地,对于关断损耗Eoff,有

(7)

(7)

式中,dvdsoff/dt和didoff/dt分别为关断过程中,vds和id的变化率;kEoff为常数。

根据式(6)和式(7),一旦固定Vdc和IL,开关损耗仅与电压变化率dvds/dt和电流变化率did/dt有关。因此,适当提高dvds/dt和did/dt,能够缩短vds和id交叠区域的持续时间,降低开关损耗。

在SiC MOSFET的开关过程中,过快的电压/电流变化率会增加Did和Dvds,增大器件的电流/电压应力,降低器件的安全裕度,缩小器件的安全工作区,降低变流器的可靠性。因此,在器件的开关过程中,应该尽可能地抑制开关过冲。

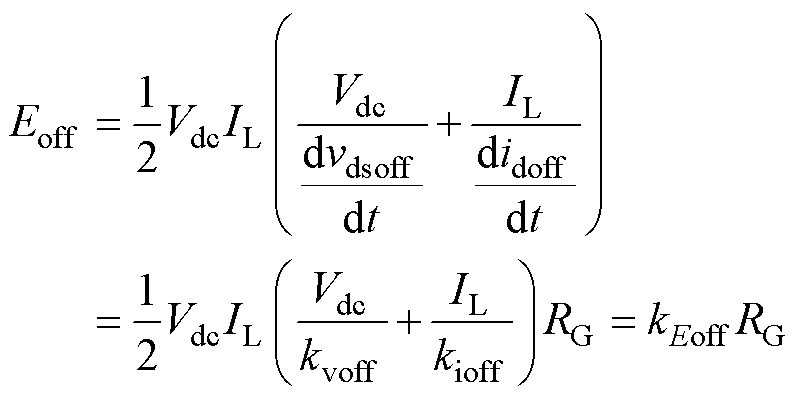

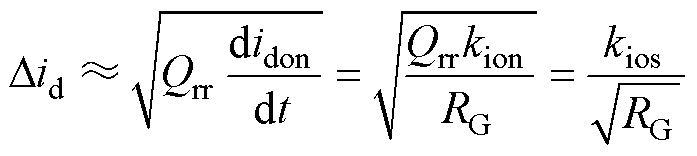

电流过冲发生在开通阶段Ⅲ [t2, t3 ,主要由上桥臂二极管的反向恢复电流引起,与漏极电流上升率didon/dt有关。开通过电流Did可以表示为

,主要由上桥臂二极管的反向恢复电流引起,与漏极电流上升率didon/dt有关。开通过电流Did可以表示为

(8)

(8)

式中,Qrr为上桥臂二极管的反向恢复电荷;kios为常数。当二极管参数确定后,可以通过降低didon/dt,来减小Did。

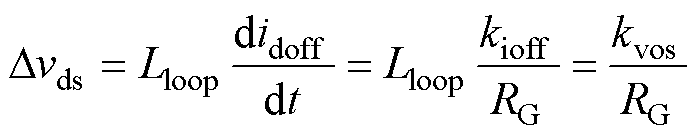

电压过冲发生在关断阶段Ⅶ [t7, t8 ,主要由功率回路的寄生电感Lloop引起,与电流下降斜率didoff/dt有关。关断过电压Dvds可以表示为

,主要由功率回路的寄生电感Lloop引起,与电流下降斜率didoff/dt有关。关断过电压Dvds可以表示为

(9)

(9)

式中,Lloop为功率回路的寄生电感,Lloop=Lbus+Ld+Ls,Lbus为直流母线寄生电感;kvos为常数。当Lloop一定时,降低did/dt可以抑制Dvds。

在SiC MOSFET的开关过程中,开关过冲之后,往往会伴随开关振荡。通常,开关振荡为衰减振荡,主要由振荡周期、振荡幅值和衰减系数三者决定。

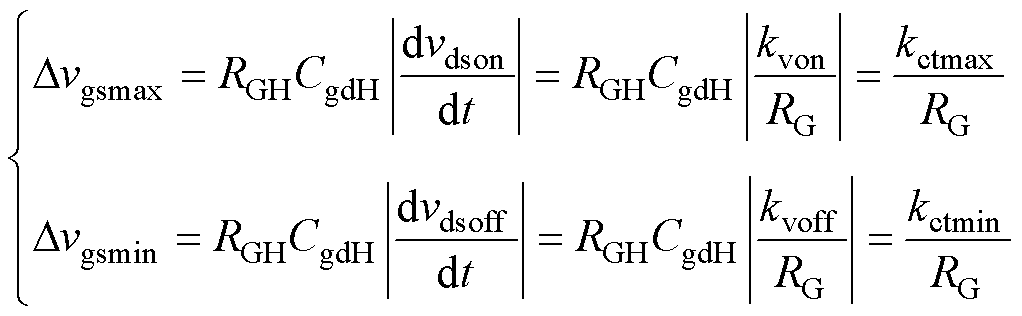

vds和id的振荡周期Tosv和Tosi与功率回路的电路参数有关,可以分别表示为

(10)

(10)

式中,Coss为SiC MOSFET的输出电容,Coss=Cgd+ Cds;CF为对侧二极管的结电容;Dvds和Did为vds和id的振荡幅值。振荡的衰减系数与功率回路的寄生电阻Rloop有关。

可见,开关振荡的周期和衰减常数由功率回路的固有参数决定,且基本固定。振荡幅值由开关过冲决定,且与did/dt有关。降低did/dt,可以抑制开关过冲Did和Dvds,并减小振荡幅值,以消除开关振荡的不利影响。

在SiC MOSFET的开关过程中,由于米勒电容的位移电流效应,较高的dvds/dt会在互补导通器件的栅-源极产生感应电压Dvgs,形成开关串扰现象。由于串扰感应电压的不利影响,当栅-源极电压的正向峰值超过阈值电压时,可能会造成器件的误导通。当栅-源极电压超过器件栅极电压的最大或最小允许值时,可能会造成器件损坏。

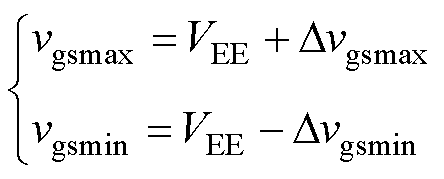

开关串扰主要由RG、Cgd和dvds/dt决定,Dvgs的最大值和最小值可分别近似表示为

(11)

(11)

式中,RGH和CgdH分别为上管的栅极电阻和米勒电容;kctmax和kctmin为常数。因此,器件栅-源极电压的正向峰值和负向峰值可分别表示为

(12)

(12)

串扰主要发生在开关过程中vds变化的阶段,即开通阶段Ⅲ [t2, t3 和关断阶段Ⅲ [t7, t8

和关断阶段Ⅲ [t7, t8 。因此,在对应阶段减小dvds/dt可以抑制串扰的不利影响。

。因此,在对应阶段减小dvds/dt可以抑制串扰的不利影响。

在SiC MOSFET器件的开通过程中,驱动信号发出后,vds和id不会立即响应,驱动电路需要对器件的Cgs充电,使vgs从VEE升至Vth,id才开始上升。同样,在器件的关断过程中,驱动电路需要对器件Cgs放电,使vgs从VCC降至Vmp,vds才开始上升。栅-源极电容的充放电过程,导致vds和id响应波形与驱动信号之间,存在开关延时。

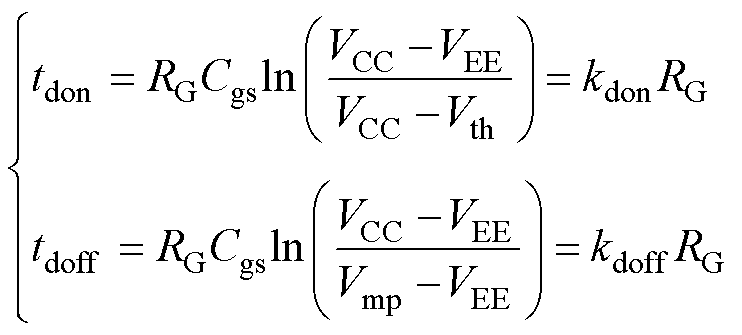

根据SiC MOSFET栅极输入电容的充放电过程,开通和关断延迟时间tdon和tdoff可近似表示为

(13)

(13)

式中,kdon和kdoff为常数。

过长的开关延迟时间,会降低器件的响应速度,制约器件的开关频率,影响变流器的控制带宽和动态性能。因此,需要通过调整栅极电阻RG,尽量降低器件的开关延迟时间。

根据以上开关轨迹的定量分析,可以发现,栅极电阻RG可直接或间接调控开关轨迹的各个特征参量,对应的控制关系以及栅极电阻对SiC MOSFET开关轨迹的调控规律如图2所示。

图2 栅极电阻对SiC MOSFET开关轨迹的调控规律

Fig.2 Principles of controlled switching trajectory of SiC MOSFET by gate resistance

综上所述,开关轨迹的6大特征量相互解耦,分别体现在开关轨迹的不同阶段,且均与栅极电阻有关。通过在不同阶段主动调节RG,可以独立地调控开关损耗、过冲、振荡、串扰、电压/电流变化率和开关延迟,实现多个优化目标的协同调控。

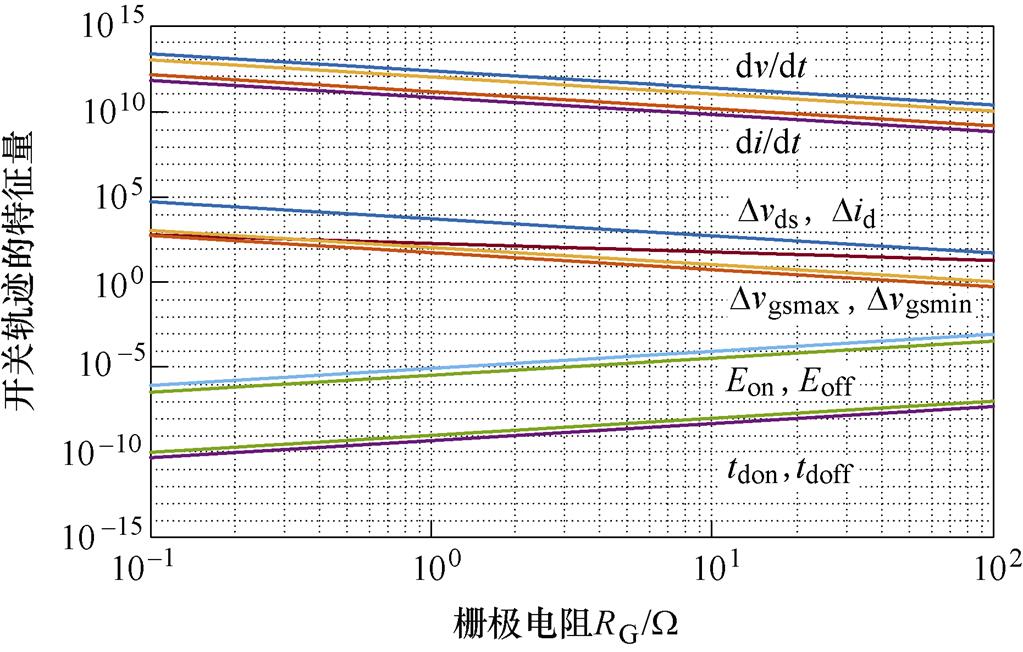

以Cree公司的SiC MOSFET器件C2M0080120D为例,器件在典型工况(800 V/20 A/25 ℃)下的参数为:Cgs=1 122.5 pF、Cgd=7.5 pF、Cds=84.5 pF、Vth=3.2 V、Vmp=5.2 V、gfs=10 S、Qrr=152 nC、Lloop= 60 nH,根据式(1)~式(13),可以得到器件开关轨迹特征量与栅极电阻RG之间的关系,栅极电阻对SiC MOSFET开关轨迹的调控规律如图3所示。可见,电压/电流变化率和开关过冲随着RG增大而减小,然而,其他特征量随着RG的增大而增大。因此,无法通过设置某一个固定的RG,同时实现各个特征量的优化调控。值得指出的是,各个特征量分别对应开关轨迹8个不同阶段,相互之间完全解耦,因此如果能在不同的开关阶段实时地改变栅极总电阻RG,独立地调节各开关阶段的特征量,可以实现开关轨迹的定制化协同优化。

图3 栅极电阻对SiC MOSFET开关轨迹调控的定量分析

Fig.3 Quantitative assessments of controlled switching trajectory of SiC MOSFET by gate resistance

根据栅极驱动电阻对SiC MOSFET器件开关行为的调控规律,本节首先分析SiC器件的开关模态,归纳各个开关模态与开关行为特征量的映射关系,最后定量设计各模态所对应的最佳栅极电阻,实现各个特征量的定向调控,并达到开关轨迹的协同优化。此外,还提出了一种变电阻栅极驱动电路的实现方法。

器件的开通和关断过程分别对应4个模态,如图1所示。各个模态分别独立控制器件的4个特征量。根据各个模态的等效电路,优化设计栅极电阻,可以同时优化开关轨迹的控制目标。选取各阶段栅极电阻时,除了考虑对特征参量的优化,还应该考虑栅极驱动回路稳定性对栅极电阻的限制。

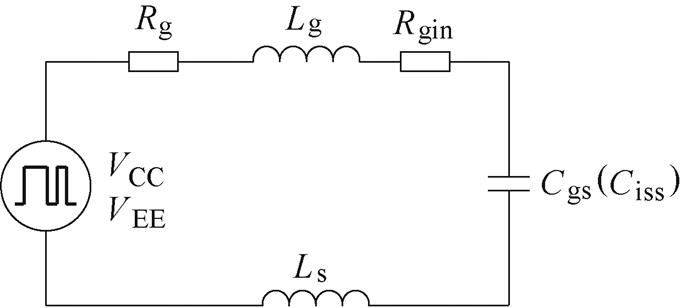

在栅极回路中,调节栅极电阻RG的本质,在于改变栅极回路在开关过程中的充放电速度。SiC MOSFET栅极回路的等效电路可以采用RLC二阶电路描述,如图4所示。

图4 SiC MOSFET器件的栅极等效电路

Fig.4 Equivalent circuit of gate loop for SiC MOSFET

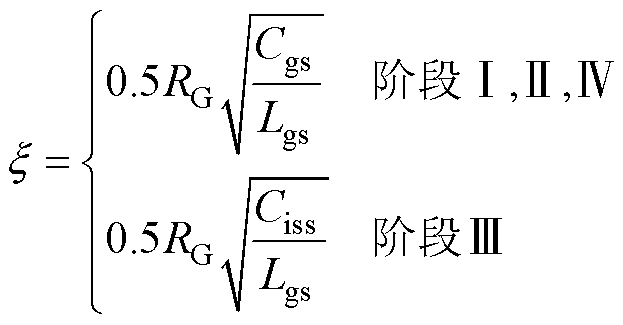

栅极回路充放电过程中的稳态和动态性能,可由该二阶电路的阻尼比x 表征,即

(14)

(14)

式中,Lgs为栅极回路的寄生电感,Lgs=Lg+Ls。为了保证驱动回路的稳定性,阻尼比应该满足x>0。

根据SiC MOSFET器件的开关模态,结合栅极回路阻尼比x 的限制和特征参量调控关系,可以定量设计各个开关模态所对应的最优栅极电阻RG。

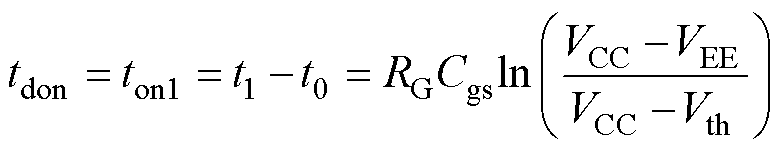

(1)开通阶段Ⅰ[t0, t1 :开通延迟。该阶段主要影响SiC MOSFET器件的开通延迟时间tdon。由于tdon越大,器件的死区时间越长,器件所允许的开关频率越低。因此,希望tdon尽可能小。将该阶段的阻尼比xon1设计为欠阻尼0<xon1<1,且xon1趋近于0,以提升器件的响应速度。开通阶段Ⅰ的持续时间ton1即为开通延迟时间,有

:开通延迟。该阶段主要影响SiC MOSFET器件的开通延迟时间tdon。由于tdon越大,器件的死区时间越长,器件所允许的开关频率越低。因此,希望tdon尽可能小。将该阶段的阻尼比xon1设计为欠阻尼0<xon1<1,且xon1趋近于0,以提升器件的响应速度。开通阶段Ⅰ的持续时间ton1即为开通延迟时间,有

(15)

(15)

(2)开通阶段Ⅱ[t1, t2 :漏极电流上升。该阶段主要影响器件的电流上升时间tron。由于tron越大,电流上升斜率didon/dt越低,器件的开通损耗Eon越大。但是,tron过小,会导致过高的didon/dt,影响下一个阶段的二极管反向恢复过程,并引发电流过冲。因此,将该阶段的阻尼比xon2设计为欠阻尼0<xon2<1,取xon2=0.5,在开关损耗和电流过冲之间寻求折中。开通阶段Ⅱ的持续时间ton2与电流上升率有关,可以表示为

:漏极电流上升。该阶段主要影响器件的电流上升时间tron。由于tron越大,电流上升斜率didon/dt越低,器件的开通损耗Eon越大。但是,tron过小,会导致过高的didon/dt,影响下一个阶段的二极管反向恢复过程,并引发电流过冲。因此,将该阶段的阻尼比xon2设计为欠阻尼0<xon2<1,取xon2=0.5,在开关损耗和电流过冲之间寻求折中。开通阶段Ⅱ的持续时间ton2与电流上升率有关,可以表示为

(16)

(16)

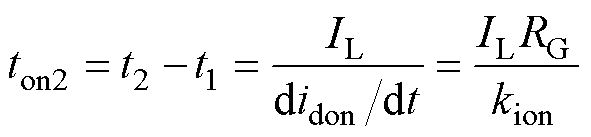

(3)开通阶段Ⅲ[t2, t3 :漏-源极电压下降。该阶段主要影响漏极电流的过冲和振荡,以及对侧器件的串扰电压峰值。因此,该阶段应该最大程度地降低漏-源电压的变化率dvdson/dt。将该阶段的阻尼比xon3设计为过阻尼xon3>1,为了确保过冲、振荡和串扰的抑制效果,选择较大的阻尼比xon3=5。开通阶段Ⅲ的持续时间可以表示为

:漏-源极电压下降。该阶段主要影响漏极电流的过冲和振荡,以及对侧器件的串扰电压峰值。因此,该阶段应该最大程度地降低漏-源电压的变化率dvdson/dt。将该阶段的阻尼比xon3设计为过阻尼xon3>1,为了确保过冲、振荡和串扰的抑制效果,选择较大的阻尼比xon3=5。开通阶段Ⅲ的持续时间可以表示为

(17)

(17)

(4)开通阶段Ⅳ[t3, t4]:栅-源极电压继续上升。该阶段保证vgs持续稳定地上升至驱动电压VCC。在该阶段,振荡和串扰现象可能仍然在持续。因此,应该首先确保栅极充电的稳定性,其次再提升栅极充电的速度。该阶段的阻尼比xon4设计为临界阻尼xon4=1。开通阶段Ⅳ的持续时间可以表示为

(18)

(18)

对于SiC MOSFET器件,其关断过程与开通过程镜像对称。各阶段的栅极电阻设计方法,与开通过程类似。

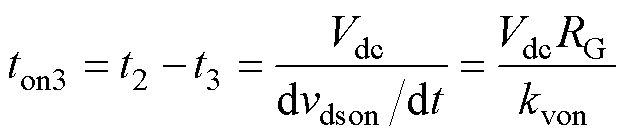

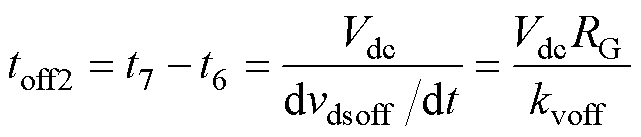

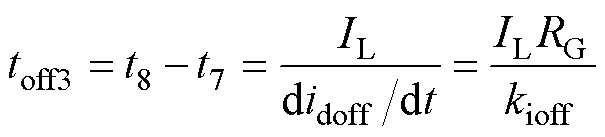

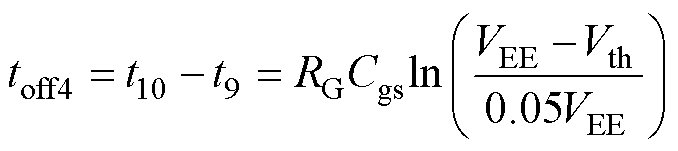

(1)关断阶段Ⅴ[t5, t6 :关断延迟。该阶段主要影响器件的关断延迟时间tdoff,将该阶段的阻尼比xoff1设计为欠阻尼0<xoff1<1,且xoff1趋近于0。关断阶段Ⅴ的持续时间toff1即为关断延迟时间,可以表示为

:关断延迟。该阶段主要影响器件的关断延迟时间tdoff,将该阶段的阻尼比xoff1设计为欠阻尼0<xoff1<1,且xoff1趋近于0。关断阶段Ⅴ的持续时间toff1即为关断延迟时间,可以表示为

(19)

(19)

(2)关断阶段Ⅵ[t6, t7 :漏-源极电压上升。该阶段主要影响器件的关断损耗,将该阶段的阻尼比xoff2设计为欠阻尼0<xoff2<1,取xoff2=0.5。关断阶段Ⅵ的持续时间可以估计为

:漏-源极电压上升。该阶段主要影响器件的关断损耗,将该阶段的阻尼比xoff2设计为欠阻尼0<xoff2<1,取xoff2=0.5。关断阶段Ⅵ的持续时间可以估计为

(20)

(20)

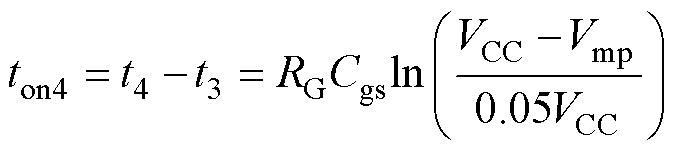

(3)关断阶段Ⅶ[t7, t8 :漏极电流下降。该阶段主要影响器件的关断电压过冲,将该阶段的阻尼比xoff3设计为过阻尼xoff3>1,取xoff3=5。关断阶段Ⅶ的持续时间可计算为

:漏极电流下降。该阶段主要影响器件的关断电压过冲,将该阶段的阻尼比xoff3设计为过阻尼xoff3>1,取xoff3=5。关断阶段Ⅶ的持续时间可计算为

(21)

(21)

(4)关断阶段Ⅷ[t8, t9]:栅-源极电压继续下降。该阶段影响器件的电压振荡,将其阻尼比xoff4设计为临界阻尼xoff4=1。在抑制振荡的同时提升动态响应速度。关断阶段Ⅷ的持续时间可以估计为

(22)

(22)

综上所述,将各开关阶段的优化阻尼比及驱动回路的结电容,代入式(14),即可计算得到各开关阶段对应的最优栅极电阻值。同理,代入电路和器件的参数,即可确定各阶段的持续时间。

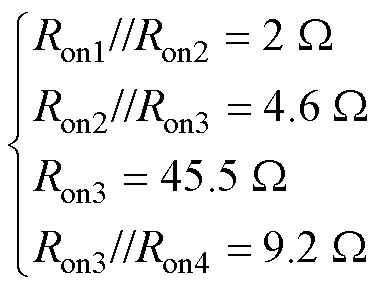

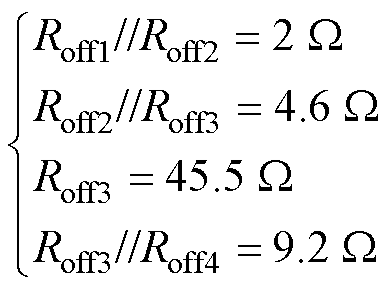

以Cree公司的SiC MOSFET器件C2M0080120D为例,采用矢量网络分析仪,可以测得器件及其PCB回路的寄生电感参数Lg=12.5 nH、Ls=10.5 nH,采用器件特性测试仪,可以测得器件的结电容Cgs= 1 100 pF、Cgd=7.5 pF。因此,开关过程各阶段所对应的栅极电阻和持续时间的理论值,见表2。

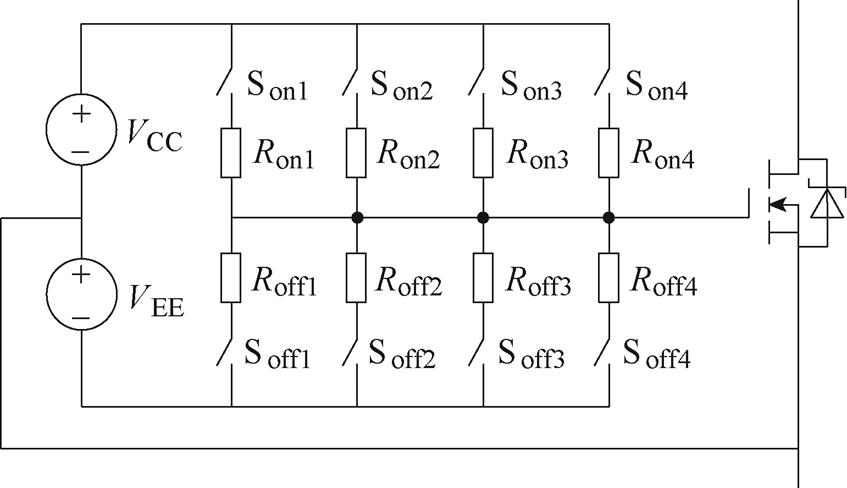

为了独立控制开关过程的各个阶段,实现对栅极回路的解耦调控,实现对开关轨迹各个特征量的协同优化,本文提出了一种四阶段变电阻的SiC MOSFET主动栅极驱动电路,如图5所示。分别采用四组开关和电阻,控制驱动回路在开关过程各阶段的栅极电阻。

表2 开关过程各阶段栅极电阻的优化结果理论值

Tab.2 Optimized gate resistances during each phase of switching process

开关阶段阻尼比x栅极电阻RG/W持续时间/ns 开通[t0, t1→02ton1=4.8 [t1, t20.54.6ton2=15.4 [t2, t3545.5ton3=14.0 [t3, t4]19.2ton4=25.3 关断[t5, t6→02toff1=5.8 [t6, t70.54.6toff2=6.8 [t7, t8545.5toff3=11.1 [t8, t9]19.2toff4=23.1

图5 变电阻的SiC MOSFET主动栅极驱动电路

Fig.5 Proposed varistor active gate drive for SiC MOSFET

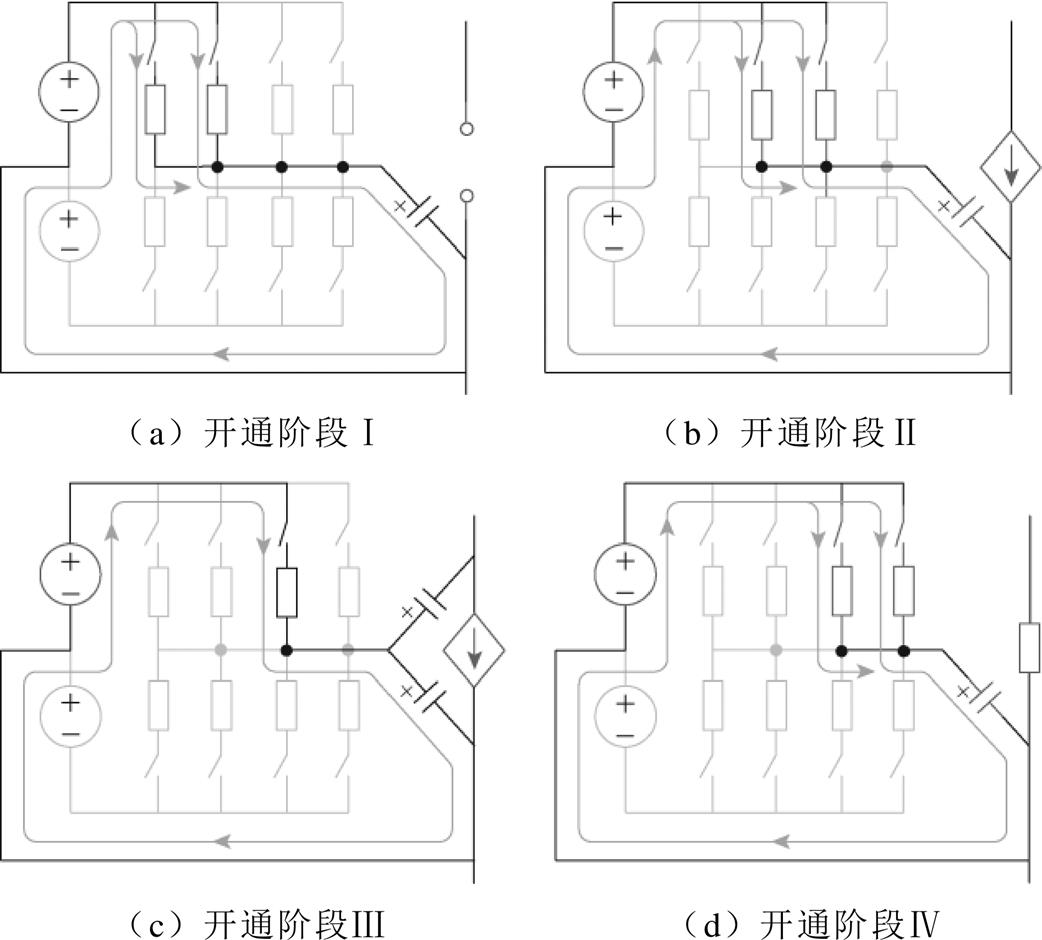

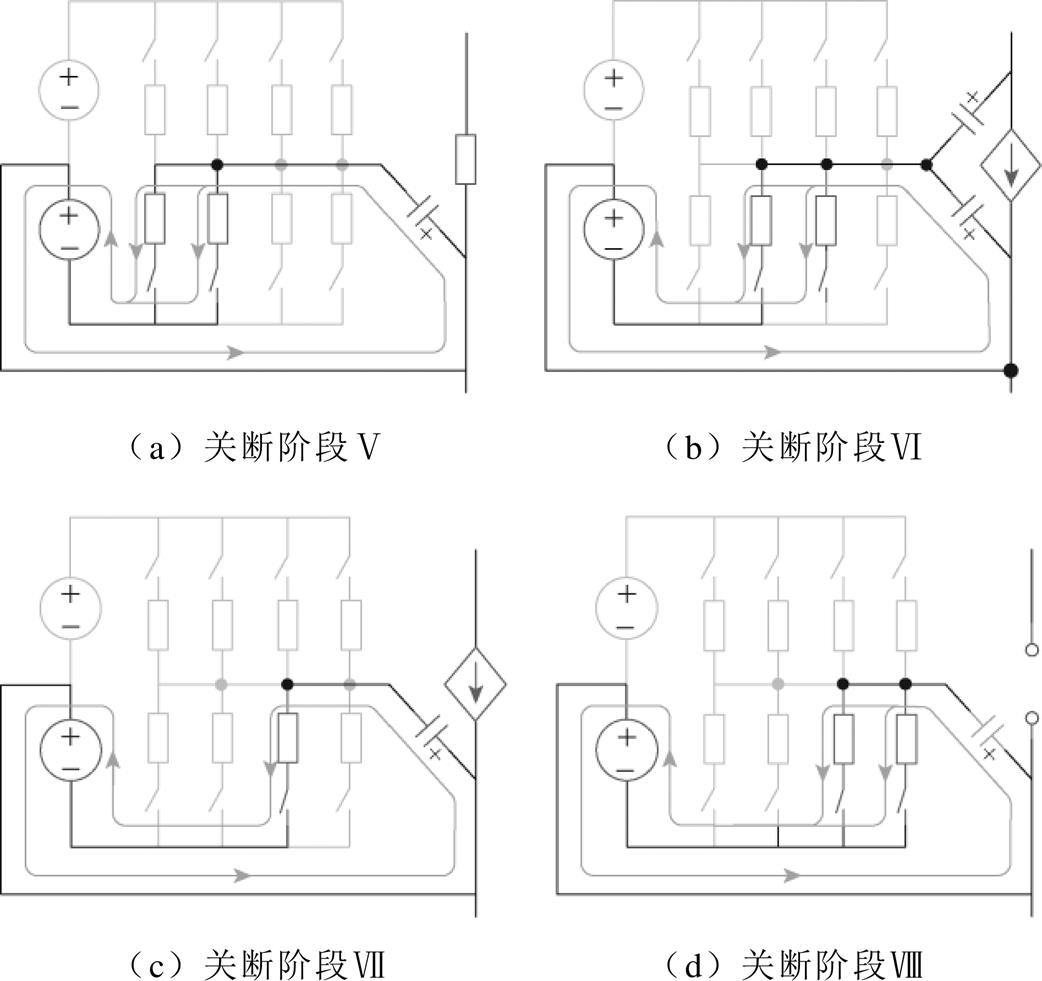

在SiC MOSFET器件开关过程中,所提驱动电路的控制时序和等效电路,如图6和图7所示。为避免在不同阶段的切换过程中出现电流断续,根据格雷码原理,所提驱动电路采用交错切换的工作模式,保证任何时刻至少有一个栅极电阻串联在驱动回路中。

图6 所提驱动电路在开通过程各阶段的工作模式

Fig.6 Operation modes of proposed gate driver during each phases of turn-on process

图7 所提驱动电路在关断过程各阶段的工作模式

Fig.7 Operation modes of proposed gate driver during each phases of turn-off process

根据图6和图7所示驱动电路的工作模式,参考表2的理论计算结果,各电阻的取值为

(23)

(23)

(24)

(24)

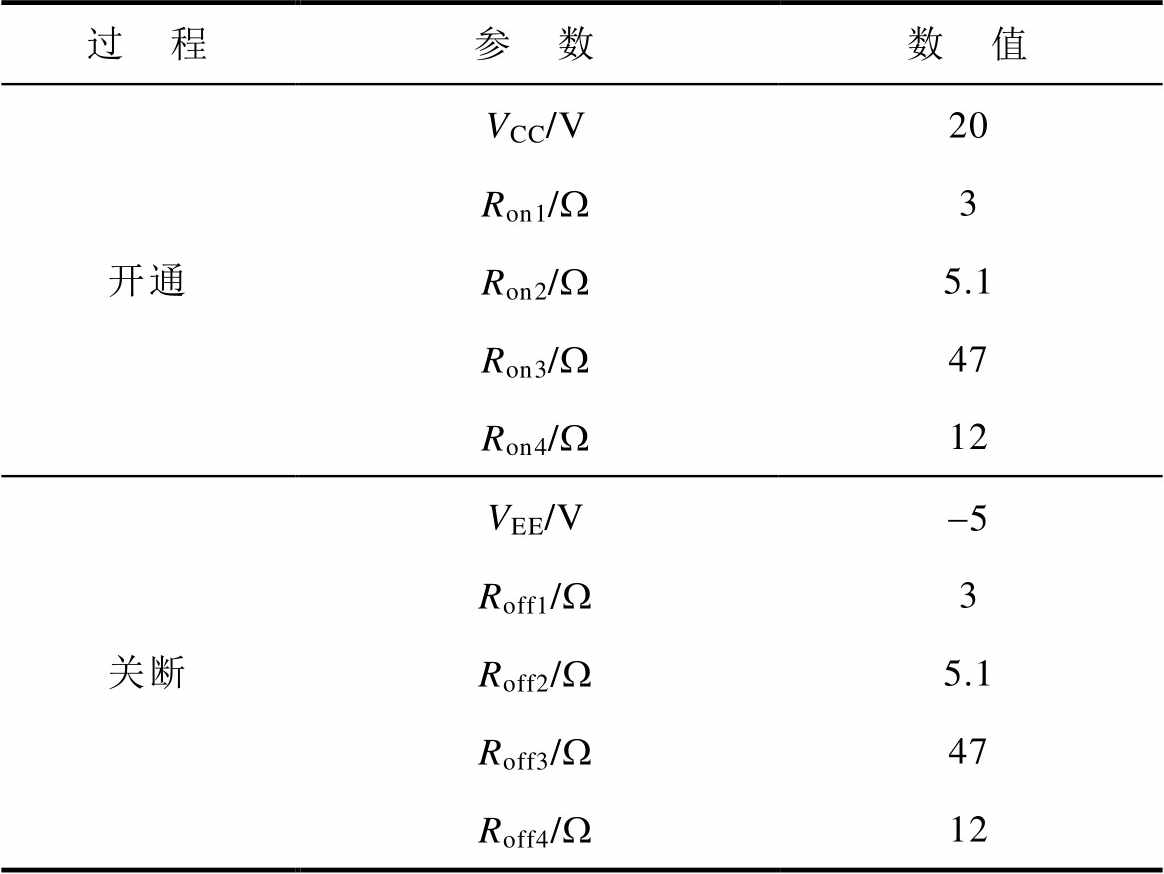

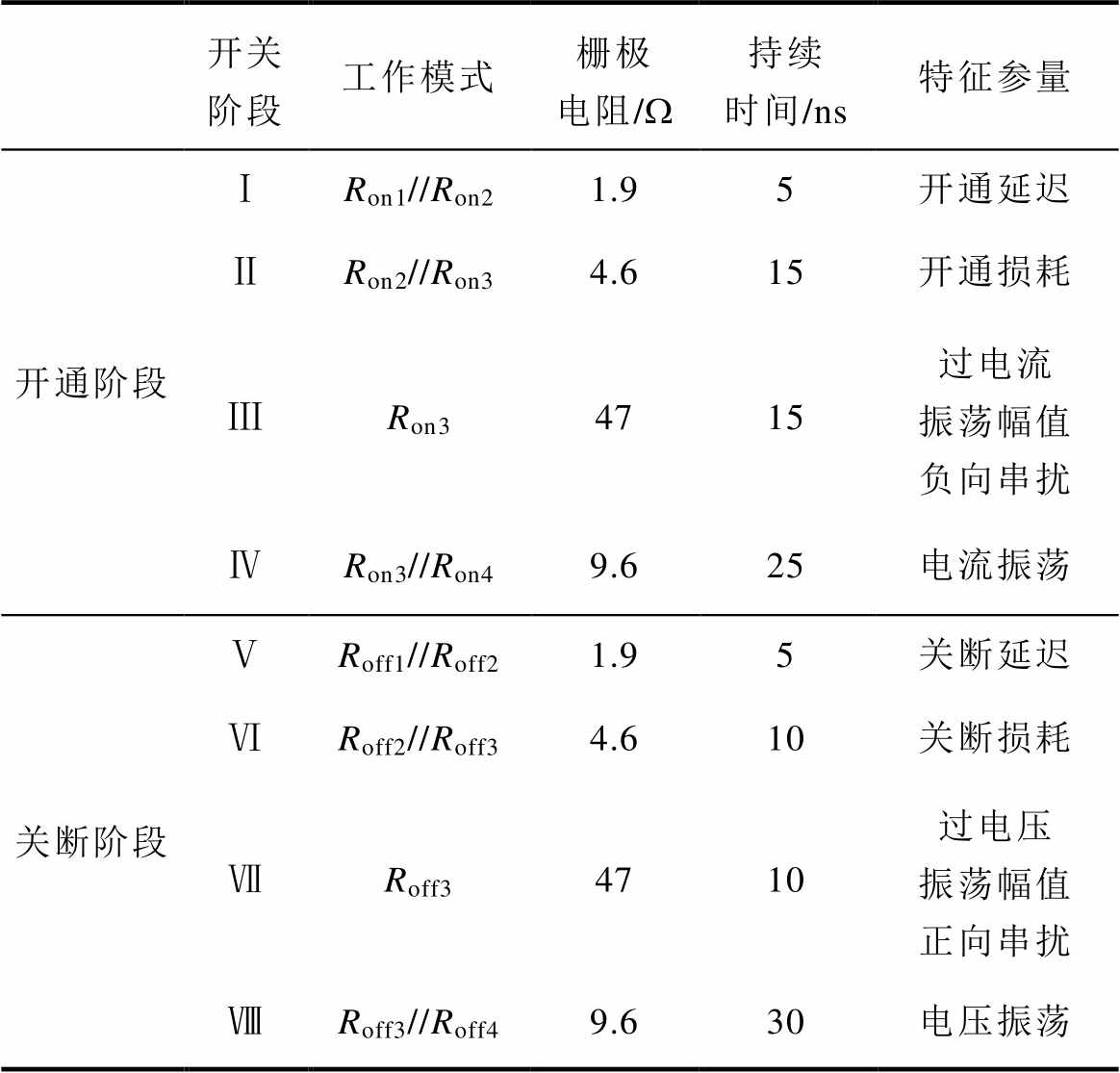

求解以上方程组,得到电阻理论取值,并结合实际电阻的标称值,确定栅极驱动电阻实际取值,所提驱动电路栅极电阻的设计结果见表3。驱动电压选择为+20/-5 V。

综上所述,可以得到所提驱动电路的工作模式和优化效果,见表4。其中,实际电阻按标称阻值选取组合,实际持续时间按FPGA实际工作主频率200 MHz对应的最小步长5ns就近选取。可见,开通和关断的各个阶段,分别对应不同的器件开关轨迹特征量。各个特征量在开关过程的8个阶段实现解耦。因此,可以通过对每个开关阶段的驱动电阻最优调节,从而实现器件开关轨迹的综合优化。

表3 所提驱动电路栅极电阻的设计结果

Tab.3 Designed gate resistances of proposed gate driver

过 程参 数数 值 开通VCC/V20 Ron1/W3 Ron2/W5.1 Ron3/W47 Ron4/W12 关断VEE/V-5 Roff1/W3 Roff2/W5.1 Roff3/W47 Roff4/W12

表4 所提驱动电路的工作模式及优化效果

Tab.4 Operation modes and optimized results of proposed gate driver

开关阶段工作模式栅极电阻/W持续时间/ns特征参量 开通阶段ⅠRon1//Ron21.95开通延迟 ⅡRon2//Ron34.615开通损耗 ⅢRon34715过电流振荡幅值负向串扰 ⅣRon3//Ron49.625电流振荡 关断阶段ⅤRoff1//Roff21.95关断延迟 ⅥRoff2//Roff34.610关断损耗 ⅦRoff34710过电压振荡幅值正向串扰 ⅧRoff3//Roff49.630电压振荡

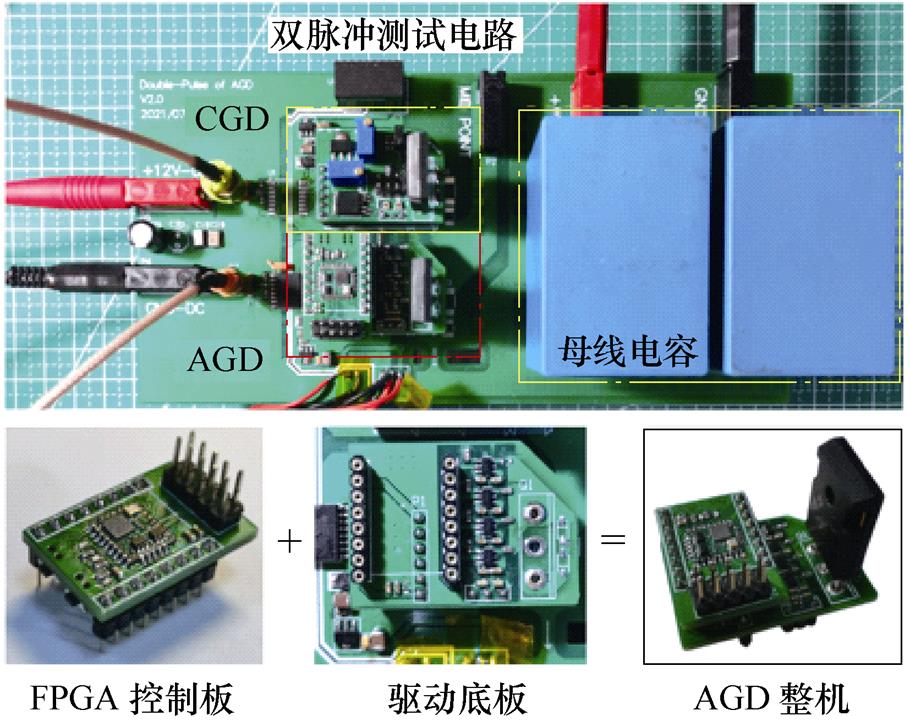

根据第2节的工作原理与设计结果,研制了AGD驱动电路样机,如图8所示。该AGD实验样机由驱动底板和FPGA控制板构成,驱动底板实现栅极电阻投切电路,其中开关结构由高速驱动芯片UCC27531实现,FPGA控制板接收来自上层控制电路的PWM驱动信号,将其转化为各个开关阶段的时序控制逻辑,实现栅极电阻的有序切换。

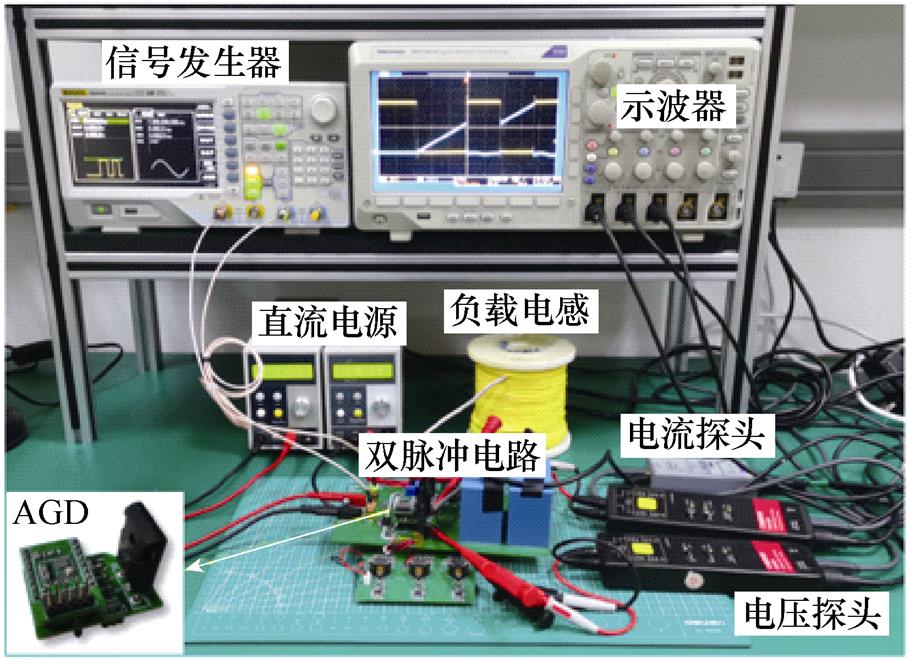

为验证所提AGD驱动电路的有效性,搭建了如图9所示的双脉冲实验平台,关键元器件和测试仪器的参数,见表5。

图8 所提AGD驱动电路及其双脉冲测试电路样机

Fig.8 Prototypes of proposed AGD gate driver and corresponding double-pulse test circuit

图9 所提AGD驱动电路样机及双脉冲实验平台

Fig.9 Prototype of proposed AGD drive circuit in double-pulse test rig

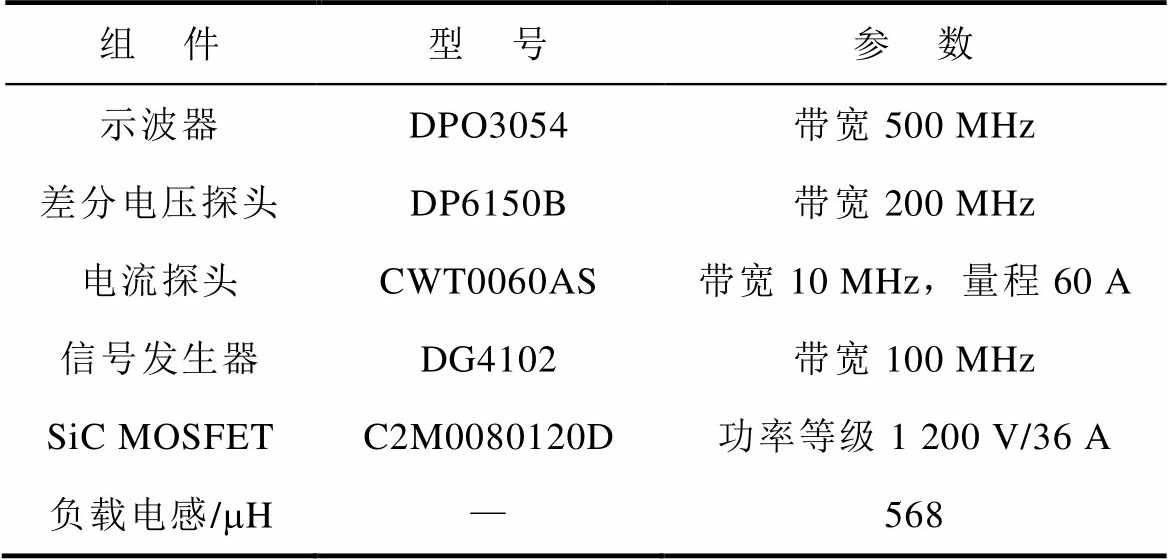

表5 双脉冲测试实验平台关键参数

Tab.5 Key parameters of double pulse test rig

组 件型 号参 数 示波器DPO3054带宽500 MHz 差分电压探头DP6150B带宽200 MHz 电流探头CWT0060AS带宽10 MHz,量程60 A 信号发生器DG4102带宽100 MHz SiC MOSFETC2M0080120D功率等级1 200 V/36 A 负载电感/mH—568

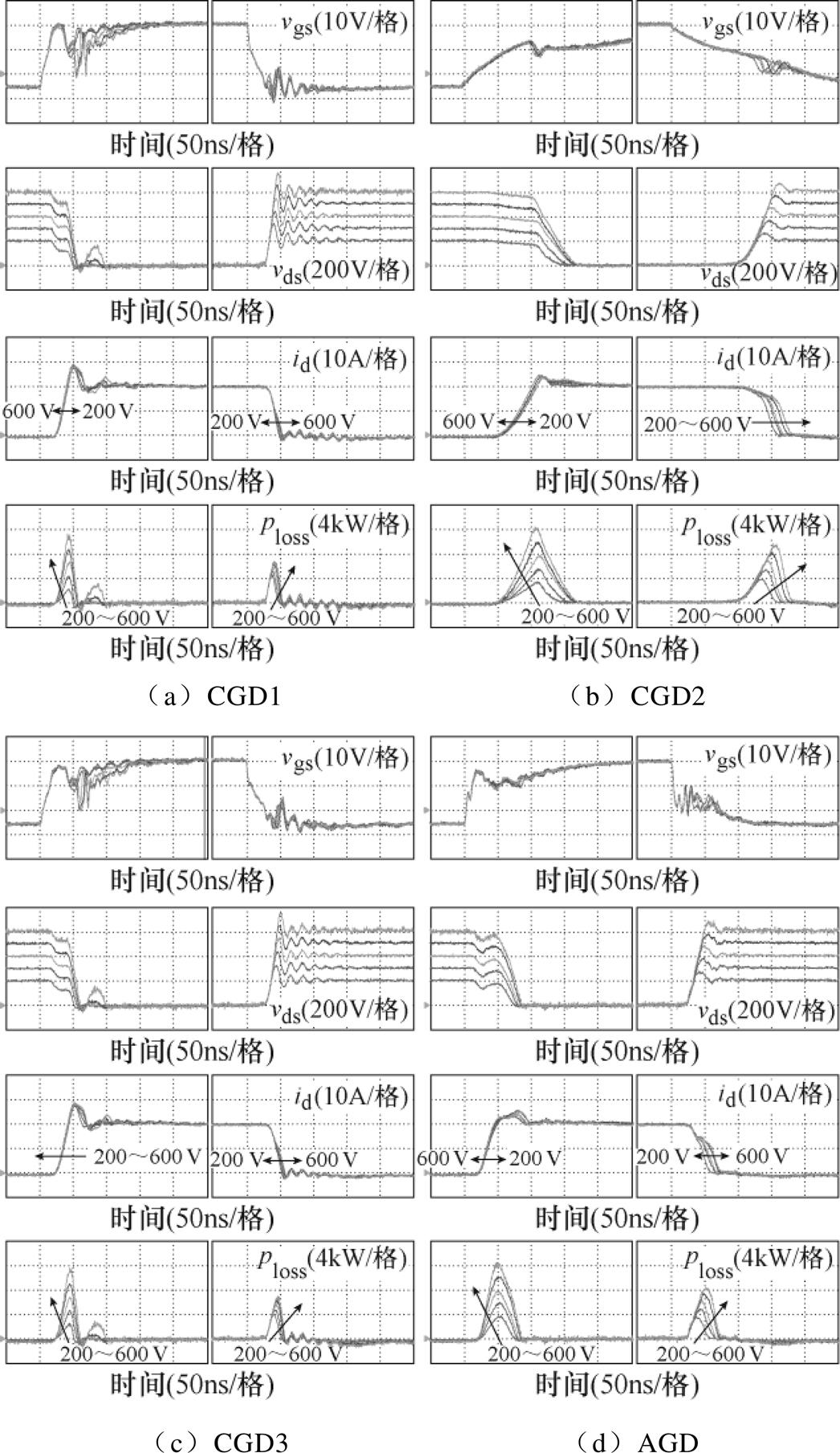

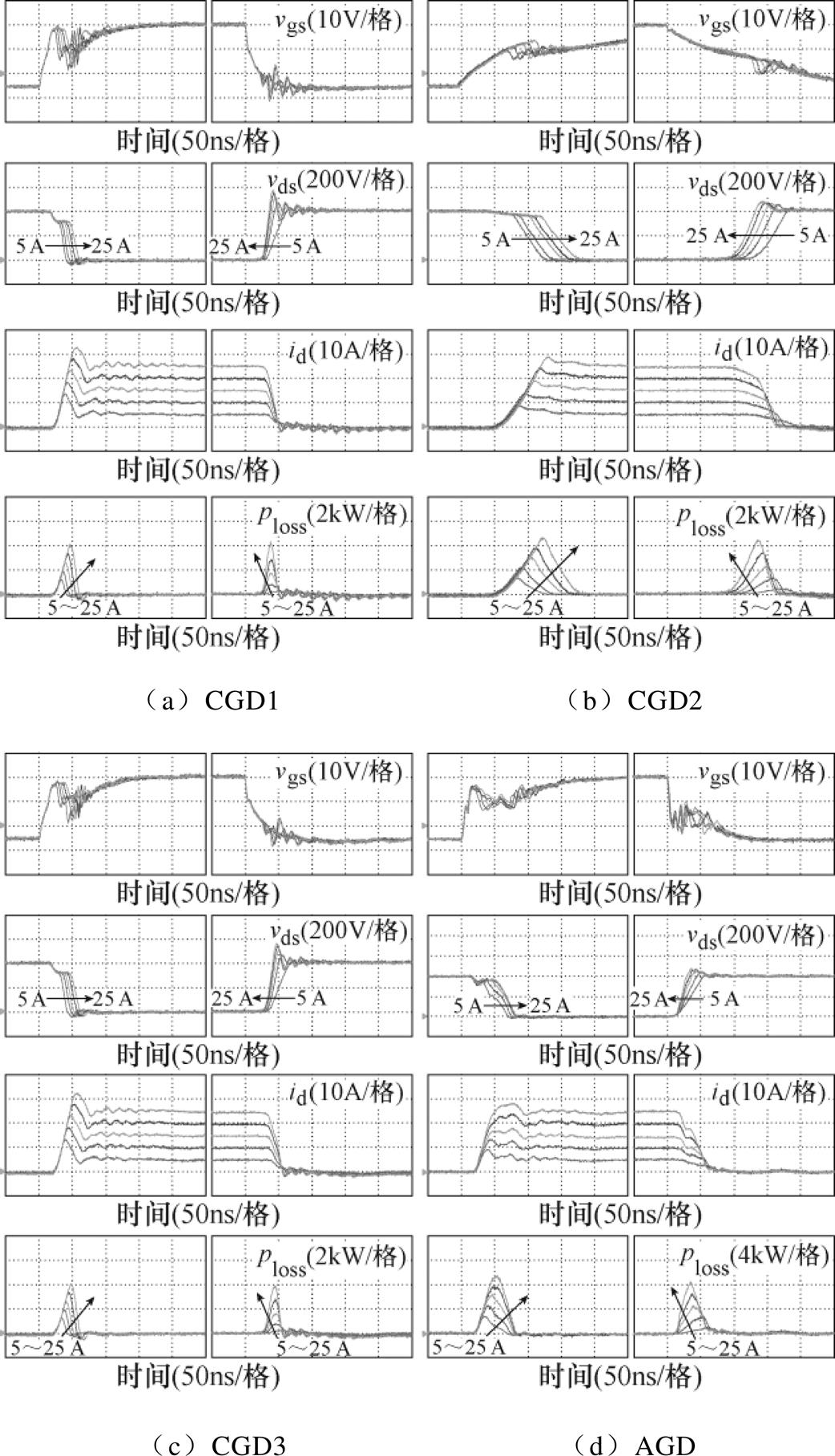

在直流母线电压600 V和负荷电流20 A的情况下,所提AGD驱动电路的实验结果如图10所示,与表4理论计算对应。可见,在器件开关轨迹的不同阶段,根据格雷码原理,每次投切一个栅极驱动电阻,控制栅极电流,调节SiC器件的栅-源电压,可以实现不同开关阶段独立控制,解决了开关轨迹多个目标的协同优化。

为了对比评估所提AGD驱动电路的实际效果,设置三种常规驱动(Conventional Gate Driver, CGD)作为对照组。其中,CGD1以提升开关速度为目标,采用较小的固定栅极电阻RG=5 W;CGD2以抑制开关振荡为目标,采用较大的固定栅极电阻RG=50 W;CGD3在开关速度和开关振荡之间寻求折中,根据式(14)按最优阻尼比x =0.707设计RG=7.5 W。各组CGD的驱动正压/负压均选择+20/-5 V。

图10 论文所提AGD驱动电路的实验结果

Fig.10 Experimental results of proposed AGD drive circuit

针对不同母线电压、负荷电流和串扰效应等工况条件,详细评测各种驱动电路的响应特性。

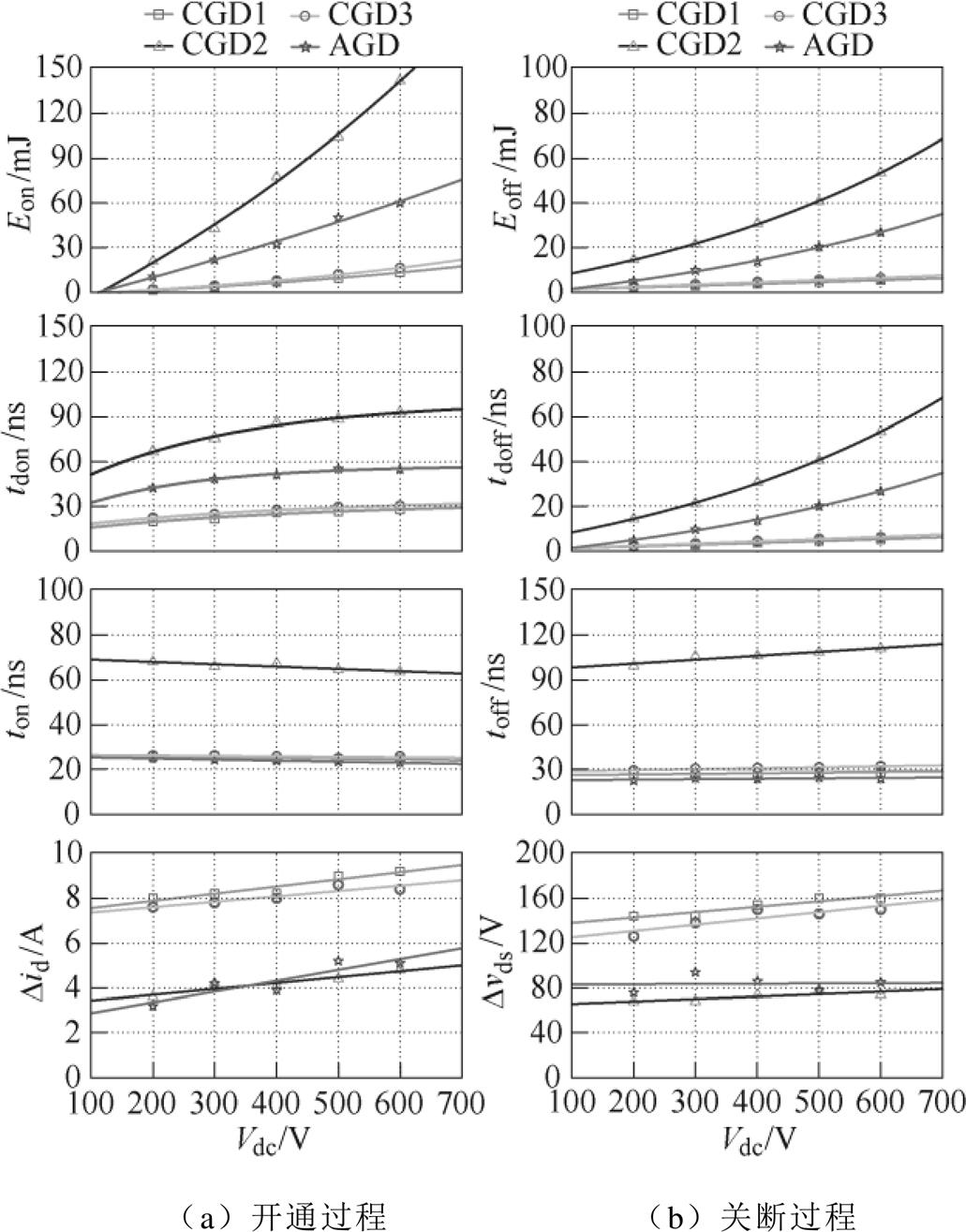

固定负载电流为20 A,在200~600 V范围内改变直流母线电压大小,测试各种驱动电路的控制效果,实验结果如图11所示。可见,增大驱动电阻,可以降低关断电压和开通电流的过冲,但是,降低了器件的开关速度,增加了器件的开关损耗。采用AGD驱动电路,能够有效优化器件的开关轨迹,在不牺牲开关速度的同时,有效抑制开关过冲和振荡。

图11 不同母线电压下各种驱动电路的开关轨迹实验结果

Fig.11 Experimental results of switching trajectories under different DC-link voltages by using studied gate drivers

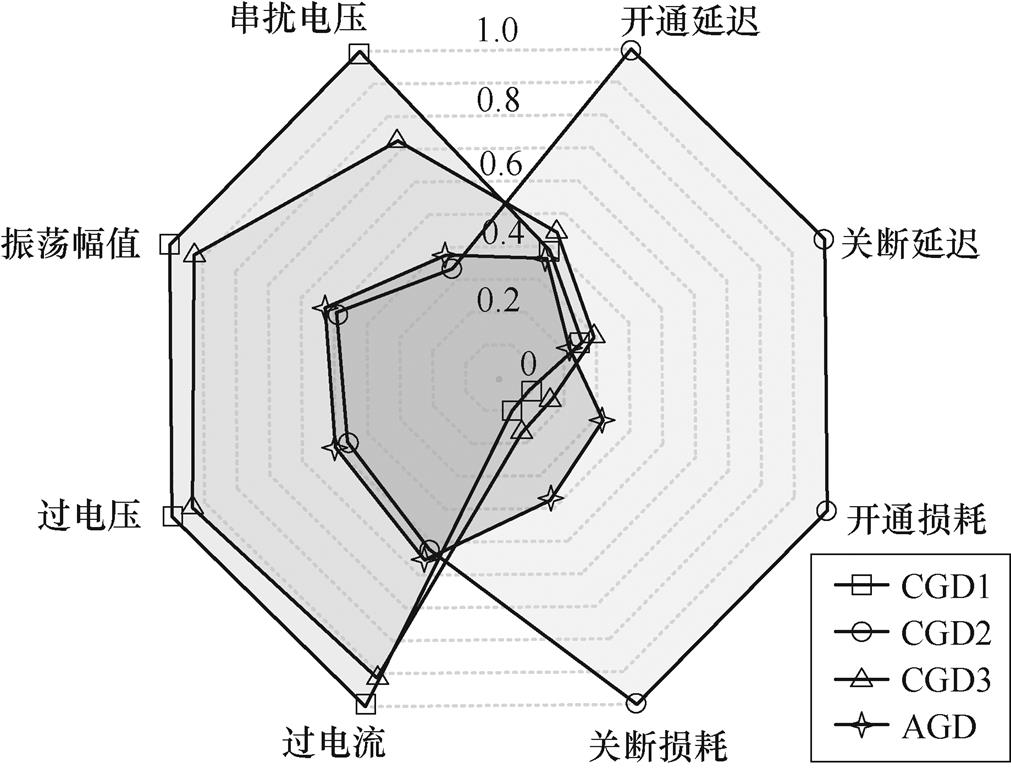

根据图11所示的实验结果,可以计算开关轨迹的开关损耗、延迟时间、电流上升/下降时间、电流/电压过冲等关键特征量,各种驱动电路的对比,如图12所示。可见,所提AGD能够有效降低开关过冲,同时不降低器件开关速度。将过电流和过电压应力转移到开关损耗中。相对于采用增大栅极电阻的驱动方法,所提AGD驱动能够实现各个性能指标之间的折中,提升开关轨迹调控的综合性能。

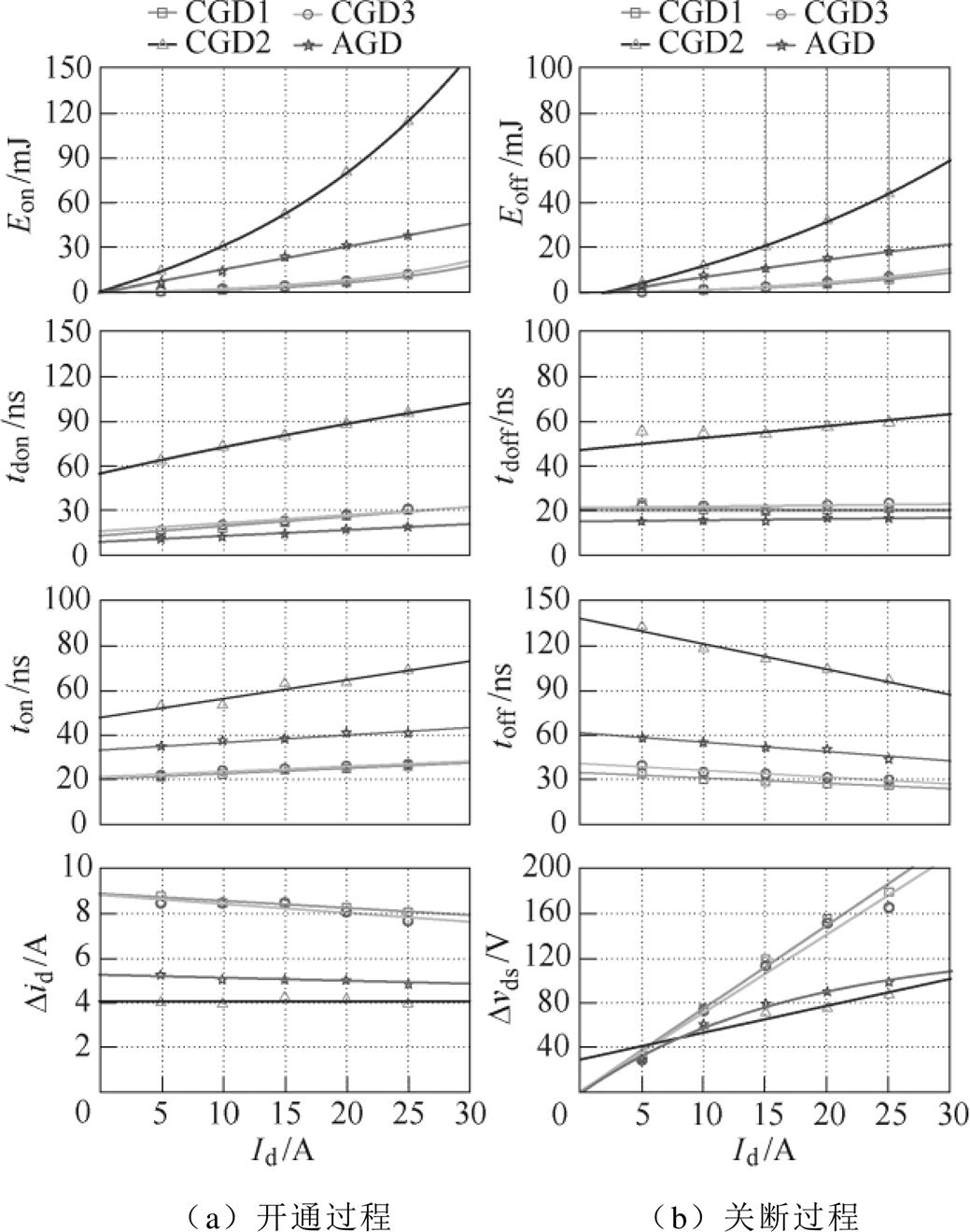

固定直流母线电压为400 V,在5~25 A范围内改变负载电流大小,测试各种驱动电路的控制效果,其实验结果如图13所示。可见,负荷电流越大,器件关断过程中的电流变化率越大,关断电压过冲越大。增大驱动电路的栅极电阻,可以降低器件的开关速度,降低开关电流/电压过冲。然而,会大幅增加器件的开关损耗。采用AGD驱动电路,能够在不牺牲开关速度的同时,抑制开关过冲。从vds、vgs的电压波形,可以发现,在开关过程中AGD的驱动电阻发生了有序变化,调控了器件不同开关阶段的性能。

根据图13的实验结果,可以得到开关轨迹的定量对比,如图14所示。AGD实现了对开关延迟、开关过冲、开关振荡和开关损耗的协同优化。在保证较短开关延迟情况下,抑制了开关过冲和开关振荡,同时将开关损耗保持在一个较低值。

图12 不同母线电压下开关轨迹的特征参量对比

Fig.12 Comparison of characteristic parameters of switching trajectories under different DC-link voltage

综上所述,对于三组典型的CGD驱动电路,CGD1采用较小的栅极电阻,开关延迟最短,损耗最小,但是开关过冲最大,且开关振荡最剧烈。CGD2采用较大的栅极电阻,开关过冲和振荡得到很好抑制,但是开关延迟最大,开关速度最慢,损耗最大。CGD3确保栅极回路的最优阻尼比,是CGD1和CGD2的一种折中,比CGD1略微降低了开关过冲,但却增加了开关损耗和开关延迟。可见,传统CGD改变固定栅极电阻下的优化,仅能优化开关轨迹各个特征量中的一个,改善某一特征量的同时,会严重牺牲其他特征量的性能;相反,AGD开关速度较快,开关延迟小于CGD1,具体最短的开关延迟;在与CGD1相近的开关速度下,AGD又能够较好地抑制开关过冲和开关振荡,其抑制效果接近CGD2;而具有与CGD2相近的过冲、振荡抑制能力的同时,AGD的开关损耗远小于CGD2。此外,当母线电压和负载电流在宽范围内变化时,所提AGD驱动均能实现对SiC MOSFET开关轨迹各特征参量的协同优化,具有较好的鲁棒性。

图13 不同负载电流下各种驱动电路的开关轨迹实验结果

Fig.13 Experimental results of switching trajectories under different load currents by using studied gate drivers

图14 不同负载电流下开关轨迹的特征参量对比

Fig.14 Comparison of characteristic parameters of switching trajectories under different load currents

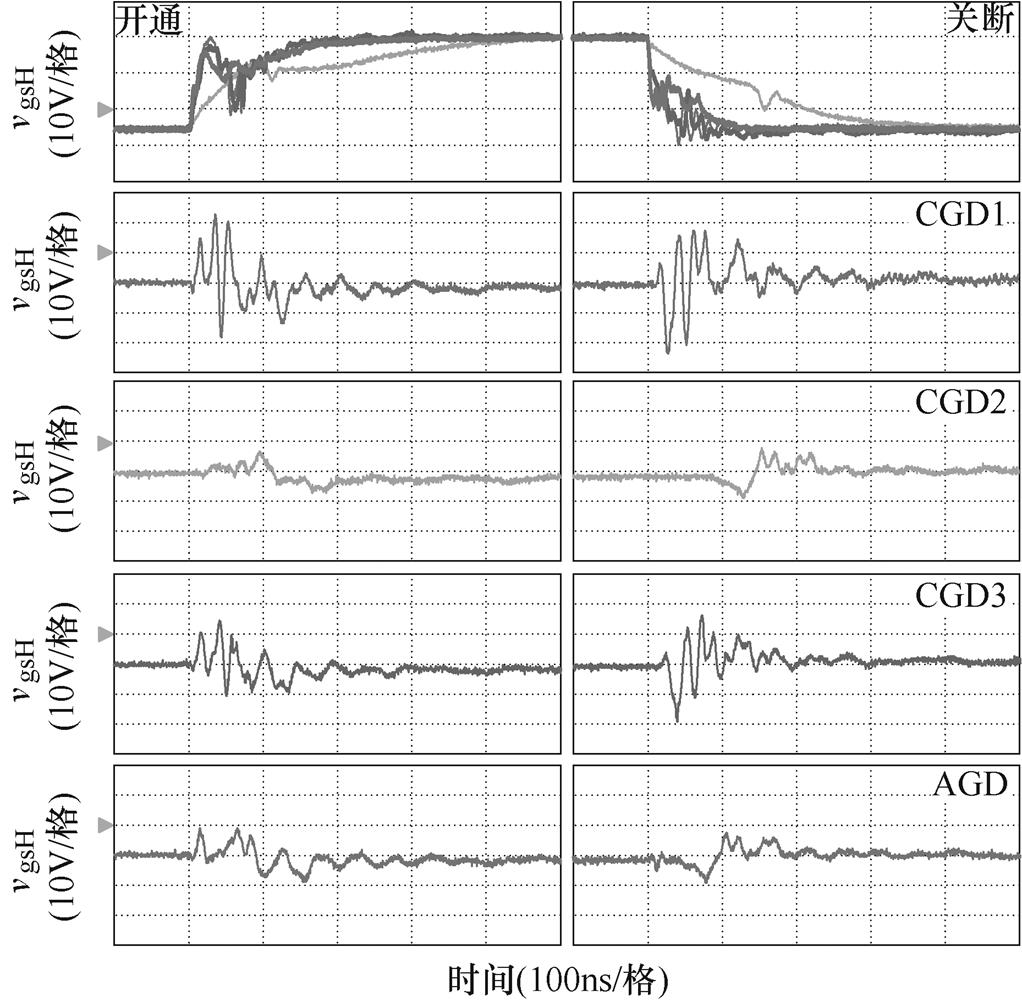

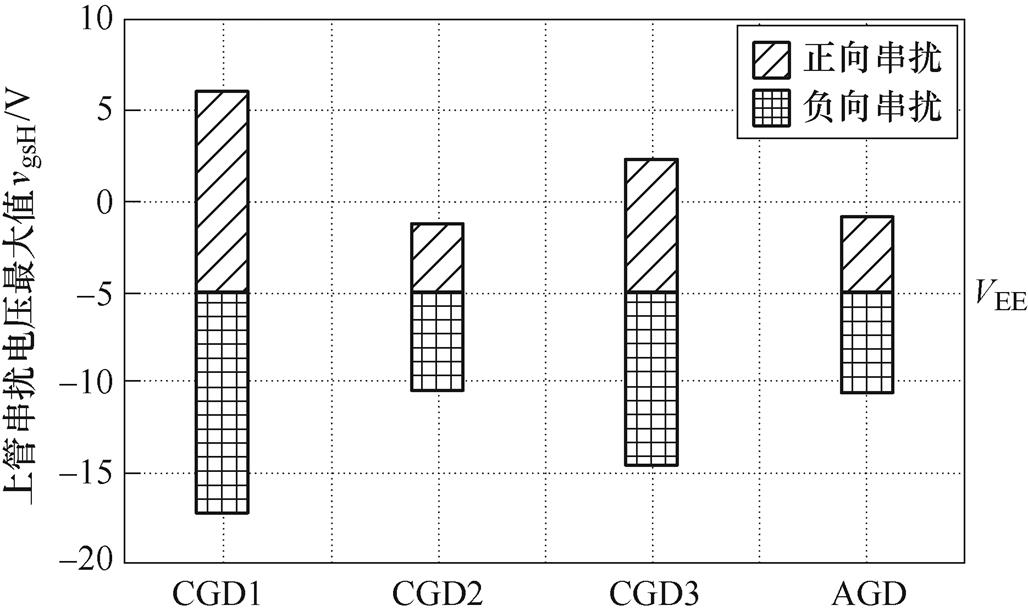

在母线电压600 V和负载电流20 A条件下,测试各种驱动电路的串扰效应,实验结果如图15所示,测试了AGD和三种典型CGD在开关过程中对上管栅极电压vgsH的串扰。

图15 600 V/20 A条件下各种驱动电路的串扰实验结果

Fig.15 Experimental crosstalk results under condition of 600 V/20 A by using different gate drivers

不同驱动在开关过程中的串扰波形如图15所示。根据以上实验波形,不同驱动的串扰电压统计如图16所示。

图16 600 V/20 A条件下不同驱动电路的串扰电压统计

Fig.16 Statistics on the crosstalk voltage of different driving circuits under the condition of 600 V/20 A

根据图15和图16实验结果所示,CGD1的串扰电压最大,正向和负向串扰峰值已超过SiC MOSFET器件的栅极安全电压,不仅可能造成器件误导通,还可能损坏器件;CGD2的串扰电压最小;CGD3只比CGD1有略微降低,但串扰峰值仍超过栅极安全电压;AGD对串扰有明显改善,对串扰电压的抑制效果接近CGD2。但是,结合实验1和实验2可知,CGD2虽然抑制了串扰,但其开通速度较慢,开关损耗较大;而AGD实现相近的串扰抑制效果的同时,保证了较快的开关速度和较低的开关损耗,所以AGD实现了其他特征参量和串扰的协同优化。

根据上述实验结果,以开关轨迹的特征量为参照,对比各种驱动电路的综合性能,如图17所示。可见,本文所提的AGD驱动电路,根据开关轨迹的不同阶段,独立控制栅极驱动电阻,实现对各个特征参量的解耦调控,实现开关轨迹各个特征量的协同优化以及开关性能的整体改善。

图17 不同驱动电路的综合评估结果

Fig.17 Comprehensive assessment of different gate drivers

驱动电路可以调控SiC器件的开关损耗、安全裕度和电磁干扰,提升变流器的电-热性能。然而,现有驱动电路难以平衡损耗、振荡、过冲、延迟、串扰之间的矛盾,无法实现多个开关轨迹的协同优化。本文通过建立驱动电阻对开关轨迹的分阶段定量模型,揭示了驱动电阻与各开关轨迹特征量之间的解耦规律,提出了一种四阶段变电阻的主动驱动电路及脉冲时序控制逻辑,采用大量实验结果,证明了所提模型和方法的可行性和有效性。可以得到以下结论。

1)SiC功率器件的开关轨迹可观、可控。开关轨迹关键特征量与驱动电阻之间的相互作用规律,可以定量描述,包括:开关损耗、开通电流过冲、关断电压过冲、开关振荡、开关延迟、串扰电压、电压变化率和电流变化率等。

2)SiC功率器件的开关轨迹特征量之间相互解耦。各个开关轨迹特征量独立影响器件开关行为,仅在器件开关过程中的某一特定阶段,独立发挥作用。因此,在开关过程的每一个阶段,动态地改变驱动电阻的大小,可以逐一地调节开关波形的特征量,实现开关轨迹的协同优化。

3)所提出的四阶段变电阻协同优化方法及其驱动电路,能够实现SiC器件开关轨迹多个特征量的协同调控,在保证器件较快开关速度、较低开关损耗的同时,有效抑制振荡过冲和串扰。

本文为SiC功率器件开关轨迹的协同优化,提出了有效的优化方法及技术方案。

参考文献

[1] 赵争鸣, 施博辰, 朱义诚. 对电力电子学的再认识:历史、现状及发展[J]. 电工技术学报, 2017, 32(12): 5-15.

Zhao Zhengming, Shi Bochen, Zhu Yicheng. Recon- sideration on power electronics: the past, present and future[J]. Transactions of China Electrotechnical Society, 2017, 32(12): 5-15.

[2] 王学梅. 宽禁带碳化硅功率器件在电动汽车中的研究与应用[J]. 中国电机工程学报, 2014, 34(3): 371- 379.

Wang Xuemei. Researches and applications of wide- bandgap SiC power devices in electric vehicles[J]. Proceedings of the CSEE, 2014, 34(3): 371-379.

[3] 曾正, 邵伟华, 胡博容, 等. SiC器件在光伏逆变器中的应用与挑战[J]. 中国电机工程学报, 2017, 37(1): 221-233.

Zeng Zheng, Shao Weihua, Hu Borong, et al. Chances and challenges of photovoltaic inverters with silicon carbide devices[J]. Proceedings of the CSEE, 2017, 37(1): 221-233.

[4] 梁美, 郑琼林, 可翀, 等. SiC MOSFET、Si CoolMOS和IGBT的特性对比及其在DAB变换器中的应用[J]. 电工技术学报, 2015, 30(12): 41-50.

Liang Mei, Trillion Q Zheng, Ke Chong, et al. Per- formance comparison of SiC MOSFET, Si CoolMOS and IGBT for DAB converter[J]. Transactions of China Electrotechnical Society, 2015, 30(12): 41-50.

[5] Wen Xuhui, Fan Tao, Ning Puqi, et al. Technical approaches towards ultra-high power density SiC inverter in electric vehicle applications[J]. CES Transactions on Electrical Machines and Systems, 2017, 1(3): 231- 237.

[6] Oswald N, Anthony P, McNeill N, et al. An experi- mental investigation of the tradeoff between switching losses and EMI generation with hard- switched all-Si, Si-SiC, and all-SiC device com- binations[J]. IEEE Transactions on Power Electronics, 2014, 29(5): 2393-2407.

[7] Yuan Xibo, Laird I, Walder S. Opportunities, challenges, and potential solutions in the application of fast-switching SiC power devices and converters[J]. IEEE Transactions on Power Electronics, 2021, 36(4): 3925-3945.

[8] Roy S K, Basu K. Analytical model to study hard turn-off switching dynamics of SiC MOSFET and Schottky diode pair[J]. IEEE Transactions on Power Electronics, 2021, 36(1): 861-875.

[9] Wang Xudong, Zhao Zhengning, Li Kai, et al. Analytical methodology for loss calculation of SiC MOSFETs[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2019, 7(1): 71-83.

[10] Qian Cheng, Wang Zhiqiang, Xin Guoqing, et al. Datasheet driven switching loss, turn-on/off over- voltage, di/dt and dv/dt prediction method for SiC MOSFET[J]. IEEE Transactions on Power Electronics, 2022, 37(8): 9551-9570.

[11] Wang Ning, Zhang Jianzhong. Nonlinear capacitance model of SiC MOSFET considering envelope of switching trajectory[J]. IEEE Transactions on Power Electronics, 2022, 37(7): 7977-7988.

[12] Stark R, Tsibizov A, Nain N, et al. Accuracy of three interterminal capacitance models for SiC power MOSFETs under fast switching[J]. IEEE Transactions on Power Electronics, 2021, 36(8): 9398-9410.

[13] Chen Kainan, Zhao Zhengming, Yuan Liqiang, et al. The impact of nonlinear junction capacitance on switching transient and its modeling for SiC MOSFET[J]. IEEE Transactions on Electron Devices, 2015, 62(2): 333-338.

[14] Fritz N, Engelmann G, Stippich A, et al. Toward an in-depth understanding of the commutation processes in a SiC MOSFET switching cell including parasitic elements[J]. IEEE Transactions on Industry Appli- cations, 2020, 56(4): 4089-4101.

[15] Noppakunkajorn J, Han Di, Sarlioglu B. Analysis of high-speed PCB with SiC devices by investigating turn-off overvoltage and interconnection inductance influence[J]. IEEE Transactions on Transportation Electrification, 2015, 1(2): 118-125.

[16] Rashid A U, Hossain M M, Emon A I, et al. Datasheet-driven compact model of silicon carbide power MOSFET including third-quadrant behavior[J]. IEEE Transactions on Power Electronics, 2021, 36(10): 11748-11762.

[17] Sun Jianning, Yuan Liqiang, Duan Renzhi, et al. A semiphysical semibehavioral analytical model for switching transient process of SiC MOSFET module[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2021, 9(2): 2258-2270.

[18] Wu Yingzhe, Yin Shan, Li Hui, et al. Impact of RC snubber on switching oscillation damping of SiC MOSFET with analytical model[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 163-178.

[19] Chen Jian, Luo Quanming, Huang Jian, et al. Analysis and design of an RC Snubber circuit to suppress false triggering oscillation for GaN devices in half-bridge circuits[J]. IEEE Transactions on Power Electronics, 2020, 35(3): 2690-2704.

[20] Haider M, Fuchs S, Zulauf G, et al. Analytical loss model for three-phase 1200V SiC MOSFET inverter drive system utilizing miller capacitor-based dv/dt- limitation[J]. IEEE Open Journal of Power Electro- nics, 2022, 3: 93-104.

[21] Miryala V K, Pandey V, Hatua K, et al. Layout inductance assisted novel turn-on switching loss recovery technique for SiC MOSFETs[J]. IEEE Journal of Emerging and Selected Topics in Industrial Electronics, 2021, 2(4): 513-525.

[22] Kim J, Shin D, Sul S K. A damping scheme for switching ringing of full SiC MOSFET by air core PCB circuit[J]. IEEE Transactions on Power Elec- tronics, 2018, 33(6): 4605-4615.

[23] Yatsugi K, Oishi K, Iizuka H. Ringing suppression of SiC MOSFET using a strongly coupled external resonator through analogy with passive PT- symmetry[J]. IEEE Transactions on Power Elec- tronics, 2021, 36(3): 2964-2970.

[24] Fiori F. On the use of magnetically coupled resonant snubbers to mitigate the electromagnetic emission of power switching circuits[J]. IEEE Transactions on Electromagnetic Compatibility, 2022, 64(1): 259-262.

[25] Wang Zhiqiang, Shi Xiaojie, Tolbert L M, et al. A di/dt feedback-based active gate driver for smart switching and fast overcurrent protection of IGBT modules[J]. IEEE Transactions on Power Electronics, 2014, 29(7): 3720-3732.

[26] 曾正, 邵伟华, 陈昊, 等. 基于栅极驱动回路的SiC MOSFET开关行为调控[J]. 中国电机工程学报, 2018, 38(4): 1165-1176, 1294.

Zeng Zheng, Shao Weihua, Chen Hao, et al. On-off behavior control of SiC MOSFET by gate drive loops[J]. Proceedings of the CSEE, 2018, 38(4): 1165-1176, 1294.

[27] 邵天骢, 郑琼林, 李志君, 等. 基于干扰动态响应机理的SiC MOSFET驱动设计[J]. 电工技术学报, 2021, 36(20): 4204-4214.

Shao Tiancong, Zheng Trillion Q, Li Zhijun, et al. SiC MOSFET gate driver design based on inter- ference dynamic response mechanism[J]. Transa- ctions of China Electrotechnical Society, 2021, 36(20): 4204-4214.

[28] 王宁, 张建忠. 基于开关轨迹优化的SiC MOSFET有源驱动电路研究综述[J]. 电工技术学报, 2022, 37(10): 2523-2537.

Wang Ning, Zhang Jianzhong. Review of active gate driver for SiC MOSFET with switching trajectory optimization[J]. Transactions of China Electro- technical Society, 2022, 37(10): 2523-2537.

[29] 凌亚涛, 赵争鸣, 姬世奇. 基于主动栅极驱动的IGBT开关特性自调节控制[J]. 电工技术学报, 2021, 36(12): 2482-2494.

Ling Yatao, Zhao Zhengming, Ji Shiqi. Self- regulating control of IGBT switching characteristics with active gate drive[J]. Transactions of China Electrotechnical Society, 2021, 36(12): 2482-2494.

[30] 李辉, 黄樟坚, 廖兴林, 等. 一种抑制SiC MOSFET桥臂串扰的改进门极驱动设计[J]. 电工技术学报, 2019, 34(2): 275-285.

Li Hui, Huang Zhangjian, Liao Xinglin, et al. An improved SiC MOSFET gate driver design for cross- talk suppression in a phase-leg configuration[J]. Transactions of China Electrotechnical Society, 2019, 34(2): 275-285.

[31] Lobsiger Y, Kolar J W. Closed-loop di/dt and dv/dt IGBT gate driver[J]. IEEE Transactions on Power Electronics, 2015, 30(6): 3402-3417.

[32] Zhao Shuang, Zhao Xingchen, Wei Yuqi, et al. A review of switching slew rate control for silicon carbide devices using active gate drivers[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2021, 9(4): 4096-4114.

[33] Zhao Shuang, Dearien A, Wu Yuheng, et al. Adaptive multi-level active gate drivers for SiC power devices[J]. IEEE Transactions on Power Electronics, 2020, 35(2): 1882-1898.

[34] Zhao Shuang, Zhao Xingchen, Dearien A, et al. An intelligent versatile model-based trajectory optimized active gate driver for silicon carbide devices[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 429-441.

[35] Sukhatme Y, Miryala V K, Ganesan P, et al. Digitally controlled gate current source-based active gate driver for silicon carbide MOSFETs[J]. IEEE Transactions on Industrial Electronics, 2020, 67(12): 10121-10133.

[36] 冯超, 李虹, 蒋艳锋, 等. 抑制瞬态电压电流尖峰和振荡的电流注入型SiC MOSFET有源驱动方法研究[J]. 中国电机工程学报, 2019, 39(19): 5666-5673, 5894.

Feng Chao, Li Hong, Jiang Yanfeng, et al. Research on current injection active drive method of SiC MOSFET with transient voltage and current spike and oscillation suppression[J]. Proceedings of the CSEE, 2019, 39(19): 5666-5673, 5894.

[37] Camacho A P, Sala V, Ghorbani H, et al. A novel active gate driver for improving SiC MOSFET switching trajectory[J]. IEEE Transactions on Industrial Electronics, 2017, 64(11): 9032-9042.

[38] Nayak P, Hatua K. Active gate driving technique for a 1200V SiC MOSFET to minimize detrimental effects of parasitic inductance in the converter Layout[J]. IEEE Transactions on Industry Applications, 2018, 54(2): 1622-1633.

[39] Engelmann G. Experimental investigation on the transient switching behavior of SiC MOSFETs using a stage-wise gate driver[J]. CPSS Transactions on Power Electronics and Applications, 2018, 3(1): 77-87.

Abstract Compared to Si counterparts, the faster switching speed of the SiC device brings lower switching losses. However, the higher dv/dt and di/dt also make it suffer from serious switching issues such as overshoot, oscillation, and crosstalk, which greatly limits the electro-thermal margin of the SiC device.Therefore, the switching trajectory of the SiC device needs to be optimized to achieve the coordinated optimization of switching losses and EMI. Besides, the parameters of the conventional gate driver (CGD) and snubber circuit are fixed, which fails to simultaneously manage all switching issues. The active gate driver (AGD) can regulate the switching trajectory. However, existing methods generally optimize a single switching parameter, unable to achieve overall improvement and coordination of the switching performance. Thus, this paper models the characteristic parameters of switching trajectories in stages and proposes a stage-by-stage coordinated optimization strategy. In addition, a four-stage variable resistance AGD is implemented to realize the coordinated optimization of each characteristic parameter.

Firstly, to evaluate the switching trajectory of the SiC device, six sets of key switching trajectory characteristic parameters, including switching loss, overshoot, oscillation, crosstalk, slew rates of voltage and current, and switching delay, are employed to reveal the regulation of the gate resistance on the switching trajectory.Secondly, based on the four-stage switching model of the SiC device and the regulation rule of the gate resistance, the optimal gate resistance of each stage is quantitatively designed with the constraint of the damping ratio of the gate loop. Thirdly, a four-stage variable resistance AGD circuit with timing control logic based on the Gray code is proposed to switch the gate resistance in each stage, thus realizing the regulation of switching trajectory.Finally, three groups of typical CGDs are adopted as control groups. According to the comparative experimental results, it is proved that the proposed method and the AGD circuit are competent in realizing the coordinated optimization of multiple characteristic parameters of the switching trajectory of the SiC device.

The comparative experiments under different bus voltages and different load currents present that the CGD1 with smaller resistance brings the most severe switching oscillation and crosstalk, along with the largest switching overshoot; The CGD2 with a larger resistance produces the largest switching delay and switching losses, alongside the slowest switching speed; The CGD3 designed with the optimal damping ratio of the gate loop is a trade-off between CGD1 and CGD2. Compared with CGD1, the switching overshoot and crosstalk are slightly reduced. However, the switching loss and switching delay are significantly increased. It can be seen that the optimization under the CGD with fixed gate resistance will inevitably deteriorate the performance of other characteristic parameters while improving one. On the contrary, the proposed AGD presents the shortest switching delay and the fastest switching speed as CGD1, while ensuring the similar suppression effect of switching overshoot, oscillation, and crosstalk as CGD2. In addition, the coordinated optimization of multiple characteristic parameters of the switching trajectory of the SiC device is implemented.

The following conclusions can be drawn from this paper: (1) The switching trajectory of the SiC device is observable and controllable. (2) The characteristic parameters of the switching trajectory can be regulated in stages to achieve coordinated optimization. (3) The proposed four-stage variable resistance co-optimization method and the AGD circuit can realize the coordinated regulation of multiple characteristic parameters of the switching trajectory, which can effectively suppress the oscillation, overshoot, and crosstalk of the SiC device while ensuring the faster switching speed and lower switching loss.

keywords:SiC MOSFET device, active gate driver, four-phase varied gate resistance, switching trajectory regulation, multi-objective coordination

DOI: 10.19595/j.cnki.1000-6753.tces.221116

中图分类号:TM464

国家自然科学基金项目(52177169)、重庆市基础研究与前沿探索项目(cstc2021zdyjA0035)和重庆市研究生科研创新项目(CYS22023)资助。

收稿日期 2022-06-14

改稿日期 2022-09-21

邹铭锐 男,1996年生,博士研究生,研究方向为新型电力电子器件封装集成与应用。E-mail: 928154685@qq.com

曾 正 男,1986年生,博士,教授,研究方向为新型电力电子器件封装集成与应用。E-mail: zengerzheng@126.com(通信作者)

(编辑 陈 诚)