图1 压接型IGBT器件内部结构[6]

Fig.1 The internal structure of press pack IGBT device[6]

摘要 压接型IGBT器件内部多颗芯片的并联连接是提高其电流等级的重要手段。然而,IGBT芯片之间的瞬态电流不均衡是限制其电流提升的主要原因之一。研究压接型IGBT器件内部的瞬态电流分布规律对于规模化IGBT并联封装设计具有重要意义。该文首先通过有限元软件提取了压接型IGBT器件内部的栅极、集电极和发射极的杂散电感,得到三个杂散电感随IGBT芯片不同位置的变化规律;其次对三个杂散电感差异下的电流分布进行了理论分析,发现电流分布主要受到功率回路和驱动回路的公共支路上杂散电感的影响;同时分别对开通和关断过程中IGBT芯片内部的载流子变化过程进行分析,发现发射极杂散电感差异主要影响开通过程的电流不均衡;然后针对三个杂散电感差异分别进行电路仿真,得到杂散电感差异对电流分布的影响规律,仿真结果验证了理论分析的有效性;最后建立了两芯片的并联均流双脉冲实验平台,平台能够调节两支路之间的杂散电感差异,实验结果进一步验证了该文理论分析的有效性。

关键词:压接型IGBT器件 瞬态均流 功率回路 驱动回路 杂散电感

绝缘栅双极型晶体管(Insulated Gate Bipolar Transistor, IGBT)自20世纪80年代被发明以来,经过几十年的发展,已经成为主流功率半导体器件,在电力变换领域占据了非常重要的地位[1-2]。

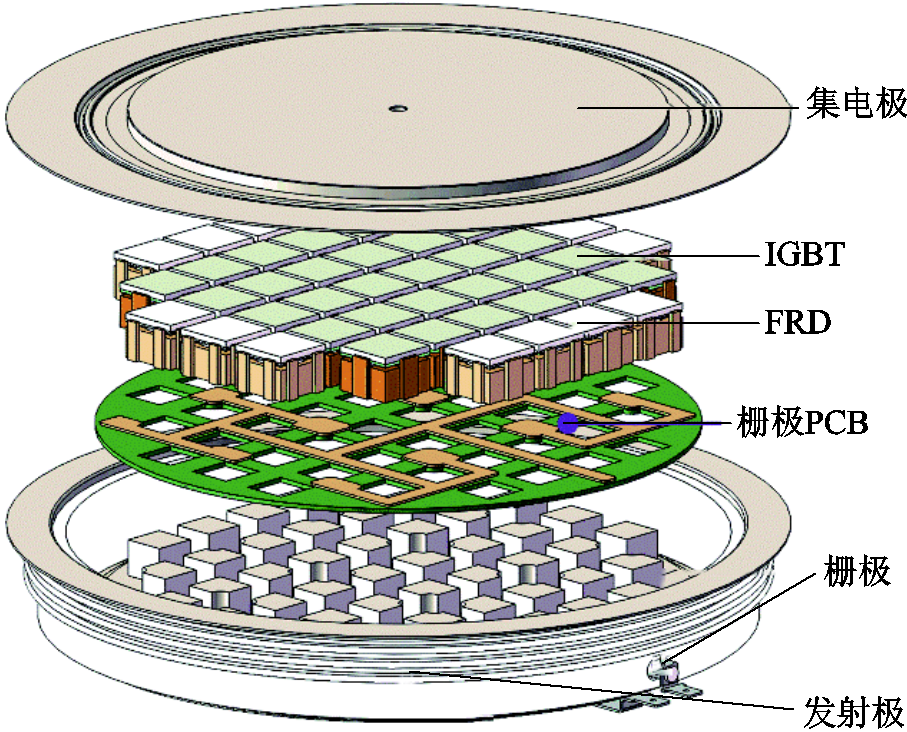

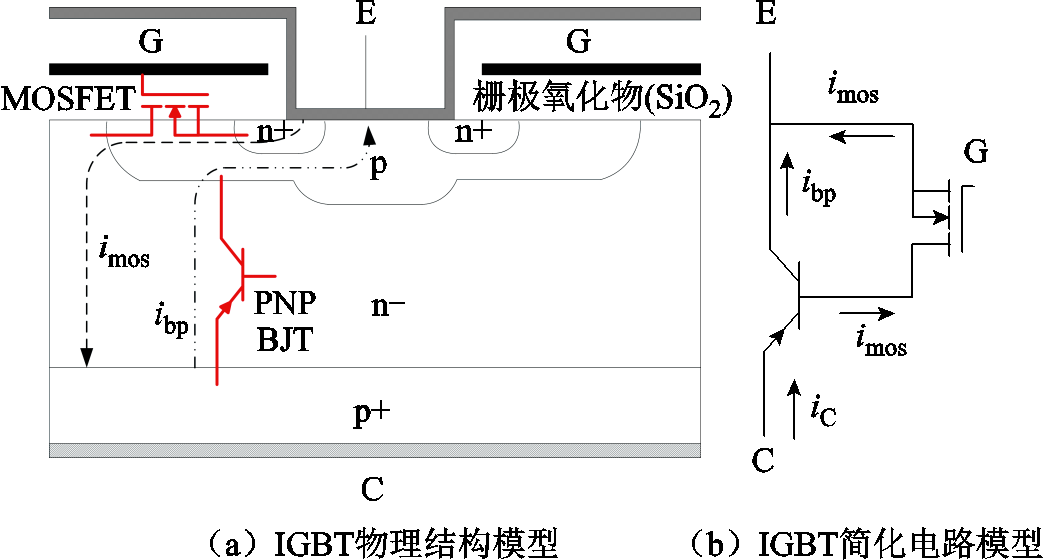

相比于传统的焊接型IGBT模块,压接型IGBT器件(Press-Pack IGBT, PPI)依靠机械压力将内部IGBT芯片并联连接在一起,取消了焊接IGBT模块中常用的绑定线连接,使之具有双面散热、失效短路等优点,已经在高压大功率领域得到了广泛的应用[3-4]。虽然压接型IGBT器件有许多优点,但同时也面临诸多挑战[5],由于压接型IGBT器件电流等级的增大,其内部需要大量的IGBT芯片并联使用,以图1所示的3.3 kV/1 500 A压接型IGBT器件[6]为例,其内部含有30颗IGBT芯片及14颗快恢复二极管(Fast Recovery Diode, FRD)芯片。由于IGBT芯片间参数的差异以及器件封装参数的差异,会导致芯片间出现电流不均衡现象,从而限制了器件的安全可靠运行,因此研究压接型IGBT器件内部的并联均流问题具有重要的学术意义。

图1 压接型IGBT器件内部结构[6]

Fig.1 The internal structure of press pack IGBT device[6]

关于压接型IGBT器件内部的芯片间并联均流问题,自其诞生以来已有很多学者进行了大量的研究。此问题分为稳态均流和瞬态均流[7]。稳态均流是指器件工作于直流或低频条件下,IGBT芯片之间的电流分布特性,主要受到芯片通态压降及封装接触电阻的影响。国内外学者通过电-热-力多物理场耦合计算得到了器件内部电-热-力的分布规律[8-10]。这些研究成果对于改善稳态电流不均衡具有很好的指导作用。相比于稳态均流,瞬态均流更加复杂,它是指器件在开通/关断时,电流快速变化过程中IGBT芯片之间的电流分布特性。其不仅受到芯片参数如阈值电压、跨导的影响,同时受到封装杂散电感的影响[11]。早期的学者和器件厂家针对IGBT芯片参数的分散性提出了筛选的指标和方法[12]。由于硅基工艺的提升,IGBT芯片参数差异能够得到很好的控制[2]。现有的研究多关注于封装杂散电感,研究方法大多是通过有限元软件提取器件的封装杂散电感,结合IGBT芯片模型在电路仿真中得到器件内部的电流分布特性[13-14]。但是,由于IGBT芯片建模过程非常复杂,现有研究通常不考虑IGBT芯片内部的半导体物理模型,仅考虑IGBT外部的电气行为,采用经过简化的IGBT行为模型。然而IGBT作为双极性器件,内部有两种载流子参与电流输运[15-17],行为模型并不能很好地反映IGBT芯片之间的瞬态均流特性。同时现有的仿真结果大多也缺乏实验的验证,使得结论缺乏足够的说服力。

此外,在之前的研究中,通常仅考虑功率回路杂散电感对IGBT瞬态均流特性的影响,实际上IGBT作为电压驱动型器件,IGBT芯片的电流直接受到驱动电压的控制[18],不同驱动回路上的杂散电感差异会影响驱动电压的大小,很可能影响到IGBT瞬态均流特性。然而现有文献对驱动回路杂散参数缺乏理论和实验的研究。

考虑到现有研究的不足,本文通过理论和实验两方面研究了IGBT瞬态均流特性的影响因素和作用机理。首先对压接型IGBT器件内部的三个杂散电感进行了提取,得到了不同IGBT芯片位置下杂散参数的差异;其次对三个杂散电感差异下的电流分布进行了理论分析,得到了电流不均衡主要受到功率回路和驱动回路的公共支路上发射极杂散电感的影响,同时对IGBT内部的载流子行为进行分析,发现发射极杂散电感差异主要影响开通过程的电流不均衡;然后在仿真软件中建立了包含封装杂散电感和考虑内部物理特性的IGBT芯片一体化仿真电路,对各个杂散电感差异进行了仿真计算,得到了各个杂散电感差异对电流分布的影响规律;最后通过建立双芯片并联的双脉冲实验平台,进一步验证了理论分析和仿真结果的有效性。

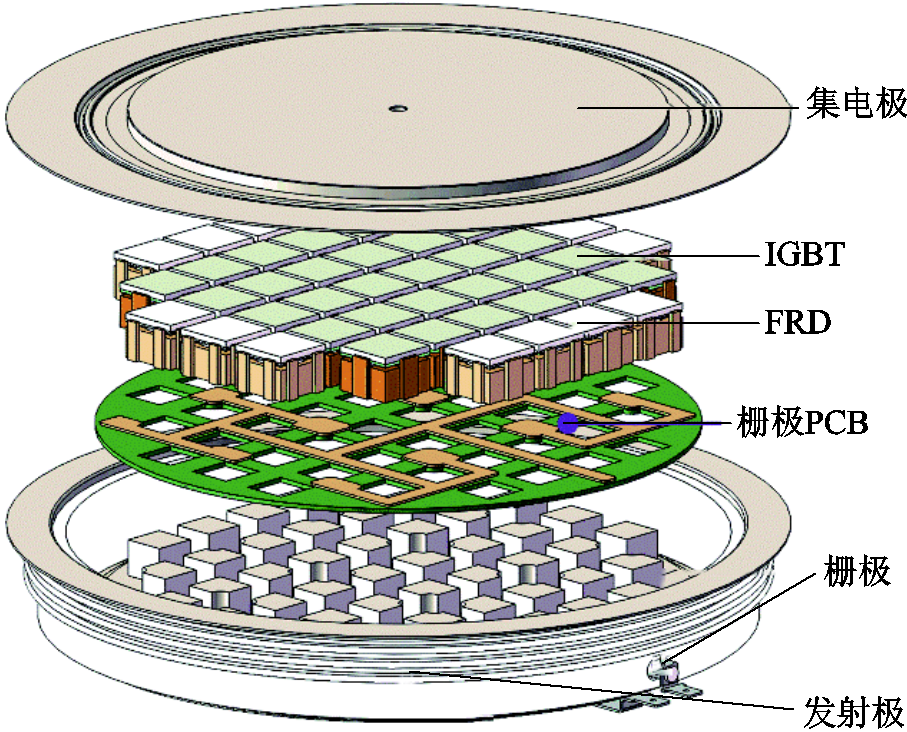

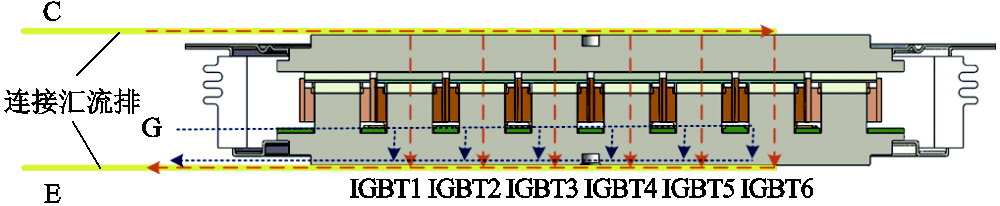

IGBT器件通常需要通过汇流排与外电路进行连接[6]。本文针对图2所示的压接型IGBT器件侧面连接汇流排的典型方式,并考虑连接汇流排对器件内部杂散电感的作用,研究瞬态电流分布的影响规律。器件内部包含两个电流路径,一个为功率回路,如图2中长虚线所示;另一个为驱动回路,如图2中点虚线所示。图2所示的截面中六个IGBT的等效电路如图3所示。图中LCn1(n=1, 2,…,6)为集电极极板的杂散电感,LCn2为集电极汇流排的杂散电感,两者之和为集电极杂散电感LCn;LGn为栅极杂散电感;LEn1为发射极极板的杂散电感,LEn2为发射极汇流排的杂散电感,两者之和为发射极杂散电感LEn。

图2 压接型IGBT器件截面图

Fig.2 Sectional view of press pack IGBT device

图3 压接型IGBT器件截面等效电路

Fig.3 The equivalent circuit of press pack IGBT devices

首先需要考虑功率回路上的杂散参数的差异,由于电流从连接汇流排的侧面流入和流出,不同位置的IGBT将有不同的杂散电感。功率回路包含集电极杂散电感和发射极杂散电感,观察图3,由于集电极杂散电感和发射极杂散电感具有一定的对称性,故以发射极杂散电感为例进行说明。

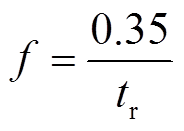

采用有限元软件提取IGBT发射极不同路径下的杂散电感。为了便于分析,以图4中压接型IGBT器件内的六个典型位置为例进行说明。参数提取时,在有限元软件中设置六个凸台表面为源点,连接汇流排引出端子为汇集点。杂散电感提取等效频率为

(1)

(1)

式中,tr为电流上升时间。因压接型IGBT芯片的瞬态电流上升时间tr为200~400 ns,因此可设定提取杂散电感的频率约为1 MHz。可得到不同位置的发射极杂散电感见表1,表中最大路径和最小路径杂散电感之间相差15.36 nH,变化率为43.43%。可以看出,在不同位置下,发射极杂散电感存在较大的差异,因此需要研究压接型IGBT器件内部功率回路杂散电感差异对并联均流特性的影响。

图4 发射极杂散电感提取模型

Fig.4 Emitter stray inductance extraction model

表1 不同位置下发射极杂散电感

Tab.1 Emitter stray inductances of different positions

位置IGBT1IGBT2IGBT3IGBT4IGBT5IGBT6 LE/nH35.3638.2741.5044.4647.7150.72

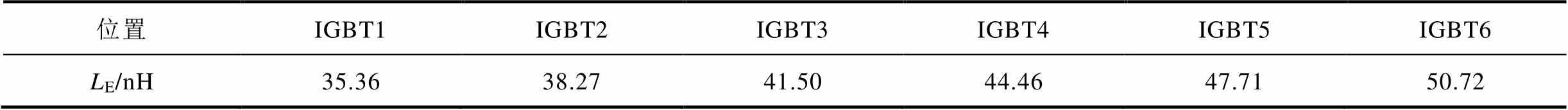

观察图3,驱动回路的杂散电感包含栅极杂散电感和发射极杂散电感。发射极杂散电感已在1.2节中进行了分析,下面考虑栅极杂散电感的差异,即图3中的IGBT杂散电感LG。目前压接型IGBT器件通常采用印制电路板(Printed Circuit Board, PCB)的连接形式,两种典型的驱动PCB布局如图5所示。

图5 两种典型的驱动PCB布局

Fig.5 The two typical driver PCB layouts

图5a的驱动路径为非对称结构(布局1),图5b的驱动路径为对称结构(布局2)。选取图中对应位置,通过有限元仿真软件提取栅极杂散电感,结果见表2。

布局1中的栅极杂散电感最大值与最小值相差27.57 nH,变化率为88.48%;布局2中的最大值与最小值相差8.84 nH,变化率为11.22%。采用布局2能够做到相对的对称,尽可能地保证了驱动侧杂散电感的一致性,但也存在一定的差异,因此需要研究栅极电感差异对瞬态均流特性的影响。

表2 不同位置下栅极杂散电感

Tab.2 Gate stray inductances of different positions

布局方式LG/nH IGBT1IGBT2IGBT3IGBT4IGBT5IGBT6 布局131.1630.3142.6042.6058.3758.73 布局278.7481.8982.5782.2383.6687.58

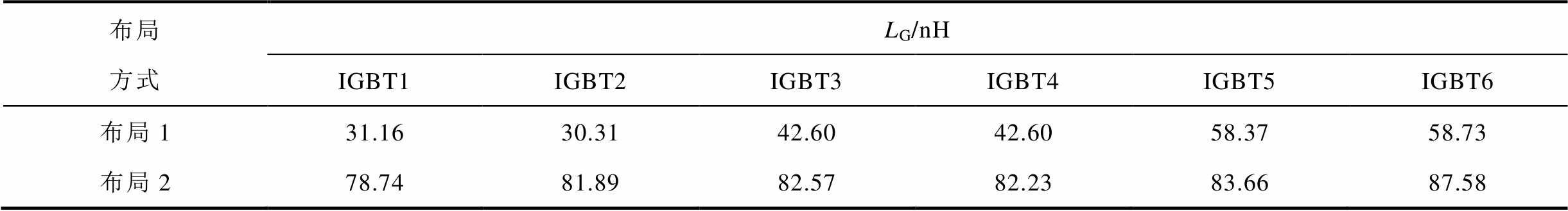

从第1节分析可知,压接型IGBT器件内部杂散电感差异主要分为集电极杂散电感差异ΔLC、发射极杂散电感差异ΔLE和栅极杂散电感差异ΔLG。下面将分析三个杂散电感差异对于电流分布 的影响。

的影响。

(2)

(2)

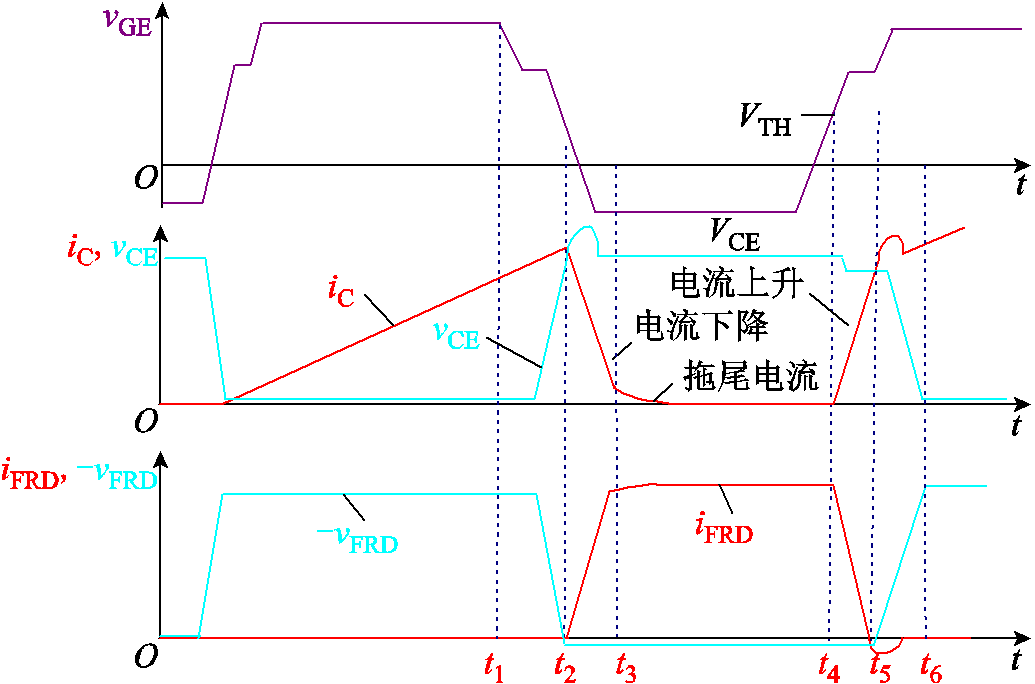

双脉冲波形示意图如图6所示,展示了IGBT和FRD电压、电流变化的详细过程。图中vGE为IGBT的栅极电压,vCE为IGBT的集射极电压,iC为IGBT的集电极电流;−vFRD为FRD上的反向电压,iFRD为FRD的正向电流。

图6 双脉冲波形示意图

Fig.6 Schematic diagram of double pulse waveforms

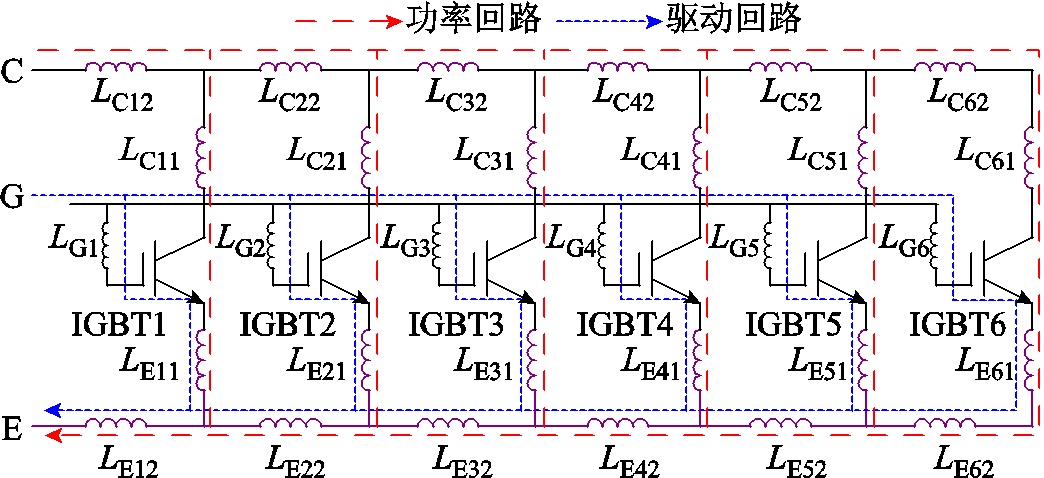

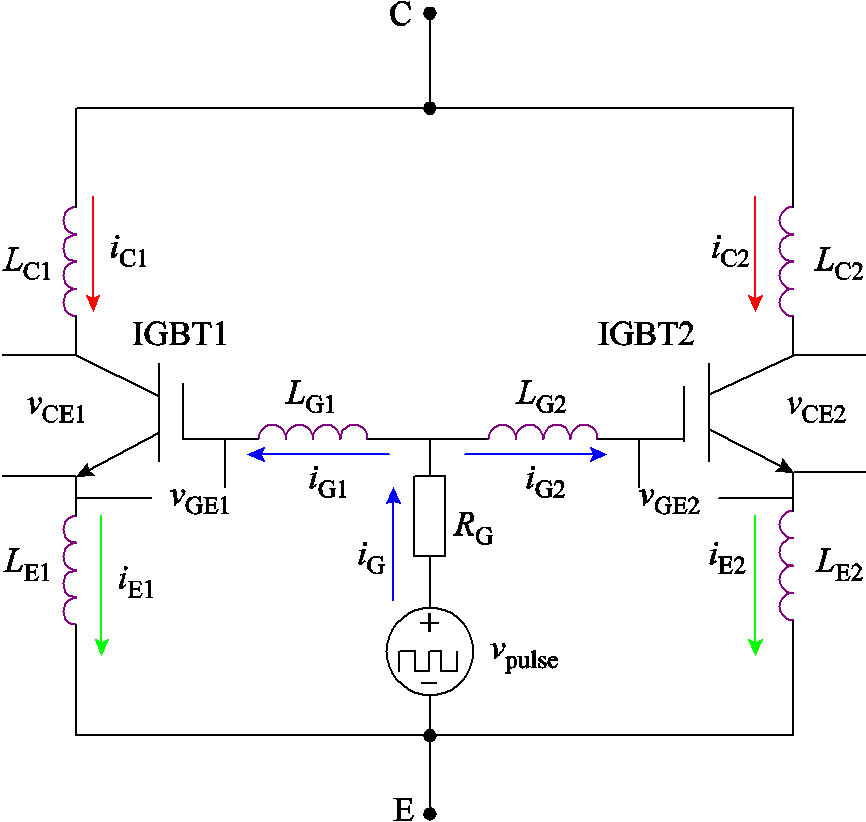

为了便于分析芯片之间的电流分布特性,以两颗IGBT芯片并联为例进行说明。两芯片并联电路如图7所示,图中LC1和LC2分别为两颗IGBT的集电极杂散电感;LG1和LG2分别为两颗IGBT的栅极杂散电感;LE1和LE2分别为两颗IGBT的发射极杂散电感;vpulse为驱动脉冲源,RG为驱动电阻。根据杂散电感所在的回路不同,下面分别从功率回路和驱动回路进行分析。

图7 两芯片并联电路

Fig.7 The circuit of two chips in parallel

1)功率回路

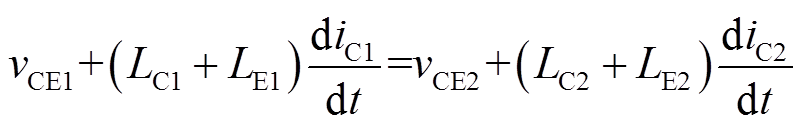

首先分析功率回路杂散电感对并联均流的影响,可以看到功率回路包含LC和LE。由于iE=iG+iC, 同时iG iC,可以认为iE≈iC。根据并联电路的电压相等,可以得到

iC,可以认为iE≈iC。根据并联电路的电压相等,可以得到

(3)

(3)

两颗IGBT芯片集射极电压差ΔvCE近似为

(4)

(4)

以ΔLC=ΔLE=15 nH、diC/dt=108 A/s为例,经过计算,可得ΔvCE≈3 V。观察图6中t2~t3和t4~t5两个时间段的电流变化过程,IGBT的集射极电压vCE基本维持在母线电压(1 500~2 500 V)下,因此ΔvCE vCE,微小的集射极电压差异不会对IGBT内部的空间电荷区产生影响。由此可知,若仅考虑功率回路杂散电感的差异,ΔLC和ΔLE基本不会影响IGBT芯片之间的电流分布。

vCE,微小的集射极电压差异不会对IGBT内部的空间电荷区产生影响。由此可知,若仅考虑功率回路杂散电感的差异,ΔLC和ΔLE基本不会影响IGBT芯片之间的电流分布。

2)驱动回路

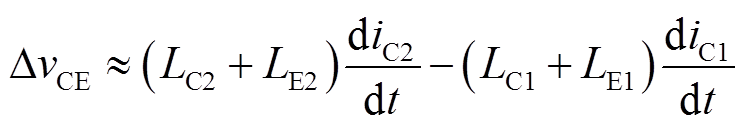

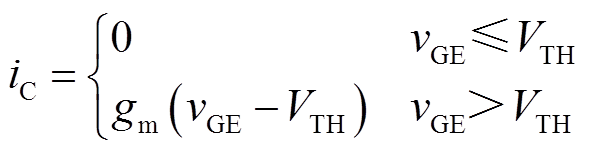

其次分析驱动回路杂散电感对芯片间并联均流的影响,根据IGBT的转移特性曲线公式

(5)

(5)

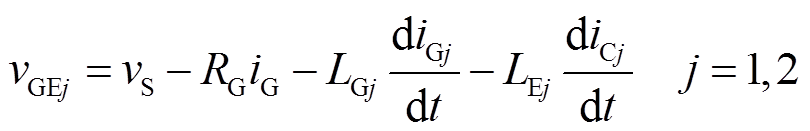

式中,gm为IGBT的跨导;VTH为IGBT的阈值电压。集电极电流iC受到栅极电压vGE的控制,从图7中可以得到栅极电压的表达式为

(6)

(6)

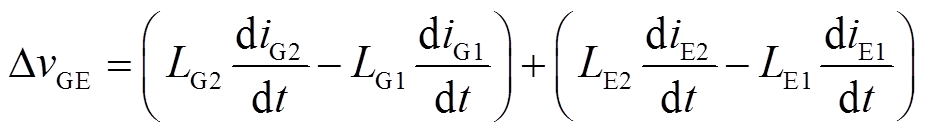

则两颗IGBT芯片栅极电压差ΔvGE为

(7)

(7)

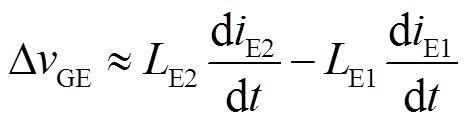

式(7)中包含两项,第一项为栅极电感LG的影响,第二项为发射极电感LE的影响。由于iG iC,因此第一项可以忽略不计,式(7)转换为

iC,因此第一项可以忽略不计,式(7)转换为

(8)

(8)

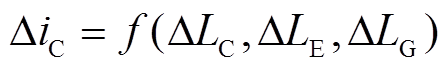

以ΔLE=15 nH、diC/dt=108 A/s为例,经过计算得ΔvGE≈1.5 V。由于vGE的变化范围为−10~15 V,ΔvGE占有较大的比例,它的影响不可忽略。综上分析,影响压接型IGBT芯片并联均流特性的主要因素为发射极电感差异ΔLE。

此外,vCE对iC的控制在IGBT开通和关断过程并不相同,原因在于IGBT为双极性器件,其内部有两种载流子(电子和空穴)参与电流输运过程。IGBT并联均流特性不仅需要考虑IGBT芯片外部电气特性,而且需要考虑IGBT芯片内部的载流子行为。IGBT内部物理结构[19]如图8所示。图中imos为IGBT内部MOS(metal-oxide-semiconductor)结构的沟道电流,ibp为双极性晶体管(Bipolar Junction Transistor, BJT)的电流。下面分别对关断过程和开通过程进行分析。

图8 IGBT内部物理结构

Fig.8 The physical structure inside IGBT

1)关断过程

首先分析IGBT的关断过程,在图6中的t1~t2时间段,由于vCE快速上升,IGBT器件内部基区空间电荷区急剧扩展,基区的过剩载流子被电场抽取形成电流ibp。由于负载电感较大,负载电流维持不变,此时IGBT的电流由imos和ibp两部分构成,vGE不能完全控制集电极电流。当栅极电压低于VTH,MOS沟道电流消失,IGBT集电极电流等于ibp。在t2时刻,vCE略高于母线电压,续流二极管FRD开通,IGBT电流向FRD换流,IGBT电流开始下降。因此,由于关断时刻前基区过剩载流子的存在,IGBT关断过程的电流不完全由栅极电压vGE控制。

2)开通过程

其次分析IGBT的开通过程,由于开通前IGBT器件处于阻断状态,vCE较高,因此开通过程中IGBT器件处于退饱和状态,且基区不存在过剩载流子。当栅极电压vGE高于VTH时,栅极沟道开通,imos电流作为PNP BJT的基极电流驱动PNP BJT开通,BJT电流ibp与基极电流imos成比例关系,两者同时增加,直到IGBT器件电压下降至饱和状态,开通过程完成。因此在开通过程中,IGBT电流完全由栅极电压vGE决定。

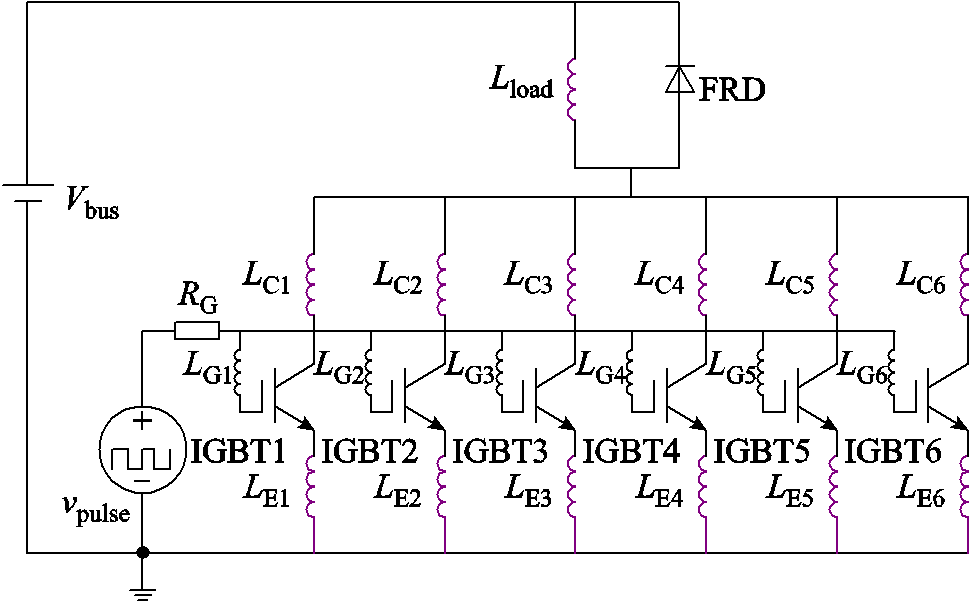

为了验证上述理论的正确性,以六颗IGBT芯片并联为例,建立了包含杂散电感的IGBT并联仿真电路模型。其中IGBT模型采用Hefner模型,它以半导体物理为基础,通过简化和假设得到半导体物理方程的解析式,是目前比较全面和准确性较高的模型。相比于行为模型,它能够反映IGBT外部的电气特性和内部的载流子行为,适合于分析并联芯片之间的电流分配。采用双脉冲电路分别对三个杂散电感差异进行仿真分析,仿真电路如图9所示。图中Vbus为母线电压,Lload为负载电感,FRD为续流二极管。

图9 多芯片并联双脉冲电路模型

Fig.9 Double pulse circuit model of multi-chip parallel

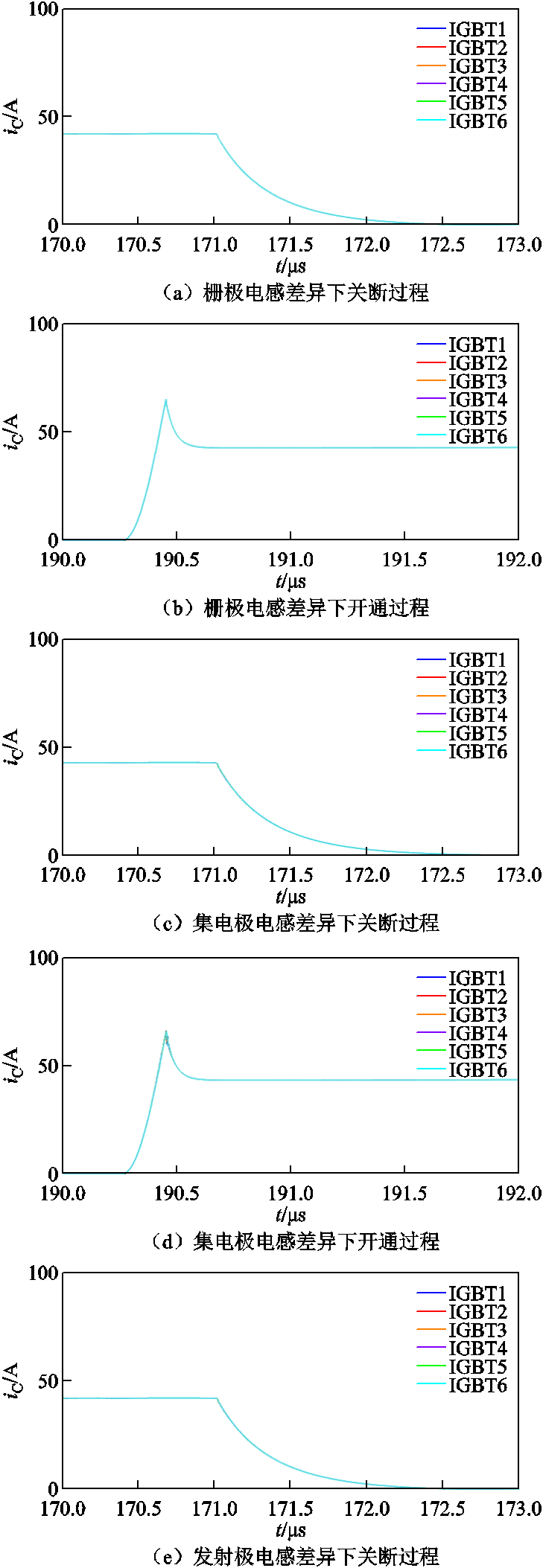

分别设置栅极、集电极和发射极其中一个在不同位置的杂散电感差异,同时保持另外两个杂散电感不变。根据第1节提取的栅极杂散电感范围(78.74~87.58 nH)以及集电极和发射极杂散电感范围(35.36~50.72 nH),搭建仿真电路1研究栅极电感差异,LG1~LG6分别设置为78、80、82、84、86、88 nH,其余杂散电感相同;仿真电路2研究集电极电感差异,LC1~LC6分别设置为35、38、41、44、47、50 nH,其余杂散电感相同;仿真电路3研究发射极电感差异,LE1~LE6分别设置为35、38、41、44、47、50 nH,其余杂散电感相同,仿真结果如图10所示。

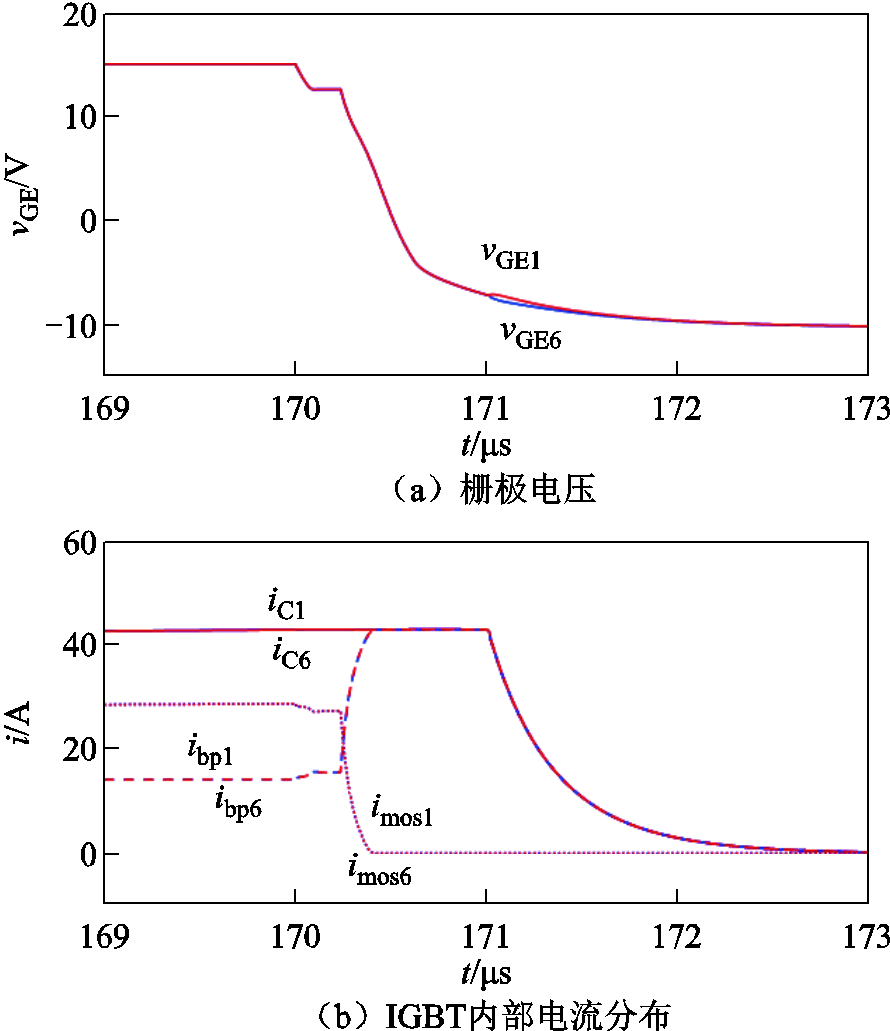

从图10中可知,在分别设置栅极杂散电感LG和集电极杂散电感LC差异时,电流没有出现明显的差异。仅在发射极电感LE出现差异时,才会在开通过程中出现明显的电流分布差异。上述仿真结果验证了本文理论分析的正确性。为了进一步讨论关断和开通过程的差别,以IGBT1和IGBT6两颗芯片内部的电流为例进行说明,IGBT关断过程电压、电流变化如图11所示。

图10 杂散电感差异对均流特性的影响

Fig.10 Influence of stray inductances difference on current sharing characteristics

图11 IGBT关断过程电压、电流变化

Fig.11 Voltage and current change during IGBT turn off

从图11中可以观察到,在170 μs时,栅极电压vGE开始下降,其内部的imos开始降低,由于外部电路没有达到IGBT总电流下降的条件,其内部的imos转化为ibp以维持总电流iC不变。到171 μs时,FRD达到开通的条件,IGBT电流开始下降,发射极杂散电感差异会导致栅极电压vGE出现差异,但此过程栅极电压vGE已下降到阈值电压VTH以下,即IGBT内部的MOS沟道已经完全关闭,即使栅极电压vGE出现差异,也不会影响外部电流的不均衡。

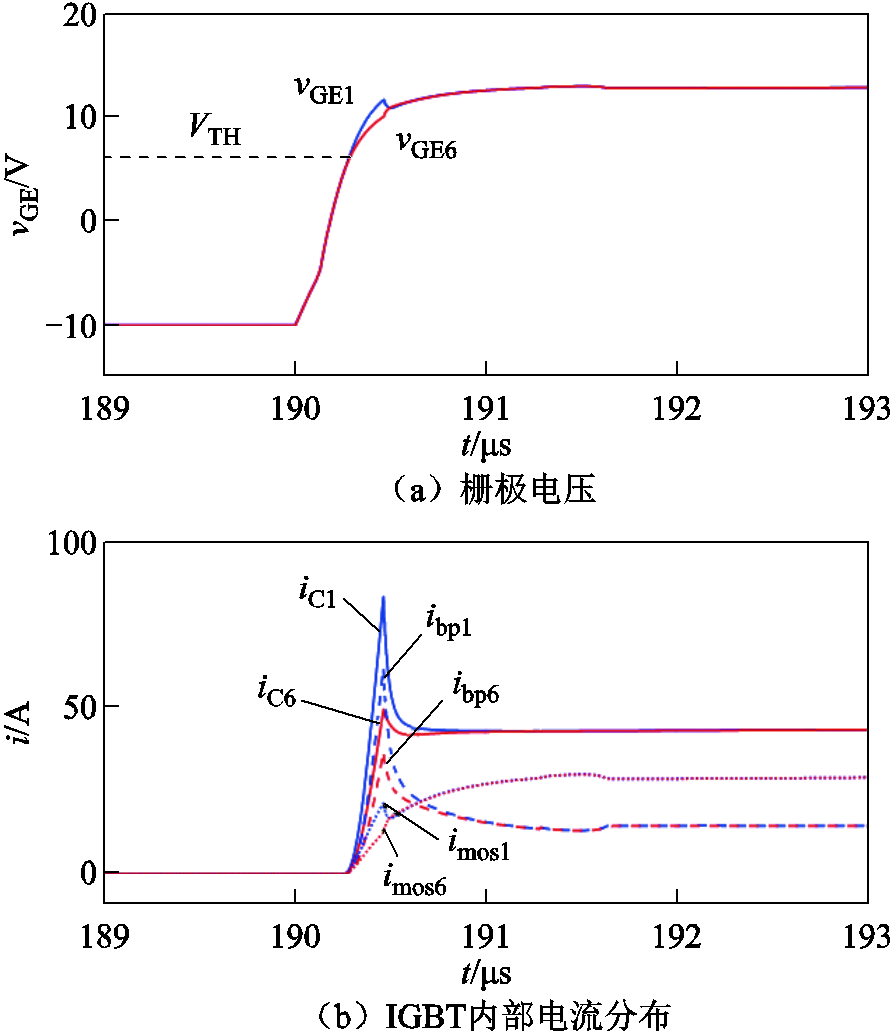

IGBT开通过程电压、电流变化如图12所示。从图12中的结果观察到,栅极电压vGE大于阈值电压VTH时,IGBT电流开始上升。由于发射极电感的差异,根据式(7),两芯片之间的vGE出现了差异,从而导致两芯片沟道电流imos出现了差异,此过程中imos和ibp具有一定的比例关系,两者同时增加,进一步导致了外部电流的不均衡。

图12 IGBT开通过程的电压、电流变化

Fig.12 Voltage and current change during IGBT turn on

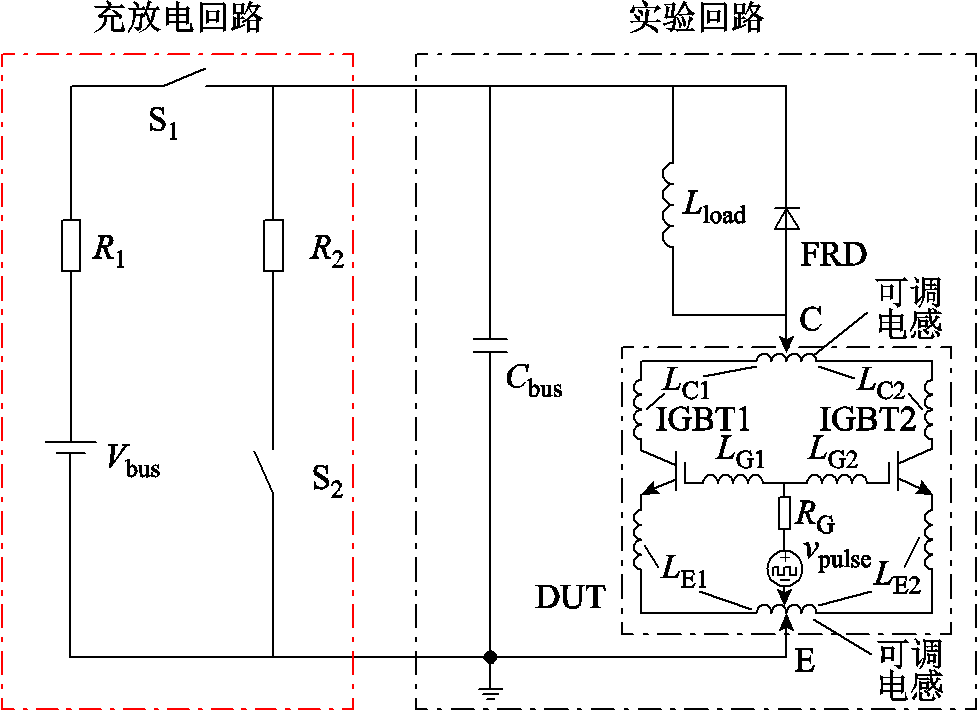

综合上述分析,仿真结果能够很好地与理论分析相对应。为了进一步验证本文理论分析的有效性,建立了两芯片并联均流实验平台。两芯片并联双脉冲实验电路如图13所示,包含充放电回路与实验回路两部分。其中充放电回路中含有高压直流电源Vbus、充电电阻R1、放电电阻R2及开关S1和S2,充电回路提供实验回路所需的母线电压。在实验回路中,Cbus为母线电容,待测器件(Device Under Test, DUT)包含两支路的IGBT芯片。

图13 两芯片并联双脉冲实验电路

Fig.13 Double pulse test circuit of dual-IGBT chips

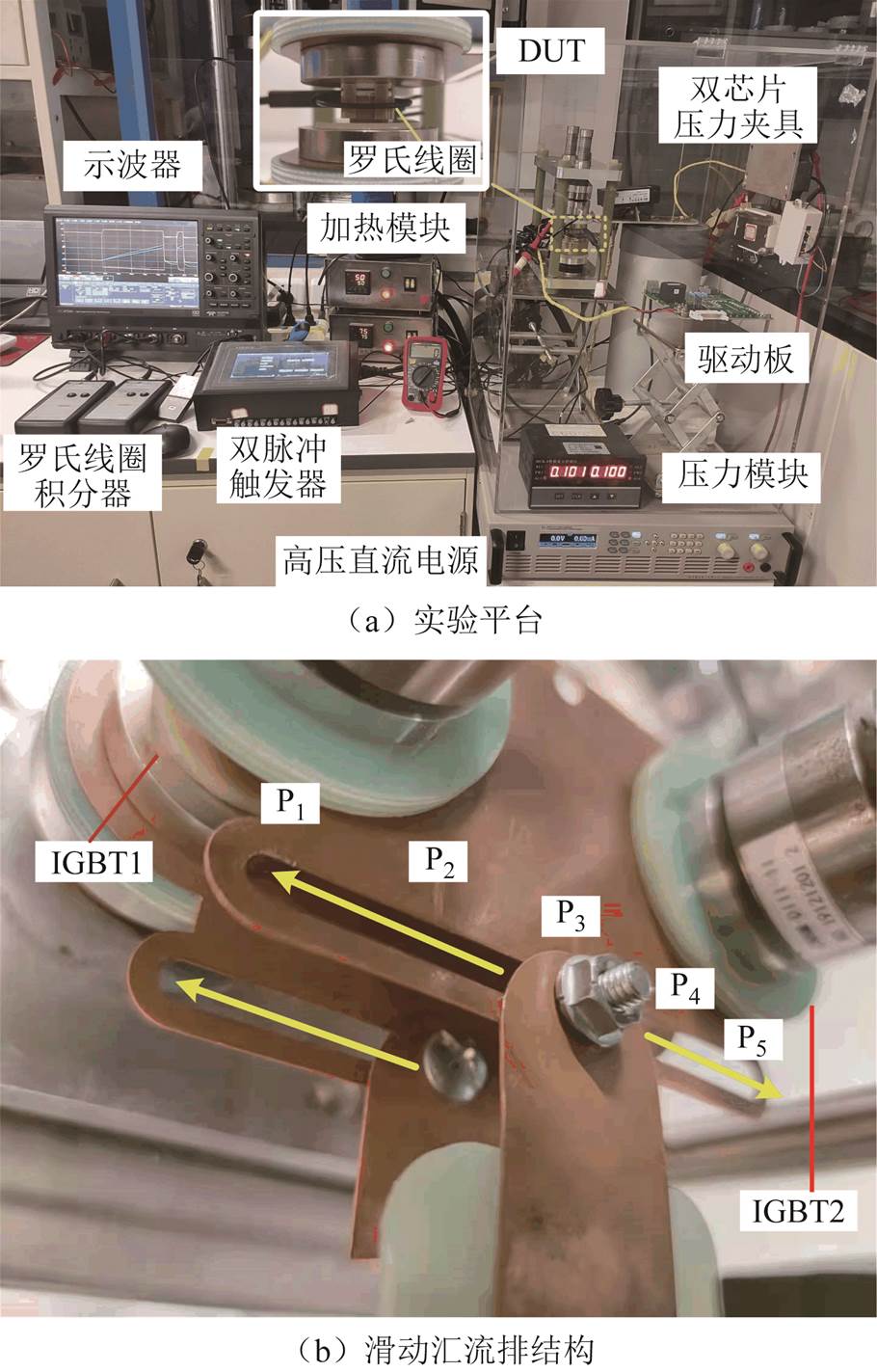

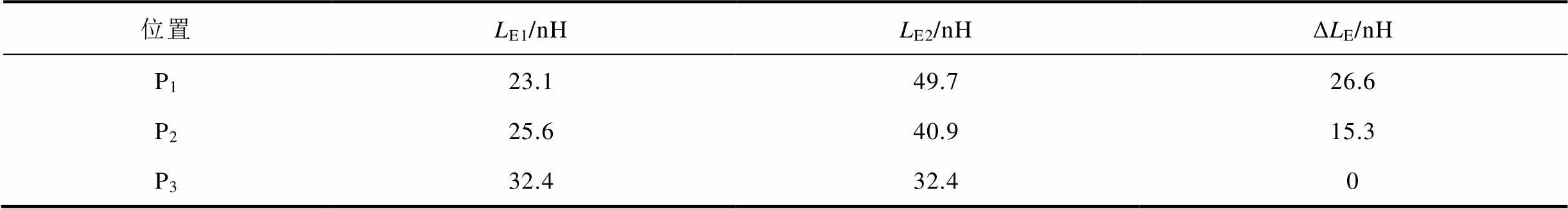

基于以上实验原理,搭建杂散电感可调的并联均流实验平台如图14a所示。两支路的杂散电感差异通过滑动汇流排实现,如图14b所示。图14b中的P3为汇流排的中心对称点,由于两侧对称,实验以P1、P2和P3三个典型位置作为实验条件,通过有限元仿真软件提取三个位置下的杂散电感,结果见表3。

图14 杂散电感可调的并联均流实验平台

Fig.14 Experiment platform with adjustable stray inductance

表3 不同汇流排连接点下的杂散电感

Tab.3 The stray inductances of different busbar positions

位置LE1/nHLE2/nHΔLE/nH P123.149.726.6 P225.640.915.3 P332.432.40

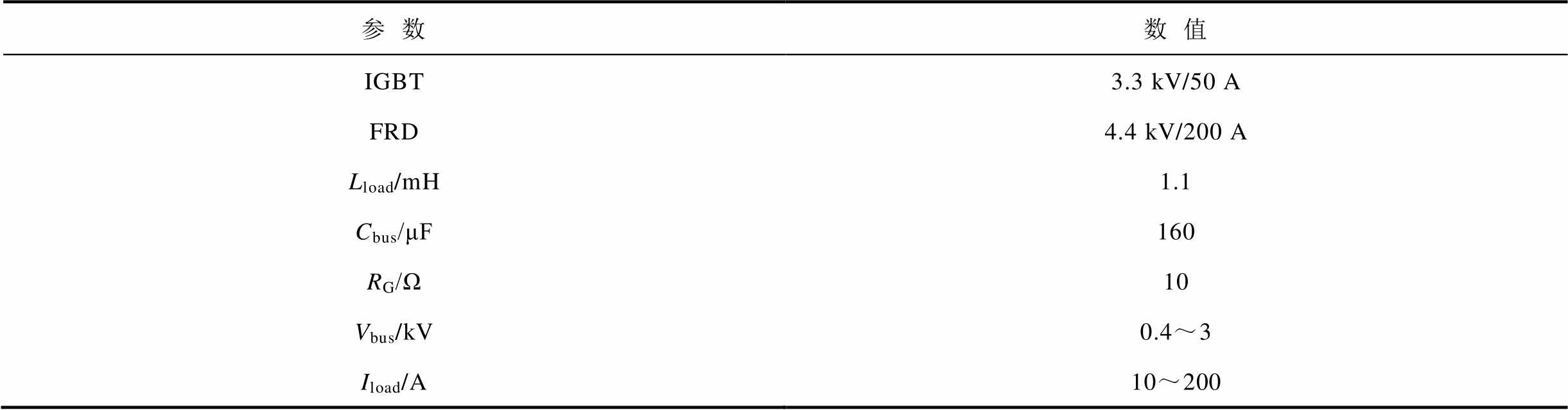

当汇流排被滑动到P1点时,连接点位置离左侧IGBT更近,此时左侧杂散电感为23.1 nH,右侧杂散电感为49.7 nH,两者之间相差26.6 nH。对比表1和表3,双支路实验平台的杂散电感范围(23.1~49.7 nH)基本能够反映真实压接型IGBT器件杂散电感的范围(35.36~50.72 nH),本文建立的实验平台可以模拟实际的压接型IGBT器件。测量部分由示波器、电压探头与电流探头组成,示波器型号为HDO4104A,测量vCE的电压探头型号为PPE4kV,测量vGE的电压探头型号为PP018,测量电流的罗氏线圈型号为CWT-Ultra mini06,放置于IGBT子模组的极板之间,为了保证探头的测量精度,已在实验前对探头进行了校准[20-21]。实验平台的其他主要参数见表4。

表4 实验平台主要参数

Tab.4 The main parameters of the experimental platform

参数数值 IGBT3.3 kV/50 A FRD4.4 kV/200 A Lload/mH1.1 Cbus/μF160 RG/Ω10 Vbus/kV0.4~3 Iload/A10~200

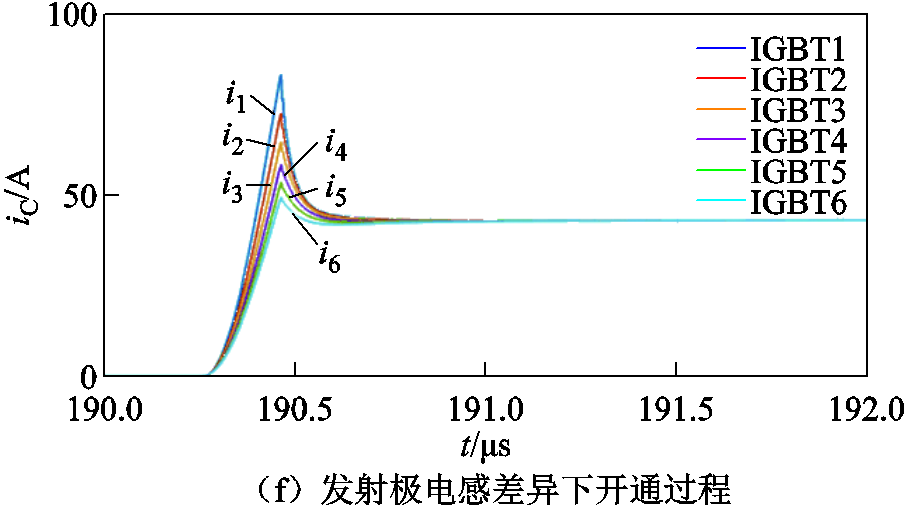

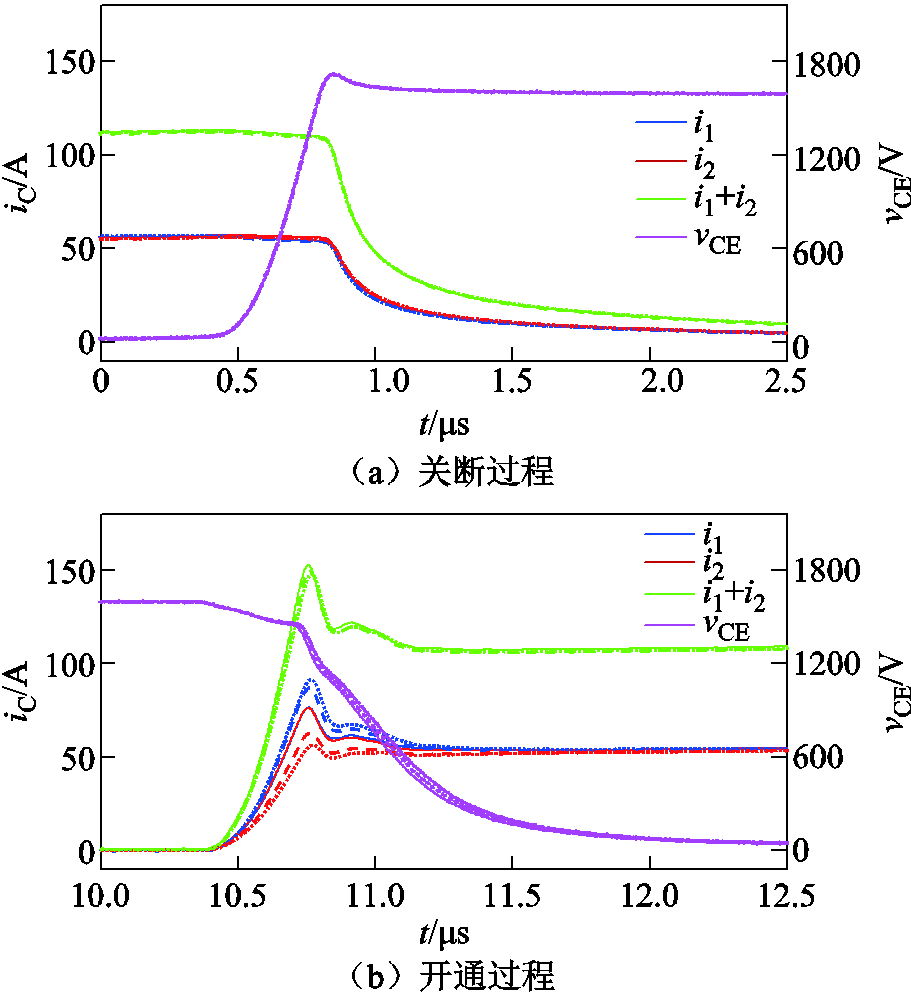

分别在P1、P2、P3点进行双脉冲实验,得到实验结果如图15所示。图中点虚线、长虚线和实线分别表示P1、P2、P3点的实验结果。

图15 不同连接汇流排位置下的实验结果

Fig.15 Experimental results under different busbar positions

从图15中可以看出,当杂散电感出现差异时,两芯片关断过程的电流分布比较均匀,而在开通过程中电流出现了明显的差异,并且电流差异随着杂散电感差异的变大而变大。当汇流排连接点在P1时,IGBT1的电流达到了91.45 A,IGBT2的电流为56.39 A,两者相差35.06 A,电流失配率达到23.7%。实验结果进一步验证了发射极杂散电感差异主要影响开通过程的电流分布。

通过上述理论和实验分析,为了改进杂散电感差异对芯片间瞬态均流的影响,应使压接型IGBT器件内部的功率回路和驱动回路分离。为此可以采用焊接型IGBT模块中常用的辅助发射极(开尔文接线)连接方式[22],这样功率回路杂散电感的压降不会传递到驱动回路上,从而避免了IGBT芯片之间的瞬态电流不均衡。

本文首先针对压接型IGBT的封装结构及侧面连接汇流排的典型方式,通过有限元分析软件,得到了压接型IGBT内部三个主要杂散电感LG、LC和LE的分布规律;其次通过对功率回路和驱动回路进行理论分析,分别得到了三个主要电感对IGBT并联均流的影响机理;然后在仿真软件中建立了含有杂散电感的IGBT并联仿真电路并搭建了杂散电感可调的并联均流实验平台,验证了本文理论分析的有效性。得到如下主要结论:

1)压接型IGBT器件内部不同IGBT位置有不同的杂散电感。原因在于连接汇流排结构和IGBT芯片布局的差异,以3.3 kV/1 500 A为例进行杂散电感提取,发射极杂散电感最大差异为15.36 nH,变化率为43.43%;栅极杂散电感最大值与最小值相差8.84 nH,变化率为11.22%。

2)并联IGBT芯片电流分布不均主要受到发射极电感差异ΔLE的影响。通过对IGBT并联均流特性进行电路分析,得到功率回路和驱动回路的公共支路上的杂散电感LE会影响栅极电压vGE的变化率,从而影响IGBT芯片之间的电流分布。

3)发射极杂散电感差异ΔLE主要影响开通过程的电流分布。通过建立IGBT物理模型,综合IGBT外特性和内部载流子行为,发现在关断过程中IGBT的电流下降速率不受栅极电压vGE的控制,而开通过程中IGBT的电流上升率受到栅极电压vGE的控制。因此发射极杂散电感差异主要影响开通过程的电流不均衡。

参考文献

[1] Baliga B J, Adler M S, Love R P, et al. The insulated gate transistor: a new three-terminal MOS-controlled bipolar power device[J]. IEEE Transactions on Electron Devices, 1984, 31(6): 821-828.

[2] Iwamuro N, Laska T. IGBT history, state-of-the-art, and future prospects[J]. IEEE Transactions on Electron Devices, 2017, 64(3): 741-752.

[3] Shigekane H, Kirihata H, Uchida Y. Developments in modern high power semiconductor devices[C]// Proceedings of the 5 th International Symposium on Power Semiconductor Devices and ICs, Monterey, CA, USA, 1993: 16-21.

[4] Wakeman F, Lockwood G, Davies M, et al. Pressure contact IGBT, the ideal switch for high power applications[C]//Conference Record of the 1999 IEEE Industry Applications Conference, Phoenix, AZ, USA, 1999: 700-707.

[5] 刘国友, 窦泽春, 罗海辉, 等. 高功率密度3600A/ 4500V压接型IGBT研制[J]. 中国电机工程学报, 2018, 38(16): 4855-4862, 4991. Liu Guoyou, Dou Zechun, Luo Haihui, et al. Development of high power density 3600A/4500V press-pack IGBT[J]. Proceedings of the CSEE, 2018, 38(16): 4855-4862, 4991.

[6] 顾妙松, 崔翔, 彭程, 等. 外部汇流汇流排对压接型IGBT器件内部多芯片并联均流特性的影响[J]. 中国电机工程学报, 2020, 40(1): 234-245, 390. Gu Miaosong, Cui Xiang, Peng Cheng, et al. Influence of the external busbar on current sharing performance inside a multi-chip press-pack IGBT device[J]. Proceedings of the CSEE, 2020, 40(1): 234-245, 390.

[7] Wu Rui, Smirnova L, Wang Huai, et al. Comprehensive investigation on current imbalance among parallel chips inside MW-scale IGBT power modules[C]//2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, Korea (South), 2015: 850-856.

[8] 张一鸣, 邓二平, 赵志斌, 等. 压接型IGBT器件封装内部多物理场耦合问题研究概述[J]. 中国电机工程学报, 2019, 39(21): 6351-6365. Zhang Yiming, Deng Erping, Zhao Zhibin, et al. A review of the multiphysics coupling problem in press pack IGBT[J]. Proceedings of the CSEE, 2019, 39(21): 6351-6365.

[9] 张玉斌, 温英科, 阮琳. 全浸式蒸发冷却IGBT电热耦合模型研究[J]. 电工技术学报, 2022, 37(15): 3845-3856. Zhang Yubin, Wen Yingke, Ruan Lin. Research on electrothermal coupling model of fully-immersed evaporative cooling IGBT[J]. Transactions of China Electrotechnical Society, 2022, 37(15): 3845-3856.

[10] 丁雪妮, 陈民铀, 赖伟, 等. 多芯片并联IGBT模块老化特征参量甄选研究[J]. 电工技术学报, 2022, 37(13): 3304-3316, 3340. Ding Xueni, Chen Minyou, Lai Wei, et al. Selection of aging characteristic parameter for multi-chips parallel IGBT module[J]. Transactions of China Electrotechnical Society, 2022, 37(13): 3304-3316, 3340.

[11] Li Helong, Zhou Wei, Wang Xiongfei, et al. Influence of paralleling dies and paralleling half-bridges on transient current distribution in multichip power modules[J]. IEEE Transactions on Power Electronics, 2018, 33(8): 6483-6487.

[12] Castellazzi A, Ciappa M, Fichtner W, et al. A study of the threshold-voltage suitability as an application-related reliability indicator for planar-gate non-punch-through IGBTs[J]. Microelectronics Reliability, 2007, 47(9/10/11): 1713-1718.

[13] Chang Yao, Zhou Yu, Luo Haoze, et al. A comprehensive investigation of dynamic switching performance for press-pack IGBT modules[C]//2017 19 th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), Warsaw, Poland, 2017: 1-9.

[14] 刘盛福, 常垚, 李武华, 等. 压接式IGBT模块的动态特性测试平台设计及杂散参数提取[J]. 电工技术学报, 2017, 32(22): 50-57. Liu Shengfu, Chang Yao, Li Wuhua, et al. Dynamic switching characteristics test platform design and parasitic parameter extraction of press-pack IGBT modules[J]. Transactions of China Electrotechnical Society, 2017, 32(22): 50-57.

[15] Gu Miaosong, Cui Xiang, Tang Xinling, et al. An electro-thermo-mechanical model basing on experimental results for press-pack IGBT including MOS side two-dimensional effects[C]//2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 2019: 502-507.

[16] Luo Yifei, Xiao Fei, Liu Binli, et al. A physics-based transient electrothermal model of high-voltage press-pack IGBTs under HVDC interruption[J]. IEEE Transactions on Power Electronics, 2020, 35(6): 5660-5669.

[17] 顾妙松, 崔翔, 彭程, 等. 电极结构与空间布置对压接型IGBT器件内部多芯片并联均流的影响(一):计算研究[J]. 中国电机工程学报, 2020, 40(7): 2318-2329, 2410. Gu Miaosong, Cui Xiang, Peng Cheng, et al. Influence of electrode structure and arrangement on current sharing performance inside a multi-chip press-pack IGBT device (part Ⅰ): analysis and calculation[J]. Proceedings of the CSEE, 2020, 40(7): 2318-2329, 2410.

[18] 顾妙松, 崔翔, 彭程, 等. 电极结构与空间布置对压接型IGBT器件内部多芯片并联均流的影响(二):实验研究[J]. 中国电机工程学报, 2020, 40(10): 3288-3297. Gu Miaosong, Cui Xiang, Peng Cheng, et al. Influence of electrode structure and arrangement on current sharing performance inside a multi-chip press-pack IGBT device (part Ⅱ): experiment[J]. Proceedings of the CSEE, 2020, 40(10): 3288-3297.

[19] Hefner A R, Diebolt D M. An experimentally verified IGBT model implemented in the Saber circuit simulator[C]//PESC '91 Record 22 nd Annual IEEE Power Electronics Specialists Conference, Cambridge, MA, USA, 2002: 10-19.

[20] 彭程, 李学宝, 顾妙松, 等. 压接型IGBT器件内部芯片电流测量时罗氏线圈的误差分析及改进方法[J]. 中国电机工程学报, 2020, 40(22): 7388-7398. Peng Cheng, Li Xuebao, Gu Miaosong, et al. Error analysis and improvement method of Rogoswski coil in current measurement of internal chips in press-pack IGBT devices[J]. Proceedings of the CSEE, 2020, 40(22): 7388-7398.

[21] 彭程, 李学宝, 张冠柔, 等. 压接型IGBT芯片动态特性实验平台设计与实现[J]. 电工技术学报, 2021, 36(12): 2471-2481. Peng Cheng, Li Xuebao, Zhang Guanrou, et al. Design and implementation of an experimental platform for dynamic characteristics of press-pack IGBT chip[J]. Transactions of China Electrotechnical Society, 2021, 36(12): 2471-2481.

[22] Li Helong, Munk-Nielsen S, Bęczkowski S, et al. Effects of auxiliary source connections in multichip power module[C]//2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 2016: 3101-3106.

Abstract The parallel connection of several chips in the PPI device is an important means to improve its current level. However, the transient current imbalance between IGBT chips is one of the main reasons that limit its current increase. It is important to study the transient current distribution in the PPI IGBT device for the package design. The existing research usually adopts the simulation method, but it does not consider the internal physical process of IGBT, and the simulation results often have a big deviation from the experimental results. In this paper, an integrated circuit model containing the package stray inductance and the internal physical characteristics of IGBT is established, and the influence law of the stray inductance on the current distribution is obtained. After that, the validity of the simulation results is verified by the double-pulse experiment platform.

Firstly, three stray inductances inside the 3.3 kV/1 500 A PPI device are extracted, and the differences in stray inductances under different IGBT chip positions are obtained. It is found that the maximum difference of emitter stray inductance is 15.36 nH and the change rate of emitter stray inductance is 43.43%, the maximum difference of gate stray inductance is 8.84 nH and the change rate of gate stray inductance is 11.22%. Secondly, three stray inductance differences are analyzed in theory, it is found that the current imbalance of IGBT chips is mainly affected by emitter stray inductance on the common branch of the power circuit and drive circuit. At the same time, the carrier behavior inside IGBT is analyzed, and it is found that the difference of emitter stray inductance mainly affects the current imbalance in the turn-on process. Then, an IGBT integrated simulation circuit is established in the simulation software, which includes the packaged stray inductance and the internal physical characteristics of IGBT chips. The difference of each stray inductance is calculated, and the influence rule of each stray inductor difference on the current distribution is obtained. When the difference between gate stray inductances LG and collector stray inductances LC is set separately, there is no obvious difference between the IGBT chip current. Only when the emitter inductance LE is different, the current distribution phenomenon will be obvious in the turn-on process. Through the calculation, the simulation results can correspond well with the theoretical analysis. Finally, a double pulse experiment platform with two parallel chips is established. The difference in stray inductance is realized by sliding the busbar. The stray inductance range of the double-branch experimental platform (23.1~49.7 nH) can reflect the stray inductance range of the real PPI device (35.36~50.72 nH). Through experiments, it is found that the current of the two chips is relatively uniform in the turn-off process, while the current is different in the turn-on process. The current difference increases with the increase of the stray inductance difference. When the busbar connection point is P1, the current of IGBT1 reaches 91.45 A and that of IGBT2 is 56.39 A, the difference is 35.06 A. The current imbalance rate reaches 23.7%, and the experimental results further verify the validity of theoretical analysis and simulation results

The following conclusions can be drawn from the simulation analysis: (1) Different positions of IGBT chips in PPI have different stray inductances. Taking 3.3 kV/1500 A as an example, the maximum change rate of emitter stray inductance is 43.43% and the change rate of gate stray inductance is 11.22%. (2) The current imbalance of IGBT chips is mainly affected by the difference in emitter inductance. Through the circuit analysis, it is found that the emitter inductance affects the change rate of VGE, thus affecting the current sharing among IGBT chips. (3) Both external characteristics and internal carrier behavior of IGBT chips are considered, it is found that the difference of emitter stray inductance mainly affects the current imbalance in the turn-on process, but hardly affects the turn-off process.

keywords:Press-pack IGBT device, transient current sharing, power path, drive path, stray inductance

DOI:10.19595/j.cnki.1000-6753.tces.220044

中图分类号:TN307; TM46

国家自然科学基金-国家电网公司联合基金重点项目(U1766219)资助。

收稿日期 2022-01-11

改稿日期 2022-07-11

彭 程 男,1993年生,博士研究生,研究方向为高压大功率半导体器件测试与封装杂散。E-mail:pengcheng.ncepu@gmail.com

李学宝 男,1988年生,博士,副教授,研究方向为先进输电技术、电力系统电磁环境与电磁兼容、高压大功率半导体器件封装技术。E-mail:lxb08357x@ncepu.edu.cn(通信作者)

(编辑 李冰)