图1 焊接式模块的封装结构

Fig.1 Packaging structure of soldered module

摘要 针对高压SiC模块的封装关键问题(即绝缘性能、寄生参数、热管理),该文提出多目标加权优化方法,实现6.5kV SiC MOSFET模块多个性能指标的折中和优化。首先,通过建立电、热、力多物理场有限元模型分别对量化指标寄生电容、焊料层热应力以及电场强度进行建模,并对三者进行加权优化,得到最优尺寸参数以保证6.5kV SiC MOSFET模块的整体性能;然后,通过对外壳和端子的设计,保证模块外部绝缘可靠的同时尽可能降低寄生电感,实现模块寄生电感和外部绝缘性能的折中;最后,通过双脉冲实验、耐压测试等验证所研制模块的性能优势及多目标加权优化方法的有效性。结果表明,所提研制模块能够在4 500V/14A的条件下可靠工作;在寄生参数、绝缘性能得到优化的同时,保证了模块整体性能的优越性。

关键词:高压SiC MOSFET 封装 多物理场 多目标加权优化

近年来,随着轨道交通、脉冲功率、高压直流输电以及新能源发电等技术的不断发展,对于高压功率半导体模块的需求越来越多[1-4]。在过去,应用在这些领域的主流器件是Si IGBT,但是由于硅材料的限制,IGBT模块的最大电压等级典型值在6.5kV,若应用于更高电压场合下就需要进行串联或者采用新型拓扑结构,这会增加变换器或设备的体积和复杂性[5-6]。因此具有高压、高频、高温等优势的SiC MOSFET器件是一种很好的替换选择,由于SiC MOSFET器件具备阻断电压高、开关损耗低、开关速度快等优势,应用于固态变压器、变换器等设备时会显著降低其体积、提高效率和功率密度,因此,已经引起国内外学术界和工业界的广泛关注[7]。

在过去的十几年里,对于高压SiC MOSFET的研究不断取得突破。在国外,CREE公司报道的SiC MOSFET已经达到10kV和15kV[8-9];三菱电机已经生产3.3kV的商用SiC MOSFET。在国内,南京电子器件研究所成功研制出6.5kV/25A和15kV/10A SiC MOSFET芯片并进行简单的封装、测试,验证其性能[10-11]。但是对于高压器件,由于芯片工艺和封装技术的不成熟,暂时没有6.5kV及以上的商用SiC MOSFET模块。

对于SiC MOSFET芯片,若想发挥其高压等优势,封装技术的创新必不可少。然而相比于国外,国内针对高压芯片封装技术的文献相对较少。

对于高压SiC MOSFET模块而言,主要存在绝缘性能[12-16]、寄生参数[17-18]、热管理[19-24]三个问题。针对绝缘性能问题,现有学者主要从材料优化和结构优化两方面实现对电场的优化。其中,材料优化方面包括:采用具有更高击穿场强的材料(如苯并环丁烯BCB)提高击穿电压[4]、通过在某些区域覆盖功能性材料(包括场相关介电材料和场相关电导率材料)调节电场[12-14];从结构优化方面提出通过铜柱互联[15]、堆叠陶瓷衬底[6, 8]、台面[12, 16]等结构改善电场分布。对于寄生参数问题,寄生电容和寄生电感的优化对于降低由SiC器件高dv/dt、di/dt引起的电磁干扰等问题至关重要,前者可以通过对陶瓷衬底的优化实现,例如,采用堆叠覆铝陶瓷板(Direct Bonded Aluminum, DBA)[8]、覆铜陶瓷板(Direct Bonded Copper, DBC)下铜层设计[17];后者可以通过采用改进DBC布局、采用消除键合线的封装结构、将2D结构转化为3D结构[18]等方法进行改进。高压模块热管理问题主要是灌封材料在高温工况下的特性(击穿场强等)改变以及由于模块内部各材料间热膨胀系数不匹配引起的应变积 累[19-20],二者均会影响模块寿命,所以目前主要采用以下方法改善问题:工艺进步(如采用铜键合线、铜带代替铝键合线)[21-22]、结构优化(如双面散热结构)[21, 23]、散热技术提高(如相变技术)[24]、采用高温材料(如采用氮化铝衬底、高温灌封材 料)[25]。目前对高压功率半导体模块进行设计时大多只是从单一某一方面进行设计,未考虑实际高压应用时各方面的矛盾。因此,高压模块设计方法也需进一步研究,目前重庆大学提出一些针对功率半导体模块的电-热耦合设计方法,但主要研究对象是常规低压模块,未针对高压模块进行特别考虑[26-27]。

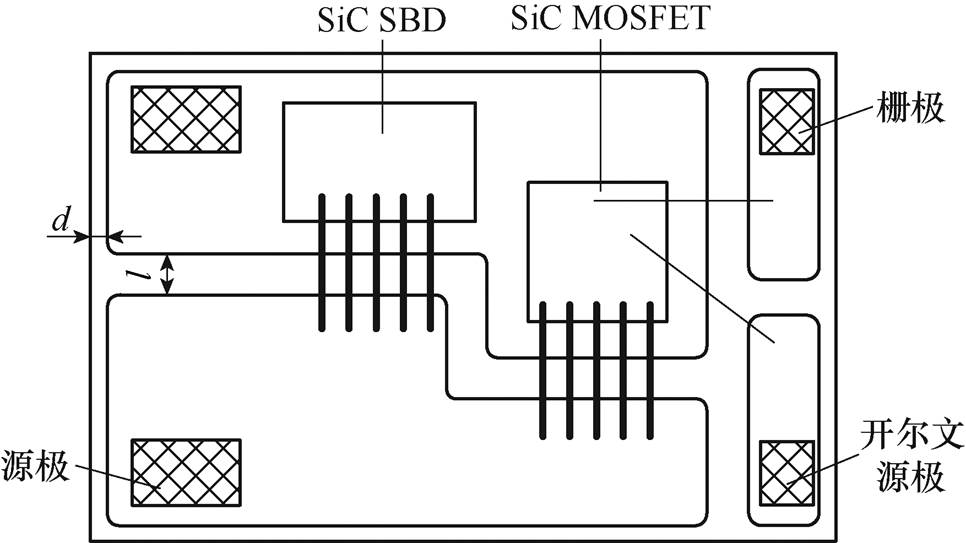

因此,为更加全面地发挥高压SiC MOSFET的优势,本文提出一种高压SiC模块多目标加权优化方法,实现模块的寄生电容、绝缘性能和热管理问题(这里主要考虑模块寿命问题)的折中设计。首先,进行初步优化,通过建立电场有限元模型对6.5kV SiC MOSFET模块内只与电场有关的DBC上铜层参数进行设计和优化。其次,通过理论研究和建立电、热、力有限元模型的方法分别建立量化指标电场强度、寄生电容、焊料层热应力与DBC各层厚度、下铜层形状的相关尺寸参数的关系模型,依此对模块内的DBC进行多目标加权优化,根据不同工况选择最优的参数。然后,在保证模块外部绝缘的同时尽可能降低寄生电感参数。最后,针对上述设计的6.5kV SiC MOSFET模块进行实际模块封装,并进行动态特性测试、耐压测试、寄生参数测量,通过实验验证上述设计的有效性。

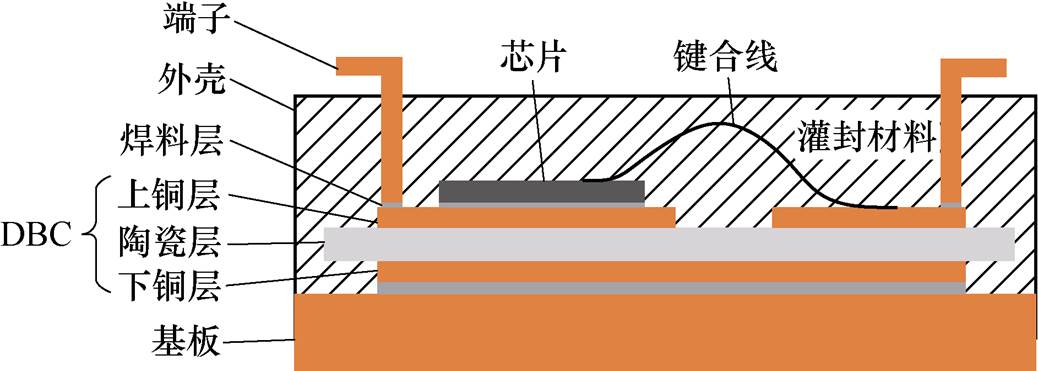

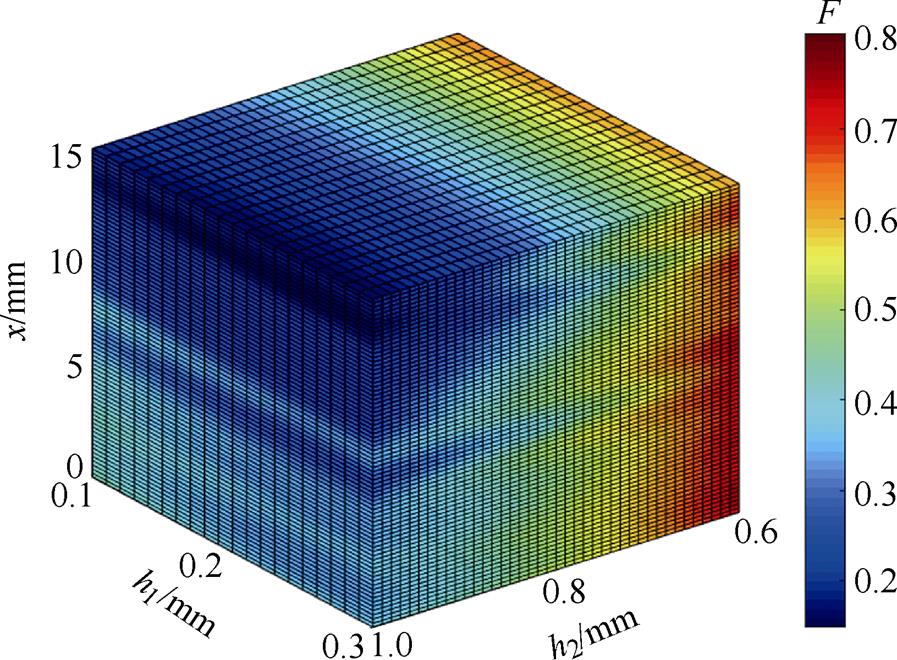

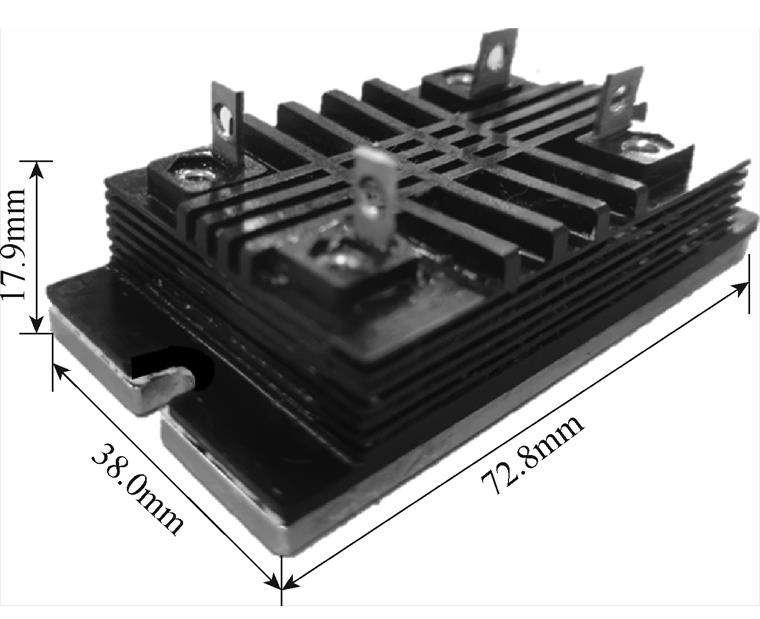

功率半导体模块封装有传统焊接封装和压接封装两种,前者因为工艺成熟应用更加广泛,本文也采用焊接式封装方案。图1为焊接式封装方案结构示意图,从上至下分别是芯片、焊料层、DBC上铜层、DBC陶瓷层、DBC下铜层、焊料层、基板七层结构,DBC起到绝缘和导热的作用,基板起到支撑DBC、缓解应力、增加模块机械强度的作用。

图1 焊接式模块的封装结构

Fig.1 Packaging structure of soldered module

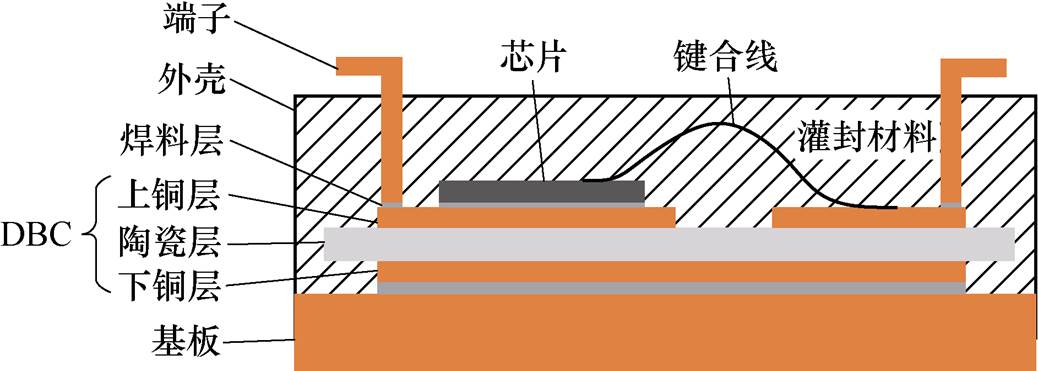

本文所研究的高压SiC MOSFET模块由南京电子器件研究所研制的6.5kV SiC MOSFET和6.5kV SiC SBD封装组成。模块中选用氧化铝(Al2O3)作为DBC陶瓷层的材料,同时为保证高压模块足够的绝缘性能,将DBC上、下铜层的拐角处取0.6mm圆角。为使模块的驱动回路和主功率回路之间解耦,从芯片源极引出开尔文源极,最终设计的6.5kV SiC MOSFET模块的原理如图2所示。为能够更加全面地发挥高压SiC MOSFET模块的优势,本文提出高压SiC MOSFET模块设计方法,其设计流程如图3所示。

图2 6.5kV SiC MOSFET模块原理

Fig.2 Schematic of 6.5kV SiC MOSFET module

对于高压模块,除芯片终端附近外,DBC三相点位置(即灌封材料、DBC铜层与DBC陶瓷层的交点)也会出现电位线畸变导致的电场集中现象,容易导致局部放电现象的发生,进而加速材料老化甚至绝缘材料击穿,导致器件损坏。文献[28]用解析和数值方法分析由三种介质组成的楔形边排列中的电场分布,说明随着与三相点距离的减小,电场强度会呈指数上升。因此该位置电场分布是高压封装中的重点研究对象。

图3 高压SiC MOSFET模块整体设计流程

Fig.3 Design flow chart of high voltage SiC MOSFET module

为研究三相点位置的电场,需要对电场进行求解。由于模块的结构较为复杂,通过理论推导的电场分布结果有限且准确性无法保证,因此本文采用有限元方法进行模块内部电场模拟。此外,由于最后的耐压测试时间远小于绝缘材料(氟油、硅凝胶等)的电荷弛豫时间,所以采用静电场分析电场分布[29],即

(1)

(1)

式中,E为电场强度;D为电位移向量; 为空间自由电荷体密度。

为空间自由电荷体密度。

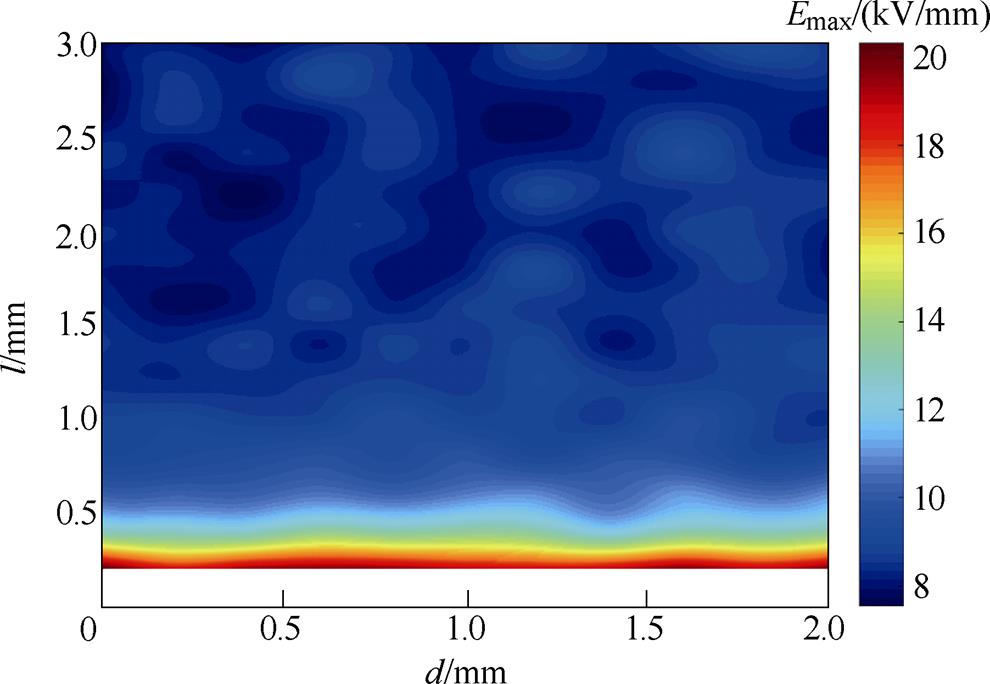

本文在保证DBC各层厚度一定的条件下,利用有限元法对DBC中只与电场分布有关的尺寸参数进行研究和优化,如图2所示,具体参数包括铜层之间的间距l、铜层与陶瓷层边缘的距离d。仿真时选择DBC铜层厚度为0.3mm、陶瓷层厚度为1.0mm作为初值;根据经验及电压等级,d=0~2mm,l= 0~3mm,得到的电场优化结果如图4所示。为消除网格划分对结果的影响,仿真结果采用DBC的平均电场强度峰值Emax,即前10%网格节点电场强度平均值。

从图4可知,对于图2所示的DBC布局,平均最大电场强度Emax与l之间大致呈Emax随l增大而减小的规律,这是因为随着l的增大,不同电位的铜层之间的爬电距离和电气间隙都增大,因此绝缘性能也增加;该DBC中,Emax与d没有明显规律,且变化幅度小于l对电场的影响,因此对于本文的DBC布局,相比于d对电场的影响,上铜层间的电位差对于电场影响更显著;此外,从图4看出,d和l对于电场强度的影响存在一定耦合作用,二者对于电场的作用会相互影响,导致当l≥1mm时,Emax与l的关系不再是单调的负相关关系。为确保模块的绝缘性能,取d=1.0mm、l=2.4mm作为DBC上铜层的尺寸参数,即初步优化结果,此时电场强度较低,绝缘性能足够,各铜层间的爬电距离也留有一定裕度。

图4 电场优化结果

Fig.4 Electric field optimization results

对于SiC MOSFET器件,其具有高开关速度、高开关频率的优势,这可以使设备的功率密度和效率得到提高。但是由于寄生电容和寄生电感的存在,器件开关过程中的高dv/dt和di/dt会引起电磁干扰(Electromagnetic Interference, EMI)问题[17],尤其需注意寄生电容的影响。电位变化导致的高dv/dt通过寄生电容产生共模电流,然后共模电流通过大地形成回路流向控制侧,对其产生影响并耦合回功率回路侧,严重时会导致器件甚至设备损坏[30]。因此降低寄生电容有利于高压SiC MOSFET模块可靠工作。

从电路级考虑,通常通过改变拓扑或集成无源滤波器实现对共模电流的抑制,但这样会增加设计的复杂程度或降低功率密度。从功率模块封装的角度出发,可以通过在DBC下铜层处引入低介电常数层(如空气、硅凝胶),将陶瓷层的寄生电容与空气层寄生电容串联以此来降低模块对地的寄生电容,或者通过增大陶瓷层厚度降低寄生电容,进而降低共模电流[17]。但需要注意,DBC下铜层和陶瓷层厚度的改变也会影响模块的寿命[15, 31-32]和电场分 布[33]。因此,提出一种高压SiC功率模块多目标加权优化方法,综合考虑模块各性能量化指标,即电场强度峰值、寄生电容以及焊料层热应力,对其进行权衡,选择最优参数保证其整体性能优异。

1.2.1 寄生电容

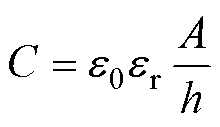

对于6.5kV SiC MOSFET模块的DBC而言,其工作过程中可能引起共模电流的寄生电容包括源极、漏极、栅极和开尔文源极寄生电容。其中,电容的计算公式为

(2)

(2)

式中, 为真空介电常数,

为真空介电常数, =8.85nF/m;

=8.85nF/m; 为介质的相对介电常数(对于DBC即Al2O3层,典型值取9.8);A为电极(对于DBC即上铜层电极)面积(mm2);h为介质(对于DBC即陶瓷层)厚度(mm)。

为介质的相对介电常数(对于DBC即Al2O3层,典型值取9.8);A为电极(对于DBC即上铜层电极)面积(mm2);h为介质(对于DBC即陶瓷层)厚度(mm)。

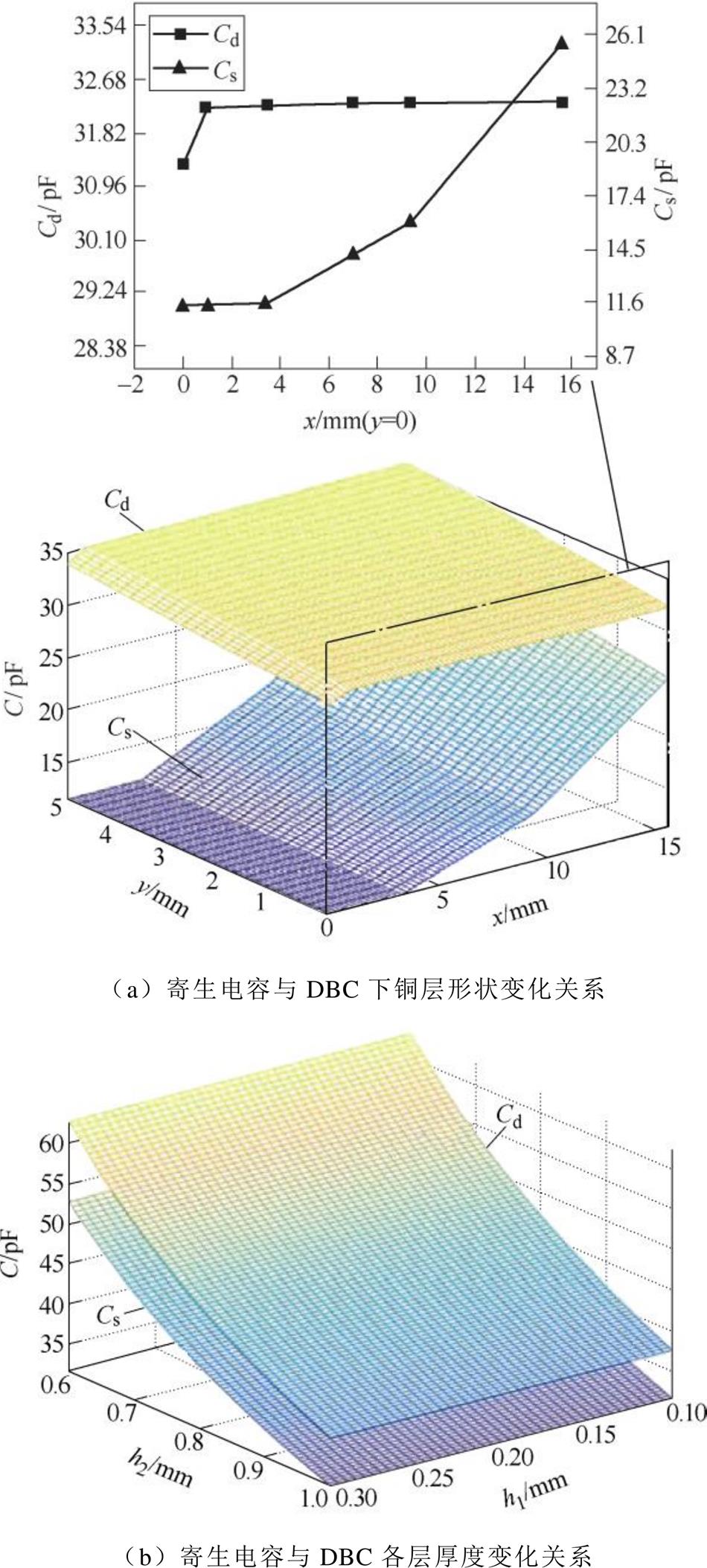

由式(2)可知,影响电容大小的因素包括厚度和电极面积。本文DBC的对地寄生电容分布如图5所示,包括源极Cs、漏极Cd,均由相应陶瓷层寄生电容和引入的低介电常数层寄生电容串、并联而成。

图5 对地寄生电容分布

Fig.5 Distribution of parasitic capacitance to ground

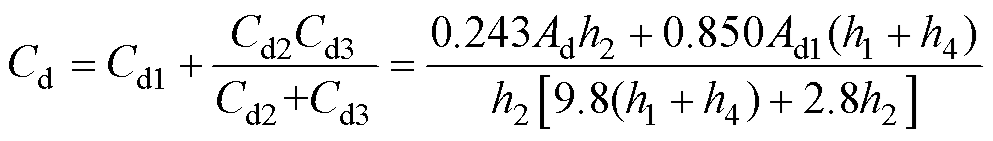

Cd、Cs理论计算表达式分别为

(3)

(3)

(4)

(4)

式中,Ad、As分别为漏极和源极上铜层面积(mm2);Ad1、As1分别为漏极和源极对应下铜层面积(见图5中红线部分)(mm2);h1、h2、h3、h4分别为上铜层厚度(mm)、陶瓷层厚度(mm)、下铜层厚度(mm)、DBC与基板间焊料层厚度(mm);Cd3、Cs3计算时取硅凝胶介电常数,其典型值为2.8pF。

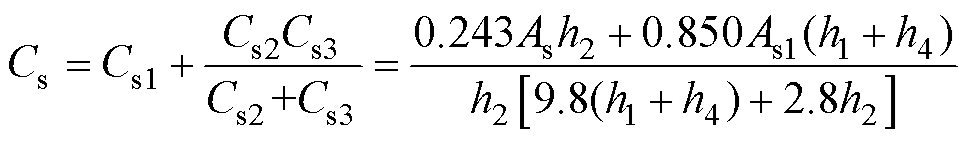

从式(3)和式(4)可知,模块漏极和源极的寄生电容与其对应下铜层面积成正比,因此为使寄生电容尽可能小,应使其面积尽可能小。但是DBC下铜层面积和形状设计需保证芯片能通过下方DBC传递热量,防止芯片因工作温度过高而烧毁,所以其面积存在下限。DBC优化前后的下铜层如图6所示。热传导过程包括横向和纵向,所以需要考虑热扩散角,根据文献[34]得到铜层热扩散角正切值约为0.3,氧化铝陶瓷热扩散角正切值约为2.66,并考虑一定裕度,得到可使寄生电容最小的下铜层形状如图6b所示,即二次优化后DBC。

图6 DBC优化前后的下铜层

Fig.6 Lower copper layers of DBC before and after optimization

图6a为传统设计的DBC下铜层。x、y为DBC从二次优化到传统设计的过渡尺寸参数(见图6b中虚线为传统设计DBC下铜层形状)。

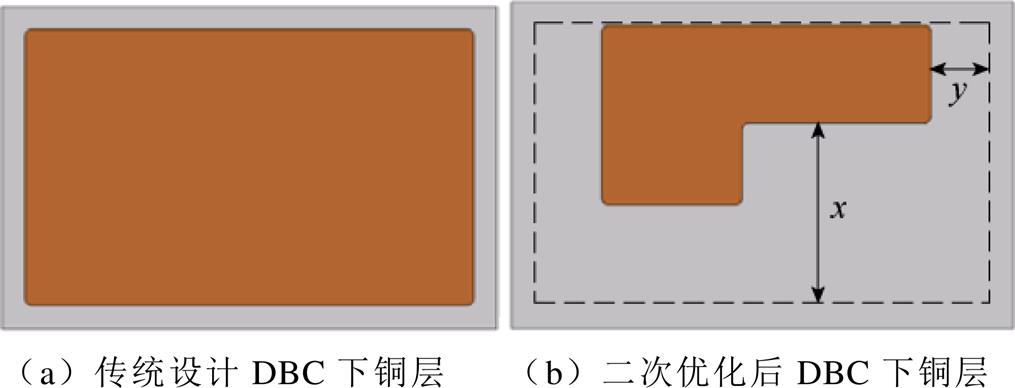

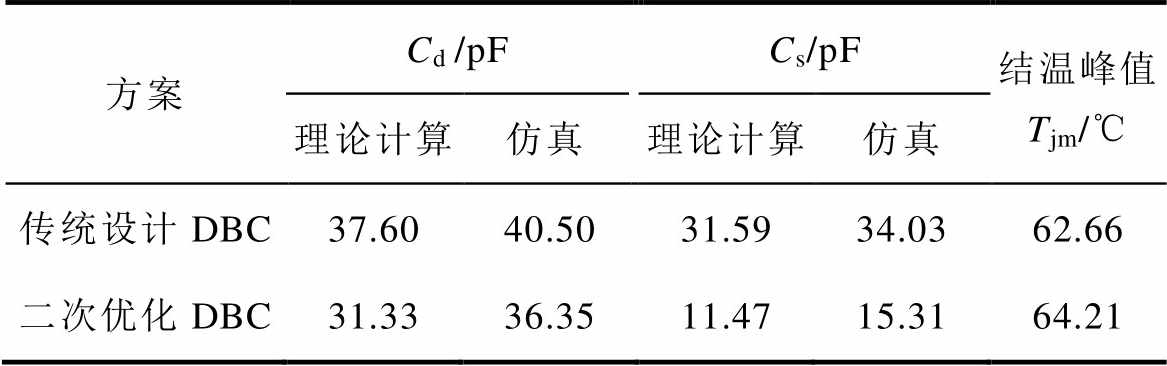

通过理论计算和仿真得到寄生电容Cd、Cs以及同一条件下仿真得到的温度峰值,结果见表1。从表中看出:相对理论计算结果,利用有限元软件提取的寄生电容结果会稍大,这是因为实际结构更复杂,仅用平行板电容器式(2)计算不够准确,但各值相对大小较为接近。相对于优化前(传统设计),无论是理论计算或软件提取结果,都可以看出,二次优化后DBC对地电容(尤其是源极电容)得以降低,从而降低EMI,增加系统可靠性;优化前后模块温度峰值较为接近,所以在考虑热扩散角并留有一定裕度的基础上进行优化对模块散热性能影响较小。除DBC下铜层设计外,DBC各层厚度也对寄生电容有显著影响,这里主要对DBC进行优化,所以焊料层厚度h4选为定值0.2mm,且取上铜层厚度与下铜层厚度相等,即h1=h3。

表1 优化前后寄生电容和温度峰值对比

Tab.1 Comparison of parasitic capacitance and peak temperature before and after optimization

方案Cd /pFCs/pF结温峰值Tjm/℃ 理论计算仿真理论计算仿真 传统设计DBC37.6040.5031.5934.0362.66 二次优化DBC31.3336.3511.4715.3164.21

图7为DBC下铜层形状和各层厚度对寄生电容的影响效果。当y一定、x增加时,As1会显著增大,且呈现初始增加缓慢、然后迅速增加的规律,导致Cs增大;而Ad1只在最开始会少量增加,之后基本不再变化,所以总体来看Cd只少量增大,基本保持不变。随着y增大,Cs和Cd也会增大,而且会导致Dx一定时,DBC对地电容增加幅度变大。综上所述,DBC对地寄生电容与下铜层形状存在显著关系,但是具体规律需要结合实际DBC布局等因素进行考虑。

图7 6.5kV SiC MOSFET模块寄生电容变化关系

Fig.7 Variation of parasitic capacitance of 6.5kV SiC MOSFET module

对于DBC厚度因素来说,陶瓷层厚度与寄生电容呈明显负相关,影响显著;而铜层本身不引入寄生电容,它是通过影响硅凝胶层的厚度进而影响寄生电容,由于该层厚度较小,所以对于DBC对地寄生电容影响较小。

1.2.2 焊料层热应力

从1.2.1节可知,通过优化DBC下铜层形状及各层厚度可以降低寄生电容,但优化过程中需注意其对于模块的寿命也存在较大影响。

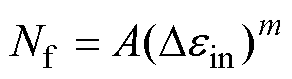

由于模块内部各层材料热膨胀系数(Coefficient Thermal Expansion, CTE)不匹配,因此在工作过程中不同层会产生不同的形变,导致作为不同材料层连接部分的焊料层产生较大的非弹性应变和应力,这些非弹性应变不断累积导致焊料层断裂或分层,最终导致其疲劳失效及弯曲变形,即双金属效应,这对于模块寿命存在严重影响[35],则应用广泛的基于应变的Coffin-Manson模型为

(5)

(5)

式中, 为应变;Nf为模块寿命;m为负值。因此焊料层热应力、应变对功率半导体模块寿命存在显著影响。文献[26, 31-32]给出应力的理论计算模型,影响DBC下铜层与基板间焊料层应力的因素除各层材料的热膨胀系数和温度差外,也与其体积有关,即其值与各层材料面积和厚度均有关。

为应变;Nf为模块寿命;m为负值。因此焊料层热应力、应变对功率半导体模块寿命存在显著影响。文献[26, 31-32]给出应力的理论计算模型,影响DBC下铜层与基板间焊料层应力的因素除各层材料的热膨胀系数和温度差外,也与其体积有关,即其值与各层材料面积和厚度均有关。

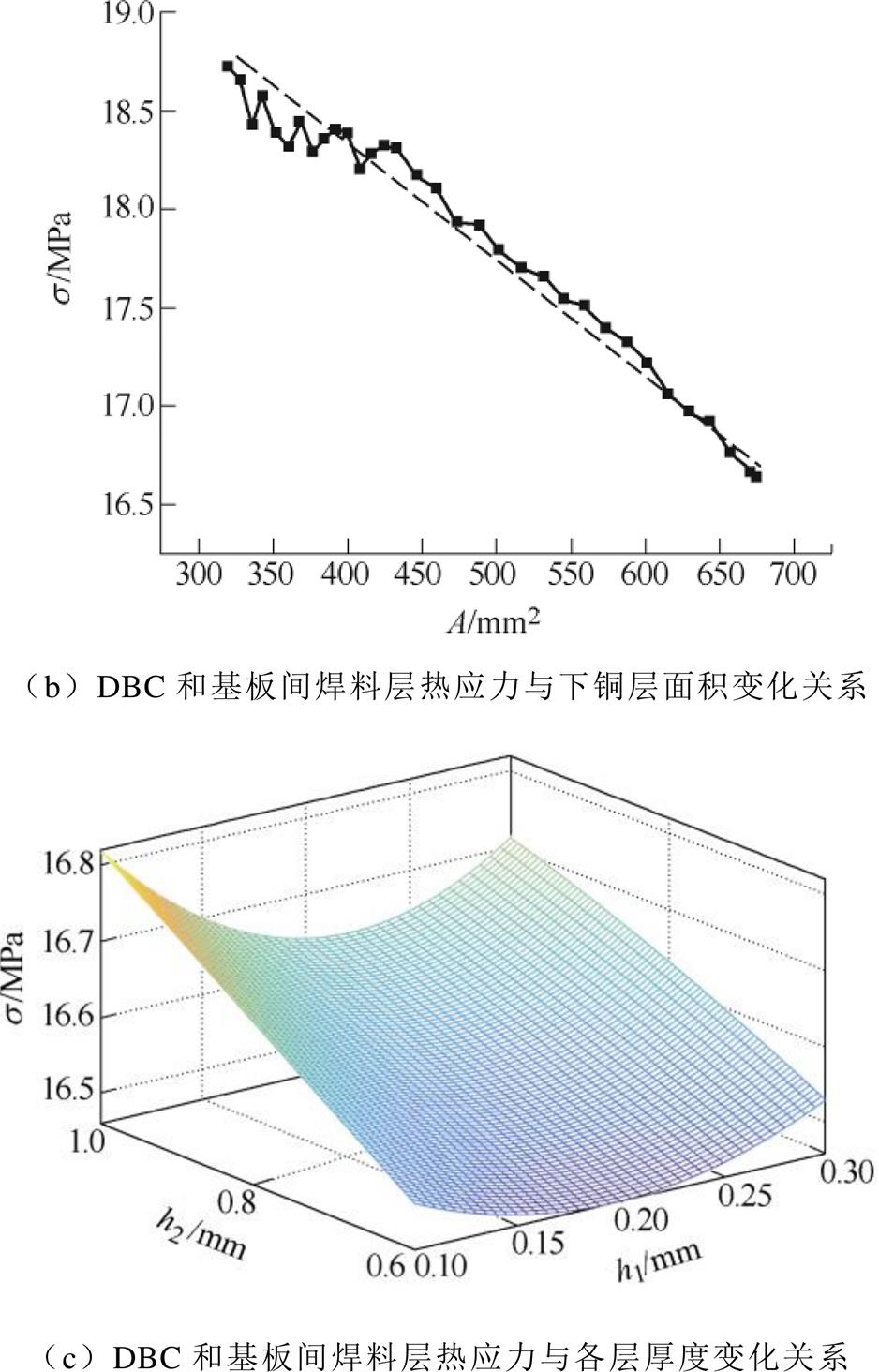

DBC与基板间焊料层的面积往往取决于DBC下铜层面积,因此对于1.2.1节通过优化下铜层形状和面积来减小对地寄生电容的方法,也会导致焊料层的面积减小,影响其应力分布进而影响模块寿命。通过有限元仿真软件建立热-力耦合有限元模型,二次优化和传统设计两种情况下DBC与基板间焊料层的平均热应力分别是18.72MPa和15.77MPa。可以看出,相比于优化前的模块,二次优化后DBC与基板间焊料层的平均热应力增加约18.71%,因此在优化寄生电容时也要考虑其对该焊料层热应力和模块寿命的影响,需在图6b的基础上逐渐增大下铜层面积,以保证寄生电容较小的同时,热应力也比较小,进行二者之间的权衡与折中。仿真中采用的SAC305焊料应该被视为粘塑性材料,因此采用准确度较高的Anand本构方程来表达材料的弹塑性应力应变关系[36]。

如图6b所示,为折中寄生电容和模块寿命,DBC下铜层面积增大的方向可以是x或y两种,具体可根据模块所处位置选择。若该SiC MOSFET模块在半桥上桥臂工作,则在换流过程中源极铜层电位变化剧烈,Cs影响增大,产生的共模电流也增大,因此可以通过增大y来减小Cs;若是模块在半桥下桥臂工作,则在换流过程中漏极铜层电位变化剧烈,Cd影响更大,因此可以通过增大x来减小Cd。本文模块工作情况未定,但由于1.2.1节中为满足芯片散热,DBC对地电容Cd已经较大,所以增大x,通过牺牲Cs来折中模块寿命,而Cd基本保持不变,此时DBC和基板间焊料层的平均热应力变小,增加模块寿命,提高可靠性。由于理论计算热应力十分复杂,所以本节通过有限元仿真获得DBC和基板间焊料层平均热应力与x的关系曲线,如图8a所示。由图8a可知,DBC与基板间焊料层平均热应力与x呈分段线性关系。其中,当x≤7mm时,焊料层热应力下降速率较慢;当x>7mm时,焊料层热应力下降速率较快,原因是相同Dx下后者的焊料层面积变化量更大。如图8b所示为DBC与基板间焊料层平均热应力与下铜层面积的关系,可以看出,二者呈明显负相关,且近似线性变化。

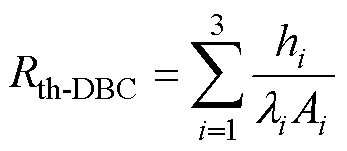

除DBC下铜层形状外,由式(6)可知,各层厚度会决定DBC热阻大小,进而通过结温影响焊料层热应力,最终作用于模块寿命乃至可靠性,因此通过有限元仿真获得DBC与基板间焊料层平均热应力与各层厚度间的关系,结果如图8c所示。

(6)

(6)

图8 DBC和基板间焊料层热应力变化关系

Fig.8 Variation of thermal stress in solder layer between DBC and substrate

式中,hi为DBC各层厚度(mm);li为各材料热导率(W/(m·K));Ai为传热面积(mm2)。

从图8c中可知,DBC各层厚度通过热阻对焊料层热应力产生影响。其中,相比于铜层厚度,陶瓷层厚度对于焊料层热应力影响更为显著,这是因为铜热导率是氧化铝的10倍以上,在DBC热阻的占比较小,所以对焊料层应力影响也较小。焊料层热应力与陶瓷层厚度近似呈线性负相关。

1.2.3 电场分布

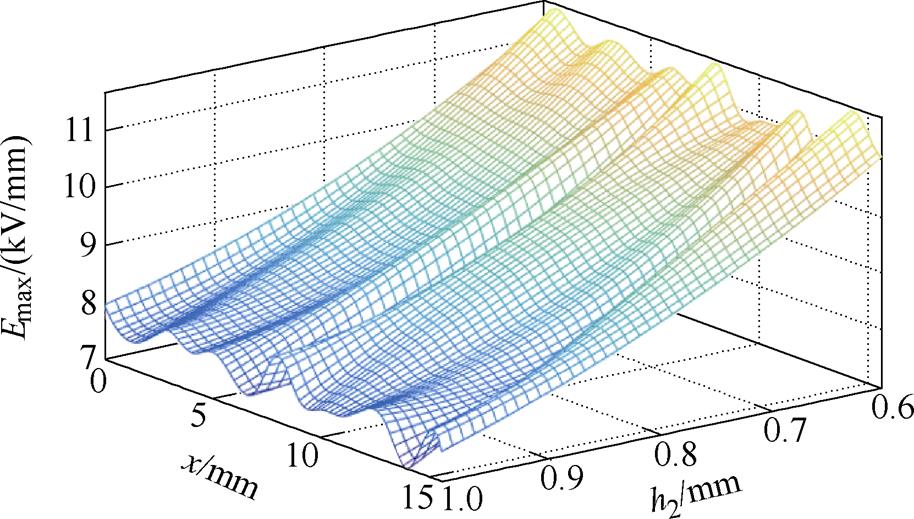

在优化寄生电容时,除需考虑模块寿命的权衡和折中外,也需考虑DBC下铜层尺寸变化和DBC各层厚度变化时对电场的影响。对于DBC,其上、下铜层与陶瓷层边缘间的距离会影响电位线分布,进而影响电场分布[33];而各层厚度,尤其是陶瓷层厚度更会极大地影响电场强度峰值,陶瓷层厚度越大,电场强度峰值越小。因此,在优化DBC下铜层形状和DBC陶瓷层厚度的过程中,同样需要考虑电场分布,以保证该6.5kV SiC MOSFET模块在优化寄生电容的同时,也满足模块绝缘性能要求。6.5kV SiC MOSFET模块电场强度变化关系如图9所示,随着陶瓷层厚度h2的增加,电场强度峰值明显呈降低趋势,近似线性;而随着x的增加,由于电位线变化引起的电场畸变会对电场强度峰值产生影响,但是这种影响没有明显分布规律。

图9 6.5kV SiC MOSFET模块电场强度变化关系

Fig.9 Variation of electric field strength of 6.5kV SiC MOSFET module

1.2.4 多目标加权优化

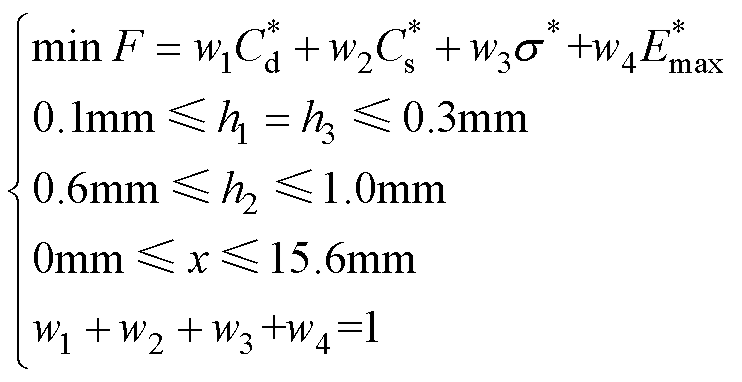

对于本文设计的6.5kV SiC MOSFET模块,可以通过对DBC优化实现电场强度峰值、寄生电容以及焊料层热应力3个参数的折中,具体方法是:通过优化DBC各层厚度(h1、h2、h3)和下铜层形状(本文量化为x)3个尺寸参数,从电场强度峰值、寄生电容以及焊料层热应力(Emax、Cd、Cs和s)的角度寻找使模块整体性能最优的解。本节将DBC设计优化问题视为多目标优化问题,因为线性加权法具有简单便捷的优势,而且电场强度与x关系不规则,若拟合成函数会导致分布规律的失真,本文采用线性加权法并结合模型数据对DBC进行多目标优化,其目标函数和约束条件为

(7)

(7)

式中,F为目标函数,是对各性能参数标准化后加权求和得到的指标,其值越小表示模块整体性能越优;wi为加权因子(即权重),用百分数表示。

式(7)中加权因子wi的具体数值可以根据不同应用场景进行选择,比如:当应用场景没有特殊要求时,可以取w1+w2=w3=w4=33.33%,且w1=w2;当处于高频工况时,由于SiC模块的高dv/dt,对寄生电容要求更高,则取更大的w1、w2;若更注重高压工况下模块的绝缘性能,则取更大的w4等。

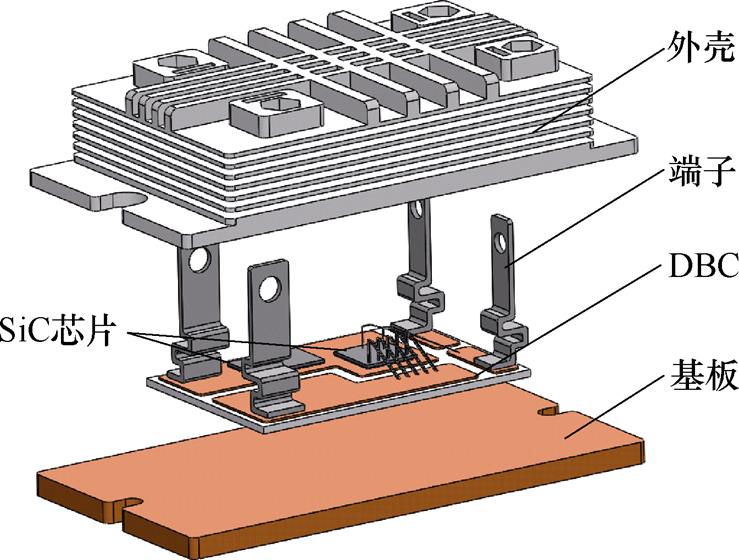

本文针对的是高压模块应用中模块整体性能的设计问题,所以取w1+w2=w3=w4=33.33%,且w1= w2=16.67%,多目标加权优化指标与DBC尺寸参数关系如图10所示,其中3个坐标轴表示3个优化的尺寸参数,颜色表示第四维,即加权优化指标F,颜色越鲜艳表示F值越大,整体性能越差。

从图10明显看出,F分布规律:随着h1、h2、x的增大,颜色越深,F值越小,模块的整体性能呈上升趋势。其中,铜层厚度h1对F影响比较小,而陶瓷层厚度h2和下铜层形状量化指标x对于整体性能指标F影响更加显著。结合数据和图像得到,当h1=h3=0.24mm、h2=1.0mm、x=14.0mm时,F最小,即整体性能最优。

图10 多目标加权优化指标与DBC尺寸参数关系

Fig.10 Relation between weighted optimization index and dimension parameters of DBC

然后通过仿真对比传统设计、二次优化后及加权优化后的模块性能见表2。由表2可知,多目标加权优化后DBC的F值最小,即整体性能最优。相比传统设计DBC(见图6a),加权优化后电场强度峰值、寄生电容都有明显降低,但是温度峰值和焊料层的平均热应力有一定提升,说明确实实现模块性能的折中,牺牲一定模块寿命提升模块绝缘性能并降低寄生电容参数,对于高压和高频工况下应用具有一定优势,且不同于较为极端的二次优化(见图6b),不会过多牺牲模块寿命来换取寄生电容的降低,甚至会影响绝缘性能乃至整体性能。通过多目标加权优化方法,实现在不增加陶瓷层厚度的同时降低电场强度,增强绝缘性能,这优于往常依照经验选择的结果。此外,栅极和开尔文源极的对地寄生电容也从4.9pF减小到2.7pF左右,降低近44.9%。

表2 优化前后模块性能对比

Tab.2 Comparison of performance before and after optimization

方案FCd/pFCs/pFs/MPaEmax/(kV/mm)Tjm/℃ 传统设计DBC0.2640.5034.0316.778.0062.66 二次优化DBC0.3736.3515.3118.727.8964.21 加权优化DBC0.1537.6528.1716.946.2463.69

针对不同工况或者对某一性能参数特别看重的情况时,采用提出的多目标加权优化方法可以通过牺牲某些在该工况下相对不重要的参数提高其他性能,尤其适用于对SiC模块的开关速度和绝缘性能要求较高的应用场景。本文是针对单面散热模块进行设计,但该设计方法对于其他封装结构(如双面散热模块)同样成立。

除上述性能参数外,模块寄生电感和外部绝缘性能也是高压模块需要注意的参数。本文的6.5kV SiC MOSFET模块寄生电感主要集中在键合线和端子上,前者与芯片电极面积有关,其决定于键合线根数和键合线直径,也可以通过优化结构减小由键合线引入的寄生电感[18]。由于本文模块只有两个芯片,结构较为简单,所以技术方案主要针对后者,通过尽可能减小端子长度降低模块寄生电感,需要注意的是,当端子较短时,外壳高度也会降低,这会使外部电气间隙和爬电距离的设计难度增加,尤其是对外部端子和基板间爬电距离的设计。本节通过在外壳增加凸起、凹槽等结构,在满足GB 4943.1- 2011对外部绝缘要求的同时[37],尽可能减小端子长度,以降低寄生电感,最终设计出的模块如图11所示,通过仿真得到其包含端子和键合线在内的功率回路寄生电感为23.02nH。

图11 6.5kV SiC MOSFET模块示意图

Fig.11 Schematic diagram of 6.5kV SiC MOSFET module

为验证提出的高压SiC模块封装设计方法的可行性,根据第1节设计结果研制6.5kV SiC MOSFET模块,并进行实验测试和验证。

最终得到6.5kV SiC MOSFET模块实物,如图12所示,其内部芯片采用南京电子器件研究所的6.5kV/25A SiC MOSFET芯片和6.5kV/25A SiC SBD芯片。芯片经过回流焊、键合、灌封、抽真空、烘干等工艺,最终形成模块,模块内部采用15mil(1mil= 25.4×10-6m)铝线引出SiC MOSFET源极和SiC SBD阳极,用5mil铝线引出SiC MOSFET栅极和开尔文源极。

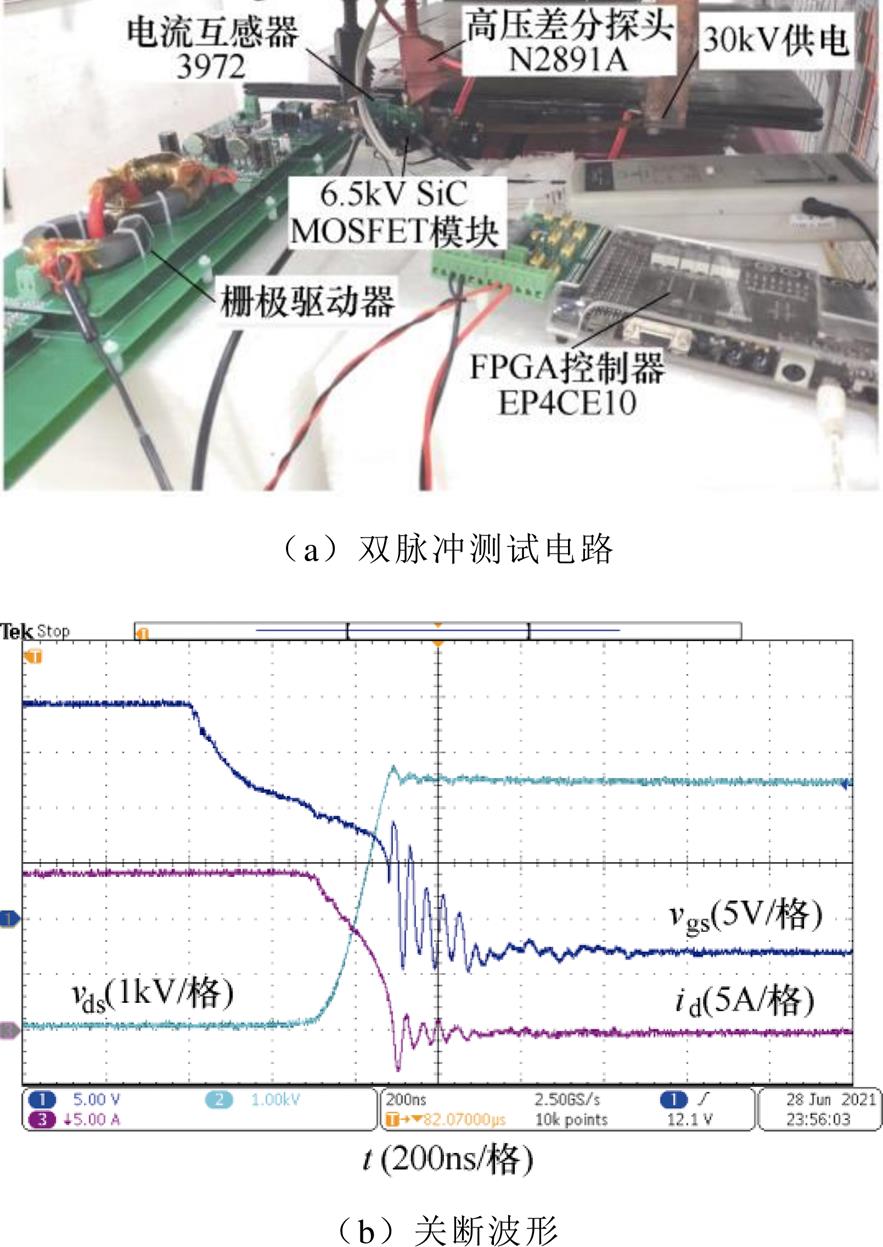

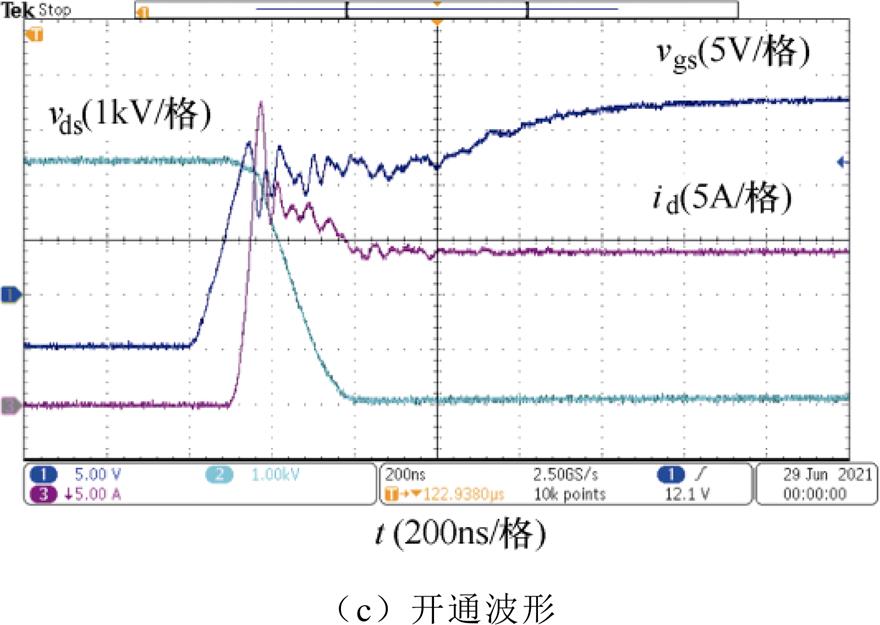

首先,为验证所研制高压SiC模块在高压条件下的动态特性,搭建双脉冲测试电路如图13a所示,测得直流母线电压为4 500V,栅极电阻为15Ω,负载电流为14A时的开关波形,如图13b、图13c所示。由图13可知:该模块的开通延迟时间为78ns(开通延迟时间定义为10%栅极电压到10%导通电流),上升时间为33ns(上升时间定义为10%导通电流到90%导通电流),dv/dt达到26.47V/ns;关断延迟时间为195ns(关断延迟时间定义为90%栅极电压到90%导通电流),下降时间为162ns(下降时间定义为90%导通电流到10%导通电流),dv/dt达到32.61V/ns,这对寄生电容参数提出较高要求。

图12 6.5kV SiC MOSFET模块实物

Fig.12 Physical view of 6.5kV SiC MOSFET module

图13 6.5kV SiC MOSFET模块双脉冲测试

Fig.13 Double pulse test of 6.5kV SiC MOSFET module

经过计算得到该模块开通、关断损耗分别为10.31mJ(开通损耗定义为10%导通电流到10%母线电压之间的模块功耗)、2.46mJ(关断损耗定义为10%母线电压到10%导通电流之间的模块功耗)。此外,关断过程中由于寄生电感产生的电压过冲约280V,仅为6.22%,说明模块寄生电感较小。

寄生参数测试包括寄生电容和寄生电感,本节均采用安捷伦4294A精密阻抗分析仪进行测量。寄生电容测试结果见表3,相比于传统设计DBC,加权优化后DBC各电极对地寄生电容都有明显优化,且数值与仿真结果相近,在应用时会降低系统的电磁干扰问题,说明多目标加权优化方法的有效性。

表3 寄生电容对比(1MHz)

Tab.3 Comparison of parasitic capacitance (1MHz)

方案漏极寄生电容/pF源极寄生电容/pF栅极寄生电容/pF开尔文源极寄生电容/pF 传统设计DBC40.533.744.894.91 加权优化DBC36.3329.141.711.56

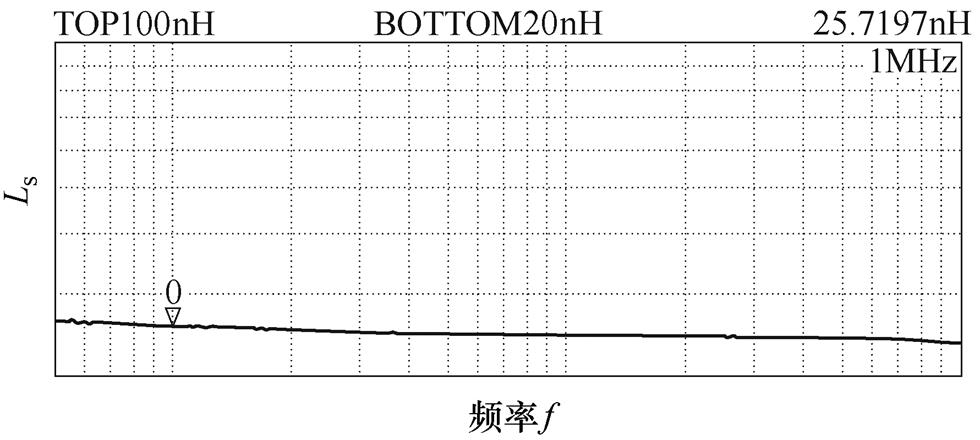

对于寄生电感参数的测试,忽略芯片自身寄生参数,在不焊接芯片的情况下用键合线连接DBC各铜层,得到1MHz下模块寄生电感为25.72nH,6.5kV SiC MOSFET模块寄生电感如图14所示,与仿真结果接近。

图14 6.5kV SiC MOSFET模块寄生电感

Fig.14 Parasitic inductance of 6.5kV SiC MOSFET module

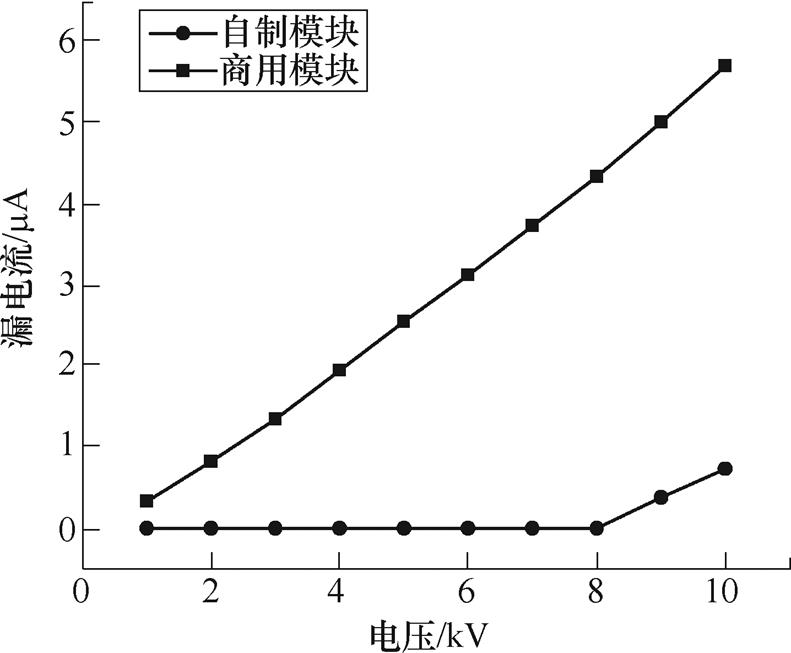

通过耐压测试实现对绝缘性能的验证,测试时将功率模块所有输出端子短接,在端子与基板之间施加直流高压,故实际被测试的为DBC与灌封材料构成的绝缘系统。结果得到不同电压下自研6.5kV SiC MOSFET和商用英飞凌6.5kV Si IGBT (FD250R65KE3-K)模块的漏电流曲线如图15所示。多目标加权优化后的模块在DC 10kV下的漏电流小于1μA,绝缘性能良好,而且其绝缘性能优于商用模块,说明本文设计在降低寄生电容的同时也保证了较优的绝缘性能。

图15 不同电压下6.5kV SiC MOSFET封装的漏电流

Fig.15 Leakage current of modules at different voltages

针对高压SiC模块的封装技术挑战,本文提出多目标加权优化方法,对6.5kV SiC MOSFET模块的绝缘性能、寄生参数、热管理问题进行研究和优化,且可以针对不同工况或要求实现性能参数的折中和优化。首先,在对DBC初步优化后,通过建立有限元模型对模块内部的电场强度峰值、寄生电容以及焊料层热应力建模,进行多目标加权优化,选择最优参数并通过仿真证明其相比于传统设计方法的优势;然后,考虑模块寄生电感与外部绝缘的矛盾,对外壳进行设计优化;最后,基于上述设计研制出6.5kV SiC MOSFET模块实物,通过实验测试其动态性能,说明模块能够在4 500V/14A的条件下可靠工作,其电流上升、下降时间分别为33ns、162ns,开通、关断损耗分别为10.31mJ、2.46mJ。此外,通过寄生参数测试和耐压测试再次验证提出的多目标加权优化方法的有效性,也展示出该6.5kV SiC MOSFET封装相比于商用6.5kV Si IGBT具有更低的漏电流。对于高压封装问题的优化,未来会将材料选择纳入设计方法,以完善高压模块封装方案。

参考文献

[1] 黄小娟, 王晓丽. 6500V/600A IGBT自主化封装研制与应用[J]. 电力电子技术, 2020, 54(8): 128-131.

Huang Xiaojuan, Wang Xiaoli. Development and app- lication of 6500V/600A IGBT self-contained package[J]. Power Electronics, 2020, 54(8): 128-131.

[2] Hinojosa M, O'Brien H, Van Brunt E, et al. Solid- state Marx generator with 24kV 4H-SIC IGBTs[C]// IEEE Pulsed Power Conference (PPC), Austin, TX, 2015: 1-5.

[3] Ji Shiqi, Zhang Zheyu, Wang Fei. Overview of high voltage SiC power semiconductor devices: development and application[J]. CES Transactions on Electrical Machines and Systems, 2017, 1(3): 254-264.

[4] Zhang Hao, Ang S S, Mantooth A, et al. A 6.5kV wire-bondless, double-sided cooling power electronic module[C]//2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, 2012: 444-450.

[5] 刘国友, 黄建伟, 覃荣震, 等. 高压大电流(4500V/ 600A)IGBT芯片研制[J]. 电工技术学报, 2021, 36(4): 810-819.

Liu Guoyou, Huang Jianwei, Qin Rongzhen, et al. Development of large size IGBT chip with high power capacity of 4500V/600A[J]. Transactions of China Electrotechnical Society, 2021, 36(4): 810-819.

[6] DiMarino C M, Mouawad B, Johnson C M, et al. 10kV SiC MOSFET power module with reduced common-mode noise and electric field[J]. IEEE Transactions on Power Electronics, 2020, 35(6): 6050- 6060.

[7] Huang A Q, Zhu Qianlai, Wang Li, et al. 15kV SiC MOSFET: an enabling technology for medium voltage solid state transformers[J]. CPSS Transa- ctions on Power Electronics and Applications, 2017, 2(2): 118-130.

[8] DiMarino C M, Mouawad B, Johnson C M, et al. Design and experimental validation of a wire-bond- less 10kV SiC MOSFET power module[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 381-394.

[9] Palmour J W, Cheng Lin, Pala V, et al. Silicon carbide power MOSFETs: breakthrough performance from 900V up to 15kV[C]//2014 IEEE 26th Inter- national Symposium on Power Semiconductor Devices & IC's (ISPSD), Waikoloa, HI, 2014: 79-82.

[10] 李士颜, 杨晓磊, 黄润华, 等. 15kV/10A SiC功率MOSFET器件设计及制备[J]. 固体电子学研究与进展, 2021, 41(2): 93-97.

Li Shiyan, Yang Xiaolei, Huang Runhua, et al. Simulation and fabrication of 15kV/10A SiC power MOSFET[J]. Research & Progress of SSE, 2021, 41(2): 93-97.

[11] 金晓行, 李士颜, 田丽欣, 等. 6.5kV高压全SiC功率MOSFET模块研制[J]. 中国电机工程学报, 2020, 40(6): 1753-1758.

Jin Xiaoxing, Li Shiyan, Tian Lixin, et al. Fabrication of 6.5kV high-voltage full SiC power MOSFET modules[J]. Proceedings of the CSEE, 2020, 40(6): 1753-1758.

[12] Tousi M M, Ghassemi M. Electric field control by nonlinear field dependent conductivity dielectrics characterization for high voltage power module packaging[C]//2019 IEEE International Workshop on Integrated Power Packaging (IWIPP), Toulouse, 2019: 54-58.

[13] 李俊杰, 梅云辉, 梁玉, 等. 功率器件高电压封装用复合电介质灌封材料研究[J]. 电工技术学报, 2022, 37(3): 786-792.

Li Junjie, Mei Yunhui, Liang Yu, et al. Study on composite dielectric encapsulation materials for high voltage power device packaging[J]. Transactions of China Electrotechnical Society, 2022, 37(3): 786-792.

[14] Wang Ningyan, Cotton I, Robertson J, et al. Partial discharge control in a power electronic module using high permittivity non-linear dielectrics[J]. IEEE Transactions on Dielectrics and Electrical Insulation, 2010, 17(4): 1319-1326.

[15] Cao Xiao, Wang Tao, Ngo K D T, et al. Parametric study of joint height for a medium-voltage planar package[J]. IEEE Transactions on Components and Packaging Technologies, 2010, 33(3): 553-562.

[16] Reynes H, Buttay C, Morel H. Protruding ceramic substrates for high voltage packaging of wide band- gap semiconductors[C]//2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, NM, 2017: 404-410.

[17] Shin J W, Wang Chiming, Dede E M. Power semi- conductor module with low-permittivity material to reduce common-mode electromagnetic interference[J]. IEEE Transactions on Power Electronics, 2018, 33(12): 10027-10031.

[18] 李宇雄. 基于层叠DBC的低杂散参数SiC混合封装集成模块关键技术研究[D]. 武汉: 华中科技大学, 2018.

[19] 刘东明, 李学宝, 顼佳宇, 等. 高压SiC器件封装用有机硅弹性体高温宽频介电特性分析[J]. 电工技术学报, 2021, 36(12): 2548-2559.

Liu Dongming, Li Xuebao, Xu Jiayu, et al. Analysis of high temperature wide band dielectric properties of organic silicone elastomer for high voltage SiC device packaging[J]. Transactions of China Electrotechnical Society, 2021, 36(12): 2548-2559.

[20] Lee H, Smet V, Tummala R. A review of SiC power module packaging technologies: challenges, advances, and emerging issues[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 239-255.

[21] 盛况, 董泽政, 吴新科. 碳化硅功率器件封装关键技术综述及展望[J]. 中国电机工程学报, 2019, 39(19): 5576-5584, 5885.

Sheng Kuang, Dong Zezheng, Wu Xinke.Review and prospect of key packaging technologies for silicon carbide power devices[J]. Proceedings of the CSEE, 2019, 39(19): 5576-5584, 5885.

[22] 刘国友, 罗海辉, 张鸿鑫, 等. 基于全铜工艺的750A/6500V高性能IGBT模块[J]. 电工技术学报, 2020, 35(21): 4501-4510.

Liu Guoyou, Luo Haihui, Zhang Hongxin, et al. High performance 750A/6500V IGBT module based on full-copper processes[J]. Transactions of China Elec- trotechnical Society, 2020, 35(21): 4501-4510.

[23] 能立强, 梅云辉, 陆国权. 基于多物理场仿真的平面封装SiC模块长寿命设计[J]. 中国电机工程学报, 2020, 40(6): 1769-1774.

Neng Liqiang, Mei Yunhui, Lu Guoquan. Reliability design for planar multi-chip SiC modules based on electro-thermo-mechanical simulation[J]. Proceedings of the CSEE, 2020, 40(6): 1769-1774.

[24] Passmore B S, Lostetter A B. A review of SiC power module packaging technologies: attaches, intercon- nections, and advanced heat transfer[C]//2017 IEEE International Workshop on Integrated Power Packaging (IWIPP), Delft, 2017: 1-5.

[25] Yao Yiying, Lu Guoquan, Boroyevich D, et al. Survey of high-temperature polymeric encapsulants for power electronics packaging[J]. IEEE Transactions on Com- ponents, Packaging and Manufacturing Technology, 2015, 5(2): 168-181.

[26] 曾正, 欧开鸿, 吴义伯, 等. 车用双面散热功率模块的热-力协同设计[J]. 电工技术学报, 2020, 35(14): 3050-3064.

Zeng Zheng, Ou Kaihong, Wu Yibo, et al. Thermo- mechanical co-design of double sided cooling power module for electric vehicle application[J]. Transa- ctions of China Electrotechnical Society, 2020, 35(14): 3050-3064.

[27] 曾正, 李晓玲, 林超彪, 等. 功率模块封装的电-热-力多目标优化设计[J]. 中国电机工程学报, 2019, 39(17): 5161-5171, 5297.

Zeng Zheng, Li Xiaoling, Lin Chaobiao, et al. Electric-thermal-stress oriented multi-objective optimal design of power module package[J]. Proceedings of the CSEE, 2019, 39(17): 5161-5171, 5297.

[28] Kawamoto T, Takuma T, Goshima H, et al. Triple- junction effect and its electric field relaxation in three dielectrics[J]. Electrical Engineering in Japan, 2009, 167(1): 1-8.

[29] Fu Pengyu, Zhao Zhibin, Cui Xiang, et al. Electrical field analysis of press-pack IGBTs[C]//2017 Sixth Asia-Pacific Conference on Antennas and Pro- pagation (APCAP), Xi'an, 2017: 1-3.

[30] Ji Shiqi, Zheng Sheng, Wang Fei, et al. Temperature- dependent characterization, modeling, and switching speed-limitation analysis of third-generation 10kV SiC MOSFET[J]. IEEE Transactions on Power Electronics, 2018, 33(5): 4317-4327.

[31] 翟超. IGBT模块封装热应力研究[D]. 杭州: 浙江大学, 2013.

[32] Suhir E. Analysis of interfacial thermal stresses in a trimaterial assembly[J]. Journal of Applied Physics, 2001, 89(7): 3685-3694.

[33] Bayer C F, Baer E, Waltrich U, et al. Simulation of the electric field strength in the vicinity of metal- lization edges on dielectric substrates[J]. IEEE Transactions on Dielectrics and Electrical Insulation, 2015, 22(1): 257-265.

[34] 邓二平. 压接型IGBT器件内部电-热-力多物理场耦合模型研究[D]. 北京: 华北电力大学, 2018.

[35] Jiang Nan, Chen Minyou, Xu Shengyou, et al. Lifetime evaluation of solder layer in an IGBT module under different temperature levels[C]//2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, 2016: 3137-3141.

[36] 欧开鸿, 曾正, 王亮, 等. 双面散热SiC功率模块的可靠性分析和寿命评估[J]. 中国电机工程学报, 2021, 41(9): 3293-3304.

Ou Kaihong, Zeng Zheng, Wang Liang, et al. Reliability analysis and lifetime assessment of double-sided cooling SiC Power Module[J]. Pro- ceedings of the CSEE, 2021,41(9): 3293-3304.

[37] GB 4943.1-2011 信息技术设备安全第1部分: 通用要求[S].

Weighted Optimization Design and Experimental Study of 6.5kV SiC MOSFET Module

Abstract Aiming at the key problems of high voltage SiC module packaging (i.e. insulation performance, parasitic parameters, thermal management), a multi-objective weighted optimization method was proposed in this paper to achieve the trade-off and optimization of multiple performance indexes of 6.5kV SiC MOSFET module. First, the parasitic capacitance, thermal stress of the solder layer and electric field strength were modeled respectively by establishing multi-physics finite element models. The three indexes were weighted and optimized to obtain the optimal dimensional parameters to ensure the overall performance of the 6.5kV SiC MOSFET module. Through the design of the housing and terminals, the parasitic inductance was reduced as much as possible while keeping the external insulation of the module reliable. The parasitic inductance and insulation performance of the module were compromised. Finally, the performance advantages of the developed module and the effectiveness of the multi-objective weighted optimization method were verified through the double pulse test and high potential test. The results show that the developed module can work reliably under the condition of 4 500V/14A. The superiority of the overall performance of the module is guaranteed, while the parasitic parameters and the insulation performance are optimized.

keywords:High voltage SiC MOSFET, packaging, multi-physics field, multi-objective weighted optimization

DOI: 10.19595/j.cnki.1000-6753.tces.212033

中图分类号:TN305.94

国家重点研发计划资助项目(2018YFB0905700)。

收稿日期 2021-12-14

改稿日期 2022-01-04

尚 海 男,1997年生,硕士研究生,研究方向为功率半导体器件封装技术。E-mail: 18833213508@163.com

梁 琳 女,1981年生,研究员,博士生导师,研究方向为功率半导体器件及其应用。E-mail: lianglin@hust.edu.cn(通信作者)

(编辑 陈诚)