图1 E-mode型GaN器件结构示意图

Fig.1 Structure of E-mode GaN device

摘要 GaN器件较传统Si器件具有耐高压、耐高温、导通电阻小和开关损耗小等优势,但其特有的动态导通电阻现象是限制其大规模应用的主要问题。该文基于动态导通电阻影响机理分析,首先提出一种GaN器件动态导通电阻综合测试平台及测试方法;然后测试了三款同电压/电流等级、不同结构GaN器件在各影响因素下的动态导通电阻,分析影响因素占比及动态导通电阻变化规律,与机理分析进行对比验证;最后从器件应用角度给出动态导通电阻优化方法。该文提出的测试平台测试变量基本涵盖实际应用中的全部动态导通电阻影响因素。实验表明,不同结构GaN器件动态导通电阻特性不同,且占主导的动态导通电阻影响因素不同。从应用层面优化动态导通电阻,可有效降低通态损耗。

关键词:GaN器件 电流崩塌效应 动态导通电阻 精确测试 优化应用方法

相较于传统硅(Silicon, Si)器件,氮化镓(Gallium Nitride, GaN)功率半导体器件因其材料特性可工作于更高的电压应力、更快的开关频率,具有更大的温度容限,更适用于高频、高功率密度的应用场合[1-2]。然而,其在实际应用中也存在一系列的可靠性问题和挑战[3-5],其中以电流崩塌效应最为显著、影响最大。该效应在器件具体参数上表现为动态导通电阻[6-7]。

GaN器件在关断状态承受漏源极高电压,当切换到开通状态时,导通电阻暂时增加、最大漏极电流减小[8-9];在不同条件下,导通电阻呈现出一定规律的动态变化。该现象即为动态导通电阻。联合电子设备工程委员会(Joint Electron Device Engineering Council, JEDEC)提出的标准对其给出定义:由于GaN器件在应用期间会遇到各种应力条件,一些电荷可能会被困在晶体管结构的特定区域中,在开关环境中动作时,会导致导通电阻增加[10]。该标准强调了动态导通电阻会产生额外的损耗,从而降低系统的整体效率。因此,在实际应用中,动态导通电阻的存在不仅使得GaN器件的通态损耗无法准确预测和计算,还会对整个系统的可靠性和工作寿命产生影响。

已有文献从器件本体层面研究动态导通电阻发生机理。文献[11]通过对增强型GaN器件的栅极和漏极分别施加脉冲,测试器件在不同高压开关条件下出现的电流崩塌效应程度,得出栅极和漏极诱导的表面陷阱捕获是引起电流崩塌效应的主要原因。文献[12]研究温度、电场、热电子或其组合对电流崩塌的影响程度,通过观察电致发光信号的强弱,发现栅极与漏极之间的存储区中热电子引起的电子捕获是造成电流崩塌的主要原因。文献[13]对比测试了栅极注入晶体管和混合漏极嵌入栅极注入晶体管在断态和半开通态条件下电致发光信号的强弱,得出热电子在电荷捕获中起主要作用,且电流崩塌的改善主要取决于电荷去捕获率而不是热电子捕获率。器件本体层面的研究解释了动态导通电阻现象出现的原因,但难以对器件使用者产生实际的参考意义。

从GaN器件在实际电力电子变换器中应用的角度,已有文献通过搭建优化后的测试平台,测试GaN器件在不同工作条件下的动态导通电阻值,对其影响因素进行研究。文献[14]提出的测试平台可通过调整电路节点连接方式而实现软/硬开关条件切换。文献[15]在传统的双脉冲测试(Double-Pulse Test, DPT)电路中增加了开关器件和二极管,通过改变控制策略,可以实现负载电流可控的DPT电路模式和多脉冲测试(Multiple-Pulse Test, MPT)模式。可测试的影响因素包括电压应力、频率和占空比。文献[16]对传统DPT电路进行优化,通过热电阻控制温度,进而研究温度对动态导通电阻的影响。现有文献中的测试平台可提供的测试变量有限,难以涵盖实际应用中的全部动态导通电阻影响因素,各有侧重但不全面。

测试结果方面,文献[17]在DPT测试平台和MPT测试平台以及实际变换器中分别测试了三款不同厂商生产的600V电压等级的GaN器件:GS66516T(GaN Systems)、PGA26C09DV(Panasonic)及TPH3206PS(Transphorm),得出其动态导通电阻与断态电压应力大小、断态电压应力时间、温度的定性关系。文献[14]分别在DPT和MPT平台测试了Infineon公司的Si MOSFET与GaN Systems公司、Panasonic公司的单体增强型GaN器件在软/硬开关条件下的动态导通电阻,得出开关条件对不同GaN器件动态导通电阻特性的影响不同。文献[15]未详细给出被测器件(Devices Under Test, DUT)的型号和结构特征,测得增强型GaN器件在硬开关条件下动态导通电阻的表现优于软开关条件,与文献[14]结论相反。综上,GaN器件结构差异及各影响因素造成的动态导通电阻变化规律还有待进一步研究。

本文将从GaN器件动态导通电阻发生机理分析出发,确定对该参数漂移具有主要贡献作用的影响因素,在此基础上提出了一种涵盖所有动态导通电阻影响因素的综合测试电路及测试方法。基于该测试平台,选取不同结构GaN器件,在除温度外的各影响因素下进行动态导通电阻精确测试,分析测试结果,并从应用角度给出抑制动态导通电阻漂移、降低动态导通电阻造成额外损耗的优化方法。

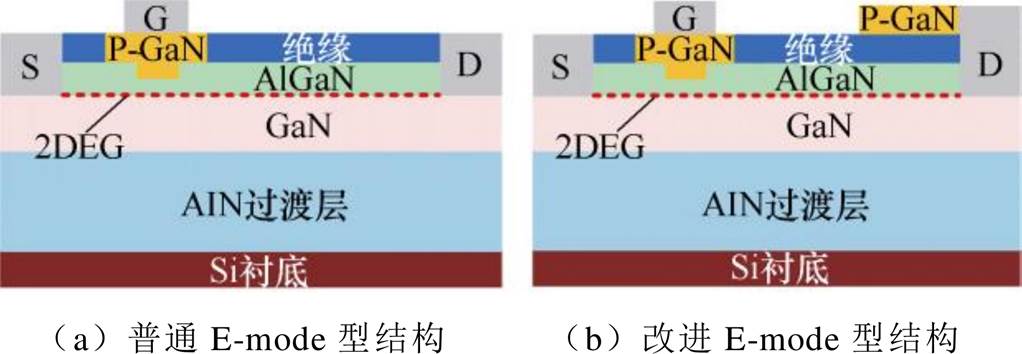

根据形成增强型的方法不同,GaN器件可分为两大类:单体增强(Enhancemend-mode, E-mode)型和级联(Cascode)型。其中,E-mode型器件又包括两种结构:普通P-GaN盖帽层结构(后文简称普通E-mode)和改进型P-GaN盖帽层结构(后文简称改进E-mode),其结构示意图分别如图1所示。不同结构GaN器件均存在不同程度的动态导通电阻现象。其中,E-mode型器件尤其是普通E-mode型器件较Cascode型器件的动态导通电阻现象更明显。因此,本节基于普通E-mode型GaN器件分析动态导通电阻现象的发生机理及影响因素。

图1 E-mode型GaN器件结构示意图

Fig.1 Structure of E-mode GaN device

如图1a所示,普通E-mode型GaN器件采用Si或碳化硅(Silicon Carbide, SiC)材料作为衬底;在衬底上方生长过渡层,主要用于减小GaN生长时不同材料间的应力差;过渡层上方为GaN层,用于生长Al GaN/GaN异质结结构。GaN器件利用Al GaN/GaN异质结界面处形成的二维电子气(Two Dimensional Electron Gas, 2DEG)构成导电沟道,这与Si MOSFET通过PN结形成导电沟道的方式完全不同[18]。结构和导电机理的差异导致动态导通电阻现象在GaN器件中尤为明显,而Si器件的导通电阻在相同温度下基本不变。

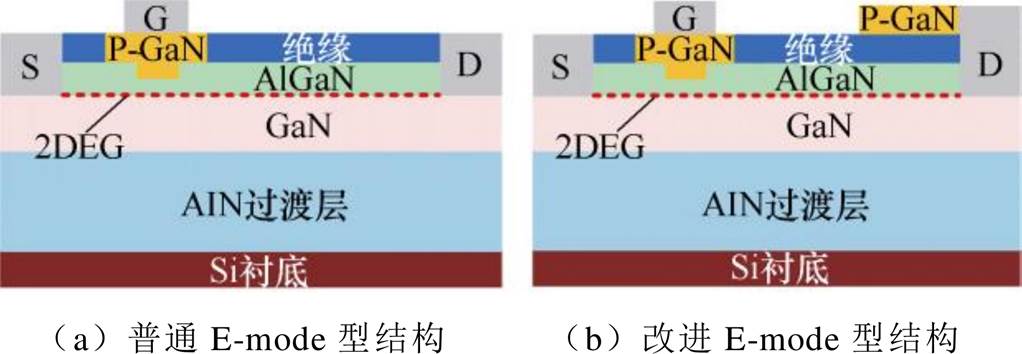

普通E-mode型GaN器件的动态导通电阻现象发生与器件内沟道和不同层之间出现的电荷捕获及去捕获有关:器件断态时,电子被捕获至沟道外;器件导通后,被捕获的电子无法完全回到沟道内参与导电过程。电荷捕获与去捕获存在两种发生机理。普通E-mode型器件动态导通电阻现象发生机理如图2所示。

图2 普通E-mode型器件动态导通电阻现象发生机理

Fig.2 Dynamic on-resistance mechanism of the common E-mode GaN devices

如图2中机理一所示。普通E-mode型GaN器件处于断态时,其漏极与源极、栅极间承受较高电压,大量电子被注入到缓冲层并被缓冲层中的空穴所捕获。断态电压应力越大,断态电压应力持续时间越长,被捕获电子数量越多,而器件开通后无法提供更多的能量将被捕获的电子去捕获到沟道内,从而加剧动态导通电阻现象。同时,器件通态时的漏极电流大小同样影响动态导通电阻。漏极电流越大,需要参加导电的电子数量越多,受动态导通电阻现象的影响就越小;反之,漏极电流越小,动态导通电阻现象在器件上就表现得越明显。因此,断态电压应力、断态电压应力持续时间及漏极电流(或称为负载电流)是动态导通电阻的三个影响因素。

如图2中机理二所示。普通E-mode型GaN器件在硬开关动作期间,漏源极同时承受高电压应力和大电流,2DEG中大量热电子向外运动,被注入到栅极与漏极表面附近以及缓冲层中,并被这些区域中的空穴捕获;相反,在软开关动作期间,由于此时漏源极并不同时存在高电压和大电流,无法提供足够的电场能量加速大量热电子向外运动并被捕获,被捕获的电子数量低于硬开关状态,因而维持沟道内电子数量平衡所需的去捕获能量也变小,不容易出现动态导通电阻现象。除软/硬开关条件外,当器件高频工作于实际变换器中时,开关频率与占空比的变化可视为每个周期内开通和关断时间的变化,因此根据机理一,也会对动态导通电阻产生影响。

综合上述分析,影响GaN器件动态导通电阻的主要因素包括:断态电压应力、断态电压应力持续时间、负载电流、开关条件、开关频率和占空比。这些影响因素同时也作为下一步测试的自变量,用于研究动态导通电阻随自变量变化的具体规律, 以及对比不同自变量对动态导通电阻的影响程度的差异。

动态导通电阻影响因素较多,传统测试平台难以涵盖所有影响因素测试。为解决这一问题,实现在同一测试平台完成GaN器件在不同影响因素下的动态导通电阻精确测试,本文提出一种动态导通电阻综合测试平台及其测试方法。

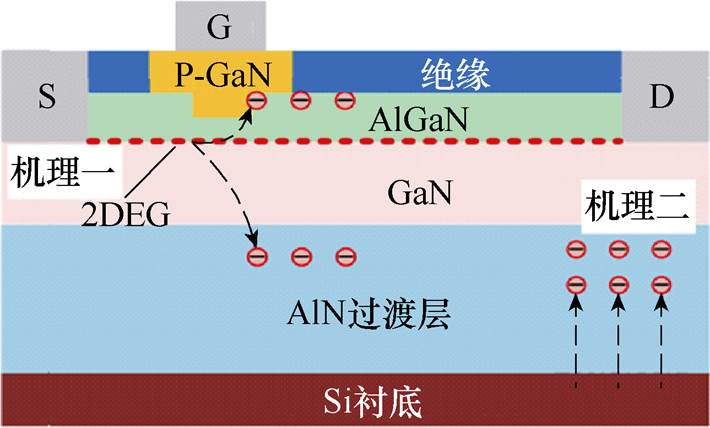

图3为动态导通电阻综合测试平台电路拓扑。该平台基于DPT平台[19-20]与四管Buck-Boost(Four- Switch Buck-Boost, FSBB)电路改进而成。Q1~Q4为待测器件安装位置,Vin为直流电压、L为电感,RL为负载安装位置。1、2、3为预留接口,根据测试需求,可连接接口2与1或接口2与3,通过转换电路连接的方式为待测器件提供不同测试模式,进而提供多样化的组合测试条件。该平台可提供的测试变量涵盖上文所述的全部GaN器件动态导通电阻影响因素。

图3 动态导通电阻综合测试平台电路拓扑

Fig.3 Topology diagram of comprehensive dynamic on-resistance test circuit

动态导通电阻测试基于待测器件开通阶段漏源极电压VDS-ON[21]和漏极电流ID的测量。在测量VDS-ON时,存在器件通态电压值与断态电压值相差过大的问题。以实验室常用的示波器MDO3054为例,该示波器的垂直分辨率为8位。当待测器件为600V/ 650V电压等级时,其最大被测断态电压应力为400V。根据8位示波器最小分辨率公式 =VDC/

=VDC/ ,此时示波器最小分辨率约为1.56V。而GaN器件的通态电压通常在几百mV到几V之间,无法满足精度要求。因此,示波器量程选择过大将导致读取的通态电压值误差过大,影响后续实验结果分析。若示波器量程选择过小,示波器无法显示断态部分波形,也不符合实验数据真实性要求。因此,为解决这一问题,提高动态导通电阻测试精度,本文提出的综合测试平台还包括并联于待测器件Q2、Q3两端的钳位电路,将待测器件处于断态时的漏源极电压钳位在一个较小值,保证测试波形完整的同时满足通态电压测试精度,同时解决示波器的量程和波形完整度问题。

,此时示波器最小分辨率约为1.56V。而GaN器件的通态电压通常在几百mV到几V之间,无法满足精度要求。因此,示波器量程选择过大将导致读取的通态电压值误差过大,影响后续实验结果分析。若示波器量程选择过小,示波器无法显示断态部分波形,也不符合实验数据真实性要求。因此,为解决这一问题,提高动态导通电阻测试精度,本文提出的综合测试平台还包括并联于待测器件Q2、Q3两端的钳位电路,将待测器件处于断态时的漏源极电压钳位在一个较小值,保证测试波形完整的同时满足通态电压测试精度,同时解决示波器的量程和波形完整度问题。

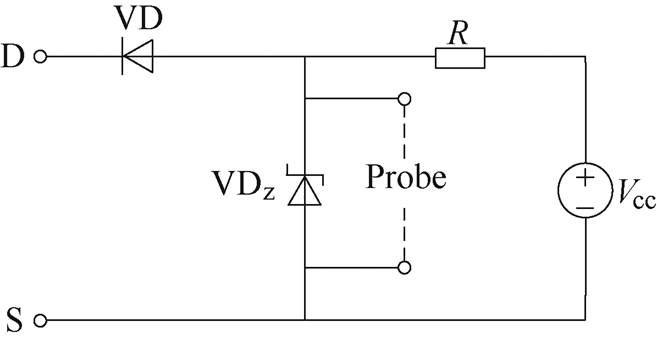

本文采用的钳位电路拓扑如图4所示,该拓扑是在文献[22]中提出的钳位电路基础上做了改进和简化,在保证测试快速性和准确性的前提下减少了所使用的元器件。图中,VD为二极管;VDz为稳压二极管;R为100W 电阻;Vcc为附加直流电压源。电压探头接于VDz两端。钳位电路的工作过程分为两个阶段:阶段一,待测器件关断时,VD也处于关断状态,电压探头测得的信号为VDz的稳压值;阶段二,待测器件导通时,VD结电容放电完毕也处于导通状态,此时电压探头测得的信号为待测器件的导通电压加上VD的正向压降。VD选取低寄生电容的SiC肖特基二极管,保证钳位电路测量时的快速性和准确性。且通过设置电阻R值,限制流过VD电流的大小,避免因为自热引起温度上升,导致VD受温度影响出现正向压降的增大。

图4 钳位电路拓扑

Fig.4 Topology diagram of clamping circuit

2.2.1 DPT模式测试

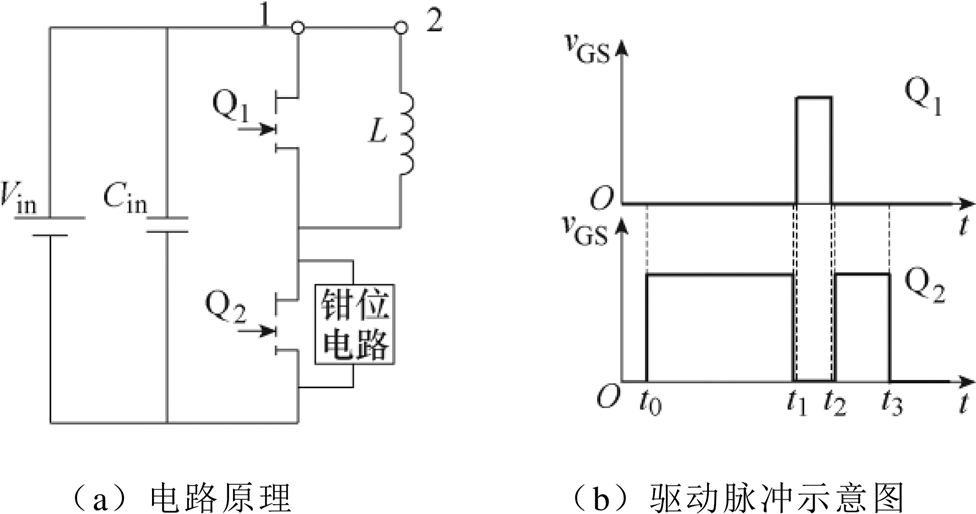

DPT模式电路原理及驱动脉冲示意图如图5所示。将接口1、2相连时,即为DPT测试模式,电路原理如图5a所示。在该模式下可测试的影响因素包括断态电压应力、断态电压应力持续时间和负载电流。具体测试步骤及测试变量控制方法如下。

图5 DPT模式电路原理及驱动脉冲示意图

Fig.5 Diagram of circuit and driving pulses in DPT mode

与传统的DPT测试原理类似,以Q2为待测器件,给Q1、Q2施加如图5b所示的驱动脉冲,测量Q2在第二个脉冲开通期间的电压电流波形。通过改变母线电压Vin来控制测试变量待测器件断态电压应力。

t0~t1:给Q2施加第一个驱动脉冲,Q2导通,电感充电。通过控制t0~t1时长改变电感电流大小,进而控制测试变量负载电流。

t1~t2:Q2关断,给Q1施加驱动脉冲,Q1导通,电感续流,此阶段电感电流大小基本保持不变。通过控制t1~t2时长而控制测试变量断态电压应力持续时间。

t2~t3:给Q2施加第二个驱动脉冲,Q2导通,此阶段为动态导通电阻测试的关键阶段。测量Q2导通期间通态电压波形并计算平均值VDS-ON、测量漏极电流ID,计算求得动态导通电阻值(dynamic on-Resistance, dRon)。

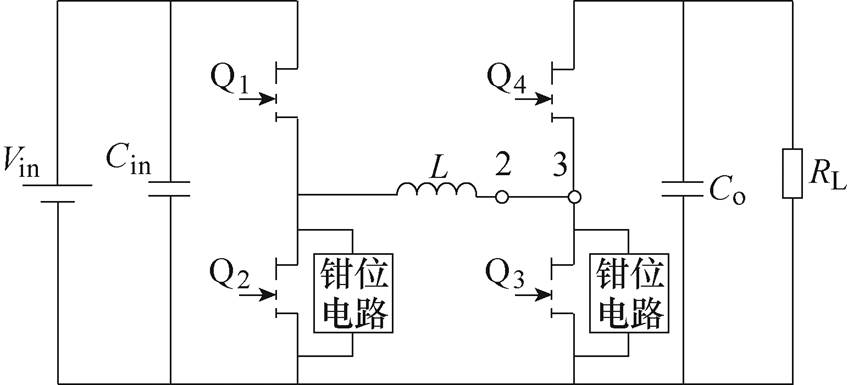

2.2.2 FSBB模式测试

将接口2、3相连时,即为FSBB测试模式,电路原理如图6所示。以Q2和Q3为被测器件,RL为阻性负载。在该模式下可测试的影响因素包括开关频率、占空比、开关条件。其中,前两项测试变量的控制通过改变驱动信号而实现,测试变量开关条件则需通过改变控制策略而实现硬开关或软开关。以下以零电压开通为例,介绍实现软开关的控制方法。

图6 FSBB模式电路原理

Fig.6 Circuit diagram in FSBB mode

图7所示为FSBB测试模式下实现软开关的控制策略及各阶段等效电路。

图7 FSBB模式软开关测试理论波形及阶段等效电路

Fig.7 Waveforms and equivalent circuits in FSBB mode with soft switching condition

t0~t1:Q1和Q3导通,该阶段给电感充电,电感电流上升,t1时刻Q3关断。

t1~t2:该阶段为Q3和Q4的死区时间,此时电感L2与Q3和Q4漏源极两端的寄生电容发生谐振,Q4两端电容放电,Q3两端电容充电,当Q4两端的电压降至零时,Q4零电压开通。

t2~t3:Q1和Q4导通,该阶段给负载供电,电感电流下降,t3时刻Q1关断。

t3~t4:该阶段为Q1和Q2的死区时间,此时电感L2与Q1和Q2漏源极两端的寄生电容发生谐振,Q2两端电容放电,Q1两端电容充电,当Q2两端的电压降至零时,Q2零电压开通。

t4~t5:Q2和Q4导通,该阶段为电感给负载提供能量,电感电流下降,t5时刻Q4关断。

t5~t6:该阶段为Q3和Q4的死区时间,此时电感L2与Q3和Q4漏源极两端的寄生电容发生谐振,Q3两端电容放电,Q4两端电容充电,当Q3两端的电压降至零时,Q3零电压开通。

t6~t7:Q2和Q3导通,该阶段电感电流基本不变,t7时刻Q2关断。

t7~t8:该阶段为Q1和Q2的死区时间,此时电感L2与Q1和Q2漏源极两端的寄生电容发生谐振,Q1两端电容放电,Q2两端电容充电,当Q1两端的电压降至零时,Q1零电压开通。

根据上述工作过程分析,被测器件在每个周期内均实现零电压开通。此外,基于该测试平台,在硬开关和软开关条件下均可分别调节开关管的开关频率和占空比,实现不同开关频率、占空比条件下的动态导通电阻测试。

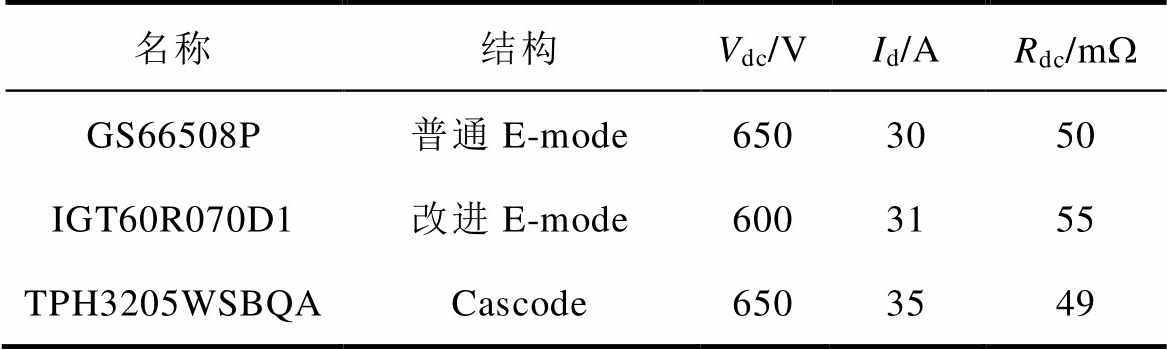

基于上述测试平台及测试方法,选取三款600V/ 650V额定电压、30A等级额定电流的GaN器件进行动态导通电阻测试。待测器件结构分别为普通E-mode型、改进E-mode型及Cascode型,具体参数见表1。通过设置不同测试条件,精确测试动态导通电阻,绘制以影响因素为自变量的动态导通电阻变化曲线,分析不同结构GaN器件动态导通电阻随影响因素的变化情况。

表1 被测器件数据手册导通电阻参数

Tab.1 DUT on-resistance parameters on datasheets

名称结构Vdc/VId/ARdc/mW GS66508P普通E-mode6503050 IGT60R070D1改进E-mode6003155 TPH3205WSBQACascode6503549

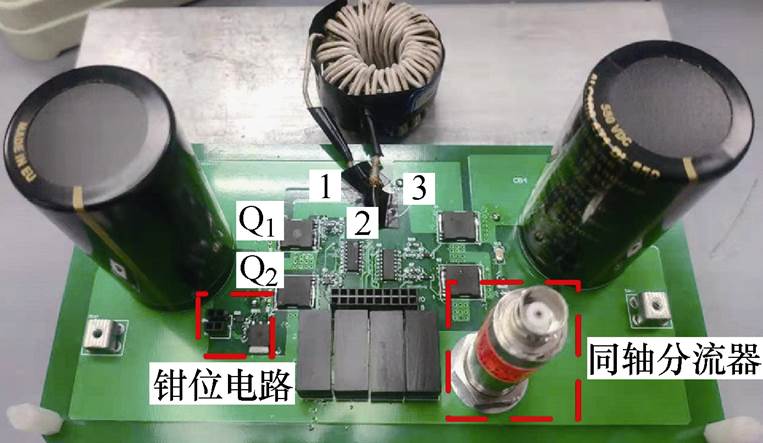

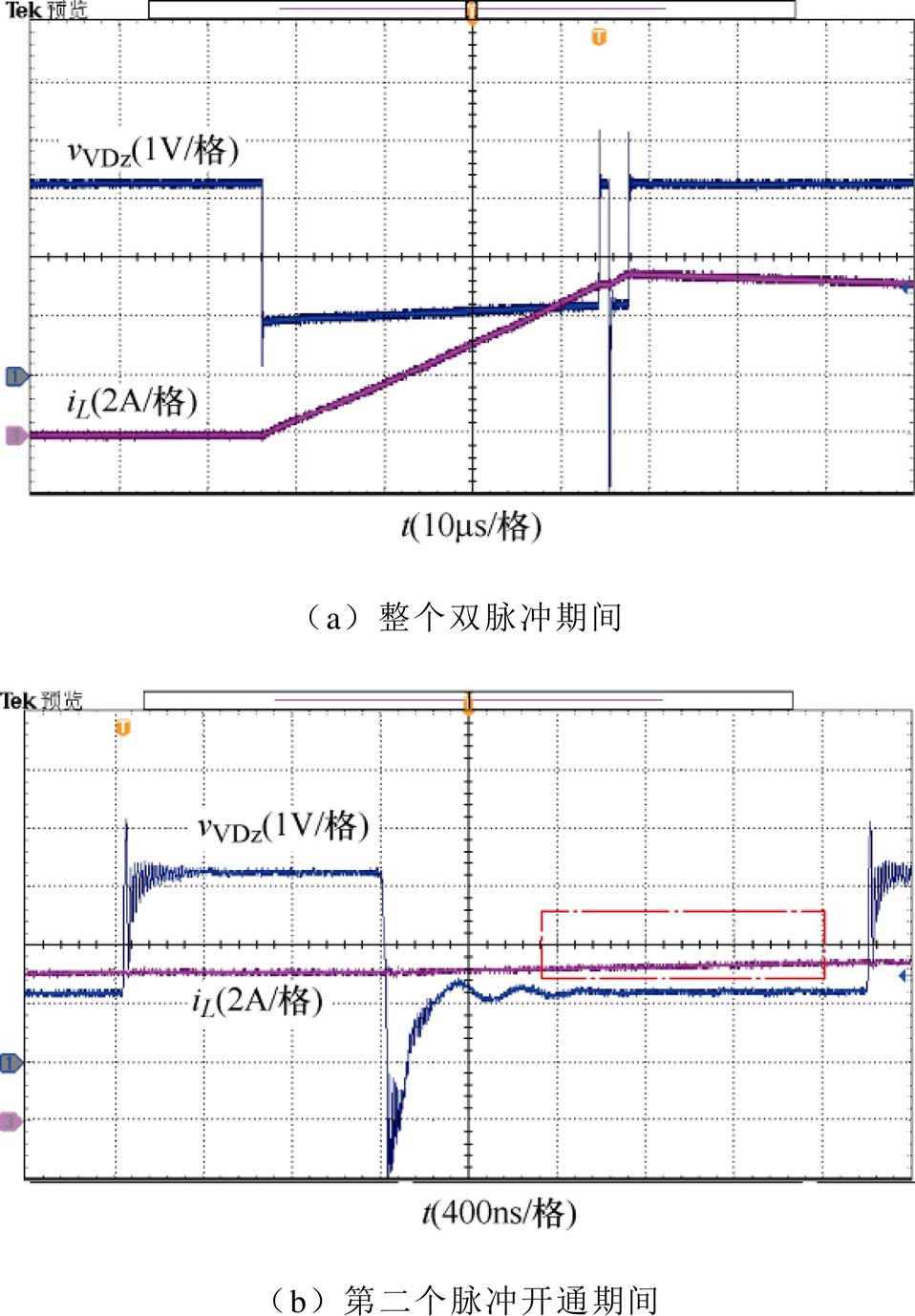

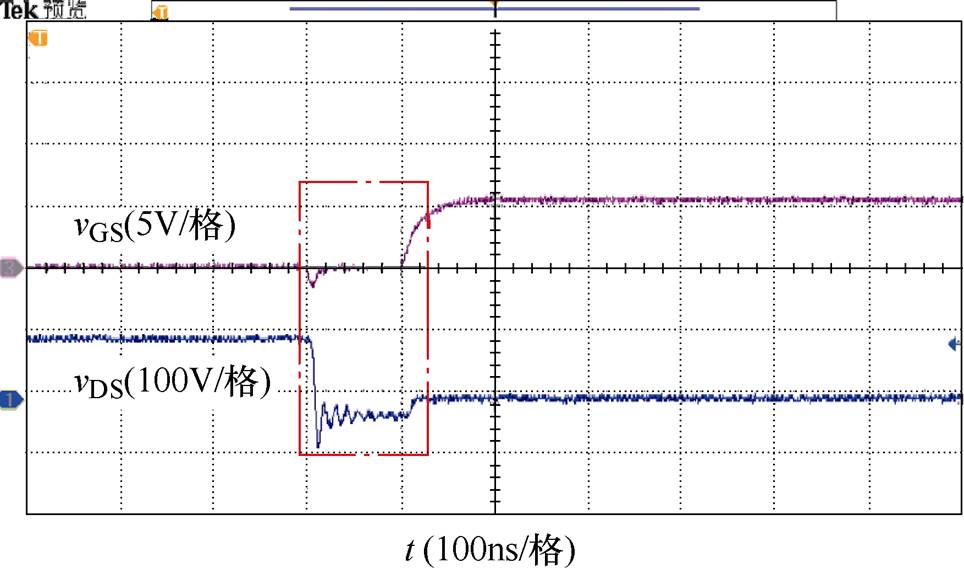

三款待测器件GS66508P、IGT60R070D1及TPH3205WSBQA的封装类型分别为GaNPX@、PG-HSOF-8-3及TO-247,根据其封装特点,分别设计测试平台PCB并进行优化,完成三款测试平台搭建。以IGT60R070D1测试平台为例,实物如图8所示。1、2、3接口为电感连接点,当电感连接于接口1、2时,Q1、Q2工作,测试平台工作于DPT测试模式。通过示波器读取钳位电压稳定值和电感电流波形如图9所示,计算该测试条件下的动态导通电阻值。测试自变量包括断态电压应力、断态电压应力持续时间及负载电流大小。当电感连接于接口2、3时,Q1~Q4工作,测试平台工作于FSBB测试模式。动态导通电阻计算方式与DPT模式相同。测试自变量包括开关频率、占空比及软/硬开关条件。为表示方便,本文以器件标称的导通电阻典型值Rdc作为基准,对测得的动态导通电阻值dRon进行标幺化,得到比导通电阻值dRon/Rdc,绘制比导通电阻与测试自变量的关系曲线。

图8 IGT60R070D1器件动态导通电阻综合测试平台

Fig.8 Comprehensive dynamic on-resistance test platform for IGT60R070D1

图9 DPT模式下的钳位电压和电感电流波形(VDC=400V, IL=5A)

Fig.9 Waveforms of clamping voltage and inductor current in DPT mode (VDC=400V, IL=5A)

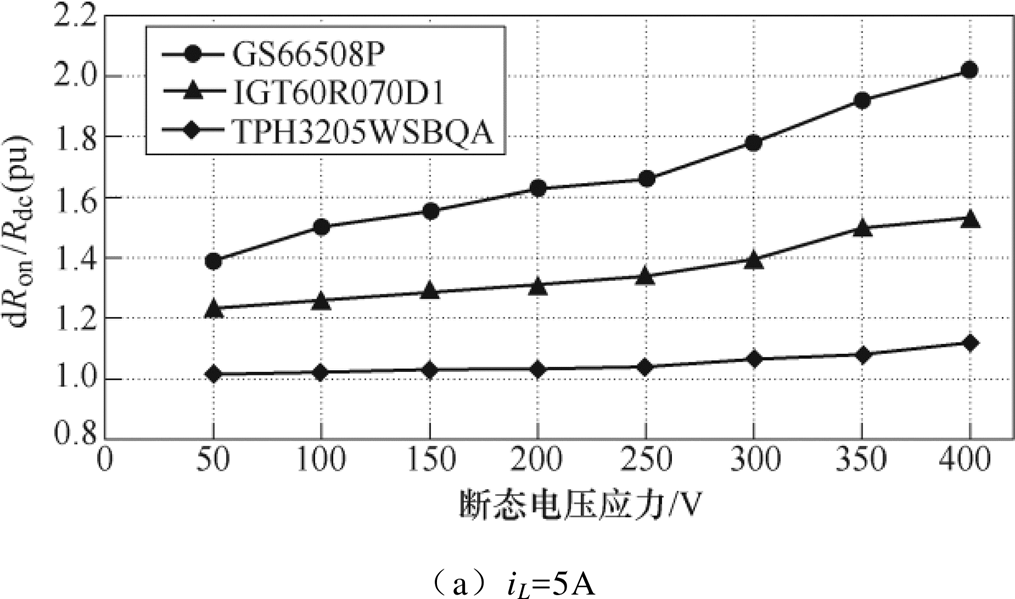

3.1.1 断态电压应力测试

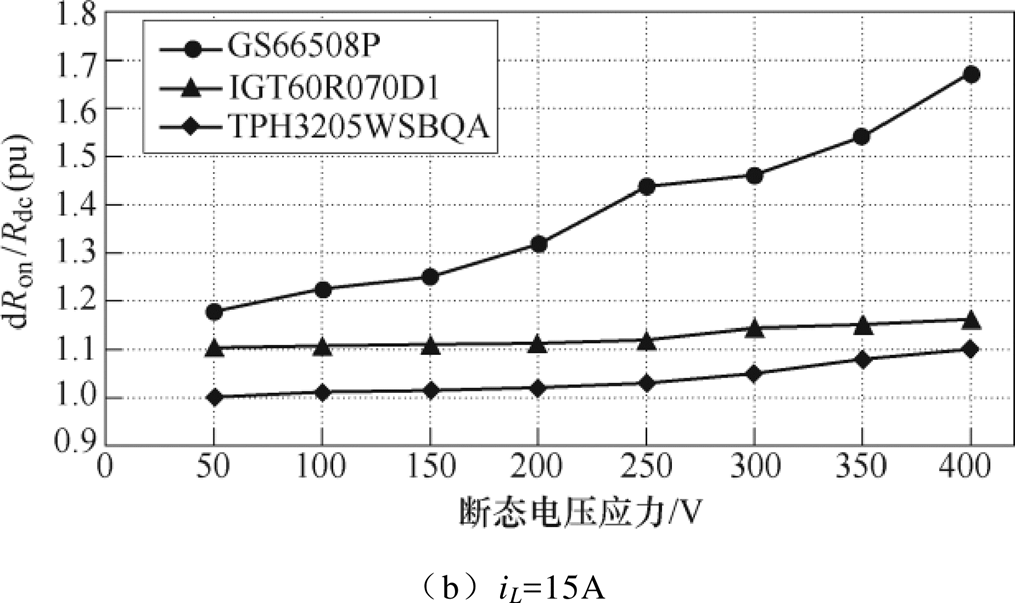

设置断态电压应力持续时间为1ms,分别控制负载电流为5A、15A,改变断态电压应力,测试动态导通电阻值。三款器件比导通电阻随断态电压应力变化曲线如图10所示。图中,纵坐标表示比导通电阻值,即测得的动态导通电阻值dRon以器件标称导通电阻典型值Rdc为标准而得到的标幺化结果。

图10 三款器件比导通电阻随断态电压应力变化曲线

Fig.10 Diagram of the specific on-resistance of the three devices as a function of the off-state voltage stress

由测试结果可知,三款器件动态导通电阻均随断态电压应力增大而增大。其中,GS66508P变化幅度最大,当断态电压应力为400V时,负载电流5A、15A情况下的比导通电阻分别达到2.017、1.674;IGT60R070D1的变化幅度受负载电流影响,负载电流为5A时,400V断态电压应力下的比导通电阻为1.533,而负载电流为15A时,比导通电阻随断态电压应力增大不明显,400V下比导通电阻为1.162;TPH3205WSBQA变化幅度最小,始终保持低的比导通电阻,最大值为1.1左右。

3.1.2 断态电压应力持续时间测试

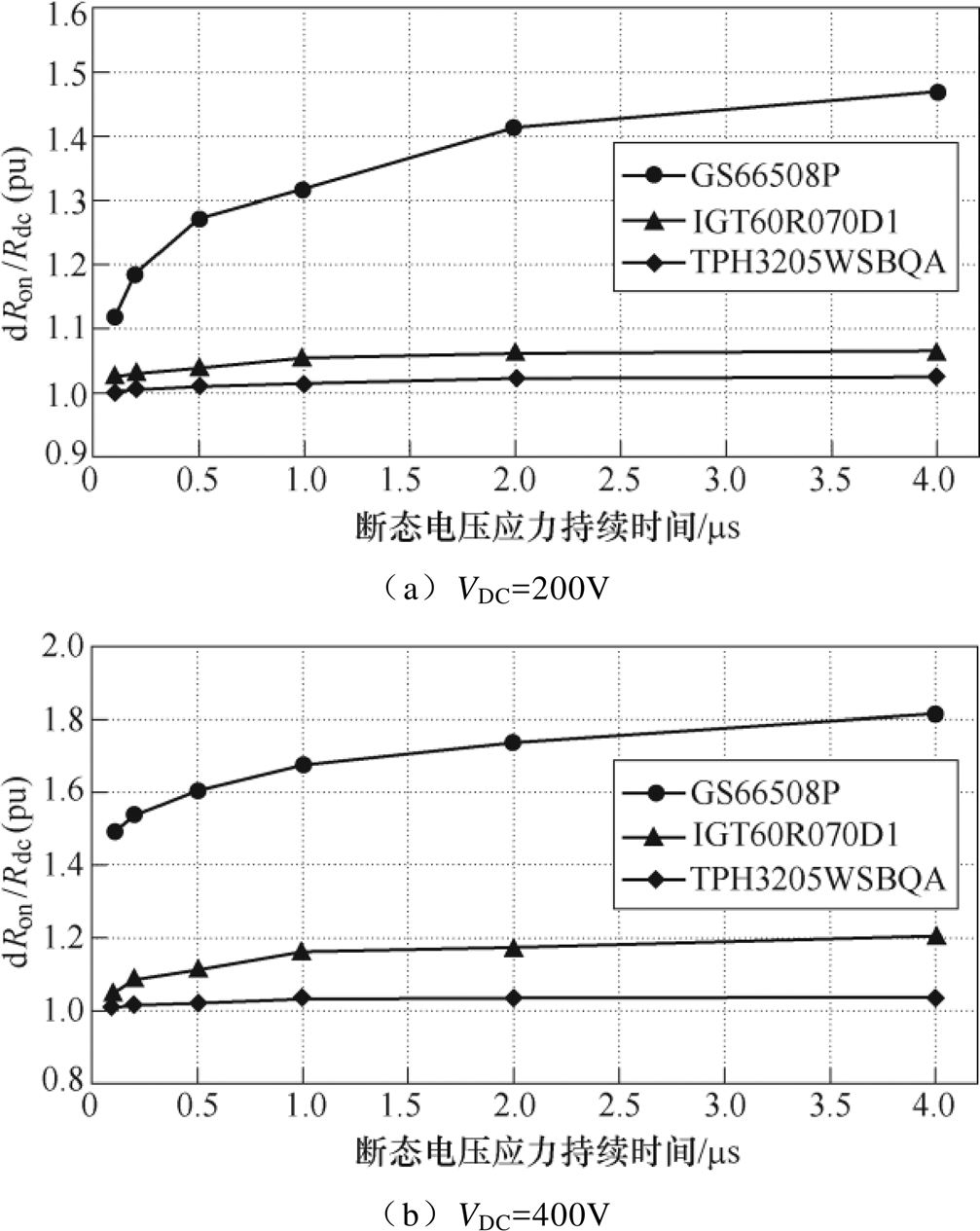

设置负载电流为15A,分别控制断态电压应力为200V、400V,改变断态电压应力持续时间,测试动态导通电阻值。三款器件比导通电阻随断态电压应力持续时间变化曲线如图11所示。

由测试结果可知,三款器件动态导通电阻均随断态电压应力持续时间的延长而增大,增大速度先快后慢,并逐渐趋于某一定值。在三款GaN器件中,GS66508P变化范围最大,IGT60R070D1增大幅度较小,TPH3205WSBQA的比导通电阻可近似为基本不变。当断态电压应力为400V、断态电压应力持续时间为4ms时,GS66508P比导通电阻为1.815、IGT60R070D1比导通电阻为1.206。

图11 三款器件比导通电阻随断态电压应力持续时间变化曲线

Fig.11 Diagram of the specific on-resistance of the three devices as a function of the blocking time

3.1.3 负载电流测试

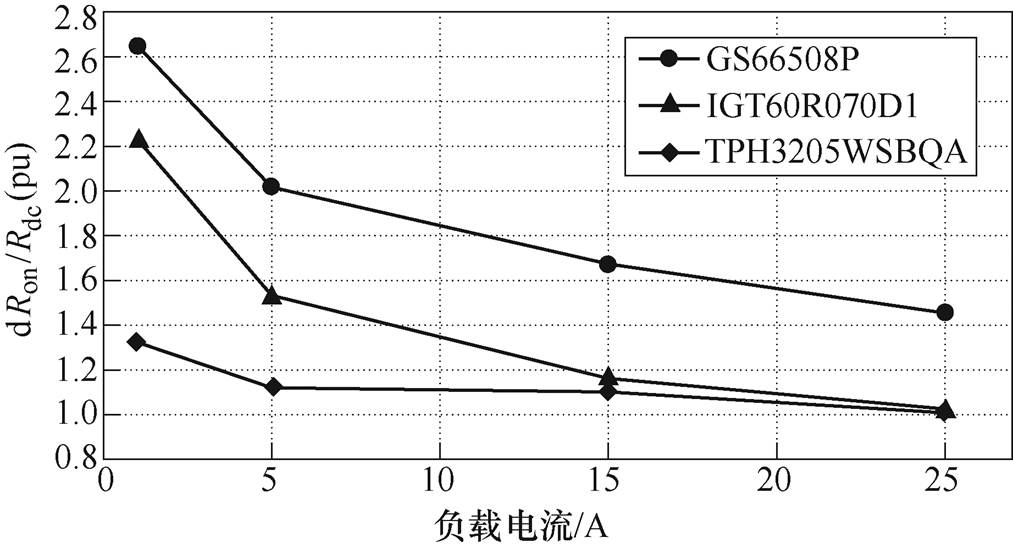

设置断态电压应力为400V、断态电压应力持续时间为1ms,改变负载电流大小,测试动态导通电阻值。三款器件比导通电阻随负载电流变化曲线如图12所示。

图12 三款器件比导通电阻随负载电流变化曲线

Fig.12 Diagram of specific on-resistance of the three devices as a function of the load current

3.2.1 开关频率测试

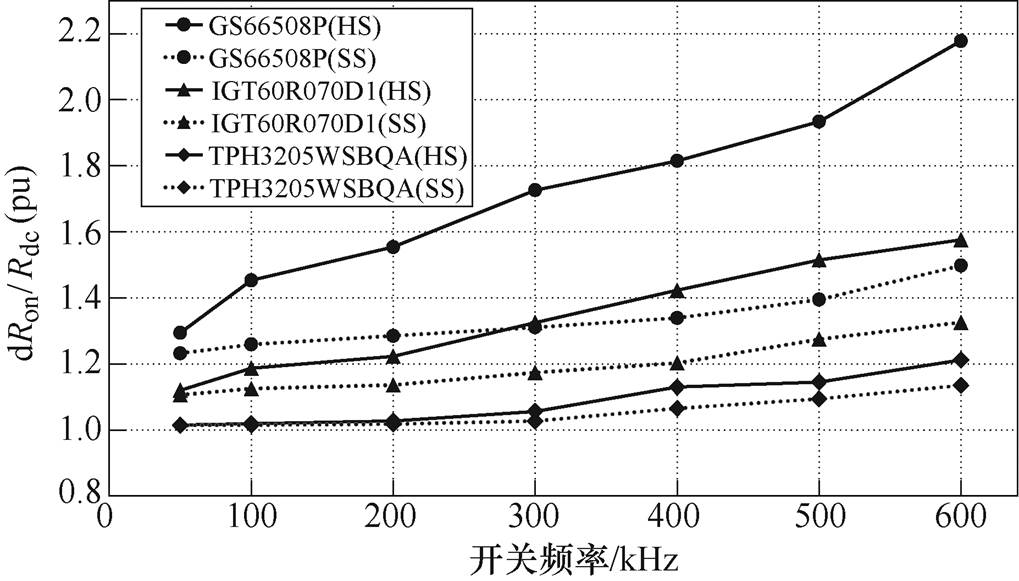

设置占空比为0.5、硬开关条件,分别在断态电压应力为100V、400V情况下,改变开关频率,测试动态导通电阻值。三款器件比导通电阻随开关频率变化曲线如图13所示。

图13 三款器件比导通电阻随开关频率变化曲线

Fig.13 Diagram of specific on-resistance of the three devices as a function of switching frequency

由测试结果可知,三款器件动态导通电阻均随开关频率的提高而增大。当断态电压应力为400V、开关频率上升至600kHz时,GS66508P、IGT60R070D1及TPH3205WSBQA的比导通电阻分别为2.178、1.576、1.212。相较于前述的断态电压应力、断态电压应力时间测试,IGT60R070D1及TPH3205WSBQA的比导通电阻增大较为明显。

3.2.2 占空比测试

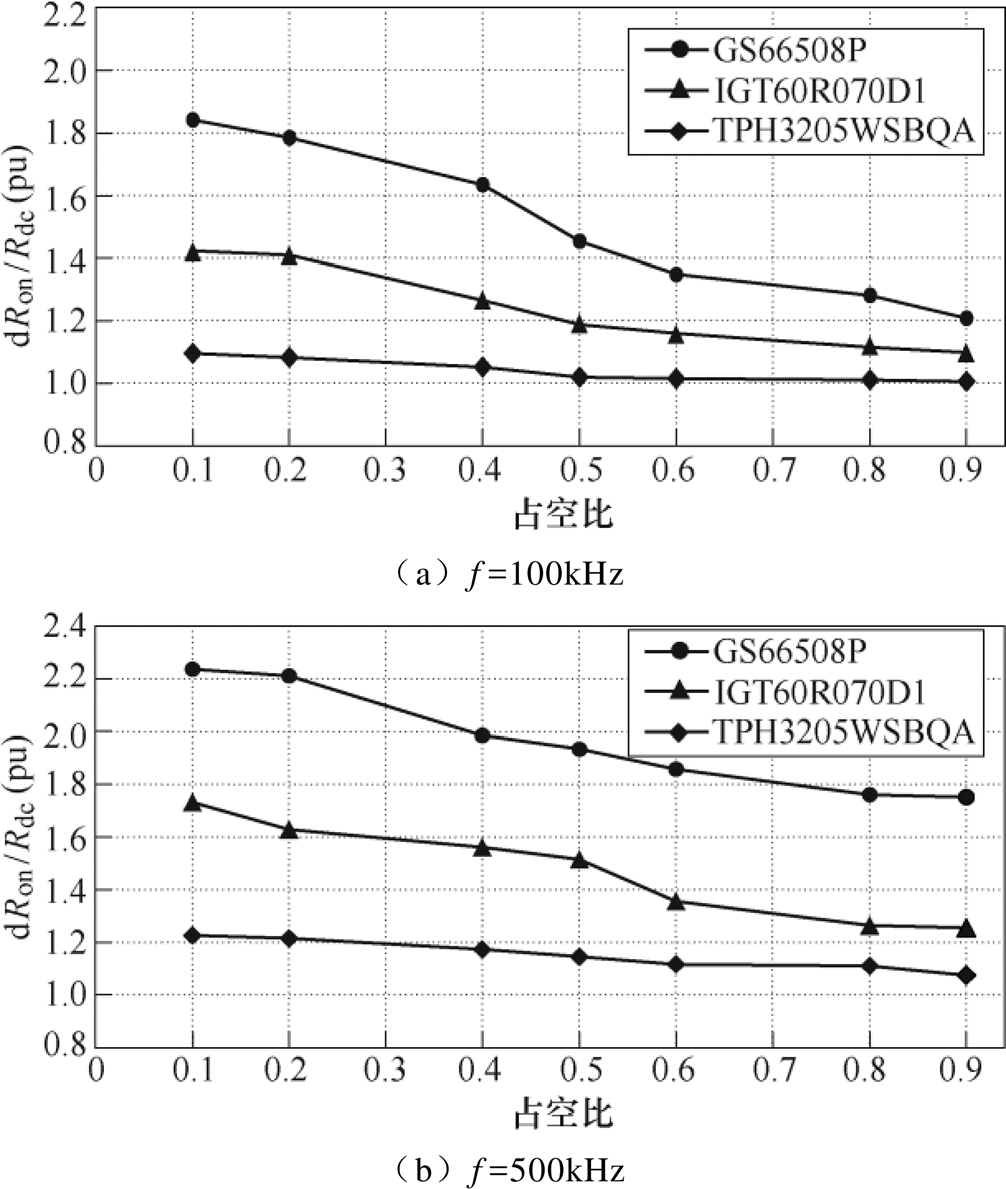

设置断态电压应力为400V、硬开关条件,分别在开关频率为100kHz、500kHz情况下,改变占空比,测试动态导通电阻值。三款器件比导通电阻随占空比的变化曲线如图14所示。

图14 三款器件比导通电阻随占空比的变化曲线

Fig.14 Diagram of specific on-resistance of three devices as a function of duty cycle

由测试结果可知,三款器件动态导通电阻均随占空比的增大而减小。占空比与频率决定器件在一个周期内的导通、关断时间。开关频率一定时,占空比越大,器件关断时间越短,可等效为DPT模式下断态电压应力持续时间越短,因而动态导通电阻减小。该变化趋势与断态电压应力持续时间测试结果一致。

当开关频率为100kHz时,随着占空比趋近于1,三款器件动态导通电阻大幅减小、逐渐趋近于典型值。当开关频率为500kHz时,动态导通电阻随占空比增大而减小的幅度降低。尤其是GS66508P器件,随着占空比从0.1升高至0.9,比导通电阻从2.236下降至1.752,动态导通电阻仍处于较高数值。由此可知,低频条件下,占空比为动态导通电阻主要影响因素;高频条件下,开关频率对动态导通电阻的影响程度超过占空比。

3.2.3 开关条件测试

由2.2节介绍的控制策略实现被测器件的零电压开通,实验波形如图15所示。设置断态电压应力为400V、占空比为0.5,改变开关频率,分别测试三款GaN器件在零电压开通条件下的动态导通电阻,并与3.2.1节硬开关条件下测试结果进行对比,绘制三款器件比导通电阻在软/硬开关条件下随开关频率变化曲线,如图16所示。

图15 待测器件零电压开通波形

Fig.15 The zero-voltage switching-on (ZVS-on) waveforms of DUT

从图16可以看出,三款被测器件均在软开关条件下出现动态导通电阻降低的现象,且在高频下更为显著。其中,GS66508P的变化最为明显。当开关频率为600kHz时,GS66508P比导通电阻从硬开关条件下的2.178下降至1.498;IGT60R070D1从1.576下降至1.326;TPH3205WSBQA从1.212下降至1.135。随着开关频率的降低,开关条件对动态导通电阻现象的影响减弱。当开关频率低至50kHz时,GS66508P软、硬开关条件下的比动态导通电阻差值很小,IGT60R070D1和TPH3205WSBQA的比动态导通电阻值基本一致。这一现象与动态导通电阻现象机制二的理论分析相符,在高压、高频条件下,软开关对动态导通电阻现象有明显的抑制作用。

图16 三款器件比导通电阻在不同开关频率下随开关条件变化曲线

Fig.16 Diagram of specific on-resistance of three devices changing with switching conditions at different switching frequencies

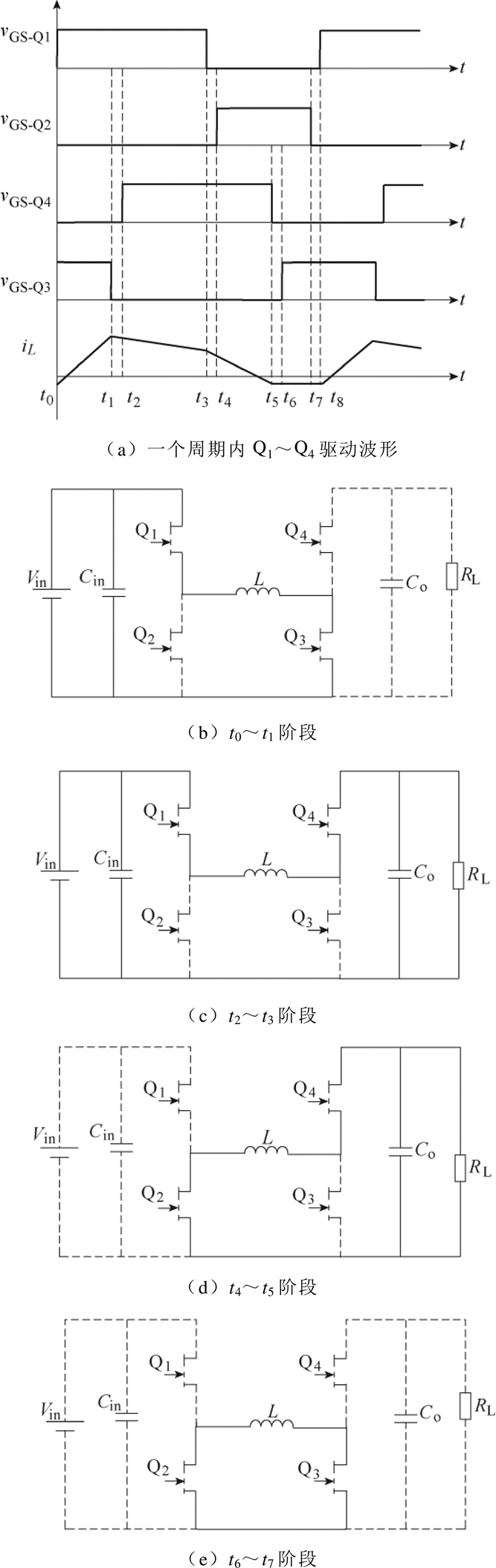

综合上述测试结果,总结三款被测GaN器件在各影响因素下的动态导通电阻变化规律,与动态导通电阻发生机理进行对照。并分别基于三款被测器件,横向比较不同影响因素对其导通电阻漂移的影响程度,定量计算动态导通电阻随影响因素的变化率,分析器件结构导致的动态导通电阻特性差异。并基于分析结果,针对不同结构GaN器件提出应用层面的动态导通电阻优化方法。

由3.2节可知,在变换器中,开关频率与占空比决定了器件在每个周期内的断态电压应力时间。因此,本节不再单独考虑断态电压应力时间对GaN器件动态导通电阻的影响程度,只取断态电压应力、负载电流、开关频率、占空比及软硬开关条件这五种影响因素进行分析。

根据650V等级GaN器件的实际应用常见工况,基于3.1节与3.2节测试结果,为五种影响因素选取适当的变化范围,横向对比各影响因素在选定变化范围内对每种器件造成的动态导通电阻漂移程度及三种器件间的动态导通电阻特性差异。针对前四项影响因素,选择的变化范围如下:断态电压应力50~400V(负载电流恒定为15A);负载电流5~15A(断态电压应力恒定为400V);开关频率50~500kHz(断态电压应力为400V、占空比恒定为0.5,负载电流取中间值10A);占空比从0.1上升至0.9(断态电压应力为400V、开关频率恒定为500kHz,负载电流取10A)。以上均保持硬开关。针对开关条件这一影响因素,保持断态电压应力400V、开关频率500kHz、占空比0.5及负载电流10A,对比软/硬开关条件下的动态导通电阻情况。

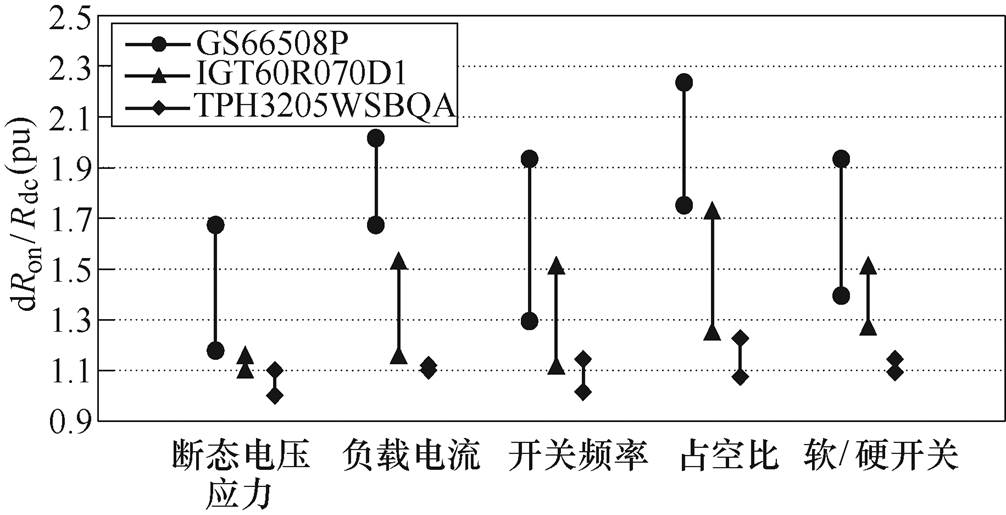

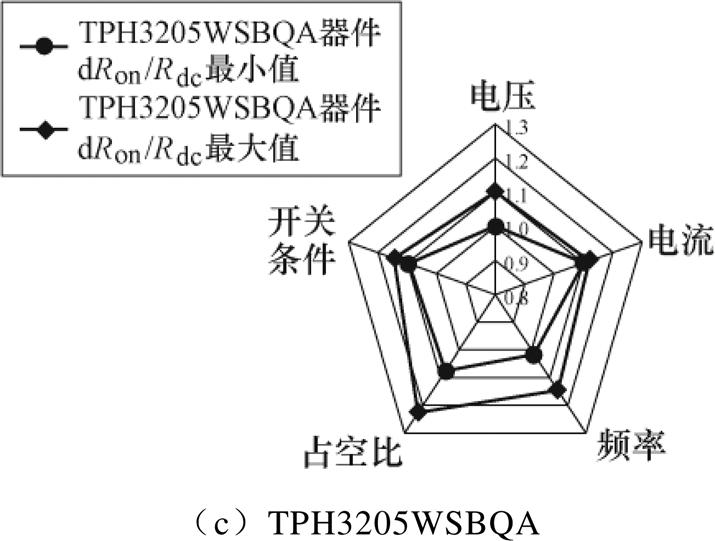

分别标记三款被测GaN器件在上述各项影响因素变化范围内的比导通电阻最大、最小值,绘制如图17所示的动态导通电阻变化范围综合对比。

图17 动态导通电阻变化范围综合对比

Fig.17 Comprehensive comparison of dynamic on-resistance variation range

图17中,横坐标依次为五种动态导通电阻影响因素,纵坐标为比导通电阻,不同形状的标记及其连接线段表示对应器件在各影响因素变化范围内的比导通电阻最值及动态导通电阻漂移区间。由图可知,GS66508P在各影响因素下的比导通电阻最大值均远高于另两款被测器件,且在每种影响因素取值范围内,动态导通电阻均呈现出大幅变化。IGT60R070D1的动态导通电阻现象次之,但断态电压应力作用远小于其他影响因素,且其引起的动态导通电阻变化范围也小于另两款器件的该值。TPH3205WSBQA的动态导通电阻现象最不明显,在高压、高频且硬开关条件下,占空比为0.1时,比导通电阻达全范围最大值1.226,但相同条件下,GS66508P和IGT60R070D1的比导通电阻为2.236和1.732。

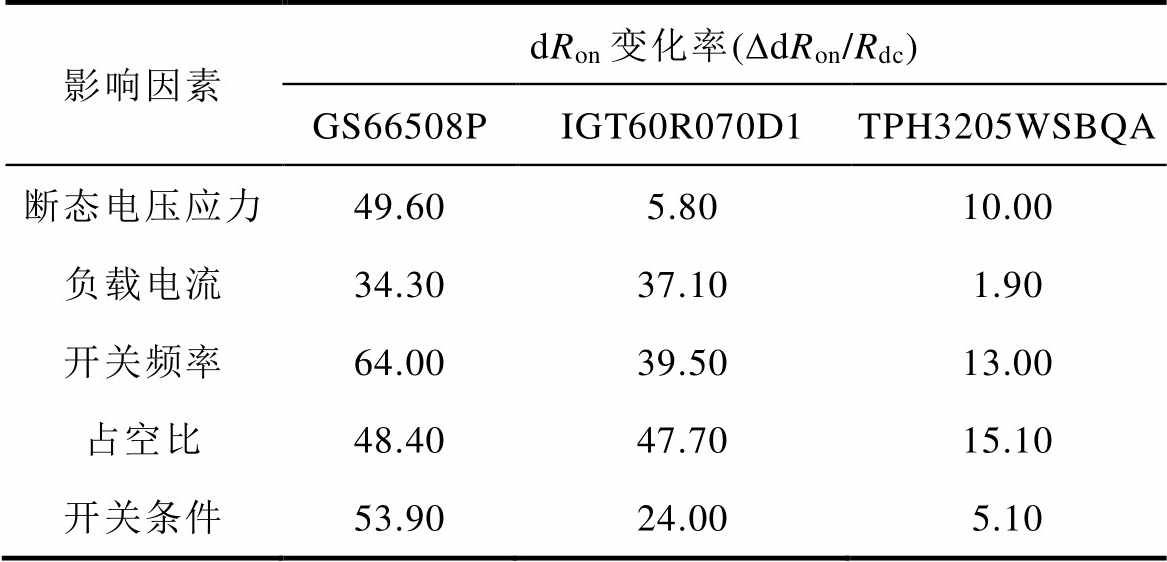

进一步比较五种影响因素对于同一款器件动态导通电阻现象的作用程度,绘制如图18所示影响因素作用效果对比,更加直观地表示每种影响因素造成的动态导通电阻变化量大小。图18中,对于可连续变化的影响因素,即电压、电流、频率及占空比,比导通电阻最大、最小值是指在图17中已选定的该影响因素变化范围内测到的最大、最小值;而开关条件这一影响因素只包含硬开关条件和软开关条件两种,则对应这一影响因素的比导通电阻最值即为在这两种开关条件下测得的器件比导通电阻,且根据前文关于开关条件的测试结果可知,最大值对应硬开关条件、最小值对应软开关条件。基于图18,分别计算三款被测器件在各影响因素下比导通电阻最大值与最小值的差值,计算差值占导通电阻标称值的百分比,结果见表2。

图18 动态导通电阻影响因素作用效果对比

Fig.18 Comparison of dynamic on-resistance variation range under different affecting factors

表2 被测器件在各影响因素下的动态导通电阻变化率

Tab.2 Dynamic on-resistance variation of the DUT under different affecting factors (%)

影响因素dRon变化率(DdRon/Rdc) GS66508PIGT60R070D1TPH3205WSBQA 断态电压应力49.605.8010.00 负载电流34.3037.101.90 开关频率64.0039.5013.00 占空比48.4047.7015.10 开关条件53.9024.005.10

由图18和表2可知,不同器件动态导通电阻变化率数值差异较大,且占主导作用的影响因素类型也不同。在三款被测器件中,GS66508P受各影响因素作用最为均衡。其中,开关频率引起的动态导通电阻变化率最大,达64%;负载电流作用最小,为34.3%;其余三种因素作用效果相近。对于IGT60R070D1,断态电压应力引起动态导通电阻变化率远小于其他影响因素,仅为5.8%;而在另外四种因素中,作用效果最大的为占空比、最小的为开关条件,其作用效果分别可达影响因素作用效果的4倍和8倍以上。TPH3205WSBQA的动态导通电阻变化率远低于另两款器件,其中,负载电流和开关条件的作用效果仅为1.9%、5.1%,占空比作用效果最大,对应导通电阻变化率为15.1%。在某些情况下,断态电压应力对IGT60R070D1、负载电流与开关条件对TPH3205WSBQA的动态导通电阻影响可近似忽略。

由上文可知,三款被测器件GS66508P、IGT60R070D1、TPH3205WSBQA分别为普通E-mode型、改进E-mode型与Cascode型。其动态导通电阻现象差异可由器件结构进行解释。E-mode型GaN器件通过在栅极引入P-GaN盖帽层的方式形成增强型,破坏了GaN晶体管的原有结构,因而会在高压情况下出现明显的电流崩塌效应,并且在高频和低占空比情况下更加明显。与普通E-mode型器件不同,改进E-mode型器件通过在漏极增加P-GaN的方式对器件结构进行了改进,从而抑制高压条件下的动态导通电阻漂移。由实验结果可知,该方法可有效抑制高压引起的动态导通电阻现象,但对其他因素引起动态导通电阻漂移的抑制效果不明显。Cascode型GaN器件通过级联低压Si管形成增强型,并未改变GaN晶体管内部结构,因而不会造成明显的电流崩塌现象,引发动态导通电阻明显增大。

相同结构的GaN器件具有相近的动态导通电阻特性,因而本文中三种型号GaN器件的测试结果及分析可推广至具有同类结构的其余型号GaN器件。

本节将基于各类结构GaN器件的动态导通电阻特性,给出应用层面的动态导通电阻优化方法。从器件选型、变换器设计等器件应用角度入手,充分发挥GaN器件优势,并减小其动态导通电阻漂移、抑制通态损耗增加、提升GaN器件应用可靠性。具体方法如下。

(1)对于普通E-mode型器件,其动态导通电阻受电压应力影响程度大,因此,在不考虑器件成本时可降额使用;改进E-mode型与Cascode型可不考虑电压应力对其动态导通电阻的影响。

(2)开关频率的提升不仅会增大器件开关损耗,也会增大三种结构GaN器件的动态导通电阻、增大通态损耗,因此,在选取开关频率时,需要平衡高频化带来的优点与引发的损耗问题。

(3)分析可知,开关频率与占空比共同决定开关管在每个周期内的断态电压应力时间;当频率一定时,占空比减小,每个周期内断态电压应力时间增大,三种结构GaN器件的动态导通电阻均随之增大。此外,在实际变换器中,死区时间的长短也影响每个周期内的断态电压应力持续时间。因此,对三种结构GaN器件设置占空比与死区时间时,在满足系统增益的前提下,均应尽可能缩短其处于断态的时间。

(4)在拓扑选择和开关条件设计方面,普通E-mode型与改进E-mode型GaN器件在高频条件下更适用于软开关条件;当受限于拓扑或控制策略而只能实现硬开关时,Cascode型GaN器件在通态损耗方面更具优势。

本文首先对GaN器件动态导通电阻发生机理及影响因素进行了分析;提出了一种GaN器件动态导通电阻综合测试平台及测试方法;针对三种不同结构(P-GaN盖帽层E-mode型、改进型P-GaN盖帽层E-mode型及Cascode型)的GaN器件分别搭建对应测试平台,进行了动态导通电阻测试,分析其在不同影响因素(包括断态电压应力、断态电压应力持续时间、负载电流、占空比、开关频率、开关条件)下的动态导通电阻现象,并从应用层面提出动态导通电阻优化方法。本研究有以下三点结论:

1)本文提出的GaN器件动态导通电阻综合测试平台可提供的测试条件基本涵盖实际应用中会对动态导通电阻产生影响的因素。基于该平台及对应的测试方法,可以方便且全面地对动态导通电阻在各影响因素下的变化情况进行精确测试。

2)三种结构GaN器件具有不同的动态导通电阻特性,随影响因素变化程度不同,且占主导的动态导通电阻影响因素不同。其中,普通E-mode型器件动态导通电阻现象最为明显,改进E-mode型器件次之,Cascode型器件动态导通电阻现象最不明显。对于普通E-mode型器件,开关频率、开关条件和断态电压应力占最主导因素;改进E-mode型器件受占空比影响最大,断态电压应力几乎不影响动态导通电阻;Cascode型器件受开关条件和负载电流的影响在一定程度均可忽略。

3)动态导通电阻会增大通态损耗,根据测试结果,在某些工作条件下,通态损耗实际值会升高到数据手册典型值2倍以上。因此,从应用层面优化动态导通电阻,对于降低通态损耗、提高效率、提高系统可靠性具有重要意义。在实际运用中,应综合器件动态导通电阻特性、电压、频率及开关条件设置,以保证在符合系统指标前提下,器件动态导通电阻实现最优化。

参考文献

[1] Millán J, Godignon P, Perpiñà X, et al. A survey of wide bandgap power semiconductor devices[J]. IEEE Transactions on Power Electronics, 2014, 29(5): 2155-2163.

[2] Flack T J, Pushpakaran B N, Bayne S B. GaN technology for power electronic applications: a review[J]. Journal of Electronic Materials, 2016, 45(6): 2673-2682.

[3] Khalil S G, Hardikar S, Sack S, et al. HV GaN reliability and status[C]//2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, 2015: 21-23.

[4] Ťapajna M, Hilt O, Bahat-Treidel E, et al. Gate reliability investigation in normally-off P-Type-GaN Cap/AlGaN/GaN HEMTs under forward bias stress[J]. IEEE Electron Device Letters, 2016, 37(4): 385-388.

[5] Ueda T. Reliability issues in GaN and SiC power devices[C]//2014 IEEE International Reliability Physics Symposium, Waikoloa, HI, 2014: 3D.4.1-3D.4.6.

[6] Wang C H, Ho S Y, Huang J J. Suppression of current collapse in enhancement-mode AlGaN/GaN high electron mobility transistors[J]. IEEE Electron Device Letters, 2016, 37(1): 74-76.

[7] Huang Huolin, Liang Y C, Samudra G S, et al. Effects of gate field plates on the surface state related current collapse in AlGaN/GaN HEMTs[J]. IEEE Transa- ctions on Power Electronics, 2014, 29(5): 2164-2173.

[8] Lu Bin, Palacios T, Risbud D, et al. Extraction of dynamic on-resistance in GaN transistors: under soft- and hard-switching conditions[C]//2011 IEEE Com- pound Semiconductor Integrated Circuit Symposium (CSICS), Waikoloa, HI, 2011: 1-4.

[9] Saito W, Nitta T, Kakiuchi Y, et al. Influence of electric field upon current collapse phenomena and reliability in high voltage GaN-HEMTs[C]//2010 22nd International Symposium on Power Semicon- ductor Devices & IC's (ISPSD), Hiroshima, 2010: 339-342.

[10] JEP173 Dynamic on-resistance test method guidelines for GaN HEMT based power conversion devices[S]. U.S.A: Jedec Solid State Technology Association, Jan. 2019.

[11] Joh J, Tipirneni N, Pendharkar S, et al. Current collapse in GaN heterojunction field effect transistors for high-voltage switching applications[C]//2014 IEEE International Reliability Physics Symposium, Waikoloa, HI, USA, 2014: 6C.5.1-6C.5.4.

[12] Hwang I, Kim J, Chong S, et al. Impact of channel hot electrons on current collapse in AlGaN/GaN HEMTs[J]. IEEE Electron Device Letters, 2013, 34(12): 1494-1496.

[13] Fabris E, Meneghini M, de Santi C, et al. Hot-electron trapping and hole-induced detrapping in GaN-based GITs and HD-GITs[J]. IEEE Transactions on Electron Devices, 2019, 66(1): 337-342.

[14] Li Rui, Wu Xinke, Yang Shu, et al. Dynamic on-state resistance test and evaluation of GaN power devices under hard- and soft-switching conditions by double and multiple pulses[J]. IEEE Transactions on Power Electronics, 2019, 34(2): 1044-1053.

[15] Martínez P J, Miaja P F, Maset E, et al. A test circuit for GaN HEMTs dynamic RON characterization in power electronics applications[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2019, 7(3): 1456-1464.

[16] Li Yuan, Zhao Yuanfu, Huang A Q, et al. Evaluation and analysis of temperature-dependent dynamic RDS,ON of GaN power devices considering high- frequency operation[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 111-123.

[17] Cai Yichen, Forsyth A J, Todd R. Impact of GaN HEMT dynamic on-state resistance on converter performance[C]//2017 IEEE Applied Power Elec- tronics Conference and Exposition (APEC), Tampa, FL, 2017: 1689-1694.

[18] Chang C Y, Li Yichen, Ren Kailin, et al. An AlGaN/GaN high electron mobility transistor with a built-in light emitter using radiative recombination of two-dimensional electron gas and holes[J]. IEEE Journal of the Electron Devices Society, 2020, 8: 346-349.

[19] 梁美, 李艳, 郑琼林, 等. 高速 SiC MOSFET开关特性的测试方法[J]. 电工技术学报, 2017, 32(14): 87-95.

Liang Mei, Li Yan, Zheng Qionglin, et al. Test method for switching performance of high speed SiC MOSFET[J]. Transactions of China Electrotechnical Society, 2017, 32(14): 87-95.

[20] 闫琪, 李艳, 王路. 基于GaN器件的双Buck逆变器共模与损耗[J]. 电工技术学报, 2017, 32(20): 133- 141.

Yan Qi, Li Yan, Wang Lu. The common-mode characteristics and loss of dual Buck grid-connected inverter based on GaN devices[J]. Transactions of China Electrotechnical Society, 2017, 32(20): 133-141.

[21] 何杰, 刘钰山, 毕大强, 等. 电压探头对宽禁带器件高频暂态电压精确测量的影响[J]. 电工技术学报, 2021, 36(2): 362-372.

He Jie, Liu Yushan, Bi Daqiang, et al. Impacts of voltage probes for accurate measurement of high- frequency transient voltage of wide-bandgap devices[J]. Transactions of China Electrotechnical Society, 2021, 36(2): 362-372.

[22] Badawi N, Dieckerhoff S. A new method for dynamic RON extraction of GaN power HEMTs[C]//Pro- ceedings of PCIM Europe 2015; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 2015: 1-6.

Accurate Measurement of Dynamic on-Resistance of GaN Devices and Affecting Factor Analysis

Abstract Compared with traditional Si devices, GaN devices have the advantages of high voltage and high temperature resistance, small on-resistance and low switching loss. However, the dynamic on-resistance of GaN devices has become the main reliability problem that limits their large-scale application. Based on the affecting factor analysis of the dynamic on-resistance, this paper proposes a comprehensive test platform and test method. The dynamic on-resistance under several affecting factors of three GaN devices with same voltage/current level and different structures is tested. The proportion of affecting factors and the change of dynamic on-resistance are analyzed. The mechanism analysis is verified by being compared with experimental results. Finally, the application methods of GaN devices with low dynamic on-resistance are given. The proposed test platform covers most of the affecting factors of dynamic on-resistance in practical applications. The experimental results show that the dynamic on-resistance characteristics and the dominant affecting factors are different with different device structures. Optimizing the dynamic on-resistance from the application level can effectively reduce the conduction loss.

keywords:GaN devices, current collapse effect, dynamic on-resistance, accurate test, optimized application method

DOI: 10.19595/j.cnki.1000-6753.tces.211710

中图分类号:TM46; TN30

国家自然科学基金面上资助项目(51877007)。

收稿日期 2021-10-28

改稿日期 2021-12-12

赵方玮 女,1995年生,博士研究生,研究方向为GaN功率器件精确测试及应用。E-mail: zhaofangwei@bjtu.edu.cn

李 艳 女,1977年生,教授,博士生导师,研究方向为电力电子高频变换器、宽禁带半导体器件应用。E-mail: liyan@bjtu.edu.cn(通信作者)

(编辑 陈 诚)