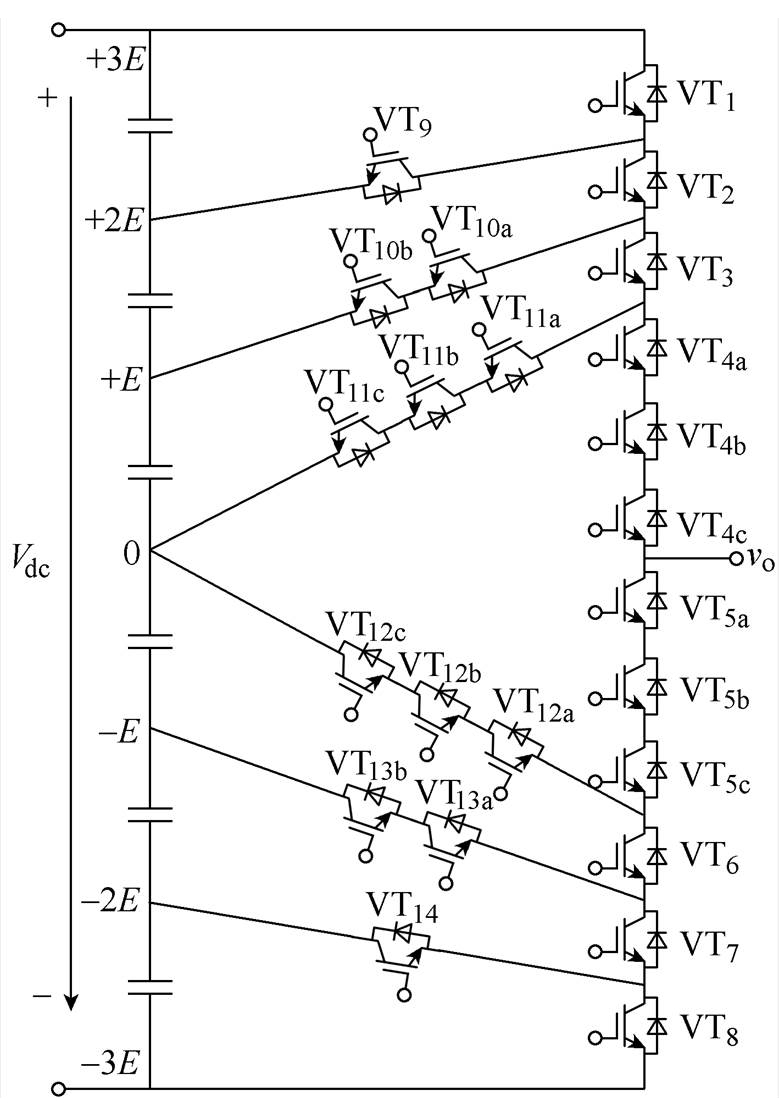

图1 七电平VMC拓扑结构

Fig.1 Configuration of seven-level VMC

摘要 只有公共直流侧电容的V形钳位多电平变换器(VMC)在中压、大功率电能变换的场合具备良好的应用价值。但当VMC电平数较高时,其换流回路电感不可避免地增大,使IGBT开关器件的关断过电压问题凸显。为此,该文提出一种简单的VMC吸收电路方案。依据VMC的运行原理,将其开关器件区分为主开关器件和辅助开关器件。主开关器件动作并切换电流通路,在每一对互补的主开关器件两端添加吸收电容(构成类似半桥开关能量缓冲单元),以抑制其关断过电压。而主开关器件相对应的辅助开关器件则先开通、后关断,仅提供静态电压支撑的功能,因此无需吸收电路保护。该文以七电平VMC为例,对所提的吸收电路方案进行了分析和研究。实验结果表明,所提的VMC吸收电路方案能够显著抑制开关器件的关断电压尖峰。并且,该方案仅需少量吸收电容与主开关一起构成类似半桥开关能量缓冲单元的形式即可实现所有开关器件的关断过电压保护,其成本低、可靠性高,具有良好的工程实用性。

关键词:V形钳位多电平变换器 吸收电路 IGBT关断过电压 电压尖峰

相较于传统的两电平变换器,多电平变换器突破了现有功率半导体器件的电压等级限制,避免了开关器件的直接串联动作;并且,其输出谐波特性较好、电磁干扰较小[1-2]。因此,多电平变换器被广泛应用于中高压、大功率电能变换的场合,如电机驱动[3]、无功补偿[4]、新能源发电并网[5]以及高压直流(High-Voltage Direct Current, HVDC)输电[6]等。近年来,不断有新型的多电平拓扑被提出,以适应不同应用场合的要求。其中,文献[7-8]提出了一种V形钳位多电平变换器(V-clamp Multilevel Converter,VMC)拓扑。对比传统的中点钳位(Neutral-Point Clamped, NPC)型与飞跨电容(Flying Capacitor, FC)型变换器,VMC大幅减少了钳位器件的数量,有利于降低变换器体积并简化控制复杂度,为中压领域的应用提供了一种优选方案。

尽管以VMC为代表的多电平变换器具备上述诸多优势,但多电平变换器结构较为复杂,换流回路较长,引入了更多的杂散电感[9-10]。当变换器切换输出电平时,较大的电流变化率(di/dt)使回路中的杂散电感感应出电压尖峰。该电压尖峰叠加在关断的IGBT器件两端,造成瞬态电压应力增大,严重时会损坏开关器件,影响到变换器的安全运行[11]。虽然采用叠层母排能够在一定程度上缓解上述问 题[12],但是,随着变换器的电平数升高,其结构复杂程度上升,为母排的设计带来了很大的困难,优化效果有限。因此,有必要为多电平变换器添加吸收电路,以抑制开关器件的关断过电压,确保多电平变换器的正常工作。

目前,针对多电平变换器吸收电路的研究主要集中在三电平NPC、FC及T型变换器[13-18]。一种方法是针对单个开关器件添加RC或RCD吸收电路,如应用于三电平NPC的3RCD吸收电路等[13];另一种方法是将两电平吸收电路拓展应用至多电平变换器中。文献[14-15]分别研究了Undeland吸收电路在三电平NPC及FC中的应用。文献[16]则提出了一种适用于三电平NPC的Mcmurry吸收电路。此外,文献[17]针对NPC变换器提出一种无源无损吸收电路单元,实现了开关器件的低电压应力开关。文献[18]则研究T型变换器的软开关技术,有效抑制了其开关器件的关断过电压尖峰。

虽然上述的吸收电路方案有效解决了三电平变换器的IGBT器件关断过电压问题,但针对电平数较高的VMC拓扑,适用性不佳。这是由于在高电平数的VMC中,其包含的IGBT开关器件数量较多,若仍然采用上述的吸收电路方案,所需添加的吸收器件总数量过多,这会大幅增加变换器的复杂程度,对变换器的成本和可靠性均造成了明显的负面影响[19]。

本文提出一种用于VMC的吸收电路方案。该方案巧妙利用了VMC的电平切换原理,将其开关器件划分为主开关器件及相对应的辅助开关器件。在电平切换的过程中,主开关器件动作以实现电流通路的切换,而其对应的辅助开关器件则延迟关断、提前开通,仅提供静态电压支撑的功能,不存在关断过电压的问题。通过这种调制方式,仅需要为主开关器件添加吸收电路。并且,由于VMC中互补动作的主开关器件相互临近,构成类似两电平半桥变换单元。因此可以在该“半桥变换单元”的正负两端添加一个吸收电容支路即可实现其关断过电压的保护。本文以七电平VMC为例,对所提的吸收电路方案进行了分析和说明。实验结果证明了所提方案的有效性。

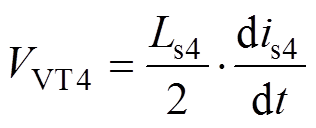

图1展示了七电平VMC的拓扑结构,由直流侧电容、输出功率桥臂及六条钳位支路构成。直流侧电容包含6个级联电容,将直流母线电压均分为7个电平,分别为+3E、+2E、+E、0、-E、-2E及-3E,其中E=Vdc/6。

图1 七电平VMC拓扑结构

Fig.1 Configuration of seven-level VMC

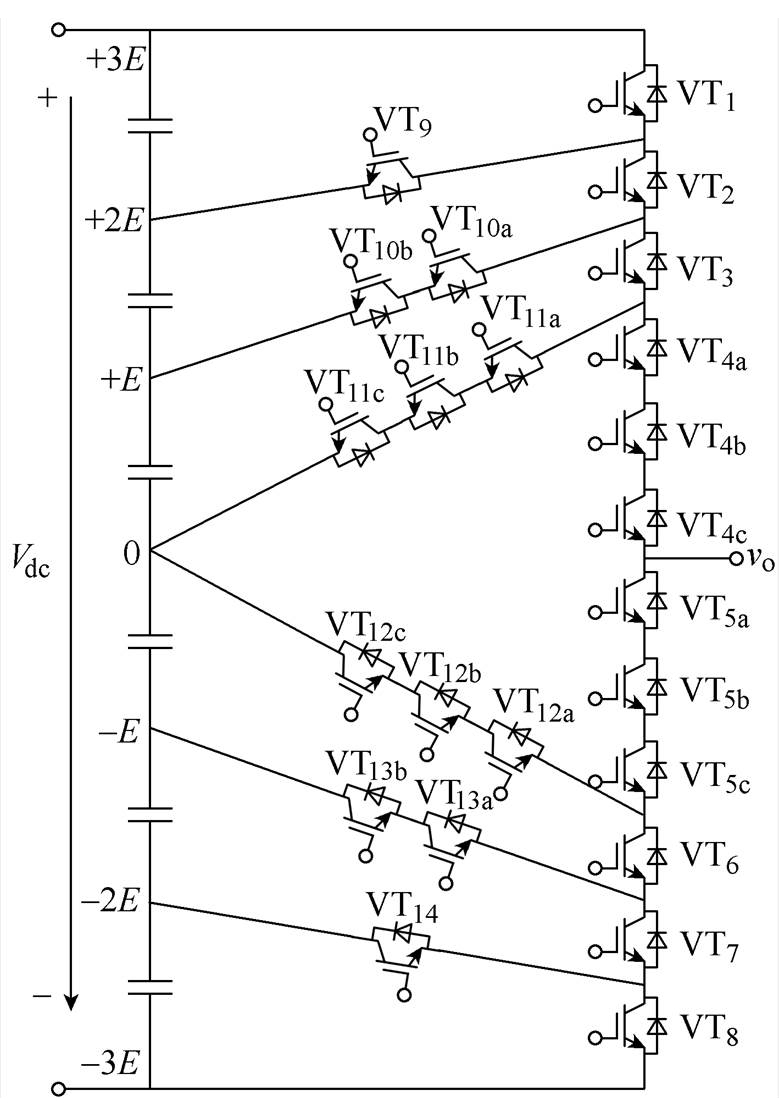

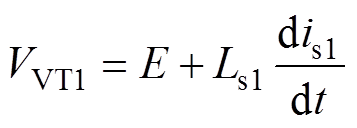

七电平VMC的开关状态见表1,表中,VT1~VT14为对应开关器件的门极信号,其值为“1”表示导通状态,为“0”表示关断状态。此处,由VT4统一表示同向串联的开关管VT4a、VT4b与VT4c,三者的动作信号同步。其他串联开关管VT5、VT10、VT11、VT12与VT13的表示与此相似。观察表1可知,开关器件VT1与VT9,VT2与VT10,VT3与VT11,VT12与VT6,VT13与VT7,VT14与VT8分别互补动作,以防止直流侧电容短路。此外,VT4在调制电压信号为正时保持导通,在调制电压信号为负时保持关断。VT5的开关状态则与VT4互补。依据表1对七电平VMC进行调制,即可分别输出直流母线的7个电平电压。

表1 七电平VMC开关状态

Tab.1 Switching states of seven-level VMC

输出电平voVT1,VT2,VT3,VT12,VT13,VT14, +3E111000 +2E011000 +E001000 0000000 -E000100 -2E000110 -3E000111

注:“1”表示导通;“0”表示判断。

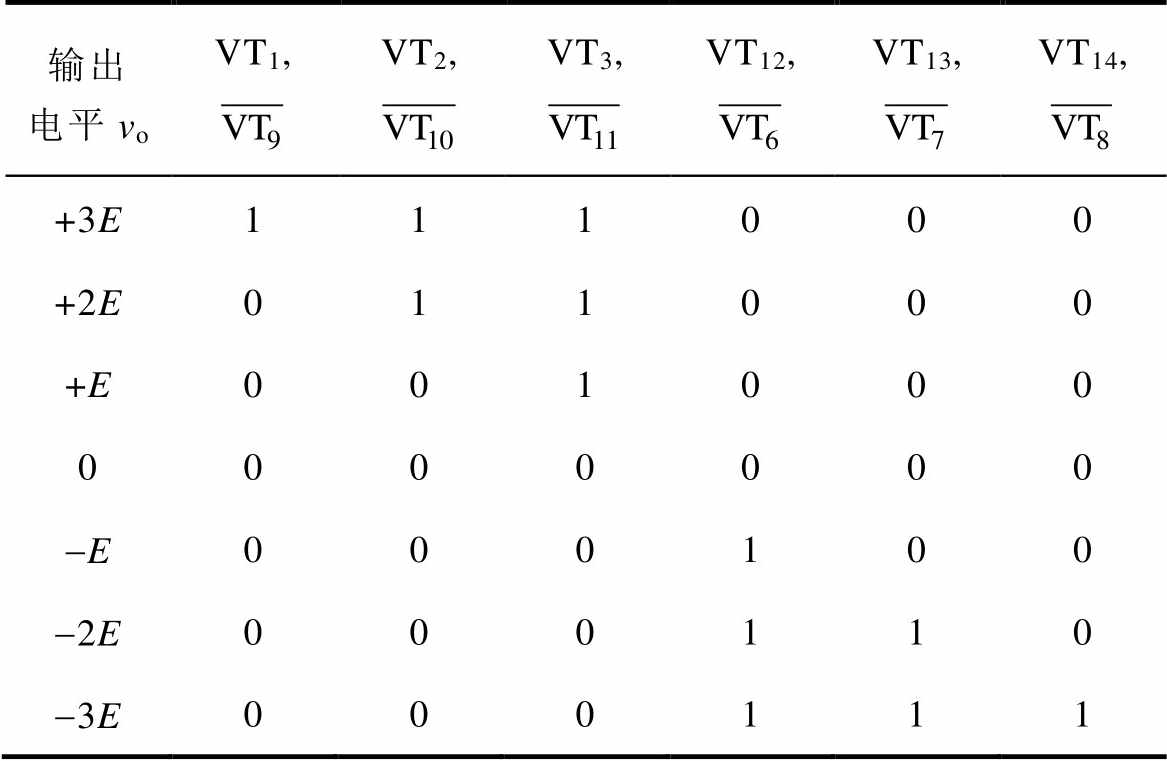

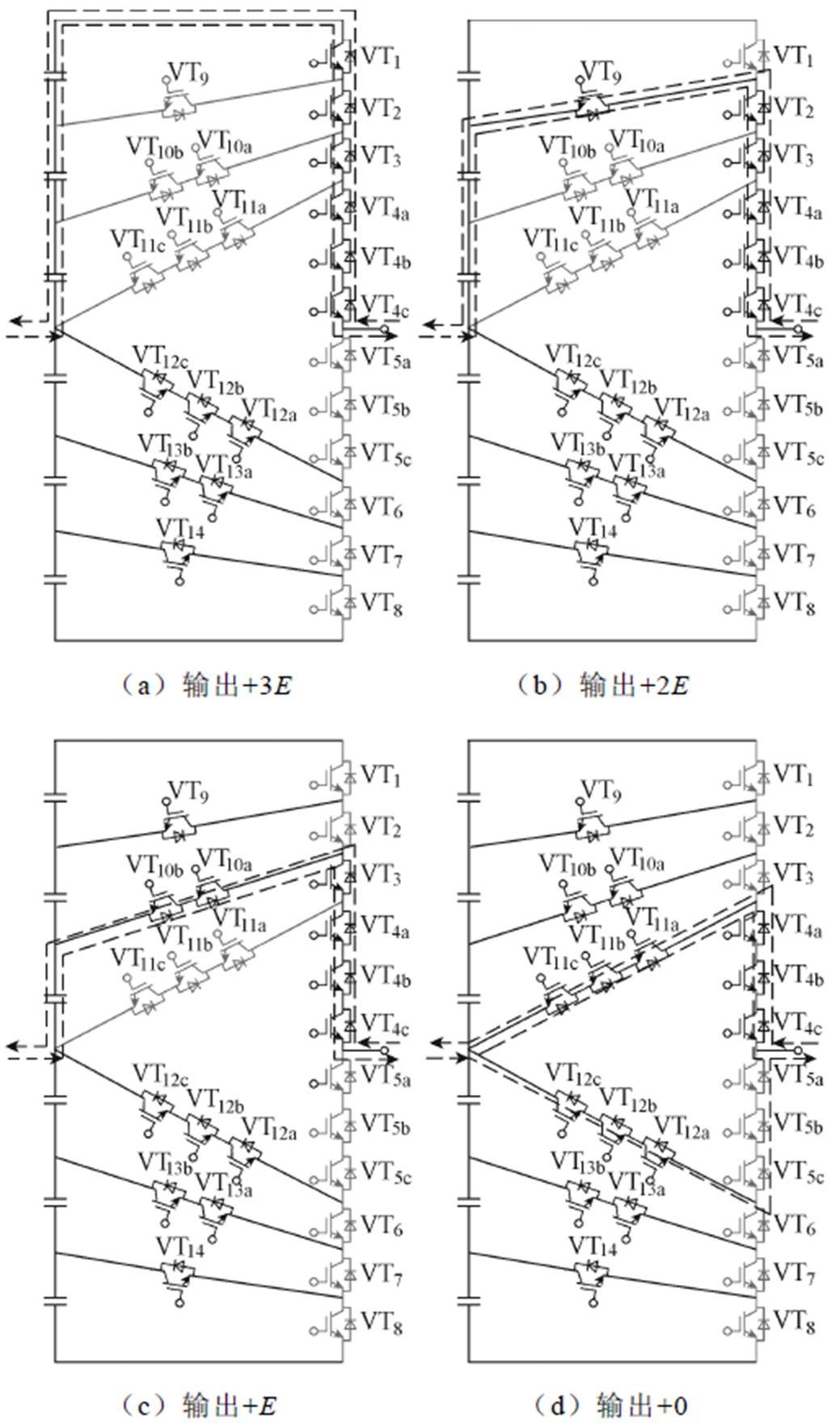

在理想情况下,VMC中所有开关器件的最大阻断电压均为E。但在实际换流过程中,考虑到换流回路的杂散电感以及二极管的反向恢复特性,开关器件会产生关断电压尖峰。图2展示了七电平VMC各输出电平的电流通路,令Io>0表示为电流方向从直流母线电容流向交流输出端,Io<0表示为电流方向从交流输出端流向直流侧母线电容。下文以Io> 0的情况为例,分析换流过程中出现的开关器件关断过电压现象。

当输出电平由+3E切换到+2E时,VT1关断、VT9开通,负载电流由VT1换流至VT9的反并联二极管通路。此时,VT1的关断电压表示为

(1)

(1)

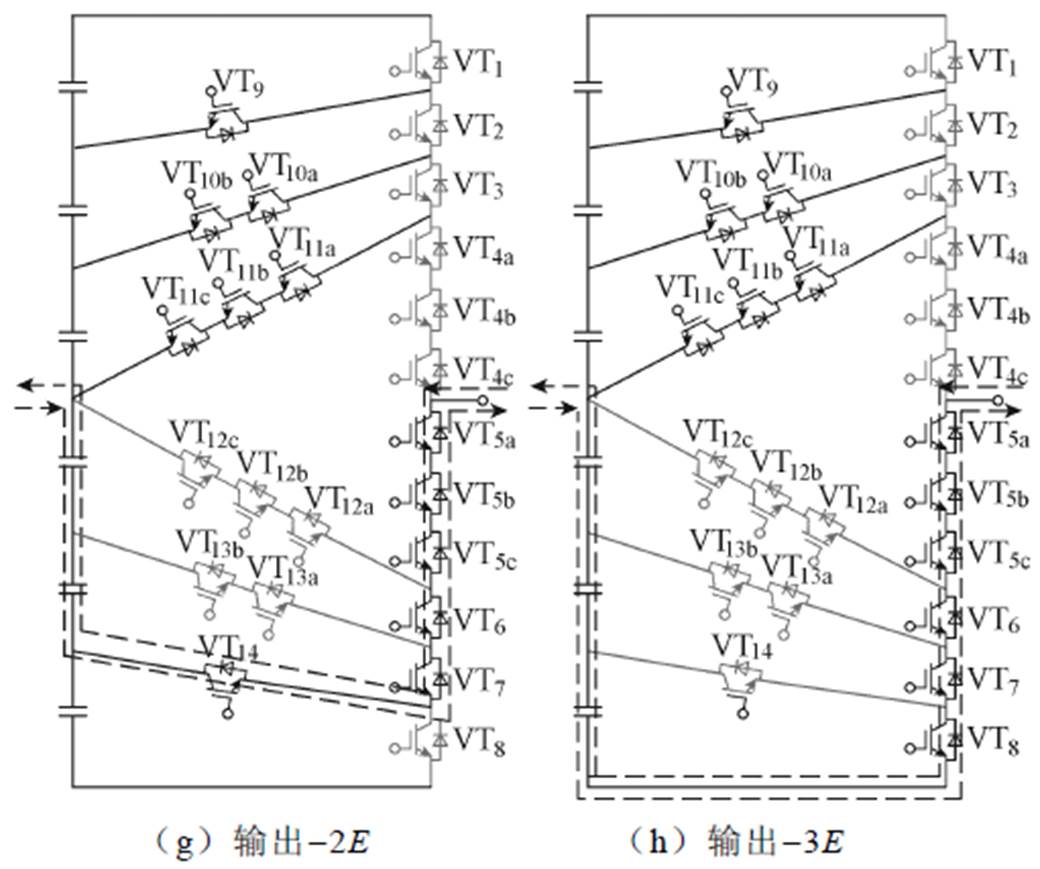

式中,Ls1为+3E与+2E电平之间的换流回路电感;dis1/dt为该换流回路的电流变化率。可以看出,Ls1的值越大,VT1的关断过电压尖峰也就越高。

而当输出电平由+2E切换到+3E时,VT9关断,VT1开通,负载电流由VT9的反并联二极管切换至VT1通路。该换流过程中,VT9的反并联二极管由正向导通的状态向反偏关断的状态转换,产生了反向恢复电流[20]。此时,VT9的关断电压尖峰主要是由反向恢复电流引起的,即

图2 七电平VMC电流通路

Fig.2 Current paths of seven-level VMC

(2)

(2)

式中,dir1/dt为反向恢复电流的变化率。同样地,较大的杂散电感Ls1也会造成较高的VT9关断过电压尖峰。

同理,上述的分析可以推广至+2E与+E电平、+E与+0电平之间切换的过程中。需要说明的是,在上述回路中,VT10与VT11代表的串联开关器件添加了静态均压电阻,实现了其闭锁状态下的静态均压,但并未添加复杂的动态均压电路。VMC中的其余串联开关器件与此相同。由于+2E与+E电平、+E与+0电平之间的换流回路相对较长,其杂散电感引起的电压尖峰也会相应更大。

特别地,当输出电平由+0切换到-0时,VT4关断、VT5开通。此时,一半的负载电流由VT11的反并联二极管及VT4换流至VT12与VT5的反并联二极管通路。在该换流过程中,VT11因始终保持导通状态,可以被当作导线。由于该换流回路中不包含直流侧电容,VT4的关断电压表示为

(3)

(3)

式中,Ls4为+0与-0电平之间的换流回路电感;dis4/dt为该换流回路的电流变化率。一般而言,VT4的关断电压幅值相对较小。但在Ls4值较大的情况下,仍存在一定的关断过电压风险。

而当输出电平由-0切换到+0时,VT5关断、VT4开通。一半的负载电流由VT12及VT5的反并联二极管换流至VT11的反并联二极管及VT4通路。由于在该换流过程结束后,仍存在一半的负载电流通过VT12与VT5的反并联二极管通路续流,因此VT5两端的关断电压VVT5=0。

依据对称性,VMC下半桥臂的换流过程也可以推导得出。而在Io<0的情况时,互补开关器件的关断电压峰值相互调换,此处不再赘述。

综上所述,在七电平VMC中,各开关器件在关断的过程中可能出现电压尖峰,因此有必要添加吸收电路进行保护。

由第2节的分析可知,若采用表1中的调制方法,在七电平VMC的各个开关器件均存在关断过电压的风险,需要添加相应的保护措施。显然,过多的保护目标不利于VMC吸收电路的简化设计。

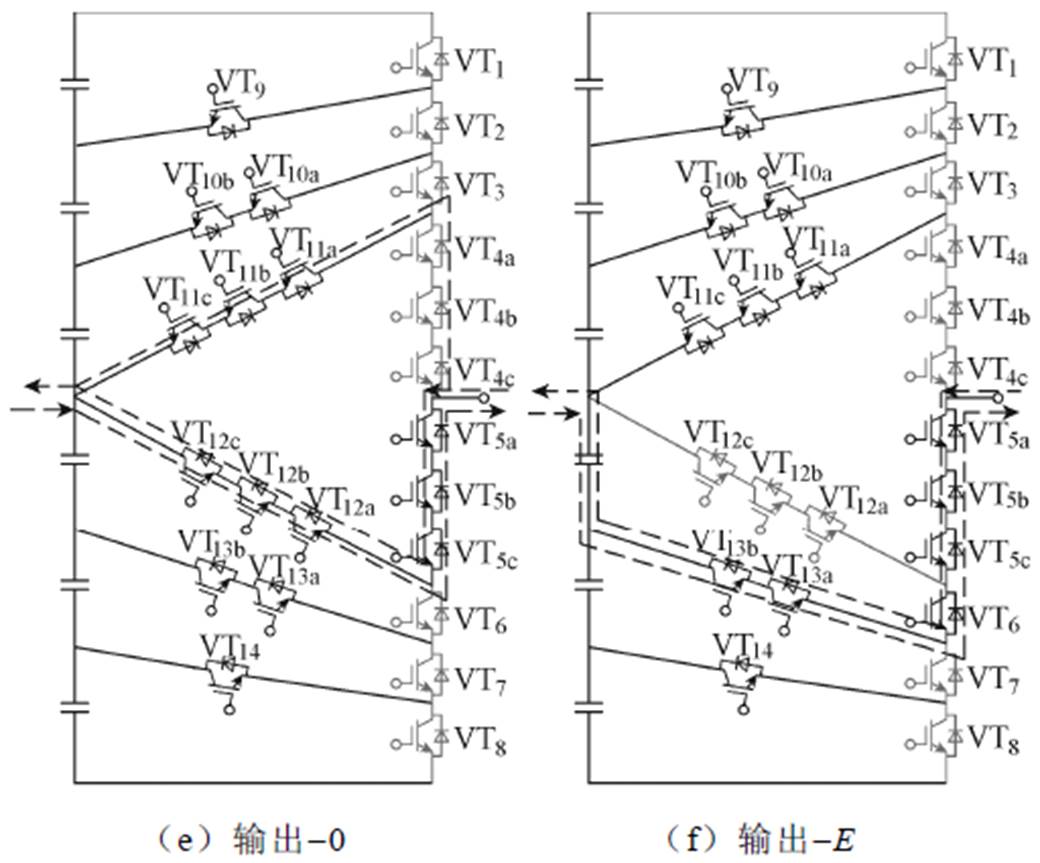

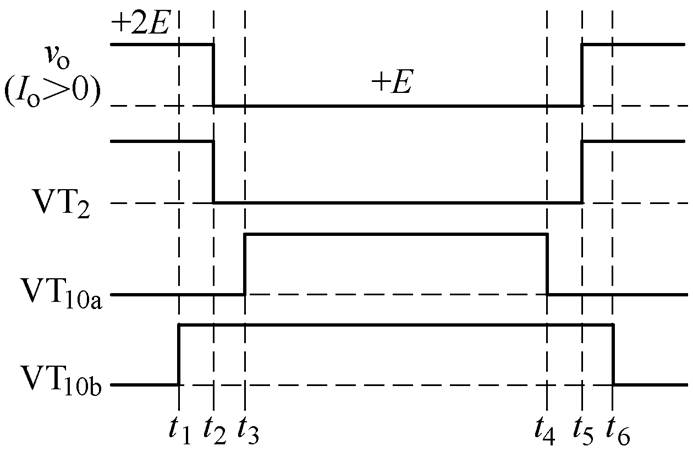

本节对VMC的调制方法进行改进,减少了存在关断过电压风险的开关器件数量。依据七电平VMC的基本运行原理,对其进行变换单元的分解,七电平VMC的变换单元示意图如图3所示。此处为直观展示,对七电平VMC的拓扑结构做了变形处理。将开关器件VT1与VT9,VT2与VT10a,VT3与VT11a,VT4c与VT5a,VT12a与VT6,VT13a与VT7,VT14a与VT8划分为主开关器件,这七对互补动作的主开关器件分别构成了变换单元Ⅰ~Ⅶ(见图3中阴影部分)。VT10b作为VT10a的辅助开关器件,VT11b和VT11c作为VT11a的辅助开关器件,VT4a和VT4b作为VT4c的辅助开关器件,VT5b和VT5c作为VT5a的辅助开关器件,VT12b和VT12c作为VT12a的辅助开关器件,VT13b作为VT13a的辅助开关器件。

图3 七电平VMC的变换单元示意图

Fig.3 Operation cells in seven-level VMC

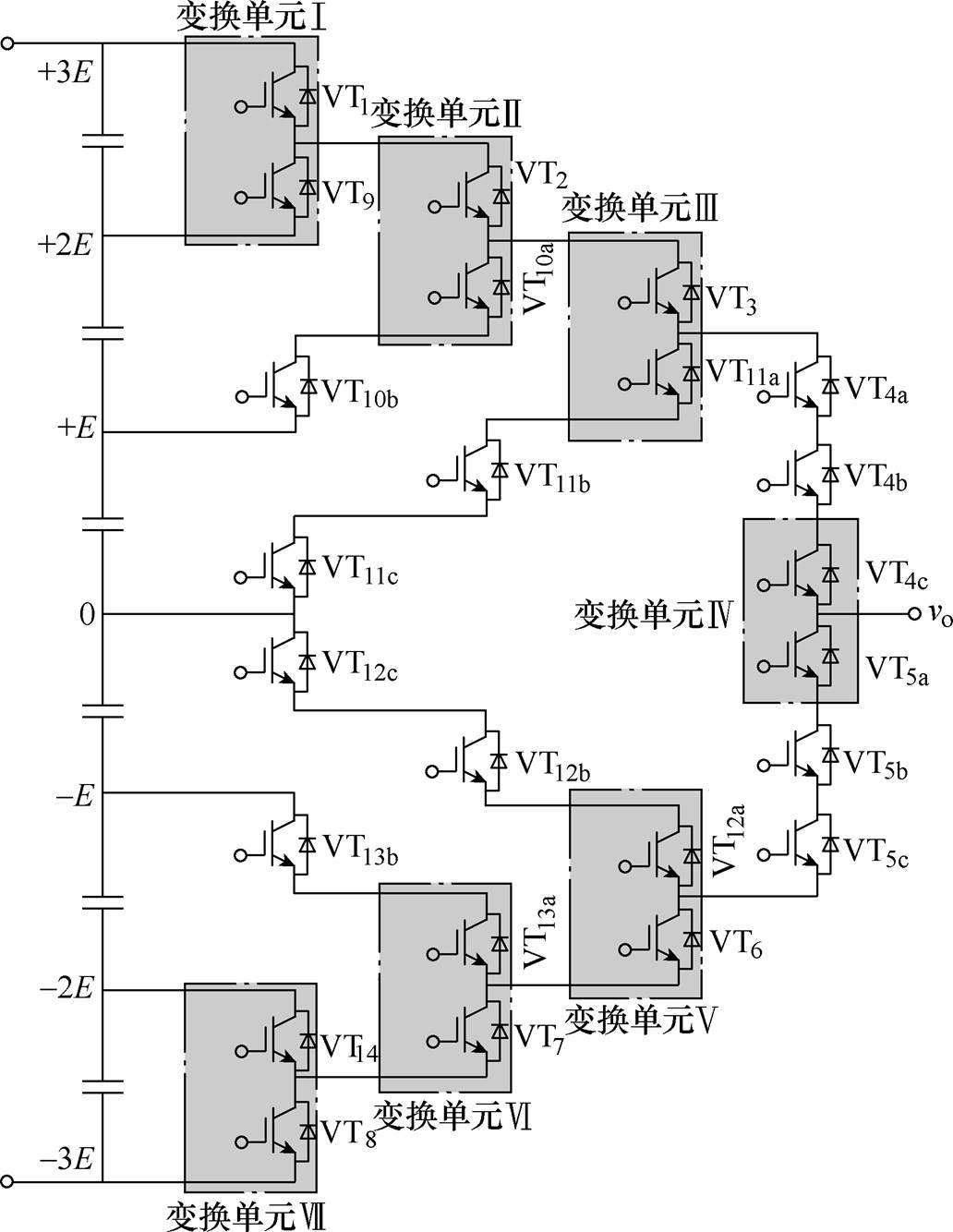

在改进的VMC调制方法中,主开关器件仍然按照表1中的开关状态进行调制;其对应的辅助开关器件不再同时动作,而是提前导通、延迟关断。按照这一原则,可以获得七电平VMC中辅助开关器件的调制信号。以输出电平+2E与+E的切换(Io>0)为例进行说明,图4展示了VT2、VT10a以及VT10b的调制信号。图中,在t1时刻之前,变换器输出+2E电平,VT2导通,VT10a及VT10b关断;在t1时刻,VT10b提前开通,此时负载电流通路未改变,VT10b为零电流开通;在t2时刻,VT2关断,负载电流通路变换,输出电平切换为+E,VT2承受关断过电压;在t3时刻,VT10a开通,该换流过程结束。在t4时刻,VT10a关断,此时负载电流仍通过VT10a、VT10b的反并联二极管通路续流;在t5时刻,VT2开通,负载电流通路变换,输出电平切换为+2E,此时VT10a承受过电压尖峰,而VT10b则保持开通状态,不承受电压;在t6时刻,VT10b关断,由于此时换流过程已经结束,VT10b为零电压关断。图4中,t1与t2,t2与t3,t4与t5,t5与t6时刻之间均相差一个死区时间,以确保开关器件的完全动作。其他辅助开关器件的调制信号可以同理获得。

图4 七电平VMC改进调制方法示意图

Fig.4 Improved modulation method of seven-level VMC

可以看出,改进的VMC调制方法实质上是对钳位支路中的串联开关器件进行“分工”。由主开关器件构成的变换单元负责实现输出电平的切换,而其辅助开关器件则提前开通、延迟关断,仅提供静态电压支撑的功能。由于辅助开关器件实现了零电流开通和零电压关断,无需添加吸收电路保护。因此当七电平VMC中采用改进的调制方法时,仅需对14个主开关器件添加关断过电压保护措施,保护目标的数量减少了10个,大幅简化了VMC吸收电路的设计难度。

对七电平VMC中的主开关器件添加吸收电路。由图3中可以看出,每一对互补动作的主开关器件构成了一组变换单元,而变换单元的工作模式相当于两电平的半桥结构。当VMC切换其相邻的输出电平时,可以看作是对应的变换单元在切换其高、低输出电平。从这一角度出发,VMC中开关器件的过电压保护可以直接采用两电平变换器的吸收电路。

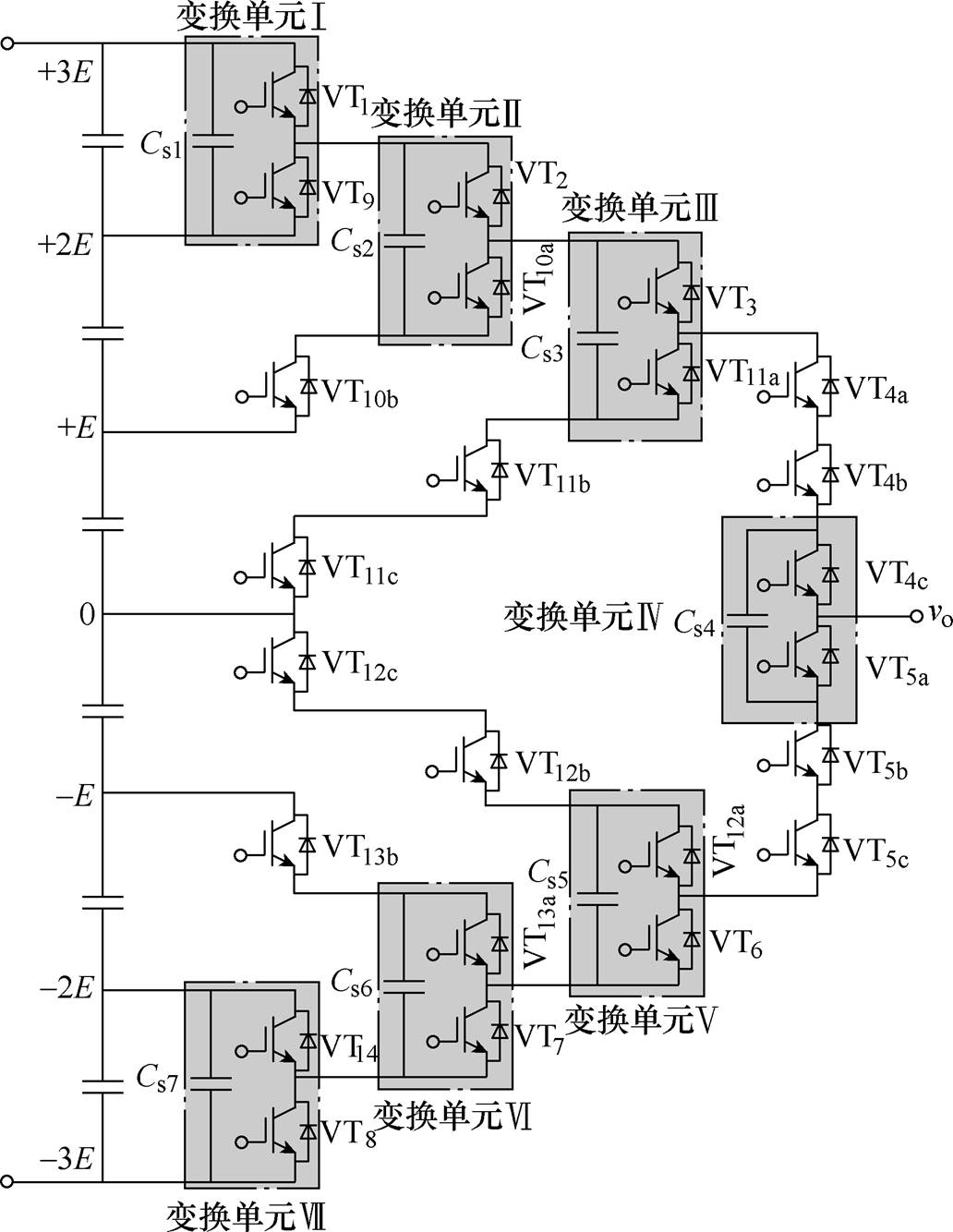

本文在VMC各变换单元的正负两端添加吸收电容支路,以解耦换流回路中大部分杂散电感的影响,降低主开关器件的关断电压尖峰。图5展示了添加吸收电容Cs1~Cs7后的七电平VMC结构。

图5 本文所提七电平VMC吸收电路方案

Fig.5 Configuration of seven-level VMC with proposed snubber circuits

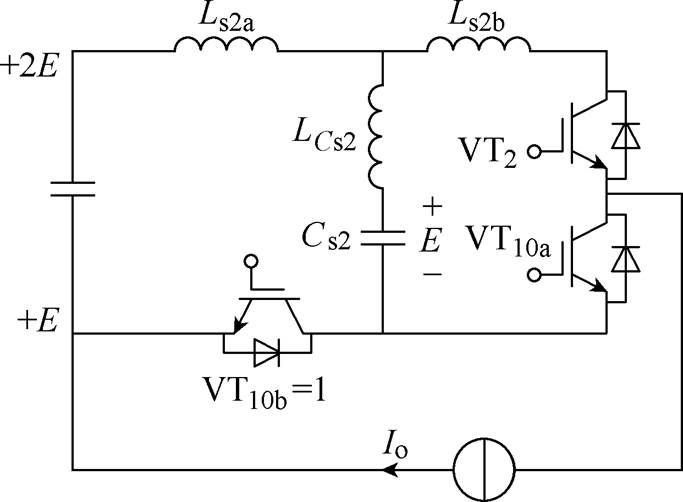

不失一般性,仍以输出电平+2E与+E的切换 (Io>0)为例来说明VMC吸收电路的保护机理,图6展示了该换流回路的等效电路。在该换流过程中,辅助开关器件VT10b保持导通状态,可以被当作导线。加入吸收电容Cs2后,该换流回路的杂散电感Ls2被分割为Ls2a与Ls2b两部分,LCs2为吸收电容的寄生电感。在电流通路切换时,存储在Ls2a中的能量大部分被Cs2所吸收,引起Cs2的波动。当Cs2取值较大时,可以近似认为其两端电压在换流过程中保持为E。此时,VT2与VT10a的关断过电压尖峰主要由Ls2b与LCs2两端的感应电压造成。

图6 +2E与+E电平换流回路等效电路

Fig.6 Equvialent circuit of commutation loop between +2E and +E states

当Ls2b与LCs2的值越小时,VT2与VT10a的关断电压值也就越接近其额定值E。由于VMC中变换单元内的主开关器件相互临近,通过合理布局设计、采用低感吸收电容的方法,即可使Ls2b与LCs2的值尽可能减小,达到抑制开关器件关断过电压的目的。同理,上述的分析结论可以应用至七电平VMC的其他变换单元中。

综合上述,采用改进的VMC调制方法,仅需添加7个吸收电容即可实现七电平VMC的开关器件过电压保护。

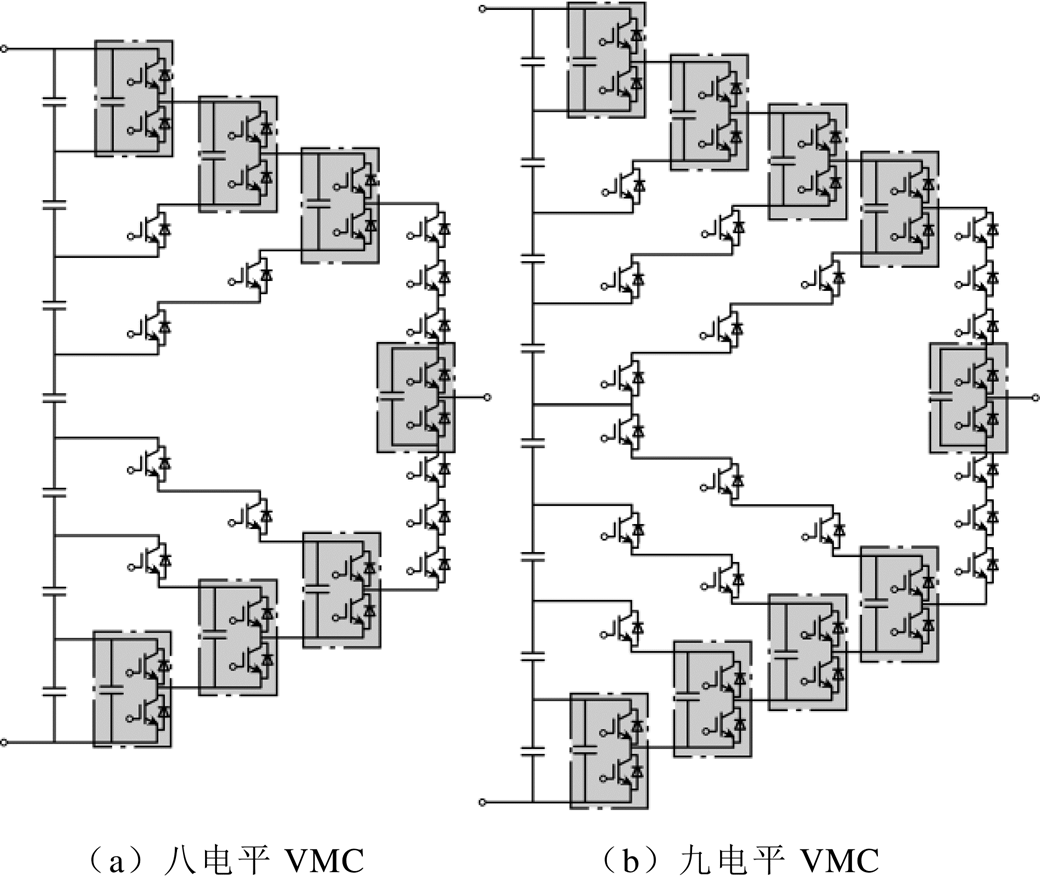

本文所提的VMC吸收电路方案可以拓展至任意电平的VMC结构中。图7a、图7b分别展示了其应用于八电平VMC、九电平VMC的示意图。

图7 VMC吸收电路方案的拓展

Fig.7 The expansion of proposed VMC snubber circuit

可以看出,该吸收电路方案应用于n电平VMC中:n为偶数时,需添加n 1个吸收电容;n为奇数时,需添加n个吸收电容。其结构简单,易于实现。

1个吸收电容;n为奇数时,需添加n个吸收电容。其结构简单,易于实现。

吸收电容值的选取将直接影响到其工作性能。本文所添加吸收电容的主要作用在于解耦开关器件的关断电压峰值与吸收回路外杂散电感的关系。此处,仍以+2E电平向+E电平的换流过程(Io>0)为例,对吸收电路的设计进行讨论。

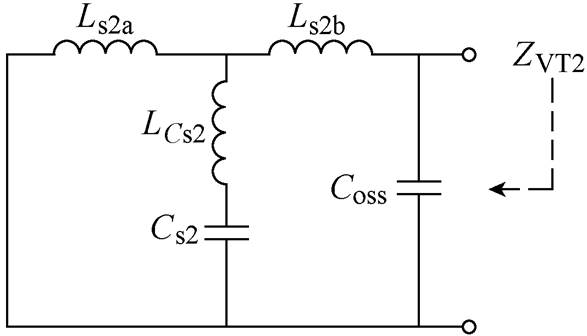

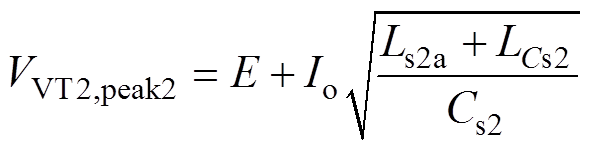

在图6中,VT2关断时出现了过电压振荡;此时VT10a的反并联二极管开始导通,等效为导线。将图6中的电压源(直流侧支撑电容)短路、将电流源开路,可以得到VT2两端的阻抗电路,如图8所示。其中,Coss为VT2的等效输出电容。

图8 VT2两端阻抗电路

Fig.8 Equvialent impedance circuit of VT2

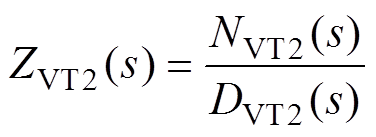

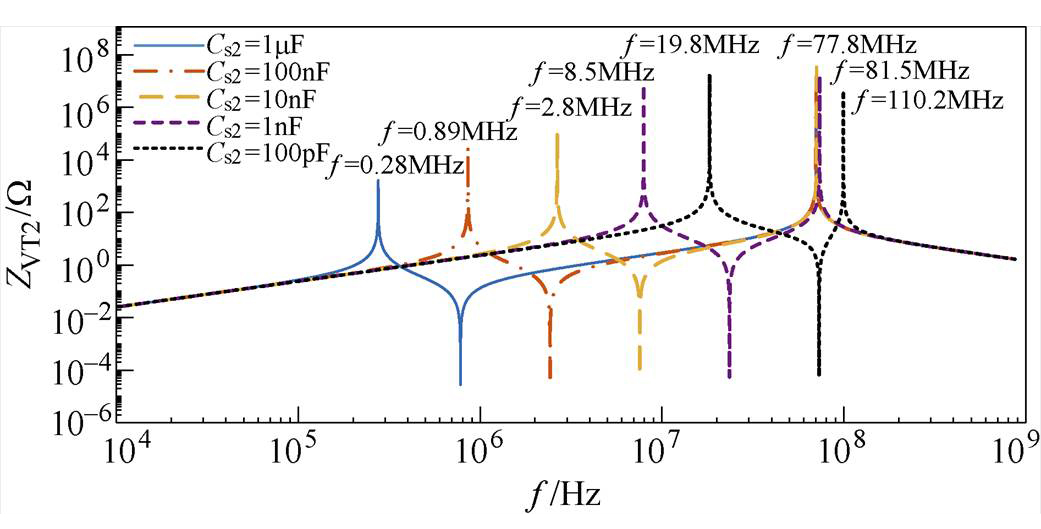

对图8求解,可得VT2两端的阻抗ZVT2为

(4)

(4)

其中

NVT2(s)=Cs2(Ls2aLCs2+Ls2aLs2b+LCs2Ls2b)s3+(Ls2a+Ls2b)s

DVT2(s)=Cs2Coss(Ls2aLCs2+Ls2aLs2b+LCs2Ls2b)s4+

(CossLs2a+CossLs2b+Cs2Ls2a+Cs2LCs2)s2+1

结合一组实际参数:Ls2a=300nH、Ls2b=20nH、LCs2=20nH、Coss=108pF,能够绘制出不同Cs2取值下的ZVT2幅频特性曲线,如图9所示。可以看出,ZVT2存在低频与高频两个谐振点。当吸收电容Cs2取值为10nF、100nF及1mF时,ZVT2的高频谐振点与Cs2无明显关系;而当Cs2取值为100pF及1nF时,ZVT2的高频谐振点随Cs2减小而向右偏移。因此,在线路杂散电感变化不大的情况下,Cs2取值满足式(5)中的经验关系,可以认为实现了VT2关断电压中的低频振荡与高频振荡之间的解耦。

图9 ZVT2的幅频特性曲线

Fig.9 Amplitude-frequency curves of ZVT2

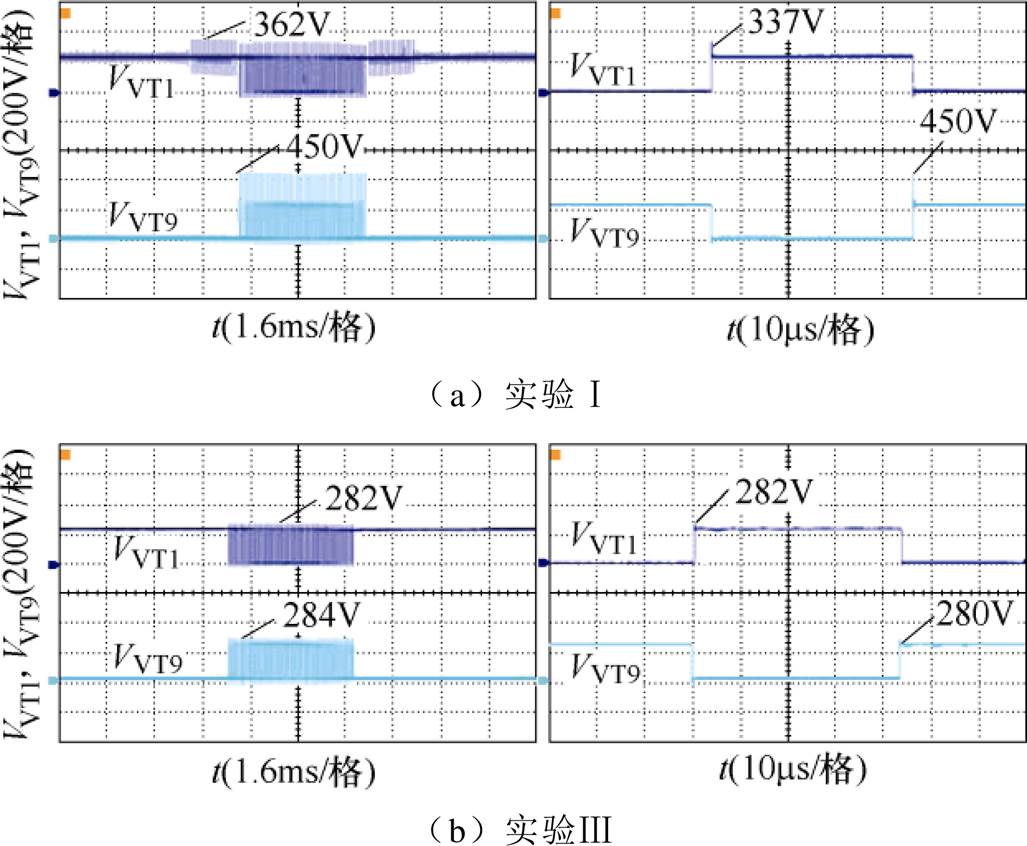

(5)

(5)

在满足式(5)的条件下,图6中的两个换流回路可以拆分开来进行分析。其中变换单元内的回路参数决定了VT2关断后的初始电压尖峰,即

(6)

(6)

式中,DIs2,max为+2E电平向+E电平换流过程中出现的最大电流变化率。

而变换单元外的回路在换流中产生了Cs2的低频电压振荡,同样会叠加在VT2两端,引起过电压为

(7)

(7)

由式(6)、式(7)可知,为实现VT2的关断电压峰值与Ls2a之间的解耦,VVT2,peak2应当小于VVT2,peak1,可得Cs2取值的另一条件为

(8)

(8)

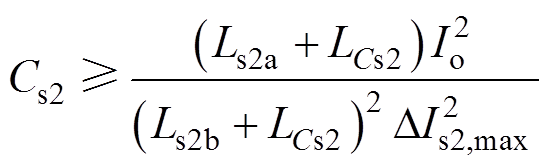

图10给出了VT2关断电压的仿真结果,直观展示了Cs2的取值是否满足式(8)的影响。观察可知,当Cs2=10nF时,VT2关断后的初始电压尖峰约为290V,但低频振荡的峰值达到了322V,VT2的最大关断电压值由低频振荡主导。而当Cs2= 1mF时,低频振荡的幅值和频率均降低,VT2的最大关断电压值变化为初始电压尖峰,获得了明显的下降。

上述的分析可以拓展至其他电平换流过程中。此处总结出吸收电路的设计原则:

图10 VT2关断电压仿真结果

Fig.10 The voltage waveforms of VT2 by simulation

(1)吸收电容取值至少应满足式(5)与式(8)的条件,以实现开关器件最大关断电压与吸收电路外杂散电感的解耦。

(2)在合理范围内增大吸收电容取值,能够有效降低低频振荡的幅值,维持输出电平的稳定。

(3)尽可能减小吸收回路内的线路电感以及吸收电容的寄生电感,有利于降低开关器件的关断过电压峰值。

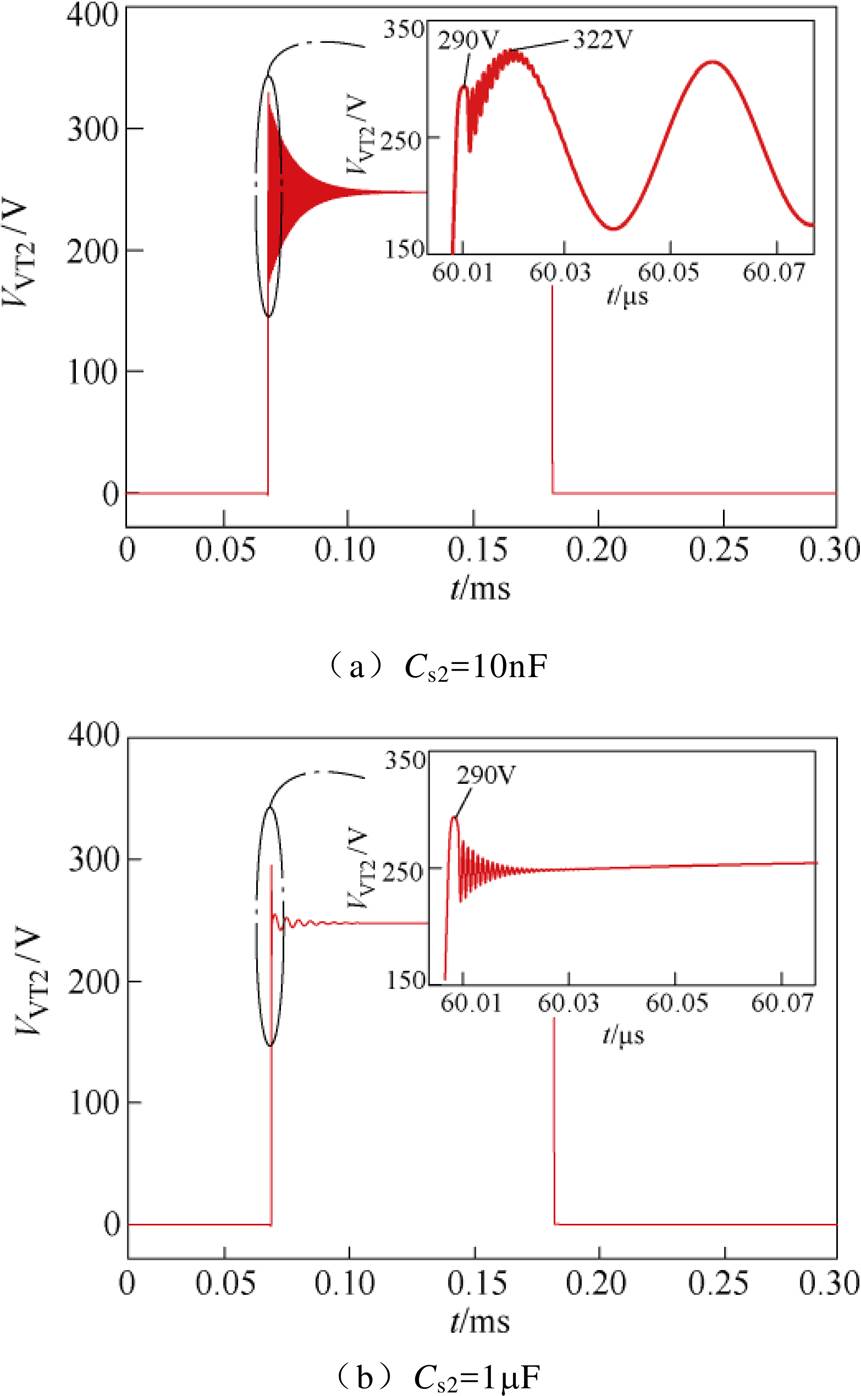

为验证本文所提VMC吸收电路方案的有效性,搭建了七电平VMC的原理样机。实验中,额定直流侧母线电压为1 440V,由6个级联直流电源供电,单个直流侧电容的额定电压为E=240V。开关器件采用Infineon公司的IKW30N60T型IGBT。负载为40W/4mH的阻感负载,负载电压的基频为50Hz。通过图11中所示的PD-PWM方法获得主开关器件的初始调制信号,图11中,0~2p 为一个基波周期。设定调制波的调制系数为0.87,载波的频率为5kHz。

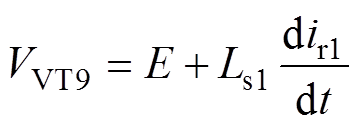

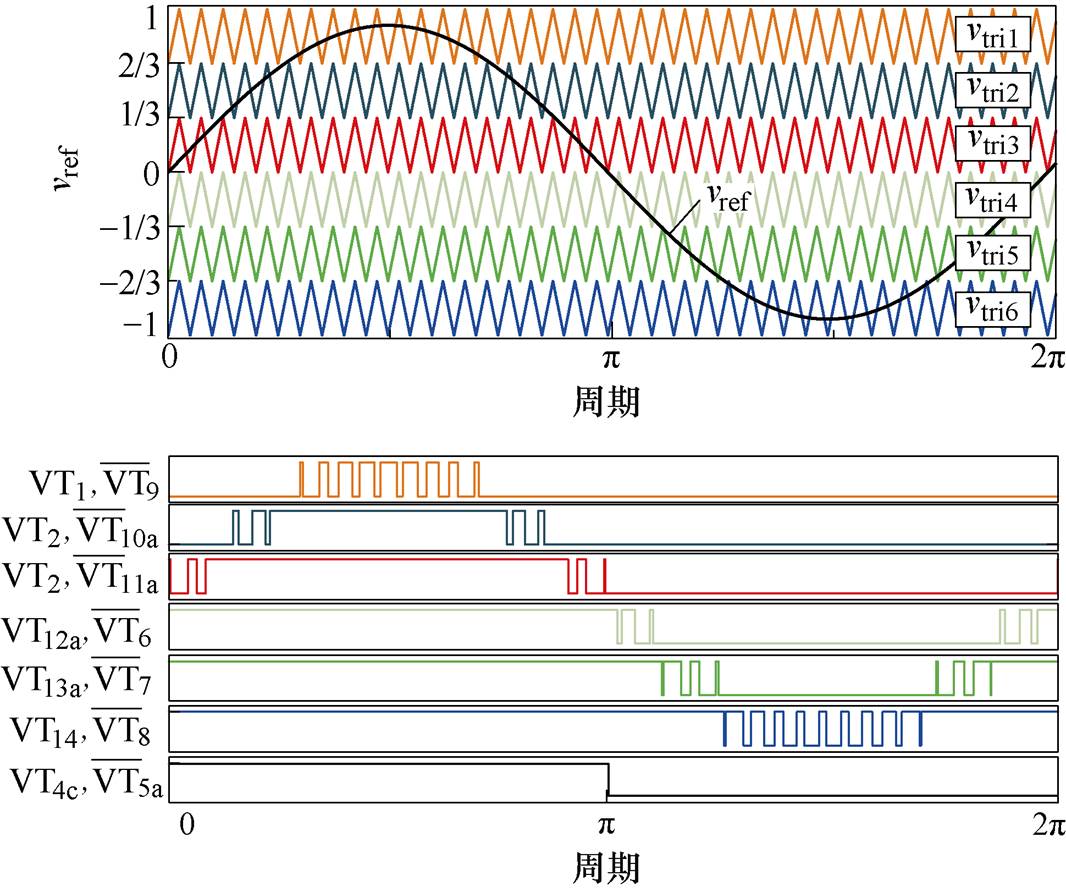

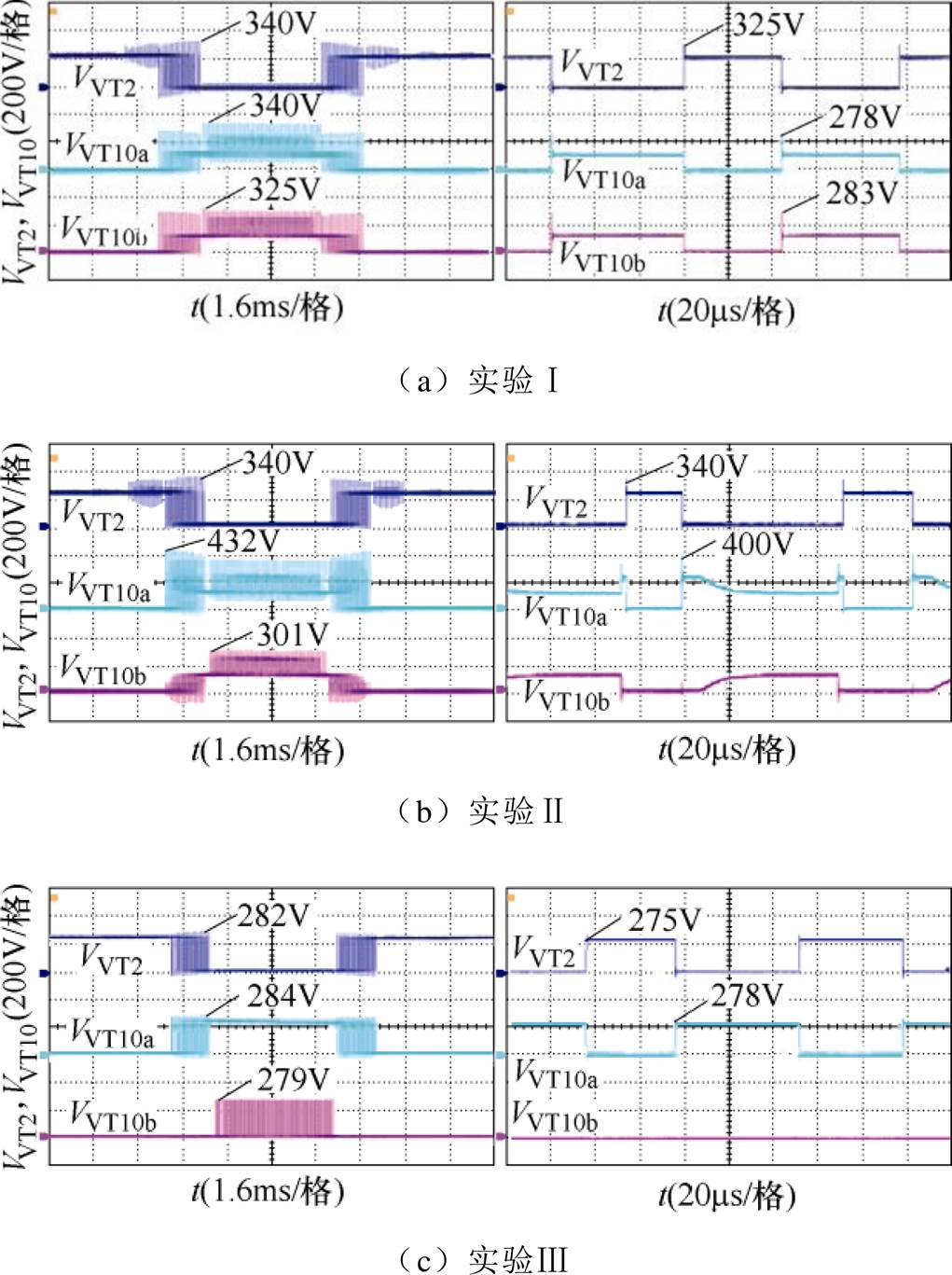

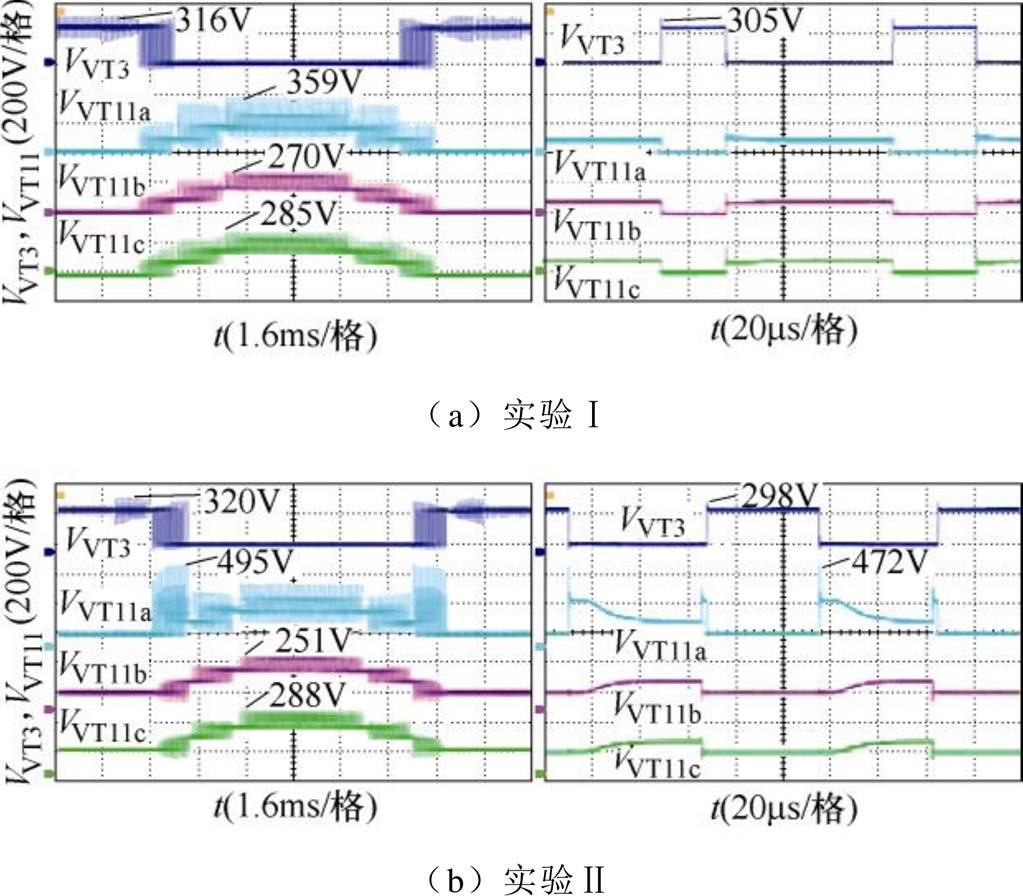

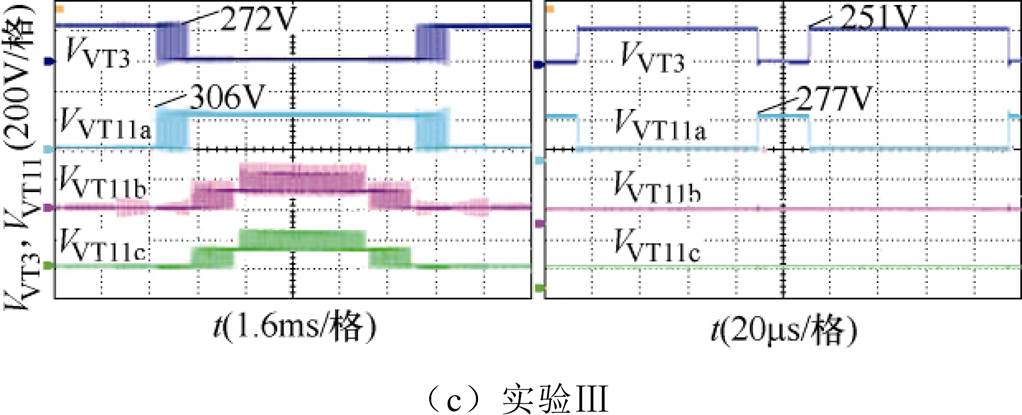

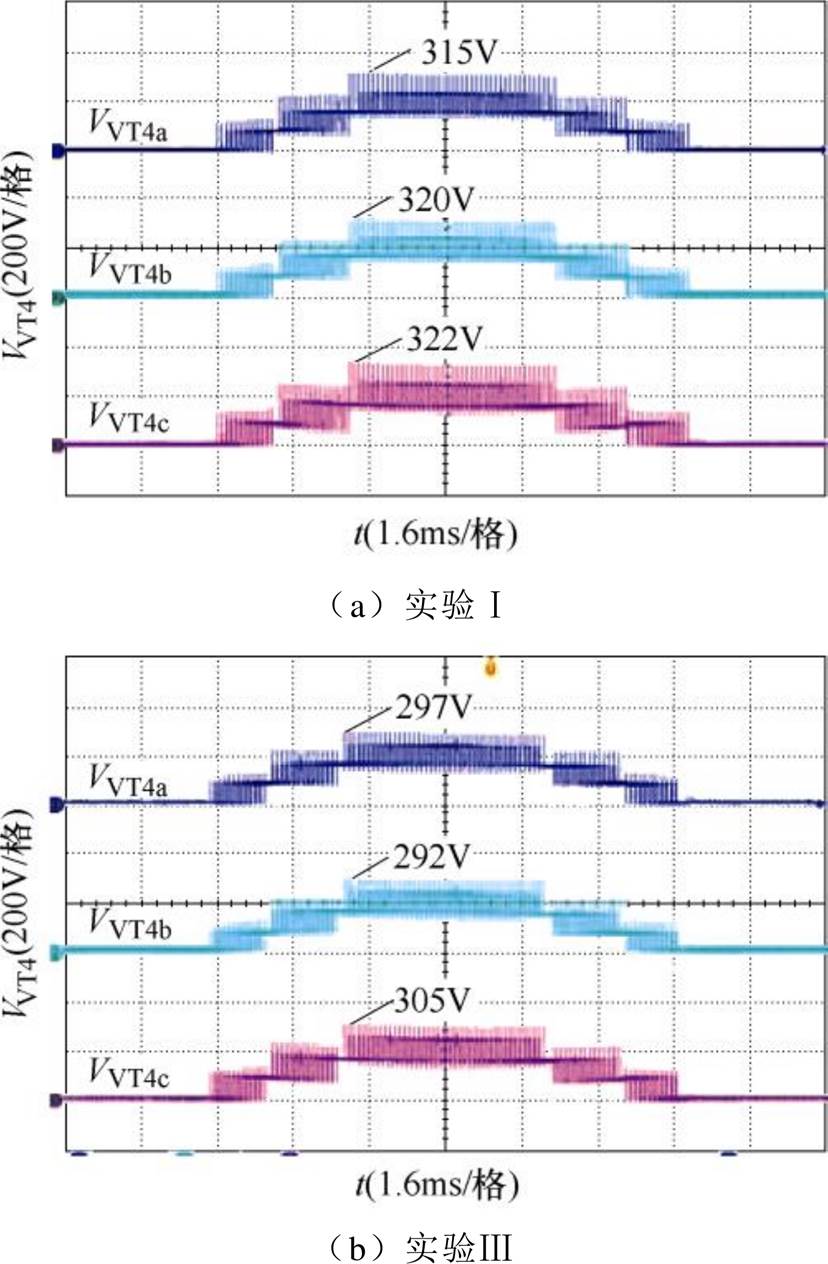

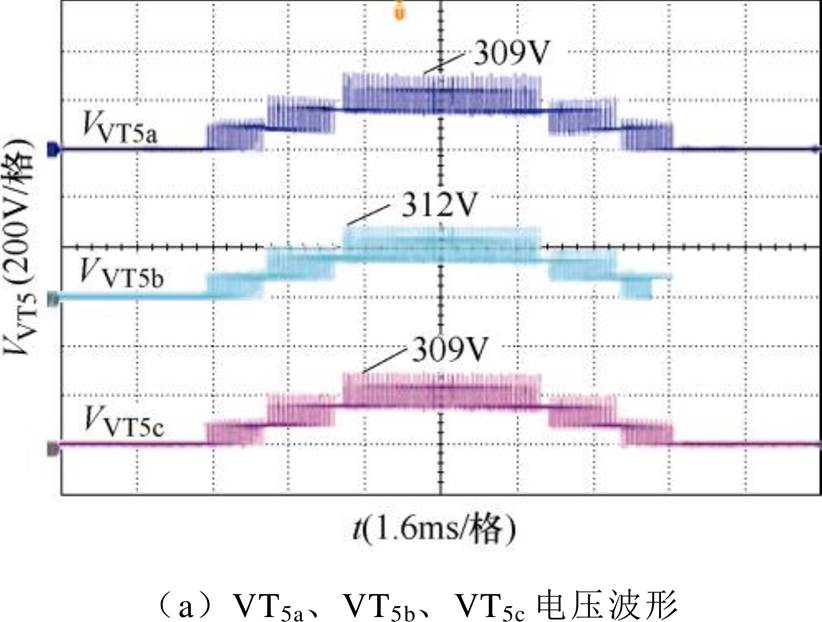

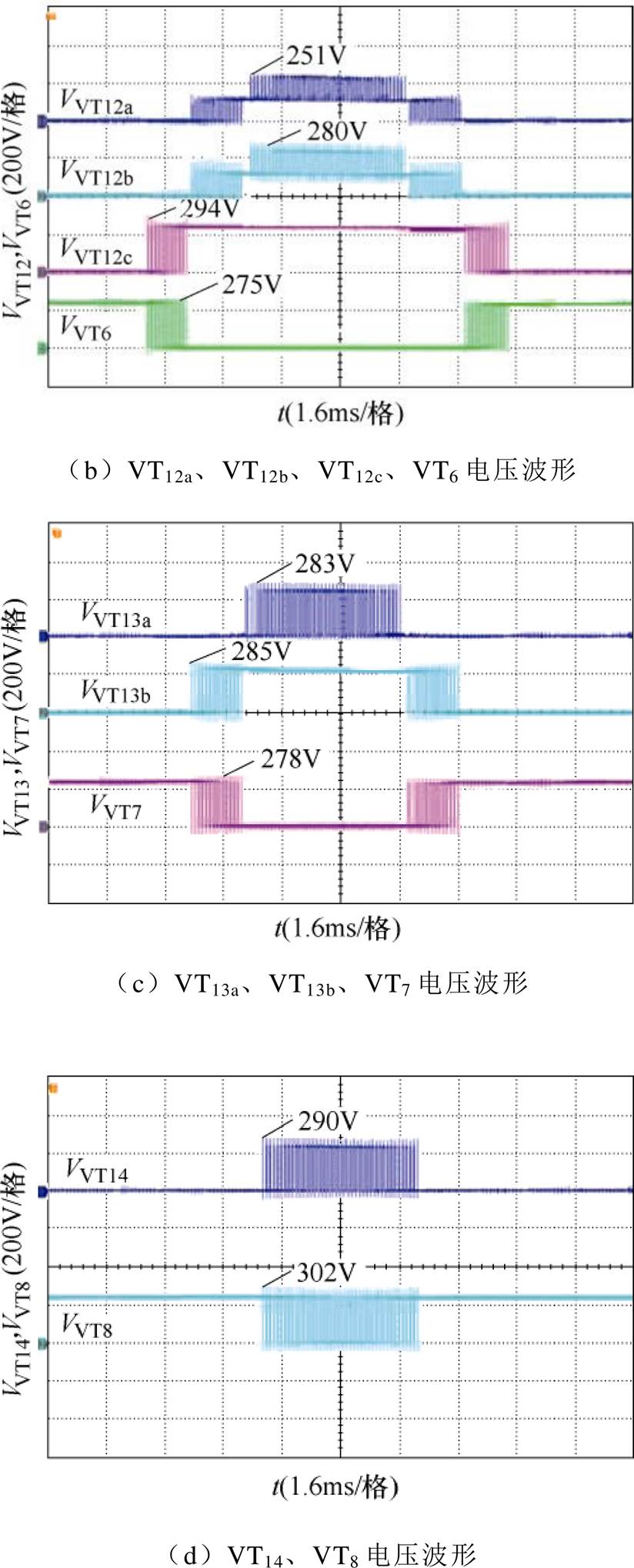

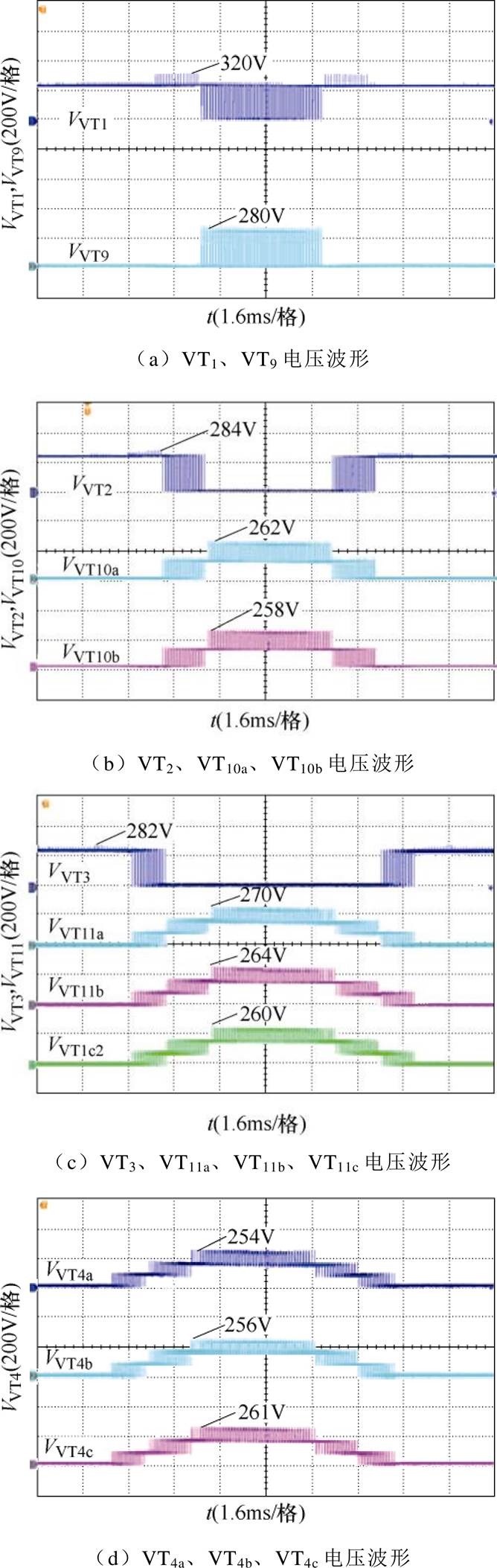

首先设计了三组实验进行对比分析。在实验Ⅰ中,不添加吸收电路,设定钳位支路的开关器件同时动作,实验Ⅰ作为基础对比组;实验Ⅱ中不添加吸收电路,设定钳位支路中的串联开关器件不同时动作,目的在于分析串联开关器件的动作无法保持完全一致时的情况;实验Ⅲ中采用本文所提出的吸收电路方案,所添加的吸收电容值为3mF。需要说明,实际应用中可以依据VMC中不同换流回路的参数对吸收电容进行差异化设计,从而进一步减小吸收电路的整体成本和体积。图12~图16分别展示了七电平VMC各开关器件的电压波形,并标出了开关器件两端的最大电压峰值。

图12为VT1、VT9两端的电压波形。由于+3E与+2E电平换流回路中不存在串联开关器件,因此没有给出实验Ⅱ的波形。由图12a可以看出,当不添加吸收电路时,VT1的关断电压峰值约为337V,超过额定值40%。而VT1的最大电压尖峰出现在+2E与+E电平切换的阶段中,为362V,超过额定值51%。这是由于+2E与+E电平换流回路中杂散电感的感应电压峰值较大,对VT1的电压产生了明显的干扰影响。VT9的最大电压尖峰约为450V,出现在其关断过程中。由于VT9反并联二管的反向恢复效应,其关断电压峰值较大,超过额定值约88%。如图12b所示,加入吸收电容支路后,VT1与VT9的最大电压峰值分别降低为282V与284V,超过额定值仅约18%。并且,吸收电容支路有效抑制了其他变换单元动作的影响。

图11 PD-PWM波形及主开关器件调制信号

Fig.11 Waveforms of PD-PWM and modualtion signals of main switches

图12 VT1与VT9电压波形

Fig.12 Voltage waveforms of VT1 and VT9

图13为VT2、VT10a、VT10b两端的电压波形。在图13a所示的实验Ⅰ中,串联开关器件VT10a与VT10b基本平均分担了串联支路两端的总电压,其最大电压尖峰分别为340V(超额定值约42%)与325V(超额定值约35%)。而在图13b中,由于VT10a先于VT10b关断,导致其两端承受串联支路的整个电压尖峰,最大值达到432V,超额定值80%。这种串联开关器件动作不一致的现象可能会由信号通路长度、开关器件特性的差异造成,最终导致先关断的开关器件承受非常高的电压尖峰。在图13c中,采用了本文所提的吸收电路方案,在+2E与+E电平切换阶段中,VT2与VT10a互补导通,其最大电压尖峰为280V左右,超额定值约17%。而VT10b作为辅助开关管,在该换流过程中不承受电压,仅在输出电平为+3E时提供电压支撑的功能,其最大电压峰值为279V。可以看出,所提吸收电路方案的电压尖峰抑制效果明显,且无需解决串联器件的一致性问题。

图13 VT2、VT10a、VT10b电压波形

Fig.13 The voltage waveforms of VT2, VT10a, and VT10b

图14为VT3、VT11a、VT11b、VT11c两端的电压波形。在图14a中,即使设定串联开关器件的调制信号相同,但由于开关器件特性的差异,VT11a两端仍承受了较多的电压尖峰。VT11a的最大电压尖峰约为360V,超额定值约50%。图14b展示了串联开关器件的不一致性更为明显时的情况,此时VT11a先关断,其关断电压峰值达到了495V,超额定值达106%,极易造成开关器件的过电压损坏。在图14c所示的实验Ⅲ中,VT11a的关断电压尖峰降低为306V,超额定值约27%。此外VT3的电压尖峰也明显降低,吸收效果明显。

图14 VT3、VT11a、VT11b、VT11c电压波形

Fig.14 The voltage waveforms of VT3, VT11a, VT11b, and VT11c

图15展示了VT4a、VT4b、VT4c两端的电压波形。这三个开关器件在基频周期内仅动作一次,在关断过程中未出现明显的电压尖峰。其最大电压峰值是由变换单元Ⅶ的动作造成的,约为320V左右。当添加吸收电容后,VT4a、VT4b、VT4c受变换单元动作的影响减小,因此两端的电压尖峰也稍有下降,约为300V左右。

图15 VT4a、VT4b、VT4c电压波形

Fig.15 The voltage waveforms of VT4a, VT4b, and VT4c

七电平VMC下半桥臂的开关器件电压波形与上半桥臂的结果类似,因此这里不再具体分析,仅将其实验Ⅲ的电压波形统一展示在图16中。

图16 七电平VMC下半桥臂电压波形(实验Ⅲ)

Fig.16 The voltage waveforms of switches in seven-level VMC lower half-bridge (experiment Ⅲ)

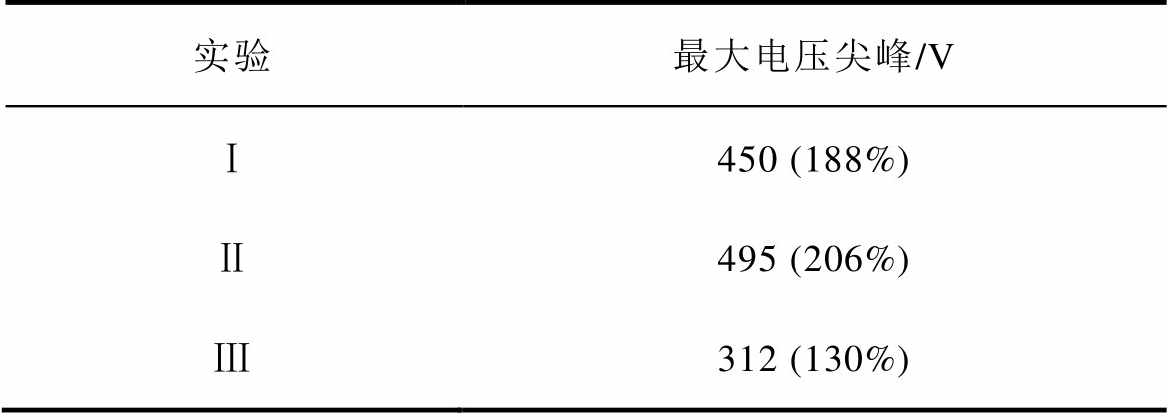

表2总结了实验Ⅰ、Ⅱ、Ⅲ中,七电平VMC各开关器件中出现的最大电压峰值及其与额定电压的比值。可以看出,在实验Ⅰ与实验Ⅱ中,开关器件的最大电压峰值接近、甚至超过额定值的两倍,对系统的安全运行带来了很大的压力。采用本文所提吸收电路方案(实验Ⅲ),将开关器件的最大电压峰值降低为额定值的1.3倍,因此可以通过设置合理的电压裕度,使系统工作在安全区域。

表2 七电平VMC开关器件最大电压峰值

Tab.2 The maximum voltage sipke of switches in seven-level VMC

实验最大电压尖峰/V Ⅰ450 (188%) Ⅱ495 (206%) Ⅲ312 (130%)

此外,图17给出了七电平VMC所有开关器件添加RC吸收电路(10W、22nF)的上半桥臂实验波形,以对比两种吸收电路的效果。可以看出,RC吸收电路能较好地抑制开关器件的关断过电压,但受到其他变换单元动作的干扰影响较大,其开关器件的最大电压尖峰约为320V,为额定值的133%。整体来看,本文所提吸收电路方案与RC吸收电路方案的吸收效果相近。但RC吸收电路为有损吸收电路,引入了额外的损耗;并且,其应用于VMC中所需的器件数量仍然较多,结构复杂。

综上可知,本文所提出的VMC吸收电路方案能够有效抑制开关器件的电压尖峰。并且,该方案所需的器件数量较少,无额外损耗,具备设计简单、可靠性高的优势。

图17 七电平VMC上半桥臂电压波形(RC吸收电路)

Fig.17 The voltage waveforms of switches in seven-level VMC upper half-bridge (with RC snubber circuit)

本文分析了VMC的开关器件关断过电压的问题,提出了一种简单有效的吸收电路方案。通过理论分析和实验结果得出如下的结论:

1)由于VMC换流回路中的杂散电感,存在开关器件关断过电压的问题。

2)采用改进的VMC调制方法,实现了对串联开关器件的功能区分。主开关器件负责实现输出电平的切换,而辅助开关器件提前导通、延迟关断,仅提供静态电压支撑的功能,避免了关断过电压的问题。改进的VMC调制方法减少了所需保护的开关器件数量,简化了吸收电路的设计难度。

3)通过在互补的主开关器件两端添加吸收电容支路,构成类似半桥开关能量缓冲单元的形式,有效抑制了主开关器件的关断过电压尖峰。

本文所提方案的吸收效果显著,所需器件较少,结构简单,便于向任意电平VMC中拓展,为VMC的实际应用提供了有效的支撑。

参考文献

[1] Kouro S, Malinowski M, Gopakumar K, et al. Recent advances and industrial applications of multilevel converters[J]. IEEE Transactions on Industrial Elec- tronics, 2010, 57(8): 2553-2580.

[2] Sathik J, Shalchi R, Sandeep N, et al. A new genera- lized multilevel converter topology based on cascaded connection of basic units[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2019, 7(4): 2498-2512.

[3] Mazuela M, Baraia I, Sanchez-Ruiz A, et al. DC-link voltage balancing strategy based on SVM and reactive power exchange for a 5L-MPC back-to-back converter for medium-voltage drives[J]. IEEE Transactions on Industrial Electronics, 2016, 63(12): 7864-7875.

[4] 李浩洋, 李泽, 郭源博, 等. 考虑开关管开路故障的三电平STATCOM建模与硬件在回路实时仿真[J]. 电工技术学报, 2019, 34(3): 552-561.

Li Haoyang, Li Ze, Guo Yuanbo, et al. Modeling and hardware-in-the-loop real-time simulation of three- level STATCOM considering switch open-circuit faults[J]. Transactions of China Electrotechnical Society, 2019, 34(3): 552-561.

[5] Bueno E J, CÓbreces S, RodrÍguez F J, et al. Design of a back-to-back NPC converter interface for wind turbines with squirrel-cage induction generator[J]. IEEE Transactions on Energy Conversion, 2008, 23(3): 932-945.

[6] 杨晓峰, 郑琼林, 薛尧, 等. 模块化多电平换流器的拓扑和工业应用综述[J]. 电网技术, 2016, 40(1): 1-10.

Yang Xiaofeng, Zheng Trillion Q, Xue Yao, et al. Review on topology and industry applications of modular multilevel converter[J]. Power System Tech- nology, 2016, 40(1): 1-10.

[7] 原露恬,王琛琛,薛尧, 等. 适用于中压领域的V形钳位多电平变换器[J]. 电工技术学报,2021,36(20): 4318-4328, 4338.

Yuan Lutian, Wang Chenchen, Xue Yao, et al. V-clamp multilevel converters suitable for medium- voltage fields[J]. Transactions of China Electro- technical Society, 2021, 36(20): 4318-4328, 4338.

[8] Xue Yao, Yang Xiaofeng, Yuan Lutian, et al. Oper- ation and control of a seven-level V-clamp multilevel converter[J]. Energies, 2019, 12(24): 4761.

[9] 易荣, 赵争鸣, 袁立强. 高压大容量变换器中母排的优化设计[J]. 电工技术学报, 2008, 23(8): 94- 100.

Yi Rong, Zhao Zhengming, Yuan Liqiang. Busbar optimization design for high power converters[J]. Transactions of China Electrotechnical Society, 2008, 23(8): 94-100.

[10] He Jiangbiao, Zhang Di, Pan Di. An improved PWM strategy for “SiC+Si” three-level active neutral point clamped converter in high-power high-frequency applications[C]//IEEE Energy Conversion Congress and Exposition (ECCE), Portland, USA, 2018: 5235- 5241.

[11] 孟庆云, 马伟明, 孙驰, 等. 考虑二极管非理想特性的中点钳位三电平电路的分析[J]. 电工技术学报, 2010, 25(6): 40-46, 54.

Meng Qingyun, Ma Weiming, Sun Chi, et al. The NPC three-level circuit considering nonideal characteri- stic of diode[J]. Transactions of China Electro- technical Society, 2010, 25(6): 40-46, 54.

[12] 刘博, 刘伟志, 董侃, 等. 基于全碳化硅功率组件的变流器母排杂散电感解析计算方法[J]. 电工技术学报, 2021, 36(10): 2105-2114.

Liu Bo, Liu Weizhi, Dong Kan, et al. Analytical calculation method for stray inductance of converter busbar based on full silicon carbide power module[J]. Transactions of China Electrotechnical Society, 2021, 36(10): 2105-2114.

[13] 赵正毅, 魏念荣, 赵良炳, 等. 一般缓冲电路的模型及三电平IGBT 变流器内外元件电压不平衡机理[J]. 中国电机工程学报, 2000, 20(6): 30-34.

Zhao Zhengyi, Wei Nianrong, Zhao Liangbing, et al. Modeling for general snubber circuits and the reason for voltage unbalance between the inner and outer devices in three level IGBT converters[J]. Pro- ceedings of the CSEE, 2000, 20(6): 30-34.

[14] 孟庆云, 晏明, 潘启军, 等. 一种适用于大容量中点钳位型三电平逆变器的绝缘栅双极型晶体管吸收电路研究[J]. 中国电机工程学报, 2016, 36(3): 755-764.

Meng Qingyun, Yan Ming, Pan Qijun, et al. Research on a insulated gate bipolar transistor snubber circuit for the high power neutral point clamped three-level inverter[J]. Proceedings of the CSEE, 2016, 36(3): 755-764.

[15] Kim I D, Nho E C, Joe C J, et al. A generalized undeland snubber for flying capacitor multilevel inverter and converter[J]. IEEE Transactions on Industrial Electronics, 2004, 51(6): 1290-1296.

[16] Tan Tianyuan, Jiang Ke, Jiang Qirong, et al. An improved McMurry snubber for three-level NPC IGBT converter[C]//International Power Engineering Conference, Singapore, 2007: 666-671.

[17] 吴洪洋, 邓焰, 何湘宁. 一种新颖的多电平逆变器无源无损吸收电路[J]. 中国电机工程学报, 2002, 22(10): 71-76.

Wu Hongyang, Deng Yan, He Xiangning. A novel passive lossless sunbber for multilevel inverters[J]. Proceedings of the CSEE, 2002, 22(10): 71-76.

[18] 牟雅洁. 基于RB-IGBT的T型三电平逆变器及其软开关技术研究[D]. 北京: 北京交通大学, 2018.

[19] 王海超, 范学鑫, 杨国润, 等. 三电平移相全桥变换器整流二极管RC吸收参数多目标优化设计[J]. 高电压技术, 2021, 47(1): 159-168.

Wang Haichao, Fan Xuexin, Yang Guorun, et al. Multi-objective optimization design of RC snubber of rectifier diodes for three-level phase-shifted full- bridge converter[J]. High Voltage Engineering, 2021, 47(1): 159-168.

[20] 袁义生, 钟青峰, 邱志卓, 等. 功率二极管反向恢复特性的建模[J]. 中国电机工程学报, 2018, 38(17): 5189-5198, 5316.

Yuan Yisheng, Zhong Qingfeng, Qiu Zhizhuo, et al. Modeling of reverse recovery characteristics of power diodes[J]. Proceedings of the CSEE, 2018, 38(17): 5189-5198, 5316.

Research on an IGBT Snubber Circuit for the V-clamp Multilevel Converter

Abstract V-clamp multilevel converter (VMC) with the energy buffer capacitor only in common DC bank is suitable for the medium-voltage and high-power applications. However, stray inductance in the current transition loop of VMC may result in the turn-off over-voltage of the IGBT. To address this problem, this paper proposes a simple and practical snubber for VMC. Based on the operation modes of VMC, the switches are classified into main switches and auxiliary switches. The main switch operates and switches the current path, and a snubber capacitor is added across each pair of complementary main switches (i.e. half-bridge switching buffer alike unit) to suppress the turn-off transient over-voltage. The auxiliary switch is turned on first and then turned off after the switching time of the corresponding main switch, and only provides the static blocking voltage and does not need dynamic over-voltage protection. A seven-level VMC is taken as an example to verify this strategy. The experimental results show that the proposed snubber circuit can effectively reduce the turn-off transient voltage of the IGBT in VMC, and only needs a small amount of snubber capacitors for main switches to form half-bridge switching buffer alike units. It has low cost, high reliability and good engineering practicability.

keywords:V-clamp multilevel converter, snubber circuit, over-voltage of IGBT, voltage spike

DOI: 10.19595/j.cnki.1000-6753.tces.211195

中图分类号:TM46

国家自然科学基金重点项目(51737001)和台达电力电子科教发展计划青年项目(DREG2021008)资助。

收稿日期 2021-08-04

改稿日期 2022-01-18

薛 尧 男,1991年生,博士研究生,研究方向为多电平变换器及其控制。E-mail: 16117392@bjtu.edu.cn

郑琼林 男,1964年生,教授,博士生导师,研究方向为铁道供电与电力牵引、电能变换与质量控制、高效电力变换器。E-mail: tqzheng@bjtu.edu.cn(通信作者)

(编辑 陈 诚)