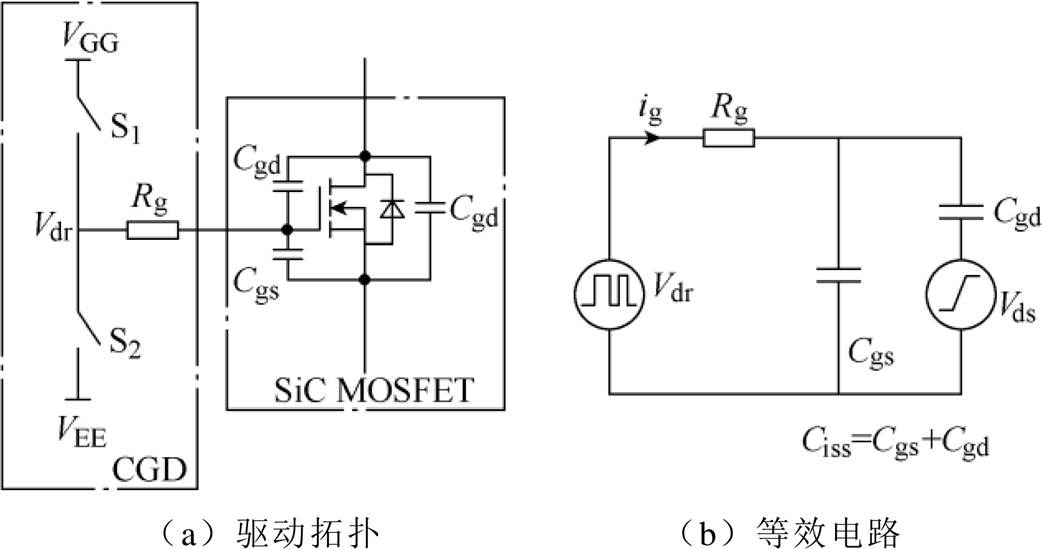

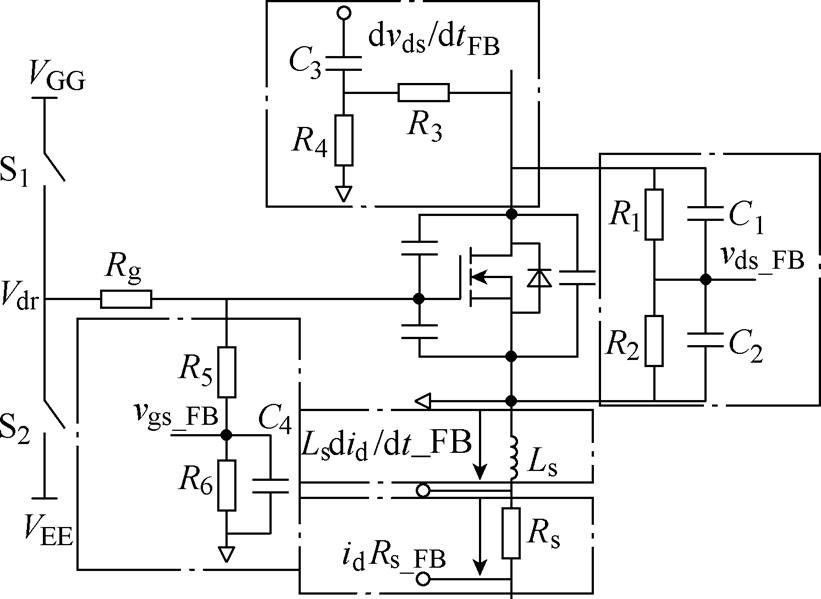

图1 CGD驱动拓扑及其等效电路

Fig.1 Topology of the CGD driver and equivalent circuit

摘要 随着SiC MOSFET的推广,其开关暂态过程中的超调、振荡以及电磁干扰问题越来越受到人们的重视。有源栅极驱动(AGD)电路作为一种新型驱动电路,已被广泛应用于SiC MOSFET开关轨迹的优化控制。首先,该文分析AGD电路的工作原理,给出不同驱动参数对开关特性的影响;其次,着重探讨阈值触发型AGD电路的工作模式,分别从暂态定位技术、逻辑处理架构和功率放大拓扑三方面对AGD电路进行归纳总结,并评价不同技术的优缺点,给出AGD电路设计的建议流程;最后,展望基于SiC MOSFET开关轨迹优化的AGD电路的发展趋势。

关键词:SiC MOSFET 有源栅极驱动 开关轨迹 振荡

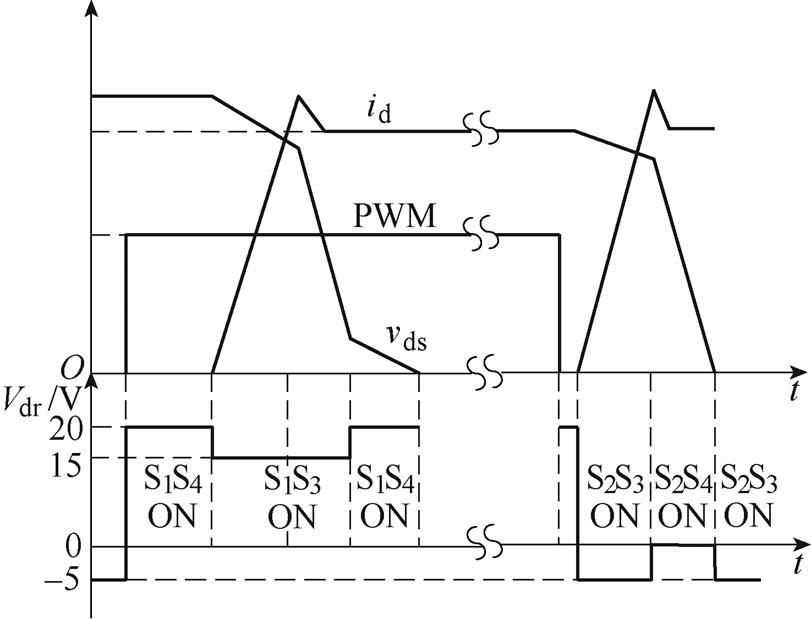

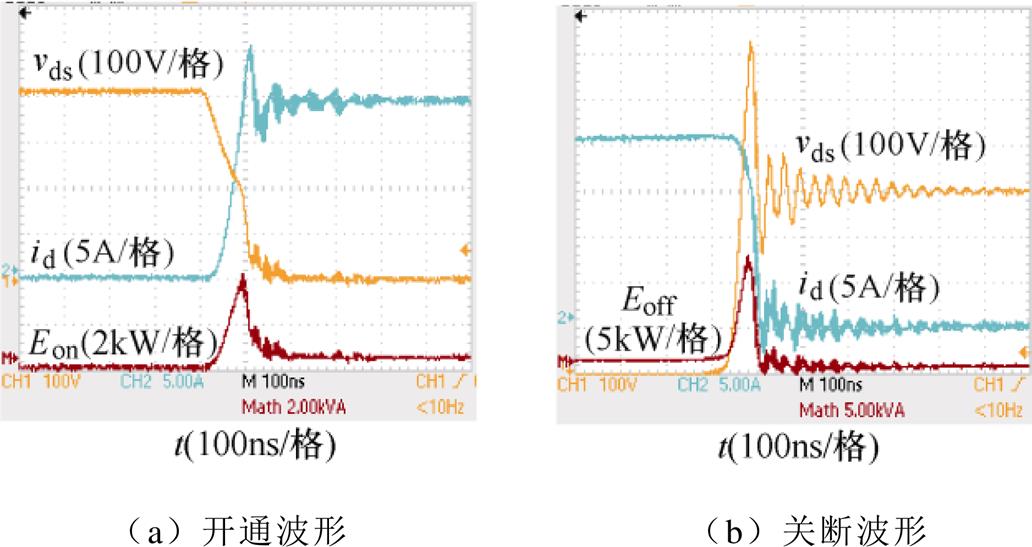

以碳化硅金属氧化物半导体场效应晶体管(Silicon Carbide Metal Oxide Semiconductor Field Effect Transistor, SiC MOSFET)为代表的宽禁带半导体器件的诞生和发展使电力电子技术迎来了新的发展,和传统的Si基器件相比,在静态特性方面,SiC MOSFET具有更低的导通电阻、更高的热导率以及能与IGBT媲美的功率等级;在动态特性方面,SiC MOSFET则具备更快的开关速度及频率上限,这有助于电力电子装置整体功率密度及效率的提升[1]。然而,开关瞬态过程的高dv/dt、di/dt以及与之相伴的超调振荡使得SiC MOSFET完全取代Si IGBT仍然受到一些限制。附录给出了ROHM公司推出的SiC MOSFET产品SCT2080KE在400V、20A工作条件下的双脉冲测试波形,实验结果体现出宽禁带器件高速开关暂态的局限性,具体表现为:

一方面,开关暂态有逾越安全工作区的风险。虽然SiC肖特基二极管消除了Si二极管的反向恢复效应,但是较大结电容使得开通过程仍存在较大的电流超调;SiC MOSFET的结电容更小,对于回路寄生电感更加敏感,特别是在器件关断时会产生较大的关断电压尖峰与持续振荡,极易突破器件的额定工作值,造成不可逆转的失效[2]。

另一方面,串扰问题值得注意。半桥电路中桥臂中点电位的瞬变通过结电容形成位移电流,与回路寄生电感与栅极驱动电阻相作用,形成电压尖峰。由于SiC器件具有更低的开通阈值,正向串扰增大了桥臂直通的风险;同时SiC可承受负关断电压绝对值更低,负向串扰会造成器件的损坏[3]。

SiC MOSFET对于开关损耗更加敏感。更快的开关速度使得SiC MOSFET电压、电流交叠区域更小,开关损耗更低,但在高频驱动的情况下,单次开通或者关断损耗的提升可能会显著降低系统效率,引发散热不良、器件失效等问题[4-5]。

电磁兼容问题是当下危害电力电子系统的重要问题之一[6-7]。电力电子装置中的半导体器件的高频、高速切换是电磁噪声的源头;而复杂的寄生参数网络为骚扰信号提供了路径。电磁干扰(Electro- magnetic Interference, EMI)不仅以泄露电流、轴电流的形式在功率回路形成安全隐患;同时对于控制侧模拟电路、数字电路形成较强的干扰,降低系统运行的可靠性。

优化PCB布局、降低回路寄生电感被证实是一种有效缓解上述问题的方式,但其非常依赖于设计人员的经验,同时为进一步降低寄生参数需要复杂的先进封装技术[8],成本昂贵。增设滤波器、吸收电路等手段都是以增加额外损耗、牺牲系统功率密度为代价的,并且往往需要进行反复的试错实验,大大降低了研发效率。

有源栅极驱动(Active Gate Driver, AGD)作为一种新型驱动电路,通过附加有源器件,调节驱动部件参数,以达到优化开关特性的目的。AGD技术最早被应用于IGBT驱动中,主要有损耗降低[9]、串扰抑制[10]、串联均压[11]、并联均流[12]、有源钳位[13]、短路保护[14]和暂态轨迹优化7个用途。SiC MOSFET相对于Si IGBT开关速度更快,所带来的超调、振荡、EMI问题更加显著,如何在不显著增加开关损耗的情况下,通过降低开关速度来优化开关轨迹,是本文AGD电路应用的目的。

本文根据现有文献,从工作原理、控制手段、电路拓扑等方面出发,归纳整理了针对SiC MOSFET轨迹优化的AGD电路相关技术,并在性能方面进行了对比,给出AGD建议的设计流程,最后讨论了未来AGD电路发展的趋势。

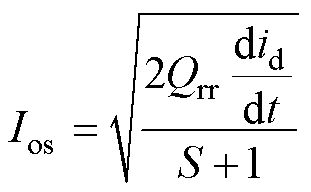

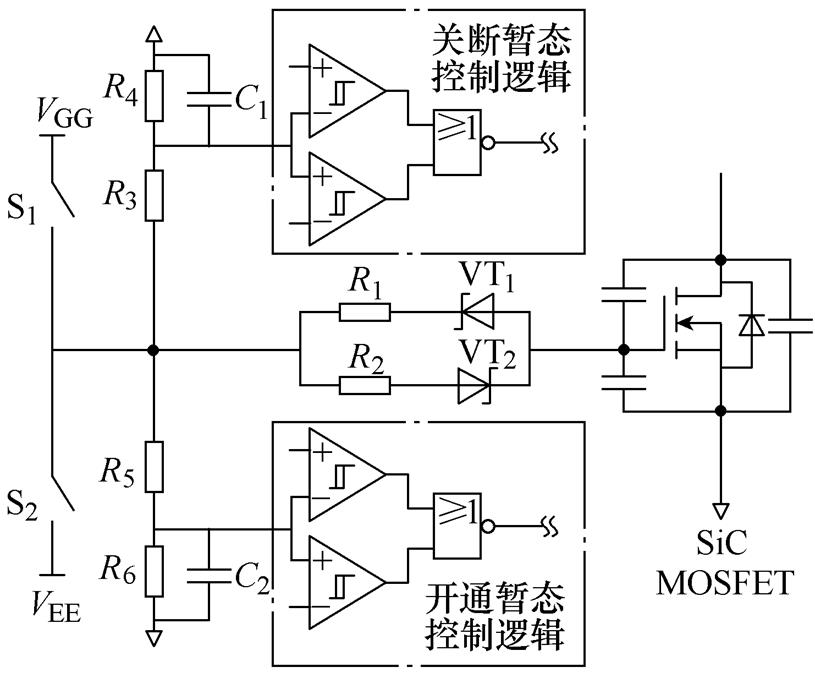

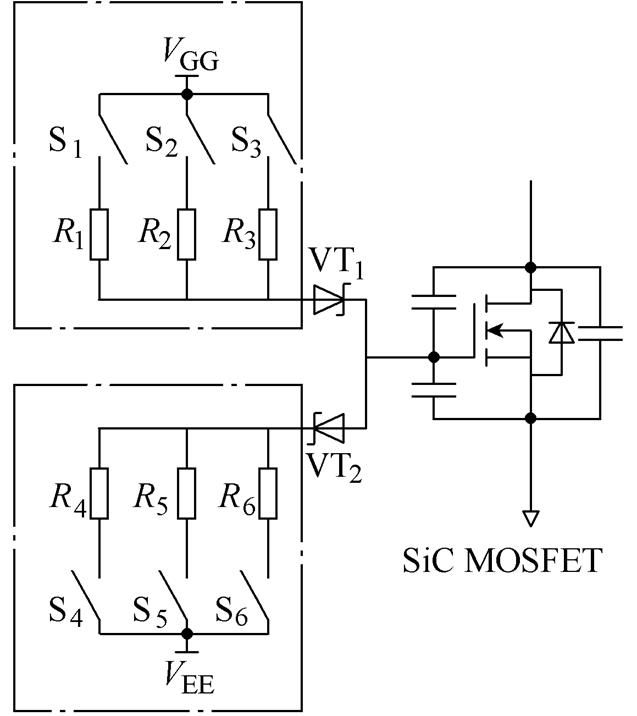

常规栅极驱动(Conventional Gate Driver, CGD)拓扑及其等效电路如图1所示,SiC MOSFET的开关暂态实际为对输入电容的充放电过程。图1中,VGG为正驱动电压,VEE为负驱动电压,S1和S2为驱动开关,Vdr为驱动输出电压,Rg为栅极驱动电阻,Cgs为栅源电容,Cgd为栅漏电容,Cds为漏源电容,Vds为漏源电压,Vgs为栅源电压,ig为栅极电流,id为漏极电流。SiC MOSFET的开关轨迹有7个基本的特征参量,分别为开关延时tdelay、漏源电压变化率dv/dt、漏极电流变化率di/dt、电流超调量Ios、电压超调量Vos、EMI水平及开关损耗Psw。

图1 CGD驱动拓扑及其等效电路

Fig.1 Topology of the CGD driver and equivalent circuit

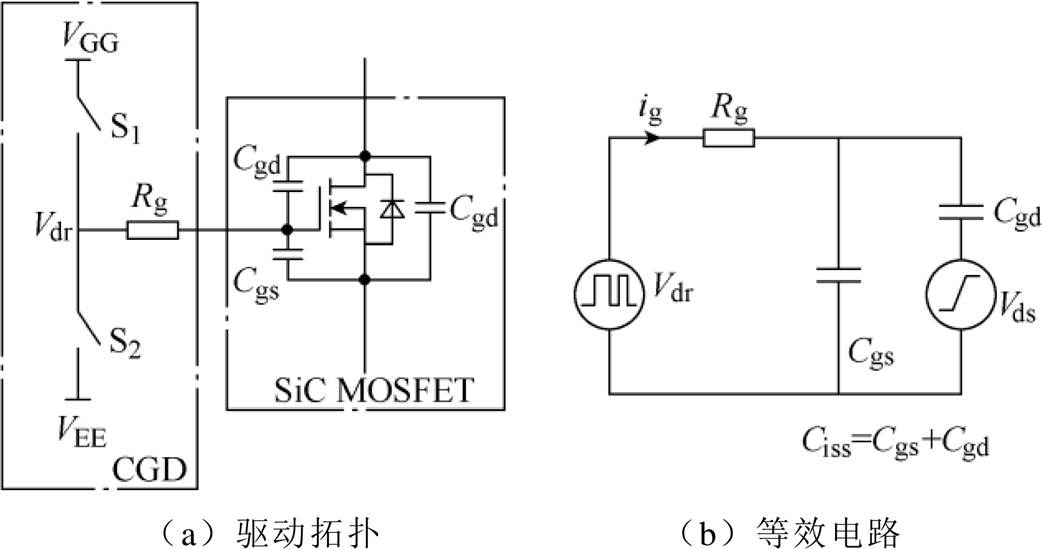

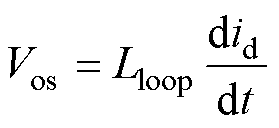

对于SiC MOSFET而言,开关过程中的高电流变化率did/dt是危害器件可靠工作的主要原因[15],具体表现为:在开通过程中,高速电流切换恶化了SiC MOSFET体二极管的反向恢复效应,额外的电流应力不仅增加了器件的开通损耗,并且电流尖峰也会以差模EMI的形式降低系统电磁兼容特性。SiC MOSFET的开通电流超调量Ios可表示为

(1)

(1)

式中,Qrr为SiC MOSFET体二极管的反向恢复电荷;S为反向恢复软度。

在关断过程中,由于回路寄生电感Lloop无法静态储能,高电流变化率会与之作用产生较高的尖峰电压。电压超调量不仅增大了器件的关断损耗,同时也增加了器件击穿的可能,并且系统的共模EMI特性也随之恶化。SiC MOSFET电压超调量表示为

(2)

(2)

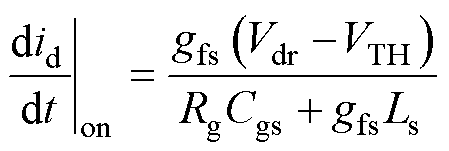

调节CGD电路中驱动电压Vdr、驱动电阻Rg、栅源电容Cgs等栅极部件的数值可以实现对于漏极电流变化率的调控,SiC MOSFET的电流变化率可近似为

(3)

(3)

(4)

(4)

式中,gfs为SiC MOSFET的电导;VTH为开通阈值电压;Vmil为米勒平台电压;Ls为器件源极电感。

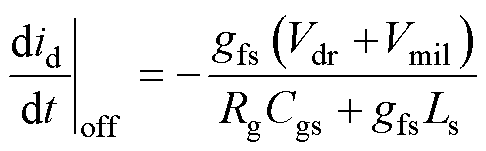

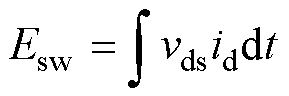

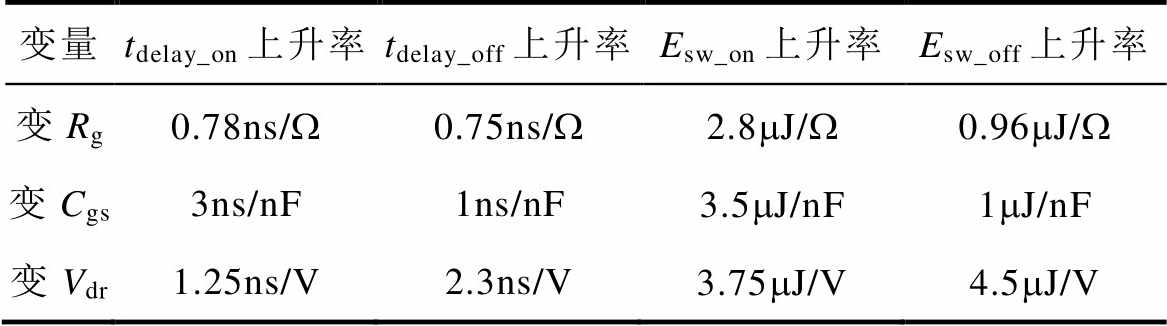

由式(3)和式(4)可以看出,增大Rg、Cgs以及降低Vdr可以有效降低did/dt的数值,进而实现电流、电压超调的抑制。根据文献[16]的实验结果,栅极部件参数对于SiC MOSFET开通电流超调抑制和关断电压超调抑制效果见表1[16]。在单位步长变化条件下,变Vdr对于电气超调量的抑制效果更为明显。

表1 不同栅极参数对于电气超调的抑制

Tab.1 The suppression in electrical overshoots of different gate parameters

变 量衰减率 IosVos 变Rg (0~50W)0.14A/W0.6V/W 变Cgs (0~20nF)0.45A/nF1.1V/nF 变Vdr (VGG=14~22V, VEE=-10~0V)1.07A/V2.4V/V

然而,人为地在设计初期调整驱动部件参数,降低SiC MOSFET开关速度虽然可以降低超调、振荡和EMI等开关暂态负面效应,但随之带来的开关延时上升和开关损耗增加却不能忽视。

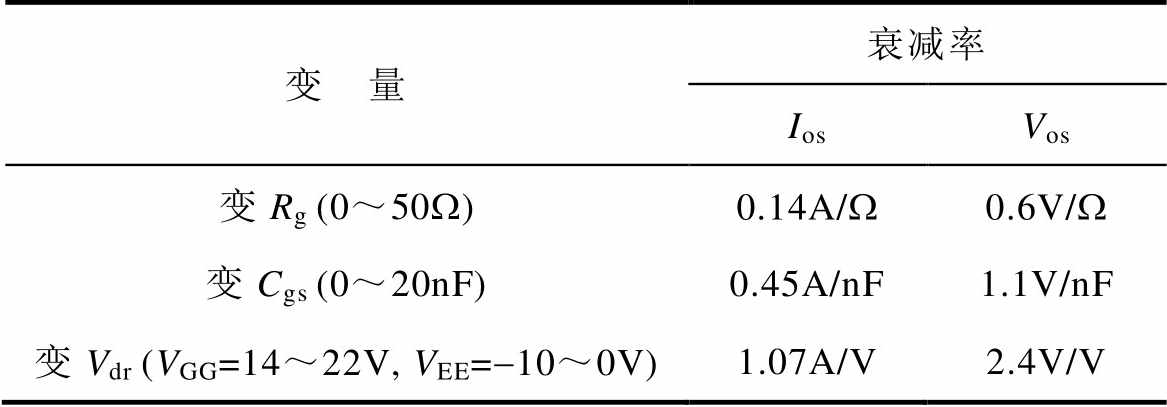

过长的开关延时一方面会增加环路的响应时延;另一方面SiC MOSFET的开关速度直接关乎死区时间的设定,一味调节栅极驱动参数都是以牺牲变换器控制性能为代价的。同时,SiC MOSFET的开关损耗被定义为漏极电流id和漏源电压vds的交叠面积,降低器件开关速度是以牺牲开关损耗、降低系统效率以及增加散热负担为代价的。SiC MOSFET的开关损耗表达式可表示为

(5)

(5)

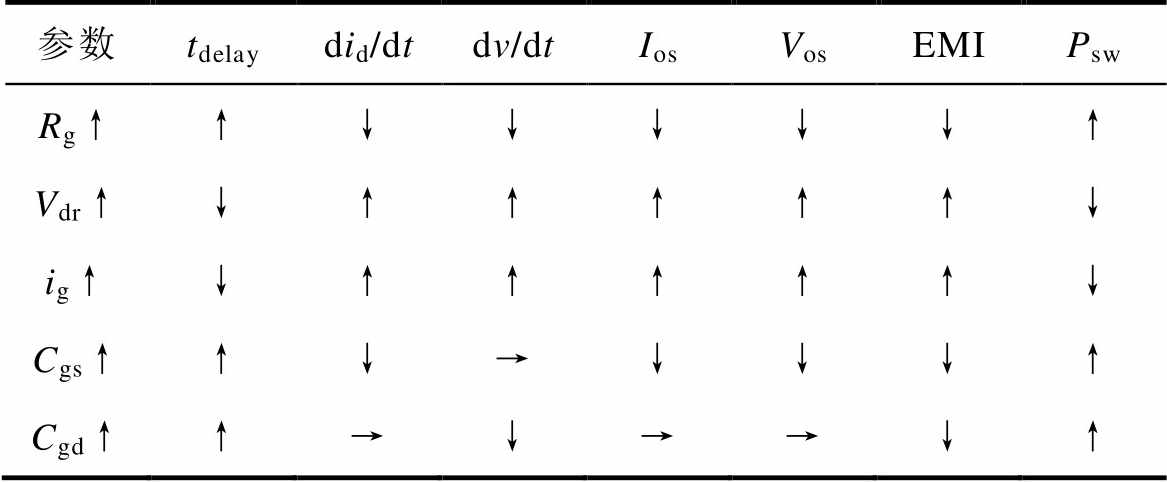

不同栅极参数对于延时和损耗的影响见表2。表2给出了和表1相同参数变化范围内,文献[16]结果中,调节栅极部件对于开关延时以及开关损耗的影响。显然,CGD中一旦设定好了栅极驱动部件参数值,那么SiC MOSFET开关轨迹就基本固定,CGD电路灵活性的缺乏导致了其很难兼顾开关损耗和超调抑制效果。表3给出了不同栅极参数对于开关特性的影响趋势。

表2 不同栅极参数对于延时和损耗的影响

Tab.2 The influence of different gate parameters on delay time and switching losses

变量tdelay_on上升率tdelay_off上升率Esw_on上升率Esw_off上升率 变Rg0.78ns/W0.75ns/W2.8mJ/W0.96mJ/W 变Cgs3ns/nF1ns/nF3.5mJ/nF1mJ/nF 变Vdr1.25ns/V2.3ns/V3.75mJ/V4.5mJ/V

表3 不同栅极参数对于开关特性的影响

Tab.3 The influence of different gate parameters on switching characteristics

参数tdelaydid/dtdv/dtIosVosEMIPsw Rg↑↑↓↓↓↓↓↑ Vdr↑↓↑↑↑↑↑↓ ig↑↓↑↑↑↑↑↓ Cgs↑↑↓→↓↓↓↑ Cgd↑↑→↓→→↓↑

注:“↑”表示增加;“→”表示基本不变;“↓”表示下降。

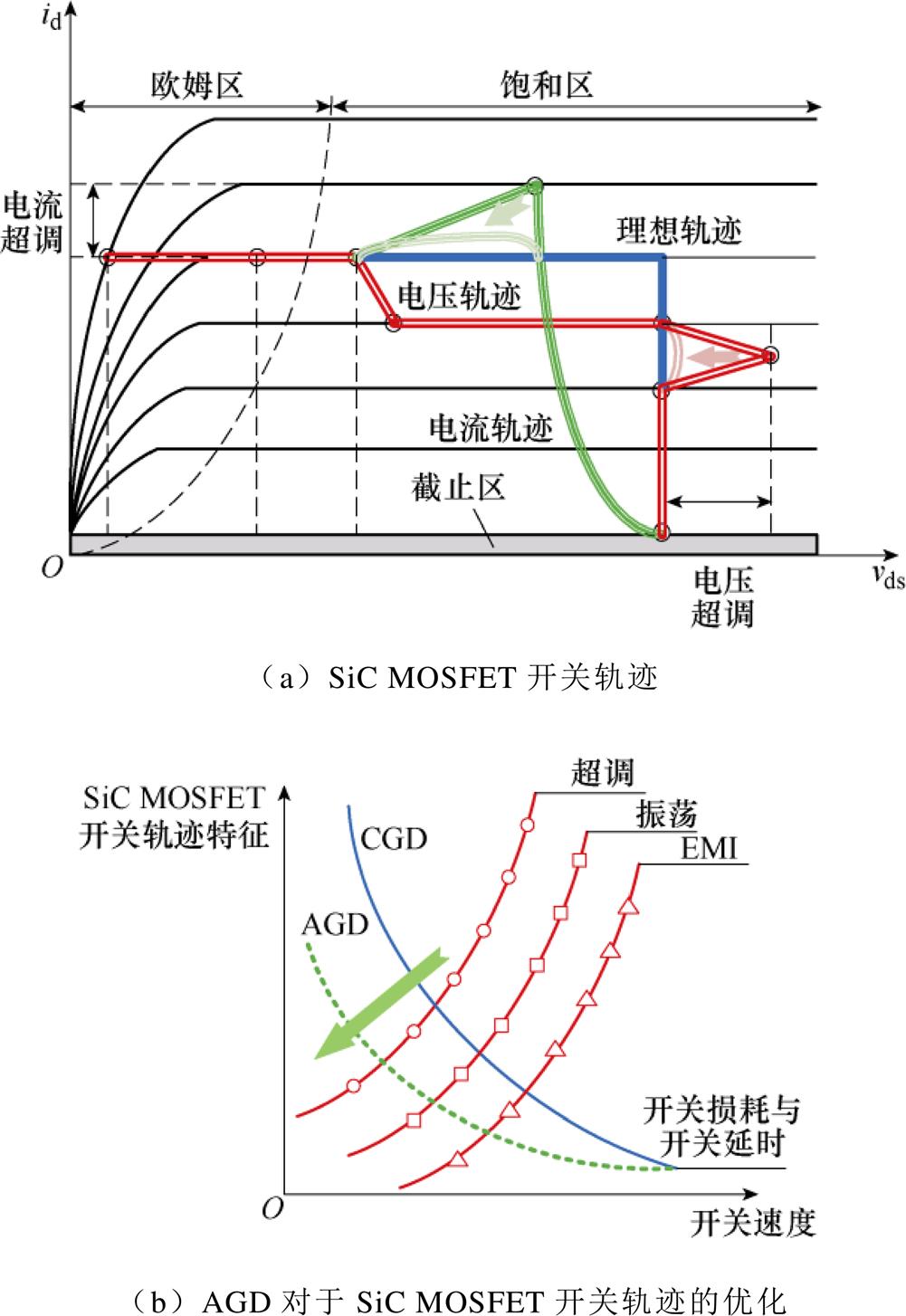

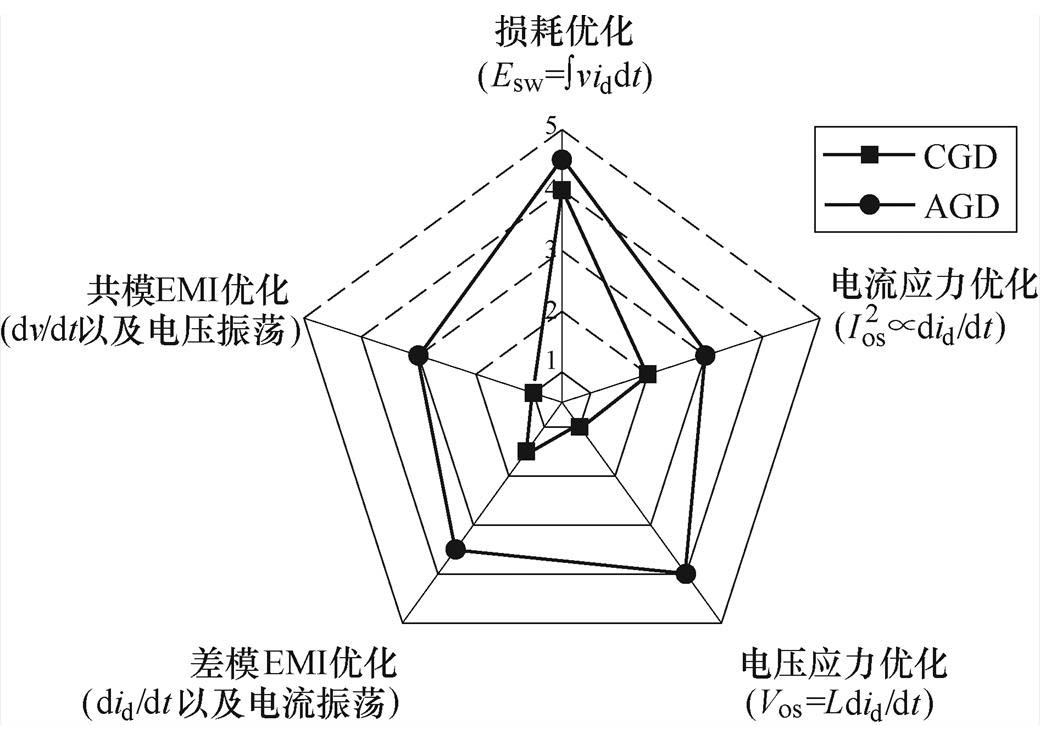

针对以上问题,AGD可以通过其特有的暂态定位功能,有针对性地调整某一暂态瞬间的某一栅极部件,只降低该阶段的开关速度,进而在不明显增加开关延时和总开关损耗的情况下,将开关瞬态的负面效应降到容许的程度。相对于传统CGD电路,AGD可以更有选择性地调节SiC MOSFET的开关轨迹,灵活度更高。SiC MOSFET开关轨迹的优化如图2所示。

基于IGBT的AGD电路分为开环型、全闭环型和阈值触发型三种控制模式。开环型[17-18]不存在反馈通路,直接在驱动电路前向通道上切换驱动参数,控制简单、响应快,缺点是受限于器件模型的精确性,不能适应电力电子装置工作点以及工作环境的变化。全闭环型[19]指实时采样功率器件的电压、电流信息,通常使用高带宽模拟PI调节器对器件的动态轨迹进行全闭环调节,该方法对于器件的控制自由度最高,但是受限于响应速度与成本。阈值触发型,又称“离散时间反馈型[20]”,是一种介于前两者之间的控制方式。通过采样反馈,当器件电压、电流等电气量超过某一阈值时,则会触发响应,通过逻辑判断,给出切换驱动部件参数的指令,以达到优化开关轨迹的目的。IGBT开关速度为ms级,而SiC MOSFET为ns级,全闭环调节方式很难追踪其暂态开关轨迹。目前,阈值触发型AGD是应用最广的SiC MOSFET有源栅极驱动电路,被广泛用于抑制SiC MOSFET开关瞬态的超调、振荡及EMI问题。

图2 SiC MOSFET开关轨迹的优化

Fig.2 Optimization of SiC MOSFET switching trajectory

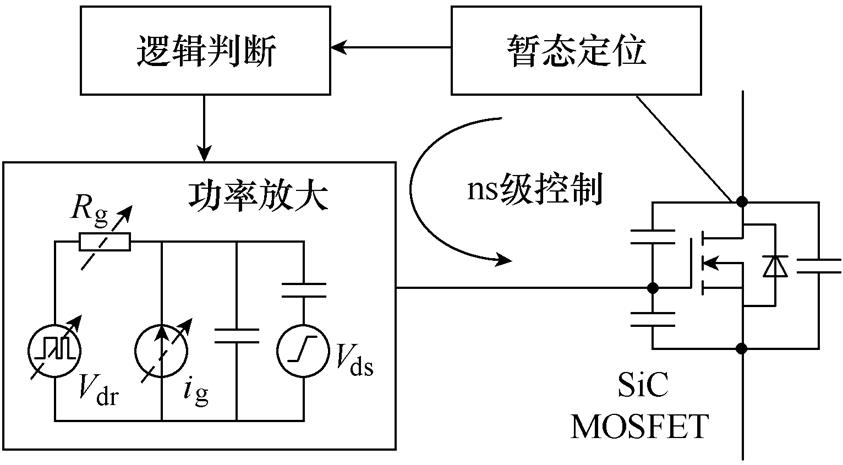

阈值触发型AGD电路结构如图3所示,暂态定位、逻辑判断、功率放大为基于开关轨迹优化的SiC MOSFET有源驱动所必须的三个基本模块电路。三个模块电路的组成形式与实现功能有所差异,在数十ns级的尺度下,共同完成了对于SiC MOSFET某一开关暂态的某一驱动部件参数的调节。从电路设计的角度出发,基于现有文献,本文分别对三个模块电路的设计思路与相关技术进行了对比与总结。

图3 阈值触发型AGD电路结构

Fig.3 Topology of the threshold-trigger AGD circuit

SiC MOSFET的开关瞬态主要分为开关延迟、电压变化、电流变化三个阶段。AGD电路可以实现对SiC MOSFET开关暂态瞬间较为精准的定位,这得益于附加的AGD检测电路,如图4所示。基本的检测电路需要满足如下几个要求:①高带宽;②具备一定的抗噪能力;③采样可以准确反映电气参数;④附加电路尽可能不影响开关特性;⑤易于设计逻辑接口。

图4 AGD检测电路

Fig.4 The detection circuit of AGD

2.1.1 基于模型时间估计的定位

根据SiC MOSFET开关暂态的动态行为模型,各阶段的持续时间都可以被近似估计。在逻辑控制电路中设计固定延时可以实现AGD作用时序的控制,本质上属于不准确的开环控制。SiC MOSFET的开关暂态时间会随着负载工况、寄生参数、驱动参数、器件选型的变化而变化,同时受温度影响较大[21]。由于该方法实现简易,不需要高速接口电路,常被用以时序微调以及作为AGD的控制变量。

2.1.2 基于栅极回路的定位

根据SiC MOSFET的跨导特性,在饱和区其可以近似等效为一个压控电流源,通过检测vgs可以得到id的状态信息。基于栅极回路的定位[22-23],不参与功率回路高压、大电流的瞬变切换,有利于接口电路的设计,同时在布局上更靠近弱电侧,避免了长反馈线拾取功率级噪声。该方法主要有以下3个缺陷:①容易受栅极回路振荡的影响而产生误判,加大滤波电容则降低了检测电路带宽;②不能很好地反映vds的信息;③采样电路一定程度上会影响开关速度。

2.1.3 基于功率回路的定位

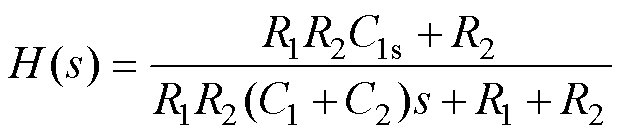

直接对SiC MOSFET的id、vds状态进行检测,可以最大程度地增加采样的精度与测量带宽。文献[24]通过二阶RC分压网络对vds进行采样,采样电路的传递函数可表示为

(6)

(6)

前馈电容C1可以加大反馈电压的摆率,提升采样带宽;积分电容C2对于反馈信号进行滤波降噪,通过选取C1与C2的数值可以达到响应速度与噪声的折中。文献[25]则通过一阶RC微分电路和I/V转换电路得到dvds/dt的信息。

对于漏极电流的检测是设计采样电路的难点。文献[22, 26-28]采用了分流电阻的检测方法,该方法实施简易,但分流电阻损耗较大,不适合大电流场合;同时必须选择低感值电阻以减小did/dt带来的采样误差。在这种应用中,昂贵的高共模抑制电流感应放大器增加了AGD的总体成本。开尔文连接的SiC MOSFET可以将Ls从驱动回路和功率回路中解耦,优化开关轨迹[29]。利用这一特殊结构,文献[24-25]通过检测Ls上的感应电压Lsdid/dt,有效地捕捉了电流变化阶段。这一方法不用外加无源器件,最大程度地利用了器件本身的寄生参数。

文献[26, 30-32]采用高带宽互感线圈对漏极电流进行实时采样,虽然测量精度较高,但这种方式价格昂贵且不易于集成。

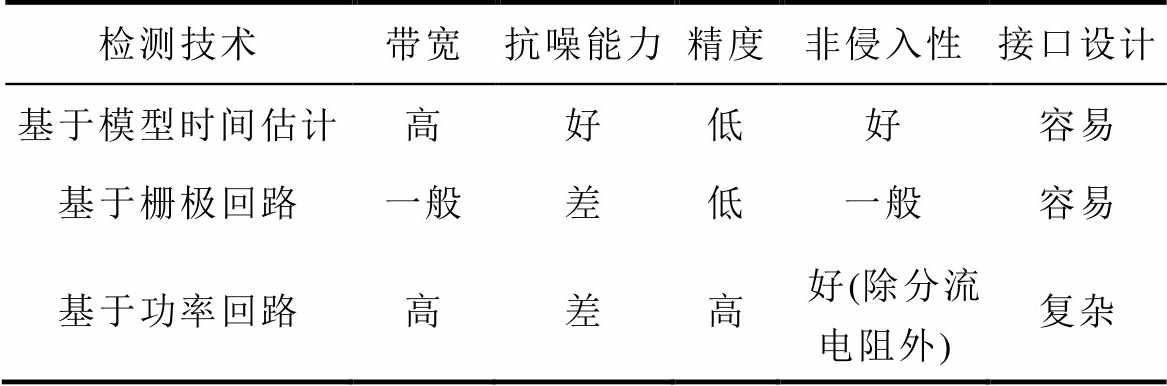

基于功率回路的检测定位技术,应对采样电路进行精细的滤波处理,同时无源器件需要有足够的耐压。三种检测技术的对比见表4。

表4 AGD检测技术对比

Tab.4 The comparison bewteen AGD detection technologies

检测技术带宽抗噪能力精度非侵入性接口设计 基于模型时间估计高好低好容易 基于栅极回路一般差低一般容易 基于功率回路高差高 好(除分流电阻外)复杂

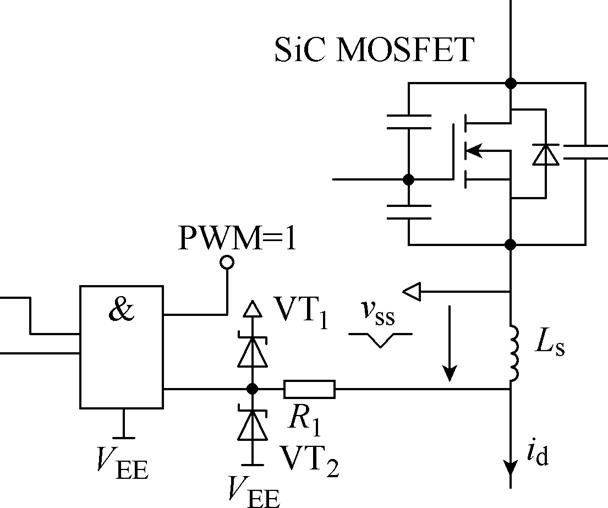

2.2.1 逻辑门翻转

以捕捉电流暂态的接口电路为例,逻辑门翻转电路如图5所示,文献[25]采取了逻辑门与功率回路直接连接的接口电路。电流上升阶段,Ls上的感应电压由0降为负值,一旦超过与门的阈值电平,就会促使电路翻转。在该设计中,逻辑门的正电源与SiC MOSFET源极相连,负电源则与负驱动电压相连。该接口电路结构简单,但将逻辑门等效为比较器使用,无法改变触发阈值,很容易受到干扰。

图5 逻辑门翻转电路

Fig.5 Logic gate flip-flop circuit

2.2.2 比较器触发

文献[24]通过使用高速比较器,完成了阈值可调的双向逻辑触发。比较器触发电路如图6所示,当id上升时,在Ls上感应出负电压将三极管VT1射极拉低,比较器1正输入端电位低于负输入端,输出翻转为0;当id下降时,在Ls上感应出正电压,当比较器2正输入端电位高于负输入端时,输出翻转为1。和采用逻辑门翻转的接口电路相比,比较器触发的方式主要有以下优点:可以灵活设置合理的参考阈值电压,有效规避误触发;构建迟滞型比较器电路可有效缓解电路的干扰振荡;部分比较器带输出锁存功能,为SiC MOSFET的状态监控提供了有用信息。

图6 比较器触发电路

Fig.6 Comparator trigger circuit

2.2.3 高速ADC采样

文献[26, 32]采用高速ADC直接读取来自高带宽电流互感器的数值。这种方法可以对SiC MOSFET的漏极电流进行实时监控,但处理速度不可避免地受限于模数转换电路的性能,同时模拟信号在SiC MOSFET驱动过程中容易受到干扰。

AGD暂态定位部分对于接口电路有如下要求:①完成1位或多位的数模转换,电平匹配;②保证强弱电接口的安全可靠;③低延时。以上三种接口电路的设计方法,从成本与结构复杂度的角度依次递增,从响应速度方面依次递减。目前,研究者使用较多的是比较器触发的方式。

在接收到暂态定位的触发信号后,AGD需要进行一定的逻辑处理。逻辑处理模块与PWM信号相结合,将逻辑分为开通暂态与关断暂态两部分,最终根据功率放大电路的设计,给出特定的减速触发信号。在实现方式方面,主要有采用离散逻辑门电路和采用可编程逻辑器件两种。

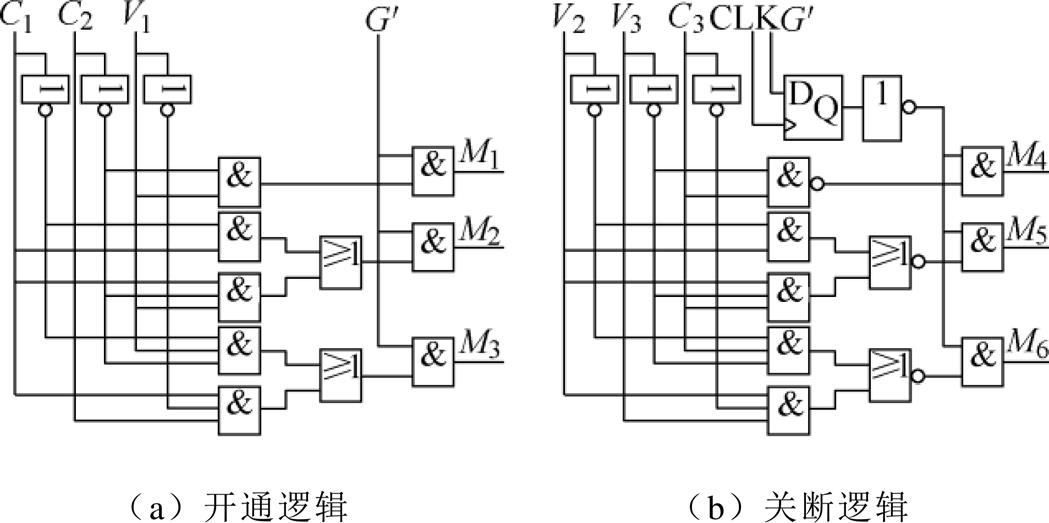

在对于开通与关断暂态独立控制的AGD电路中,采用离散逻辑器件在成本方面具有较大优势。离散器件构成的逻辑判断电路如图7所示,文献[23]仅使用两个比较器和一个或非门就完成了逻辑处理工作,并且开通与关断的逻辑电路完全一致。采用离散器件的逻辑处理方式对后期集成电路设计具有指导意义,但对于功率放大结构复杂的AGD电路,会导致器件堆积的问题,增加了设计难度以及系统功耗。每一个逻辑门芯片都至少具有数ns的延时,多级串联使用的情况下对于AGD处理速度的影响较大。

图7 离散器件构成的逻辑判断电路

Fig.7 Logic judgment circuit with discrete devices

采用可编程逻辑器件FPGA或CPLD是目前复杂逻辑处理的首选。文献[27]的开通与译码逻辑如图8所示,显然采用HDL语言可以大大简化设计的复杂度。由于可编程逻辑器件具有相对固定的延时,有利于多路逻辑的综合,拓展了AGD功率放大电路设计的自由度。但对于简单逻辑控制的AGD电路,采用可编程器件会造成资源的浪费,同时在成本方面也不具备优势。

图8 AGD电路动作逻辑

Fig.8 The action logic of AGD circuit

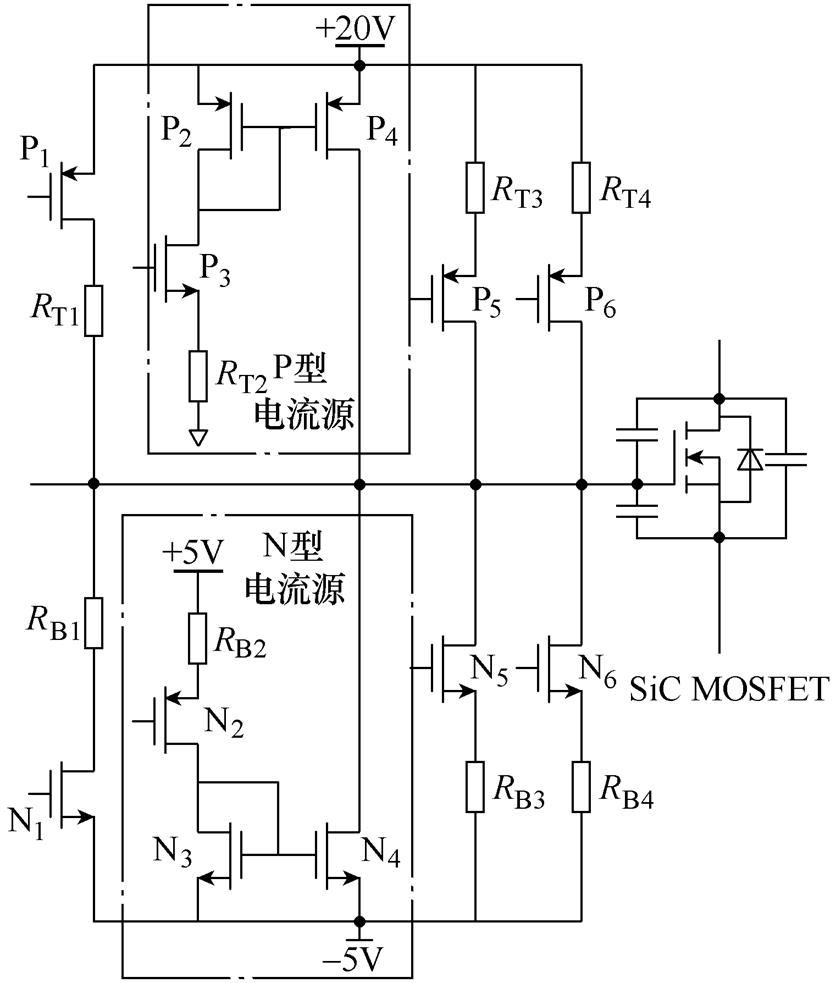

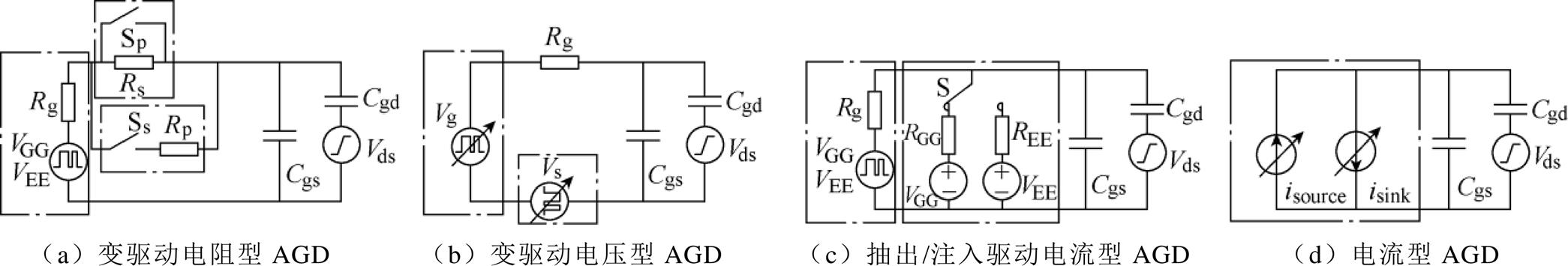

功率放大驱动部分是AGD电路的核心。通过该模块内部晶体管的动作,可以改变SiC MOSFET开关暂态阶段驱动电阻Rg、驱动电压Vdr、驱动电流ig的数值,以达到抑制超调、振荡、EMI的目的。根据改变的栅极物理量的不同,功率放大部分主要有变驱动电阻型、变驱动电压型、抽取/注入驱动电流型以及电流型等。调节Ciss也可对SiC MOSFET开关暂态的did/dt、dv/dt进行调节,但由于以下原因很少应用:①电容容差大,温漂严重;②对附加Cgd耐压要求较高;③SiC MOSFET输入电容非线性,模型不精确;④修改电容参数有增大串扰风险;⑤不易于集成。

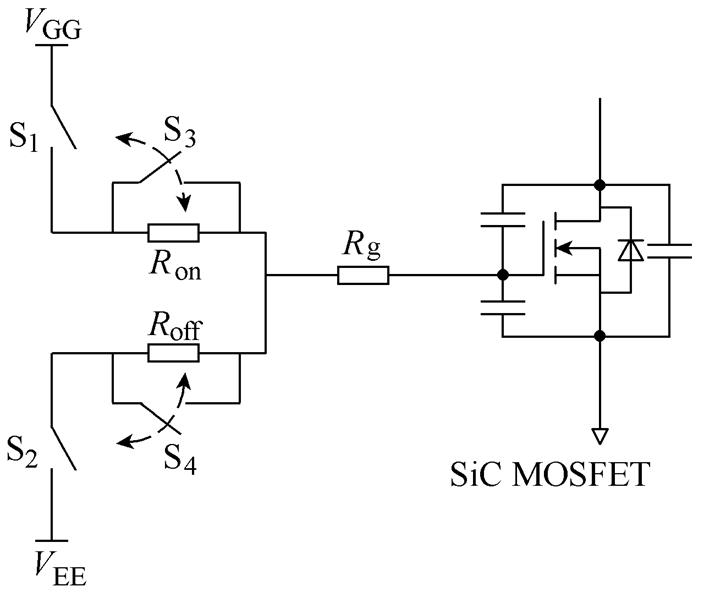

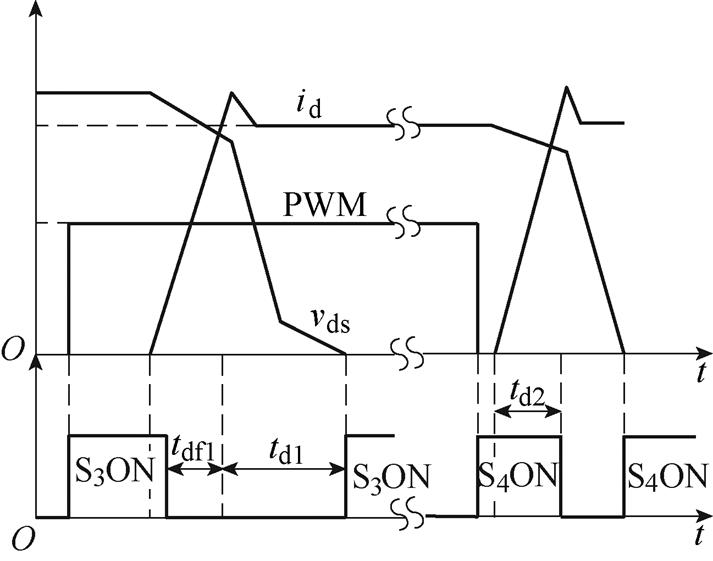

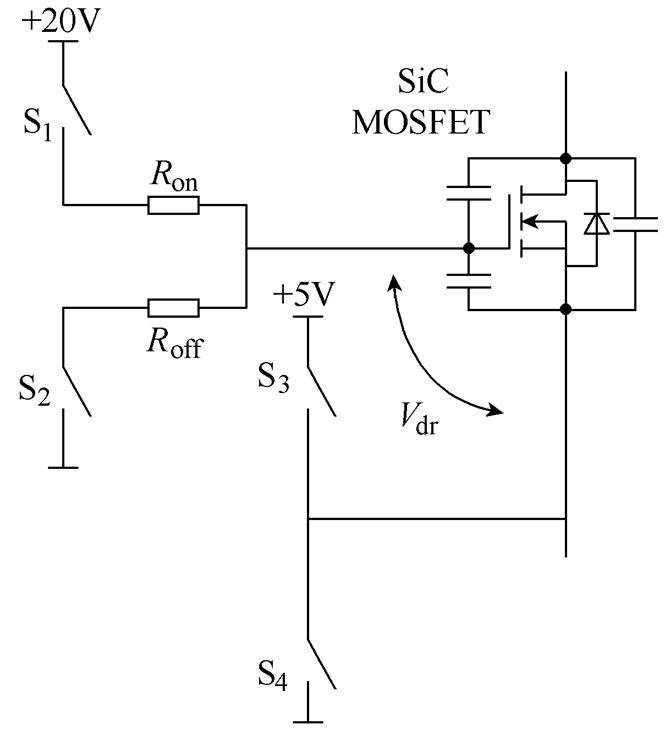

文献[33]将驱动电阻分为两部分,通过旁路其中一个电阻,而达到调节总驱动电阻的目的。文献[33]提出的串联电阻型AGD如图9所示,调节电阻Ron和Roff与原驱动电阻Rg为串联关系。S1和S2的断开,使得开关速度下降,继而电压、电流超调与did/dt,dv/dt下降,缓解了EMI。通过调节S3、S4断开的时间,从而达到开关速度与开关损耗的折中。图10为该电路的AGD控制时序[33]。

文献[27]将SiC MOSFET开通与关断暂态分为精确的八个阶段,通过多级并联电阻的方式,改变总的驱动电阻值,如图11所示。该设计在开通和关断某一暂态时,最多可以实现六种驱动电阻数值的选择,并且可以通过增加并联支路数达到更多组合方式。

图9 串联电阻型AGD

Fig.9 Series resistance type AGD

图10 AGD控制时序

Fig.10 Control sequence of the AGD

图11 并联电阻型AGD

Fig.11 Parallel resistance type AGD

通过调整驱动电阻串并联形式的AGD电路结构可重复性高、便于集成。但每个电阻几乎都需要一个与之对应的晶体管及驱动电路,增加了器件的数量与控制复杂度,切换速度以及稳定性也值得关注。同时,想达到更高分辨率的驱动电阻调节,必须增加串并联支路的数量,使得系统更加复杂。

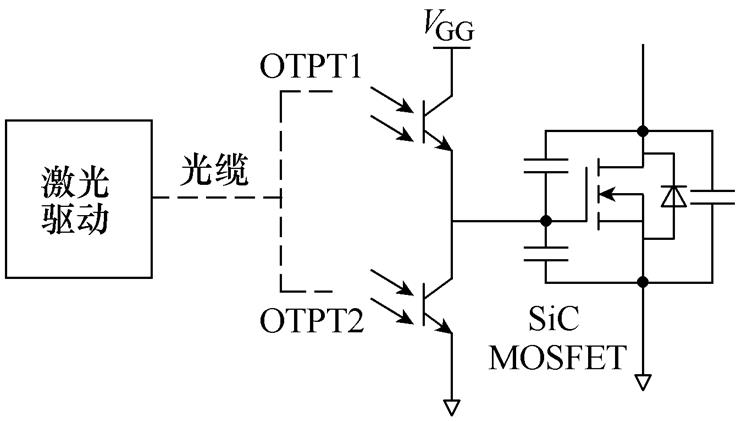

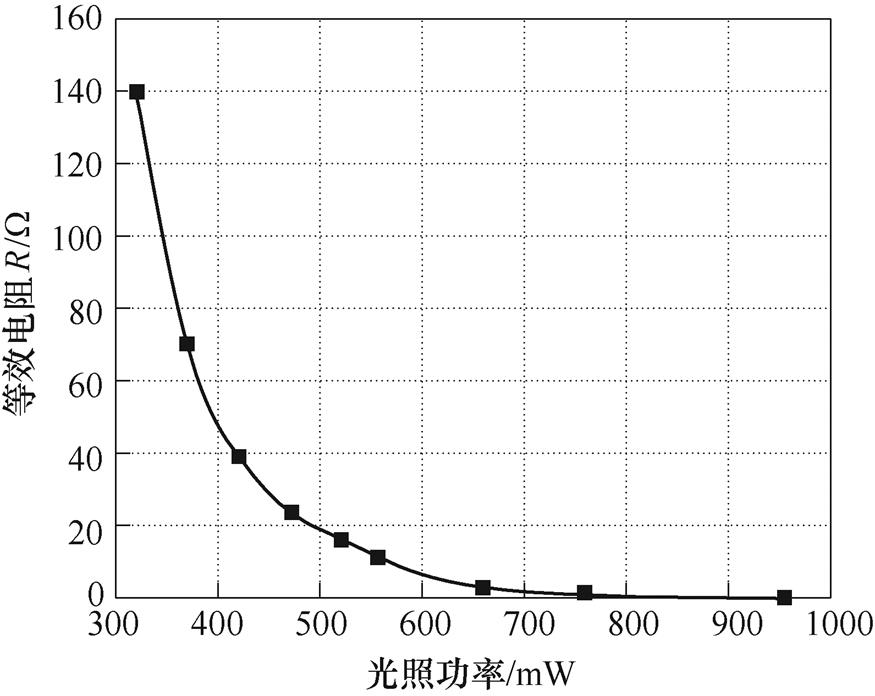

为达到Rg的无级调节,砷化镓光触发功率晶体管(GaAs-based Optically Triggered Power Transistor, GaAs-OTPT)被应用于AGD电路中[34],光控电阻型AGD如图12所示。OTPT的等效电阻随照射其表面的光照功率的上升而减低,通过可调激光源,能够实现驱动电阻的无级调节,OTPT器件的光学特性如图13所示[34]。虽然该结构同样能有效调节SiC MOSFET的开关暂态,但OTPT等效电阻的非线性、系统调节速度以及附加电路成本使得该方法的推广仍存在着一些挑战。

图12 光控电阻型AGD

Fig.12 Optocal controlled resistance type AGD

图13 OTPT器件的光学特性

Fig.13 Optical characteristics of the OTPT device

降低驱动电压可以减缓对于Ciss的充电速度。文献[24]将传统的两电平驱动,拓展为四电平驱动,如图14所示,通过增设一对推挽管,在开关瞬态向漏极投切一个辅助电平,在不破坏原有驱动结构的情况下,有效降低了驱动电压的绝对值。图15给出了等效栅极驱动电压Vdr的变化情况[24]。该结构通过调节投切时间来达到开关速度与开关损耗的折中,但无法调节单个驱动电平。

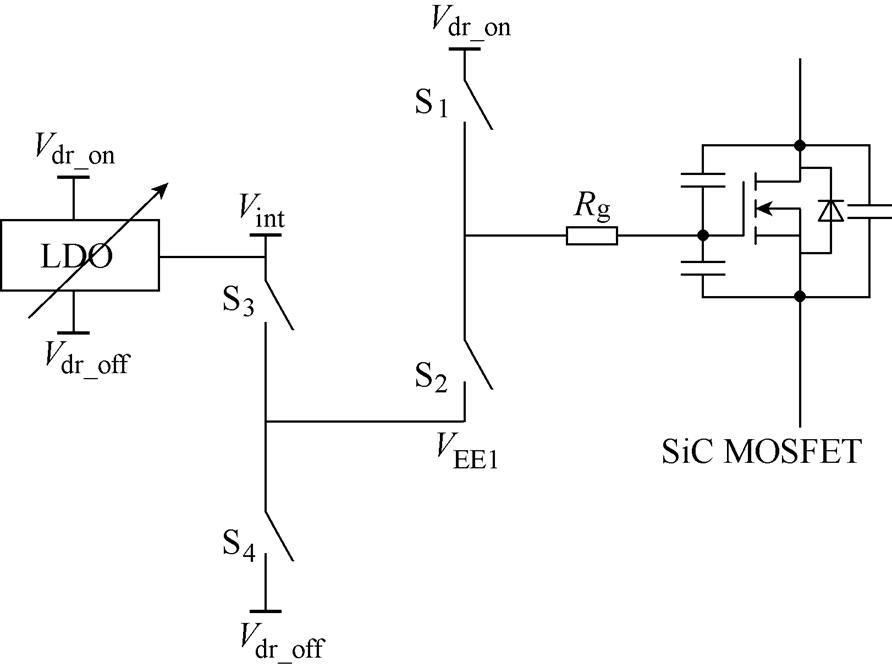

为提升驱动电压的调节自由度,可调线性稳压器(Low Dropout Regulator, LDO)被应用于文献[30]中。带LDO型三电平驱动AGD如图16所示[30],该设计为三电平驱动,两推挽电路呈垂直级联结构,增加级联阶数可以输出更多的驱动电平。输出电压可调的LDO使得Vint不再固定,用户可以根据使用场合灵活设定,但无法在线实时调节。

图14 四电平驱动AGD

Fig.14 Four-level AGD

图15 四电平驱动AGD的控制时序

Fig.15 Control sequence of the four-level AGD

图16 带LDO型三电平驱动AGD

Fig.16 Three-level AGD with LDO

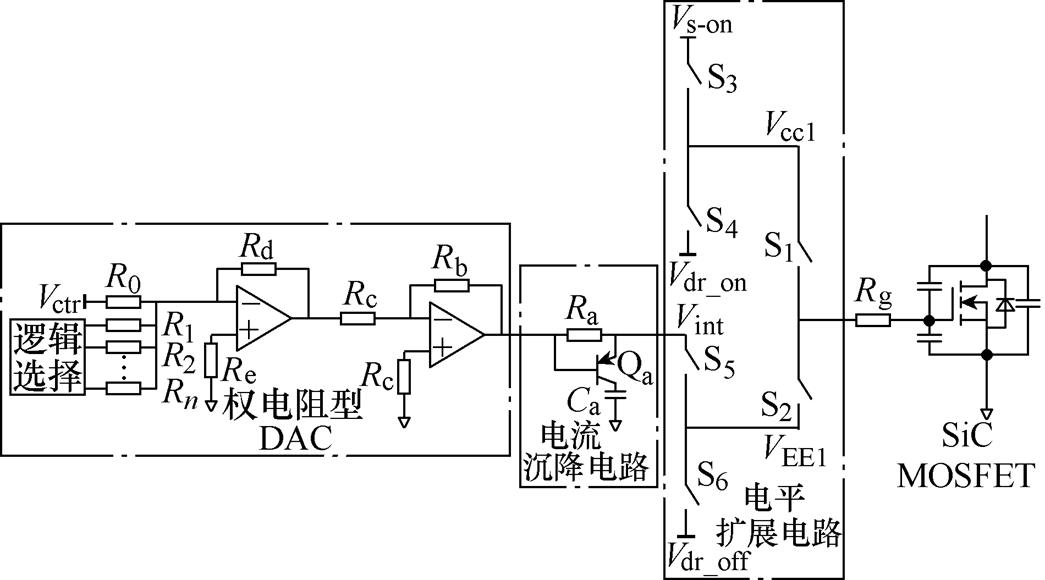

文献[31]将驱动电平数提升为4个,带DAC型四电平驱动AGD如图17所示。为进一步提高驱动电压在线调节的自由度,该设计搭建了权电阻型DAC。在使用n个增益电阻的情况下,可以输出2n级驱动电压;在n足够大时,近似可达成驱动电压的无级调节。附加的电流沉降电路提升了驱动电压的下拉能力,可以有效降低误触发风险。此设计中,高速DAC与高带宽功放等设计增加了成本与设计的复杂度。

图17 带DAC型四电平驱动AGD

Fig.17 Four-level AGD with DAC proposed

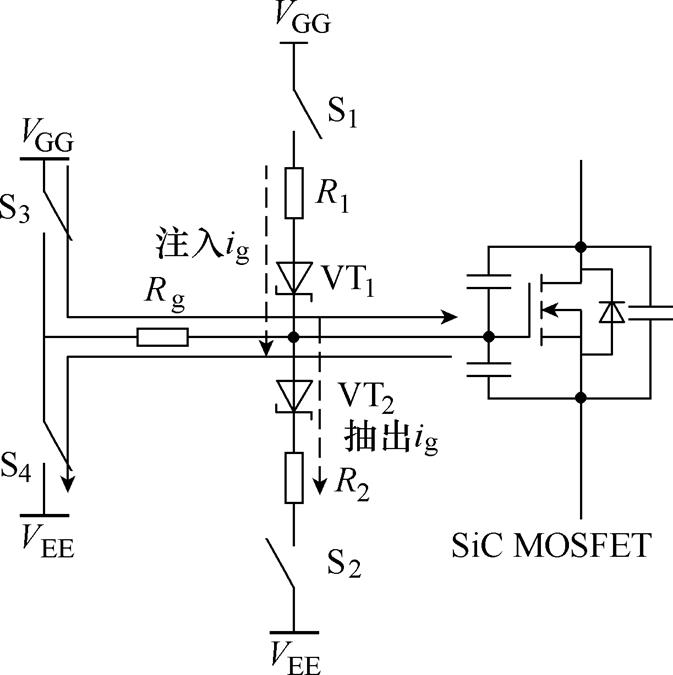

在SiC MOSFET高速开启瞬态,抽取一部分栅极驱动电流ig,有利于降低开通速度,减小电流超调;在关断瞬态,注入一部分ig,有利于减小关断速度,降低电压应力以及EMI水平。文献[25]在开关暂态阶段分别导通S1和S2,以实现动态栅极电流调节的功能,抽出/注入驱动电流型AGD如图18所示。经分析,在忽略防电流倒灌二极管压降以及将辅助开关管视为理想开关的情况下,抽出/注入驱动电流型的AGD电路等效为变驱动电阻型和变电压型的复合电路,本质上仍为电压型驱动电路。

图18 抽出/注入驱动电流型AGD

Fig.18 Injecting/extracting ig type AGD

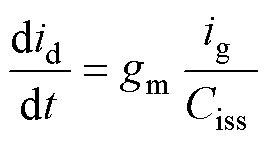

传统电压型驱动电路在开关瞬态可以等效为RC充电电路,SiC MOSFET是一个复杂的高阶数学模型。采用恒栅极电流的AGD电路有利于对SiC MOSFET驱动进行降阶处理,直接调节ig更有利于对did/dt、dv/dt进行精确调节,进而更有针对性地优化开关轨迹,分别表示为

(7)

(7)

(8)

(8)

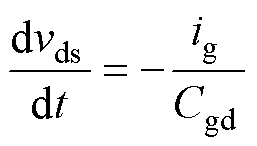

文献[32]提出了应用于SiC MOSFET的电流源驱动电路,电流型AGD如图19所示。上部分P型电流源主导开通过程的栅极电流控制,P1、RT1主要用以缩短开通延时;P2、P4、P3、RT2构成的可控电流镜可从栅极注入恒定电流,用于开通did/dt的斜率控制;RT3、P5用于抑制开通电流超调;RT4、P6用于加快开通时的电压下降速度以进一步减小开通损耗。下部分N型电流源电路主要用于从栅极抽取恒定的驱动电流,功能与P型电路类似,不再赘述。

图19 电流型AGD

Fig.19 Injecting/extracting ig type AGD

表5给出了本节所提四大类AGD功率放大驱动的性能对比,并作出了相关解释。调节步长精度表示AGD对于Rg、Vdr、ig控制的准确度,可以看出,调Vdr与恒ig型可以获得较高的调节精度,这得益于内部模拟器件工作于线性区域,但不可避免地会增加AGD电路的能耗。变电阻型、抽取/注入电流型、以及文献[24]中的变Vdr结构虽然调节精度受限,但由于其工作于开关模式,在能耗方面有着独特的优势。AGD电路属于新型驱动电路,由于器件数量的增加,在可靠性方面逊于CGD电路。表5中可靠性的评价标准为附加电路受损情况下,SiC MOSFET能否继续运行。对于激光驱动、恒流驱动的AGD,由于改变了CGD驱动的电路架构,所以可靠性下降。变Rg结构,根据切换开关管的串并联关系,可以得知文献[33]的设计在可靠性方面优于文献[27]。变电压型AGD的主要敏感部件为DAC与BUFFER电路,同时也是其成本明显高于其他AGD电路的原因。

图20给出了四种功率放大模式的等效电路结构性能对比。可以看出,变驱动电阻型和抽出/注入驱动电流型AGD电路均保留了原CGD电路的驱动架构。变电压型AGD在固定某些附加电平的情况下等效于CGD电路。电流型AGD表现为以可变电流源替代电压源。

表5 不同功率放大结构的性能对比

Tab.5 Performance comparison between different power amplifier structures

结构类型参考文献调节步长精度功耗可靠性成本 变驱动电阻型[27]低 (须增加并联电阻单元)低 (并联结构)一般低 [33]低 (须增加串联电阻单元)一般 (串联结构)高低 [34]低 (限于光敏器件非线性与激光精度,可无级调节)高 (辅助电路庞大,器件线性工作)低高 (附加光学器件及驱动) 变驱动电压型[24]低 (须增加级联电源个数)低 (开关模式)高一般 [30]高 (限于LDO精度,不能在线调节)高 (LDO耗能)一般一般 [31]高 (须增加权电阻个数,转换速度受限)高 (DAC与BUFEER耗能)低高 (高性能模拟器件) 抽出/注入驱动电流型[25]低 (变电阻、变电压复合型)一般 (二极管压降)高低 电流源型[32]高 (须提升恒流源质量)高 (电流镜耗能)低低

图20 AGD等效电路

Fig.20 Equivalent circuit topology of AGD

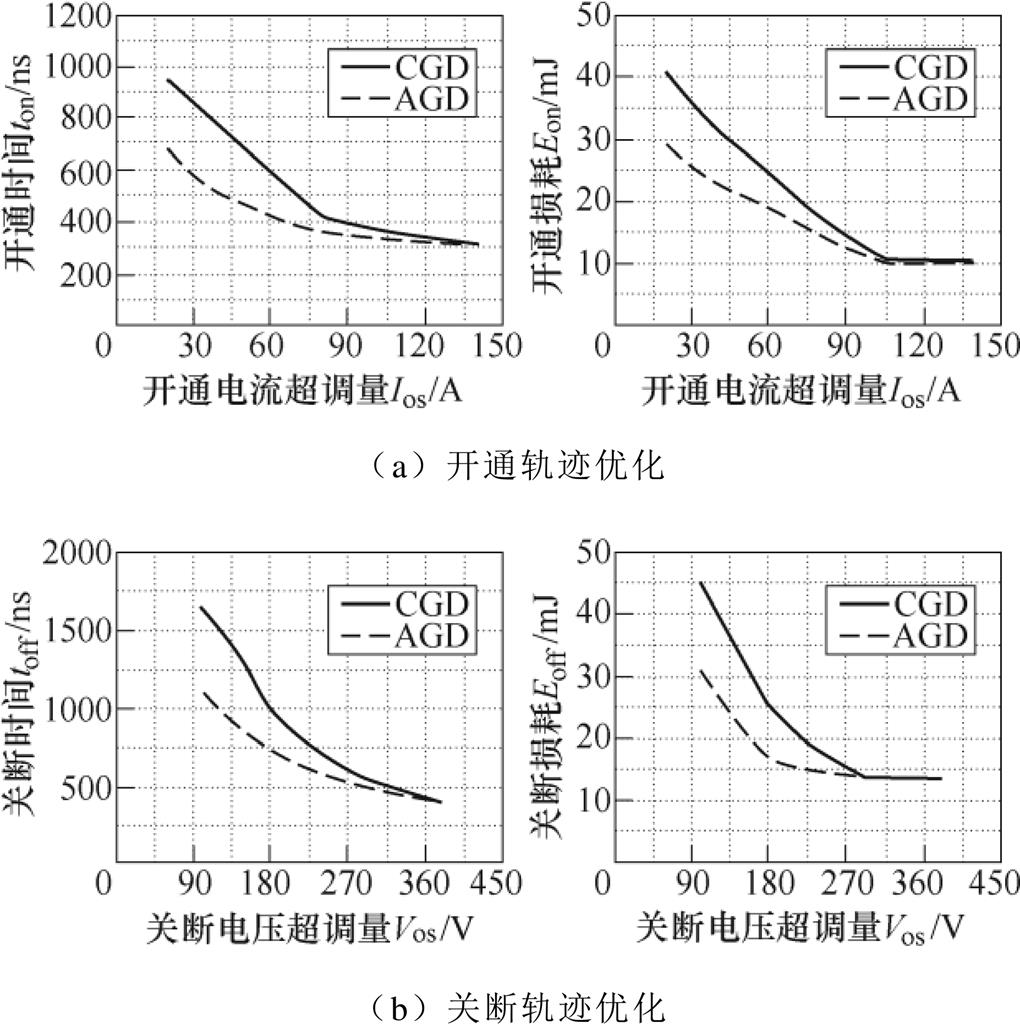

图21展示了文献[24]所提出的变驱动电压型AGD对于SiC MOSFET开关轨迹的优化效果,实验在500V/280A双脉冲测试平台上进行。在开通轨迹的优化对比中,相同电流超调量的情况下AGD电路所带来的开通延时以及开通损耗远低于CGD电路;在关断轨迹的优化对比中,相同电压超调量下AGD的关断延时以及关断损耗同样远低于CGD电路。图21展示的SiC MOSFET开关轨迹优化趋势与图2的分析一致。

图21 AGD的开关轨迹优化效果

Fig.21 Switching trajectory optimization of AGD proposed

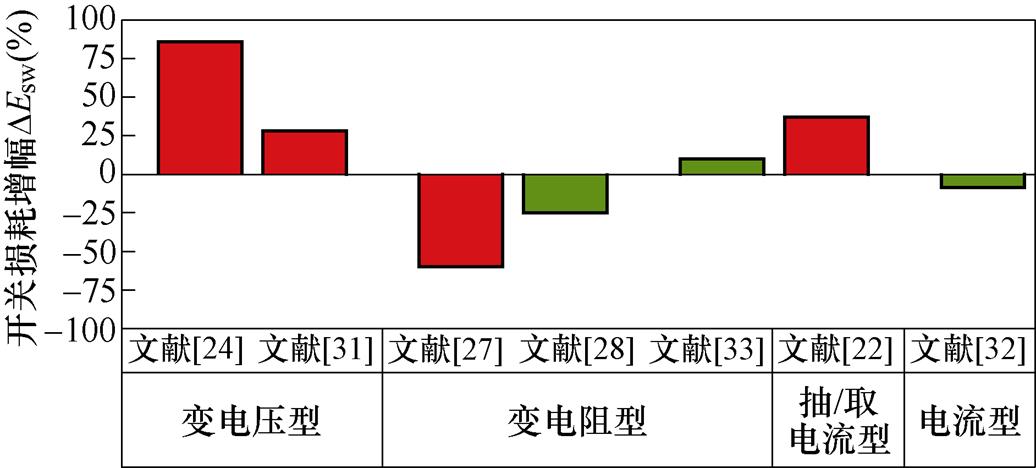

相同电流、电压抑制效果下SiC MOSFET开关损耗的增幅是衡量AGD电路性能的重要指标。AGD电路不仅不会显著增大开关损耗,同时可以通过抑制电气超调来降低开关损耗,提升系统效率。由于各文献中双脉冲测试电路寄生参数和工作点存在差异,为直观对比不同类型AGD电路中SiC MOSFET开关轨迹的优化效果,采用百分比的形式对总开关损耗增幅DEsw进行统计。图22给出了开通电流超调量和关断电压超调量抑制均在40%~60%范围内,不同AGD总开关损耗的增幅。显然,即使相较于CGD电路优势明显,但不同AGD技术在损耗优化方面的表现不尽相同。文献[27]所采用的变电阻型AGD展示出最优良的损耗特性,在40%电流超调抑制、47%电压超调抑制的情况下可以使得SiC MOSFET的总开关损耗降低近60%,而文献[24]所提出的AGD电路则会使得开关损耗上升86%,这为高效率系统设计带来了挑战。SiC MOSFET开关暂态定位的准确度直接决定了AGD的损耗特性,一旦对于开关管开关暂态的捕捉产生偏移,开关损耗就会大大上升。采用低成本的比较器触发进行暂态定位的精度相较于采用实时ADC采样低一些。

图22 不同AGD的损耗性能对比

Fig.22 Loss performance comparison of different AGD circuits

SiC MOSFET的开关轨迹优化主要分为三个步骤:①确定时间节点;②选取轨迹路径;③执行轨迹优化。开关轨迹优化的时间节点大多在电力电子变换器主电路设计完成之后,此时电路拓扑、回路寄生参数、功率器件选型、负载电流范围等因素基本落实,SiC MOSFET初始条件下的开关轨迹也随之确定,AGD可以更有针对性开展调控。

SiC MOSFET开关轨迹优化路径的选取是以初始轨迹以及变换器应用环境要求为导向的。首先,设计者需要借助CGD电路对SiC MOSFET进行双脉冲测试,以获得其初始开关轨迹下开关损耗、电气超调、电磁干扰发射强度等基本数据。其次,结合初始轨迹和应用场景确定开关轨迹优化的方向,电气应力、EMI强度、开关损耗的同步降低是最理想的开关轨迹,但由于降低开关速度势必会影响开关损耗,有时需要设计者确定轨迹优化的重心,例如,应用于精密仪器的电源必须以削弱EMI为导向,器件安全区裕度不足时必须以降低电气超调量为导向,而追求高效率的电力电子装置则必须以最小化开关损耗为导向。最后,设计者需要从初始轨迹出发,初步确定AGD电路的参数,提升AGD参数整定的效率。图23给出了SiC MOSFET最理想的开关轨迹优化趋势。

图23 SiC MOSFET轨迹优化趋势

Fig.23 Trajectory optimization trend of SiC MOSFETs

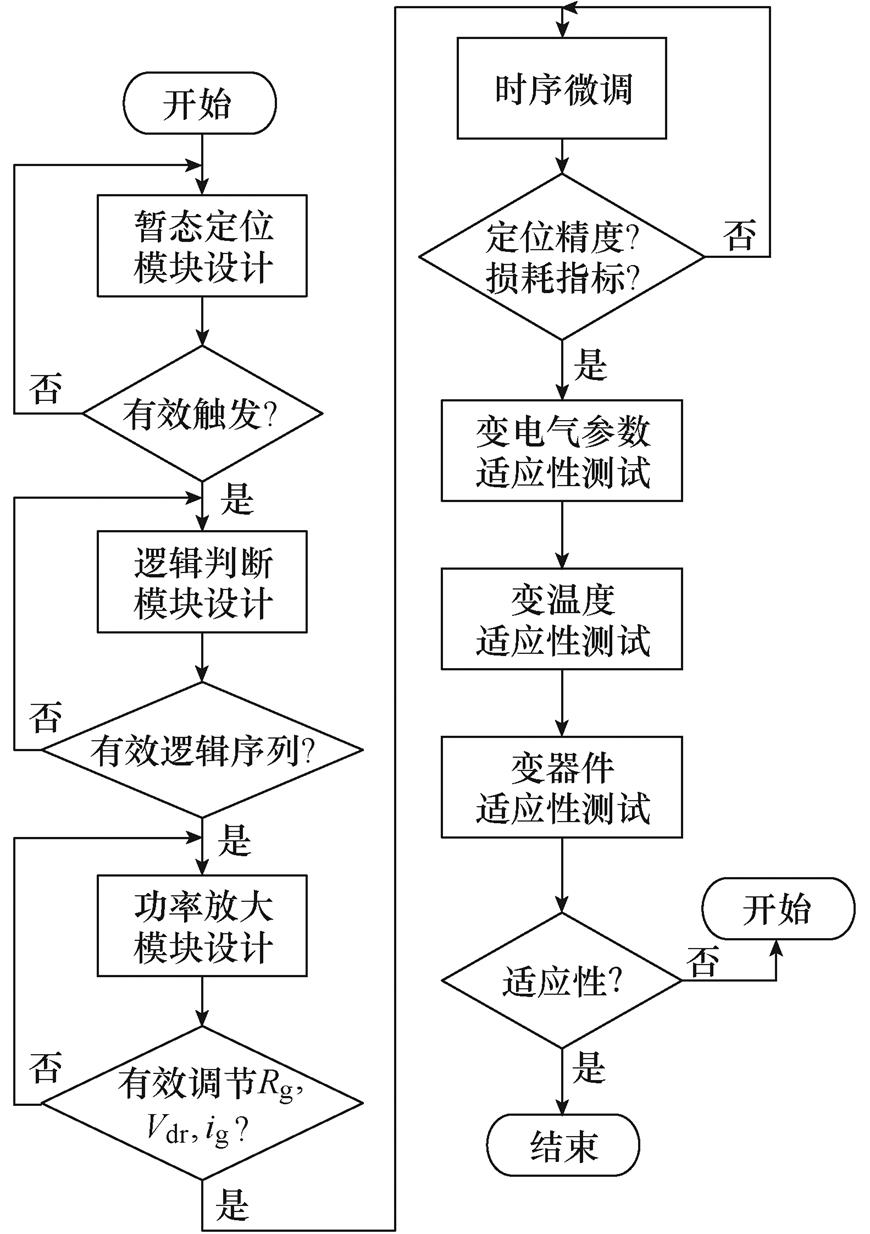

暂态定位、逻辑判断、功率放大三部分共同完成了AGD的开关轨迹优化功能。目前,不同文献在三个模块电路的设计上均作出了不同类型的尝试。在对各设计方案进行横向对比后,给出了基于开关轨迹优化的SiC MOSFET有源驱动电路的基本设计流程,如图24所示。

图24 AGD设计流程

Fig.24 AGD circuit design process

暂态定位模块的触发、逻辑判断模块的信号处理序列以及功率放大模块的可靠调节是AGD电路有效工作的必要前提。其中,环路响应的速度与对SiC MOSFET开关噪声的抑制能力是设计者选择不同模块设计方案时需要重点关注的问题。

在功率放大模块完成对于SiC MOSFET的超调、振荡、EMI等负面效应的抑制效果后,需要对AGD操作的时序进行微调:一方面,闭环调节使得SiC MOSFET的开关速度产生变化,暂态定位点会产生一定的漂移,需要进行相应的补偿;另一方面,随着开关速度的降低,SiC MOSFET的开关损耗会上升,调节作用时间能够实现开关损耗与开关速度的折中[24, 33]。常用的时序微调方法有调节暂态定位触发阈值[22-24]以及在逻辑处理模块中加入延时两种[24, 26, 30-31]。

能否适应SiC MOSFET的实际运行是衡量AGD电路质量的重要标准,不同类型的参数适应性测试是必不可少的。变电气参数适应性测试主要有三类:①变母线电压测试[24-25],以验证SiC MOSFET在不同电压应力条件下AGD电路的有效性;②变负载电流测试[22, 24-25, 31-32],以验证不同工作负载下AGD电路的有效性;③变无源参数测试[22-23, 25-28],即在不同驱动电阻、寄生参数等条件下验证AGD电路的有效性。变温度参数适应性测试[31]主要有两个目的:一方面,验证AGD中附加模拟电路在长时间工作条件下是否会产生显著温漂影响正常工作;另一方面,验证AGD能否继续适应SiC MOSFET发热所带来的轨迹漂移。变器件适应性测试[30, 33]则是验证AGD电路对于SiC 器件的普适性,不同型号的SiC MOSFET的开关特性有所不同,优秀的AGD电路可以在不大幅修改设计参数情况下适应不同器件。

以上步骤基本保证AGD的可靠性,成本的校核应渗透在子模块的方案选择中,同样需要考虑。

宽禁带半导体的有源栅极驱动的相关研究目前仍处于起步阶段。与应用于IGBT的AGD电路[35-36]相类似,基于开关轨迹优化的SiC MOSFET有源驱动电路未来发展趋势与技术难题主要有以下几点:

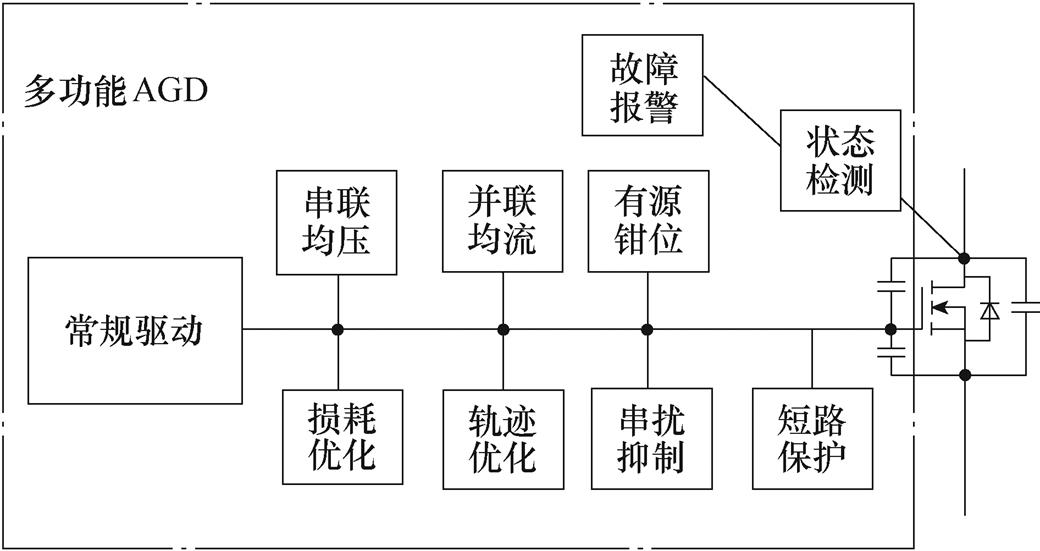

1)功能复化

随着SiC器件的逐步推广,对于驱动电路的要求也逐步增多。单纯某一种类型的有源驱动并不能很好地对SiC MOSFET开关瞬态进行多角度的改善。将短路保护、串扰抑制等其他功能纳入基于开关轨迹优化的AGD电路成为必然要求,多功能AGD驱动架构如图25所示。如何对于大量的附加电路进行分时复用,进而简化设计、降低成本是技术难点。

图25 多功能AGD驱动架构

Fig.25 Multifunctional AGD driver architecture

2)控制升级

控制稳定性方面,SiC MOSFET跨导与结电容有着很强的非线性特征[37],并且电压源驱动下的SiC MOSFET的响应特性是复杂的高阶数学方程。同时,阈值切换型AGD电路本质上属于一种非线性的闭环控制,无法使用全闭环型AGD中伯德图、根轨迹等分析工具来研究控制系统的稳定性。目前,对于SiC MOSFET开关暂态的建模工作仍在进行之中。

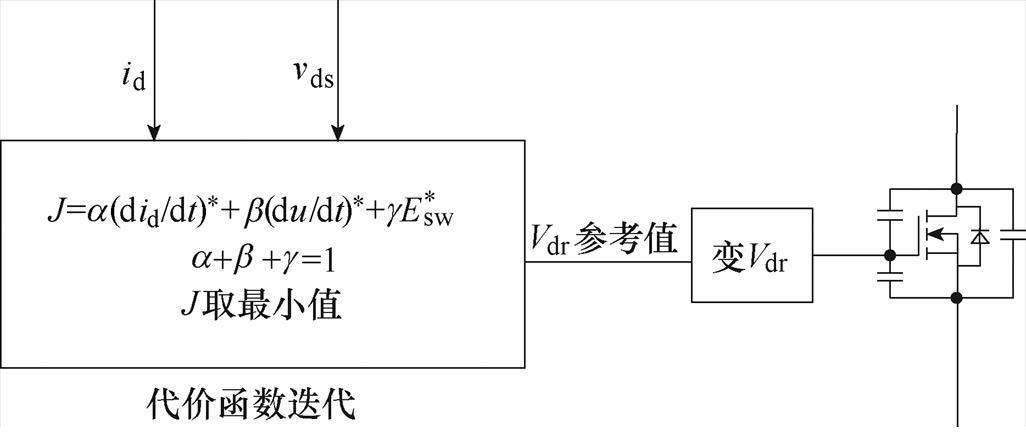

控制精度方面,SiC MOSFET的开关轨迹随着工作电压、负载电流的变化而变化[38],这对于AGD电路开关轨迹优化的效果产生一定的影响:一方面,AGD的暂态定位点有可能产生一定的偏移,功率放大电路的动作可能产生超前或滞后;另一方面,SiC MOSFET漏源电压的超调振荡随着负载电流的增大而恶化,在调节参数相对固定的情况下,AGD电路可能在重载时发生失效,在轻载时则会造成多余的开关损耗。目前,基于开关轨迹优化的AGD电路的自适应调节技术还鲜有报道。文献[31]提出了基于代价函数的在线参数选择的AGD逻辑处理架构,如图26所示。该方法可以大幅提升AGD的控制精度,通过设置权重因子a、b、g 实现对于did/dt、dv/dt、Esw等多个指标的折中控制,但是控制器运算速度、迭代算法收敛性以及硬件成本成为需要进一步解决的问题。

图26 基于代价函数的在线型AGD

Fig.26 Online AGD based on cost function

响应带宽方面,随着高性能模拟、数字器件技术的进步,更高的响应速度得以应用于SiC MOSFET的ns级控制。高频数字信号交互所带来的信号完整问题[39]、运算放大器增益带宽积与压摆率的限制[40]以及附加器件布局方式有待深入研究。

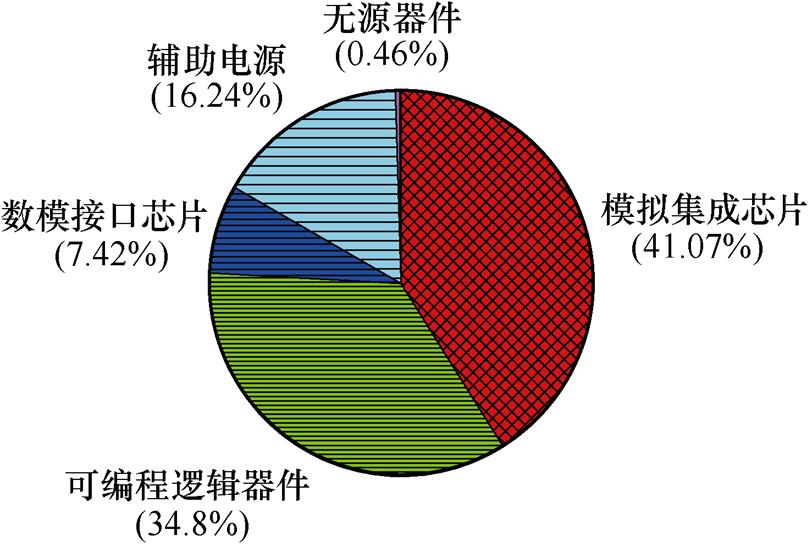

3)硬件集成与成本约束

AGD电路最终的市场化必须缩小体积、降低成本,并以单片的形式推荐给用户。图27给出了文献[31]中AGD电路的成本分布。图中,模拟集成电路与可编程逻辑器件是制约AGD市场化的主要因素。在电路集成方面,数字电路的集成化易于实现,而如比较器、DAC、Buffer等模拟电路的集成则复杂得多,对于SiC MOSFET开关暂态的电磁干扰也更为敏感。另外,辅助电源的个数也需要加以控制。进一步简化附加有源电路是未来AGD的发展趋势。

图27 AGD的成本分布

Fig.27 The cost distribution of AGD

SiC MOSFET高速开关轨迹中的超调、振荡、EMI问题成为制约其进一步推广的因素。本文综述了目前基于SiC MOSFET开关轨迹优化的SiC MOSFET有源驱动电路相关技术。

1)阐述了SiC MOSFET轨迹优化的含义,分析了AGD电路的工作原理,总结了不同栅极驱动参数对于SiC MOSFET开关特性的影响,着重剖析阈值触发型AGD电路的工作模式。

2)分别从暂态定位、逻辑判断、功率放大三个子电路的设计方案角度出发,对现有文献进行综述,并对比了不同技术之间的性能差异,得出四种主流AGD架构的等效电路模型。

3)给出了AGD电路基本的设计流程建议。

4)讨论了AGD电路技术未来的发展方向。

随着宽禁带器件驱动技术的不断发展,基于SiC MOSFET开关轨迹优化的有源栅极驱动技术具有巨大的研究价值与广阔的应用空间。

附 录

SCT2080KE的双脉冲测试波形如附图1所示。

附图1 SiC MOSFET开关暂态实验波形

App.Fig.1 Experimental waveforms in switching transients of SiC MOSFET

参考文献

[1] 梁美, 郑琼林, 可翀, 等. SiC MOSFET、Si CoolMOS和IGBT的特性对比及其在DAB变换器中的应用[J]. 电工技术学报, 2015, 30(12): 41-50.

Liang Mei, Zheng Qionglin, Ke Chong, et al. Performance comparison of SiC MOSFET, Si CoolMOS and IGBT for DAB converter[J]. Transa- ctions of China Electrotechnical Society, 2015, 30(12): 41-50.

[2] Schrock J, Pushpakaran B, Bilbao A, et al. Failure analysis of 1200V/150A SiC MOSFET under repetitive pulsed overcurrent conditions[J]. IEEE Transactions on Power Electronics, 2016, 31(3): 1816-1821.

[3] Li Hong, Jiang Yanfeng, Qiu Zhidong, et al. A predictive algorithm for crosstalk peaks of SiC MOSFET by considering the nonlinearity of gate- drain capacitance[J]. IEEE Transactions on Industrial Electronics, 2021, 36(3): 2823-2834.

[4] Roy S, Basu K. Analytical estimation of turn on switching loss of SiC mosfet and schottky diode pair from datasheet parameters[J]. IEEE Transactions on Power Electronics, 2019, 34(9): 9118-9130.

[5] Roy S, Basu K. Analytical model to study hard turn- off switching dynamics of SiC MOSFET and schottky diode pair[J]. IEEE Transactions on Power Elec- tronics, 2021, 36(1): 861-875.

[6] Zhang Zheyu, Wang Fred, Tolbert L, et al. Evaluation of switching performance of SiC devices in PWM inverter-fed induction motor drives[J]. IEEE Transa- ctions on Power Electronics, 2015, 30(10): 5701- 5711.

[7] 段卓琳, 张栋, 范涛. SiC电机驱动系统传导电磁干扰建模及预测[J]. 电工技术学报, 2020, 35(22): 4726-4738.

Duan Zhuolin, Zhang Dong, Fan Tao. Modeling and prediction of electromagnetic interference in SiC motor drive systems[J]. Transactions of China Electrotechnical Society, 2020, 35(22): 4726-4738.

[8] Zhu Nan, Mantooth H, Xu Dehong, et al. A solution to press-pack packaging of SiC MOSFETs[J]. IEEE Transactions on Industrial Electronics, 2017, 64(10): 8224-8234.

[9] Gui Handong, Sun Jingjing, Tolbert L. Charge pump gate drive to reduce turn-on switching loss of SiC MOSFETs[J]. IEEE Transactions on Power Elec- tronics, 2020, 35(12): 13136-13147.

[10] Zhang Zheyu, Wang Fred, Tolbert L, et al. Active gate driver for crosstalk suppression of SiC devices in a phase-leg configuration[J]. IEEE Transactions on Power Electronics, 2014, 29(4): 1986-1997.

[11] Marzoughi A, Burgos R, Boroyevich D. Active gate-driver with dv/dt controller for dynamic voltage balancing in series-connected SiC MOSFETs[J]. IEEE Transactions on Industrial Electronics, 2019, 66(4): 2488-2498.

[12] Wen Yang, Yang Yuan, Gao Yong. Active gate driver for improving current sharing performance of paralleled high-power SiC MOSFET modules[J]. IEEE Transactions on Power Electronics, 2021, 36(2): 1491-1505.

[13] Aeloiza E, Kadavelugu A, Rodrigues R. Novel bipolar active miller clamp for parallel SiC MOSFET power modules[C]//IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 2018: 401- 407.

[14] 吴海富, 张建忠, 赵进, 等. SiC MOSFET短路检测与保护研究综述[J]. 电工技术学报, 2019, 34(21): 4519-4528.

Wu Haifu, Zhang Jianzhong, Zhao Jin, et al. Review of short-circuit detection and protection of silicon carbide MOSFETs[J]. Transactions of China Elec- trotechnical Society, 2019, 34(21): 4519-4528.

[15] Wang Jianjing, Chung H, Li R. Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance[J]. IEEE Transactions on Power Electronics, 2013, 28(1): 573-590.

[16] Zeng Zheng, Li Xiaoling. Comparative study on multiple degrees of freedom of gate drivers for transient behavior regulation of SiC MOSFET[J]. IEEE Transactions on Power Electronics, 2018, 33(10): 8754-8763.

[17] Grbovic P. An IGBT gate driver for feed-forward control of turn-on losses and reverse recovery current[J]. IEEE Transactions on Power Electronics, 2008, 23(2): 643-652.

[18] Grbovic P, Gruson F, Idir N, et al. Turn-on per- formance of reverse blocking IGBT (RB IGBT) and optimization using advanced gate driver[J]. IEEE Transactions on Power Electronics, 2010, 25(4): 970-980.

[19] Shu Lu, Zhang Junming, Peng Fangzheng, et al. Active current source IGBT gate drive with closed- loop di/dt and dv/dt control[J]. IEEE Transactions on Power Electronics, 2017, 32(5): 3787-3796.

[20] 朱义诚, 赵争鸣, 施博辰, 等. 绝缘栅型功率开关器件栅极驱动主动控制技术综述[J]. 高电压技术, 2019, 45(7): 2082-2092.

Zhu Yicheng, Zhao Zhengming, Shi Bochen, et al. Review of active gate control methods for insulated- gate power switching devices[J]. High Voltage Engineering, 2019, 45(7): 2082-2092.

[21] 王莉娜, 邓洁, 杨军一, 等. Si和SiC功率器件结温提取技术现状及展望[J]. 电工技术学报, 2019, 34(4): 703-716.

Wang Lina, Deng Jie, Yang Junyi, et al. Junction temperature extraction methods for Si and SiC power devices-a review and possible alternatives[J]. Transa- ctions of China Electrotechnical Society, 2019, 34(4): 703-716.

[22] 李先允, 卢乙, 倪喜军, 等. 一种改进SiC MOSFET开关性能的有源驱动电路[J]. 中国电机工程学报, 2020, 40(18): 5760-5770.

Li Xianyun, Lu Yi, Ni Xijun, et al. An active gate driver for improving switching performance of SiC MOSFET[J]. Proceedings of the CSEE, 2020, 40(18): 5760-5770.

[23] 冯超, 李虹, 蒋艳锋, 等. 抑制瞬态电压电流尖峰和振荡的电流注入型SiC MOSFET有源驱动方法研究[J]. 中国电机工程学报, 2019, 39(19): 5666-5673, 5894.

Feng Chao, Li Hong, Jiang Yanfeng, et al. Research on current injection active drive method of SiC MOSFET with transient voltage and current spike and oscillation suppression[J]. Proceedings of the CSEE, 2019, 39(19): 5666-5673, 5894.

[24] Yang Yuan, Wen Yang, Gao Yong. A novel active gate driver for improving switching performance of high-power SiC MOSFET modules[J]. IEEE Transa- ctions on Power Electronics, 2019, 34(8): 7775- 7787.

[25] 刘平, 李海鹏, 苗轶如, 等. 基于驱动电流动态调节的低过冲低损耗SiC MOSFET有源门极驱动[J]. 中国电机工程学报, 2020, 40(18): 5730-5742.

Liu Ping, Li Haipeng, Miao Yiru, et al. Low overshoot and low loss active gate driver for SiC MOSFET based on driving current dynamic regu- lation[J]. Proceedings of the CSEE, 2020, 40(18): 5730-5742.

[26] Acharya S, She Xu, Tao Fengfeng, et al. Active gate driver for SiC-MOSFET-based PV inverter with enhanced operating range[J]. IEEE Transactions on Industry Applications, 2019, 55(2): 1677-1689.

[27] Nayak P, Hatua K. Active gate driving technique for a 1200V SiC MOSFET to minimize detrimental effects of parasitic inductance in the converter layout[J]. IEEE Transactions on Industry Applications, 2018, 54(2): 1622-1633.

[28] Nayak P, Hatua K. Parasitic inductance and capacitance-assisted active gate driving technique to minimize switching loss of SiC MOSFET[J]. IEEE Transactions on Industrial Electronics, 2017, 64(10): 8288-8298.

[29] Chen Kainan, Zhao Zhengmin, Yuan Liqiang, et al. The impact of nonlinear junction capacitance on switching transient and its modeling for SiC MOSFET[J]. IEEE Transactions on Electron Devices, 2014, 62(2): 333-338.

[30] Zhao Shuang, Dearien A, Wu Yuheng. Adaptive multi-level active gate drivers for SiC power devices[J]. IEEE Transactions on Power Electronics, 2020, 35(2): 1882-1898.

[31] Zhao Shuang, Zhao Xingcheng, Dearien A, et al. An intelligent versatile model-based trajectory-optimized active gate driver for silicon carbide devices[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 429-441.

[32] Sukhatme Y, Miryala V, Ganesan P, et al. Digitally controlled gate current source-based active gate driver for silicon carbide MOSFETs[J]. IEEE Transactions on Industrial Electronics, 2020, 67(12): 10121-10133.

[33] Camacho A, Sala V, Ghorbani H, et al. A novel active gate driver for improving SiC MOSFET switching trajectory[J]. IEEE Transactions on Industrial Elec- tronics, 2017, 64(11): 9032-9042.

[34] Riazmontazer H, Mazumder S. Optically switched- drive-based unified independent dv/dt and di/dt control for turn-off transition of power MOSFETs[J]. IEEE Transactions on Power Electronics, 2015, 30(4): 2338-2349.

[35] 黄华震, 仝涵, 王宁燕, 等. 考虑寄生振荡的IGBT分段暂态模型对电磁干扰预测的影响分析[J]. 电工技术学报, 2021, 36(12): 2434-2445.

Huang Huazhen, Tong Han, Wang Ningyan, et al. Analysis of the influence of IGBT segmented transient model with parasitic oscillation on elec- tromagnetic interference prediction[J]. Transactions of China Electrotechnical Society, 2021, 36(12): 2434-2445.

[36] 凌亚涛, 赵争鸣, 姬世奇. 基于主动栅极驱动的IGBT开关特性自调节控制[J]. 电工技术学报, 2021, 36(12): 2482-2494.

Ling Yatao, Zhao Zhengming, Ji Shiqi. Self- regulating control of IGBT switching characteristics with active gate drive[J]. Transactions of China Electrotechnical Society, 2021, 36(12): 2482-2494.

[37] Duan Zhuolin, Fan Tao, Wen Xuhui, et al. Improved SiC power MOSFET model considering nonlinear junction capacitances[J]. IEEE Transactions on Power Electronics, 2018, 33(3): 2509-2517.

[38] Yamaguchi K, Katsura K, Yamada T, et al. Criteria for using antiparallel SiC SBDs with SiC MOSFETs for SiC-based inverters[J]. IEEE Transactions on Power Electronics, 2020, 35(1): 619-629.

[39] Chuang Haohsiang, Guo Weida, Lin Yuhsiang, et al. Signal/power integrity modeling of high-speed memory modules using chip-package-board coanalysis[J]. IEEE Transactions on Electromagnetic Compatibility, 2010, 52(2): 381-391.

[40] Hoi Lee, Mok P. Active-feedback frequency- compensation technique for low-power multistage amplifiers[J]. IEEE Journal of Solid-State Circuits, 2003, 38(3): 511-520.

Review of Active Gate Driver for SiC MOSFET with Switching Trajectory Optimization

Abstract With the popularization of SiC MOSFETs, the problems of overshoot, oscillation and electromagnetic interference in the switching transient process have attracted more and more attention. As a novel driver, active gate driver (AGD) is widely used in the switching trajectory optimization of SiC MOSFETs. First of all, this paper analyzes the working principle of the AGD circuit, and gives the influence of different driving parameters on the switching characteristics. Secondly, this paper focuses on the working mode of the threshold-trigger type AGD circuit. It summarizes the AGD circuit from the three aspects of transient positioning technology, logic processing architecture, and power amplification topology. The advantages and disadvantages of different technologies are evaluated, and the process of AGD circuit design is proposed. Finally, the development trend of AGD circuit for SiC MOSFET switch trajectory is discussed.

keywords:SiC MOSFET, active gate driver (AGD), switching trajectory, oscillation

DOI: 10.19595/j.cnki.1000-6753.tces.210560

中图分类号:TM46

王 宁 男,1998年生,硕士研究生,研究方向为宽禁带半导体器件电磁暂态建模及其主动控制策略。E-mail: 875313179@qq.com

张建忠 男,1970年生,研究员,博士生导师,主要研究领域为新能源发电和电力电子技术。E-mail: jiz@seu.edu.cn(通信作者)

收稿日期 2021-04-20

改稿日期 2021-07-08

国家自然科学基金重大资助项目(51991384)。

(编辑 陈 诚)