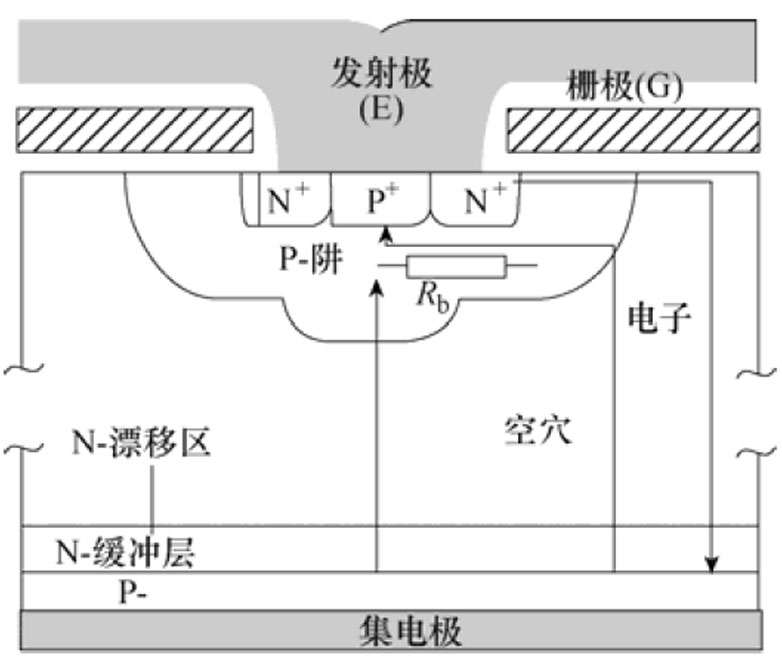

图1 IGBT结构示意图

Fig.1 Schematic cross-section of IGBT cell structure

摘要 提高绝缘栅双极晶体管(IGBT)单芯片电流容量,对减小封装器件芯片并联数、简化封装结构、改善芯片均流至关重要。该文基于高压、大电流、高可靠性IGBT应用需求,通过高压IGBT芯片坚强元胞设计及其协同控制技术实现了元胞之间的开关同步,通过光刻拼版技术解决大尺寸芯片的工艺制造,通过单芯片压接封装验证了大尺寸芯片设计及其性能,探索出一条大尺寸IGBT芯片设计、制造与验证的技术路径。研究开发了全球第一片42mm×42mm大尺寸高压IGBT芯片,攻克了高压IGBT芯片内部大规模元胞集成及其均流控制的技术难题,首次实现了4 500V/600A单芯片功率容量,具备优良的动静态特性和更宽的安全工作区,并可以显著提高IGBT封装功率密度与可靠性。

关键词:大尺寸IGBT芯片 电流容量 均流 压接

绝缘栅双极晶体管(Insulated Gate Bipolar Transistor, IGBT)作为能量处理与控制的“CPU”,耐受电压高、电流容量大、驱动功率小、开关速度快、使用方便灵活,已成为电力电子装置的主流开关器件[1-2]。随着高铁、轨道交通、新能源与电力系统应用技术的发展,对IGBT的功率容量与可靠性提出了越来越高的要求[3-4]。

IGBT芯片融合了传统电力电子器件技术与微电子制造工艺,线宽越来越精细,已经进入亚微米工艺技术时代[1]。由于常规芯片设计与制造工艺的限制,单芯片电流容量受到一定限制,已见报道的4 500V IGBT单芯片最大电流容量约150A[5-6]。如果应用系统需要更大的电流,一般通过多芯片并联封装来实现。IGBT封装过程中,无论是传统焊接型IGBT模块,还是压接型封装,各并联支路不可避免地存在杂散电感和电阻,这会影响并联芯片之间的电流分布,继而影响IGBT器件电流能力、功率密度与应用可靠性。

IGBT芯片包括有效区(元胞区)和边缘终端区两部分,高压芯片的终端区域占芯片面积的相当大一部分,如13.5mm×13.5mm尺寸的4 500V芯片,终端面积占总个芯片面积40%以上。因此单芯片尺寸越大,就可以取代更多并联的小芯片,省去很多不必要的(小芯片)终端区域,相比划片区域,节约成本。同时在同等电流能力条件下,因为大芯片的终端区域面积比多个并联的小芯片终端面积总和要小很多,所以大芯片的终端漏电流将会明显得到改善。

单芯片电流容量越大,则芯片并联数相应减小,同时因为封装结构的简化,可以进一步改善芯片之间的均流状况,从而提高IGBT器件效率与应用可靠性[7-9],因此单芯片电流容量成为制约IGBT模块功率容量、功率密度和应用可靠性的主要技术瓶颈。提高IGBT芯片的电流容量,需要并联更多的IGBT元胞,意味着需要更大的有效区来集成这些并联元胞。芯片的大尺寸及其内部并联元胞之间的开关同步与均流,对芯片本身的设计与制造带来巨大挑战,主要体现在芯片内部元胞本身的鲁棒性、元胞间的开关同步和大尺寸芯片焊接应力控制等长期困扰业界的技术难题上,如果处理不当,芯片内部元胞不均流和封装过程中因热膨胀系数失配而带来的焊接应力都会对芯片造成损伤。

影响芯片大尺寸化的另一个因素是IGBT芯片制造能力,包括光刻机曝光面积、工艺稳定性与良率水平。一般说来,芯片尺寸越大,芯片的良率越低,所以要实现大尺寸芯片的量产,芯片工艺线必须稳定并且维持在比较高的良率水平。另一方面,光刻机曝光面积与光刻精度成反比,在确保一定光刻精度的情况下,步进和扫描光刻机曝光面积都会受到限制,一般6in光刻机曝光面积为16mm×16mm,8in光刻机曝光面积为22mm×22mm,一般光刻机曝光面积最大不超过26mm×33mm。综合考虑各种因素,常规IGBT芯片尺寸一般不会超过16mm× 16mm,芯片电流、功率容量就会受到较大限制。

本文通过把宏观层面的IGBT芯片均流转换成微观层面元胞间的开关同步来解决IGBT封装过程中的芯片均流与可靠性问题,详细分析了并联元胞本身的鲁棒性设计和更大尺寸、更大规模元胞集成时的开关同步机制,成功研制出42mm×42mm大尺寸4 500V/600A超大功率IGBT芯片,展示出优越的综合性能和强鲁棒性,为IGBT器件并联芯片之间的均流问题提供了一个全新的技术解决方案,也为大尺寸IGBT芯片描绘了一个广阔的应用前景。

IGBT芯片由成千上万个元胞组成,要实现芯片级大尺寸设计,集成更多的并联元胞,不仅要解决单元胞自身的鲁棒性和多元胞之间的协同性,而且要通过优化体结构和终端结构设计,降低芯片损耗和终端漏电,提高芯片静、动态特性和可靠性。下面从四个方面展开分析。

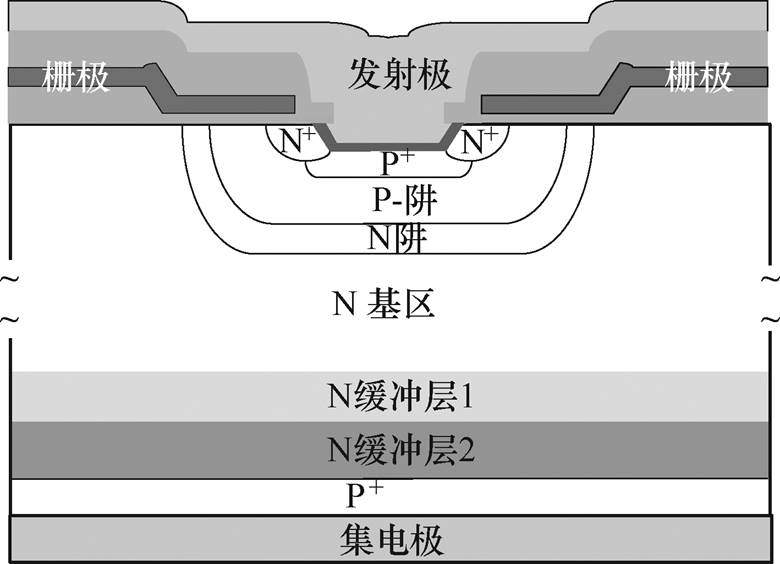

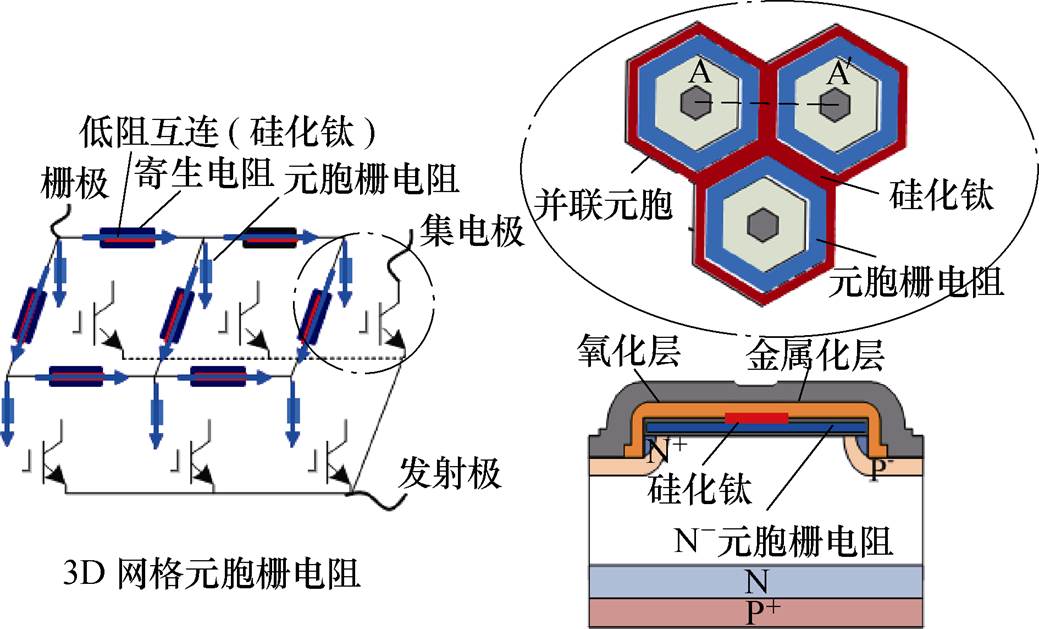

IGBT是MOS结构控制的双极结型晶体管,基本结构如图1所示。在正向阻断时,如果在栅极(G)施加一个大于阈值电压的正向电压,则在栅极正下方P基区表面形成导电沟道,沟道电流作为PNP晶体管基极电流,PNP晶体管导通,此时集电极向漂移区注入空穴,并与通过沟道电流注入过来的电子在漂移区形成电导调制,显著降低漂移区电阻。IGBT正向电流包括MOS沟道的电子电流和PNP晶体管集电极空穴电流两部分。沟道电子电流直接由栅压来控制,随沟道的消失而消失;空穴电流则由通过栅压形成的沟道电流间接控制,沟道消失后通过漂移区电子与空穴的复合来实现PNP晶体管的关断。

IGBT导通时,如果集电极电压比较高,则IGBT 的沟道会被夹断,导致其沟道电流饱和,不再随着集电极电压的增大而增大,IGBT的饱和电流[10]为

图1 IGBT结构示意图

Fig.1 Schematic cross-section of IGBT cell structure

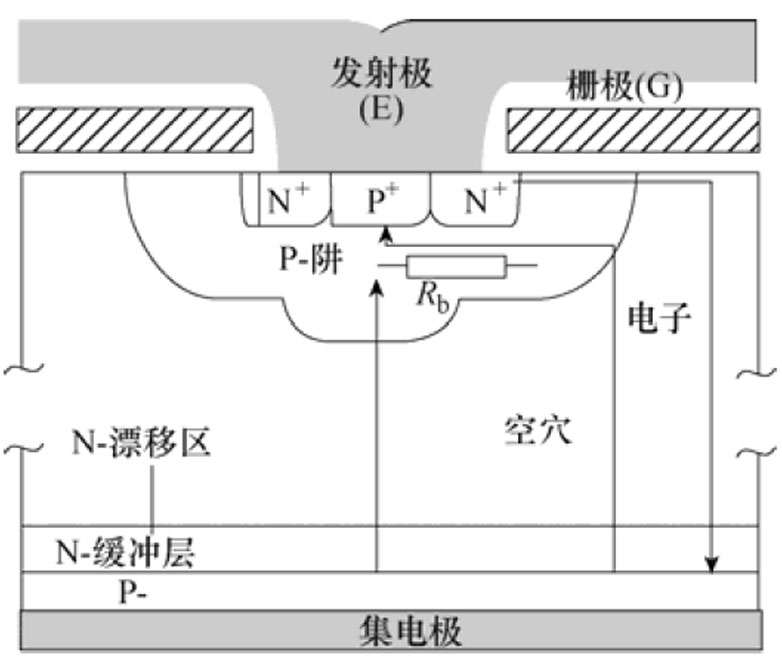

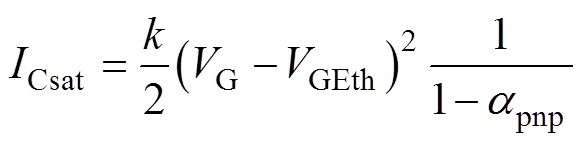

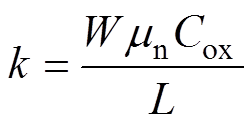

(1)

(1)其中

式中,W为对应沟道宽度;mn为沟道电子漂移率;Cox为单位面积栅电容;L为沟道长度;VG为栅极电压;VGEth为阈值电压;apnp为PNP晶体管的共基极电流增益。

由此可见,IGBT饱和电流大小不仅与栅压相关,而且与PNP晶体管电流增益apnp有关系,取决于背面空穴注入效率和基区载流子传输因子。为了控制IGBT的饱和电流,PNP晶体管增益apnp就不能调得过高。通过调节apnp,可以有效控制双极晶体管电流和MOS沟道电流的比例,从而充分利用MOS电流的正温度系数特征,确保在大电流应用下各元胞的均流能力。理论上讲,较小的饱和电流能使IGBT在短路状态下耗散功率更低,有益于提升IGBT的短路安全工作区,但饱和电流的控制同时也要兼顾通态损耗的大小。

IGBT由于芯片内部寄生的PNPN晶闸管结构,不可避免地存在闩锁效应,通过采用增强型平面栅(enhanced Double-diffused Metal Oxide Semicon- ductor, DMOS+)新型U形嵌入式发射极结构[11](见图2)可大幅度降低P基区内N+源极下方的横向电阻Rb(见图1),从而有效抑制闩锁效应。通过在P基区外包裹一层N阱层形成载流子存储层如图2所示,对发射极空穴的抽取形成势垒,使大量的非平衡载流子在发射极附近堆积,以提升元胞区发射极侧的载流子浓度,如图3所示,通过增强IGBT体内漂移区电导调制效应,来降低芯片体内导通电阻,在相同的电流下,IGBT芯片的导通压降得以明显降低。

图2 DMOS+ U形元胞示意图

Fig.2 Schematic cross-section of DMOS+ U-cell

图3 注入增强型元胞载流子浓度

Fig.3 Carrier distribution for injection enhancement cell

为了实现上述设计,采用了双阱高温推进、基-射自对准和抗应力侧墙等工艺技术,将发射极从表面延伸到U形元胞P阱内部,降低了电阻Rb、空穴电流在Rb上形成的压降和寄生NPN晶体管增益anpn,显著提高了寄生晶闸管的触发阈值,抑制了高压IGBT在高电流密度下动、静态闩锁效应的发生,从而提高了反偏安全工作区(Reverse Blocking Safe Operation Area, RBSOA)性能。

芯片纵向结构设计是在选择合适的衬底掺杂浓度的基础上,重点考虑与之对应的缓冲层和集电极设计。缓冲层的引入能够大幅度降低IGBT芯片厚度,在有效降低通态损耗的同时又降低开关损耗。缓冲层的设计在保证足够的耐压基础上,要兼顾IGBT的关断能力与短路电流耐量的协调。关断过程要处理好基区载流子的快速抽取以及载流子抽取过程中避免触发寄生PNPN晶闸管导通而使IGBT闩锁。空穴注入效率由集电极区结构及缓冲层结构共同决定。

前面已经讨论过降低背面集电极注入效率和PNP晶体管增益apnp可以提高IGBT的关断能力,从而扩大IGBT的RBSOA。但从IGBT体内电场演变来看,短路时载流子在电场的作用下会形成电流集中,电场峰值从阻断状态下位于发射极区一侧转移到集电极区一侧,此时提高背面空穴注入效率可以增加靠近集电极区域内的总载流子浓度,拉低电场峰值,从而提高短路能力[12]。

大尺寸芯片采用多重缓冲层结构,即在常规缓冲层和集电极区之间增加一个或多个薄缓冲层,如图4所示,实现了空穴注入效率与电场调节的解耦,对导通损耗、关断损耗、短路能力及开关特性软度可独立调控,在确保IGBT关断能力的同时,降低芯片的功耗与边缘漏电流,提高短路安全工作区性能。

图4 增强型受控缓冲层

Fig.4 Controlled buffer layer for injection enhancement

集电极结构设计方面,在芯片元胞区所对应的集电极区部分采用较高浓度掺杂,而与芯片终端区所对应的集电极区部分则采用较低浓度掺杂,如图5所示,有效控制背面集电极区空穴注入效率,减少器件关断时的少子抽取时间,从而改善芯片关断时的拖尾电流,大大提高芯片的开关速度。

图5 横向变掺杂集电极

Fig.5 The collector for the variation of lateral doping structure

通过上述集电极变掺杂与多重缓冲层相结合的IGBT芯片纵向结构设计,结合芯片正面U形元胞及载流子存储层设计,优化了体内载流子分布,通过载流子存储层抬高了正面空穴浓度,通过集电极局部空穴注入控制技术降低了背面空穴浓度,通过多重缓冲层的设计优化了短路电流能力,从而协调了通态损耗、关断损耗[13]与短路电流能力之间的矛盾,大大提高了元胞的鲁棒性。

高压IGBT芯片终端结构直接影响IGBT的耐压能力和漏电性能。高温下,由于终端界面态引起电荷集中,漏电急剧增加,导致IGBT耐压能力与稳定性下降。高可靠性终端结构,一方面取决于边缘终端设计,应尽可能降低边缘电场强度;另一方面,要优化终端钝化工艺,处理好终端界面电荷积累引起的漏电问题。

由于PN结弯曲或PN结终止处表面非理想因素的影响,反偏PN结击穿电压受限于表面附近或弯曲处局部电场,相对于体内平面结可能会提前出现击穿现象,因此必须设计高可靠性终端结构,降低局部电场,提高表面击穿电压及电压稳定性,使高压IGBT芯片终端击穿电压接近于体内平面结的耐压水平,确保IGBT芯片电压稳定性及抗过电压能力。

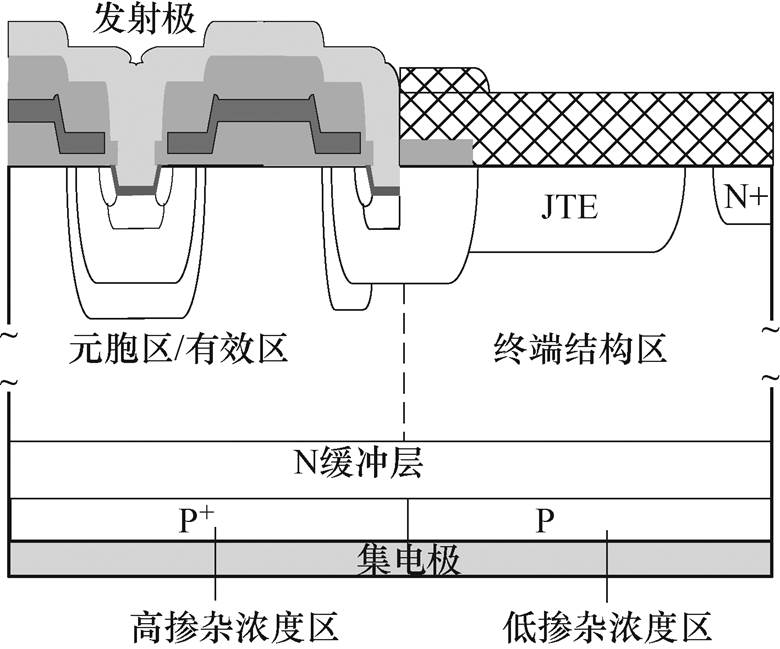

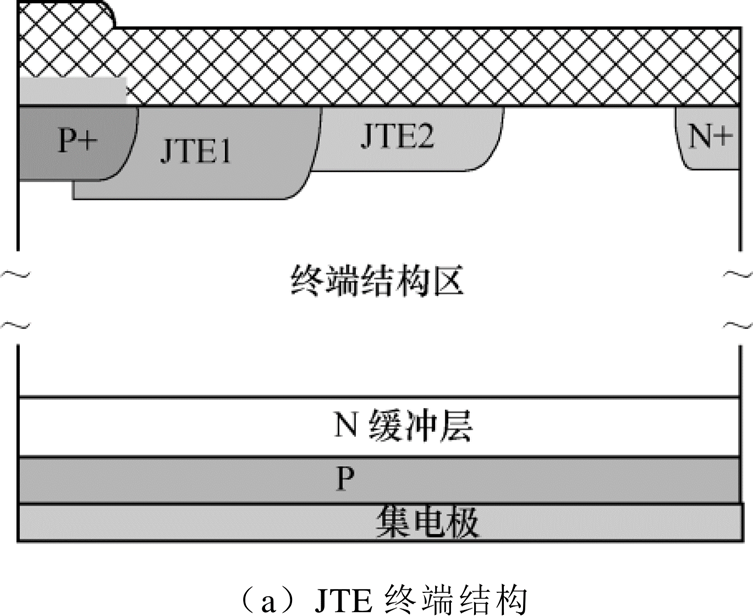

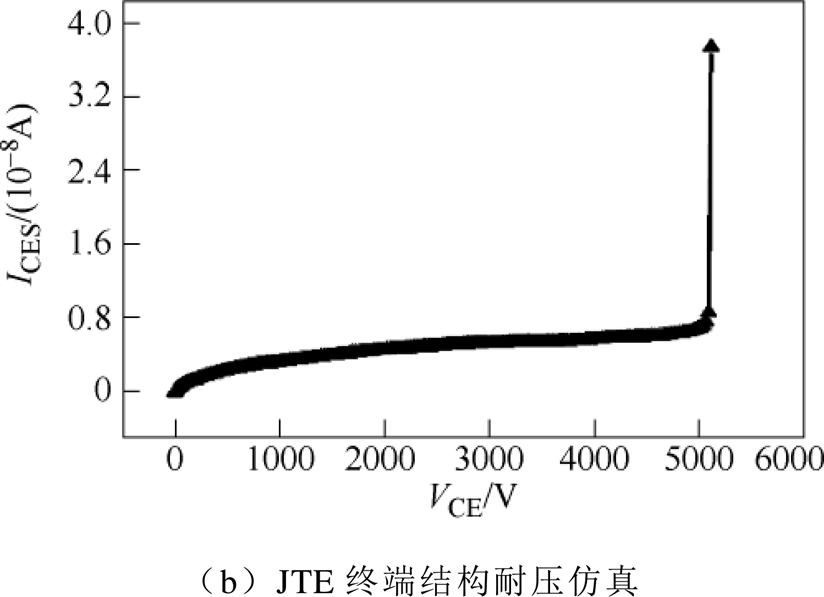

高压IGBT导通时,终端区内存在大量的载流子;关断时,这些载流子“涌向”终端区边缘,造成电流局部聚集并发生动态雪崩,终端区边缘的电场集中会进一步加剧雪崩发生和终端失效。4 500V大尺寸IGBT芯片采用两级结终端扩展(Junction Termination Extension, JTE)设计,如图6a所示。

为了进一步改善终端区的电场分布,在上述两级结终端扩展的基础上,引入P+总线结构,如图6a所示。在导通时,P+总线对于发射极的电子注入相当于一个势垒,能够降低IGBT导通时的电子注入效率,从而减少终端区内的载流子浓度,降低关断时终端区边缘的局部电流密度;在关断时,P+总线作为一个等电位环,为空穴提供快速抽取通道,进一步减轻了载流子局部聚集;通过P+总线环绕边缘元胞并将其引出至芯片正面并与发射极金属电极相连的设计,改善了芯片有效区边缘的欧姆接触和电场,确保芯片边缘电势均匀分布,抑制了终端区边缘的动态雪崩,提升终端区的关断电流能力。此外,通过P+总线覆盖栅电极下方的设计,保护并防止栅极区下方区域在反向耐压时的耗尽及反型,提高反向耐压性能,并提高IGBT抗闩锁能力。TCAD仿真结果显示,终端结构在常温下的雪崩电压近5 100V,如图6b所示。

图6 4 500V IGBT终端结构及耐压仿真结果

Fig.6 The termination structure and withstanding voltage simulation for 4 500V IGBT

P+总线与P环工艺同时完成,不会增加额外的工艺成本。边缘终端钝化选择半绝缘含氧多晶硅(Semi-Insulating Polycrystalline Silicon, SIPOS)作为终端保护薄膜,通过对淀积温度、氧含量等工艺参数的精确控制,实现了SIPOS结构中SiO2、无定形硅、多晶硅等多种微晶的均匀分布,提升了微晶间相互转化的激活能,提高了SIPOS薄膜的稳定性,降低了界面电荷。4 500V IGBT芯片[14]在125℃的高温漏电低至0.7mA,在2 800V电压下的关断电流为额定电流的6.75倍,证明4 500V高压IGBT芯片不仅有非常稳定的边缘终端,而且RBSOA能力也很强。

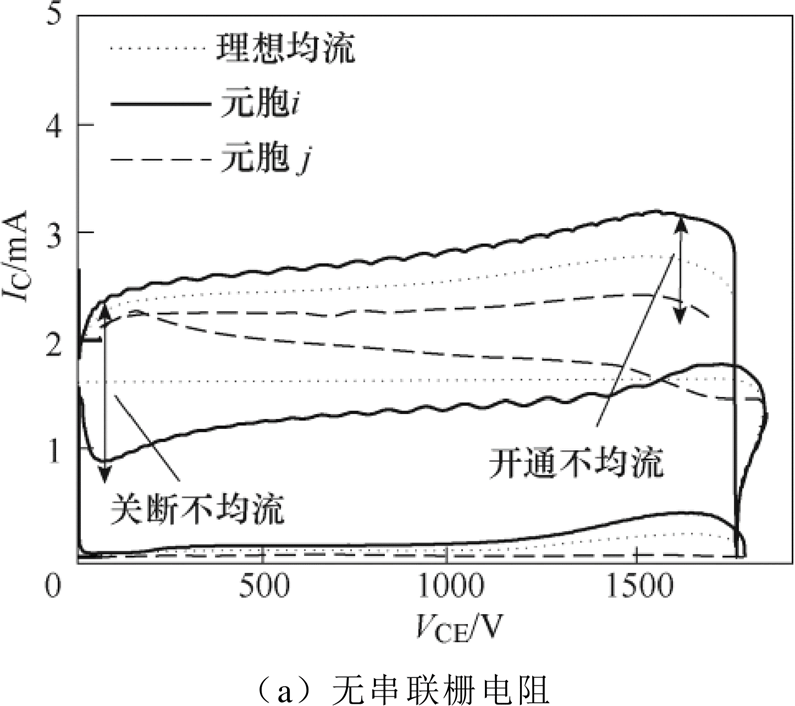

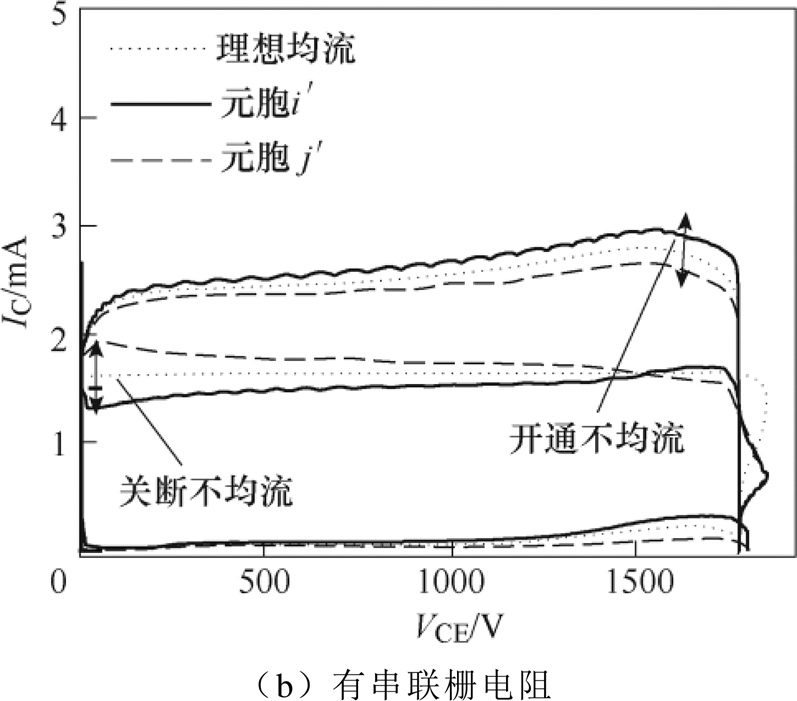

IGBT芯片通过元胞并联来实现大电流容量,元胞间分布参数不均匀会导致开关同步问题,从而引起元胞之间不均流,影响其电流输出能力。常规IGBT芯片[15]因多晶硅栅互连引入的RC网络导致信号延迟,随着元胞与芯片中心栅焊盘距离的增大,内部多晶硅电阻与互连电容增加,并联IGBT元胞的互连延迟更大,会引起元胞开关不同步,尤其是在开关瞬态和短路工况,寄生电阻与电容是IGBT元胞之间电流不均衡的主要影响因素。

大尺寸芯片集成了更多元胞,元胞在芯片中的位置不同,制造工艺的不均匀性会造成元胞之间的不均匀性,元胞开关同步将面临更大的技术挑战。并联元胞不均流主要是寄生电阻产生延迟导致的栅极驱动信号不同步和工艺不均匀引起的元胞之间的差异两方面的因素造成的。为了压缩常规并联元胞之间栅极信号延迟、改善元胞开关同步和均流状况,引入元胞栅电阻结构[16],IGBT元胞栅电阻和低时延栅极互连结构如图7所示。

图7 IGBT元胞栅电阻和低时延栅极互连结构

Fig.7 IGBT cell gate resistor and its interconnect structure for low time-delay

利用硅化钛与多晶硅工艺来实现元胞栅电阻结构,可以减小并联元胞间的时间常数差异,改善开关一致性和元胞级均流。在降低芯片内部寄生的分布电阻方面,在原来只在母排上进行光刻与刻蚀以将多晶硅栅引出的基础上,还在每个元胞的最外围处设置光刻窗口,对多晶硅栅上的SiO2进行刻蚀,然后进行钛化(TiSix)处理,再覆盖一层氧化层,形成浮动电极,结合低电阻硅化钛工艺,实现元胞栅极互连,确保了驱动信号同步;引入多晶硅元胞栅电阻,实现开关时间的精确控制,确保元胞开关过程中的均流,提高芯片最大关断电流及短路电流的耐受能力。

采用低阻硅化钛网络实现元胞之间栅极信号互连,通过降低互连寄生电阻、减小栅极信号在每一个并联元胞驱动信号延迟,从而确保每一个元胞开关信号同步;在每一个元胞栅极设计一个适当大小的多晶硅电阻,改善元胞动态均流、抑制电流电压过冲及振荡,元胞栅电阻对元胞均流的影响如图8所示,从而提高整个IGBT芯片最大关断电流及短路电流耐受能力[6]。

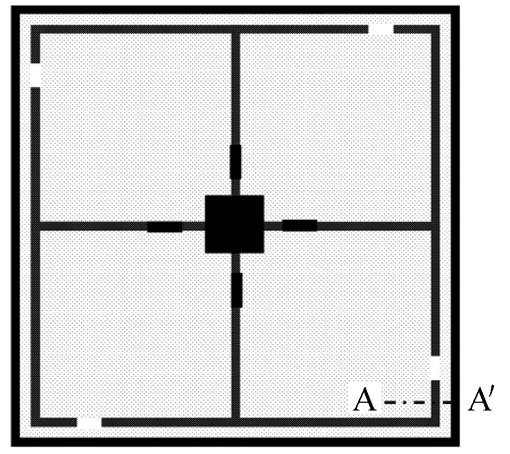

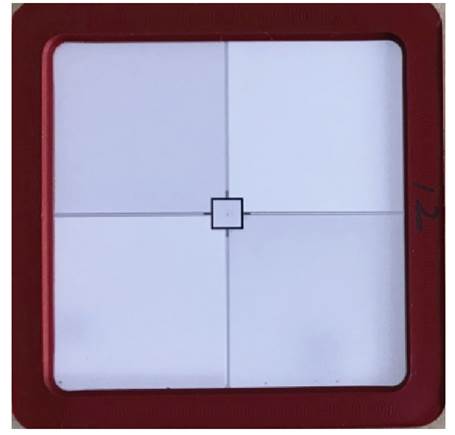

基于8in高压IGBT芯片生产线及其低温缓冲层、基-射自对准和抗应力侧墙、SIPOS钝化为核心的IGBT成套工艺[17],采用DMOS+ U形元胞设计、双面载流子协同控制技术,在21mm×21mm角栅IGBT芯片光刻掩膜基础上,通过光刻拼版的方法[18]成功地完成了42mm×42mm中心栅极IGBT芯片的研制,光刻掩膜4×90°旋转拼版效果如图9所示。终端钝化在常规SIPOS+聚酰亚铵(Polyimide, PI)的基础上,增加红胶保护,一方面进一步增强终端钝化效果和边缘爬电距离;另一方面红胶固化后可以作为封装上钼片的定位圈,如图10所示。此芯片的额定电压和电流分别达到4 500V和600A。

图8 元胞栅电阻对元胞均流的影响

Fig.8 The influence of cell current-sharing on cell gate resistor

图9 光刻掩膜4×90°旋转拼版效果

Fig.9 The effect of lithography masking at 90-degree rotate for 4 times

图10 42mm×42mm IGBT芯片

Fig.10 42mm×42mm IGBT chip

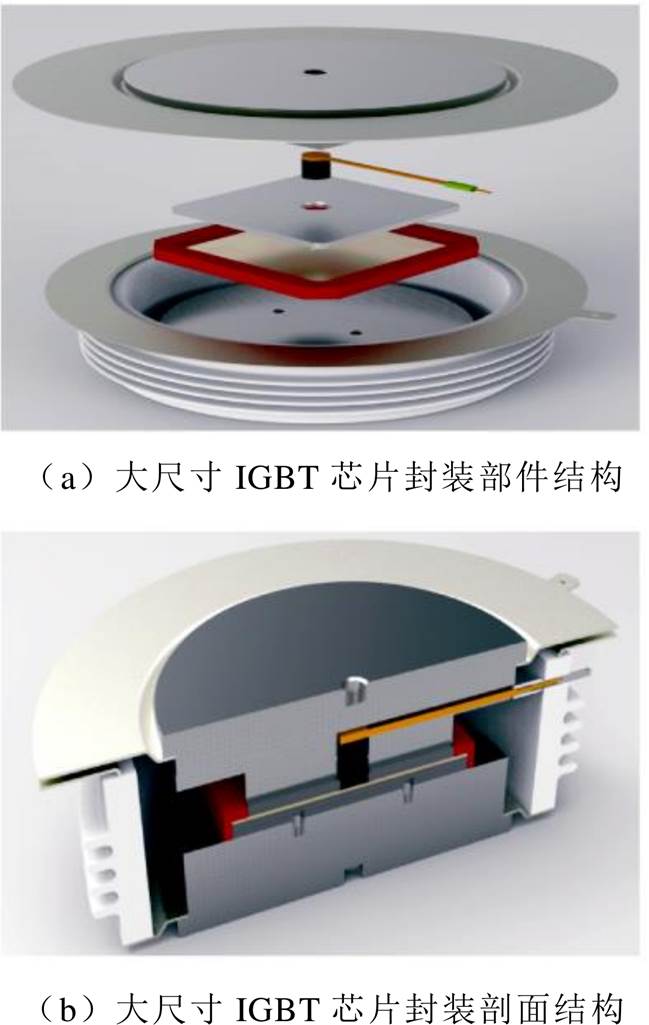

大尺寸IGBT芯片,采用压接封装技术,完成4 500V/600A IGBT产品的试制,4 500V/600A大容量IGBT器件如图11所示。其封装部件示意图及剖面结构如图12所示。

图11 4 500V/600A大容量IGBT器件

Fig.11 IGBT device with a capacity of 4 500V/600A

图12 大尺寸IGBT单芯片压接封装结构

Fig.12 Packaging structure of large size IGBT chip

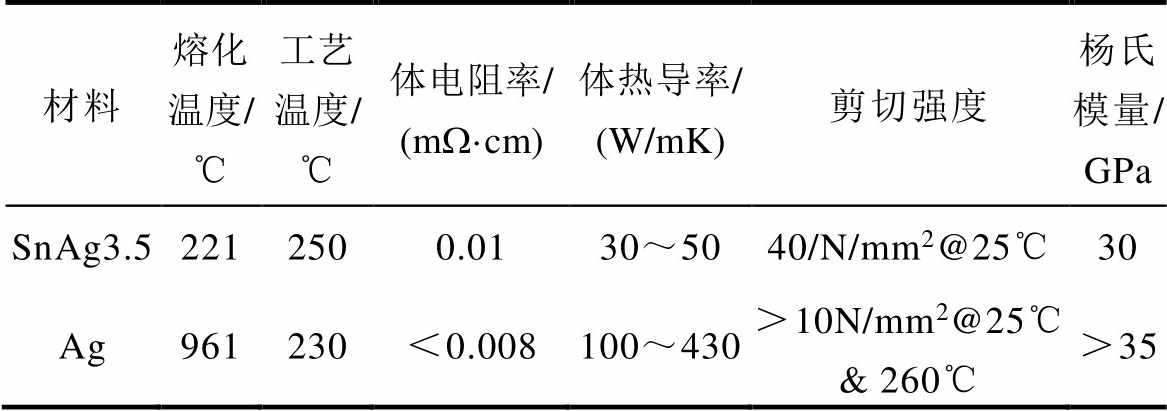

为了充分发挥大尺寸IGBT芯片的性能,可以将42mm×42mm芯片与同尺寸钼片焊接在一起,以增强芯片的机械强度。另外,鉴于传统焊料在运行过程中的疲劳会使焊层退化,增加焊层热阻并使芯片结温升高,从而影响芯片的使用寿命。低温银烧结技术[19]能够较好地解决此问题,它利用钠米或微米银取代传统焊料,在一定压力和较低的温度下实现IGBT芯片与陶瓷衬板或钼片互连。与传统焊料(SnAg3.5)相比,焊接温度低、焊接强度高、焊层阻抗低[20],SnAg3.5焊料与Ag烧结材料特性比较见表1。由于焊接温度低,低温银烧结技术在大尺寸芯片互连方面具有更大优势,不仅可以大大提高焊层的导热、导电性能,而且可以降低异质材料因热膨胀系数失配带来的芯片形变和应力,均匀控制焊层的厚度,这对大尺寸芯片的封装尤其是压接封装是至关重要的,可以明显提升芯片的使用寿命。

表1 SnAg3.5焊料与Ag烧结材料特性比较

Tab.1 Comparison of properities between SnAg3.5 solder and silver sintering materials

材料熔化温度/℃工艺温度/℃体电阻率/ (mW·cm)体热导率/ (W/mK)剪切强度杨氏模量/ GPa SnAg3.52212500.0130~5040/N/mm2@25℃30 Ag961230<0.008100~430>10N/mm2@25℃& 260℃>35

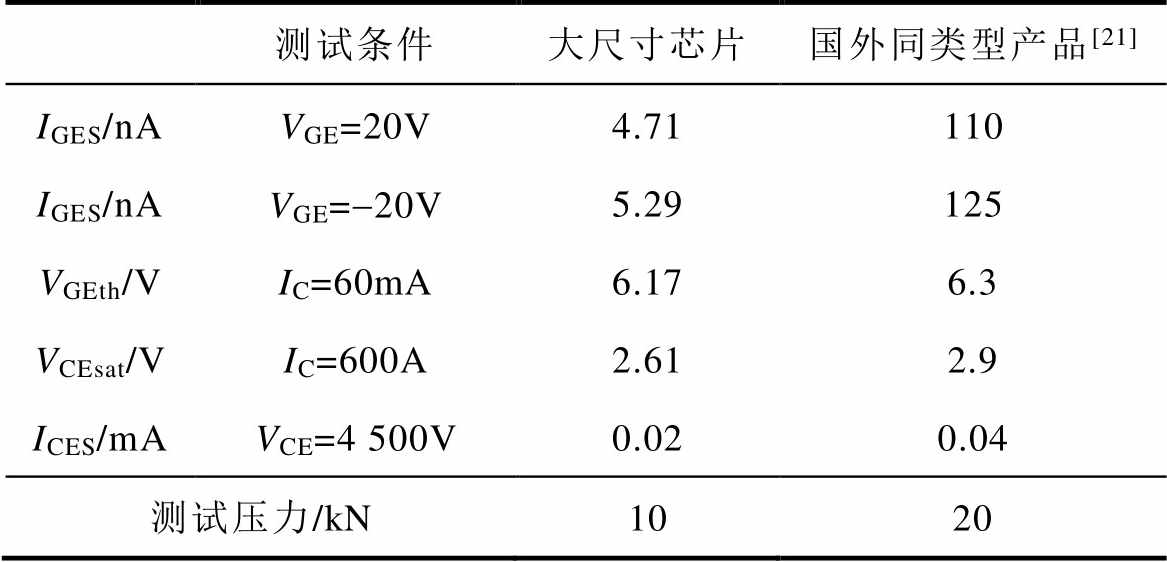

利用压接封装好的大尺寸IGBT芯片(4 500V/ 600A),分别进行了静态、动态、安全工作区和极限能力测试,并和国外同类型产品进行了性能上的对比。

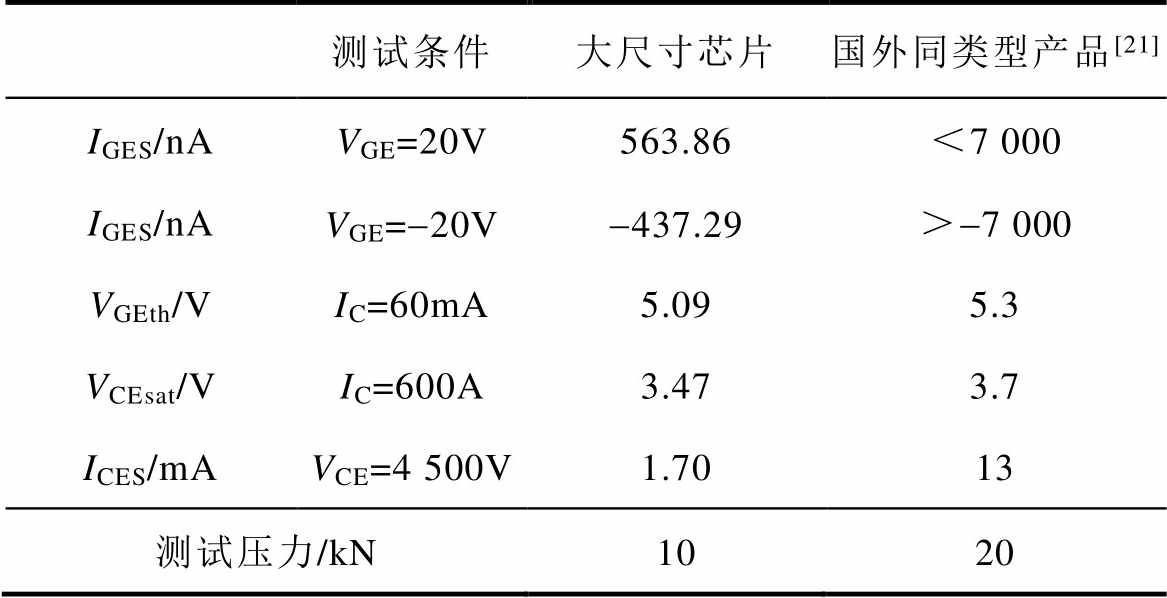

大尺寸芯片在常温和高温下的静态性能分别见表2、表3,Westcode相同容量压接型器件产品T0600TB45A(4 500V/600A)[21]是由12个小IGBT芯片并联封装而成,其参数在此一并列出以便于比较。

表2 常温(25℃)静态测试

Tab.2 Static testing data under room temperature (25℃)

测试条件大尺寸芯片国外同类型产品[21] IGES/nAVGE=20V4.71110 IGES/nAVGE=-20V5.29125 VGEth/VIC=60mA6.176.3 VCEsat/VIC=600A2.612.9 ICES/mAVCE=4 500V0.020.04 测试压力/kN1020

可以看出,和国外同类型产品相比,大尺寸IGBT芯片的饱和压降(VCEsat)在常温和高温下分别低0.29V(10%)和0.23V(6.2%)。栅极阈值电压(VGEth)相当,但大尺寸芯片的栅极-发射极间漏电流(IGES)比国外同类产品要低一个数量级。值得一提的是,大尺寸芯片的集电极-发射机间漏电流(ICES)比国外产品也要低近一个数量级,主要原因在于,和由多个小芯片并联达到同等电流等级相比,大芯片的终端面积相比小芯片的终端面积之和大幅度减少,边缘终端漏电流的贡献大大减少,从而有效抑制了ICES。对大尺寸芯片分别进行了常温和125℃高温测试,其雪崩击穿电压分别为5 075V和5 400V左右,在额定电压(4 500V)下高温漏电流低于0.5mA,说明大芯片边缘终端设计和钝化性能优良,耐压稳定性好。

表3 高温(125℃)静态测试

Tab.3 Static testing data under high temperature (125℃)

测试条件大尺寸芯片国外同类型产品[21] IGES/nAVGE=20V563.86<7 000 IGES/nAVGE=-20V-437.29>-7 000 VGEth/VIC=60mA5.095.3 VCEsat/VIC=600A3.473.7 ICES/mAVCE=4 500V1.7013 测试压力/kN1020

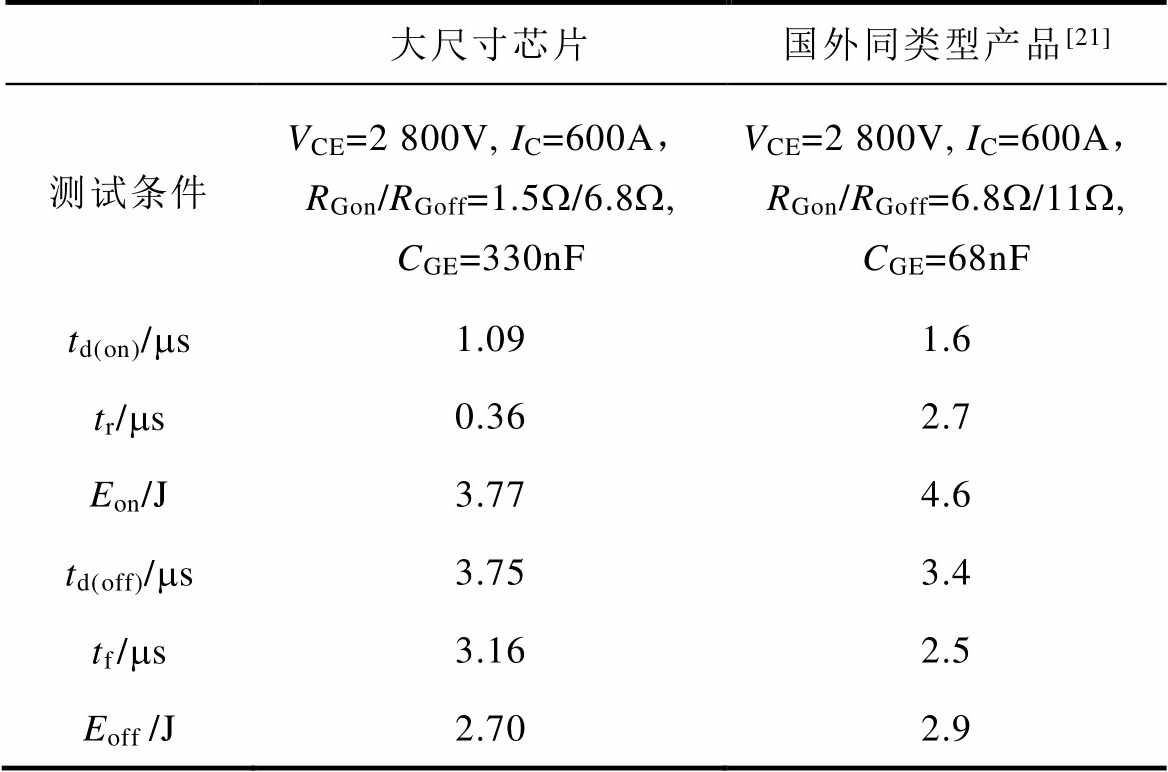

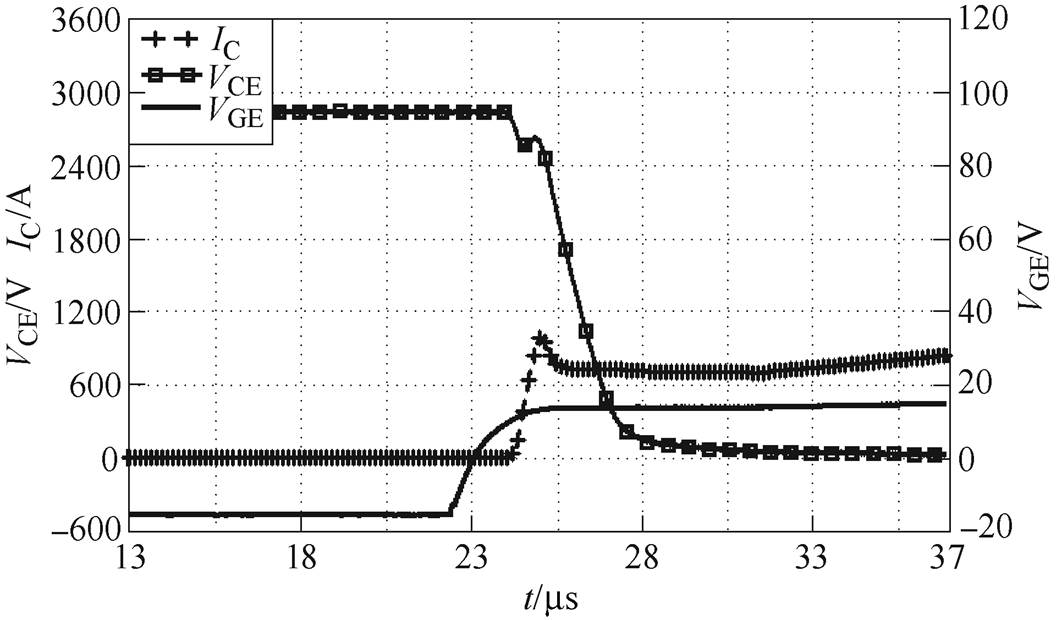

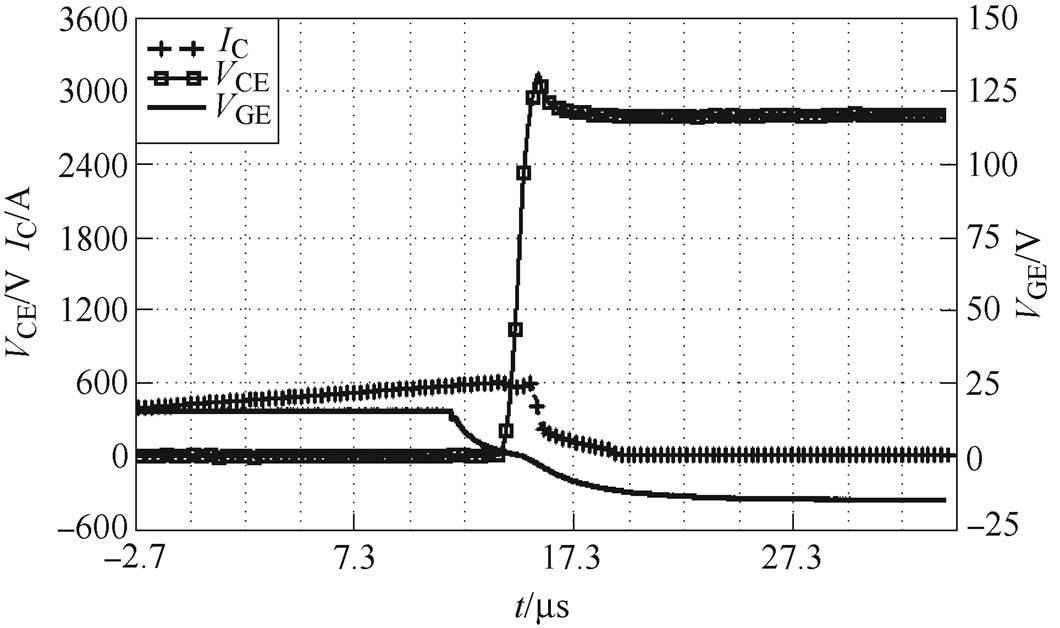

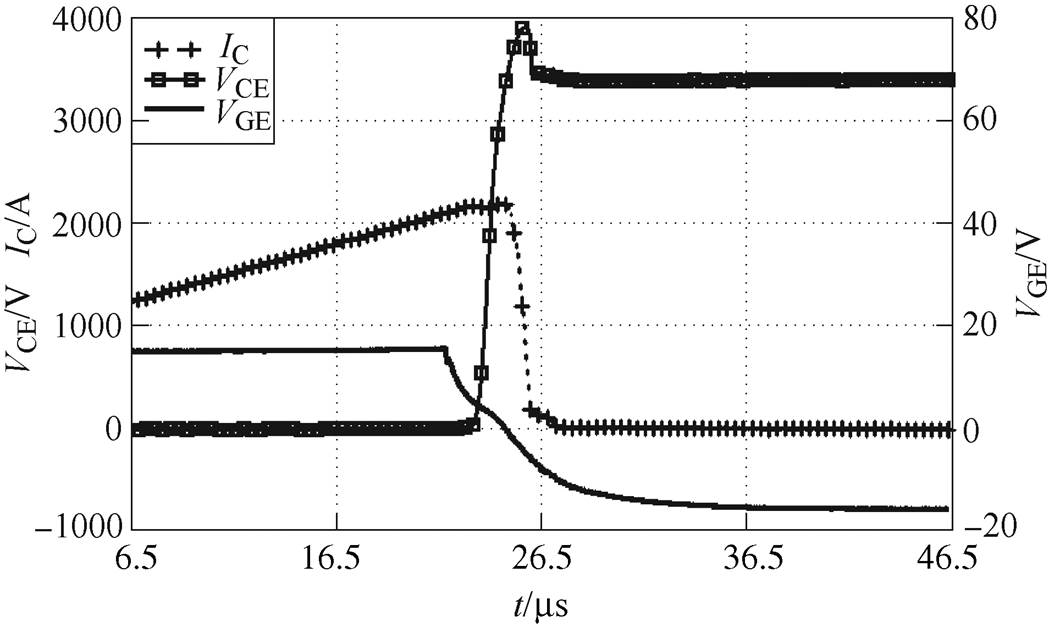

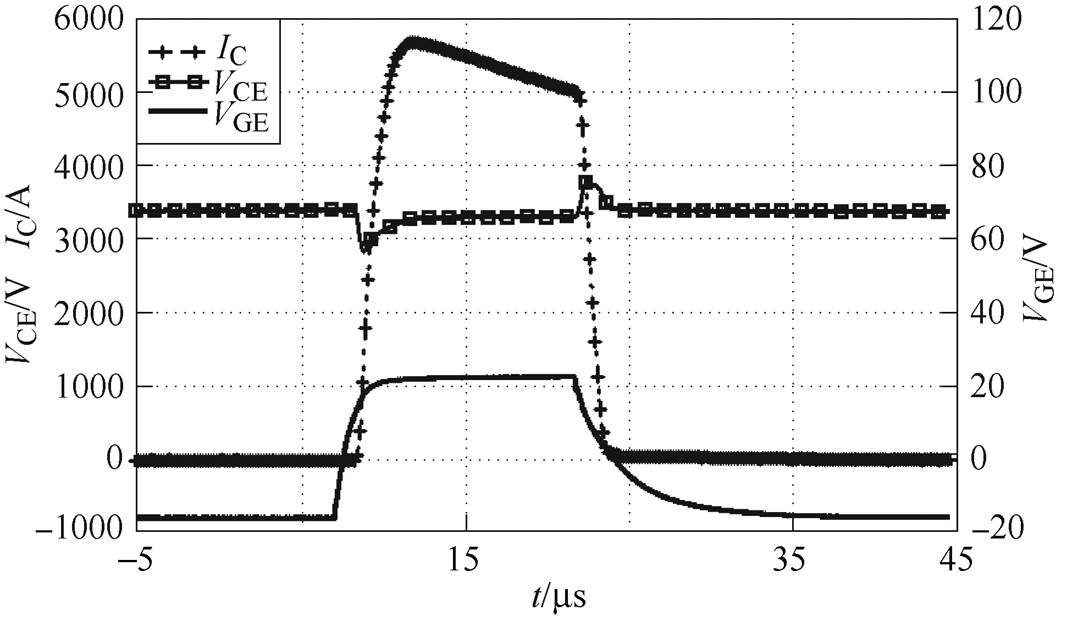

表4对比了大尺寸IGBT芯片和国外同类型产品的高温动态性能。可以看出,大尺寸IGBT芯片的开通时间包括开通延迟时间(td(on))和上升时间(tr)都比国外同类型产品要低,而开通损耗(Eon)主要产生在这段时间,这也就解释了为什么大尺寸芯片的Eon比国外产品要低0.83J(18%)。图13展现了大尺寸IGBT芯片高温下的开通波形动态。关断波形动态如图14所示。其中,RGon为开通电阻,RGoff为关断电阻,CGE为栅电容。考虑到大尺寸芯片的均流要求,芯片的软开关特性有一定程度的增强,所以关断波形中能看出有一定的拖尾电流,所以大尺寸芯片的关断时间包括关断延迟时间(td(off))和下降时间(tf)比同类型产品要长,但大尺寸芯片的关断损耗却相对低0.2J(7%),是因为在关断过程中的过冲电压很低,如图14所示。这也意味着大尺寸芯片有更宽的安全工作区,确保对应过程中有足够的电压余量应对可能出现的未知电路异常。

表4 大尺寸IGBT高温(125℃)动态参数测试数据

Tab.4 Dynamic testing data of large size IGBT under high temperature (125℃)

大尺寸芯片国外同类型产品[21] 测试条件VCE=2 800V, IC=600A,RGon/RGoff=1.5W/6.8W, CGE=330nFVCE=2 800V, IC=600A,RGon/RGoff=6.8W/11W, CGE=68nF td(on)/ms1.091.6 tr/ms0.362.7 Eon/J3.774.6 td(off)/ms3.753.4 tf/ms3.162.5 Eoff /J2.702.9

图13 125℃下典型开通波形

Fig.13 Typical turn on waveforms under 125℃

图14 125℃下典型关断波形

Fig.14 Typical turn off waveforms under 125℃

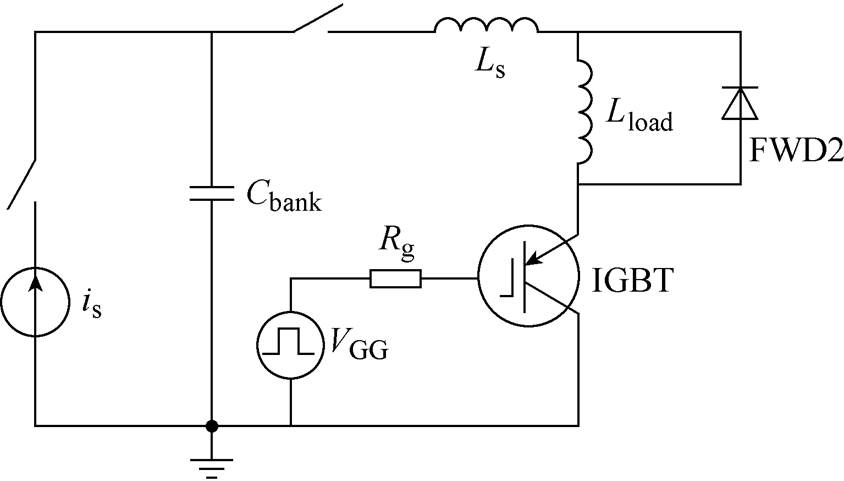

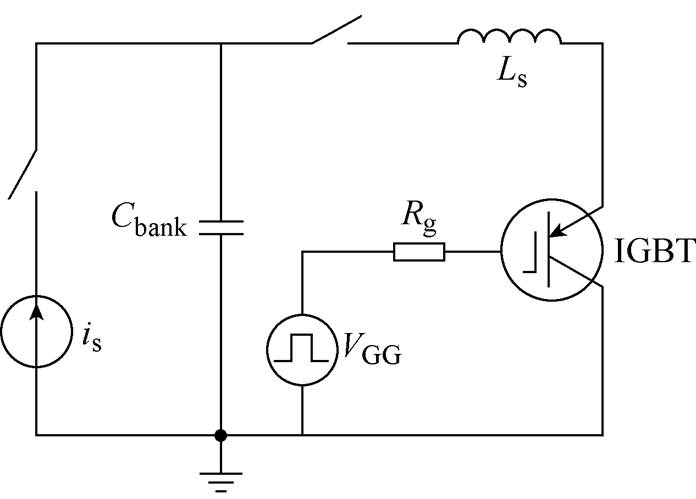

大尺寸IGBT芯片同时还进行了RBSOA和短路安全工作区(Short Circuit Safe Operation Area, SCSOA)的极限能力测试。其测试电路原理分别如图15和图16所示。图中,VGG为栅电压,Rg为栅电阻,FWD2为反并联二极管,Lload为负载电感,Ls为寄生电感,Cbank为测试源电容,is为测试源电流。

图15 RBSOA测试电路原理

Fig.15 Schematic view of electrical circuit used for RBSOA

图16 SCSOA测试电路原理

Fig.16 Schematic view of electrical circuit used for SCSOA

图17 大尺寸IGBT芯片125℃下关断3.7倍额定电流

Fig.17 Turn off at 3.7 times rating current under 125℃

图17显示大尺寸IGBT芯片在125℃高温,VCE=3 400V条件下关断3.7倍额定电流的波形。ABB半导体公司曾在文献[22]里报道过40A/4 500V压接型IGBT单芯片能够在125℃高温下VCE=3 600V时关断3倍额定电流,但在关断过程中已发生动态雪崩并触发了开关自钳位效应(Switching Self Clamping Mode, SSCM),过冲峰值电压达到近5 500V,所以关断波形中出现了振荡现象。而大尺寸芯片额定电流是ABB同类产品的15倍,在关断3.7倍额定电流条件下过冲峰值电压还不到4 000V。虽然ABB的VCE要高200V,但大尺寸芯片的优势还是很明显的。

基于图16所示的测试电路,大尺寸IGBT芯片顺利通过VGE=23V、VCE=3 400V极限条件下9.5倍额定电流(短路峰值电流ISCpeak=5 731A)高温短路能力测试,具备非常优异的动态开关特性,波形如图18所示。ABB小尺寸芯片(4 500V/40A)[22]通过常温、VGE=17.5V条件下10倍额定电流极限短路能力测试,但其关断过冲电压已经超过4 500V且VCE曲线出现振荡。而大尺寸芯片(4 500V/600A)过冲时电压才3 800V左右,且曲线圆滑,没有振荡,显示出非常坚强的鲁棒性和动态均流能力,抗动态闩锁能力也很强。

图18 VGE=23V下短路测试波形(125℃)

Fig.18 Short-circuit testing waveforms under 125℃ and VGE=23V

从应用层面讲,增大IGBT芯片面积,提高单芯片电流容量,可以简化芯片封装结构,改善并联芯片之间的均流状况,进一步提高IGBT及其封装器件功率密度与应用可靠性。

大尺寸IGBT芯片在应用层面可以减少芯片并联数,但在芯片内部则需要大幅度提高并联元胞集成度,面临更加苛刻的大规模元胞开关同步与均流难题。作为大功率IGBT模块功能单芯片化的一次尝试,作者试图通过微观层面的技术创新优化IGBT宏观应用层面的多芯片并联问题。

本文基于U形元胞及其载流子存储层设计、多重缓冲层结合横向变掺杂集电极设计实现了正背两面载流子注入的协同控制,高压IGBT通态损耗、关断能力与短路电流耐量得以同步优化,元胞鲁棒性更强;通过元胞栅电阻及低阻硅化钛互连网络设计创新,实现了元胞之间的开关同步和电流均衡;依托先进8in IGBT芯片制造成套工艺、光刻拼版与多重曝光技术,完成了42mm×42mm芯片制造;通过压接封装技术,实现了IGBT芯片的双面散热、失效短路、低感互连和长期可靠工作。探索出一整套大尺寸IGBT芯片设计、制造与封装技术。

通过对大尺寸4 500V/600A IGBT芯片进行系统的不同温度下的静、动态和安全工作区极限能力测试验证,并和国外同类产品进行比较,显示出大尺寸芯片元胞间的均流状况得到了很好的调控,保证了单个大芯片提供大电流的能力,在通态损耗、关断损耗与短路电流能力三者折中关系上明显优于常规设计和国外同类产品。就单芯片性能对比来说,大尺寸4 500V/600A IGBT芯片在RBSOA和SCSOA极限能力上也优于国外小尺寸4 500V/40A压接型IGBT芯片。

大尺寸IGBT芯片不仅适用于单芯片封装,也适应多芯片焊接和压接封装,组成各种电路结构的IGBT器件;设计开发更大尺寸、更大功率容量的IGBT芯片,封装结构将得到进一步简化,功率密度和功率容量也有望得到进一步提高。

本文展示了大尺寸芯片实现常规设计10倍以上、近50万个高压IGBT元胞的集成,较好地解决了大规模集成元胞之间的开关同步与均流问题,且具备进一步提高元胞集成度、芯片电流容量的能力。显示大尺寸芯片设计与制造技术对于提高单芯片电流、简化大容量器件封装结构具有光明的发展前景。

参考文献

[1] 丁荣军, 刘国友. 轨道交通用高压IGBT技术特点及其发展趋势[J]. 机车电传动, 2014(1): 1-6.

Ding Rongjun, Liu Guoyou. Technical features and development trend of high-voltage IGBT for rail transit traction application[J]. Electric Drive for Locomotives, 2014(1): 1-6.

[2] 刘国友, 黄建伟, 覃荣震, 等. 智能电网用高功率密度1500A/3300V绝缘栅双极晶体管模块[J]. 中国电机工程学报, 2016, 36(10): 2784-2792.

Liu Guoyou, Huang Jianwei, Qin Rongzhen, et al. High power density 1500A/3300V insulated gate bipolar transistor module for smart grid application[J]. Proceedings of the CSEE, 2016, 36(10): 2784-2792.

[3] 刘国友, 罗海辉, 李群锋, 等. 轨道交通用750A/ 6500V高功率密度IGBT模块[J]. 机车电传动, 2016(6): 21-26.

Liu Guoyou, Luo Haihui, Li Qunfeng, et al. 750A/ 6500V high power density IGBT module for rail transit application[J]. Electric Drive for Locomotives, 2016(6): 21-26.

[4] 汪波, 罗毅飞, 张烁, 等. IGBT极限功耗与热失效机理分析[J]. 电工技术学报, 2016, 31(12): 135-141.

Wang Bo, Luo Yifei, Zhang Shuo, et al. Analysis of limiting power dissipation and thermal failure mechanism[J]. Transactions of China Electrotecnical Society, 2016, 31(12): 135-141.

[5] 刘国友, 窦泽春, 罗海辉, 等. 高功率密度3600A/ 4500V压接型IGBT研制[J]. 中国电机工程学报, 2018, 38(16): 4855-4862.

Liu Guoyou, Dou Zechun, Luo Haihui, et al. Development of high power density 3600A/4500V press-pack IGBT[J]. Proceedings of the CSEE, 2018, 38(16): 4855-4862.

[6] 刘国友, 窦泽春, 罗海辉, 等. 压接型IGBT均流设计研究[J]. 中国电力, 2019, 52(9): 20-29.

Liu Guoyou, Dou Zechun, Luo Haihui, et al. Current- sharing design of press-pack IGBT[J]. Electric Power, 2019, 52(9): 20-29.

[7] 周静, 康升扬, 李辉, 等. 内部压力不均对压接式IGBT器件电热特性的影响分析[J]. 电工技术学报, 2019, 34(16): 3408-3415.

Zhou Jing, Kang Shengyang, Li Hui, et al. Simulation of influence of unbalanced clamping force on electro- thermal characteristics of press-pack IGBT devices[J]. Transactions of China Electrotecnical Society, 2019, 34(16): 3408-3415.

[8] 唐新灵, 崔翔, 赵志斌, 等. 并联IGBT芯片的等离子体抽取渡越时间振荡机理及其特性分析[J]. 电工技术学报, 2018, 33(10): 254-264.

Tang Xinling, Cui Xiang, Zhao Zhibin, et al. Mecha- nism and characteristics of plasma extraction transit time oscillation of paralleled IGBT chips[J]. Transa- ctions of China Electrotecnical Society, 2018, 33(10): 254-264.

[9] 邓二平, 赵志斌, 张朋, 等. 压接型IGBT器件内部压力分布[J]. 电工技术学报, 2017, 32(6): 201-208.

Deng Erping, Zhao Zhibin, Zhang Peng, et al. Clam- ping force distribution within press pack IGBTs[J]. Transactions of China Electrotecnical Society, 2017, 32(6): 201-208.

[10] Baliga B J. Fundamentals of power semiconductor devices[M]. New York: Springer US, 2008.

[11] 刘国友, 罗海辉, 张鸿鑫, 等. 基于全铜工艺的750A/ 6500V高性能IGBT模块[J]. 电工技术学报, 2020, 35(21): 4501-4510.

Liu Guoyou, Luo Haihui, Zhang Hongxin, et al. High performance 750A/6500V IGBT module based on full-copper process[J]. Transactions of China Electro- technical Society, 2020, 35(21): 4501-4510.

[12] Chokhawala R S, Catt J, Kiraly L. Discussion on IGBT short-circuit behavior and fault protection schemes[J]. IEEE Transactions on Industry Appli- cations, 1995, 31(2): 256-263.

[13] Wang Hengyu, Su Ming, Sheng Kuang. Theoretical performance limit of the IGBT[J]. IEEE Transactions on Electron Devices, 2017, 64(10): 4184-4192.

[14] 张大华, 马亮, 张中华, 等. 低导通损耗宽安全工作区4500V IGBT器件研制[J]. 大功率变流, 2017(5): 60-64.

Zhang Dahua, Ma Liang, Zhang Zhonghua, et al. Development of the 4500V IGBT device with low on- state loss and wide safe operation area[J]. High Power Converter Technology, 2017(5): 60-64.

[15] Long Hongyao, Sweet M R, Ngwendson Luther-King, et al. Current distribution analysis of insulated gate bipolar transistor cells[J]. Japanese Journal of Applied Physics, 2010, 49: 04DP14.

[16] 刘国友, 覃荣震, 黄建伟, 等. 一种功率半导体芯片栅电阻[P]. 中国, ZL201310259231.X.

[17] Liu Guoyou, Ding Rongjun, Luo Haihui. Deve- lopment of 8-inch key processes for insulated-gate bipolar[J]. Engineering, 2015, 1(3): 361-366.

[18] 程银华, 刘国友, 王梦洁, 等. 一种功率半导体芯片, 该芯片的光刻版及其曝光方法[P]. 中国, ZL201710325616.X.

[19] Christian G. Low temperature sinter technology die attachment for power electronic applications[C]// Chartered Institute of Procurement & Supply, Nuremberg, 2010: 1-5.

[20] Krebs T, Duch S, Schmitt W, et al. A breakthrough in power electronics reliability- new die attach and wire bonding materials[C]//IEEE Electronic Components & Technology Conference, Las Vegas, 2013: 28-31.

[21] Westcode datasheet T0600TB45A[Z]. 2011: 1-7.

[22] Eicher S, Rahimo M, Tsyplakov E. 4.5kV press pack IGBT designed for ruggedness and reliability[C]// Conference Record of the 2004 IEEE Industry Applications Conference, 39th IAS Annual Meeting, Seattle, USA, 2004: 1534-1539.

Development of Large Size IGBT Chip with High Power Capacity of 4 500V/600A

Abstract Increasing IGBT single-chip current capacity is essential for reducing the parallel number of packaged chips, simplifying the package architecture and improving the chip current sharing capability. According to the application requirements of high voltage, high current and high reliability for IGBT chips, this paper realized cell switching synchronization through robust cell design and its coordinated control, and solved the process manufacturing of large size chips through special photolithography technology. The single-chip press packaging was used to verify the design and performance of large size chips. A technical path for the design, manufacturing and verification of large size IGBT chips was explored. The world’s first 42mm×42mm large-size high-voltage IGBT chip with the power capacity of 4 500V/600A was developed. It has excellent dynamic and static characteristics, a wider safe operation area (SOA), and can significantly improve the packaging power density and reliability.

keywords:Large size IGBT chip, current capacity, current sharing, press pack

中图分类号:TN433

DOI: 10.19595/j.cnki.1000-6753.tces.191758

收稿日期2019-12-13

改稿日期 2020-02-20

刘国友 男,1966年生,教授级高工,研究方向为功率半导体及其应用。E-mail: liugy@csrzic.com(通信作者)

黄建伟 男,1962年生,教授级高工,研究方向为新型功率半导体器件。E-mail: huangjw@csrzic.com

(编辑 崔文静)