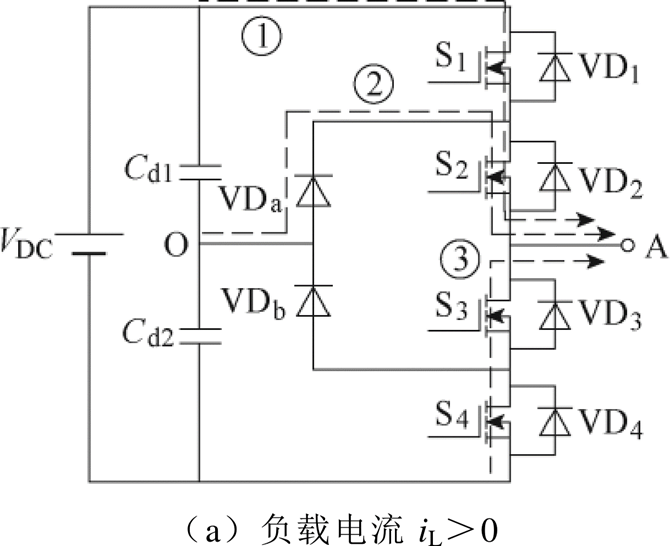

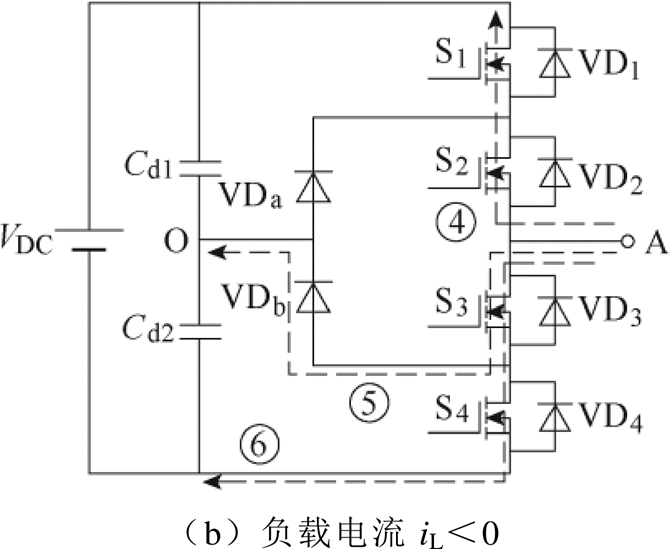

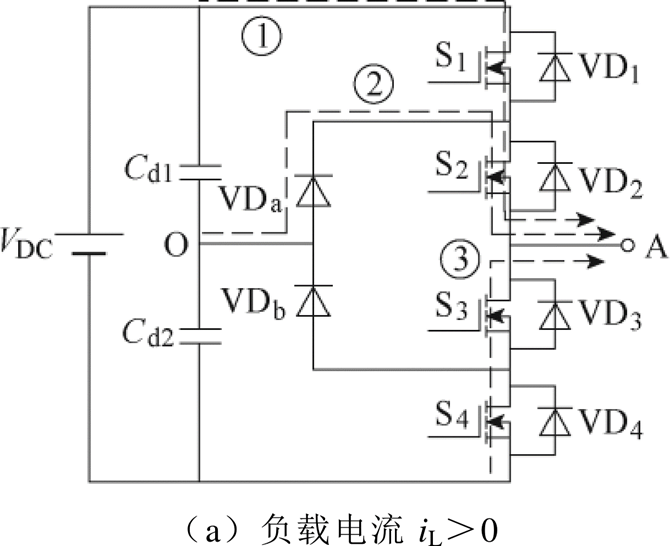

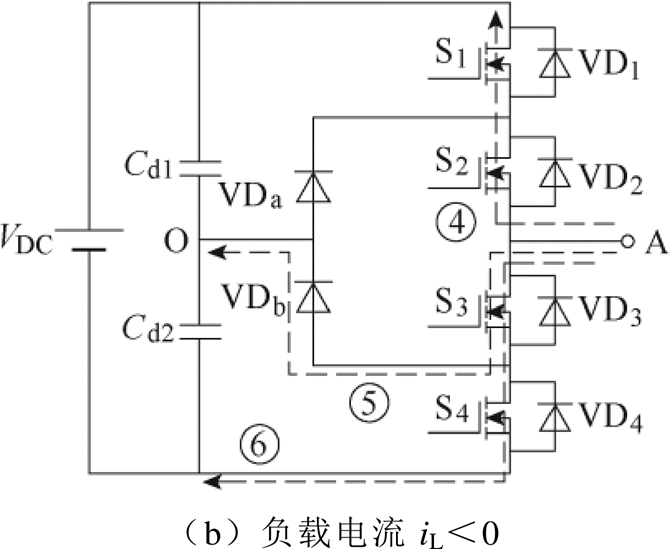

图1 NPC三电平拓扑及其正常工作状态

Fig.1 NPC three-level topology and its normal working state

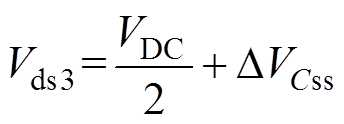

摘要 为保证SiC MOSFET在三电平拓扑中应用的可靠性,需对其进行过电压与过电流保护。该文针对短路导致的过电压情况,提出在中点钳位(NPC)拓扑中加入大电容值飞跨电容的方法,并结合短路保护,保证发生短路故障时SiC MOSFET不过电压损坏,且能快速保护关断,以减小过电流风险。通过搭建短路测试平台,验证了三电平电路发生短路故障时,大电容值飞跨电容对SiC MOSFET起到过电压保护作用,且SiC MOSFET的短路保护时间在2ms以内。

关键词:三电平 大电容值 飞跨电容 过电压保护

SiC MOSFET作为宽禁带半导体器件,与同功率等级的Si IGBT相比,具有耐高温、耐高压、散热性能好、工作频率高、开关损耗小等优点,其在高频高压的场合下有更好的应用前景[1-4]。但SiC MOSFET的短路承受时间较短[5],若电路因过载、内部驱动错误、干扰或控制不当等原因出现短路故障,此时SiC MOSFET未及时关断,将导致其短路失效,器件永久损坏[6-9]。将SiC MOSFET应用在三电平拓扑中,有利于减小功率变换器的损耗,从而提高其输出效率[10-11],但同时其短路的情况也更加复杂。发生短路故障时,SiC MOSFET若无保护措施,将因过电流或过电压而损坏。因此,三电平拓扑中SiC MOSFET的过电压与过电流保护对提高系统工作可靠性具有重要意义。

对SiC MOSFET进行短路保护(Short Circuit Protection, SCP),能够有效防止其过电流损坏[12]。主要方法有源极串电阻法[13]、杂散电感检测法[14]、门极电荷检测法[15]、退饱和法(又称DESAT法)[16]及印制电路板(Printed circuit boards, PCB)罗氏线圈法[17]等。目前最有效且应用最为广泛的短路保护方法为DESAT法与PCB罗氏线圈法。文献[18]测试了两种方法在相同短路故障下的短路保护能力,证明其均能对SiC MOSFET进行短路保护。其中,PCB罗氏线圈法虽能快速检测故障,并快速保护SiC MOSFET,但其设计相对复杂(包括线圈制作与积分电路设计),且成本较高。为降低成本,同时简化设计,本文中点钳位(Neutral Point Clamped, NPC)三电平拓扑中SiC MOSFET的短路保护采用DESAT法。

SiC MOSFET的过电压保护方法主要是在各开关管两端并联一个RCD吸收电路(即电阻、电容、二极管的组合电路),以减小开关管关断时因寄生电感存在而产生的电压过冲[19-20]。若在NPC三电平拓扑中发生短路故障,可能导致某些开关管瞬间过电压,此时RCD吸收电路不起作用,需寻求新的过电压保护方法。针对短路导致的过电压情况,本文在NPC拓扑中加入大电容值的飞跨电容,能够有效地对内管起电压钳位作用,同时避免了小电容值飞跨电容充放电速度过快所可能出现的短路过电压问题,而外管电压将由钳位二极管进行钳位。在NPC三电平拓扑的正常工作状态及可能出现的六种短路状态中,大电容值的飞跨电容均能有效地起到过电压保护作用。

综上所述,本文结合DESAT法,通过在NPC拓扑中引入大电容值的飞跨电容,简化了过电压保护电路的设计,同时对三电平拓扑中的SiC MOSFET起到过电压与过电流保护作用。本文还对NPC三电平拓扑中的短路状态进行分析,并对飞跨电容的选取方法、SiC MOSFET的驱动电路设计进行说明,确保设计电路能在各种短路故障下起到保护作用。最后,本文搭建了NPC三电平拓扑的短路测试平台,对三电平电路的短路状态进行测试,实验结果表明,所设计电路中各开关管无过电压现象,且能够在2µs内切除短路故障,验证了所设计电路的过电压与过电流保护效果。

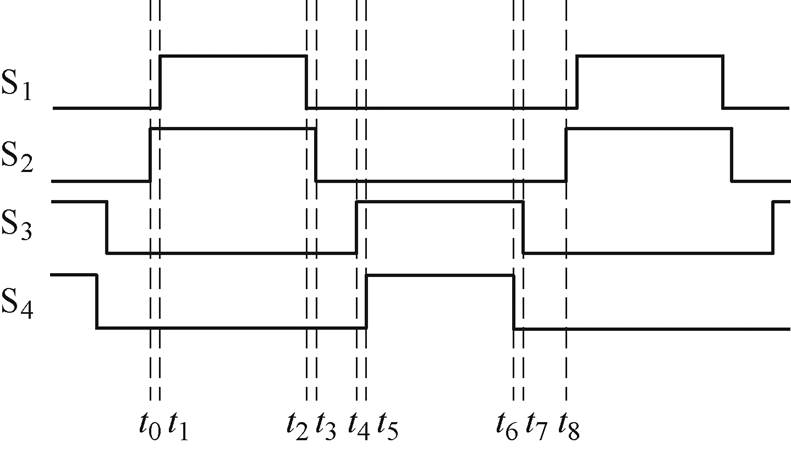

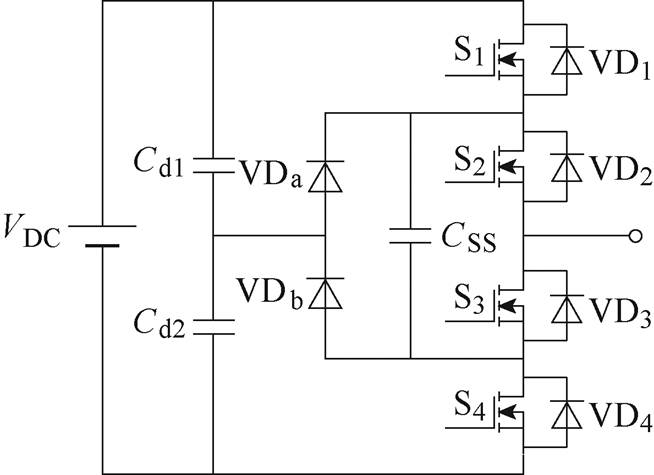

图1所示为常见的NPC三电平拓扑,常用于DC-DC变换器中,在增大电压等级的同时能够实现大功率变换。图中,VDC为直流母线电压,Cd1、Cd2为直流母线电容,S1~S4为SiC MOSFET,VD1~VD4为SiC MOSFET的体二极管,VDa、VDb为钳位二极管,iL为负载电流(设定从A点流出为正方向)。正常工作时,S1、S2驱动信号相同,S3、S4驱动信号相同,但为了避免桥臂直通的危险,内管(S2、S3)与外管(S1、S4)之间设有一定的死区时间,以满足“外管先于内管关断,内管先于外管导通”的原则。内管对(S2、S3)之间与外管对(S1、S4)之间也均设有死区。三电平拓扑的典型驱动波形如图2所示,图中,t1~t2、t3~t4、t5~t6、t7~t8为内外管死区时间,记为Td1;t0~t1、t4~t5为内管对死区时间,记为Td2;t3~t6为外管对死区时间,记为Td3。

图1 NPC三电平拓扑及其正常工作状态

Fig.1 NPC three-level topology and its normal working state

表1为NPC三电平拓扑的四种正常工作模态,分别为P模态、O1模态、O2模态、N模态。结合图1、图2可知:

图2 三电平拓扑典型驱动波形

Fig.2 Typical driving waveforms of three-level topology

表1 NPC拓扑的四种正常工作模态

Tab.1 Four working modes of NPC topology

工作模态S1S2S3S4UAO P1100VDC/2 O101000 O200100 N0011-VDC/2

(1)当iL>0时,如图1a有①②③三条电流回路。其中,P模态对应①回路,电流经S1、S2流向负载;O1模态对应②回路,电流经VDa、S2流向负载;O2模态、N模态对应③回路,电流经VD3、VD4(或S3、S4)流向负载。

(2)当iL<0时,如图1b有④⑤⑥三条电流回路。其中,P模态、O1模态对应④回路,电流经VD1、VD2(或S1、S2)从负载流入;O2模态对应⑤回路,电流经S3、VDb从负载流入;N模态对应⑥回路,电流经S3、S4从负载流入。

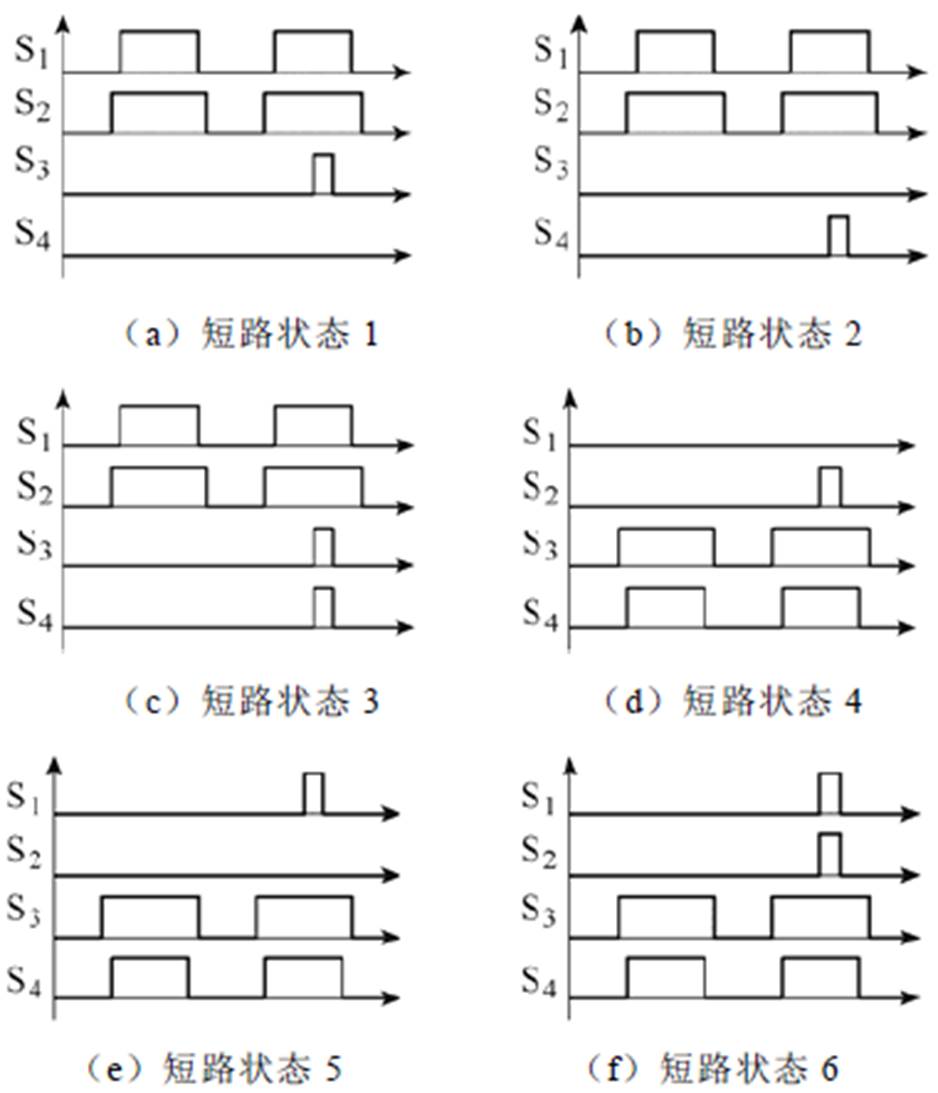

在运用NPC三电平拓扑时,尽管遵循了“外管先于内管关断,内管先于外管导通”的原则,在一定程度上避免了桥臂直通的风险。但将SiC MOSFET应用在NPC三电平拓扑中时,因SiC MOSFET的门极阈值电压低,且易受寄生参数影响,在实际工作中容易发生误导通现象[9],体现为NPC三电平拓扑中的不同短路状态。表2列出了NPC三电平拓扑可能出现的六种短路状态。表中,“0”表示开关管关断,“1”表示开关管导通,“0-1”表示开关管误导通,短路状态1、4称为内管短路,短路状态2、5称为外管短路,短路状态3、6称为桥臂直通。短路状态1~3即上桥臂开关管正常导通时,下桥臂开关管误导通造成的短路故障,短路状态4~6即下桥臂开关管正常导通时,上桥臂开关管误导通造成的短路故障(上桥臂指S1、S2,下桥臂指S3、S4)。短路状态1~3与短路状态4~6的短路情况相同,仅上下桥臂的区别,因此本文仅对短路状态1~3进行分析,短路状态4~6的分析类似,不再赘述。

表2 NPC拓扑的六种短路状态

Tab.2 Six short circuit states of NPC topology

短路状态S1S2S3S4 1110-10 21100-1 3110-10-1 400-111 50-1011 60-10-111

(1)短路状态1:S1、S2正常导通时,S3误导通,形成Cd1-S1-S2-S3-VDb-Cd2的回路,S1~S3存在过电流风险。此时S4被钳位二极管VDb所钳位,无过电压风险。

(2)短路状态2:S1、S2正常导通时,S4误导通,该状态下,S3需承受全部的母线电压,在电压等级较高时将直接过电压损坏。

(3)短路状态3:S1、S2正常导通时,S3、S4误导通,形成Cd1-S1-S2-S3-S4-Cd2的回路,S1~S4存在过电流风险。

根据上述NPC三电平拓扑短路状态的分析可以发现,在短路状态2、4时,内管因无钳位措施将瞬间过电压损坏,这对于成本较高的SiC MOSFET而言是需要避免的。因此,为了保证SiC MOSFET在NPC三电平电路中发生短路故障时,不因过电压而损坏,本文在NPC拓扑中VDa的阴极与VDb的阳极之间并联一个大电容值飞跨电容,以形成图3所示的飞跨电容型NPC拓扑,对内管的电压起钳位作用,图中,CSS即为飞跨电容。

图3 飞跨电容型NPC拓扑

Fig.3 NPC topology with flying capacitor

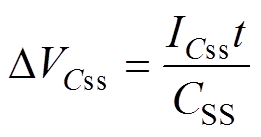

飞跨电容型NPC拓扑由F. Canales首次提出[21],将飞跨电容CSS引入NPC拓扑,有助于通过移相控制方法实现DC-DC变换器所有开关管的零电压开通(Zero Voltage Switch, ZVS),以减小开关损耗。正常运行时,CSS预充电至VDC/2,并保持稳定,对内管进行钳位,防止内管过电压损坏。同时,飞跨电容CSS还起到了平衡母线电容(Cd1、Cd2)电压的作用[22-24]。发生短路故障时,短路电流流经飞跨电容CSS,对其进行充放电,有

(1)

(1)式中,DVCss为飞跨电容电压的变化量;ICss为飞跨电容在短路期间的平均电流;t为短路持续时间。可以看出,CSS电容值越小,其两端电压的变化量越大,即充放电速度越快。

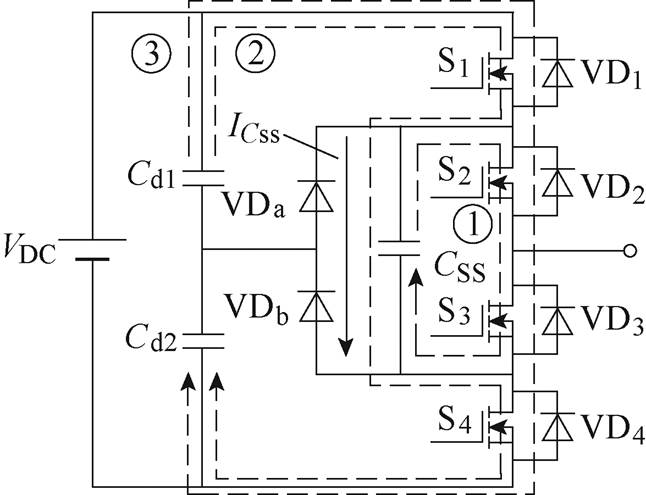

图4为飞跨电容型NPC拓扑短路故障时的短路电流回路,其中,ICss为流过CSS的电流,箭头所指方向定义为正方向。图4中,①②③为短路状态1~3的短路电流回路,分别为CSS-S2-S3-CSS、Cd1-S1- CSS-S4-Cd2和Cd1-S1-S2-S3-S4-Cd2。①回路为短路状态1的短路回路,称为内管短路回路,飞跨电容CSS放电;②回路为短路状态2的短路回路,称为外管短路回路,飞跨电容CSS充电;③回路为短路状态3的短路回路,称为桥臂直通回路,飞跨电容CSS的充放电情况需通过实验考查。

图4 飞跨电容型NPC拓扑短路电流回路

Fig.4 Short circuit current loop of NPC topology withflying capacitor

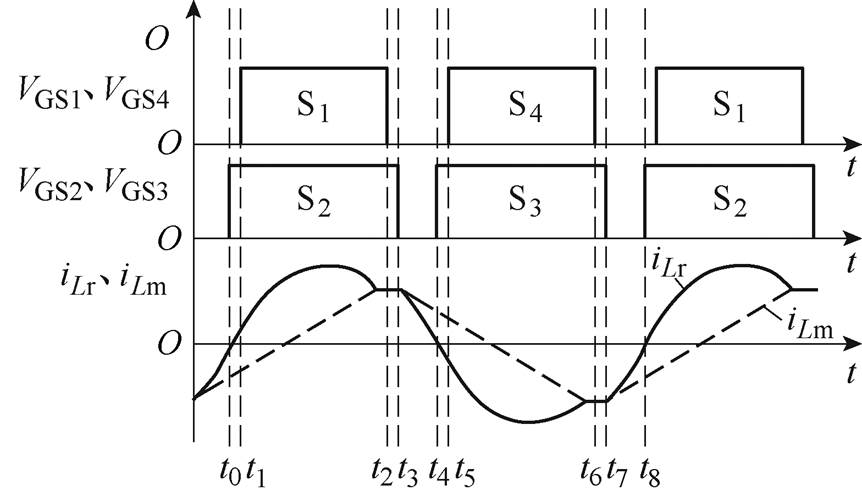

可以发现,当电路为短路状态2时,飞跨电容CSS充电,DVCss增加,则此时S3管两端电压Vds3为

(2)

(2)可知,在短路故障期间,只要保证Vds3不超过开关管的耐压值,就能避免其过电压损坏。因此选择合适电容值的飞跨电容,使得DVCss在短路期间较小,以保证在发生外管短路故障时,其电压不超过内管的击穿电压,避免内管过电压损坏;在发生内管短路时,输入电压与其电压的差值不超过外管的击穿电压,避免外管过电压损坏。同时,由于寄生电感的存在,开关管在关断时承受的最大电压会超过飞跨电容电压(飞跨电容电压加上寄生电感产生的感应电动势),因此,CSS的最大电压值在设计时应留有一定的裕量。

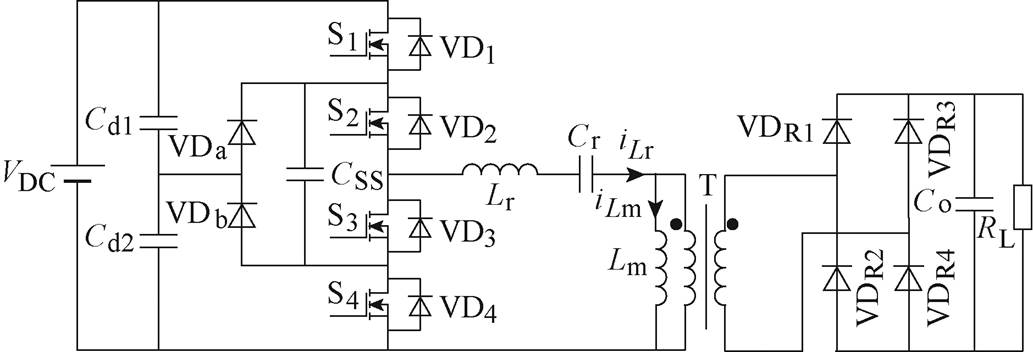

考虑到飞跨电容的引入可能会对电路的正常工作产生一定的影响,对此进行分析[25],包括飞跨电容引入对开关器件的影响以及对整个电路的影响。以半桥三电平LLC谐振变换器为例,电路如图5所示,工作波形如图6所示,其中开关频率略小于谐振频率,忽略寄生电容充放电过程[26]。图5中,Lr为谐振电感,Cr为谐振电容,Lm为励磁电感,T为变压器,VDR1~VDR4为二次侧整流二极管,Co为输出滤波电容,RL为负载电阻,iLr为谐振电流,iLm为励磁电流。

图5 半桥三电平LLC谐振变换器

Fig.5 Half bridge three level LLC resonant converter

图6 半桥三电平LLC谐振变换器工作波形

Fig.6 Working waveform of half bridge three level LLC resonant converter

[t0, t1]:t0前,谐振电流iLr为负,S1、S2的体二极管导通,电流回路为Cd2-Lm-Cr-Lr-VD2-VD1-Cd1。t0时刻,S2零电压开通,电流回路不变,谐振电流iLr由负变正后,电流回路变为Cd2-VDa-S2-Lr-Cr-Lm- Cd2,此时Lm不参与谐振,二次侧整流二极管VDR1、VDR4导通。

[t1, t2]:t1时刻,S1零电压开通,电流回路为Cd1- S1-S2-Lr-Cr-Lm-Cd2,Lm不参与谐振,二次侧整流二极管VDR1、VDR4导通。当iLr=iLm时,Lm参与谐振,二次侧整流二极管均为截止状态。

[t2, t3]:t2时刻,S1关断,电流回路变为Cd2-VDa- S2-Lr-Cr-Lm-Cd2,Lm参与谐振,二次侧整流二极管均为截止状态。

[t3, t4]:t3时刻,S2关断,电流回路变为VD3-Lr- Cr-Lm-VD4,Lm不参与谐振,二次侧整流二极管VDR2、VDR3导通。

[t4, t5]:t4前,谐振电流iLr为正,S3、S4的体二极管导通,电流回路为VD3-Lr-Cr-Lm-VD4,Lm不参与谐振,二次侧整流二极管VDR2、VDR3导通。t4时刻,S3零电压开通,电流回路不变,谐振电流iLr由正变负后,电流回路变为Cd2-Lm-Cr-Lr-S3-VDb- Cd2,此时Lm不参与谐振,二次侧整流二极管VDR2、VDR3导通。

[t5, t6]:t5时刻,S4零电压开通,电流回路为S4-Lm-Cr-Lr-S3,Lm不参与谐振,二次侧整流二极管VDR1、VDR4导通。当iLr=iLm时,Lm参与谐振,二次侧整流二极管均为截止状态。

[t6, t7]:t6时刻,S4关断,电流回路变为Cd2- Lm-Cr-Lr-S3-VDb-Cd2,Lm参与谐振,二次侧整流二极管均为截止状态。

[t7, t8]:t7时刻,S3关断,电流回路变为Cd2-Lm- Cr-Lr-VD2-VD1-Cd1,Lm不参与谐振,二次侧整流二极管VDR1、VDR4导通。

上述t1~t8时间段对电路的分析中,飞跨电容CSS未参与工作,电路处于稳定工作状态。因此,飞跨电容的引入不会影响环路稳定性。

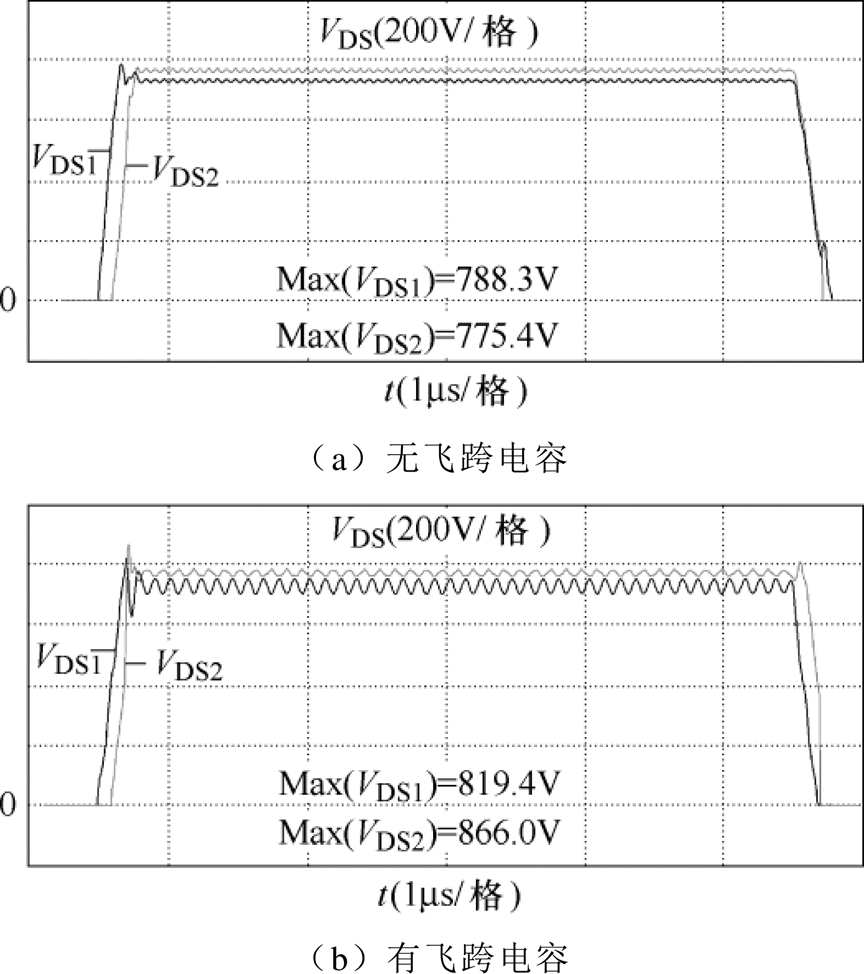

为探究飞跨电容对器件开关波形的影响,通过仿真进行有无飞跨电容半桥三电平LLC谐振变换器的开关特性对比。其中,仿真的直流母线电压VDC=1 500V,开关管电压承受能力为半母线电压750V,仿真结果如图7所示。结果表明,飞跨电容的引入会增大开关管的尖峰电压,且振荡幅度略微增大,但均在可接受范围内,采用1 200V耐压的开关管即能保证电路的正常工作。

在保证各开关管在短路故障时不过电压损坏的基础上,需要考虑快速切除短路故障,以避免开关管过电流损坏。本文采用的短路保护方法为DESAT法。

图7 有无飞跨电容的半桥三电平LLC谐振变换器仿真结果

Fig.7 Simulation results of half bridge three level LLC resonant converter with or without flying capacitor

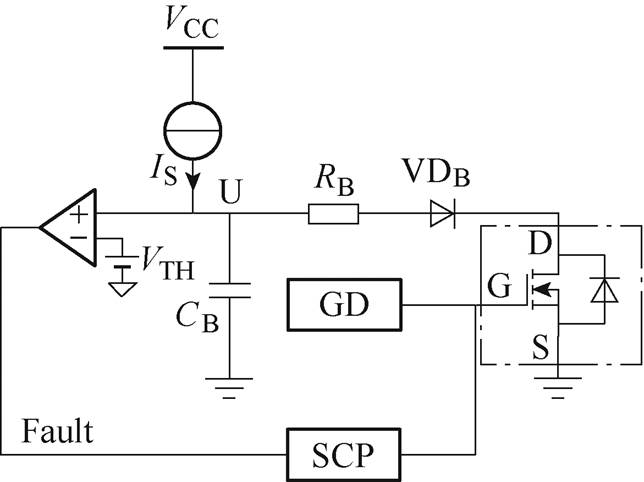

图8为DESAT法原理图,图中,VCC为辅助电源的电压,IS为恒流源(仅在SiC MOSFET导通时工作),CB、RB、VDB分别为DESAT电容、DESAT电阻、DESAT二极管,VTH为参考电压,GD为SiC MOSFET的驱动单元,SCP为SiC MOSFET的短路保护单元,U点对地电压称为DESAT电压。图8中,Fault为比较器输出信号,SiC MOSFET正常导通时,其输出为低电平,SCP单元不动作;短路故障时其输出高电平,SCP单元动作,SiC MOSFET保护关断。

图8 DESAT法原理图

Fig.8 Schematic diagram of DESAT method

SiC MOSFET正常导通时,DESAT电压应满足

(3)

(3)式中,VCB为DESAT电压;VRB为RB两端电压;VDB为VDB的导通压降;Vds.on为SiC MOSFET通态压降。此时比较器输出为低电平,SCP单元不动作。

当SiC MOSFET发生短路故障,VDS瞬间增大,DESAT二极管VDB截止,恒流源IS对DESAT电容CB进行快速充电,从而VCB>VTH,比较器输出高电平,短路保护单元SCP动作,触发SiC MOSFET保护关断。

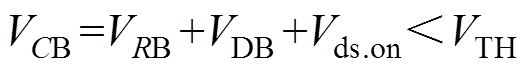

本文选取Texas Instrument的ISO5852S作为SiC MOSFET驱动芯片,该芯片带有DESAT功能,且仅在开关管导通时起作用,其DESAT阈值电压的典型值为9V[27]。通过芯片的DESAT引脚检测漏源极电压VDS,当DESAT电压超过设定阈值电压,驱动芯片发出故障信号,同时封锁驱动脉冲,SiC MOSFET保护关断。SiC MOSFET正常关断时的关断速度很快,高di/dt与杂散电感形成漏源极电压的电压过冲。如果在短路保护关断时以同样的速度关断SiC MOSFET,将出现很大的电压过冲,严重时将导致SiC MOSFET过电压损坏。芯片内部的软关断功能能够很好地解决这个问题。当芯片的短路保护功能触发,SiC MOSFET将以较慢的速度关断,产生较小的电压过冲。

图9为本文所设计的部分驱动电路,图中,VCC和VEE分别为驱动正压、负压,Rgh、Rgl、Ron、Roff、VDoff为驱动电阻元件。ISO5852S的输出端(OUTH/ OUTL)串接电阻RX至DESAT端,以加快CB在短路故障时的充电速度,从而缩短短路保护时间。RS、CS用于调节SiC MOSFET的软关断速度,防止关断速度过快带来过大的电压过冲,损坏开关管[28]。NPN三极管与PNP三极管所组成的推挽电路用于增加驱动电路的驱动能力。

图9 SiC MOSFET的驱动电路

Fig.9 Driving circuit of SiC MOSFET

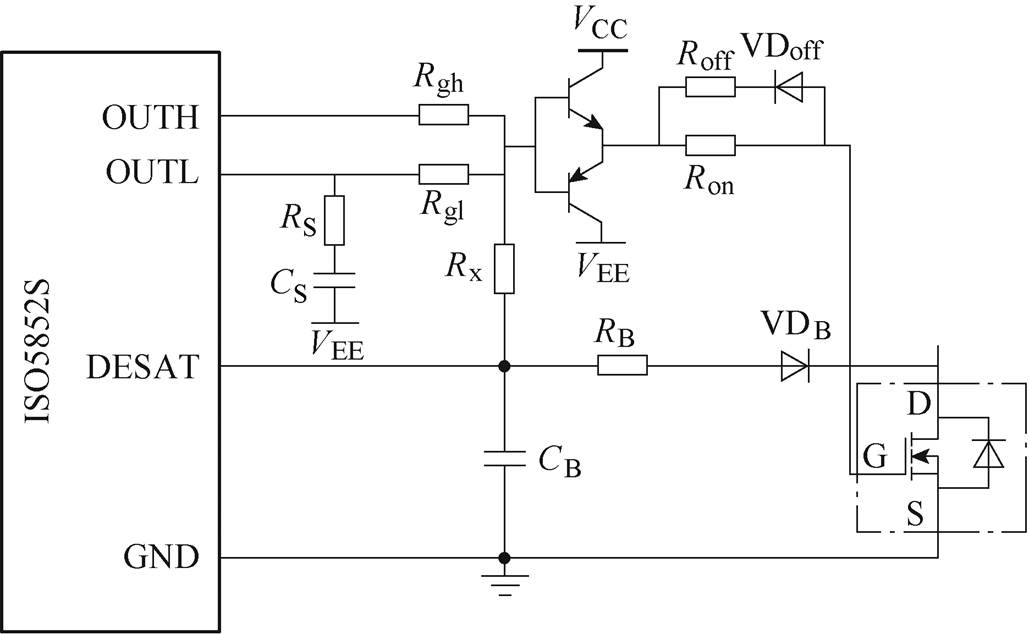

为了验证所设计电路的短路保护效果,本文搭建了NPC三电平拓扑的短路测试平台,如图10所示。图11为其中的短路测试电路。图中,L为已知电感值的负载电感(本文选取L=225mH),并联于S3管漏极与S4管源极之间。

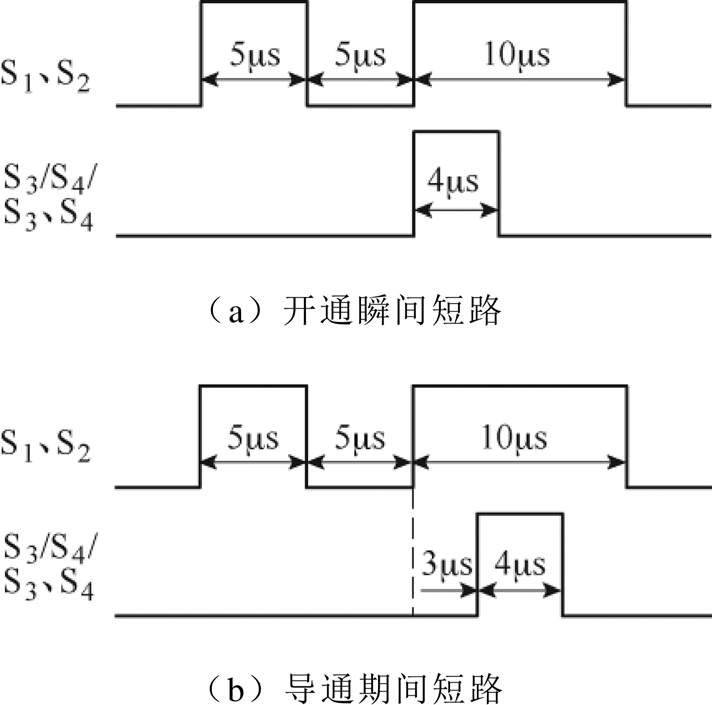

图12为NPC三电平拓扑六种短路状态的短路测试脉冲设置,通过向开关管S1~S4发送如图12a~图12c所示脉冲信号,模拟短路故障,进行短路状态1~3的短路测试。其中,每种短路状态又可分两种短路情况(开通瞬间短路与导通期间短路),驱动波形如图13所示。本文短路状态1~3的短路测试中,开通瞬间短路是指上桥臂两个开关管开通瞬间,下桥臂有开关管同时误导通,即S1、S2开通瞬间,S3或S4或S3、S4同时误导通造成瞬间短路故障;导通期间短路是指上桥臂两个开关管处于导通状态时,下桥臂有开关管误导通,即S1、S2导通期间,S3或S4或S3、S4同时误导通所造成的短路故障。

图10 NPC三电平拓扑短路测试平台

Fig.10 Short circuit test platform for NPC three-level topology

图11 短路测试电路

Fig.11 Short circuit test circuit

图12 NPC拓扑的短路状态

Fig.12 Short circuit state of NPC topology

图13 驱动脉冲设置

Fig.13 Drive pulse settings

本文采用Infineon公司1 200V/200A的SiC MOSFET模块FF6MR12W2M1_B11进行实验。其短路测试驱动电路参数见表3,驱动电压为15V/-3V。SiC模块额定电流为200A,短路电流最大值为其8~10倍,约为2 000A,短路持续时间设计不超过2ms,若DVCss=50V,根据式(1),选取飞跨电容CSS=80mF,直流母线电容Cd1=Cd2=240mF。

表3 短路测试驱动电路参数

Tab.3 Short circuit test parameters drive circuit

参 数数 值参 数数 值 Rgh/W1RB/kW1 Rgl/W1CB/pF30 Roff/W2RS/W10 Ron/W20CS/nF10 Rx/kW4.7——

设定直流母线电压VDC=1 500V,实验开始时,需对飞跨电容CSS进行预充电,使飞跨电容电压VCss稳定于750V时再对母线电容进行充电,VDC=1 500V时断开直流电压源,向SiC MOSFET发送脉冲信号,驱动脉冲设置如图13所示,内外管死区时间设置为100ns。由于所选SiC MOSFET模块的引脚短,难以用商用罗氏线圈测取其开关管电流,因而仅通过示波器观察其栅源极电压VGS波形以及漏源极电压VDS波形,同时观察飞跨电容CSS的充放电电流ICss,测试结果如图14~图16所示。

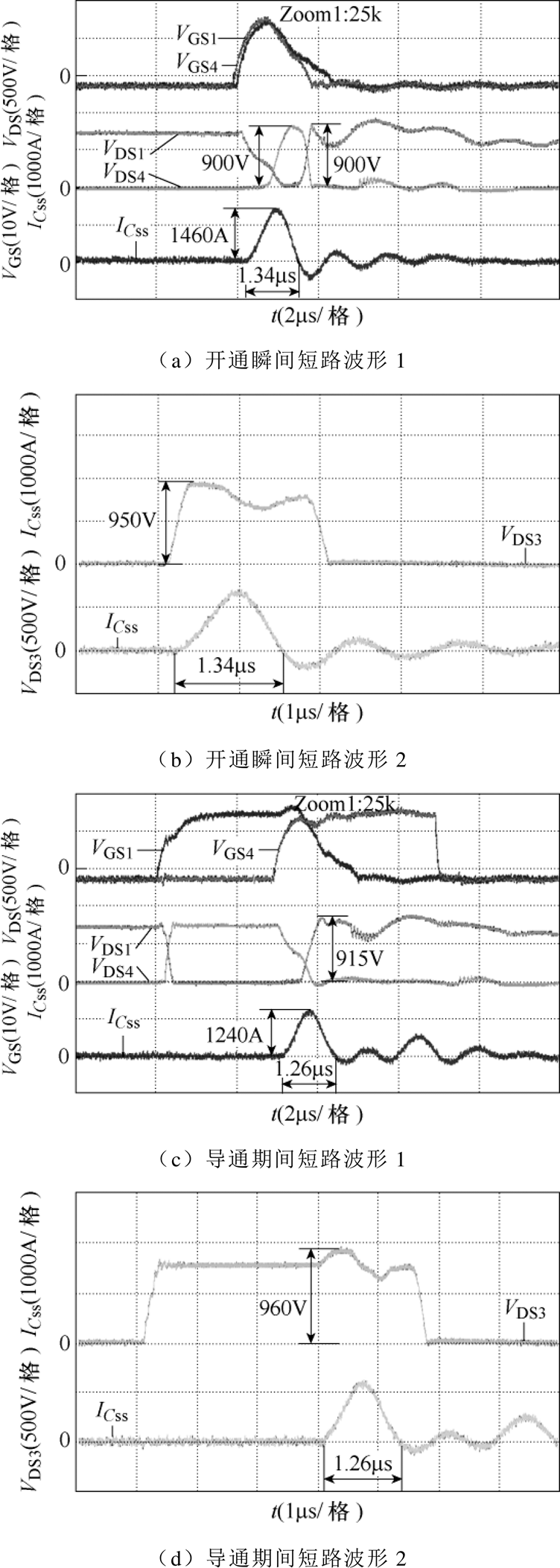

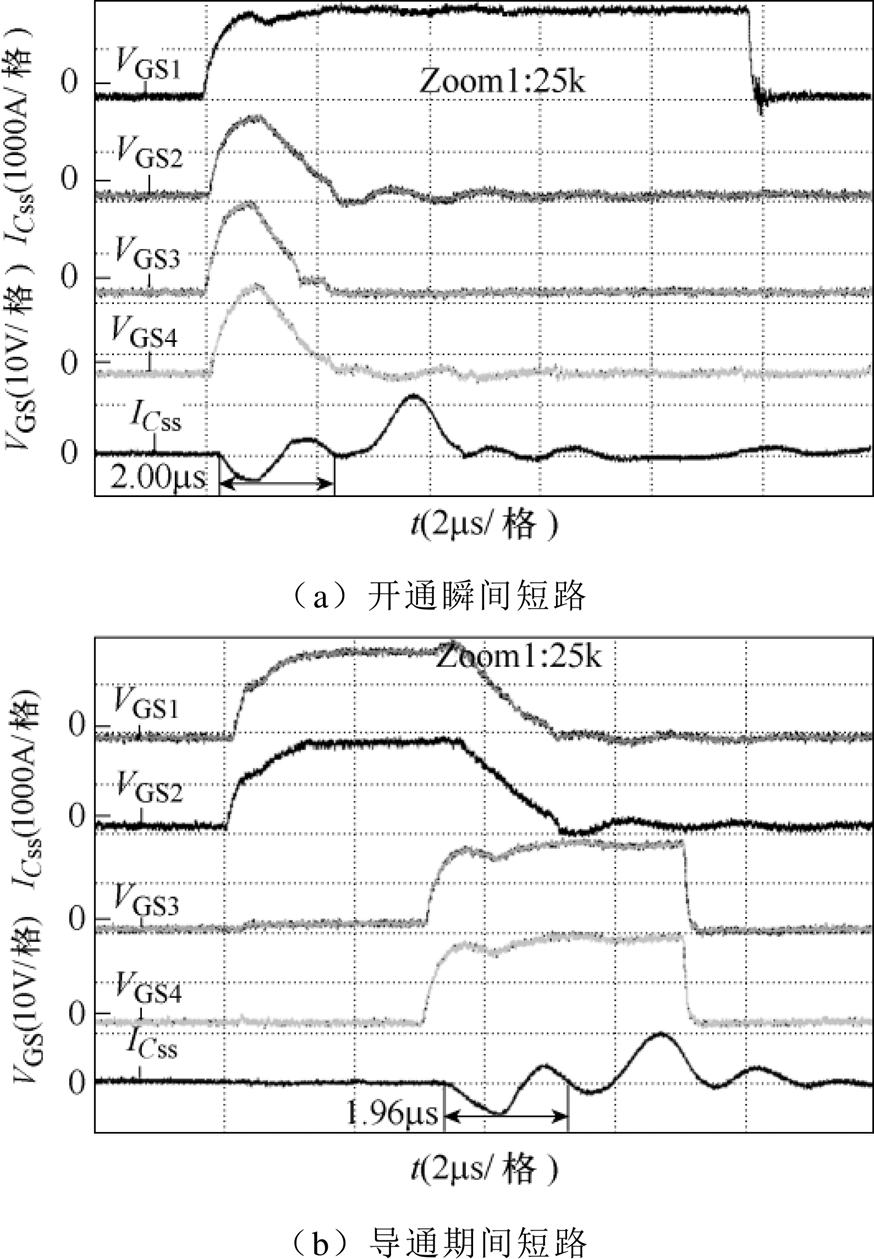

短路状态1~3中,SiC MOSFET保护关断时,其关断速度明显小于正常关断时的关断速度,例如图14c中,短路状态1导通期间短路情况下,VGS2的下降速度明显小于VGS3的下降速度,说明S2触发保护关断,芯片的软关断功能使能。因而可以通过观察SiC MOSFET的VGS波形来判断其是否触发保护。本次实验中,各个SiC MOSFET的电压过冲均小于250V,无过电压风险。

图14 短路状态1测试波形

Fig.14 Test waveform of short circuit state 1

图15 短路状态2测试波形

Fig.15 Test waveform of short circuit state 2

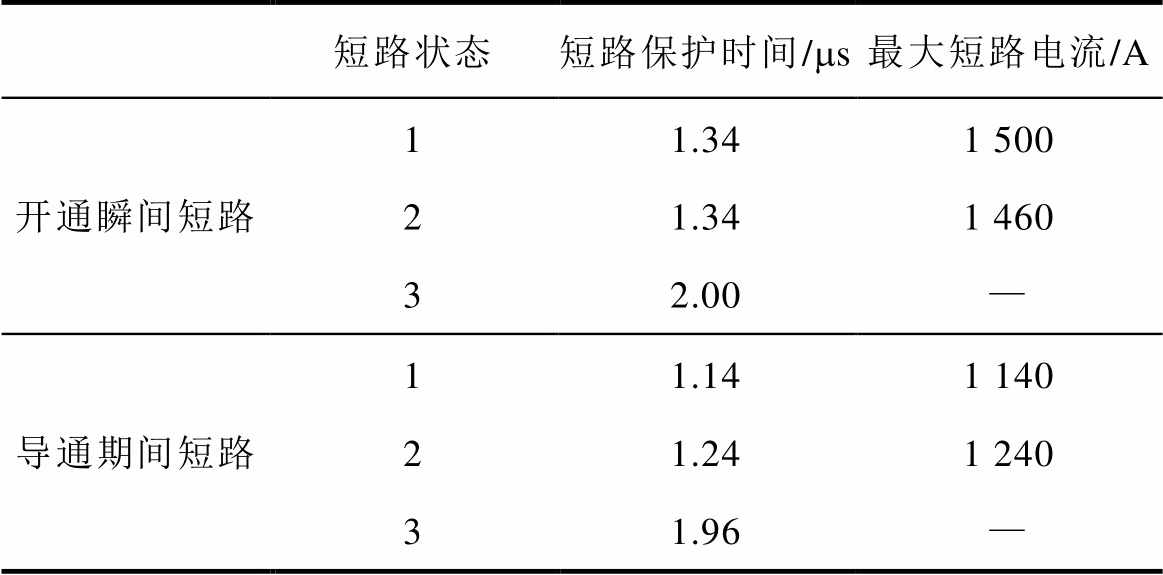

开关管保护关断,短路电流能够在短时间内下降为0。定义短路电流持续时间为短路保护时间,则短路状态1、2中飞跨电容CSS的放电电流、充电电流即为短路电流,而短路状态3中,由于飞跨电容CSS存在放电和充电两个过程,不能用其表示短路电流,仅记CSS开始放电至充电结束的时间为短路保护时间。短路保护时间与最大短路电流见表4,从图14~图16及表4可以发现,短路状态1~3的短路保护时间在2ms以内,且短路状态1、2的最大短路电流为1 500A,小于所选SiC MOSFET额定电流的10倍。

图16 短路状态3测试波形

Fig.16 Test waveform of short circuit state 3

表4 短路保护时间与最大短路电流

Tab.4 Short circuit protection time and maximum short circuit current

短路状态短路保护时间/ms最大短路电流/A 开通瞬间短路11.341 500 21.341 460 32.00— 导通期间短路11.141 140 21.241 240 31.96—

短路状态1的短路回路为图4所示的①,即为CSS-S2-S3-CSS,实际处于短路状态的是S2、S3。图14为短路状态1测试波形,观察VGS2、VGS3波形可以发现,在开通瞬间短路情况下,S2、S3先后保护关断,避免了开关管损坏的风险。而在导通期间短路情况下,S3未导通前,S2的DESAT电容CB已经开始充电,因而在发生短路故障时,其DESAT电压相比S3更快到达阈值电压,S2率先保护关断,短路回路①被切除,S3 DESAT电压未到达其阈值,恢复正常导通状态,开关管无损坏风险。如图14b和图14d所示,S4被钳位二极管VDb所钳位,最大电压为880V,无过电压风险。

短路状态2的短路回路为图4所示的②,即为Cd1-S1-CSS-S4-Cd2,实际处于短路状态的是S1、S4。图15为短路状态2测试波形,观察VGS1、VGS4波形可以发现,在开通瞬间短路情况下,S1、S4先后保护关断,避免了开关管损坏的风险。而在导通期间短路情况下,S4未导通前,S1的DESAT电容CB已经开始充电,因而在发生短路故障时,其DESAT电压相比S4更快到达阈值电压,S1率先保护关断,短路回路②被切除,S4 DESAT电压未到达其阈值,恢复正常导通状态,开关管无损坏风险。如图15b和图15d所示,S3被大电容值飞跨电容CSS所钳位,最大电压为915V,无过电压风险。

短路状态3的短路回路有3条,为图4所示的①、②和③,即为CSS-S2-S3-CSS、Cd1-S1-CSS-S4-Cd2和Cd1-S1-S2-S3-S4-Cd2。实际工作中,S1~S4均处于短路状态,电路处于桥臂直通状态,短路回路为回路③,若外管先保护关断,则短路回路变为回路①,CSS放电;若内管先保护关断,则短路回路变为回路②,CSS充电。从图16短路状态3测试波形中ICss波形可以发现,飞跨电容CSS先放电后充电,因而短路回路为③→②。观察VGS1~VGS4波形可以发现,在开通瞬间短路情况下,S1、S2保护关断,短路回路被切除,S3、S4继续导通,开关管无损坏风险;在导通期间短路情况下,S2~S4保护关断,短路回路被切除,S1继续导通,开关管无损坏风险。

观察图14、图15的VDS波形可以发现,VDS电压上升的开关管更快地触发短路保护(VGS更快下降至负压),VDS电压下降的开关管触发短路保护的时间相对较长,甚至没有触发保护。原因在于发生短路故障时,导通状态(包括误导通状态)的开关管VDS若快速增大,则较大的dv/dt将通过VDB的结电容向CB充电,加快其充电速度,更快到达DESAT阈值电压,更快触发保护关断;导通状态(包括误导通状态)的开关管VDS若快速减小,则较大的dv/dt将通过VDB的结电容从CB抽取电流,减慢其充电速度,因而其到达DESAT阈值电压的时间相对较长,触发短路保护的时间也更长。

本文针对三电平拓扑中的SiC MOSFET因短路故障而过电压、过电流损坏这一问题,结合短路保护方法——DESAT法,在NPC拓扑中引入大电容值飞跨电容,在实现所有开关管短路保护的同时,避免开关管过电压损坏的风险。在短路测试中,开关管能够有效地触发短路保护,且各开关管的最大电压均不超过其击穿电压,验证了本文拓扑改进及驱动设计的可行性,有效地实现了NPC三电平拓扑中的SiC MOSFET过电压与过电流保护。

参考文献

[1] Millán J, Godignon P, Perpiñà X, et al. A survey of wide bandgap power semiconductor devices[J]. IEEE Transactions on Power Electronics, 2014, 29(5): 2155-2163.

[2] Shenai K. Future prospects of widebandgap (WBG) semiconductor power switching devices[J]. IEEE Transactions on Electron Devices, 2015, 62(2): 248- 257.

[3] 梁美, 郑琼林, 可翀, 等. SiC MOSFET、Si Cool- MOS和IGBT的特性对比及其在DAB变换器中的应用[J]. 电工技术学报, 2015, 30(12): 41-50.

Liang Mei, Zheng Trillion Q, Ke Chong, et al. Performance comparison of SiC MOSFET, Si CoolMOS and IGBT for DAB converter[J]. Transa- ctions of China Electrotechnical Society, 2015, 30(12): 41-50.

[4] 柯俊吉, 赵志斌, 谢宗奎, 等. 考虑寄生参数影响的碳化硅MOSFET开关暂态分析模型[J]. 电工技术学报, 2018, 33(8): 1762-1774.

Ke Junji, Zhao Zhibin, Xie Zongkui, et al. Analytical switching transient model for silicon carbide MOSFET under the influence of parasitic parame- ters[J]. Transactions of China Electrotechnical Society, 2018, 33(8): 1762-1774.

[5] Wang Zhiqiang, Shi Xiaojie, Xue Yang, et al. Design and performance evaluation of overcurrent protection schemes for silicon carbide (SiC) power MOSFETs[J]. IEEE Transactions on Industrial Electronics, 2014, 61(10): 5570-5581.

[6] 邵伟华, 冉立, 曾正, 等. SiC MOSFET短路特性评估及其温度依赖性模型[J]. 中国电机工程学报, 2018, 38(7): 2121-2131.

Shao Weihua, Ran Li, Zeng Zheng, et al. Short- circuit evaluation and temperature-dependent model of SiC MOSFET[J]. Proceedings of the CSEE, 2018, 38(7): 2121-2131.

[7] Wang Zhiqiang, Shi Xiaojie, Tolbert L M, et al. Temperature-dependent short-circuit capability of silicon carbide power MOSFETs[J]. IEEE Transa- ctions on Power Electronics, 2016, 31(2): 1555-1566.

[8] 李辉, 黄樟坚, 廖兴林, 等. 一种抑制SiC MOSFET桥臂串扰的改进门极驱动设计[J]. 电工技术学报, 2019, 34(2): 275-285.

Li Hui, Huang Zhangjian, Liao Xinglin, et al. An improved SiC MOSFET gate driver design for cross- talk suppression in a phase-leg configuration[J]. Transactions of China Electrotechnical Society, 2019, 34(2): 275-285.

[9] 巴腾飞, 李艳, 梁美. 寄生参数对SiC MOSFET栅源极电压影响的研究[J]. 电工技术学报, 2016, 31(13): 64-73.

Ba Tengfei, Li Yan, Liang Mei, et al. The effect of parasitic parameters on gate-source voltage of SiC MOSFET[J]. Transactions of China Electrotechnical Society, 2016, 31(13): 64-73.

[10] Anthon A, Zhang Zhe, Andersen M A E, et al. Com- parative evaluation of the loss and thermal perfor- mance of advanced three-level inverter topologies[J]. IEEE Transactions on Industry Applications, 2017, 53(2): 1381-1389.

[11] Wu Wenjun, Cai Yuxi, Wang Wenxuan, et al. The security protection of SiC MOSFET NPC tri-level converter[C]//2018 1st Workshop on Wide Bandgap Power Devices and Applications in Asia, Xi’an, China, 2018: 1-8.

[12] 吴海富, 张建忠, 赵进, 等. SiC MOSFET短路检测与保护研究综述[J]. 电工技术学报, 2019, 34(21): 4519-4528.

Wu Haifu, Zhang Jianzhong, Zhao Jin, et al. Review of short-circuit detection and protection of silicon carbide MOSFETs[J]. Transactions of China Electro- technical Society, 2019, 34(21): 4519-4528.

[13] 方跃财. SiC MOSFET特性研究: 驱动、短路与保护[D]. 杭州: 浙江大学, 2018.

[14] Sun Keyao, Wang Jun, Burgos R, et al. Analysis and design of an overcurrent protection scheme based on parasitic inductance of SiC MOSFET power module[C]//2018 IEEE Applied Power Electronics Conference and Exposition, San Antonio, TX, 2018: 2806-2812.

[15] Horiguchi T, Kinouchi S, Nakayama Y, et al. A fast short-circuit protection method using gate charge characteristics of SiC MOSFETs[C]//2015 IEEE Energy Conversion Congress and Exposition, Mon- treal, QC, 2015: 4759-4764.

[16] Zhang Xuan, Li He, Brothers J A, et al. A gate drive with power over fiber-based isolated power supply and comprehensive protection functions for 15kV SiC MOSFET[J]. IEEE Journal of Emerging & Selected Topics in Power Electronics, 2016, 4(3): 946-955.

[17] Wang Jun, Shen Zhiyu, Burgos R, et al. Integrated switch current sensor for shortcircuit protection and current control of 1.7kV SiC MOSFET modules[C]//IEEE Energy Conversion Congress and Exposition, Milwaukee, WI, 2016: 1-7.

[18] Mocevic S, Wang Jun, Burgos R, et al. Comparison between desaturation sensing and Rogowski coil current sensing for shortcircuit protection of 1.2kV, 300A SiC MOSFET module[C]//IEEE Applied Power Electronics Conference and Exposition, San Antonio, TX, 2018: 2666-2672.

[19] Yamashita Y, Furuta J, Inamori S, et al. Design of RCD snubber considering wiring inductance for MHz-switching of SiC-MOSFET[C]//IEEE 18th Work- shop on Control and Modeling for Power Electronics, Stanford, CA, 2017: 1-6.

[20] Liu Shengsheng, Lin Hua, Wang Tao. Comparative study of three different passive snubber circuits for SiC power MOSFETs[C]//IEEE Applied Power Elec- tronics Conference and Exposition, Anaheim, CA, USA, 2019: 354-358.

[21] Canales F, Barbosa P M, Burdio J M, et al. A zero voltage switching three-level DC/DC converter[C]// Twenty-Second International Telecommunications Energy Conference (Cat. No.00CH37131), Phoenix, AZ, USA, 2000: 512-517.

[22] 葛兴来, 张晓华, 岳岩. 低载波比下三电平NPC逆变器同步SVPWM算法[J]. 电机与控制学报, 2018, 22(9): 24-32.

Ge Xinglai, Zhang Xiaohua, Yue Yan. Comparative study on synchronized space vector PWM for three level neutral point clamped VSI under low carrier ratio[J]. Electric Machines and Control, 2018, 22(9): 24-32.

[23] 冯思硕, 王金花, 杨欢, 等. 混合钳位式三电平逆变器新型调制策略研究[J]. 电工技术学报, 2016, 31(13): 46-54.

Feng Sishuo, Wang Jinhua, Yang Huan, et al. Research on a novel modulation strategy of the hybrid clamped three-level inverter[J]. Transactions of China Electrotechnical Society, 2016, 31(13): 46-54.

[24] 李瑞生, 徐军, 翟登辉, 等. 三电平DC/DC电源转换技术研究[J]. 电力系统保护与控制, 2017, 45(11): 73-80.

Li Ruisheng, Xu Jun, Zhai Denghui, et al. Research of three-level DC/DC conversion technology[J]. Power System Protection and Control, 2017, 45(11): 73-80.

[25] 刘朋, 陈昌松, 段善旭. 带飞跨电容的三电平全桥直流变换器输入中点电压的自平衡分析[J]. 电工技术学报, 2018, 33(18): 4335-4344.

Liu Peng, Chen Changsong, Duan Shanxu. Self- balance mechanism analysis of the neutral point voltage in three-level full bridge DC-DC converter with flying capacitors[J]. Transactions of China Electrotechnical Society, 2018, 33(18): 4335-4344.

[26] 吕征宇, 李佳晨, 杨华. 新型LLC谐振变换器数字同步整流驱动方式[J]. 电机与控制学报, 2018, 22(1): 16-22.

Lü Zhengyu, Li Jiachen, Yang Hua. Digital syn- chronous rectification driving method for LLC resonant converter[J]. Electric Machines and Control, 2018, 22(1): 16-22.

[27] Texas Instruments. ISO 5852S High-CMTI 2.5A and 5AReinforced Isolated IGBT, MOSFET Gate Driver with Split Outputs and Active Protection Features[DB/OL]. http://www.ti.com/lit/ds/symlink/iso5852s.pdf.

[28] Texas Instruments. IGBT gate driver reference design for parallel IGBTs with short-circuit protection and external BJT buffer[DB/OL]. http://www.ti.com.cn/ cn/lit/ug/tiduc70a/tiduc70a.pdf.

Overvoltage and Overcurrent Protection of SiC MOSFET in Three-Level Topology with Flying Capacitor

Abstract In order to ensure the reliability of SiC MOSFET application in three-level topology, it is necessary to carry out overvoltage protection and overcurrent protection. According to the overvoltage caused by short circuit, combined with the short circuit protection method, this paper proposes a method of adding a flying capacitor with a large capacitance to the Neutral Point Clamped (NPC) topology. In this way, the SiC MOSFET is not damaged when a short circuit fault occurs and can be quickly turned off to reduce the risk of overcurrent. By setting up a short-circuit test platform, it is verified that when a short-circuit fault occurs in the three-level circuit, the flying capacitor with large capacitance can protect SiC MOSFET from overvoltage, and the short-circuit protection time of SiC MOSFET is less than 2ms.

keywords:Three-level, large-capacitance, flying capacitor, overvoltage protection

中图分类号:TN386.1; TM131.1

DOI: 10.19595/j.cnki.1000-6753.tces.191638

国家自然科学基金联合基金资助项目(U1766207)。

收稿日期 2019-11-26

改稿日期 2020-02-15

庄桂元 男,1995年生,硕士研究生,研究方向为SiC MOSFET的短路保护。E-mail: zhuang_guiyuan@126.com(通信作者)

张 兴 男,1963年生,教授,博士生导师,研究方向为智能光伏发电及其逆变控制技术。E-mail: honglf@ustc.edu.cn

(编辑 崔文静)