图1 双脉冲测试电路

Fig.1 Double pulse test circuit

摘要 压接型IGBT芯片在正常的运行工况下承受着电-热-力多物理量的综合作用,研究电-热-力影响下的IGBT芯片动态特性对于指导IGBT芯片建模以及规模化IGBT并联封装设计具有重要意义。为了全面获得电-热-力综合影响下压接型IGBT芯片的动态特性,该文结合双脉冲测试电路原理,研制出具备电-热-力灵活调节的压接型IGBT芯片动态特性实验平台。通过对动态特性实验平台关键问题进行有限元仿真计算,实现平台回路寄生电感、IGBT芯片表面压力分布及机械夹具温度分布的优化设计。在此基础上建立压接型IGBT芯片动态特性实验平台,对实验平台进行综合调试,结果表明,该文所设计的实验平台具有寄生电感小、IGBT芯片表面压力分布均衡及机械夹具各组件温度分布合理的特点,可以满足电-热-力综合影响因素下压接型IGBT芯片动态特性实验的需求。

关键词:压接型IGBT芯片 动态特性 寄生电感 温度 机械压力

绝缘栅双极型晶体管(Insulated Gate Bipolar Transistor, IGBT)自20世纪80年代被发明以来,经过几十年的发展,已经成为功率半导体器件的主流,在电力变换领域占据了非常重要的地位[1-2]。相比于传统的焊接型IGBT模块,压接型IGBT器件依靠机械压力将内部IGBT芯片并联连接在一起,取消了焊接型IGBT模块中常用的绑定线连接,使其具有双面散热、失效短路、功率密度大等优点,在高压大功率领域得到了广泛的应用[3-5]。

虽然压接型IGBT器件具有诸多优点,但对功率芯片研发和封装集成技术也提出了诸多挑战[6]。难点之一是复杂电-热-力条件下器件内部大量IGBT芯片之间的并联均流问题[7]。并联均流问题可分为静态均流和动态均流,相比于静态均流,动态均流问题更加严峻[8-9]。原因在于IGBT芯片动态特性在生产之初便已存在一定分散性,并且与芯片工作时的温度、机械压力等环境变量之间具有耦合关系[10-13],因此全面研究压接型IGBT芯片的动态特性及其影响因素对于规模化芯片并联电流均衡具有重要意义。对此,国内外一些学者对压接型IGBT芯片动态特性开展了理论方面的研究,通过建立内部机理模型来反映IGBT芯片的外特性,例如,通过温度改变载流子寿命影响IGBT芯片特性,通过压力改变载流子迁移率和半导体形变来影响IGBT芯片特性,这些模型对于推动芯片研发和封装设计具有一定的指导意义[14-15]。另外,一些学者开展了实验研究,浙江大学通过优化母排设计研制出了压接型IGBT器件级的动态特性实验平台,平台具有高电压、大电流及低寄生电感的特点[16]。重庆大学研制了压接型IGBT芯片级均流实验平台,得到了电-热-力耦合关系下静态均流特性[17],另外现有的商业化功率测试仪通常采用测IGBT裸片的方法得到其动态特性,但这种方法不能反映压接型IGBT芯片的实际工况。根据目前的研究进展,尚未有针对压接型IGBT芯片的动态特性实验平台。因此亟需研制一款综合考虑电-热-力影响下的压接型IGBT芯片动态特性实验平台。

本文结合压接型IGBT器件封装的特点,首先,提出了在电-热-力影响因素下,压接型IGBT芯片动态特性实验平台的设计要求;其次,对各个技术要求分别进行了寄生电感、温度和压力的仿真计算,并提出了合理的设计方案;最后,综合各个影响因素研制出了具有实验回路寄生电感小、芯片表面压力分布均匀及机械夹具温度分布合理的实验平台,为压接型IGBT芯片动态特性测试提供了实验基础。

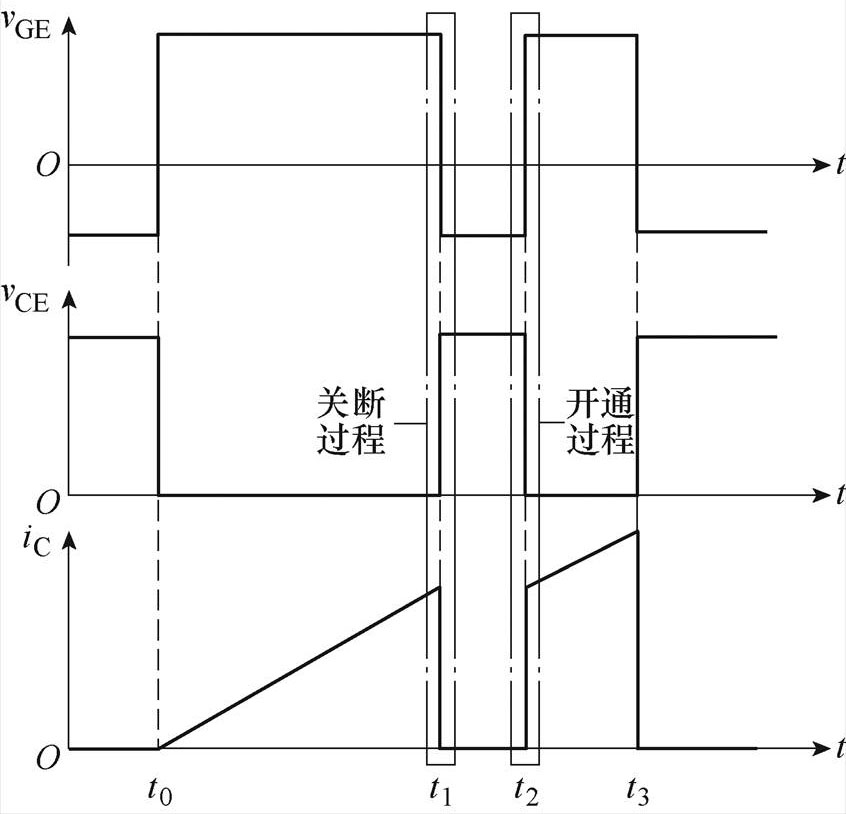

在IGBT动态特性的测试中,一般采用IEC标准中的二极管钳位感性负载测试电路,又叫做双脉冲测试电路[18],其基本电路如图1所示。

图1 双脉冲测试电路

Fig.1 Double pulse test circuit

图1中包含充放电回路与实验回路两部分。其中二极管采用快恢复二极管(Fast Recovery Diode, FRD),充放电回路为母线电容C提供实验回路所需的母线电压。实验回路通过调节驱动触发源的脉冲宽度来获得双脉冲实验波形,波形示意图如图2所示。

首先由高压直流电源为母线电容充电至IGBT测试所需电压。在t0时刻,IGBT导通,经过t0~t1建立IGBT动态特性测试所需的电流;在t1时刻,IGBT关断,负载电感电流由IGBT换流到FRD上;在t2时刻,IGBT再次开通,电流由FRD换流到IGBT上,经过t2~t3,IGBT电流继续上升,到达t3时刻,IGBT再次关断,双脉冲实验结束。IGBT的动态特性需要关注图2中t1时刻IGBT的关断过程及t2时刻IGBT的开通过程。

图2 双脉冲实验波形示意图

Fig.2 Schematic diagram of double pulse test waveforms

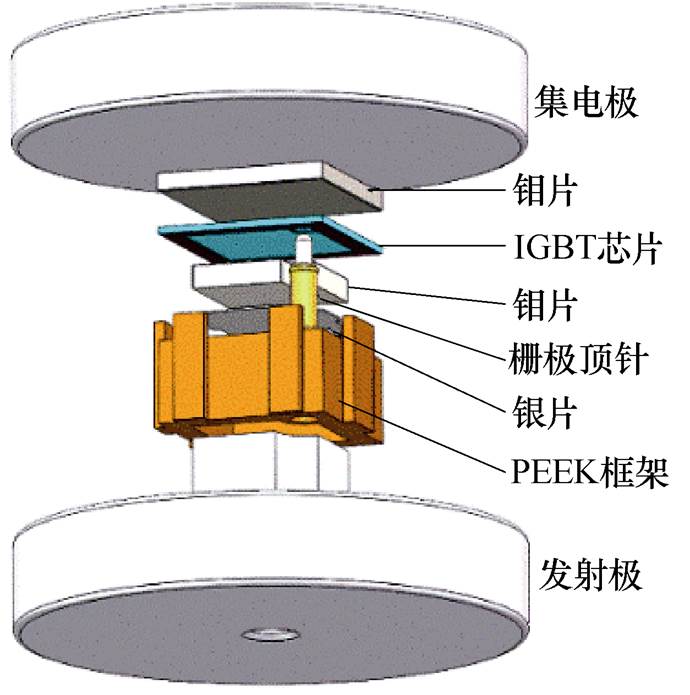

压接型IGBT子模组结构如图3所示,包含集电极与发射极极板、钼片、IGBT芯片、银片和PEEK框架等部件。相比于焊接IGBT模块,压接型IGBT芯片与外部电路的电气连接是通过压力接触实现的。

图3 压接型IGBT子模组结构

Fig.3 Structure of press-pack IGBT submodule

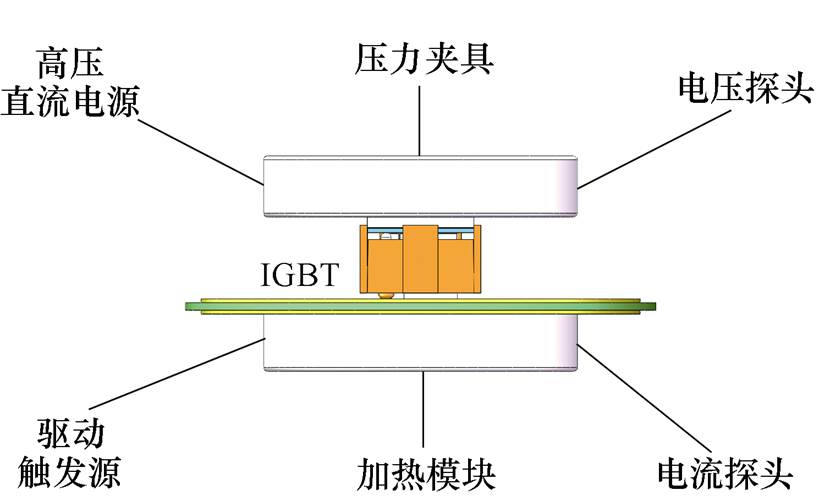

为了全面获得电-热-力影响下压接型IGBT芯片的动态特性,实验平台需要具有灵活调节电压、温度及机械压力的能力,压接型IGBT芯片实验框图如图4所示。

图4中,不同电压等级可以通过调整高压直流电源进行设置,不同机械压力可以通过调节压力夹具获得,不同温度可以通过加热模块设置。为实现电-热-力综合影响下芯片动态特性的准确测试,需要考虑以下三方面的问题:

图4 压接型IGBT芯片实验框图

Fig.4 The diagram for press-pack IGBT chip test

1)连接母排寄生电感

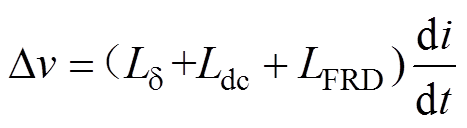

实验回路各元件之间需要有电气连接,从而不可避免地产生寄生电感,见图1实验回路部分。在双脉冲实验IGBT开通关断的瞬间,回路中会产生较大的di/dt,从而在寄生电感上感应出电压 为

为

(1)

(1)式中, 为连接母排的寄生电感;Ldc为母线电容内部的寄生电感;LFRD为续流二极管内部的寄生电感。感应电压

为连接母排的寄生电感;Ldc为母线电容内部的寄生电感;LFRD为续流二极管内部的寄生电感。感应电压 与母线电压vbus叠加在一起,作用在压接型IGBT芯片上,形成电压过冲,即

与母线电压vbus叠加在一起,作用在压接型IGBT芯片上,形成电压过冲,即

(2)

(2)

通过上述分析,寄生电感过大会引起压接型IGBT芯片承受较大的电气应力,严重影响IGBT芯片的安全工作区[16]。因此,需要减小回路的寄生电感,其中,Ldc和LFRD分别为母线电容和续流二极管内部的寄生电感,在产品生产之初就已确定,较难改变。为此,可以通过减小连接母排的寄生电感 来减小实验过程中压接型IGBT芯片所受的电压过冲。

来减小实验过程中压接型IGBT芯片所受的电压过冲。

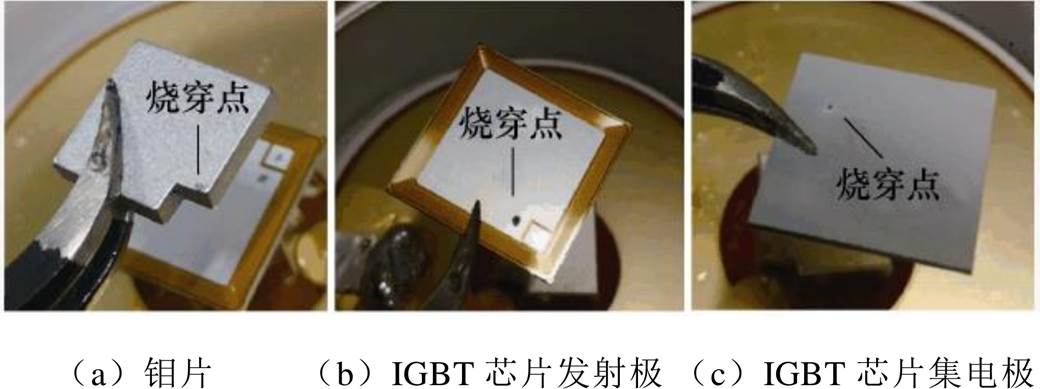

2)芯片表面压力分布

压接型IGBT芯片内部有大量的元胞并联而成,如果芯片受力不均衡会导致芯片内部元胞的电气特性及芯片与钼片的接触特性不同,从而降低整个IGBT芯片的性能[19-20]。因边缘应力集中失效的IGBT芯片如图5所示,由于压接型IGBT芯片表面受力不均,导致边缘应力集中,造成芯片边缘烧穿而整个芯片失效。为此,实验平台需要保证压接型IGBT芯片表面的受力均匀,以减小边缘应力集中进而对压接型IGBT芯片的损伤。

3)机械夹具温度分布

在压接型IGBT芯片动态特性实验中,通常情况下IGBT芯片的结温与加热板温度存在一定的温度梯度,使得IGBT芯片结温存在偏差。为此,实验平台需保证机械夹具各组件的温度分布合理,以尽量减小压接型IGBT芯片的结温误差。

图5 因边缘应力集中失效的IGBT芯片

Fig.5 Failure IGBT chip due to edge stress concentration

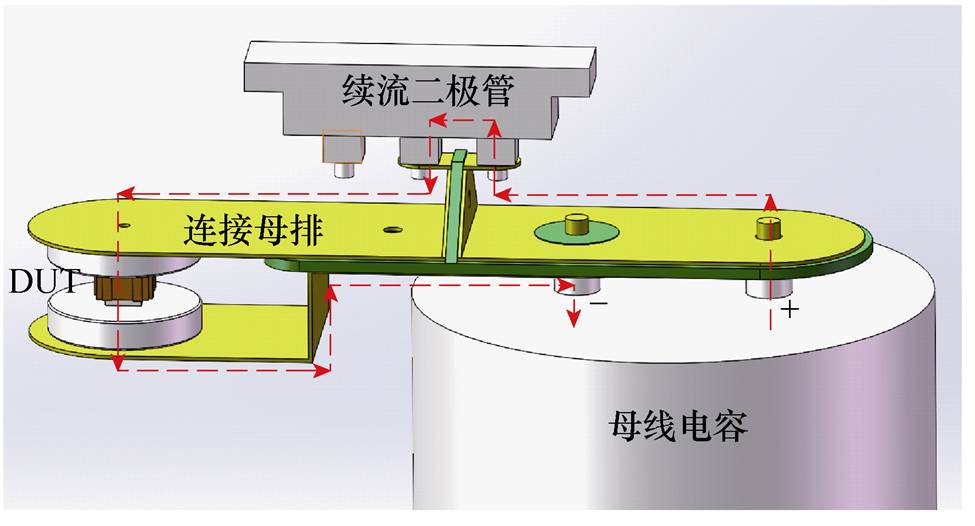

为了减小功率回路的寄生电感,通常采用母排的连接形式,连接母排示意图如图6所示。

图6 连接母排示意图

Fig.6 The diagram of connecting busbar

为了得到低寄生电感连接母排较好的设计方案,本文通过有限元计算软件对不同连接母排结构的寄生电感进行提取。仿真中为了得到更加准确的寄生电感值,建立了整个电流回路的三维有限元计算模型。需要说明的是,由于仅对比不同连接母排下寄生电感的大小且续流二极管内部的寄生电感恒定,为了简化计算,续流二极管使用短导线段进行代替;激励源施加在图6所示的母线电容的正负端子上,其频率计算式为

(3)

(3)式中,f为等效频率;tr为电流上升时间。因压接型IGBT芯片的瞬态电流上升时间tr为200~400ns,可得设定激励源的频率约为1MHz。

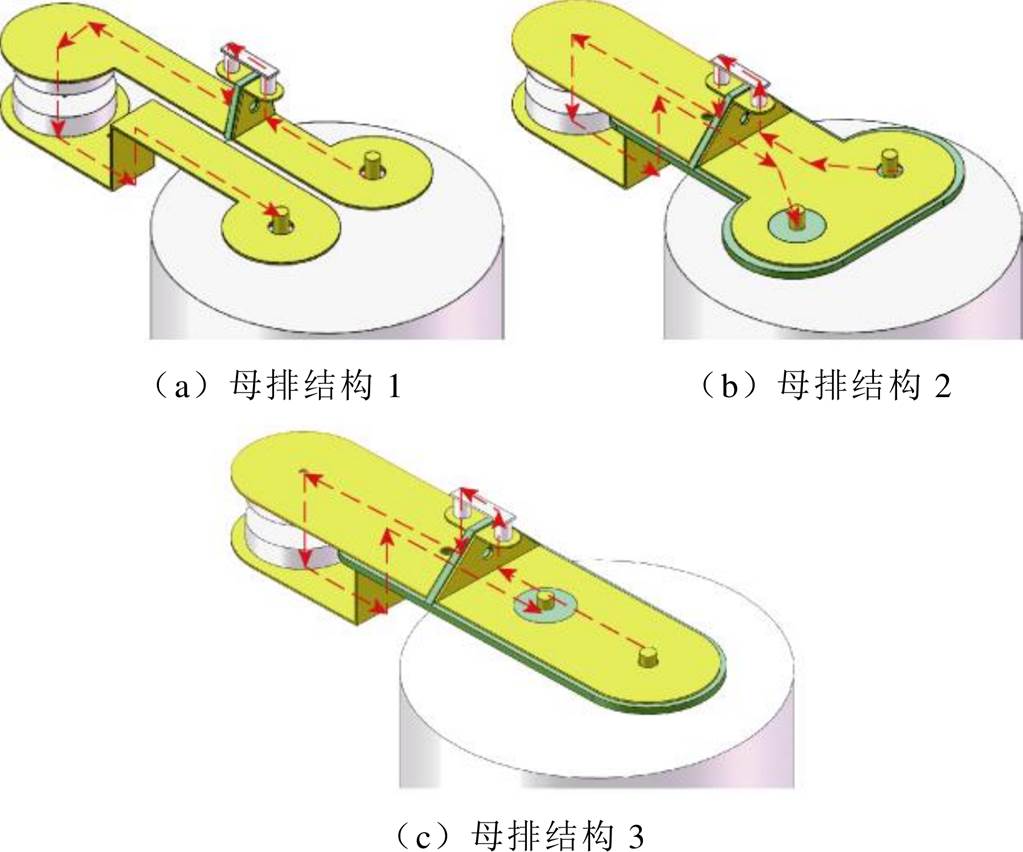

1)不同母排结构寄生电感对比

降低连接母排寄生电感的设计原则为使不同导体电流产生的磁链相互抵消,为此需要使电流异向的两个导体距离尽可能的近,图7为本文给出的三种母排结构,图中,母排结构1为非叠层母排,电流的流通路径较大,母排结构2和母排结构3同为叠层母排,区别在于母线电容处电流的走向不同,母排结构2中电流方向与母线电容端子垂直,母排结构3中电流方向与母线电容端子同方向。

图7 不同连接母排结构

Fig.7 Different structures of connecting busbar

为了比较不同母排结构的寄生电感,通过有限元软件提取了三种母排结构的寄生电感见表1。

表1 三种母排结构的寄生电感

Tab.1 Parasitic inductance of three busbar structures

母排结构寄生电感/nH 185.75 247.55 345.60

由表1结果可以看出,母排结构2与母排结构3相对于母排结构1,寄生电感显著减小,原因在于叠层结构可以相互抵消很大一部分磁链,其中母排结构3的寄生电感值仅为母排结构1的53.2%;母排结构3相比于母排结构2寄生电感略微减小,降低了4.1%,原因在于母排结构2中,图7b上、下两层母排的电流在母线电容处分别流向两个电容端子,弱化了磁链的抵消作用。因此本文采用母排结构3作为连接形式。

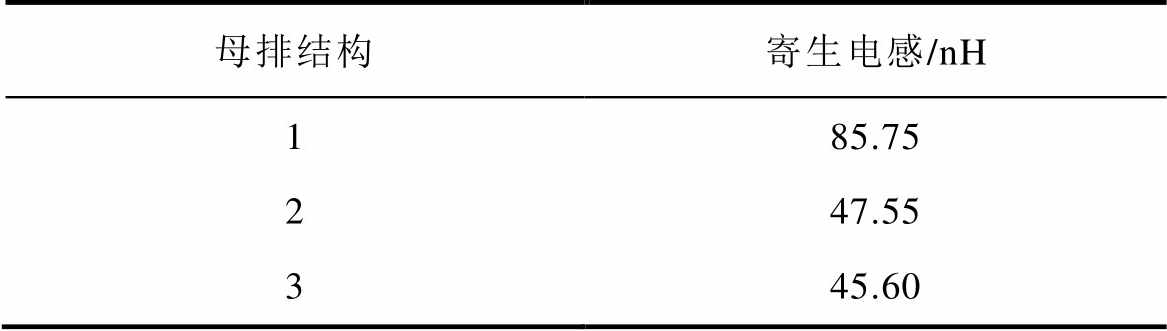

2)不同母排尺寸对比

除了母排结构,本文对不同母排尺寸也进行了有限元参数提取,对比不同尺寸下叠层母排的寄生电感。不同叠层母排尺寸如图8所示,设置叠层母排在不同长度l、不同间距h及不同宽度w,不同母排尺寸寄生电感见表2。

图8 不同叠层母排尺寸

Fig.8 Different sizes of laminated busbar

表2 不同母排尺寸寄生电感

Tab.2 Parasitic inductance of different busbar sizes

尺寸/mm电感/nH 长度l19349.04 16847.29 14345.6 间距h447.02 345.6 244.14 宽度w3053.74 4048.96 5045.6 6043.64 7041.93

由表2可以看出,寄生电感随着叠层母排长度的减小而减小,且呈线性变化,为此应尽量减小母排的长度;寄生电感随着叠层母排间距的减小而减小,但同时叠层母排需要满足4.5kV以上的绝缘能力,为此母排之间要有一定的安全裕度;寄生电感随着叠层母排宽度的增大而减小,但减幅越来越小;因此,综合考虑保证足够放置电压测量探头、电流测量探头空间及绝缘要求下,本平台选择叠层区 长×宽×厚为143mm×50mm×3mm作为设计尺寸。

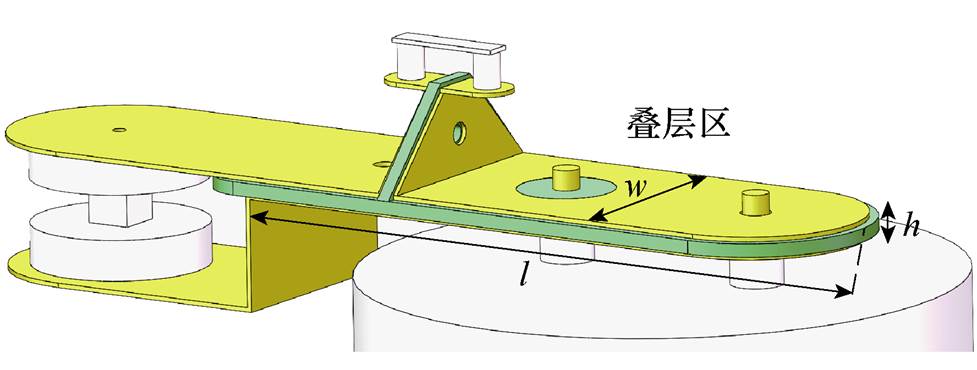

通过1.2节的分析,在压接型IGBT芯片动态特性实验中要严格保证IGBT芯片表面的受力均衡。但由于压力夹具各组件的加工精度不能保证任意两个平面的平行度,以及压力夹具在人为装配过程存在偏心问题,很难保证压接型IGBT芯片表面的受力均衡。为此,本文提出了如图9所示的压力均衡装置,即双面球碗结构。

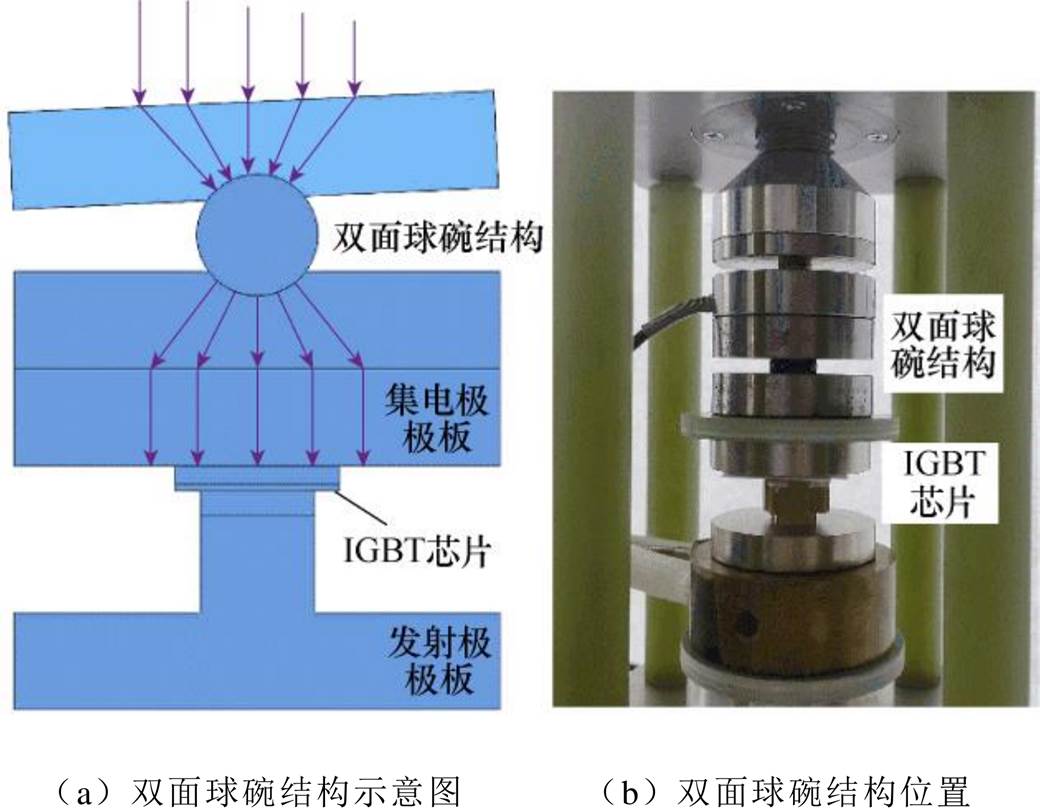

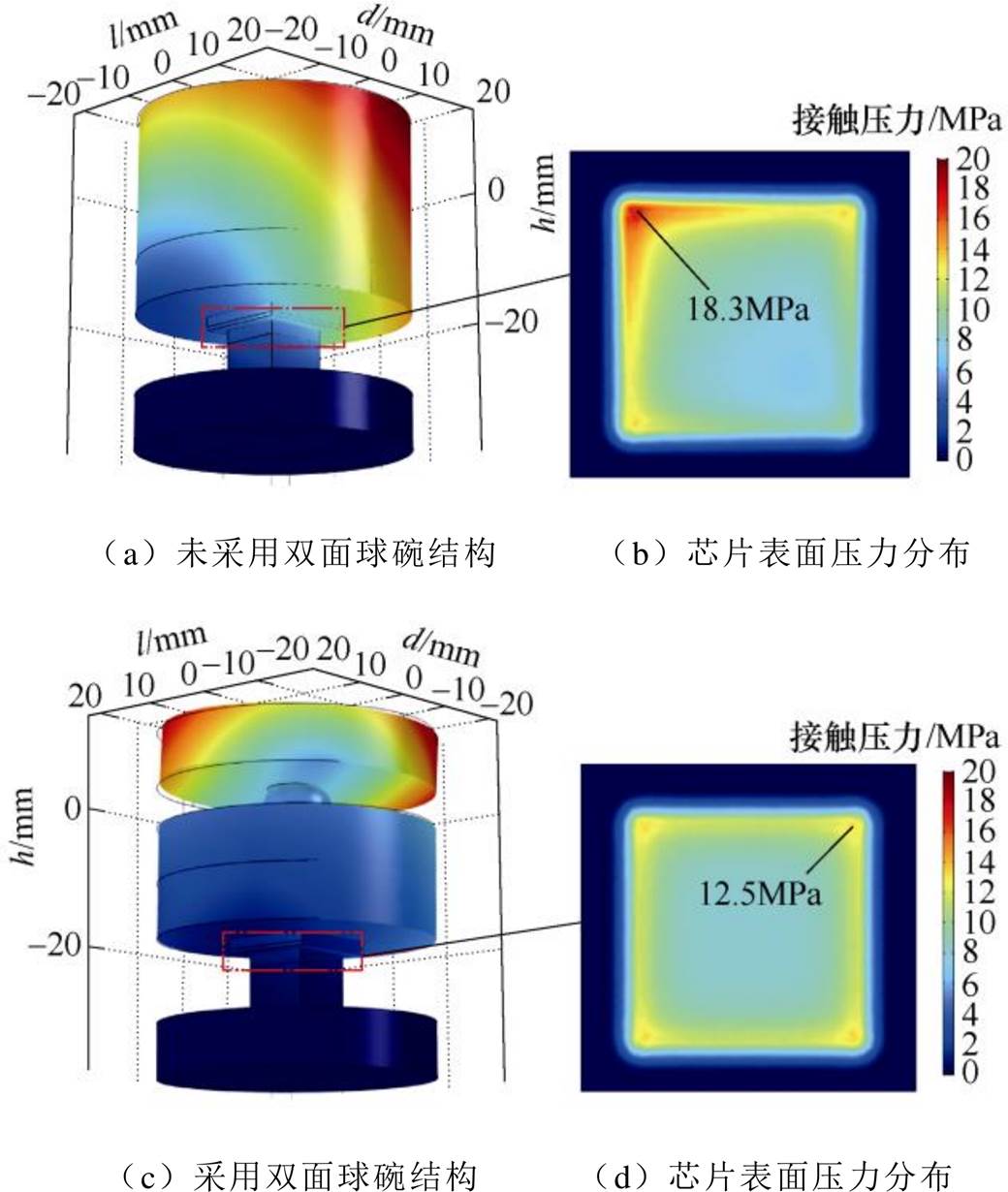

双面球碗结构由带有球型凹槽的两个极板与钢珠组成,提供了水平方向的自由度,当机械压力偏心时,双面球碗结构会通过球型凹槽与钢珠之间的滑动来改变机械应力的方向,使得作用在芯片表面的机械应力垂直于芯片表面,改善压接型IGBT芯片表面的应力分布。为此,在三维有限元仿真软件中建立了压接型IGBT芯片的受力分析模型,其中对不影响IGBT芯片表面受力分布的结构进行了简化处理,例如,去除了压接型IGBT子模组的PEEK框架、栅极顶针等结构。为了模拟外部组件不平整对压接型IGBT芯片表面受力的影响,分别对未采用双面球碗结构和采用双面球碗结构时压力分布特性进行了仿真计算,从而观察压接型IGBT芯片表面的受力情况,芯片表面压力分布计算结果如图10所示。

图9 压力均衡装置

Fig.9 The device of pressure balancing

从图10a、图10b可以看出,在未采用本文所提双面球碗结构时,IGBT芯片表面的左上角出现了明显的边缘应力集中,压强最大点达到了18.3MPa,为压强平均值10MPa的1.83倍,此应力集中点即为IGBT芯片的易损点;当采用双面球碗结构后,观察图10c中的双面球碗结构的上极板,虽然外部压力不均匀,但经过双面球碗结构的找平后,可以使图10d中芯片表面的受力较为均衡,压强最大点仅为12.5MPa,为压强平均值10MPa的1.25倍。因此,本文所设计的双面球碗结构可以明显改善压接型IGBT芯片表面的应力分布。

图10 芯片表面压力分布计算结果

Fig.10 Calculation results of pressure distribution on the chip surface

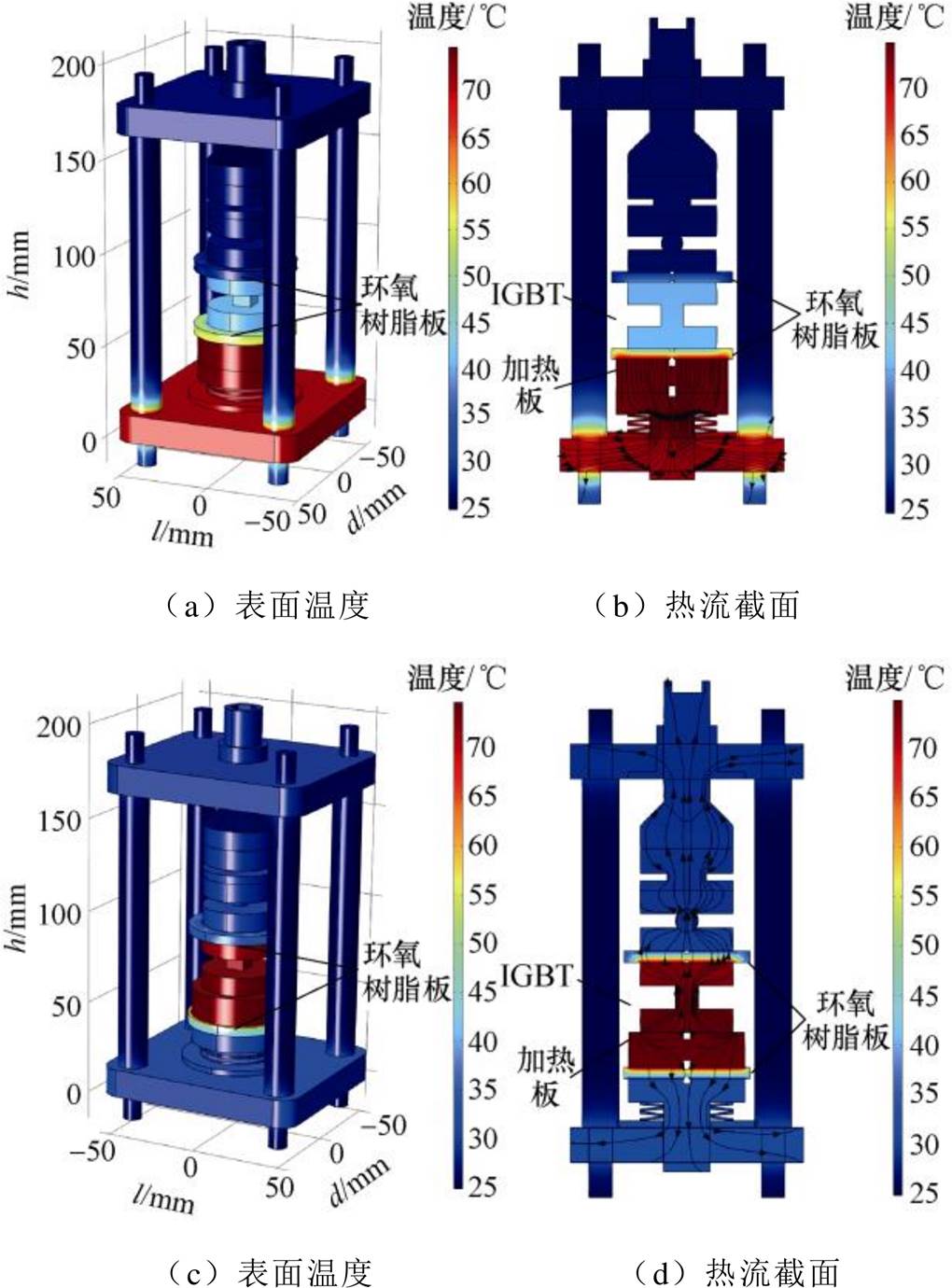

为了保证压接型IGBT芯片结温更加准确,应尽可能使压接型IGBT芯片的结温等于加热板的温度。为此本文设计了可灵活调节温度的加热模块,加热模块包含加热板、热电偶和PID控制中心三部分,通过热电偶的反馈作用与PID控制中心调控加热板的输出功率,从而保证加热板温度的准确性和稳定性。此外,考虑到实验平台加热区域会通过热传导与热辐射的方式与环境进行热量交换,从而产生温度梯度。为了得到较为合理的温度分布,减小压接型IGBT芯片结温的误差,采用环氧树脂板来控制热量流动。在三维有限元仿真软件中建立机械夹具的热力学模型,计算环氧树脂板在不同位置时整个机械夹具的温度分布,压力夹具各组件温度分布计算结果如图11所示。

从图11a、图11b可以看出,当环氧树脂板位于IGBT的两侧时,由于环氧树脂板热阻较大,产生了较大的温度梯度,导致IGBT温度为43.5℃,未能达到设定温度75℃。由图11c、图11d可以看出,当环氧树脂位于加热板与IGBT的两侧时,加热板与IGBT直接接触,同时环氧树脂板隔绝了大多数热量流动,保证了稳态情况下IGBT达到了设定温度75℃。另外需要说明的是IGBT的下极板为接地点,加热板不会受到高电压损坏的风险。

图11 压力夹具各组件温度分布计算结果

Fig.11 Calculation results of temperature distribution of each component in pressure fixture

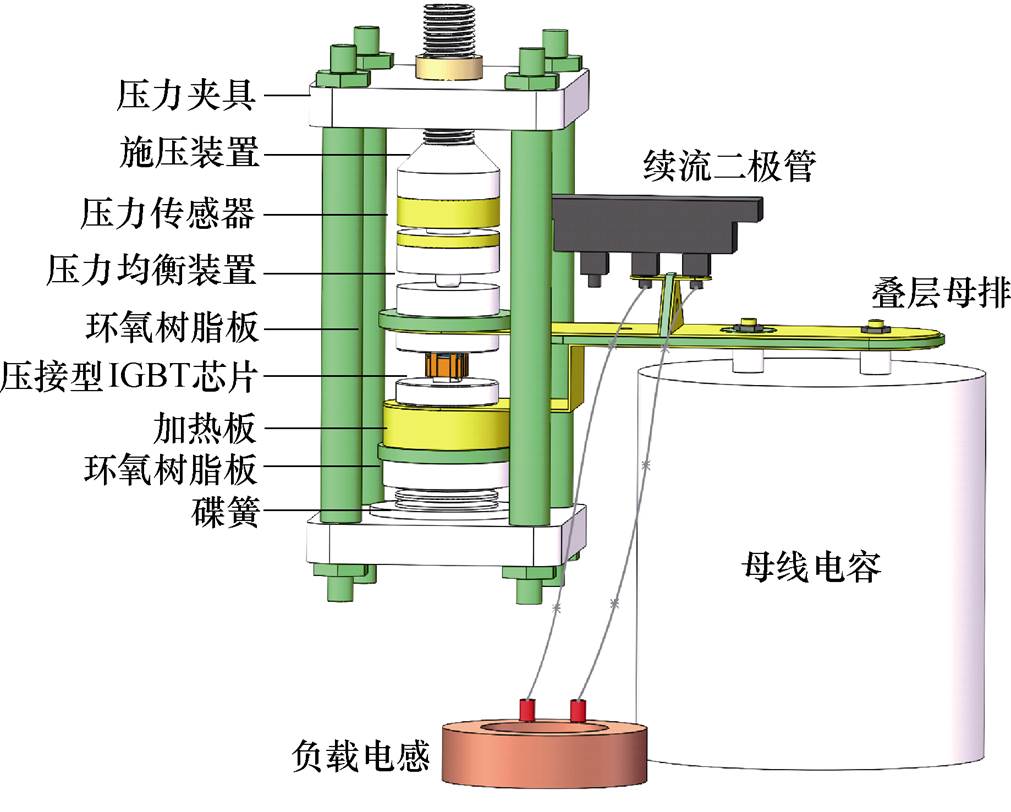

根据上述理论分析和计算,本文建立的双脉冲实验平台主体结构如图12所示。图12中,左侧从上到下依次为:压力夹具及施压装置共同作用提供压接型IGBT芯片所需的机械压力,压力传感器读取施加在IGBT芯片上的机械压力,压力均衡装置保证IGBT芯片表面受力均衡,环氧树脂板同时提供隔热和绝缘的作用,加热板提供实验所需温度,碟簧为压力夹具施加机械压力提供压力缓冲;右侧叠层母排提供实验回路的电气连接,母线电容型号为TDK4400K160D136,最高电压4.4kV,电容值为160μF,负载电感值为1mH。

图12 实验平台主体结构

Fig.12 Main structure of the experimental platform

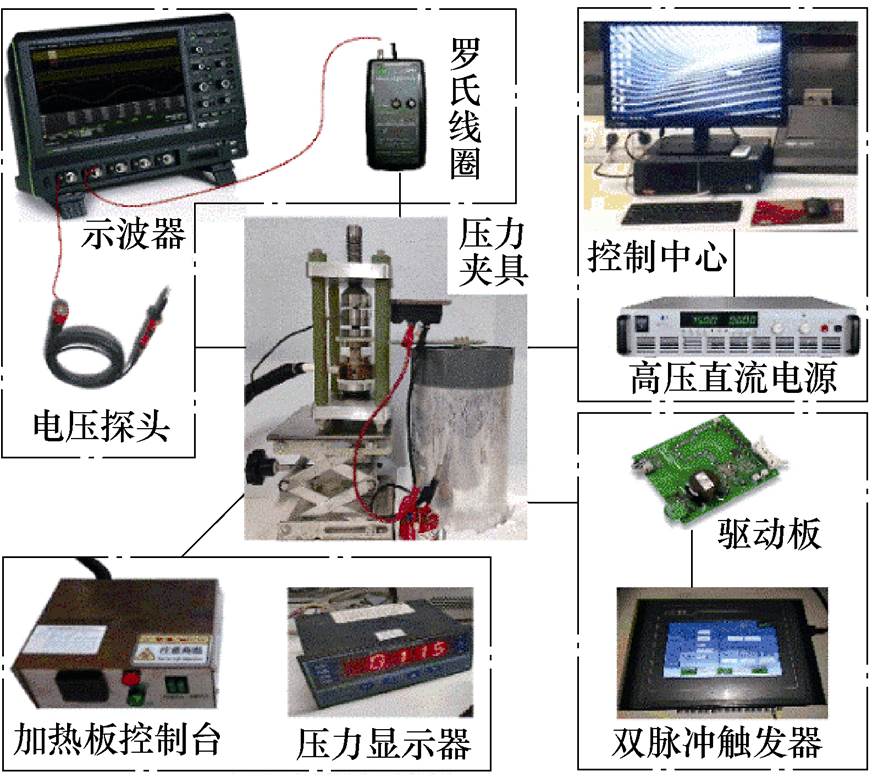

结合实验平台的测量部分及其辅助部分,双脉冲实验平台实物如图13所示。

图13 双脉冲实验平台实物

Fig.13 Physical diagram of double pulse test platform

图13中,测量部分包含:用来测量vCE的电压探头型号为PPE4kV;用来测量vGE的电压探头型号为PP018;用来测量电流的罗氏线圈型号为CWT- Ultra mini06,示波器型号为HDO4104A。辅助部分包含有:双脉冲触发器结合驱动板提供IGBT所需的驱动波形;高压直流电源型号为HPPS1217,可通过计算机远程调控为母线电容充电,电压范围为0~5kV;加热板控制台可以灵活调节并实时监测加热板温度,加热温度范围为25~250℃,调节精度为1℃;压力显示器可以实时显示机械压力的大小,压力范围为0~5kN,精度为0.01kN。

采用国产某型号3.3kV/50A的压接型IGBT芯片进行实验。为了验证本实验平台的相关功能完善性和可靠性,分别对电压过冲、压力分布、温度分布进行了实验测量,并且得到了电-热-力影响因素下压接型IGBT芯片的动态特性。

3.2.1 电压影响因素

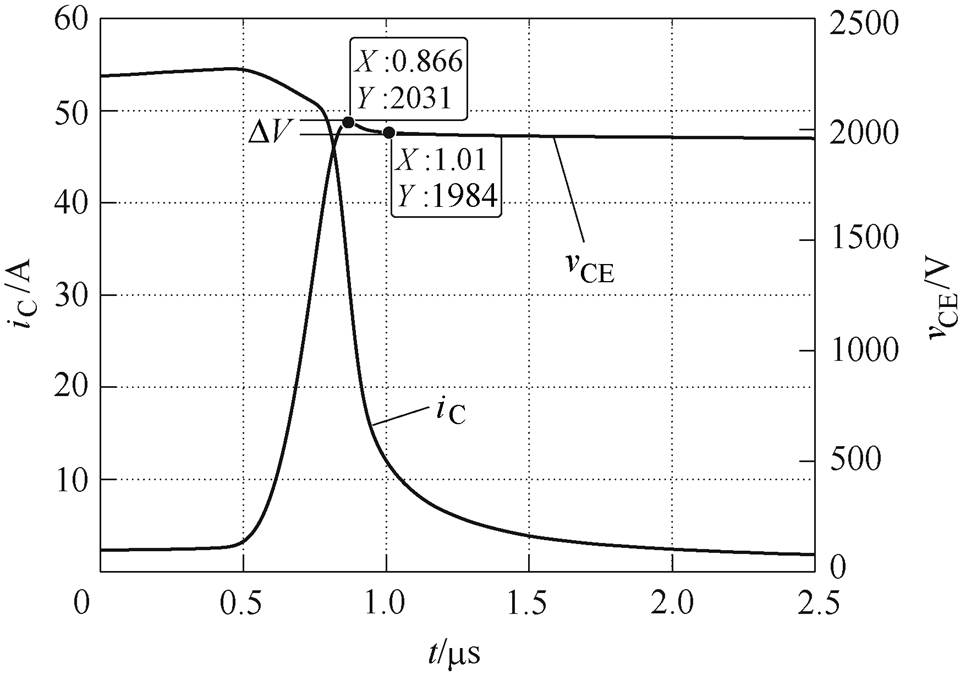

为了验证本文采用叠层母排的效果,在母线电压2kV、负载电流50A下进行实验,关断过程如图14所示。

观察得到电压过冲DV=47V,相比于母线电压2kV,IGBT芯片电压过冲百分比为2.35%,可以满足双脉冲实验的要求。根据双脉冲实验波形提取寄生电感方法[21],计算得到回路寄生电感为142.42nH,查数据手册得母线电容的寄生电感为60nH[22],续流二极管单桥臂的寄生电感为20nH[23],其中实验中续流二极管由两个桥臂串联连接,计算得母排寄生电感为42.42nH,与仿真结果45.60nH较为吻合。

图14 双脉冲实验电压过冲

Fig.14 Voltage overshoot of double pulse test

同时在不同母线电压下分别进行了实验,机械压力为1kN,温度为25℃,不同母线电压下动态特性如图15所示。

图15 不同母线电压下动态特性

Fig.15 Dynamic characteristics under different bus voltages

从图15可以看出,随着母线电压的升高,关断延时增大,二极管反向恢复电流引起的电流过冲增大。但在不同母线电压下,电流变化率几乎不变,电压过冲都能维持在较低的水平,均可以满足压接型IGBT芯片动态特性测试的需求。

3.2.2 压力影响因素

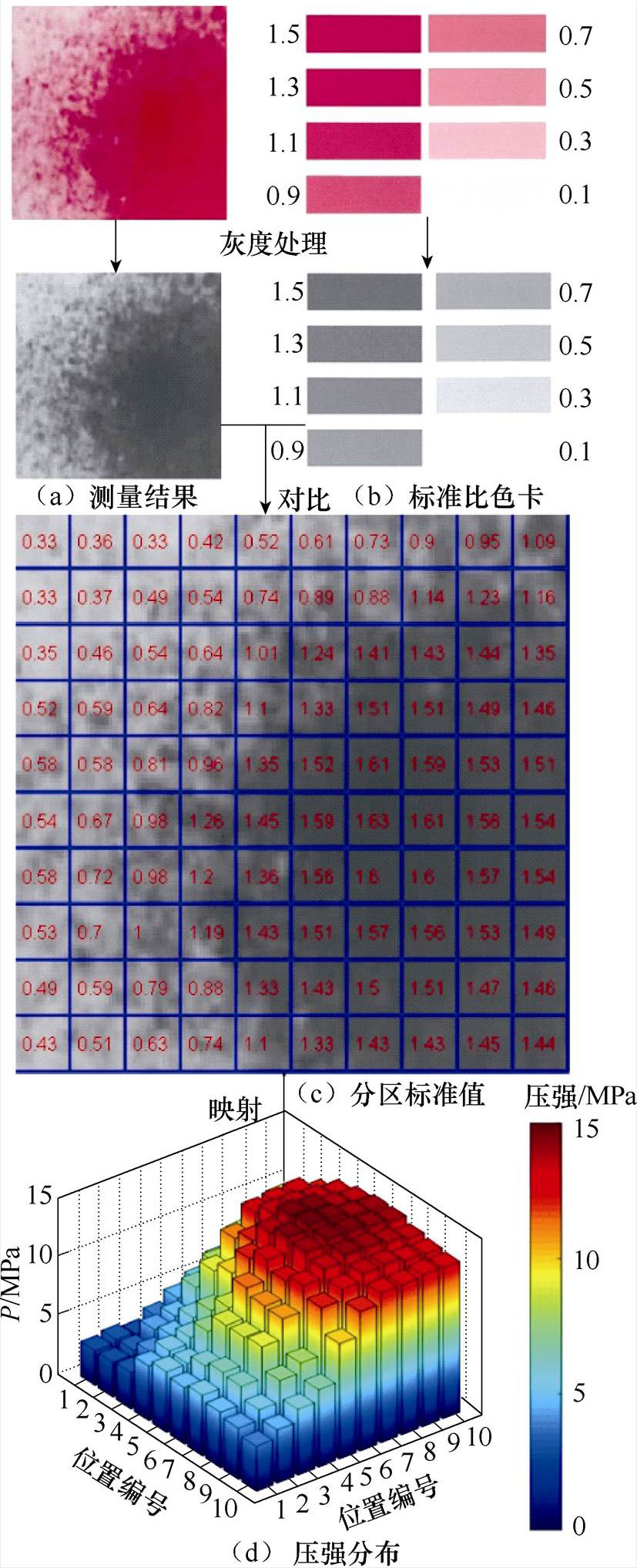

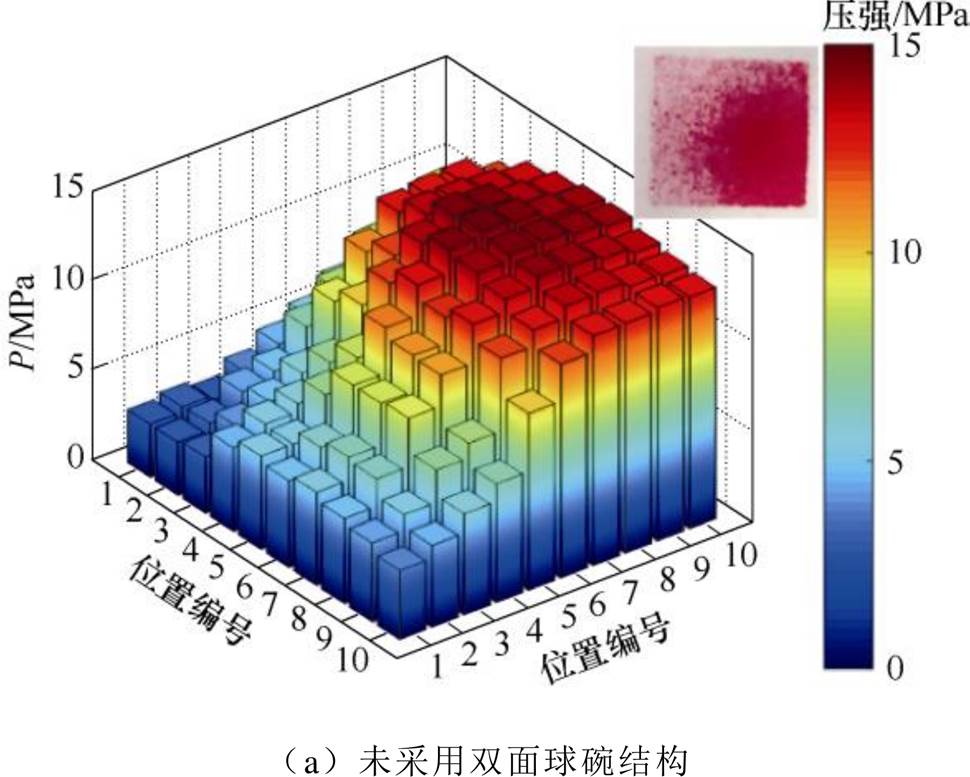

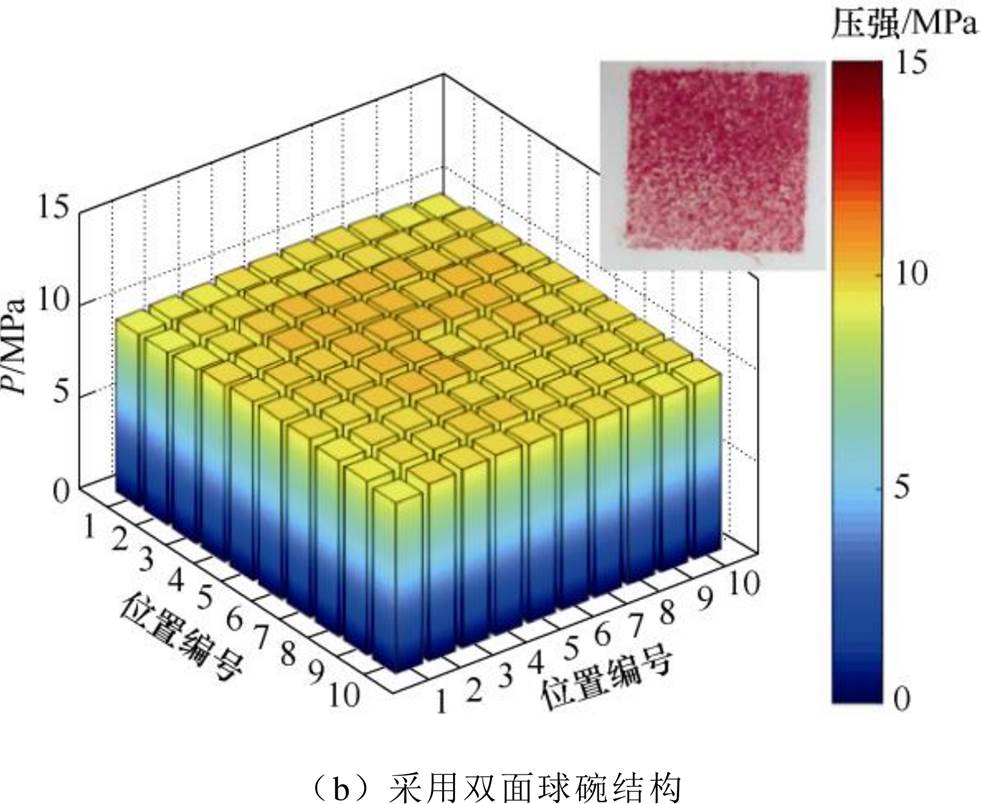

为了验证本文所提双面球碗结构的实际效果,通过Fuji压力纸测量压接型IGBT芯片表面的压力分布,可以通过压力纸颜色的深浅来定性表征压力分布的大小。设置两组实验分别为采用双面球碗结构和未采用双面球碗结构,同样施加1kN额定机械压力,压力值通过施压夹具中串联的压力传感器读取。为了更为直观地得到芯片表面压力分布,需要对Fuji压力纸进行灰度处理,其中以未采用双面球碗结构为例进行说明,灰度处理过程如图16所示,两种情况下的芯片表面压力分布结果如图17所示。

图16 压力纸灰度处理过程

Fig.16 Grayscale processing of pressure paper

图17 芯片表面压力分布实验结果

Fig.17 Experimental results of pressure distribution on the chip surface

由图17可以看出,当压力夹具中未加双面球碗结构时,压强最大值为14.67MPa,超出压强平均值10MPa的46.7%,其中36%的面积压强超过13MPa;当压力夹具中加入双面球碗结构后,压强最大值为10.26MPa,仅超出平均值2.6%,可以看出,双面球碗结构可以明显改善压接型IGBT芯片表面的压力分布,有效地避免了压接型IGBT芯片的边缘应力集中。

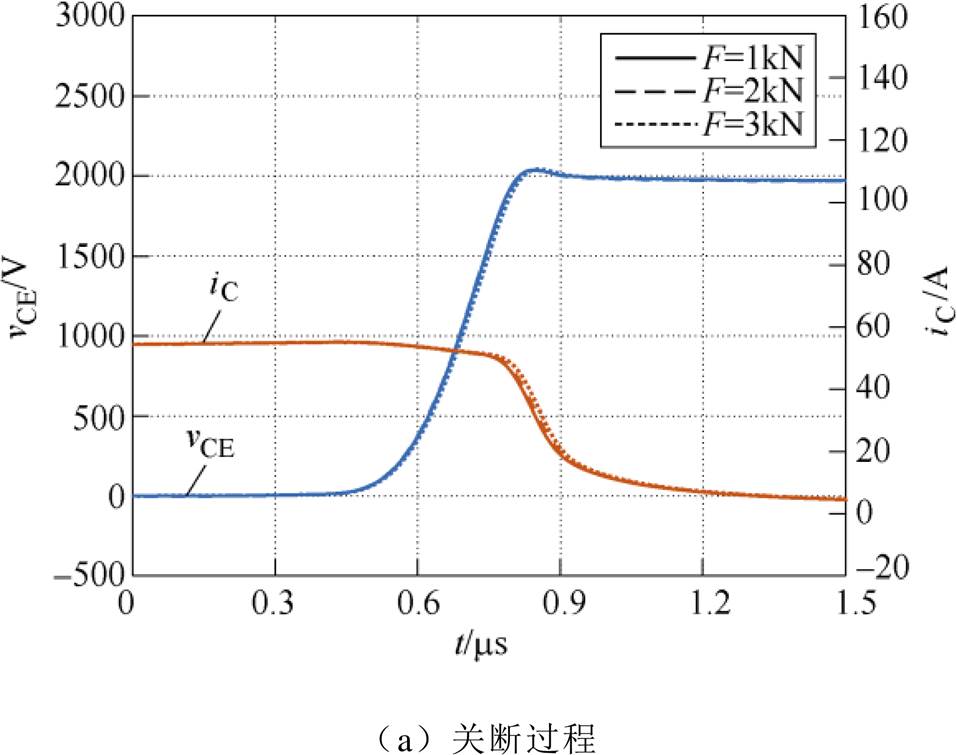

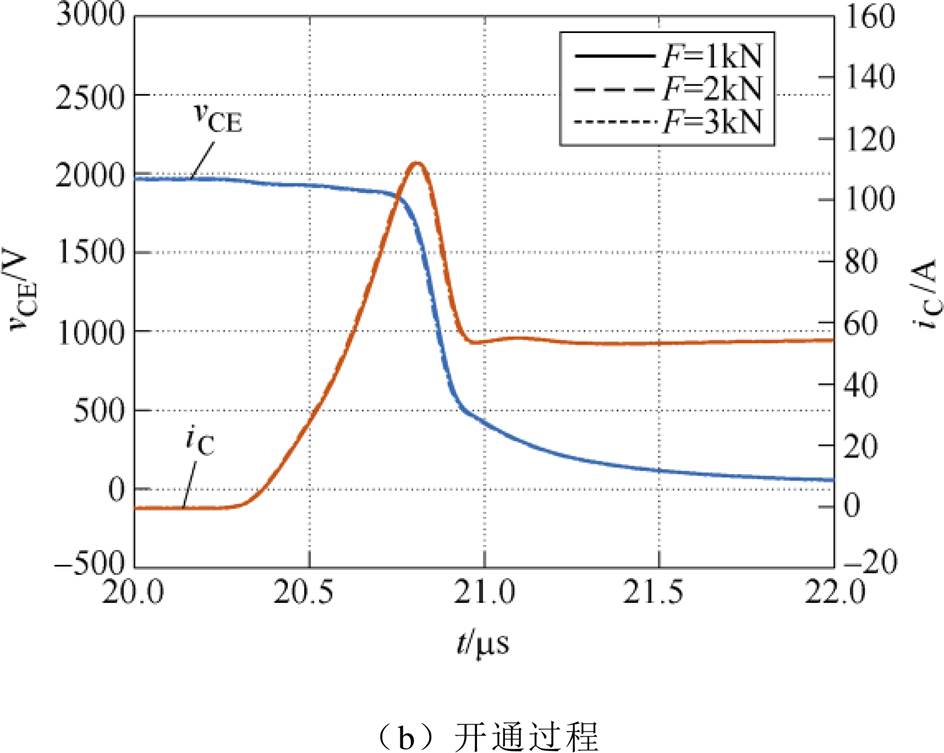

为了得到不同机械压力下压接型IGBT芯片的动态特性,分别设置机械压力为1kN、2kN及3kN,母线电压为2kV,负载电流为50A,温度为25℃,不同机械压力下动态特性如图18所示。

从图18可以看出,机械压力对IGBT芯片的开通和关断过程影响都很微弱。相比而言,机械压力对关断过程的影响大于对开通过程的影响,机械压力越大,电流关断时间越长。

图18 不同机械压力下动态特性

Fig.18 Dynamic characteristics under different pressures

3.2.3 温度影响因素

为了验证各组件温度分布的合理性,参考图11的三维有限元计算结果,设置环氧树脂板与仿真条件相同的两组实验,两组实验加热板温度同为75℃,通过FLIR E8红外热成像仪观察各组件的温度分布,机械夹具各组件温度分布实验结果如图19所示。

图19 机械夹具各组件温度分布实验结果

Fig.19 Experimental results of temperature distribution of each component in mechanical fixture

由图19可得,加热板设定温度为75℃,图19a中IGBT的温度为55.8℃,误差为25.60%,图19b中IGBT的温度为74.8℃,误差为0.27%。通过调整环氧树脂板的位置可以提高IGBT加热温度的精度。另外,需要说明的,是本实验平台相较于传统恒温箱加热的方式,更加灵活,同时克服了在恒温箱中进行实验,部分组件不耐高温的缺点。

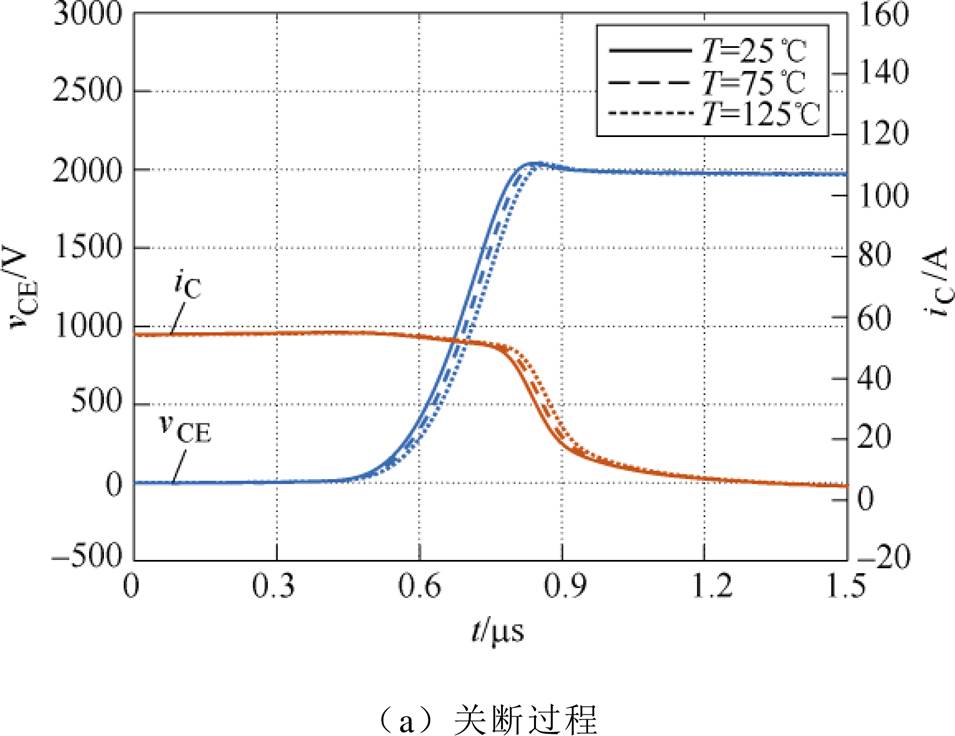

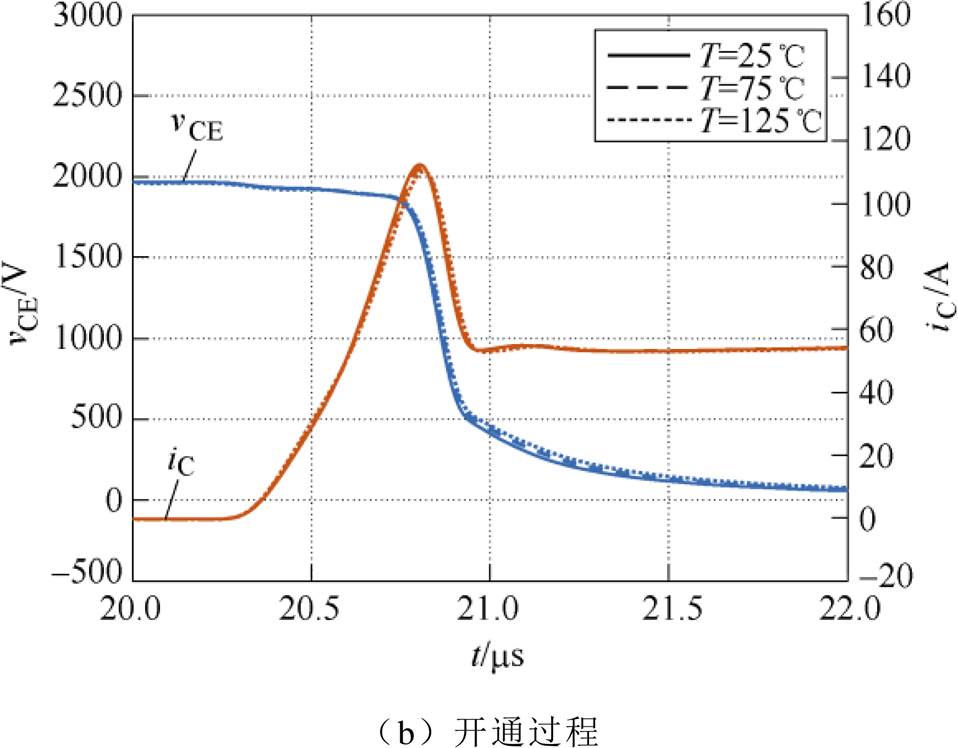

为了得到不同温度下压接型IGBT芯片的动态特性,分别设置温度为25℃、75℃和125℃,母线电压为2kV,机械压力为1kN,负载电流为50A,不同温度下动态特性如图20所示。

图20 不同温度下动态特性

Fig.20 Dynamic characteristics under different temperatures

从图20可以看出,温度主要影响关断过程,对开通过程影响不明显,且随着温度的升高,关断延时增大,电压过冲略微减小,开通过程电流过冲略微减小,电压拖尾时间增长。

以上实验结果验证了本实验平台具有寄生电感小、芯片表面压力分布均衡、实验夹具温度分布合理的特点,且具备多影响因素下电-热-力灵活可调的能力,满足了压接型IGBT芯片在不同条件下的实验需求。

本文针对电-热-力综合作用下压接型IGBT芯片动态特性测试需求,对实验平台的关键问题进行了仿真计算和实验验证。所研制平台具有回路寄生电感小、芯片表面受力均衡及机械夹具温度分布合理的特点,可以满足不同电压、机械压力及温度下压接型IGBT芯片动态特性测试的需求,为压接型IGBT芯片动态特性测试提供了实验基础。基于仿真分析和实验结果,可以得到以下结论:

1)通过叠层母排结构及合理的母排尺寸设计,减小了实验回路的寄生电感,实验测得本文母排的寄生电感仅为42.42nH,满足双脉冲测试的需求。

2)采用双面球碗结构有效地改善了压接型IGBT芯片表面受力不均的问题,实验结果表明,双面球碗结构使芯片表面受力不均衡度由46.7%降低到2.6%,在1~3倍额定机械压力下均能保证压接型IGBT芯片的安全测试。

3)采用环氧树脂板改善了压力夹具各组件温度分布,实验结果表明,合理的环氧树脂板位置使IGBT芯片结温误差由25.60%降低到0.27%,有效地减小了压接型IGBT芯片结温误差对动态特性测试的影响。

参考文献

[1] Baliga B J, Adler M S, Gray P V, et al. The insulated gate rectifier (IGR): a new power switching device[C]//International Electron Devices Meeting, San Francisco, CA, USA, 1982: 264-267.

[2] Iwamuro N, Laska T. IGBT history, state-of-the-art, and future prospects[J]. IEEE Transactions on Electron Devices, 2017, 64(3): 741-752.

[3] Shigekane H, Kirihata H, Uchida Y. Developments in modern high power semiconductor devices[C]//The 5th International Symposium on Power Semi- conductor Devices and ICS, Monterey, 1993: 16-21.

[4] Kirihata H, Takahashi Y, Wakimoto H, et al. Investigation of flat-pack IGBT reliability[C]//1998 IEEE Industry Applications Conference, St.louis, 1998: 1016-1021.

[5] Wakeman F, Lockwood G, Davies M, et al. Pressure contact IGBT, the ideal switch for high power appli- cations[C]//IEEE Industry Applications Conference, Phoenix, 1999: 700-707.

[6] 刘国友, 窦泽春, 罗海辉, 等. 高功率密度3600A/ 4500V压接型IGBT研制[J]. 中国电机工程学报, 2018, 38(16): 4855-4862.

Liu Guoyou, Dou Zechun, Luo Haihui, et al. Development of high power density 3600A/4500V press-pack IGBT[J]. Proceedings of the CSEE, 2018, 38(16): 4855-4862.

[7] Wu Rui, Smirnova L, Wang Huai, et al. Com- prehensive investigation on current imbalance among parallel chips inside MW-scale IGBT power modules[C]//2015 9th International Conference on Power Electronics and ECCE Asia, Seoul, 2015: 850-856.

[8] 黄先进, 凌超, 孙湖, 等. 多芯并联封装IGBT缺陷与失效先导判据[J]. 电工技术学报, 2019, 34(增刊2): 518-527.

Huang Xianjin, Ling Chao, Sun Hu, et al. The leading criterion for defects and failures in multi-chip parallel package IGBTs[J]. Transactions of China Electro- technical Society, 2019, 34(S2): 518-527.

[9] Li Helong, Zhou Wei, Wang Xiongfei, et al. Influence of paralleling dies and paralleling half-bridges on transient current distribution in multichip power modules[J]. IEEE Transactions on Power Electronics, 2018, 33(8): 6483-6487.

[10] Gu Miaosong, Cui Xiang, Tang Xinling, et al. An electro-thermo-mechanical model basing on experi- mental results for press-pack IGBT including mos side two-dimensional effects[C]//2019 IEEE Applied Power Electronics Conference and Exposition, Anaheim, 2019: 502-507.

[11] 张一鸣, 邓二平, 赵志斌, 等. 压接型IGBT器件封装内部多物理场耦合问题研究概述[J]. 中国电机工程学报, 2019, 39(21): 6351-6365.

Zhang Yiming, Deng Erping, Zhao Zhibin, et al. A review of the multiphysics coupling problem in press pack IGBT[J]. Proceedings of the CSEE, 2019, 39(21): 6351-6365.

[12] Lai Wei, Li Hui, Chen Minyou, et al. Investigation on the effects of unbalanced clamping force on multi-chip press pack IGBT modules[J]. IEEE Journal of Emerging and Selected Topics in Power Electro- nics, 2019, 7(4): 2314-2322.

[13] 贾英杰, 肖飞, 罗毅飞, 等. 基于场路耦合的大功率IGBT多速率电热联合仿真方法[J]. 电工技术学报, 2020, 35(9): 1952-1961.

Jia Yingjie,Xiao Fei, Luo Yifei, et al. Multi-rate electro-thermal simulation method for high power IGBT based on field-circuit coupling[J]. Transactions of China Electrotechnical Society, 2020, 35(9): 1952-1961.

[14] Luo Yifei, Xiao Fei, Liu Binli, et al. A physics-based transient electrothermal model of high-voltage press-pack IGBTs under HVDC interruption[J]. IEEE Transactions on Power Electronics, 2020, 35(6): 5660-5669.

[15] Belmehdi Y, Azzopardi S, Woirgard E, et al. A correlation between thermo-mechanical finite elements tool with electro-thermal finite elements tool: towards an electro-mechanical finite elements modeling for IGBT used in power assemblies[C]// 11th International Thermal, Mechanical & Multi- Physics Simulation and Experiments in Micro- electronics and Microsystems, Bordeaux, 2010: 1-5.

[16] 刘盛福, 常垚, 李武华, 等. 压接式IGBT模块的动态特性测试平台设计及杂散参数提取[J]. 电工技术学报, 2017, 32(22): 50-57.

Liu Shengfu, Chang Yao, Li Wuhua, et al. Dynamic switching characteristics test platform design and parasitic parameter extraction of press-pack IGBT modules[J]. Transactions of China Electrotechnical Society, 2017, 32(22): 50-57.

[17] 邓真宇, 陈民铀, 赖伟, 等. 多芯片并联压接式IGBT热-力不均对电流分布的影响分析及建模[J]. 中国电机工程学报, 2020, 40(23): 7699- 7710.

Deng Zhenyu, Chen Minyou, Lai Wei, et al. Analysis and modeling of the influence of thermal-force unevenness of multi-chip parallel press-pack IGBT devices on current distribution[J]. Proceedings of the CSEE, 2020, 40(23): 7699-7710.

[18] IEC-60747-9 Semiconductor devices-discrete devices, Part 9: insulated-gate bipolar transistors (IGBTs)[S]. British Standard, 2007.

[19] Tinschert L, Ardal A R, Poller T, et al. Possible failure modes in press-pack IGBTs[J]. Micro- electronics Reliability, 2015, 55(6): 903-911.

[20] 周静, 康升扬, 李辉, 等. 内部压力不均对压接式IGBT器件电热特性的影响分析[J]. 电工技术学报, 2019, 34(16): 3408-3415.

Zhou Jing, Kang Shengyang, Li Hui, et al. Simulation of influence of unbalanced clamping force on electro- thermal characteristics of press-pack IGBT devices[J]. Transactions of China Electrotechnical Society, 2019, 34(16): 3408-3415.

[21] 唐新灵, 张璧君, 张语, 等. IGBT动态测试平台杂散电感提取方法[J]. 电网技术, 2020, 44(4): 1267-1275.

Tang Xinling, Zhang Bijun, Zhang Yu, et al. Stray inductance extraction method of IGBT dynamic test platform[J]. Power System Technology, 2020, 44(4): 1267-1275.

[22] IXYS corporation press-pack IGBT’s devices, assemblies & supporting products/New-DC link capacitors[Z]. IUK-TSM-2015-003 Issue 4[2016-05-23].

[23] Infineon corporation technical information, FF400R12KT3[Z]. Datasheet.[2013-10-03].

Design and Implementation of an Experimental Platform for Dynamic Characteristics of Press-Pack IGBT Chip

Abstract The press-pack IGBT chip is subjected to the comprehensive action of electro- thermo-mechanical under normal operating conditions. The study of the dynamic characteristics of IGBT chip under the influence of electro-thermo-mechanical is of great significance for guiding the modeling of IGBT chips and the design of large-scale IGBT parallel packaging. In order to obtain the dynamic characteristics of the press-pack IGBT chip under the comprehensive influence of electro- thermo-mechanical, in this paper, an experimental platform with a flexible electro-thermo-mechanical adjustment for the dynamic characteristics of the press-pack IGBT chip is developed, combined with the principle of the double pulse test circuit. Through the finite element simulation of the key problems of the dynamic characteristic experimental platform, the optimal design of parasitic inductance, IGBT chip surface pressure distribution and mechanical fixture temperature distribution is realized. On this basis, an experimental platform for dynamic characteristics of press-pack IGBT chip is established. Through comprehensive testing of the dynamic characteristic experimental platform, it is shown that the experimental platform has the characteristics of small parasitic inductance, balanced pressure distribution on the IGBT chip surface, and reasonable temperature distribution of each component of the mechanical fixture, which can meet the requirements of the dynamic characteristic test of the press-pack IGBT chip under comprehensive electro-thermo-mechanical influence.

keywords:Press-pack IGBT chip, dynamic characteristics, parasitic inductance, temperature, mechanical pressure

中图分类号:TN307

DOI: 10.19595/j.cnki.1000-6753.tces.201445

国家自然科学基金-国家电网公司联合基金重点项目(U1766219)和国家电网有限公司科技项目(520201190095)资助。

收稿日期 2020-11-01

改稿日期 2020-12-17

彭 程 男,1993年生,博士研究生,研究方向高压大功率半导体器件测试与封装技术。E-mail: pengcheng@ncepu.cn

李学宝 男,1988年生,博士,副教授,研究方向为先进输电技术、电力系统电磁环境与电磁兼容、高压大功率半导体器件封装技术。E-mail: lxb08357x@ncepu.edu.cn(通信作者)

(编辑 陈 诚)