图1 SiC MOSFET串联短路故障电路原理

Fig.1 Principle of SiC MOSFET series short-circuit test

摘要 在电力电子系统中,因器件击穿、硬件电路缺陷或系统控制失误导致碳化硅(SiC)金属氧化物半导体场效应晶体管(MOSFET)误开通时,桥臂电流回路中多个器件处于开通状态,形成串联短路故障。该文以SiC MOSFET半桥电路为研究对象,详细介绍SiC MOSFET串联短路的动态过程,理论分析负载电流、栅极驱动电压和结温温升对SiC MOSFET短路动态特性的影响规律,推导出SiC MOSFET分压模型,并采用仿真模型进行验证。实验基于1 200V/80A SiC MOSFET测试平台验证电路参数对短路损耗和结温分布的影响。理论与实验结果表明,SiC MOSFET串联短路分压特性对电路参数具有较高敏感度,漏极电压与漏极电流不平衡动态变化会改变器件短路损耗,进而影响结温温升,造成串联短路SiC MOSFET不稳定变化。

关键词:SiC MOSFET 串联短路 分压特性 结温分布

SiC MOSFET作为新一代功率半导体器件,正处在快速商业化发展阶段。SiC MOSFET因其具有高开关速率、低开关损耗、高击穿电压、高热导率等特点,已被广泛应用于新能源汽车、太阳能、风能变换器、无线电能传输等领域[1-5]。但是,SiC MOSFET的挑战是与优势共存的[6-8],尤其是在以短路故障为代表的极端故障下,高压、大电流、高结温所带来的冲击严重影响了器件的性能。在高栅极电压下,SiC MOSFET发生短路故障时产生的短路电流是额定电流的数倍甚至10倍以上。退饱和效应导致的高漏极电压使得器件结温在极短的时间内迅速上升,大幅降低SiC MOSFET的短路耐受水平。器件内P基区、N-漂移区的高电场促使高空穴电流注入栅氧化层形成栅极泄漏电流,结温温升则进一步增大泄漏电流,造成栅氧化层退化甚至击穿。由于焊料层与芯片热膨胀系数不同,高温度梯度下形成强烈的热冲击,产生热切应力,导致焊料层疲劳,减少功率器件的寿命,给功率变换器的可靠运行带来极大的挑战[9-13]。因此,为保证SiC MOSFET器件的可靠运行,有必要对造成器件短路的故障因素及其影响规律进行详细研究。

依据电流回路电感值将SiC MOSFET短路分为两种故障形式:硬开关故障(Hard Switching Fault, HSF)和负载短路故障(Fault Under Load, FUL)[14-15]。HSF电流回路的电感极小,器件在开通瞬态便发生短路故障,漏-源极承受高母线电压;FUL电流回路的电感略高,器件在进入导通状态后形成短路,漏-源极电压由导通压降迅速上升至高电压。针对SiC MOSFET的短路特性,国内外学者展开一系列研究。文献[16-19]的分析结果表明,栅极驱动电压决定了SiC MOSFET短路电流等级,短路电流的上升速率则与驱动参数有关。文献[20-21]的研究结果表明,SiC MOSFET短路电流在低温下具有正温度系数,而在高温下具有负温度系数。文献[22-23]对CREE和ROHM商业1.2kV SiC MOSFET进行短路耐受能力检测,结果表明高母线电压及高环境温度下,器件在3ms短路时间内便会出现明显的栅极泄漏电流,说明SiC MOSFET的短路耐受时间极短。

上述关于SiC MOSFET短路特性的研究是基于单个器件进行的,其短路特点在于SiC MOSFET漏源极几乎承受全部母线电压。然而在功率变换系统运行过程中,因硬件电路缺陷或控制失误导致SiC MOSFET误开通时,上、下桥臂器件将同时短路。采用半桥电路进行短路实验时发现,短路回路中的SiC MOSFET会出现动态分压行为,其分压特性易受电路参数和结温的影响。

本文首先介绍SiC MOSFET串联短路工作特性。分别针对负载电流、驱动电压和结温对SiC MOSFET串联短路分压特性的影响规律进行理论分析。选取罗姆公司的BSM080D12P2C008 SiC MOSFET半桥模块作为测试对象进行仿真验证并对串联器件耐受水平进行评估。最后通过实验分析并验证电路参数变化对器件损耗及结温的影响。

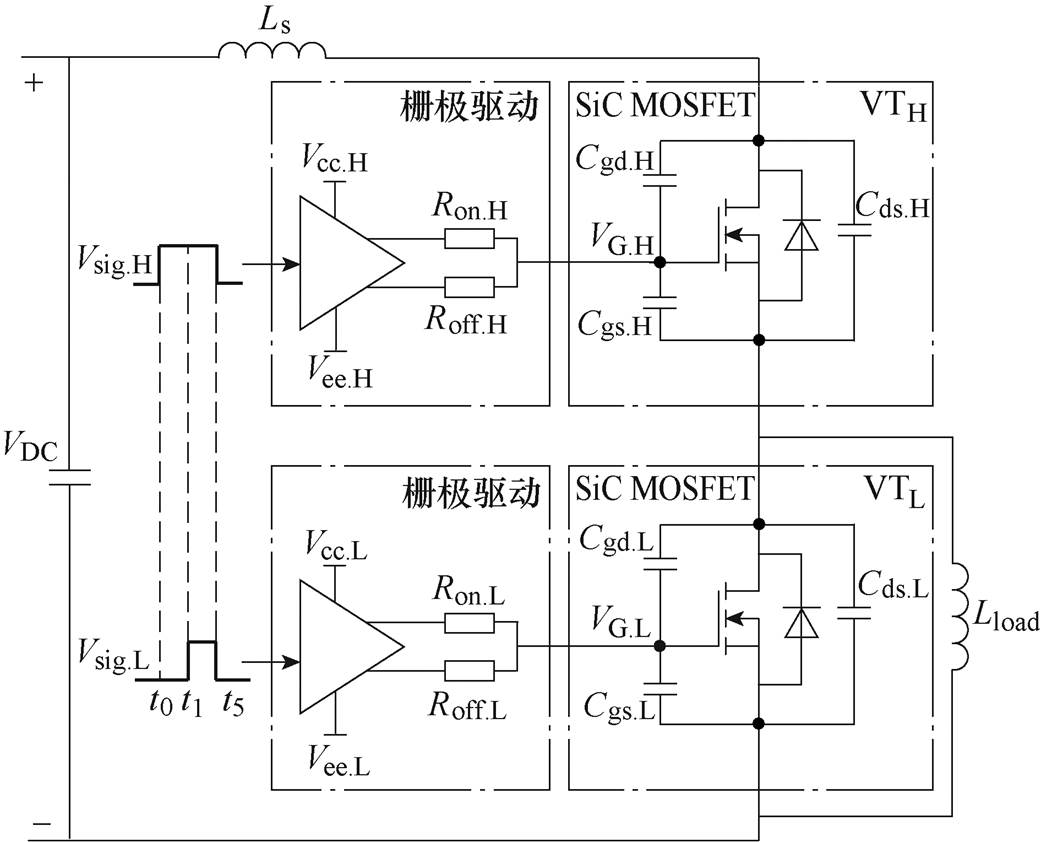

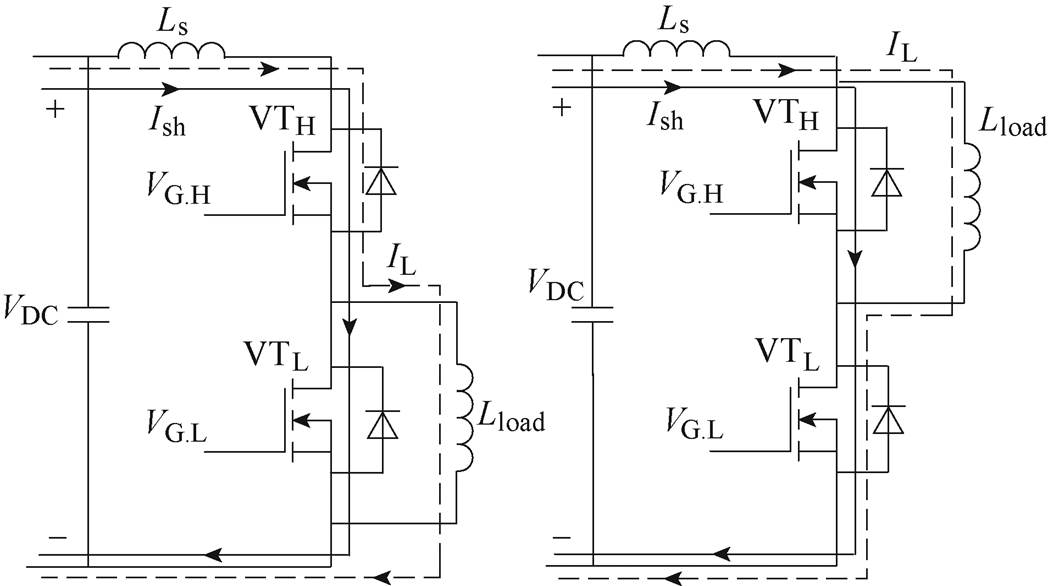

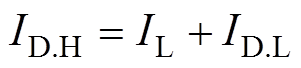

SiC MOSFET半桥串联短路故障电路原理如图1所示。VTH与VTL为待测SiC MOSFET器件。栅极驱动器在接受到开关信号Vsig.x(x=H, L)后,向SiC MOSFET栅极提供正驱动电压Vcc.x和负驱动电压Vee.x实现器件的开通和关断。Ron.x为栅极开通电阻,Roff.x为栅极关断电阻,Ls为等效杂散电感,VDC为母线电压,负载电感Lload与VTL并联。Cgs.x、Cgd.x、Cds.x为器件的结电容。

图1 SiC MOSFET串联短路故障电路原理

Fig.1 Principle of SiC MOSFET series short-circuit test

串联短路故障的测试原理为:首先在t0时刻,Vsig.H转换为高电平,栅极驱动开通VTH,VDC通过VTH向负载Lload充电,产生负载电流IL。随后在t1时刻,Vsig.L转换为高电平,驱动开通VTL,形成串联短路。IL的大小可通过改变t0~t1的时间间隔进行调节,在极短的时间间隔内IL≈0A。最后在经过设定好的短路时间后,同时关断VTH与VTL。

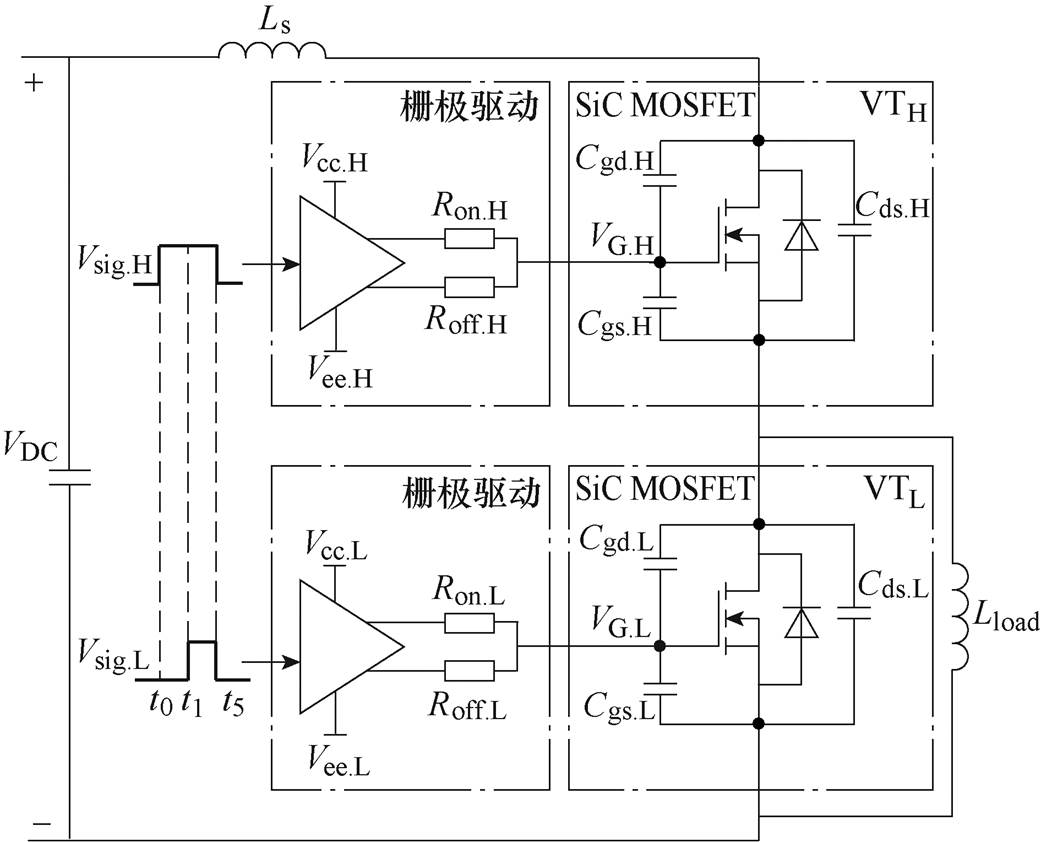

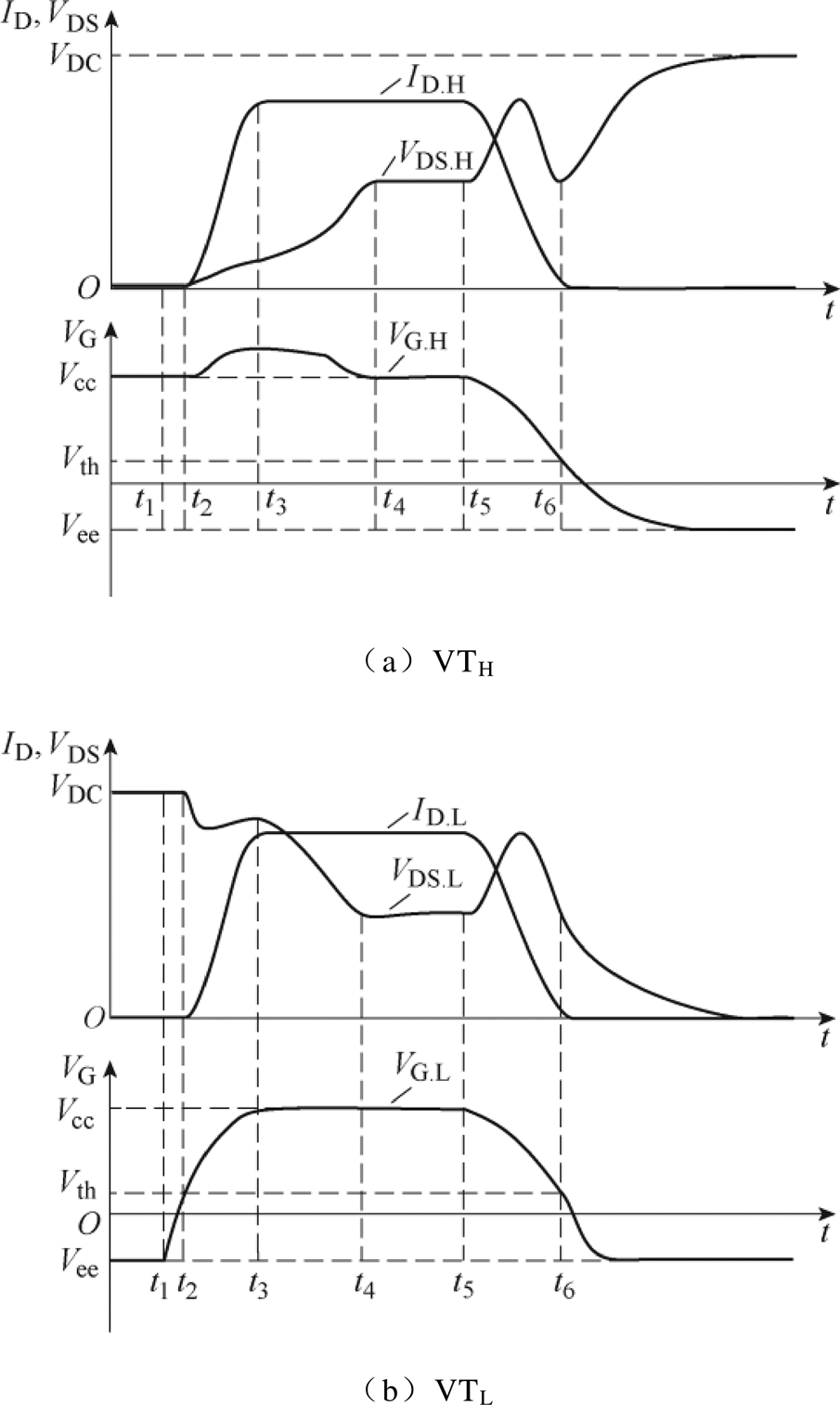

理想情况下,VTH与VTL开通时驱动参数相同,即Vcc.H=Vcc.L,Ron.H=Ron.L,Roff.H=Roff.L。VTH与VTL的短路动态过程由t1时刻开始,分为四个阶段,串联短路波形示意图如图2所示。

图2 串联短路波形示意图

Fig.2 Schematic diagram of short-circuit waveforms

1)开通延迟阶段[t1, t2]

在t1时刻,VTL的栅极电压VG.L开始上升,VTH和VTL的工作状态保持不变。此刻,VTH为正常导通状态,栅极电压VG.H=Vcc,漏极电流IDS.H=IL≈0A。VTL为关断状态,漏源极电压VDS.L=VDC,漏极电流IDS.L=0A。

2)电流上升阶段[t2, t3]

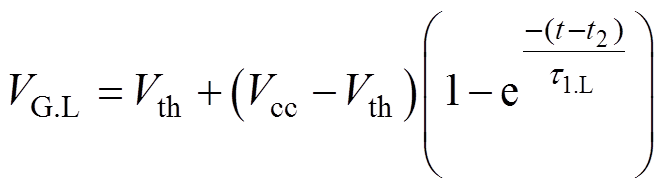

在t2时刻,VG.L上升至阈值电压Vth,短路电流Ish迅速上升,VTL的栅极电压VG.L表示为

(1)

(1)式中,t1.L为VTL栅极时间常数,t1.L=Ron.LCgs.L。

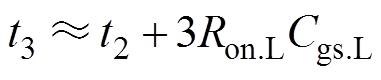

在t3时刻,VG.L基本上升至Vcc,短路电流建立完毕。在电路理论上,该阶段所建立的栅极电路模型为阻容串联电路,其稳定时间约为3倍的栅极时间常数,即

(2)

(2)可以看出,在外加栅极电阻和栅极电容不变的情况下,该阶段时间保持不变。

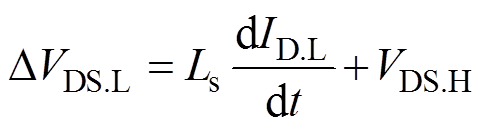

短路电流的上升使得VTH的导通压降上升,相应的VTL漏源极电压有所降低。受短路电流回路等效杂散电感Ls的影响,VTL出现电压缺口DVDS.L为

(3)

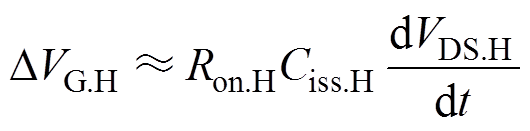

(3)此外VTH导通压降通过栅-漏极电容Cgd.H向栅极充电,导致栅极电压VG.H>Vcc,形成栅极过电压尖峰DVG.H,即

(4)

(4)

式中,Ciss.H为VTH输入电容,Ciss.H=Cgs.H+Cgd.H。

3)分压阶段[t3, t5]

在短路电流建立后,VTH与VTL形成串联直通,母线电压将由这两个器件共同承担,VTH与VTL出现动态分压现象。VDS.H开始快速上升,相应地,VDS.L开始下降,在忽略结温温升的理想情况下,VTH与VTL在t4时刻均分母线电压,在动态分压的过程中,VTH的栅极通过Ron.H放电,最终栅极电压尖峰DVG.H消失,即

(5)

(5)此外,在分压过程中,VTH与VTL均承受高电压,该阶段漏极电流ID.H和ID.L表示为

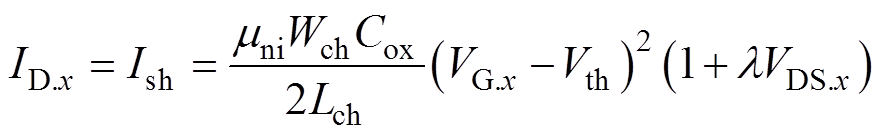

(6)

(6)

式中,Ish为短路电流;l 为沟道夹断系数;mni为沟道载流子迁移速率;Lch为沟道长度;Wch为沟道宽度;Cox为栅氧化层等效电容。

然而在实际串联短路现象中,VTH与VTL不同短路状态下漏极电压差异导致损耗上升速率不同。在损耗差异的影响下,VTH与VTL的结温出现了偏差。饱和电流受到器件结温差异的影响而发生变化,漏极电压也发生动态变化,分压效果变得不稳定。

4)关断阶段[t5, t6]

在t5时刻将VTH与VTL同时关断。短路电流Ish立即下降,受杂散电感的影响,VTH与VTL的漏极电压出现过电压尖峰,理想状态下,VTH过电压尖峰Vpk.H与VTL过电压尖峰Vpk.L一致,即

(7)

(7)在t6时刻VG.H与VG.L下降至阈值电压Vth,短路电流降为0A。由于负载电感Lload与VTL并联,VDS.H上升至全母线电压。此刻VTH与VTL已经处于关断状态,漏极电压的变化速率取决于负载电感的大小,即负载电感越大,漏极电压变化越缓。

本节将分析负载电流、驱动电压以及结温温升对串联短路分压特性的影响,建立器件分压模型,并进行仿真分析。

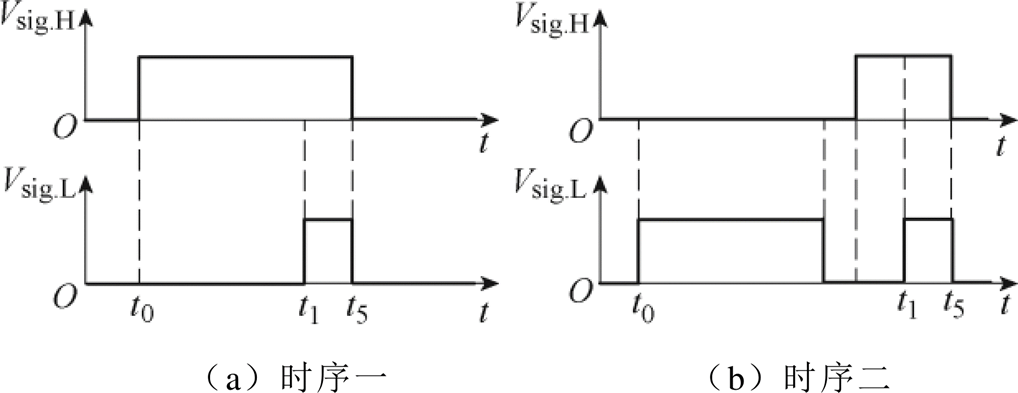

串联短路时负载电流的存在使得流过VTH与VTL的漏极电流ID.H和ID.L不相等。在测试中为了产生正、反向的负载电流IL,需要对VTH与VTL的开关脉冲进行调整,形成正、反向负载电流的开关时序如图3所示。时序脉冲形成的短路电流Ish与负载电流IL路径如图4所示。

图3 形成正、反向负载电流的开关时序

Fig.3 Switching sequence to form positive and negative load currents

图4 短路电流Ish与负载电流IL路径

Fig.4 Short-circuit current and load current path

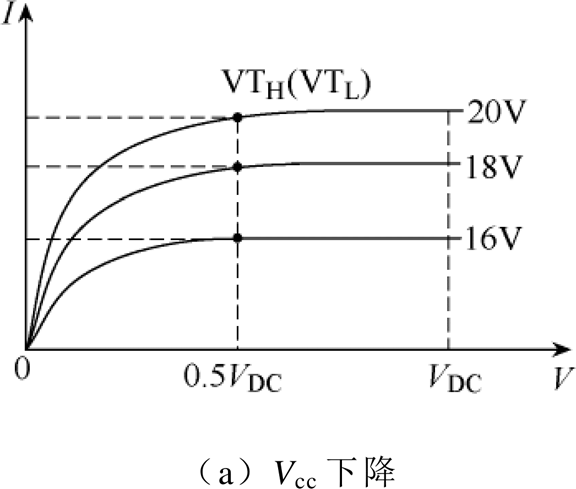

在图3a所示的时序脉冲一中,延长t0~t1的时间使IL上升,并从半桥中性端流出,设为正向电流。当IL达到预定值后,再将VTL开通。在图3b所示的时序脉冲二中,需要将负载电感与VTH并联,如图4b所示。首先将VTL开通,母线电压向负载充电,IL流入半桥中性端,设为反向电流。同样延长t0~t1的时间,当负载电流达到预定值后,将VTL关断,随后将VTH开通,当VTH完全导通后,在t1时刻,将VTL再次开通。有负载电流时VTH和VTL的输出特性如图5所示。

图5 有负载电流时VTH和VTL的输出特性

Fig.5 The output characteristics of VTH and VTL with load current

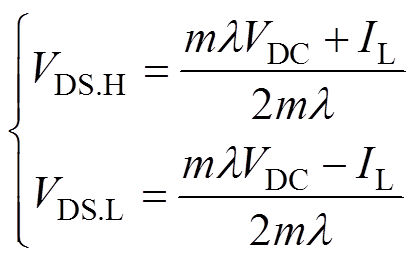

由于负载电感过高,在极短的短路过程中负载电流基本保持不变。负载电流的存在使得VTH与VTL漏极电流不同,ID.H和ID.L的关系为

(8)

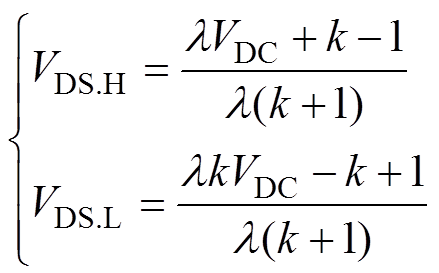

(8)由式(6)和式(8)计算VTH与VTL分压稳定后VDS.H与VDS.L分别为

(9)

(9)

其中

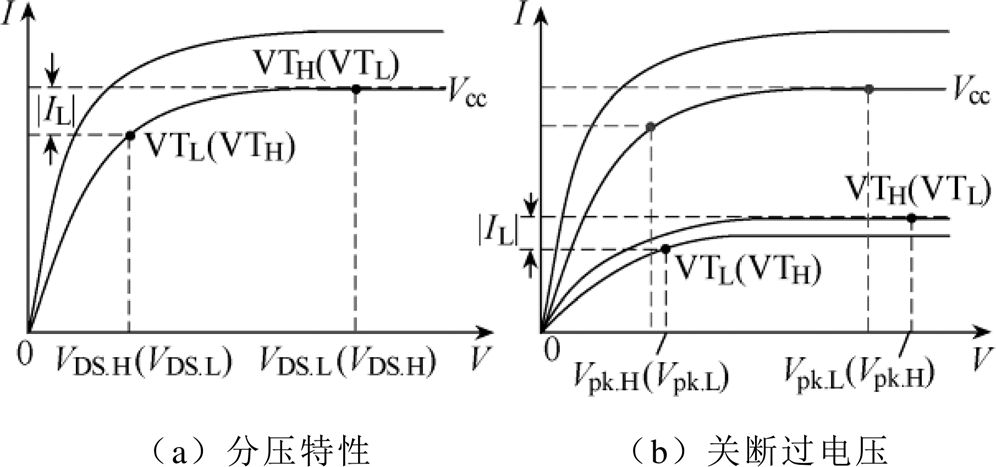

由式(9)可知,当IL=0A时,VDS.H=VDS.L=0.5VDC,即VTH与VTL均分母线电压;当IL>0A时,VDS.H>VDS.L,即VTH承受更多的母线电压;而当IL<0A时,分压情况正好相反。其分压特性表现在SiC MOSFET输出特性时如图5a所示,在相同的栅极电压下,漏极电流大的器件分担更多的母线电压,导致VTH与VTL无法均压。随着IL的增大,不均压程度恶化。

正、反向负载电流对串联短路影响仿真波形如图6所示。正向负载电流下SiC MOSFET串联短路仿真波形如图6a所示,IL依次为40A、80A、160A和240A。在电流上升阶段,VTL驱动参数不变,ID.L上升速率不受影响。在分压阶段,ID.L随负载电流的增加而下降至Ish-IL,ID.H基本保持Ish不变,由于VTH承担更多的母线电压,VDS.H由导通压降上升至高于半母线电压的过程中与VDS.L出现交叉,交叉点位于半母线电压处。在关断过程中,随着VG.H的降低,由于ID.H>ID.L,VTL栅极电压VG.L下降速率快于VTH栅极电压VG.H。由图5b可知,在电流下降过程中,VTH承担更高的电压尖峰。需要注意的是,当负载电流较大时,VTH过电压尖峰会超过母线电压,较大杂散电感下,增加了VTH过电压击穿的风险。

图6 正、反向负载电流对串联短路影响仿真波形

Fig.6 Simulation waveforms of the effect of positive and negative load currents on short-circuit

当IL为反向电流时,VTH与VTL的分压效果与正向电流时相反,如图6b所示。IL分别为-40A,-80A,-160A和-240A。在电流上升阶段,ID.L上升至Ish后保持稳定,ID.H则上升至Ish-IL。在进入分压阶段,由于ID.L>ID.H,VTL分担更多的母线电压,因而VTH与VTL漏极电压无交叉点。在关断过程中,VG.L下降速率慢于VG.H,VTL承受更高的电压尖峰,因而在较大杂散电感下,会增加VTL过电压击穿的风险。

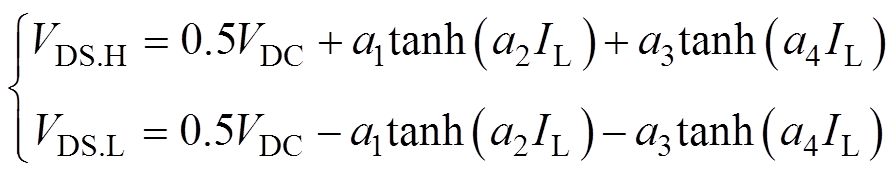

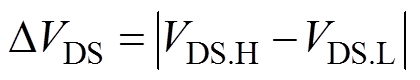

分压阶段VDS.H和VDS.L受负载电流影响曲线如图7所示。变化趋势呈双曲正切函数,拟合曲线可设为

(10)

(10)式中,a1~a4为拟合系数,在本文仿真条件下,a1= 135,a2=0.006,a3=80,a4=0.02。

设VTH与VTL的漏极电压差DVDS为

(11)

(11)则DVDS随负载电流IL的变化速率为

图7 负载电流IL与漏极电压VDS.x关系曲线

Fig.7 Relation curves of IL versus VDS.x

(12)

(12)图7所示的DVDS的变化表明,在发生串联短路时,VTH与VTL的分压特性对负载电流的敏感度较高。

在功率变换系统中,由于负载电流多为正弦变化,当发生串联短路时,VTH与VTL无法均压,其中一个器件会分担更多的母线电压,在负载电流过高时,该器件将承受绝大部分母线电压。

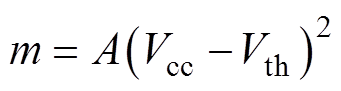

SiC MOSFET的饱和电流由栅极电压决定,因而在驱动电压降低时,短路电流随之减小。当VTH与VTL出现驱动电压差异时,同样会影响串联短路分压特性。将式(6)中的VG.x分别用Vcc.H和Vcc.L代替,计算出VTH与VTL的漏极电压分别为

(13)

(13)其中

由式(13)可知,当同时降低VTH与VTL驱动电压并保证驱动电压一致时,k=1,VDS.H=VDS.L= 0.5VDC;当仅降低Vcc.H时,k<1,VDS.H分担更多的母线电压;而仅降低Vcc.L时,k>1,VDS.L分担更多的母线电压。

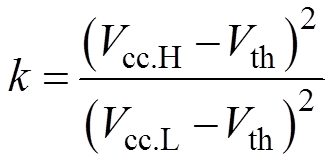

驱动电压变化下VTH与VTL输出特性如图8所示,在驱动电压Vcc下降时,由图8a可知,Ish会随之降低,但因Vcc.H=Vcc.L,VTH与VTL仍会保持均压状态。当VTH与VTL驱动电压不一致时,由图8b可知,栅极电压较小的器件决定了Ish的大小,并分担较多的母线电压。随着驱动电压差DVG(DVG= VG.H-VG.L)的增大,VTH与VTL不均压程度将恶化。

图8 驱动电压变化下VTH与VTL输出特性

Fig.8 The output characteristic of VTH and VTL under the driving voltage variation

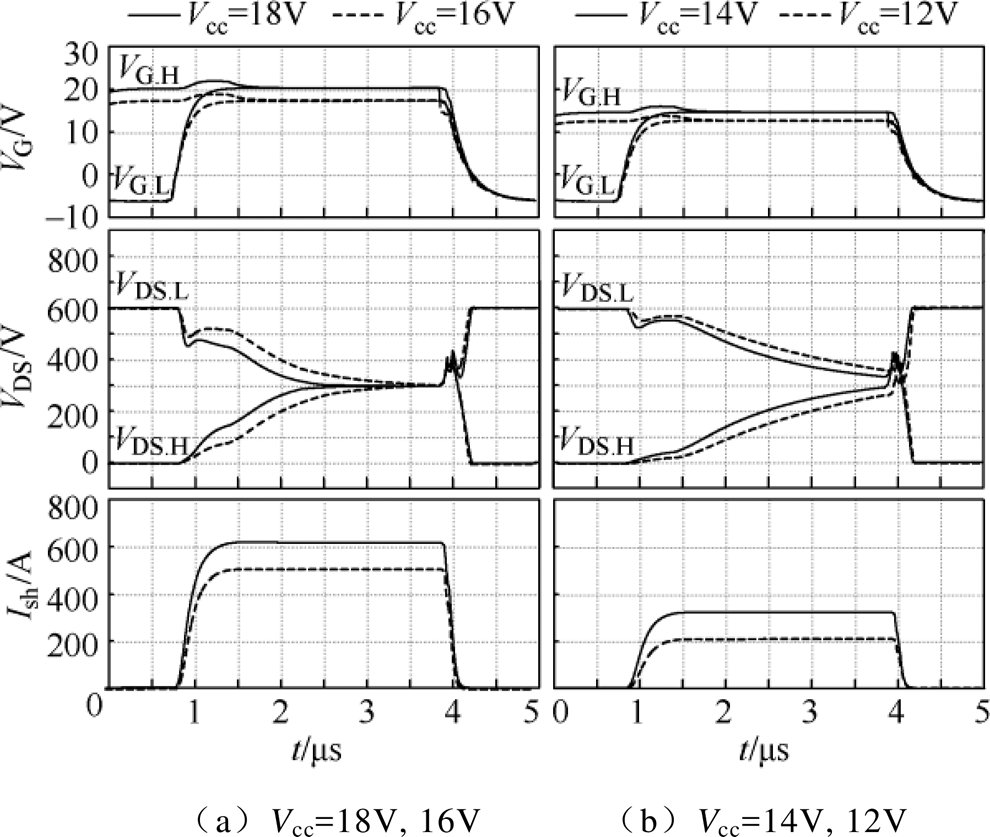

图9为驱动电压Vcc对串联短路影响仿真波形。Vcc依次设为18V、16V、14V和12V。由于VTL的栅极时间常数不变,Vcc的减小不会影响电流上升阶段的时长,但因栅极电压上升减缓,漏极电流与电压变化速率降低。Ish上升速率的减小,使得杂散电感Ls的感应电动势与VTH导通压降下降,VTL的电压缺口有所减小。在分压阶段,漏极电压变化速率的减缓,导致VTH与VTL达到半母线电压的时刻向后推迟。在分压结束后,VTH与VTL仍会保持均压状态,但若驱动电压过低,即当Vcc=12V或10V时,分压完成时刻超过短路时间,VTH与VTL还没有完成分压,短路便已结束。

图9 驱动电压Vcc对串联短路影响仿真波形

Fig.9 Simulation waveforms of the effect of driving voltage Vcc on short-circuit

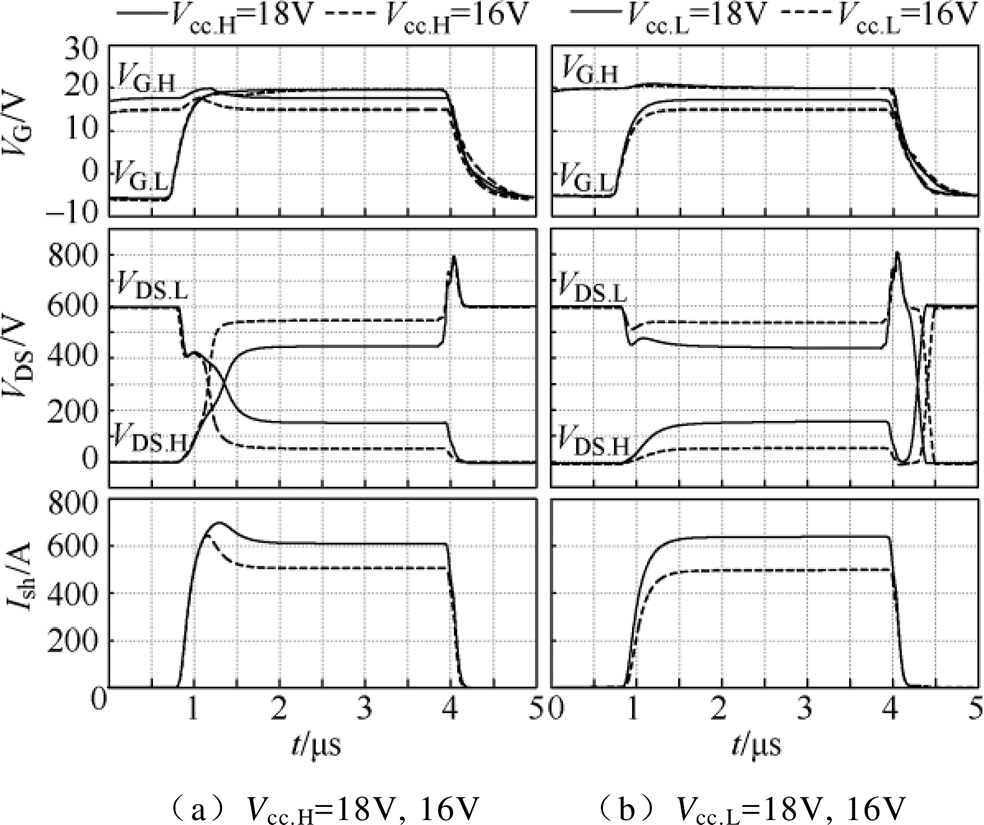

Vcc.H与Vcc.L对串联短路影响仿真波形如图10所示。Vcc.H依次设为18V和16V,Vcc.L保持为20V。由于Vcc.H<Vcc.L,Ish受到Vcc.H的抑制而减小。在电流上升阶段,VTH栅极过电压尖峰暂时提高了最大饱和电流,形成短路电流尖峰,随后在分压阶段,短路电流迅速下降,VTH将分担更多的母线电压,导致VTH与VTL的漏极电压出现交叉。此外在关断过程中,VTH将承受过高的过电压尖峰,甚至超过了母线电压,在高杂散电感下增加了VTH过电压击穿的风险。

图10 Vcc.H与Vcc.L对串联短路影响仿真波形

Fig.10 Simulation waveforms of the effect of driving voltage Vcc.H and Vcc.L on short-circuit

降低驱动电压Vcc.L至18V和16V,Vcc.H保持为20V时,Ish受Vcc.L的抑制,其分压特性与降低Vcc.H时正好相反。由于Vcc.L<Vcc.H,VTL将始终分担较多的母线电压,因而VTH与VTL漏极电压无交叉点。同样在关断过程中,VTL产生过高的过电压尖峰,在高杂散电感下增加了VTL过电压击穿的风险。

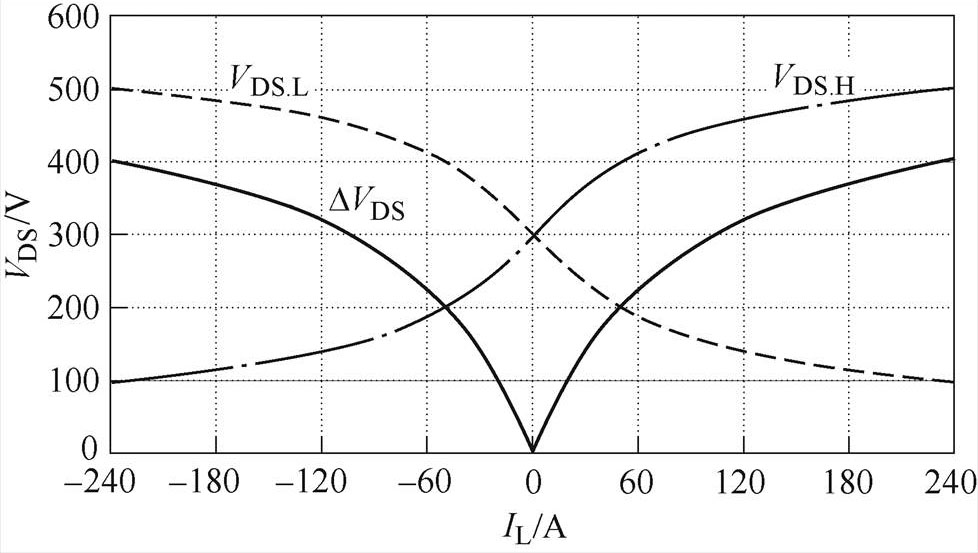

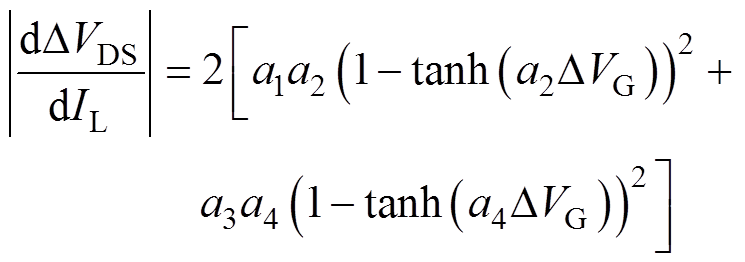

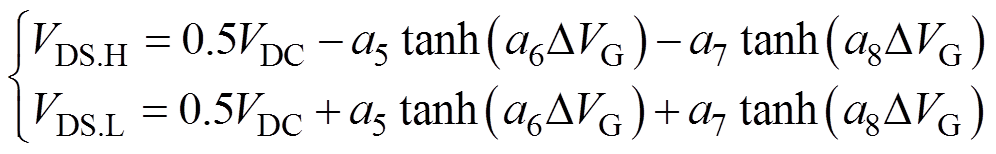

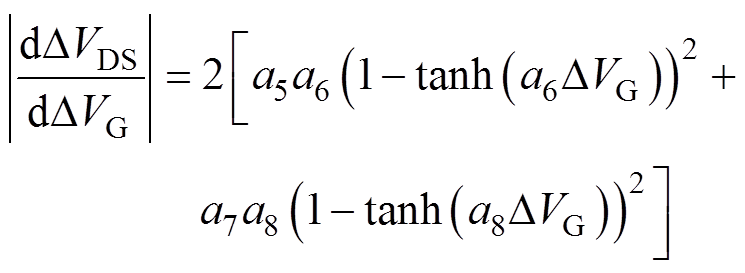

VTH与VTL的漏极电压随驱动电压差DVG的变化曲线如图11所示,VDS.H和VDS.L与DVG呈双曲线函数关系,其拟合曲线设为

(14)

(14)式中,a5~a8为拟合系数,在本文仿真条件下,a5= 146,a6=0.4,a7=142,a8=2.8。

VTH与VTL漏极电压差DVDS随栅极电压差DVG的变化速率表示为

图11 驱动电压差DVG与VDS.x关系曲线

Fig.11 Relation curves between VDS.x and DVG

(15)

(15)随着DVG的增大,DVDS增加幅度逐渐减小。同时在DVG较小的情况下,DVG略微增加都会导致VTH与VTL严重的分压不均。该曲线说明串联短路时VTH和VTL的分压特性对驱动电压差有较高的敏 感度。

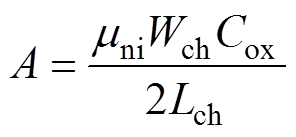

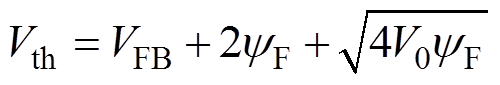

上述分析在不考虑结温温升的理想条件下进行,有利于展现电路参数对串联短路分压特性的影响。然而实际串联短路过程中,高电压大电流产生的耗散功率在数ms内全部加在芯片上,导致结温Tj迅速上升,改变器件的工作特性。温度影响短路特性的主要因素为阈值电压Vth和沟道迁移率mni的温度相关性。阈值电压Vth的表达式为

(16)

(16)式中,VFB为平带电压;V0为常数,由半导体中掺杂质量分数和氧化层厚度决定;ΨF为费米势,是半导体禁带中间能级和费米能级之间的电势差,随着温度的升高,费米能级逐渐向禁带中线靠拢,导致形成反型层所需能带弯曲表面势2yF降低,因而Vth具有负温度特性。

对于N型SiC MOSFET,沟道自由电子在运输过程中受到体晶格散射、声光子散射、表面粗糙度散射和库伦散射的影响[12],形成四种不同的载流子迁移率。其中库伦散射形成的载流子迁移率具有正温度系数,声子散射形成的载流子迁移率具有负温度系数。在短路初期,Tj较低,沟道载流子迁移率主要受库伦散射的影响。由式(6)可知,低温下mni与Vth的温度效应共同导致短路电流增大,此时SiC MOSFET呈正温度特性。随着Tj的继续上升,声子散射所占的比重增加,弱化了库伦散射正温度效应,短路电流上升幅度减小甚至开始下降,SiC MOSFET转为负温度特性。

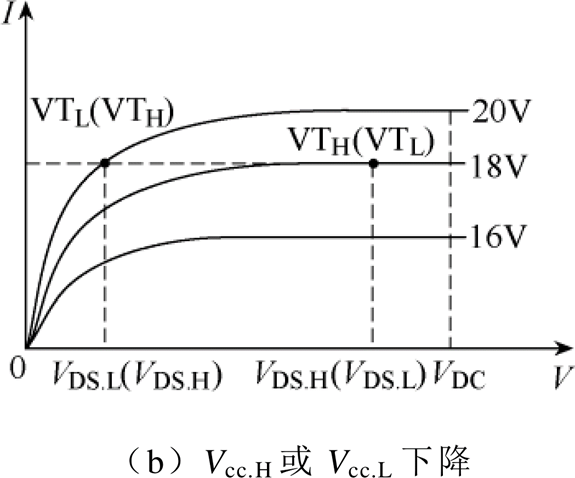

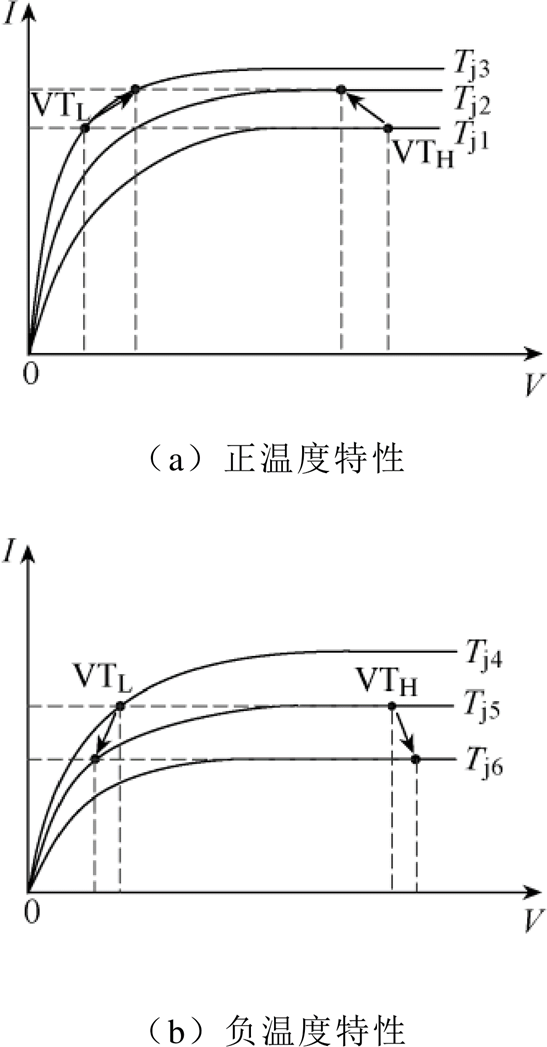

由图12所示的正、负温度效应下输出特性曲线可知,当器件呈正温度特性时,Ish由结温较低的器件决定,该器件承受较高的母线电压,但随着VTH与VTL结温同时上升,器件分压不均程度减弱。当器件呈负温度特性时,Ish由结温较高的器件决定,该器件承受较高的母线电压,且随着器件结温的上升,器件分压不均程度恶化。

图12 正、负温度效应下输出特性曲线(Tj1<Tj2<Tj3<Tj4<Tj5<Tj6

Fig.12 The output characteristic curves under positive and negative temperature coefficient (Tj1<Tj2<Tj3<Tj4<Tj5<Tj6)

结温Tj对串联短路影响仿真波形如图13所示,在电流上升阶段,受漏极电压的主要影响,VTH与VTL的结温出现偏差,使得器件载流子迁移速率不同。在结温较低时,Ish呈正温度系数。由于电流上升阶段VTL承受绝大部分母线电压,VTH的结温Tj.H小于VTL的结温Tj.L,因而短路电流由VTH决定。在进入分压阶段,由于Tj.H<Tj.L,VTL承担较少的母线电压,VTH与VTL漏极电压到达交叉点后,VDS.L将继续下降。随后,由于VDS.L<VDS.H,VTH与VTL的结温差DTj(DTj=|Tj.H-Tj.L|)开始缩小,VDS.H与VDS.L在达到波峰或波谷之后向半母线电压合拢。

随着短路时间的推移,当结温较高时,Ish逐渐趋向于负温度特性,短路电流随着温升由上升转为下降状态,VTH与VTL的漏极电压发生反向变化,仿真中VDS.H上升,VDS.L逐渐减小,进一步扩大了器件的结温差。若短路时间继续增加,VDS.H承受大部分母线电压,且因结温过高产生的泄漏电流对器件造成严重的损伤。

图13 结温Tj对串联短路影响仿真波形

Fig.13 Simulation waveforms of the effect of Tj

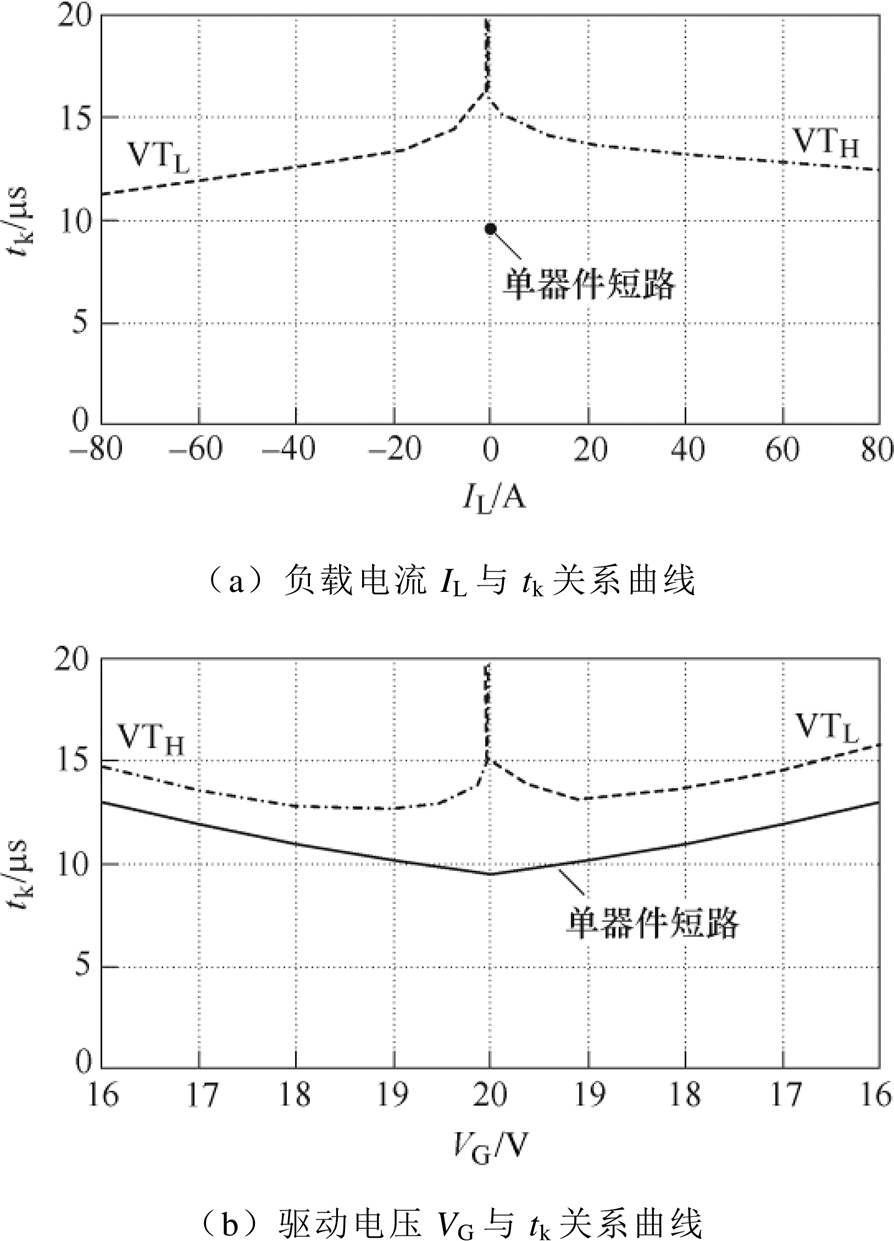

在研究SiC MOSFET单器件的短路特性时,由于待测器件承受全母线电压,大短路电流下,结温极速上升,待测器件在极短的时间内达到临界温度,表现出低短路耐受水平。相对于SiC MOSFET串联短路特性,由第2节的分析可知,VTH与VTL敏感的分压特性会使串联短路损耗被分解,减缓了结温温升。由于在不同初始条件即负载电流或驱动电压下,串联器件的动态分压变化较大,导致短路耐受水平呈现出不固定性。通常当短路器件结温上升至1 000℃左右时可能对该器件造成损伤[22],因而本文以Tj=1 000℃为结温节点作为评价短路耐受水平参考值,在不同初始条件下,tk为VTH与VTL上升至该节点的短路时间,初始条件对串联短路器件耐受水平影响如图14所示。

受短路电流负温度特性的影响,VTH与VTL仅有其中一个能够达到该结温节点。在IL=0A,Vcc.H= Vcc.L=20V的条件下,VTH达到了该结温,短路时间为15.2ms,高于相同驱动条件下单器件短路仿真结果的9.6ms,主要原因在于短路初期VTH与VTL较好的均压效果减缓了结温的温升,从而提高了器件的短路耐受时间。在图14a中,随着负载电流正向增加,短路时间有所减小,在IL=80A时,tk降至12.4ms。而当负载电流为反向电流时,结温节点转移至VTL,短路时间同样随着负载电流反向增加而减小,在IL=-80A时,tk降至11.2ms。当改变驱动电压时,在图14b中,结温节点出现在驱动电压较小的器件上。当VTL与VTH驱动电压差|DVG|<1V时,短路前期均压效果变差导致tk有所降低,而随着|DVG|持续增大,短路电流大幅降低,tk反向上升。与图中实线所示单器件驱动电压降低的短路仿真结果相比,串联器件的短路时间仍然较长,主要原因在于,驱动电压较高的器件承受数十伏的导通电压,在一定程度上分担了短路损耗。

图14 初始条件对串联短路器件耐受水平影响

Fig.14 Influence of initial conditions on the withstand level of series short circuit devices

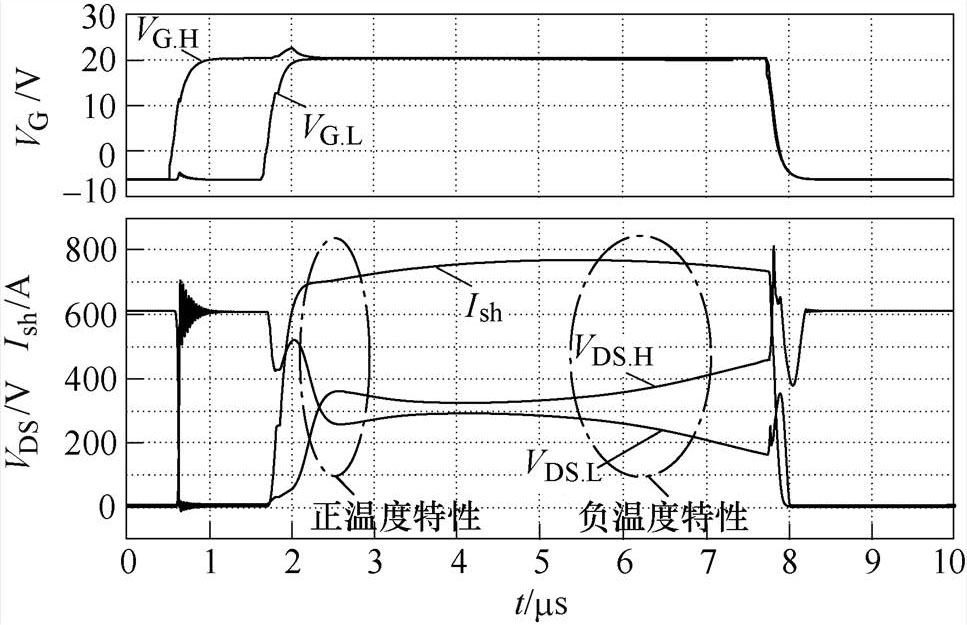

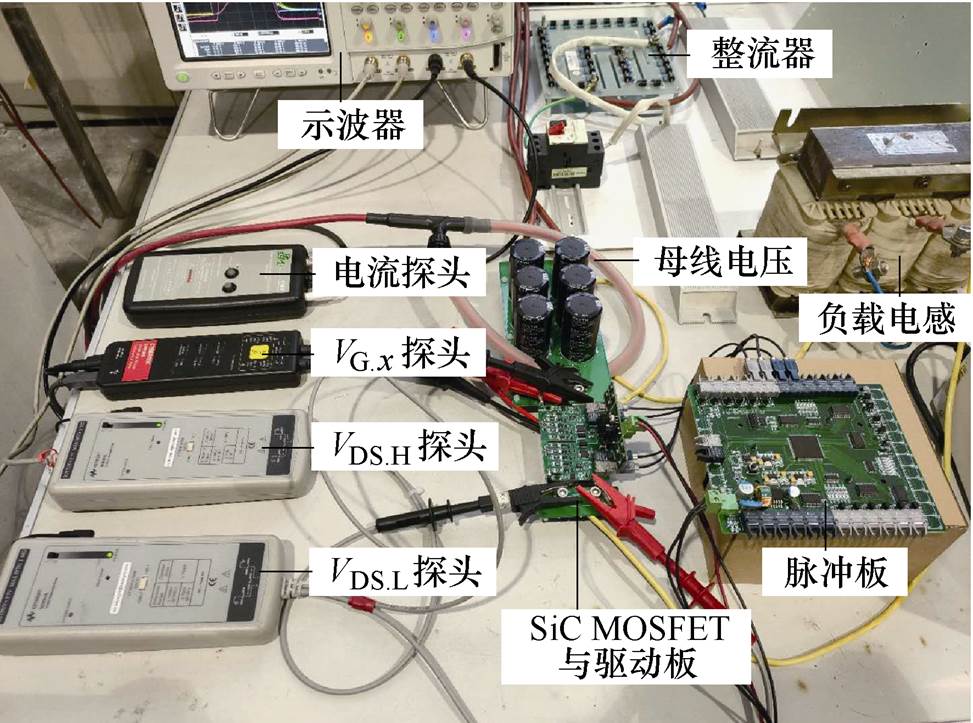

搭建SiC MOSFET串联短路实验平台如图15所示,采用SiC MOSFET半桥模块BSM080D12P2C008为实验对象,实验初始条件为Vcc.x=20V,Vee.x=-5V,Ron.x=10W,Roff.x=20W,VDC=600V,Lload=300mH。

图15 SiC MOSFET串联短路实验平台

Fig.15 SiC MOSFET series short-circuit test platform

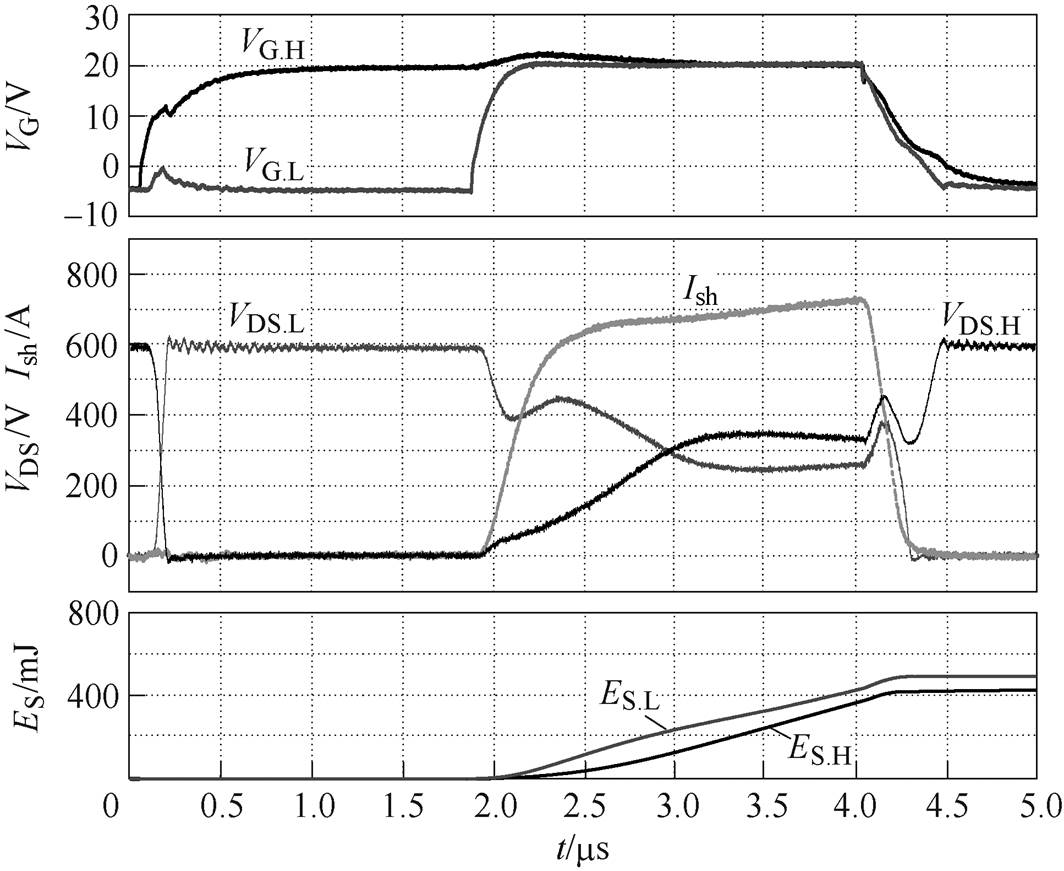

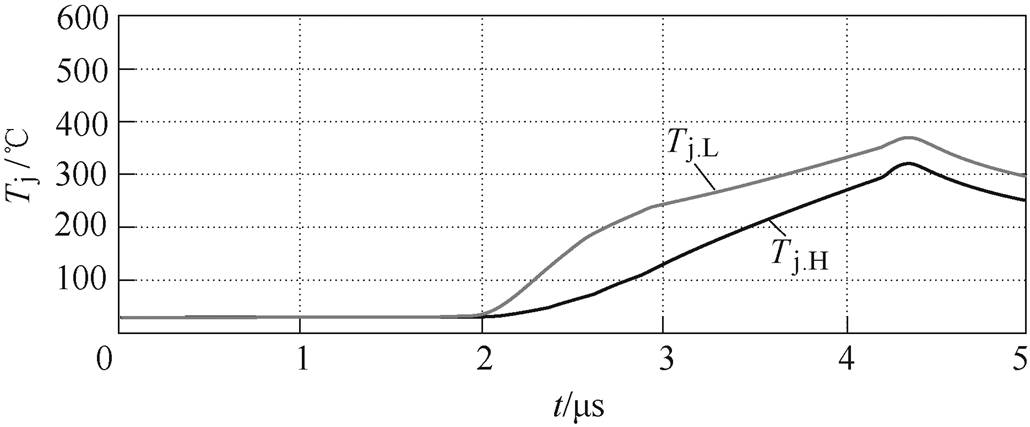

为了保护SiC MOSFET模块不被损坏且可重复使用,将短路检测时间设置为2ms。利用FPGA脉冲分配板产生时序脉冲控制SiC MOSFET的开通与关断。SiC MOSFET串联短路实验波形如图16所示。短路电流上升至680A后进入分压阶段,受VTH与VTL正温度特性影响,短路电流随着短路持续时间的增加而缓慢上升。在短路初期VDS.L>VDS.H,VTL短路损耗ES.L上升速率较高。在短路故障发生约1ms时,VDS.H与VDS.L出现交叉点,随后VDS.L<VDS.H,ES.L上升速率将小于VTH短路损耗ES.H上升速率,结温温差逐渐缩小。在短路故障发生1.4ms时,VDS.L降到波谷240V,相应地,VDS.H上升至波峰360V。由于结温差的缩小,VTH与VTL的漏极电压开始朝半母线电压合拢。最终在关断后,ES.H和ES.L分别为430mJ和490mJ。

图16 SiC MOSFET串联短路实验波形

Fig.16 Experimental waveforms of SiC MOSFET on series short-circuit

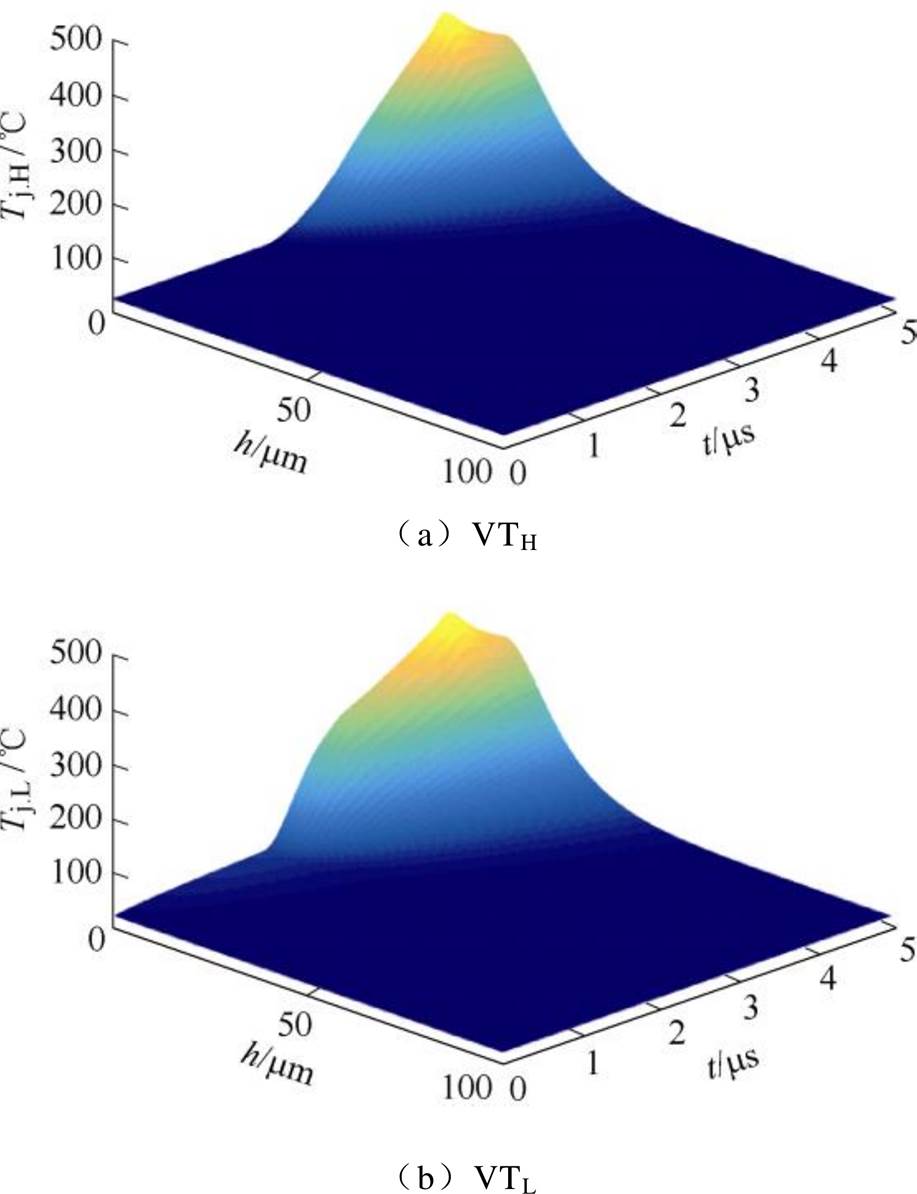

在短路运行过程中,器件很难通过实验直接测得结温的瞬态变化。为了分析串联短路器件结温温升特性,采用文献[22]的基于传热学非稳态热传导原理,建立关于SiC MOSFET芯片的热电模型。通过热电模型的计算,VTH与VTL内部结构纵向结温分布如图17所示,图中,h为SiC MOSFET耗尽层纵向分布,参考零点为P基区与N-漂移区的PN结,P基区耗尽层距离零点为负值,N-漂移区耗尽层距离零点为正值。整个短路期间,待测器件的温度分布非常集中,温度最高值一直处于PN结附近,此处电场强度最大,对应的热激励密度最高,因而将该处的温度作为待测器件的结温。随着h的增加,器件温度急剧下降,当h>60mm时,热传导过程几乎可以忽略。

图17 内部结构纵向结温分布

Fig.17 Longitudinal junction temperature distribution of the internal structure of the device

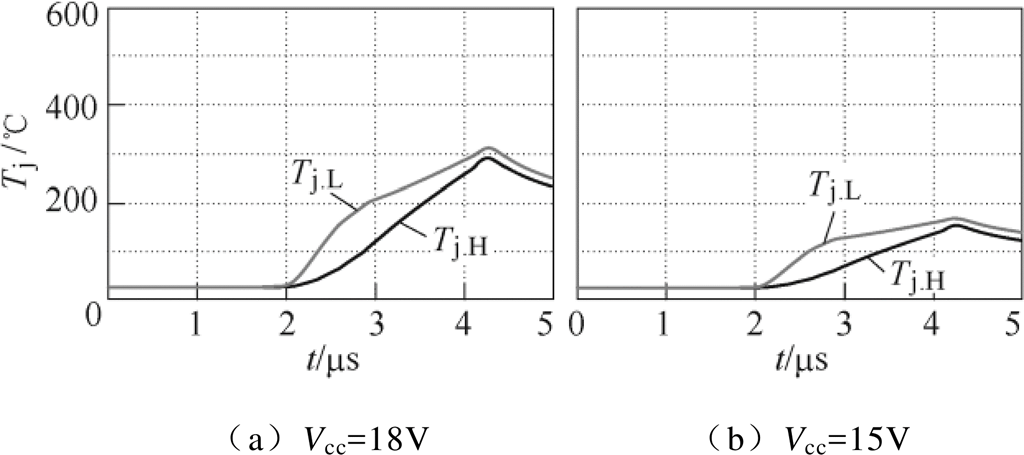

VTH与VTL计算结温随时间的变化曲线如图18所示。在器件关断后,Tj.H和Tj.L分别为324℃和378℃,结温差DTj=54℃。相对于对单个功率器件的短路实验,VTH和VTL的分压特性大幅降低了器件的结温温升,因而在常规的短路保护时间内器件受到的短路冲击大幅减小。

图18 VTH和VTL的计算结温温升

Fig.18 Calculation junction temperature rise of VTH and VTL

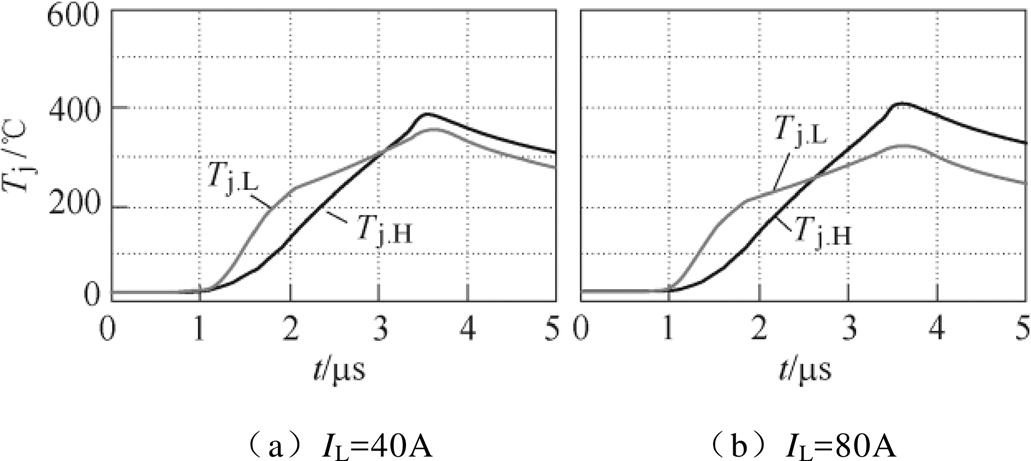

正向负载电流IL对串联短路影响的实验波形如图19所示,实验选取负载电流绝对值为40A和80A。与图16的IL=0A进行比较,当负载为正向电流时,VTH承担更多的母线电压,与理论分析一致。在分压过程中,VDS.L的下降导致ES.L上升速率减小,相应地,ES.H上升速率增大。当IL=40A时,ES.L降低至473mJ,略小于ES.H的505mJ,此时DES很小。正向负载电流IL对串联短路结温影响计算波形如图20所示。从图20可知,VTH与VTL的结温差DTj较小,在关断时刻Tj.H与Tj.L分别为382℃和364℃。而当IL=80A时,ES.L进一步降低至431mJ,ES.H则上升至533mJ,导致DTj增大,由图20可得,在关断时刻Tj.H与Tj.L分别为407℃和322℃,DTj上升至85℃。

图19 正向负载电流IL对串联短路影响的实验波形

Fig.19 Experimental waveforms of the effect of forward load current IL on series short-circuit

图20 正向负载电流IL对串联短路结温影响计算波形

Fig.20 Calculation waveforms of the effect of forward load current IL on junction temperature

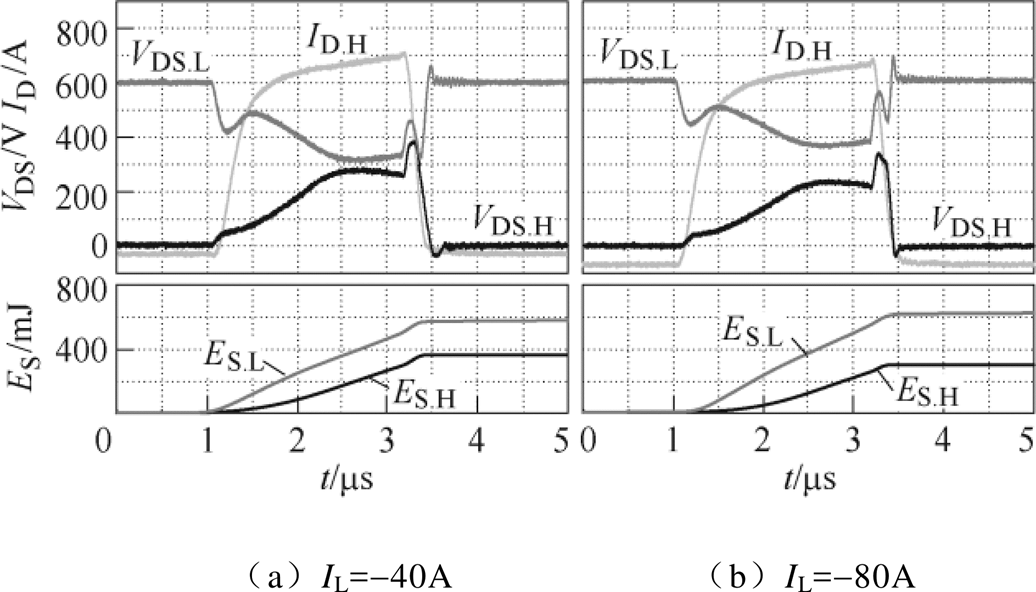

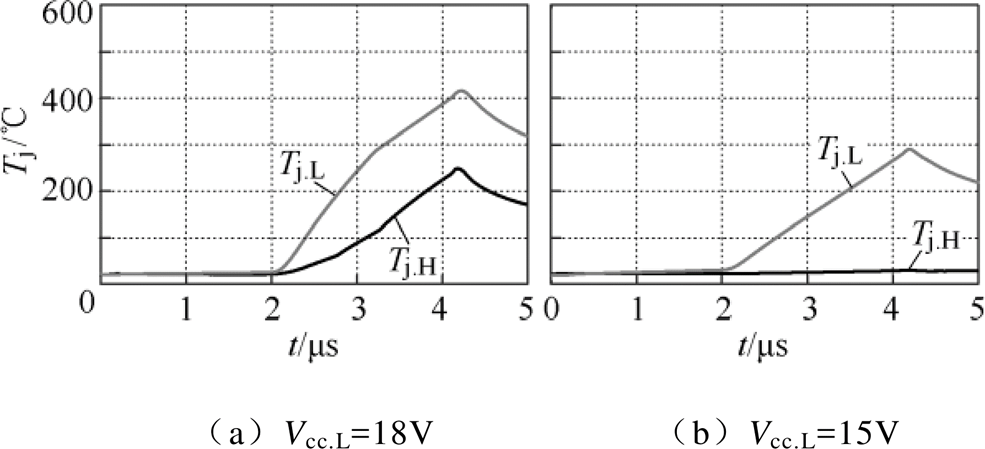

当负载流过反向电流时,反向负载电流对串联短路影响的实验波形如图21所示,VTH与VTL漏极电压变化幅度减小,因而无交叉点,与理论分析一致。由于VTL的漏极电压与漏极电流都高于VTH,导致ES.L上升速率始终高于ES.H。当IL=-40A时,ES.L增大至583mJ,则ES.H减小至372mJ,DES大幅增加。反向负载电流IL对串联短路结温影响的计算波形如图22所示。从图22可知,在关断时刻Tj.H与Tj.L分别为304℃和435℃,DTj增大至131℃。当IL=-80A时,ES.L进一步上升至610mJ,ES.H减小至290mJ,在图22中,Tj.L上升至472℃,Tj.H下降至276℃,DTj进一步增大至204℃。

由上述分析可以看出,反向负载电流导致VTH与VTL损耗不均恒性要比正向负载电流严重,且VTL的结温远高于VTH,VTL因结温过高,短路耐受能力将大幅减弱。

图21 反向负载电流对串联短路影响的实验波形

Fig.21 Experimental waveforms of the effect of reverse load current IL on series short-circuit

图22 反向负载电流IL对串联短路结温影响的计算波形

Fig.22 Calculation waveforms of the effect of reverse load current IL on junction temperature

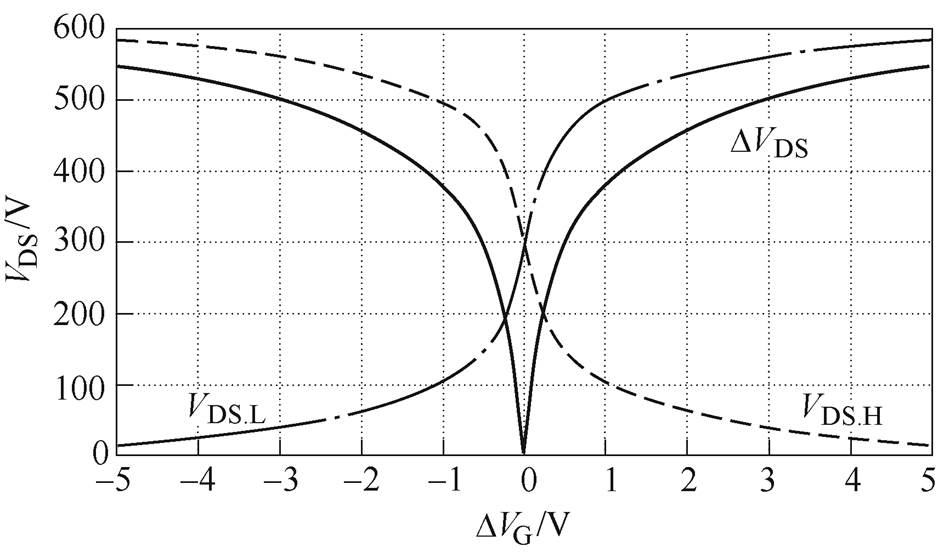

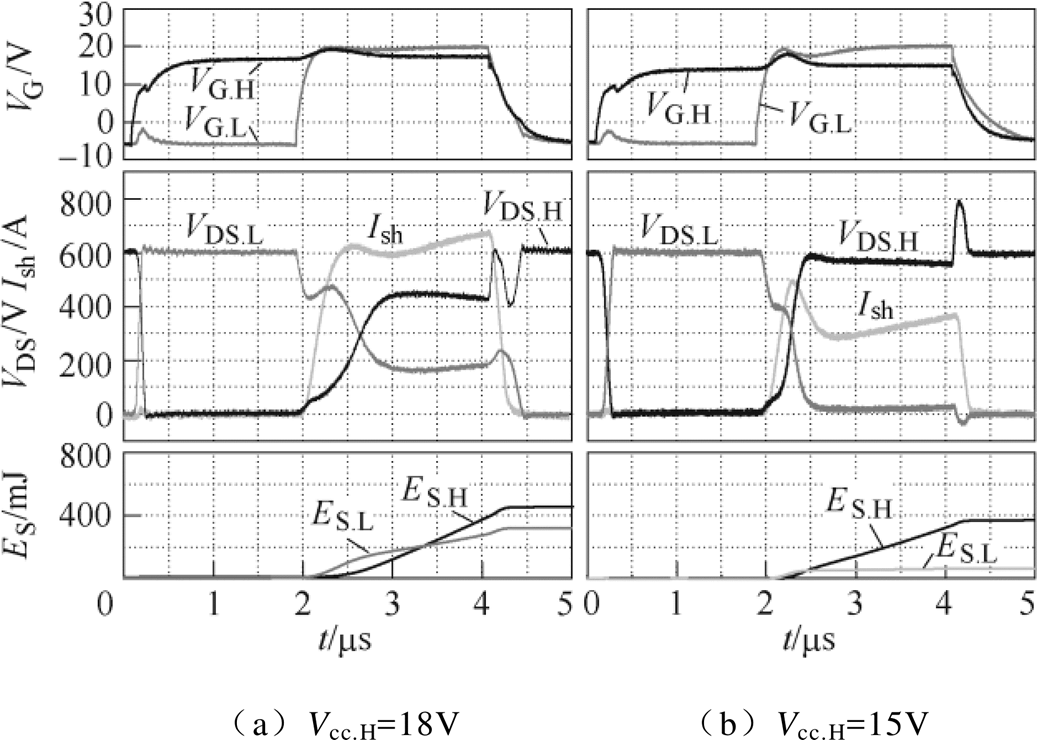

图23为同时降低VTH与VTL驱动电压Vcc的实验波形。选取Vcc为18V和15V进行实验。与图16的Vcc=20V进行比较,驱动电压的下降使得短路电流明显减小。当Vcc=18V时,短路电流Ish下降了约100A。Ish上升速率降低导致VTL电压缺口和VTH导通压降减小,在电流上升阶段,ES.L上升速率有所提高。而在分压阶段,由于Ish的减小,VTH与VTL损耗上升速率减缓,ES.H和ES.L的损耗分别下降至365mJ和412mJ。当Vcc=15V时,Ish下降了约360A,ES.H和ES.L大幅降低至171mJ和213mJ。驱动电压Vcc对串联短路结温影响的计算波形如图24所示。由图24可以看出,短路电流的大幅下降,导致了VTH与VTL的结温温升大幅降低,当Vcc=18V时,Tj.H与Tj.L分别下降至293℃和315℃;当Vcc=15V时,Tj.H与Tj.L的结温进一步降至156℃和172℃。且DTj在逐渐减小。

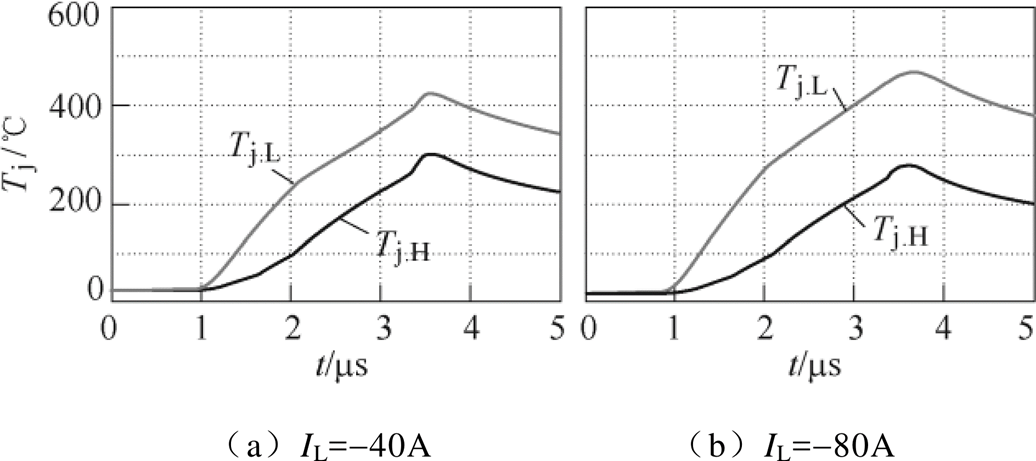

若VTH与VTL驱动电压不同,首先降低VTH驱动电压Vcc.H,选取Vcc.H为18V和15V,驱动电压Vcc.H对串联短路影响的实验波形如图25所示。与图16的Vcc.H=20V进行比较,Vcc.H的降低使VTH与VTL漏极电压变化幅度大幅增加。当Vcc.H=18V时,Ish以及VDS.L的下降,使得ES.L大幅下降至330mJ。ES.H则由于VDS.H的上升与Ish的下降相互抵消而略微上升至450mJ。当Vcc.H=15V时,VTH承受了绝大部分母线电压,在短路电流大幅减小的影响下,ES.L极小,ES.H则下降至380mJ。若进一步降低Vcc.H,ES.H将因短路电流的下降进一步降低,而ES.L的变化忽略不计。通过热电模型计算的驱动电压Vcc.H对串联短路结温影响的计算波形如图26所示。Ish和VDS.L的降低导致Tj.L大幅下降,当Vcc.H=18V时,Tj.H略微上升至354℃,在进入分压阶段后,Tj.L上升速率明显变缓,最终降为242℃,DTj增大至112℃。当Vcc.H=15V时,由于短路电流的大幅下降,Tj.H下降至301℃,而Tj.L在电流上升阶段略微升高后,在进入分压阶段,由于漏极电压急速下降,结温上升非常缓慢,并受温度传导特性的影响开始缓慢下降,最终Tj.L降至约50℃,DTj进一步增大至287℃。

图23 驱动电压Vcc对串联短路影响的实验波形

Fig.23 Experimental waveforms of the effect of driving voltage Vcc on series short-circuit

图24 驱动电压Vcc对串联短路结温影响的计算波形

Fig.24 Calculation waveforms of the effect of driving voltage Vcc on junction temperature

当仅降低VTL驱动电压Vcc.L时,驱动电压Vcc.L对串联短路影响的实验波形如图27所示。选取Vcc.L为18V和15V进行实验。与图16的Vcc.L=20V进行比较,由于VTL开通速率减缓,VTH与VTL的分压过程变得十分缓慢,VTL承受了较多的母线电压,增大了器件的损耗差。当Vcc.L=18V时,短路电流的下降以及VTH分压的减小使得ES.H的损耗大幅下降至240mJ,VTL则因漏极电压的上升而增加至550mJ。当Vcc.L=15V时,VTL几乎承受了全部的母线电压,由于短路电流大幅减小,ES.L下降至380mJ,ES.H的变化忽略不计。VTH与VTL的结温温升如图28所示。Vcc.L的降低大幅减小了VTH的结温,当Vcc.L=18V时,Tj.L上升至417℃,Tj.H上升速率明显变缓,最终结温降为259℃,DTj增大至158℃。当Vcc.L=15V时,Tj.L下降至297℃,而Tj.H温升忽略不计。

图25 驱动电压Vcc.H对串联短路影响的实验波形

Fig.25 Experimental waveforms of the effect of driving voltage Vcc.H on series short-circuit

图26 驱动电压Vcc.H对串联短路结温影响的计算波形

Fig.26 Calculation waveforms of the effect of driving voltage Vcc.H on junction temperature

图27 驱动电压Vcc.L对串联短路影响的实验波形

Fig.27 Experimental waveforms of the effect of driving voltage Vcc.L on series short-circuit

图28 驱动电压Vcc.L对串联短路结温影响的计算波形

Fig.28 Calculation waveforms of the effect of driving voltage Vcc.L on junction temperature

由上述分析可以看出,驱动电压差的增大,会加剧器件结温不平衡分布,但短路电流的降低减小了短路损耗与结温温升,降低了短路故障对器件的冲击。

本文以SiC MOSFET半桥模块为研究对象,对发生串联短路时SiC MOSFET的分压特性进行详细分析。区别于单一器件短路时承受全母线电压,串联短路时上、下桥臂器件共同分担母线电压。建立串联短路分压模型,结合仿真详细分析负载电流、驱动电压和结温温升对短路分压特性的影响,结合实验分析电路参数对短路器件损耗与结温的影响。理论分析、仿真和实验结果表明,器件串联短路特性尤其是分压特性极易受外部电路参数的影响,反向负载电流、驱动电压差的增加会造成上、下桥臂器件结温不平衡,影响器件的可靠性。

参考文献

[1] 周林, 李寒江, 解宝, 等. SiC MOSFET的Saber建模及其在光伏并网逆变器中的应用和分析[J]. 电工技术学报, 2019, 34(20): 4251-4263.

Zhou Lin, Li Hanjiang, Xie Bao, et al. Saber modeling of SiC MOSFET and its application and analysis in photovoltaic grid-connected inverter[J]. Transactions of China Electrotechnical Society, 2019, 34(20): 4251-4263.

[2] She Xu, Huang A Q, Óscar L, et al. Review of silicon carbide power devices and their applications[J]. IEEE Transactions on Industrial Electronics, 2017, 64(10): 8193-8205.

[3] 盛况, 郭清, 张军明, 等.碳化硅电力电子器件在电力系统的应用展望[J]. 中国电机工程学报, 2012, 32(30): 1-7.

Sheng Kuang, Guo Qing, Zhang Junming, et al. Development and prospect of SiC power devices in power grid[J]. Proceedings of the CSEE, 2012, 32(30): 1-7.

[4] Laird I, Yuan Xibo, Scoltock J, et al. A design optimization tool for maximizing the power density of 3-phase DC-AC converters using silicon carbide (SiC) devices[J]. IEEE Transactions on Power Electronics, 2019, 33(4): 2913-2932.

[5] 庄桂元, 张兴, 刘威, 等. 带飞跨电容的三电平拓扑中SiC MOSFET过电压与过电流保护[J]. 电工技术学报, 2021, 36(2): 341-351.

Zhuang Guiyuan, Zhang Xing, Liu Wei, et al. Over- voltage and overcurrent protection of SiC MOSFET in three-level topology with flying capacitor[J]. Transa- ctions of China Electrotechnical Society, 2021, 36(2): 341-351.

[6] 陈杰, 邓二平, 赵子轩, 等. 不同老化试验方法下SiC MOSFET失效机理分析[J]. 电工技术学报, 2020, 35(24): 5105-5114.

Chen Jie, Deng Erping, Zhao Zixuan, et al. Failure mechanism analysis of SiC MOSFET under different aging test methods[J]. Transactions of China Electro- technical Society, 2020, 35(24): 5105-5114.

[7] 王莉娜, 马浩博, 袁恺, 等. SiC MOSFET半桥电路开关瞬态过电流、过电压建模与影响因素分析[J]. 电工技术学报, 2020, 35(17): 3652-3665.

Wang Lina, Ma Haobo, Yuan Kai, et al. Modeling and influencing factor analysis of SiC MOSFET half- bridge circuit switching transient overcurrent and overvoltage[J]. Transactions of China Electrotechnical Society, 2020, 35(17): 3652-3665.

[8] 李辉, 黄樟坚, 廖兴林, 等. 一种抑制SiC MOSFET桥臂串扰的改进门极驱动设计[J]. 电工技术学报, 2019, 34(2): 275-285.

Li Hui, Huang Zhangjian, Liao Xinglin, et al. An improved SiC MOSFET gate driver design for crosstalk suppression in a phase-leg configuration[J]. Transactions of China Electrotechnical Society, 2019, 34(2): 275-285.

[9] Zhou Xintian, Su Hongyuan, Wang Yan. Investiga- tions on the degradation of 1.2kV 4H-SiC MOSFETs under repetitive short-circuit tests[J]. IEEE Transa- ctions on Electronic Devices, 2016, 63(11): 4346- 4351.

[10] Reigosa P D, Luo Haoze, Francesco I. Implications of ageing through power cycling on the short circuit robustness of 1.2kV SiC MOSFETs[J]. IEEE Transa- ctions on Power Electronics, 2019, 34(11): 11182- 11190.

[11] Nguyen T, Ahmed A, Thang T V, et al. Gate oxide reliability issues of SiC MOSFETs under short-circuit operation[J]. IEEE Transactions on Power Electronics, 2015, 30(5): 2445-2455.

[12] Zhou Yuming, Liu Hangzhi, Mu Shilu, et al. Short- circuit failure model of SiC MOSFET including the interface trapped charges[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 90-98.

[13] Sun Jiahui, Wei Jin, Zheng Zheyang, et al. Short circuit capability and short sircuit induced vth instabi- lity of a 1.2kV SiC power MOSFET[J]. IEEE Journal of Emerging and Selected Topics in Power Elec- tronics, 2019, 7(3): 1539-1546.

[14] Ji Shiqi, Marko L, Huang Xingxuan, et al. Short circuit characterization and protection of 10kV SiC MOSFET[J]. IEEE Transactions on Power Electronics, 2019, 34(2): 1755-1767.

[15] 吴海富, 张建忠, 赵进, 等. SiC MOSFET短路检测与保护研究综述[J]. 电工技术学报, 2019, 34(21): 4519-4528.

Wu Haifu, Zhang Jianzhong, Zhao Jin, et al. Review of short-circuit detection and protection of silicon carbide MOSFETs[J]. Transactions of China Electro- technical Society, 2019, 34(21): 4519-4528.

[16] 王占扩, 童朝南, 黄伟超. SiC MOSFET短路特性及过流保护研究[J]. 中国电机工程学报, 2020, 40(18): 5751-5760.

Wang Zhankuo, Tong Chaonan, Huang Weichao. Reasearch on short-circuit characteristics and over- current protection of SiC MOSFET[J]. Proceedings of the CSEE, 2020, 40(18): 5751-5760.

[17] 高勇, 乔小可, 孟昭亮, 等. SiC MOSFET的短路特性[J]. 半导体技术, 2019, 44(5): 342-348.

Gao Yong, Qiao Xiaoke, Meng Zhaoliang, et al. Short-circuit characteristics of SiC MOSFETs[J]. Semiconductor Technology, 2019, 44(5): 342-348.

[18] Sadik D P, Colmenares J, Tolstoy G, et al. Short- circuit protection circuits for silicon-carbide power transistors[J]. IEEE Transactions on Industrial Elec- tronics, 2016, 63(4): 1995-2004.

[19] Wang Jun, Jiang Xi, Li Zongjian, et al. Short-circuit ruggedness and failure mechanisms of Si/SiC hybrid switch[J]. IEEE Transactions on Power Electronics, 2019, 34(3): 2771-2780.

[20] 秦海鸿, 徐克峰, 王丹, 等. SiC MOSFET短路特性[J]. 南京航空航天大学学报, 2018, 50(3): 348-354.

Qin Haihong, Xu Kefeng, Wang Dan, et al. Short-circuit characteristics of SiC MOSFETs[J]. Journal of Nanjing University of Aeronautics & Astronautics, 2018, 50(3): 348-354.

[21] Eni E P, Bęczkowski S, Munk-Nielsen S, et al. Short- circuit degradation of 10kV 10A SiC MOSFET[J]. IEEE Transactions on Power Electronics, 2017, 32(12): 9342-9354.

[22] Wang Zhiqiang, Shi Xiaojie, Tolbert L M, et al. Temperature-dependent short-circuit capability of silicon carbide power MOSFETs[J]. IEEE Transa- ctions on Power Electronics, 2016, 31(2): 1555-1566.

[23] Kadavelugu A, Aeloiza E, Belcastro C. Short-circuit performance of multi-chip SiC MOSFET modules[C]// IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, 2017: 285- 290.

Dynamic Characterization Assessment on Series Short-Circuit of SiC MOSFET

Abstract In power electronic systems, when SiC MOSFET is turned on incorrectly due to breakdown devices, hardware circuit defects or system control errors, at least two devices work in the short-circuit current loop, forming series short-circuit faults. Based on the half-bridge structure, the switching principle of SiC MOSFETs in short-circuit was introduced in detail. To study the influence mechanism of load current, gate drive voltage and junction temperature, the short circuit test was carried out under different experimental situations. The drain-source voltage sharing model of SiC MOSFET was derived and verified by simulation. The changes of short-circuit loss and junction temperature distribution caused by circuit parameters were compared on the 1 200V/80A SiC MOSFET experimental bench. The results show that the dynamic characteristics of SiC MOSFET are highly sensitive to circuit parameters in series short-circuit. The unbalanced dynamic change of drain-source voltage and drain current affect the short-circuit loss of devices, which in turn changes the junction temperature distribution.

keywords:SiC MOSFET, series short-circuit, voltage dividing characteristic, junction tem- perature distribution

中图分类号:TM46

DOI: 10.19595/j.cnki.1000-6753.tces.201432

国家重点研发计划子课题资助项目(2016YFC0600804)。

收稿日期 2020-11-01

改稿日期 2021-02-02

张经纬 男,1991年生,博士研究生,研究方向为SiC器件特性分析与驱动设计。E-mail: tb19130011b4@cumt.edu.cn

谭国俊 男,1962年生,教授,博士生导师,研究方向为电力电子与电力传动。E-mail: gjtan_cumt@163.com(通信作者)

(编辑 陈 诚)