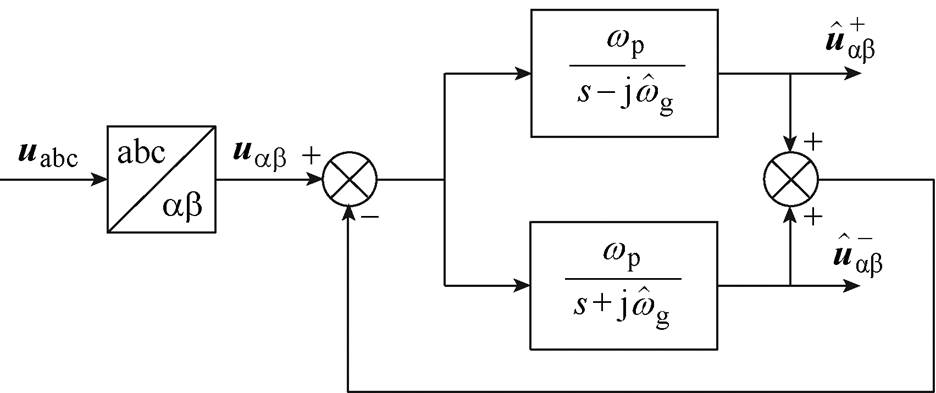

图1 现有的CCF结构

Fig.1 Existing CCF structure

摘要 近年来,前置复数滤波器(CCF)的锁相环(PLL)技术成为电网同步研究中的热点。然而,现有的CCF-PLL已被证实其数学模型和控制性能与传统的实数滤波器型PLL基本一致。为提高系统的控制性能,该文提出一种CCF结构完全复数化的三相PLL技术。首先,给出前级滤波结构关于电压的传递函数,验证该结构可以准确分离出电网的基波正负序分量。其次,进行前级结构关于基波正序相位的数学建模,结合后级的同步旋转坐标系PLL,构建整个PLL系统关于相位的数学模型,并利用三阶最佳校正法对系统进行设计,确定相关控制参数。研究发现,若采用与CCF-PLL相同的开环截止频率,所提PLL的中频段宽度更宽、相位裕度更大。另外,还设计了多重全复数滤波结构级联的三相PLL,以便更彻底地抑制电网谐波。最后,通过仿真和实验进行验证,结果表明,相比CCF-PLL,所提PLL的控制性能更佳。

关键词:锁相环 复数滤波器 控制性能 相位裕度

传统能源(如煤、石油和天然气等)的过度使用致使不可再生能源日趋枯竭;另外,采用传统能源发电会造成环境污染和生态破坏等问题。所以,基于可再生绿色能源(如太阳能和风能等)的开发和利用备受关注[1]。采用并网逆变器将绿色能源发出的电能并入电网是一种行之有效的手段[2]。在逆变器的控制中,调节电网电压和输出电流之间的相位差[3]、实现并网逆变器的孤岛检测功能[4]和故障穿越功能[5-6]通常都要用到锁相环(Phase Locked Loop, PLL)技术。因此,PLL技术已成为分布式发电系统并网运行的众多关键技术之一[7]。

在三相PLL的研究中,技术比较成熟的有同步旋转坐标系(Synchronous Rotating Frame, SRF)型PLL[8]、滑动平均滤波器(Moving Average Filter, MAF)型PLL[9-10]、自适应陷波器(Adaptive Notch Filter, ANF)型PLL[11-12]、双二阶广义积分器(Double Second-Order Generalized Integrator, DSOGI)型PLL[13-14]和复数滤波器(Complex Coefficient Filter, CCF)型PLL[15-18]。其中,由文献[15]提出的CCF技术由于控制结构简单、滤波原理清晰等特点在三相PLL的研究中受到持续关注。该CCF结构在电网的基波正、负序分量(Fundamental Positive-and Negative-Sequence Components, FPSC/FNSC)处具有频率极性的选择性,无需对称分量法即可分离出FPSC和FNSC。文献[16]为改善并网电流质量,介绍了如何在三相静止坐标系下直接使用CCF结构。文献[17]提出了对高次谐波抑制能力更强的高阶CCF控制方案。文献[18]将重复控制的内模嵌入到CCF结构中,使PLL能够完全滤除电网中的主要谐波。除PLL外,CCF结构在逆变器的电流控制[19]、锁频环[20]和电机控制[21]中也都得到了成功运用。

然而,上述相关文献对CCF-PLL研究时,将前级的CCF结构和后级的SRF-PLL作为独立系统对待,并分开进行了处理。文献[22-24]指出,前置滤波器型PLL的前、后两级是相互联系的,不能看成分立系统。文献[22-23]将前后两级结合起来分析,对整个PLL系统进行了小信号数学建模,研究表明:CCF-PLL虽然结构简单,但其数学模型与ANF-PLL、DSOGI-PLL等实数滤波器型PLL是一致的。文献[23-24]通过对比实验发现,CCF-PLL的控制性能与实数滤波器型PLL相比基本无异,并无突出优势。

为提高CCF-PLL的控制性能,提出了一种将CCF结构进一步复数化的三相PLL技术。为充分发挥复数系统的优势,将CCF所对应传递函数分子也改用复数表示。改进后的CCF结构不仅保持了正负频率的选择性,还提高了前级滤波结构的截止频率,从而加大了整个PLL系统的中频段宽度和相位裕度。仿真和对比实验表明,所提PLL在保留CCF- PLL能顺利分离FPSC/FNSC和精确锁频、锁相的同时,显著地提高了系统的控制性能。

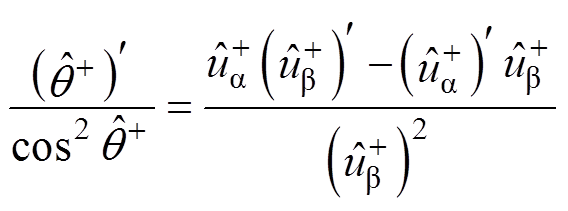

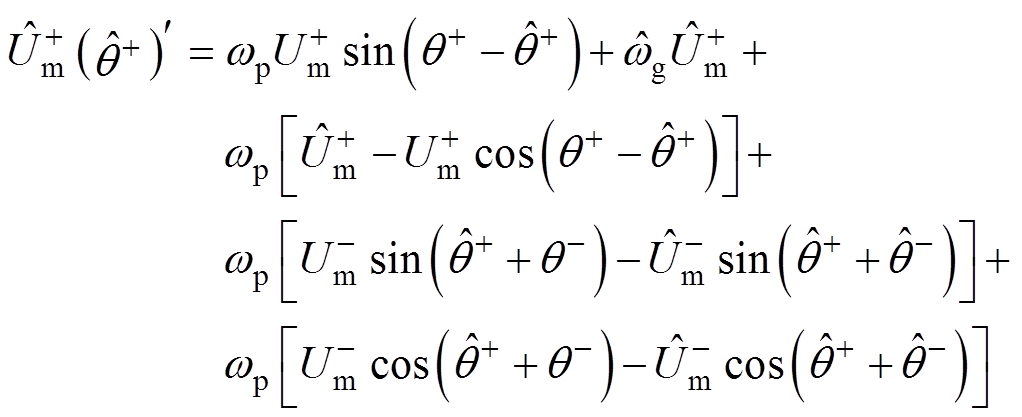

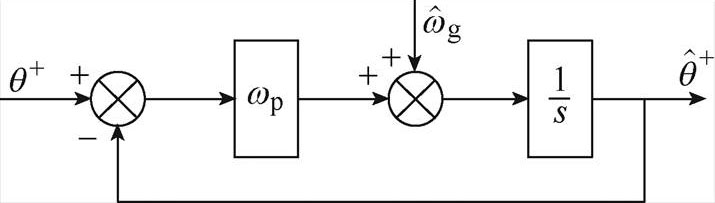

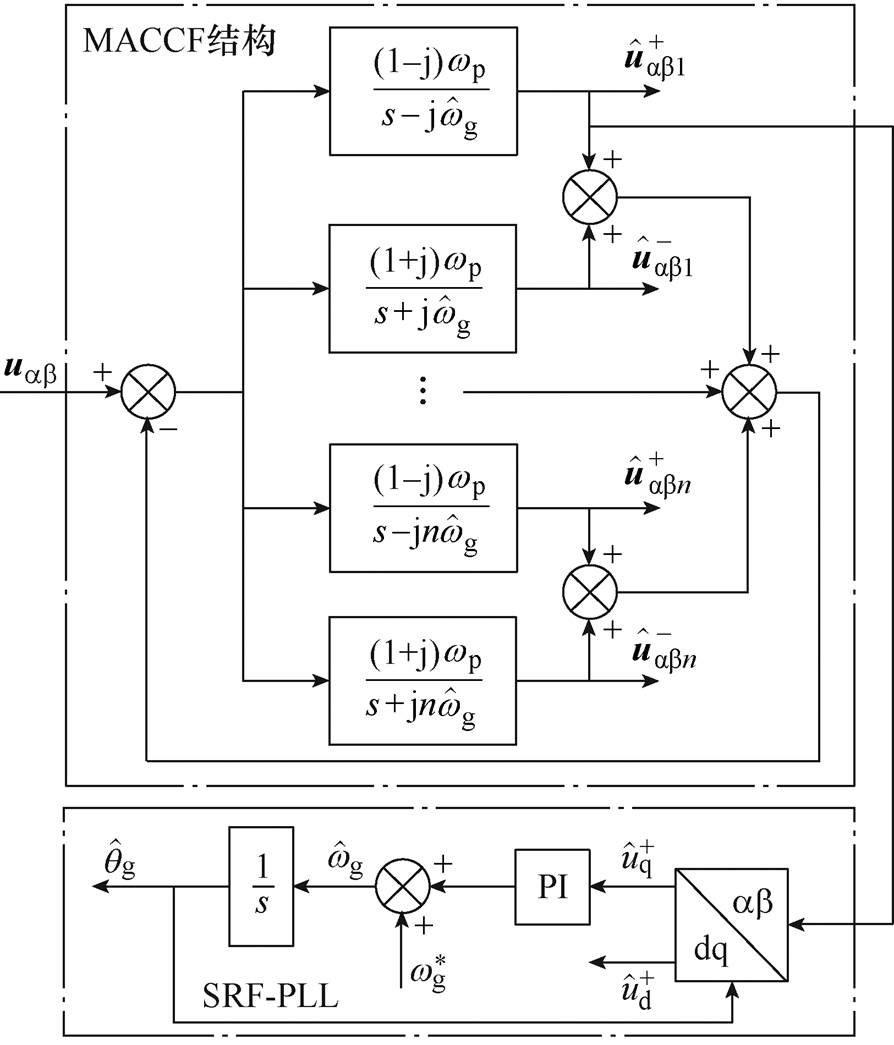

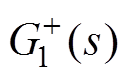

现有的CCF结构[15-21]如图1所示。

图1 现有的CCF结构

Fig.1 Existing CCF structure

图1中,uabc、uab 分别为三相电网电压及其a、b 轴分量; 、

、 分别为CCF结构分离出的电网FPSC和FNSC;

分别为CCF结构分离出的电网FPSC和FNSC; 为后级SRF-PLL提取出的电网角频率;

为后级SRF-PLL提取出的电网角频率; 为CCF结构的截止角频率。

为CCF结构的截止角频率。

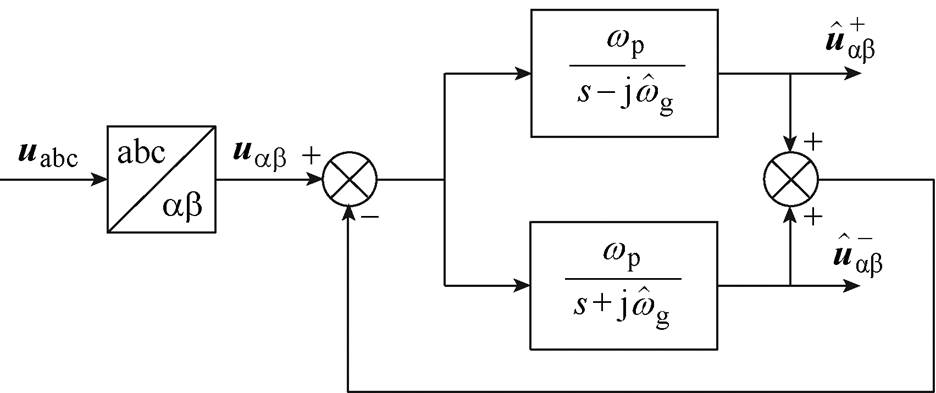

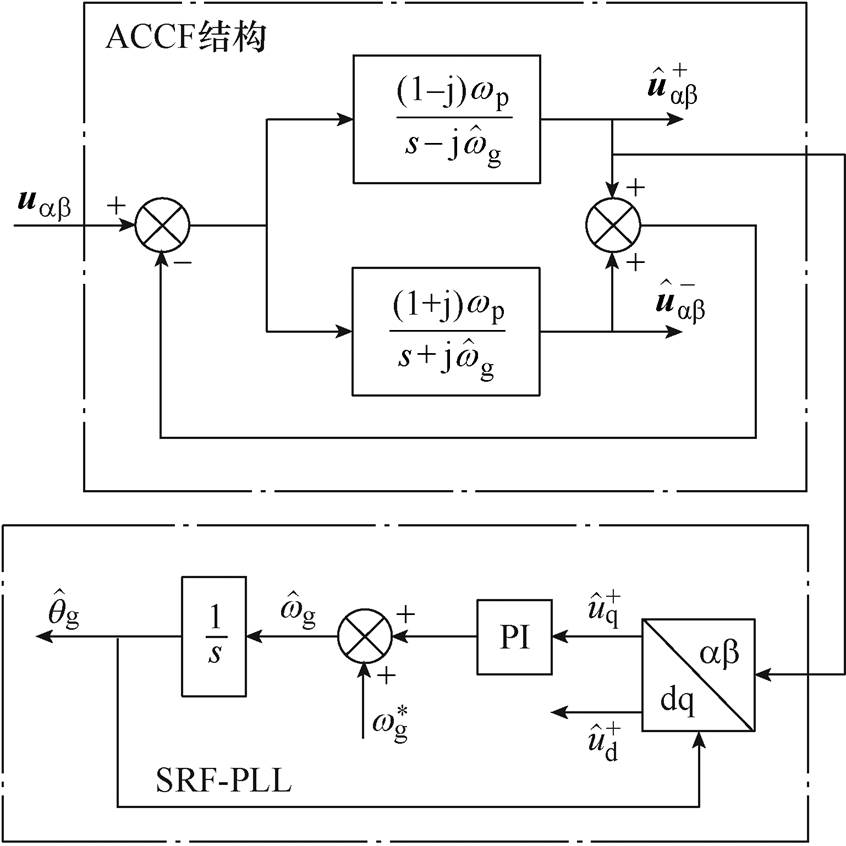

为改善控制性能,提出的全复数型滤波器(All Complex Coefficient Filter, ACCF)结构如图2所示。

图2 提出的ACCF结构

Fig.2 Proposed ACCF structure

对比图1和图2可以发现,ACCF结构即为将CCF结构中滤波器的增益采用复数表示。容易求得ACCF结构中输入 到输出

到输出 、

、 的传递函数

的传递函数 和

和 分别为

分别为

(1)

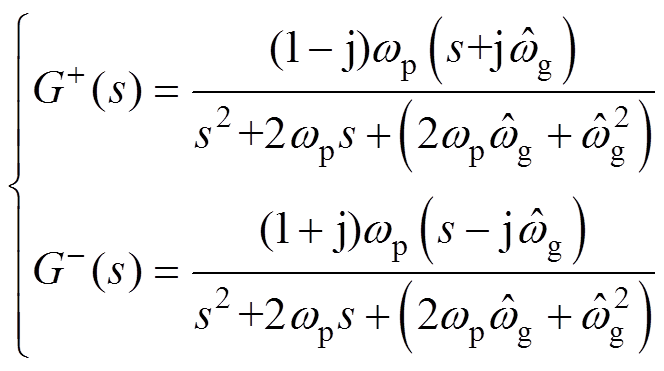

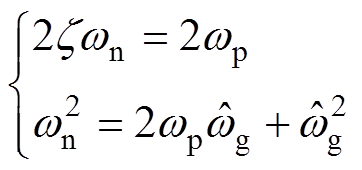

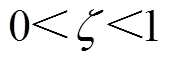

(1)由式(1)可知,ACCF结构关于电压是一个二阶线性系统,其阻尼比z 和自然角频率wn满足

(2)

(2)

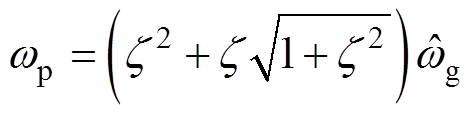

将式(2)中的wn消去,可解得wp为

(3)

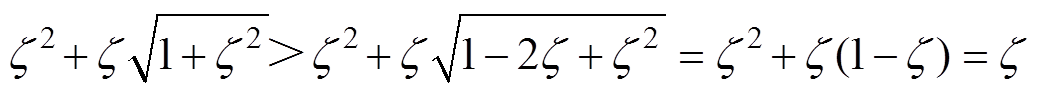

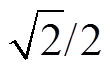

(3)在CCF结构中, [15, 24]。由于二阶系统一般选在欠阻尼状态下运行[25],即

[15, 24]。由于二阶系统一般选在欠阻尼状态下运行[25],即 ,故有

,故有 。

。

可见,相比CCF结构,ACCF结构的wp有所增大;而wp的大小直接影响整个PLL系统的中频段宽度和相位裕度(具体参见2.3节),因此,wp值的不同势必会导致ACCF结构与CCF结构在PLL系统的控制性能上表现出不一样的动态行为。

为兼顾二阶系统的响应速度和滤波性能,通常选取z 的值为最佳阻尼比 [23-25]。将

[23-25]。将 、

、 代入式(3)可得,

代入式(3)可得, 。

。

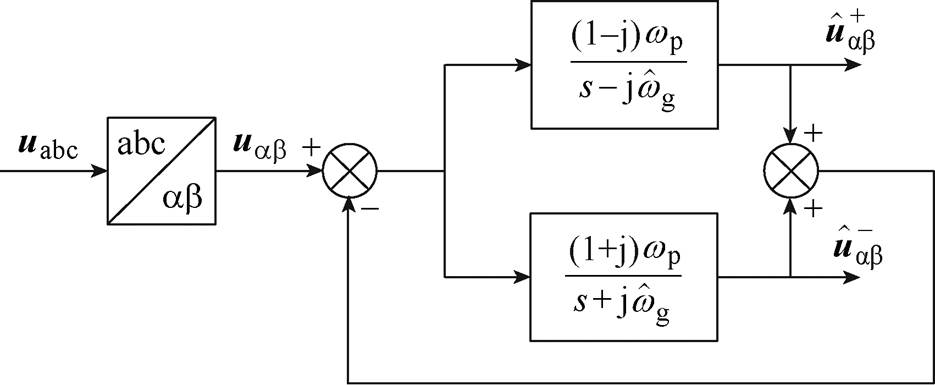

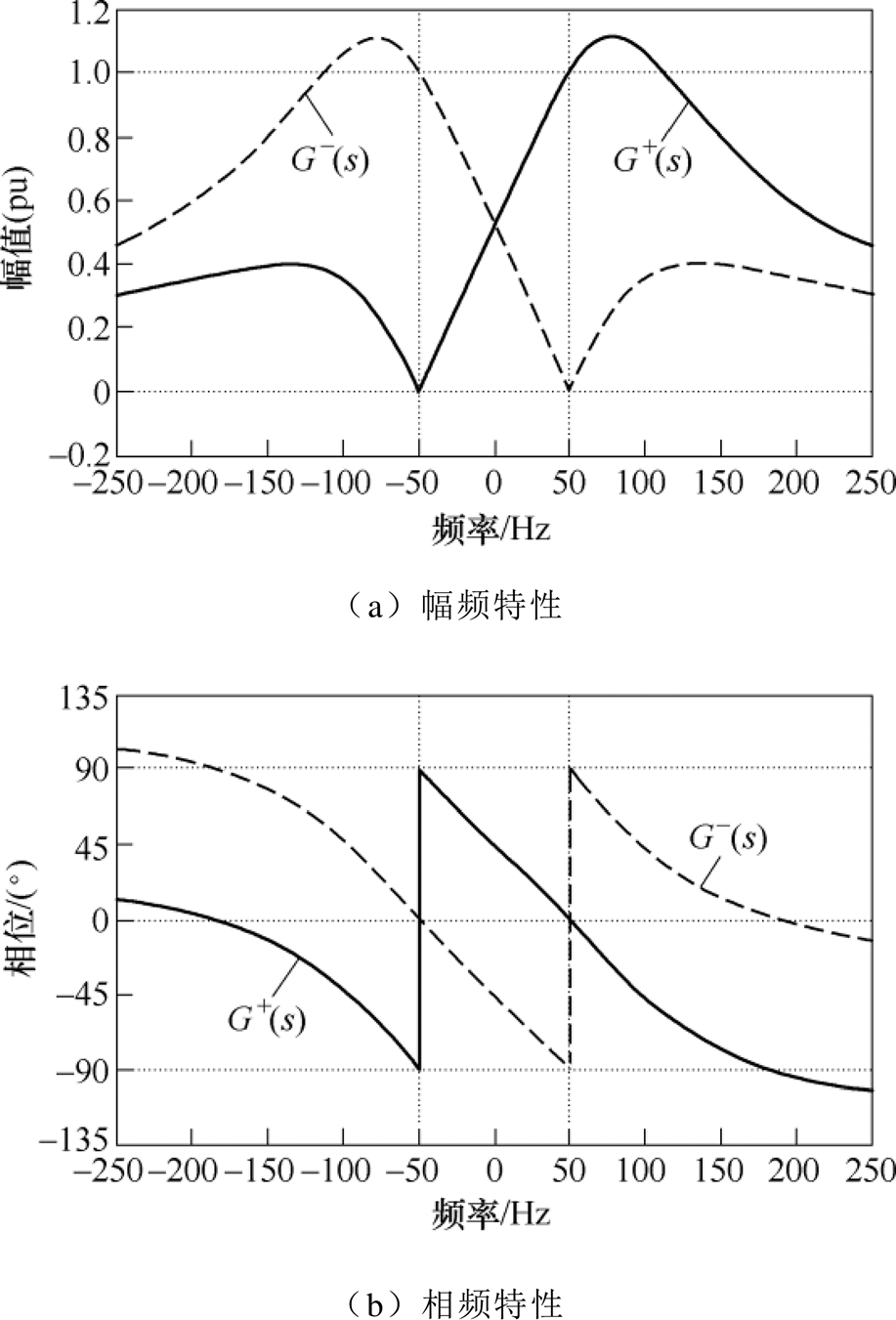

根据式(1)可画出 和

和 的频率特性曲线如图3所示(

的频率特性曲线如图3所示( )。

)。

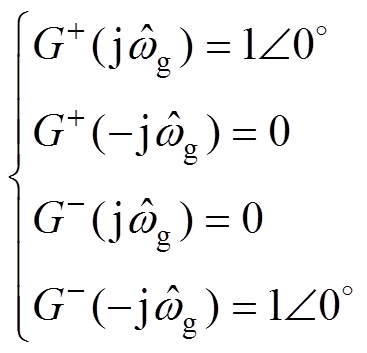

由式(1)和图3可得

图3 G+(s)和 的频率特性曲线

的频率特性曲线

Fig.3 Magnitude/phase-frequency curves of G+(s) and

(4)

(4)经典控制理论[25]指出,若角频率为w0的正弦信号经线性系统G(s)作用后,其输出信号的角频率保持不变,而幅值是原信号的|G(jw0)|倍,相位会在原来的基础上偏移∠G(jw0)。

鉴于此,由式(4)和图3可知,电网的FPSC(FNSC)通过系统G+(s)( )输出后,其幅值和相位均未发生变化,即G+(s)(

)输出后,其幅值和相位均未发生变化,即G+(s)( )对FPSC(FNSC)可以实现同幅、同频、同相的“原样”输出;而FNSC(FPSC)通过G+(s)(

)对FPSC(FNSC)可以实现同幅、同频、同相的“原样”输出;而FNSC(FPSC)通过G+(s)( )输出后,其幅值衰减至0,即G+(s)(

)输出后,其幅值衰减至0,即G+(s)( )对FNSC(FPSC)可以完全滤除。因此,提出的ACCF结构能够成功分离出电网的FPSC和FNSC。

)对FNSC(FPSC)可以完全滤除。因此,提出的ACCF结构能够成功分离出电网的FPSC和FNSC。

以上对正负序电压的分析建立在ACCF结构关于电压的数学模型之上,而PLL需要提取出FPSC的相位,所以还要对ACCF结构关于基波正序相位进行数学建模。

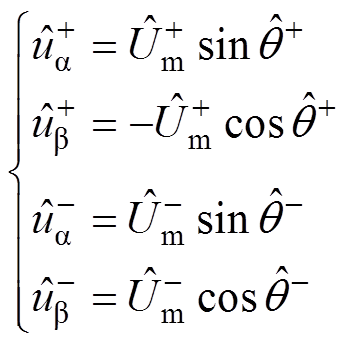

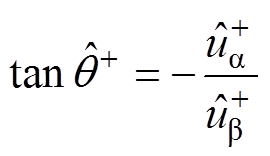

假设由ACCF结构分离出的FPSC和FNSC为

(5)

(5)式中, (

( )、

)、 (

( )分别为

)分别为 (

( )的幅值和相位。

)的幅值和相位。

由式(5)可得

(6)

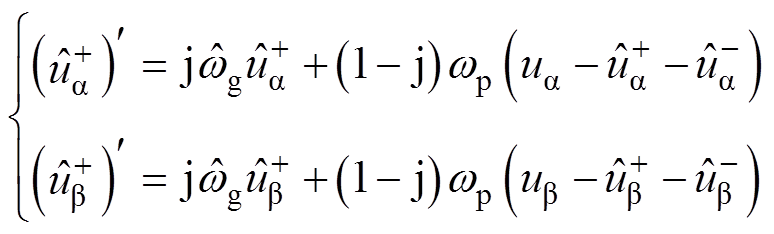

(6)将式(6)两端对时间求导,得

(7)

(7)

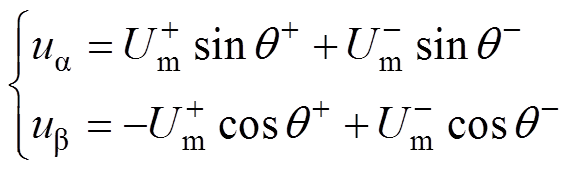

根据图2,可得ACCF结构中正序滤波器的输入、输出关系为

(8)

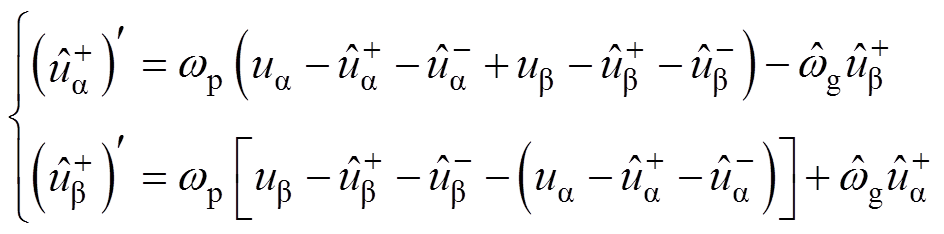

(8)式中,uab 的具体表达式为

(9)

(9)

式中, (

( )、

)、 (

( )分别为电网FPSC(FNSC)的实际幅值和相位。

)分别为电网FPSC(FNSC)的实际幅值和相位。

在三相电力系统的ab 坐标系下,任一变量hab均满足[16-18]:jha=-hb,jhb=ha。因此,式(8)可进一步转化为

(10)

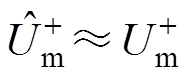

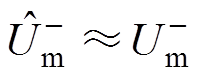

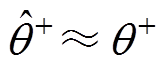

(10)将式(5)、式(9)和式(10)代入到式(7)并化简得

(11)

(11)

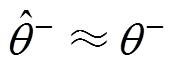

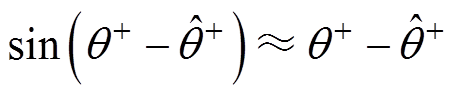

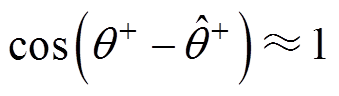

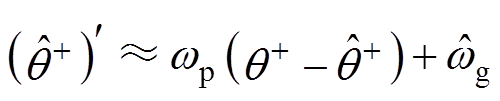

考虑到稳态时有 ,

,  ,

,  ,

,  ,

,  和

和 ,可将式(11)进一步简化为

,可将式(11)进一步简化为

(12)

(12)式(12)即为ACCF结构关于基波正序相位的时域数学模型,其复数域的数学模型如图4所示。

图4 ACCF结构关于基波正序相位的数学模型

Fig.4 Mathematical model of the ACCF structure on the fundamental positive-sequence phase

提出的基于ACCF结构的三相PLL如图5所示。图中, 为

为 的dq轴分量;

的dq轴分量; 为PLL捕获的相位;

为PLL捕获的相位; 为电网的理想角频率,

为电网的理想角频率, =100prad/s。

=100prad/s。

图5 基于ACCF结构的三相PLL

Fig.5 ACCF-based three-phase PLL

由图5可见,所提PLL分为前后两级:前级为ACCF结构,负责将uab 的FPSC和FNSC分离出来;后级为SRF-PLL,负责将FPSC中的幅值、频率和相位等信息精确提取出来。后级提取的 反馈到前级供正负序CCF使用,可使PLL在电网频率发生变化时对频率起到自适应调节的作用。

反馈到前级供正负序CCF使用,可使PLL在电网频率发生变化时对频率起到自适应调节的作用。

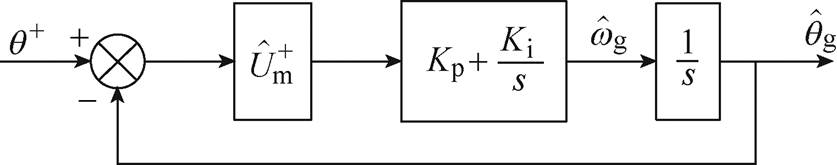

SRF-PLL在理想电网条件下的锁频和锁相能力十分突出(其基本工作原理可参见文献[8]),因此在畸变/不平衡电网环境中通常作为前置滤波器型PLL(如DSOGI-PLL、CCF-PLL等)的后级使用。该PLL关于相位的数学模型如图6所示。图中,Kp、Ki分别为PI控制器的比例和积分系数。

图6 SRF-PLL关于相位的数学模型

Fig.6 Mathematical model of SRF-PLL onthe phase

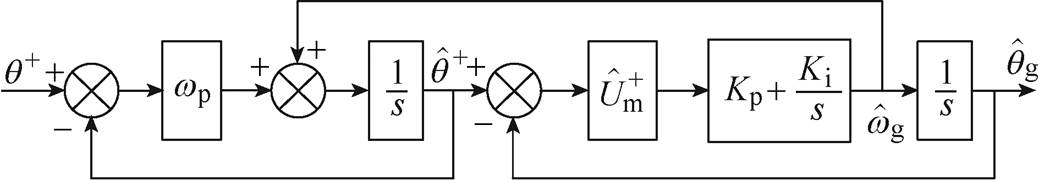

将前后两级关于基波正序相位的数学模型(见图4和图6)结合起来,可得整个PLL系统(见图5)的数学模型如图7所示。

图7 ACCF-PLL关于基波正序相位的数学模型

Fig.7 Mathematical model of ACCF-PLL on the fundamental positive-sequence phase

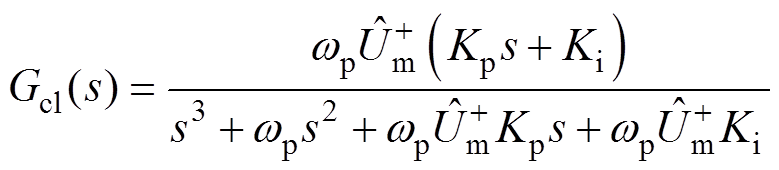

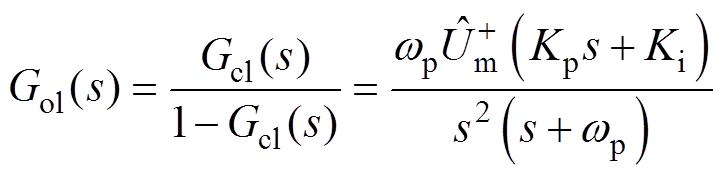

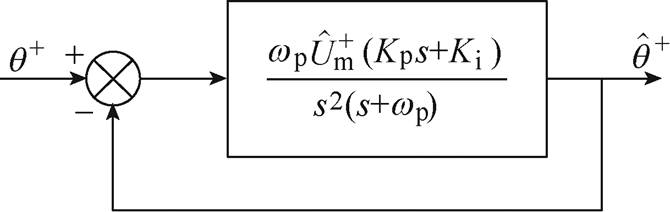

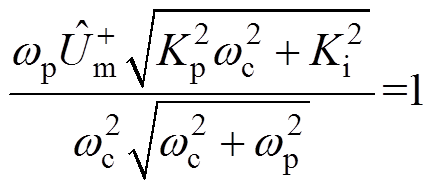

根据梅森增益公式[25],可得图7对应控制系统的闭环传递函数为

(13)

(13)对控制系统进行分析和校正时,通常以其开环传递函数为研究对象。由式(13)可得,ACCF-PLL对应系统的等效开环传递函数为

(14)

(14)

因此,ACCF-PLL的等效数学模型如图8所示。

图8 ACCF-PLL的等效数学模型

Fig.8 Equivalent mathematical model of ACCF-PLL

由图8可知,该控制结构为Ⅱ型单位反馈系统,可以无静差地跟踪像电网相位这样的斜坡输入。

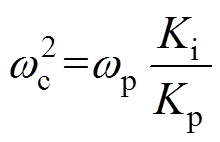

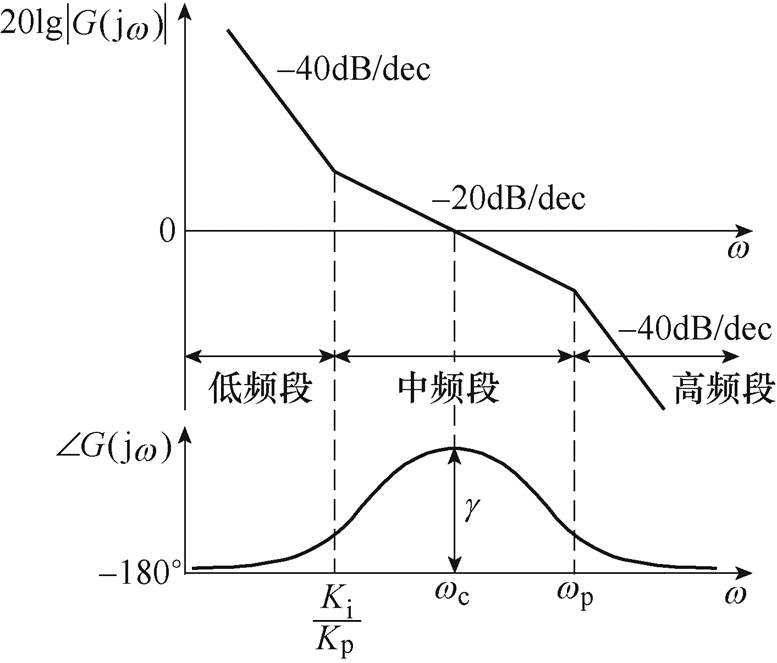

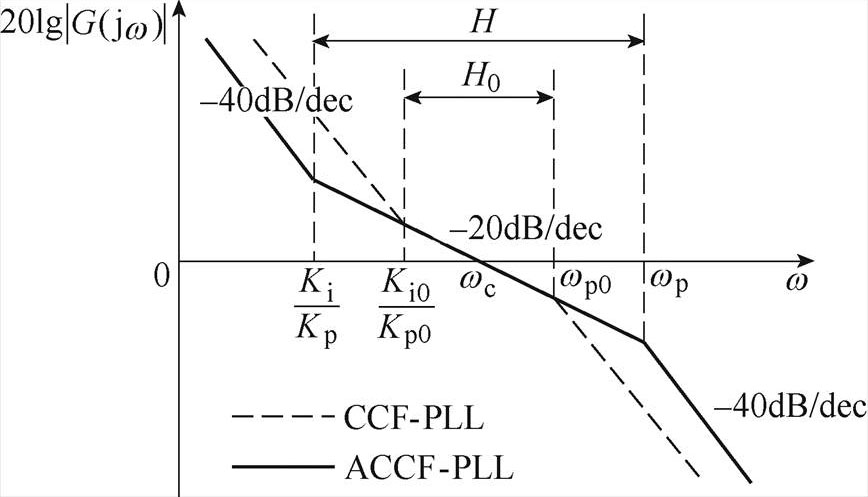

由于ACCF-PLL为三阶控制系统,可采用三阶最佳设计法[23, 25]对其校正,期望的系统频率特性曲线如图9所示。图中,wc、g 分别为系统的开环截止频率和相位裕度。

该设计法的主导思想是使控制系统取得最大的相位裕度,此时wc为中频段的几何中心,即

(15)

(15)由式(14)可知,wc满足

(16)

(16)

联立式(15)和式(16)可解得

图9 三阶最佳设计法下系统的频率特性曲线

Fig.9 Magnitude/phase-frequency curves under third-order optimal design method

(17)

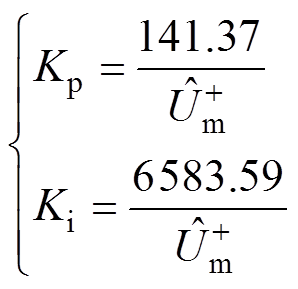

(17)由图9可知,wc的值需小于wp。若wc靠近wp,则系统的响应速度变快,但其中频段宽度和相位裕度都会减小,输出信号的超调量会增大,同时系统的滤波性能降低;若wc远离wp,虽然系统的稳定性和抗干扰性增强,但其响应速度变慢。所以,wc的取值要兼顾系统的快速性、超调量和滤波性能。文献[23-24]通过研究分析和论证,推荐wc的取值区间为40p~50prad/s,本文取wc=45prad/s。将wc= 141.37rad/s、wp=429.15rad/s代入式(17)可得

(18)

(18)

根据电网电压的幅值,由式(18)即可求出PI控制器的参数Kp和Ki。

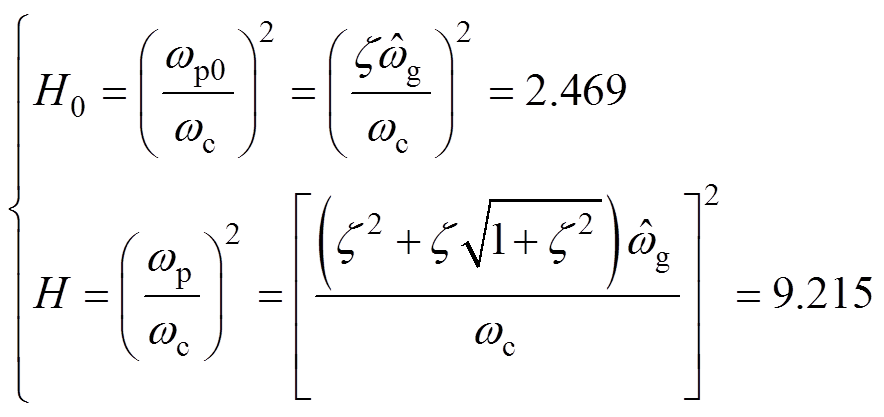

文献[22-24]推导出,ACCF-PLL的数学模型如图8所示,故可采用相同的设计方法对CCF-PLL和ACCF- PLL进行分析。为具有可比性,两者的前级滤波系统采用相同的阻尼比 ,且整个控制系统选用相同的开环截止频率45prad/s,使它们的分离特性、响应速度和滤波特性基本一致。图10展示了两种PLL在三阶最佳设计法下的幅频特性曲线。

,且整个控制系统选用相同的开环截止频率45prad/s,使它们的分离特性、响应速度和滤波特性基本一致。图10展示了两种PLL在三阶最佳设计法下的幅频特性曲线。

图10中,wp0为CCF-PLL前级滤波结构的截止角频率;Kp0、Ki0分别为CCF-PLL中PI控制器的比例项和积分项系数;H0、H分别为CCF-PLL和ACCF-PLL对应控制系统的中频段宽度。由图10可得

图10 CCF-PLL和ACCF-PLL的幅频特性曲线

Fig.10 Magnitude-frequency curves of CCF-PLL and ACCF-PLL

(19)

(19)根据相位裕度和中频段宽度的关系[25],可得

(20)

(20)

式中,g0为CCF-PLL的系统相位裕度。

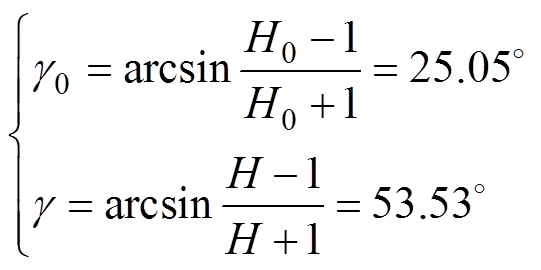

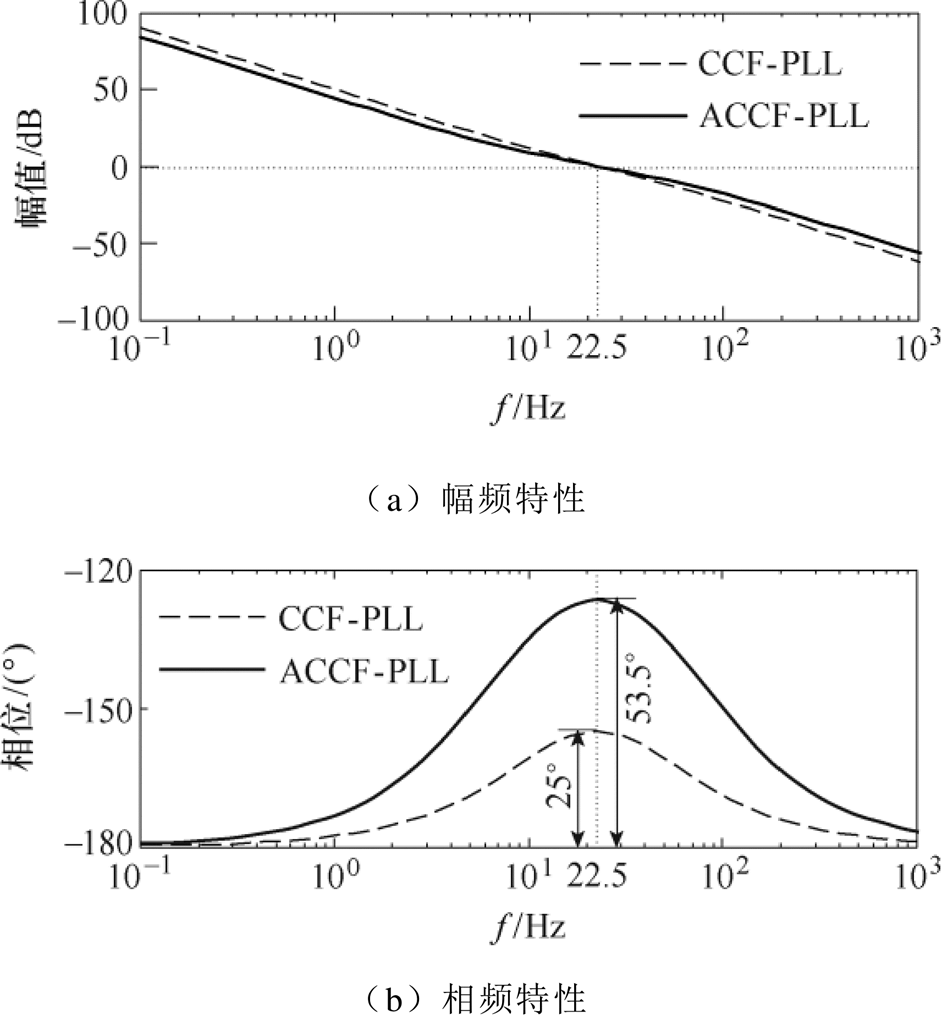

图11给出了CCF-PLL和ACCF-PLL对应控制系统的Bode图。经典控制理论[25]指出,要使控制系统有一个良好的动态调节过程,其相位裕度要达到45°~70°。若相位裕度过低于此范围,系统的动态性能较差,对参数变化较敏感;过高于此范围,系统的稳定程度过好,动态过程会变得很缓慢。由式(20)和图11可知,ACCF-PLL的相位裕度处于上述范围内,而CCF-PLL的相位裕度过低。因此,ACCF-PLL势必会展现出比CCF-PLL更好的动态 性能。

图11 CCF-PLL和ACCF-PLL的Bode图

Fig.11 Bode diagram of CCF-PLL and ACCF-PLL

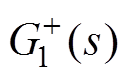

电网电压除存在基波负序外,还会受到谐波污染[26]。ACCF-PLL经上述设计法校正后虽对谐波有一定的抑制能力,但无法将谐波完全滤除。为此,本文仿照多重CCF(Multiple CCF, MCCF)型PLL[15]的架构,设计了如图12所示的基于多重ACCF(Multiple ACCF, MACCF)结构的三相PLL。

图12 基于MACCF结构的三相PLL

Fig.12 MACCF-based three-phase PLL

图12中, (

( )、

)、 (

( )分别为MACCF结构分离出的电网基波和n次谐波的正(负)序分量,n = 2, 3, 4,···。

)分别为MACCF结构分离出的电网基波和n次谐波的正(负)序分量,n = 2, 3, 4,···。

由图12可求得,MACCF结构中输入uab 到输出 的传递函数

的传递函数 为

为

(21)

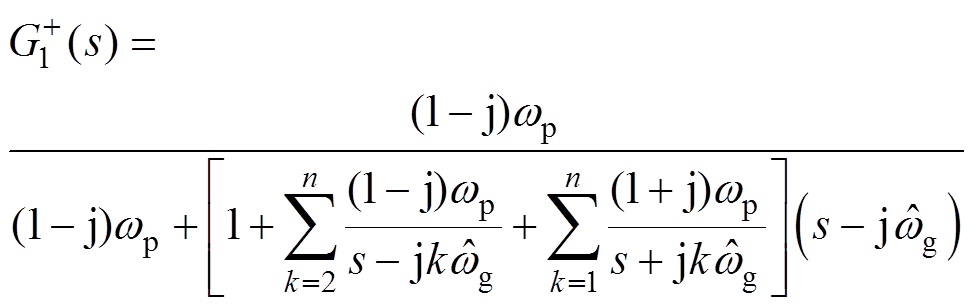

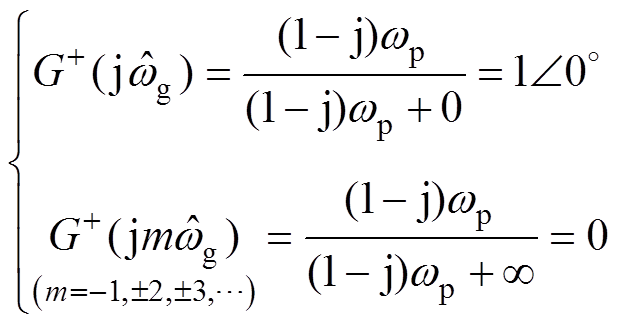

(21)根据式(21),容易求得

(22)

(22)

由式(22)可以看到, 可以复现出电网的FPSC,而对FNSC及各次谐波的正负序能够完全消除。因此

可以复现出电网的FPSC,而对FNSC及各次谐波的正负序能够完全消除。因此 只含有电网的FPSC,从而使后级的SRF-PLL能够提取出纯净的幅值、频率和相位。

只含有电网的FPSC,从而使后级的SRF-PLL能够提取出纯净的幅值、频率和相位。

同理可分析出 只含有电网的FNSC,

只含有电网的FNSC, (

( )只含有电网n次谐波的正(负)序分量。

)只含有电网n次谐波的正(负)序分量。

在实际电网的谐波中,主要以低次(-5次和+7次)谐波为主,高次谐波含量很小[26]。因此,在实际应用MACCF-PLL时,只要在MACCF结构中配置主要的滤波模块即可,而不必过多罗列。

本文1.2节中已提及:在ab 坐标系下,任一变量hab 均满足:jha=-hb,jhb=ha。故ACCF结构中正负序滤波器的实现方法如图13所示。图中,rab、yab 分别为复数滤波器的输入和输出信号。

图13 全复数型滤波器的实现方法

Fig.13 Implementation of the ACCF

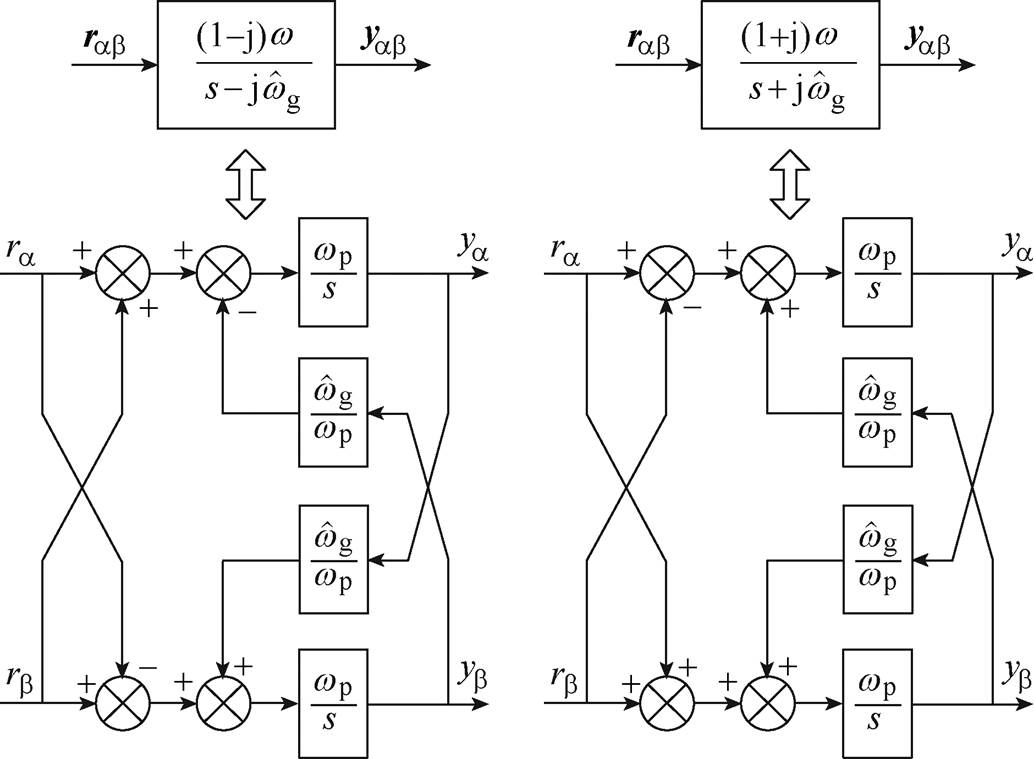

为确保离散精度和避免出现代数环,这里采用三阶Adams-Bashforth算法[15, 17]对图13和后级PI控制器及积分器中的拉普拉斯算子s进行离散化,具体的数字离散化算法为

(23)

(23)式中,Ts为采样周期。

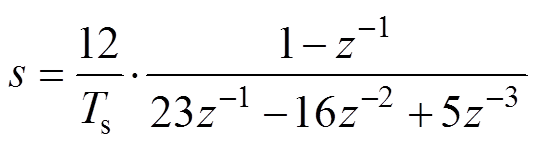

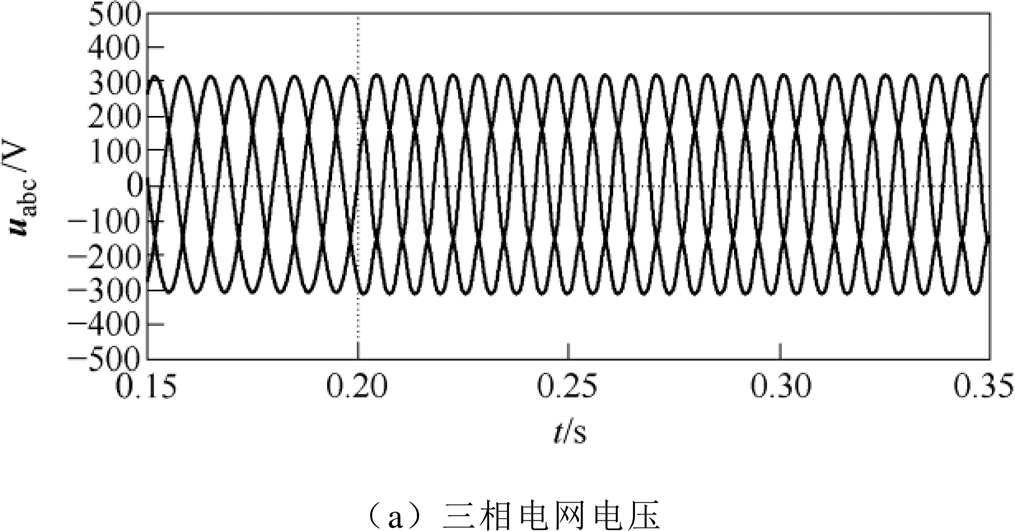

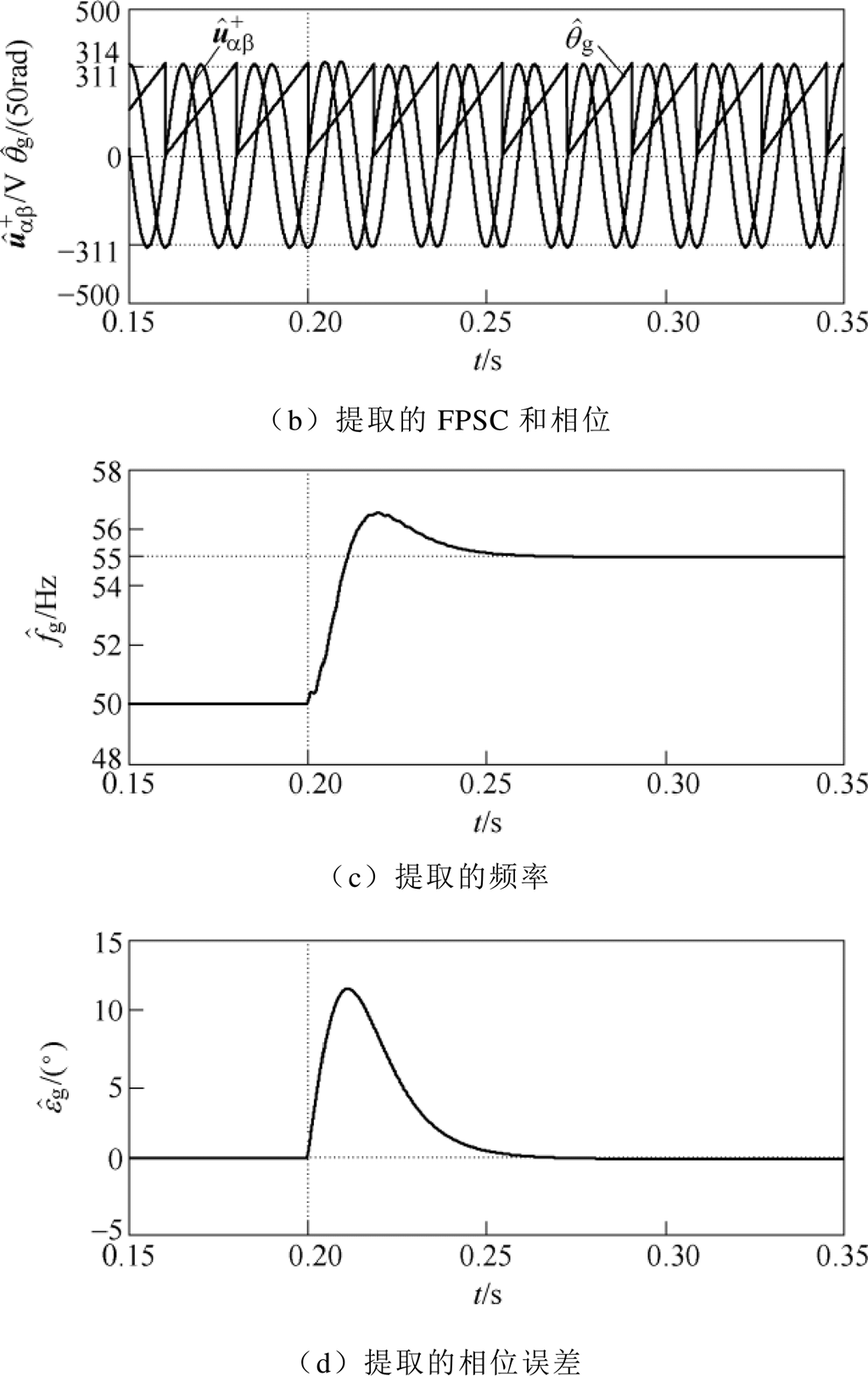

为测试ACCF-PLL的正确性,利用Matlab/ Simulink对该PLL进行了仿真验证。仿真时设置三相电网电压在0~0.2s内为理想电网,即其每相幅值为311V、频率为50Hz;0.2s后,对“注入25%的FNSC”和“频率突变+5Hz”这两种电网变化情况进行验证。控制参数设置为:wp=429.15rad/s,Ts=50ms,Kp=141.37/311,Ki=6 583.59/311。为模拟电网的实际情况,根据国标[27]规定的最恶劣情形,在电网变化的两种测试中均加入了4%的-5次谐波和3%的+7次谐波(使电网总谐波畸变率(Total Harmonic Distortion, THD)达5%),且前级ACCF结构中配置了-5次和+7次滤波模块。电网不平衡情况下的仿真结果和电网频率突变情况下的仿真结果分别如图14和图15所示。图中, 为PLL提取的相位误差;

为PLL提取的相位误差; 为PLL提取的电网频率。

为PLL提取的电网频率。

正负序分离方面:由图14b~图14d可知,分离出的FPSC除在电网突然变化的极短时间内有略微抖动外,其余时间均未发生变化,其幅值保持在1(pu);分离出的FNSC在电网变化后开始出现,其幅值在半个理想电网周期(0.01s)内即由0上升并收敛于0.25(pu)。可见,提出的ACCF-PLL具备迅速、准确的正负序分离能力。

图14 电网不平衡情况下的仿真结果

Fig.14 Simulation results under grid unbalanced conditions

图15 电网频率突变情况下的仿真结果

Fig.15 Simulation results under variable grid frequency conditions

锁频方面:图15c给出了捕获频率的动态响应过程,具体表现为提取的频率在电网变化后由50Hz开始快速追踪,并最终以55Hz为基准作衰减收敛,该过程的动态调节时间为44ms。因此,ACCF-PLL能在较短时间内无静差地锁住频率。

锁相方面:图14b和图15b显示,捕获的相位紧随基波正序电压而变化,即在 的两个相邻正向过零点之间由0线性增至2p;图14e和图15d表明,提取的相位误差在电网变化前后的稳态时均能很好地稳定在0°,即PLL锁住的相位与电网实际的相位之间不存在稳态误差。所以,ACCF-PLL实现了精准锁相。

的两个相邻正向过零点之间由0线性增至2p;图14e和图15d表明,提取的相位误差在电网变化前后的稳态时均能很好地稳定在0°,即PLL锁住的相位与电网实际的相位之间不存在稳态误差。所以,ACCF-PLL实现了精准锁相。

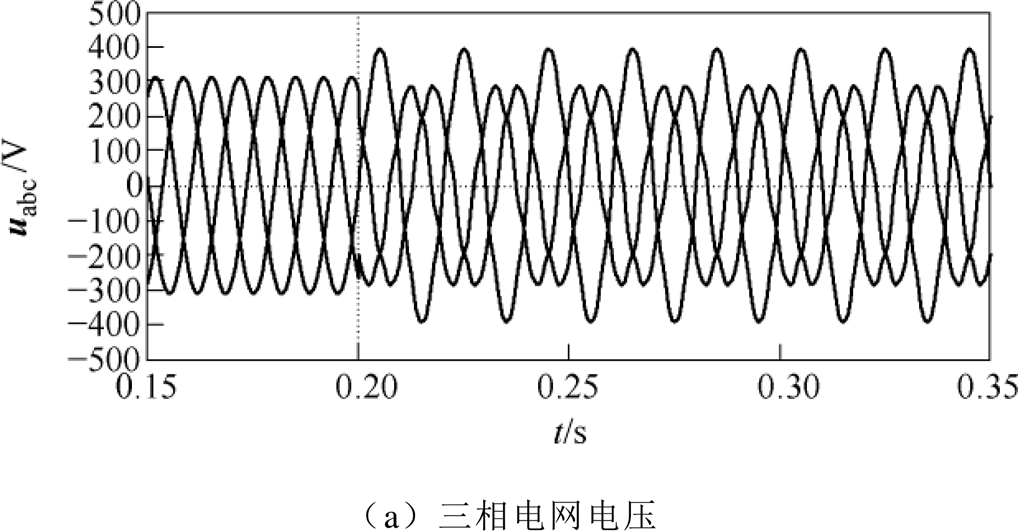

为进一步测试ACCF-PLL的控制性能,将其与CCF-PLL进行对比实验验证,选用TMS320F28335 DSP作为控制芯片,内部变量(如电压、幅值、频率和相位等)由DAC7725数模转换芯片输出,设置DSP的采样频率为20kHz(即采样周期Ts= 50ms)。实验中对“频率突变+5Hz”和“相位跳变+20°”这两种电网情形进行测试。电网变化时,在这两种情况下都注入了FNSC、-5次和+7次谐波,其含量分别为15%、10%和5%。两PLL的前级结构中都配置了-5次和+7次滤波模块。ACCF-PLL的实验参数与仿真一致。为保证两PLL在同一基础上进行对比,CCF-PLL前级滤波结构的系统阻尼比也设为 ,得wp=222.14rad/s;其PI参数也由三阶最佳设计法进行整定,整定结果与式(17)一致(其中的wc与ACCF-PLL相同,取为45prad/s)。频率突变+5Hz下的实验结果和相位跳变+20°下的实验结果分别如图16和图17所示。

,得wp=222.14rad/s;其PI参数也由三阶最佳设计法进行整定,整定结果与式(17)一致(其中的wc与ACCF-PLL相同,取为45prad/s)。频率突变+5Hz下的实验结果和相位跳变+20°下的实验结果分别如图16和图17所示。

稳态性能上:在这两种畸变/不平衡的电网测试环境中,ACCF-PLL都能成功提取出电网的FPSC/ FNSC(见图16b和图17b)、相位(见图16c和图17c)和频率(见图16d和图17d)。由FPSC/FNSC的幅值曲线(见图16c和图17c)、频率响应曲线(见图16d和图17d)和相位误差曲线(见图16d和图17d)可以看到,这些变量都能无波动地稳定在初始值(或0)和无偏差地跟踪预设的变化值,说明所设计的ACCF-PLL是一个稳定的无静差控制系统,能够精确进行基波正负序分离、锁频和锁相。

图16 频率突变+5Hz下的实验结果

Fig.16 Experimental results under frequency step change of +5Hz

图17 相位跳变+20°下的实验结果

Fig.17 Experimental results under phase jump of +20°

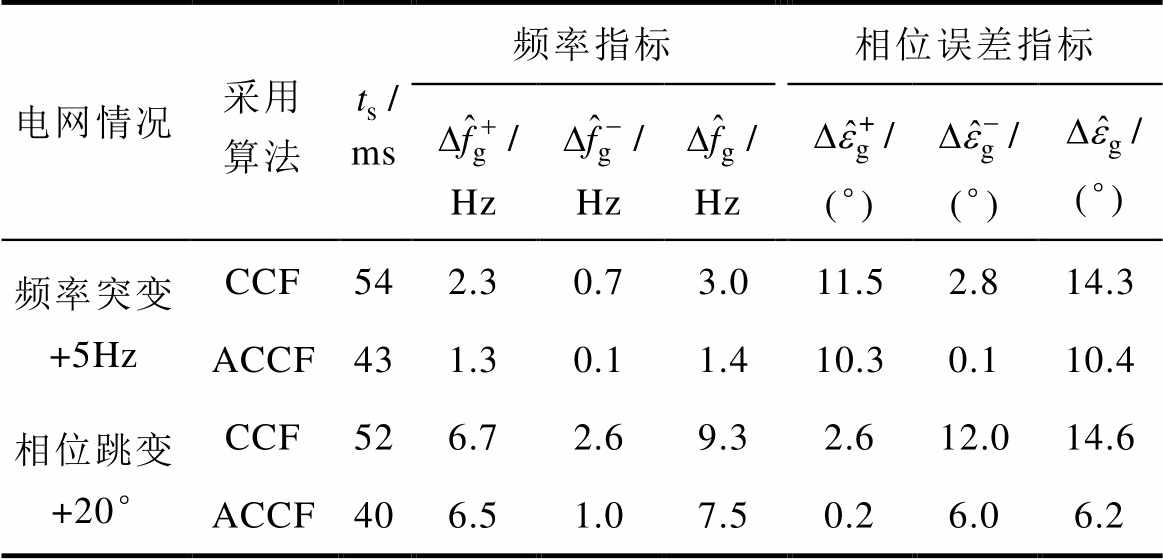

动态性能上:图16d和图17d展示了CCF-PLL和ACCF-PLL在提取电网频率及相位误差上的对比结果。表1根据实验数据给出了两者具体的动态指标值。可见,ACCF-PLL在动态收敛过程中表现出的衰减程度和速度都要大于CCF-PLL;产生的频率超调和相位误差超调要小于CCF-PLL,尤其是第二次离开稳态值的反向超调要比CCF-PLL小很多;两种PLL虽看似有相近的调节时间,但ACCF-PLL进入终值误差带的时刻要早于CCF-PLL,响应速度更快。综上,ACCF-PLL呈现出的动态行为要优于CCF-PLL。

表1 CCF-PLL和ACCF-PLL的动态指标值

Tab.1 The dynamic index ofCCF-PLL and ACCF-PLL

电网情况采用算法/ ms频率指标相位误差指标 / Hz/ Hz/ Hz/ (°)/ (°)/ (°) 频率突变+5HzCCF542.30.73.011.52.814.3 ACCF431.30.11.410.30.110.4 相位跳变+20°CCF526.72.69.32.612.014.6 ACCF406.51.07.50.26.06.2

表1中, 为系统调节时间;

为系统调节时间; (

( )为频率(相位误差)偏离稳态值的最大正向偏差;

)为频率(相位误差)偏离稳态值的最大正向偏差; (

( )为最大负向偏差;

)为最大负向偏差; (

( )为峰-峰偏差值。

)为峰-峰偏差值。

抗干扰性能上:由图16a和图17a可以看出,测试PLL的电网环境是较为恶劣的,但两种PLL提取的各信号在稳态时不存在谐波或波动,即PLL完全抑制了所加入的各次谐波。因此,CCF-PLL和ACCF-PLL都具备较强的抗干扰能力。

为改进PLL的控制性能,在CCF-PLL的基础上,提出了一种将前级CCF结构全面复数化的三相PLL技术,即ACCF-PLL算法。通过理论分析、仿真验证和对比实验,得出如下结论:

1)ACCF结构保持了CCF结构控制原理简单的优势,在FPSC和FNSC处具有正负频率的选择性,无需对称分量法即可分离出FPSC和FNSC。

2)相比CCF结构,ACCF结构提高了其截止频率,从而能够拉宽整个PLL系统的中频段宽度。

3)若CCF-PLL和ACCF-PLL的前级滤波结构选用相同的阻尼比,且整个控制系统采用一致的开环截止频率,经三阶最佳设计法校正后,ACCF-PLL的相位裕度明显优于CCF-PLL。

4)在电网频率、相位和负序突变时,ACCF-PLL都能准确进行基波正负序分离、锁频和锁相;测得的频率和相位误差超调量要小于CCF-PLL,系统响应速度也快于后者。因此,ACCF-PLL表现出的动态性能更优异。

5)在畸变电网环境下,ACCF结构中配置的滤波模块能完全消除电网谐波对系统输出的影响。

参考文献

[1] Tezer T, Yaman R, Yaman G. Evaluation of approaches used for optimization of stand-alone hybrid renewable energy systems[J]. Renewable and Sustainable Energy Reviews, 2017, 73: 840-853.

[2] 涂春鸣, 高家元, 赵晋斌, 等. 弱电网下具有定稳定裕度的并网逆变器阻抗重塑分析与设计[J]. 电工技术学报, 2020, 35(6): 1327-1335.

Tu Chunming, Gao Jiayuan, Zhao Jinbin, et al. Analysis and design of grid-connected inverter impedance remodeling with fixed stability margin in weak grid[J]. Transactions of China Electrotechnical Society, 2020, 35(6): 1327-1335.

[3] Castelló J, Espí J M, García-gil R. A new generalized robust predictive current control for grid-connected inverters compensates anti-aliasing filters delay[J]. IEEE Transactions on Industrial Electronics, 2016, 63(7): 4485-4494.

[4] 王晓寰, 张旭东, 郭红强. 基于相位簇扰动的下垂控制并网逆变器孤岛检测[J]. 电工技术学报, 2020, 35(8): 1728-1738.

Wang Xiaohuan, Zhang Xudong, Guo Hongqiang. Islanding detection of droop-controlled grid-connected inverters on phase cluster disturbance[J]. Transactions of China Electrotechnical Society, 2020, 35(8): 1728- 1738.

[5] Guo Xiaoqiang, Liu Wenzhao, Lu Zhigang. Flexible power regulation and current-limited control of the grid-connected inverter under unbalanced grid voltage faults[J]. IEEE Transactions on Industrial Electronics, 2017, 64(9): 7425-7432.

[6] 涂春鸣, 葛钦, 肖凡, 等. 基于光伏电源支撑的多端口固态变压器故障穿越策略[J]. 电工技术学报, 2020, 35(16): 3498-3508.

Tu Chunming, Ge Qin, Xiao Fan, et al. Fault ride- through control strategy of solid state transformer with PV power generation[J]. Transactions of China Electrotechnical Society, 2020, 35(16): 3498-3508.

[7] 何宇, 漆汉宏, 罗琦, 等. 基于分数阶滤波器的三相锁相环技术[J]. 电工技术学报, 2019, 34(12): 2572-2583.

He Yu, Qi Hanhong, Luo Qi, et al. A novel three- phase phase-locked loop method based on fractional- order filter[J]. Transactions of China Electrotechnical Society, 2019, 34(12): 2572-2583.

[8] Hans F, Schumacher W, Harnefors L. Small-signal modeling of three-phase synchronous reference frame phase-locked loops[J]. IEEE Transactions on Power Electronics, 2018, 33(7): 5556-5560.

[9] Golestan S, Guerrero J M, Vidal A, et al. PLL with MAF-based prefiltering stage: small-signal modeling and performance enhancement[J]. IEEE Transactions on Power Electronics, 2016, 31(6): 4013-4019.

[10] Li Haoyuan, Zhang Xing, Xu Chengjun, et al. Sensorless control of IPMSM using moving-average- filter based PLL on HF pulsating signal injection method[J]. IEEE Transactions on Energy Conversion, 2020, 35(1): 43-52.

[11] Lee K J, Lee J P, Shin D, et al. A novel grid synchronization PLL method based on adaptive low-pass notch filter for grid-connected PCS[J]. IEEE Transactions on Industrial Electronics, 2014, 61(1): 292-301.

[12] 张国强, 王高林, 徐殿国, 等. 基于自适应陷波滤波器的内置式永磁电机转子位置观测方法[J]. 中国电机工程学报, 2016, 36(9): 2521-2527.

Zhang Guoqiang, Wang Gaolin, Xu Dianguo, et al. Adaptive notch filter based rotor position estimation for interior permanent magnet synchronous motors[J]. Proceedings of the CSEE, 2016, 36(9): 2521-2527.

[13] 杨才伟, 王剑, 游小杰, 等. 二阶广义积分器锁频环数字实现准确性对比[J]. 电工技术学报, 2019, 34(12): 2584-2596.

Yang Caiwei, Wang Jian, You Xiaojie, et al. Accuracy comparison of digital implementation on the second-order generalized integrator frequency- locked loop[J]. Transactions of China Electro- technical Society, 2019, 34(12): 2584-2596.

[14] Chen Ke, Ai Wu, Chen Bing, et al. Measuring and reconstruction algorithm based on improved second- order generalised integrator configured as a quadrature signal generator and phase locked loop for the three- phase AC signals of independent power generation systems[J]. IET Power Electronics, 2016, 9(11): 2155-2161.

[15] Guo Xiaoqiang, Wu Weiyang, Chen Zhe. Multiple- complex coefficient-filter-based phase-locked loop and synchronization technique for three-phase grid- interfaced converters in distributed utility networks[J]. IEEE Transactions on Industrial Electronics, 2011, 58(4): 1194-1204.

[16] Guo Xiaoqiang, Guerrero J M. Abc-frame complex- coefficient filter and controller based current harmonic elimination strategy for three-phase grid connected inverter[J]. Journal of Modern Power Systems and Clean Energy, 2016, 4(1): 87-93.

[17] Li Weiwei, Ruan Xinbo, Bao Chenlei, et al. Grid synchronization systems of three-phase grid- connected power converters: a complex-vector-filter perspective[J]. IEEE Transactions on Industrial Electronics, 2014, 61(4): 1855-1870.

[18] 何宇, 漆汉宏, 邓超, 等. 一种嵌入重复控制内模的三相锁相环的设计与实现[J]. 电工技术学报, 2016, 31(22): 83-91.

He Yu, Qi Hanhong, Deng Chao, et al. A novel three-phase phase-locked loop method based on internal model of repetitive control[J]. Transactions of China Electrotechnical Society, 2016, 31(22): 83-91.

[19] Busada C, Jorge S G, Leon A E, et al. Current controller based on reduced order generalized integrators for distributed generation systems[J]. IEEE Transactions on Industrial Electronics, 2012, 59(7): 2898-2909.

[20] Guest E, Mijatovic N. Discrete-time complex band- pass filters for three-phase converter systems[J]. IEEE Transactions on Industrial Electronics, 2019, 66(6): 4650-4660.

[21] An Quntao, Zhang Jianqiu, An Qi, et al. Frequency- adaptive complex-coefficient filter-based enhanced sliding mode observer for sensorless control of permanent magnet synchronous motor drives[J]. IEEE Transactions on Industry Applications, 2020, 56(1): 335-343.

[22] Ramezani M, Golestan S, Li S, et al. A simple approach to enhance the performance of complex- coefficient filter-based PLL in grid-connected appli- cations[J]. IEEE Transactions on Industrial Electro- nics, 2018, 65(6): 5081-5085.

[23] Golestan S, Monfared M, Freijedo F D. Design- oriented study of advanced synchronous reference frame phase-locked loops[J]. IEEE Transactions on Power Electronics, 2013, 28(2): 765-778.

[24] Golestan S, Monfared M, Freijedo F D, et al. Performance improvement of a prefiltered synchronous- reference-frame PLL by using a PID-type loop filter[J]. IEEE Transactions on Industrial Electronics, 2014, 61(7): 3469-3479.

[25] 胡寿松. 自动控制原理[M]. 6版. 北京: 科学出版社, 2013.

[26] Ahmed H, Bierhoff M, Benbouzid M, et al. Multiple nonlinear harmonic oscillator-based frequency esti- mation for distorted grid voltage[J]. IEEE Transa- ctions on Instrumentation and Measurement, 2020, 69(6): 2817-2825.

[27] 曲涛, 任元, 林海雪, 等. GB/T 14549-1993电能质量—公用电网谐波[S]. 中华人民共和国国家标准, 1993.

A Three-Phase Phase-Locked Loop Technique Based on All Complex Coefficient Filter

Abstract Recently, the complex-coefficient-filter (CCF)-based phase-locked loop (PLL) technique has become a hotspot in grid synchronization research. However, the mathematical model and control performance of the current CCF-PLL have been confirmed to be basically consistent with the traditional real coefficient filter PLL. In order to improve the control performance, a novel three-phase PLL based on all complex coefficient filter is put forward. Firstly, the voltage transfer function of the pre-stage filter structure is given, and it is demonstrated that the structure can accurately separate the fundamental positive- and negative-sequence components. Then, the mathematical model of the pre-stage structure on the fundamental positive-sequence phase is derived. Combined with the post-stage synchronous rotating frame PLL, the mathematical model of the entire PLL system is built, and then the system is designed by the third-order optimum correction method. Wherein, the related control parameters are determined. It is shown that with the same open-loop cut-off frequency, the proposed PLL has a wider mid-frequency band width and a larger phase margin than the CCF-PLL. In addition, a multiple all-complex-coefficient-filter based PLL is designed to thoroughly eliminate harmonics. Finally, simulation and experimental results show that the control performance of the proposed PLL is better than that of the CCF-PLL.

keywords:Phase-locked loop, complex coefficient filter, control performance, phase margin

中图分类号:TM464

DOI: 10.19595/j.cnki.1000-6753.tces.L90095

江苏省高等学校自然科学研究项目(19KJB460028, 20KJB520021)、江苏省高等学校优秀科技创新团队项目(2019SJK07)和江苏信息职业技术学院2020年重点科研课题项目(JSITKY202008)资助。

收稿日期 2020-06-22

改稿日期 2020-10-22

何 宇 男,1989年生,硕士,讲师,研究方向为电力电子功率变换与控制、新能源发电技术。E-mail: galuohua@163.com

漆汉宏 男,1968年生,博士,教授,博士生导师,研究方向为电力电子功率变换与控制、新能源发电技术。E-mail: hhqi@ysu.edu.cn(通信作者)

(编辑 陈 诚)