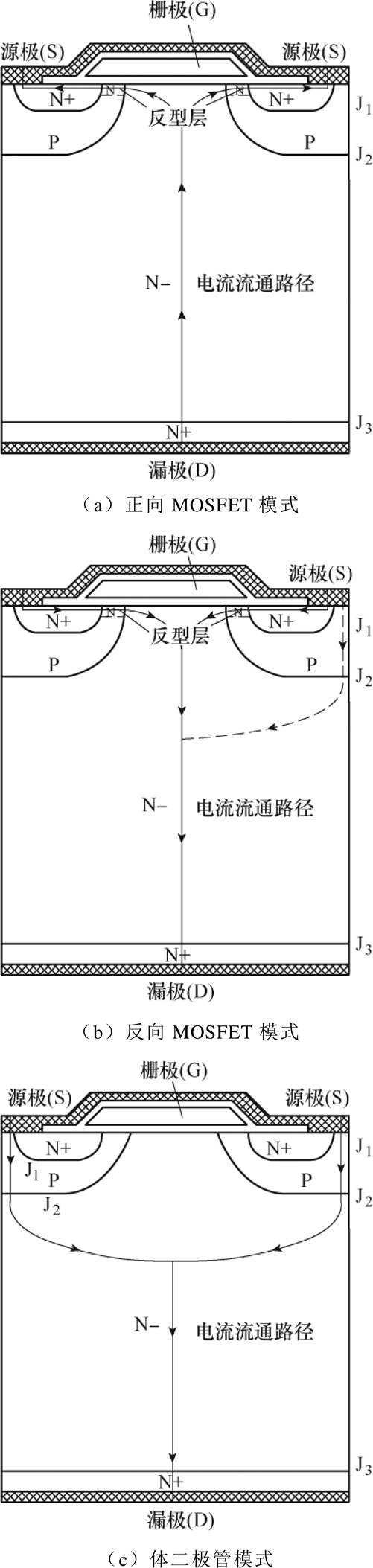

图1 MOSFET的三种不同导通模式

Fig.1 Three different conduction modes for MOSFET

摘要 SiC MOSFET凭借其优异的电热特性,正逐渐投入市场,长期运行其可靠性成为关注的重点,功率循环试验是考核器件可靠性最重要的老化试验。MOSFET具有三种导通模式,分别对应三种不同的功率循环测试方法。为探究和对比SiC MOSFET在不同老化试验方法下的失效机理和失效表征参数的变化规律,对其在不同导通模式下进行功率循环试验,基于不同导通模式下的特性分析,重点对比正向MOSFET模式和体二极管模式。SiC MOSFET中的界面陷阱会造成阈值电压漂移,为此提出一种判断准则以及相应的功率循环试验方法,可以将阈值电压漂移对试验结果的影响最小化,并在老化试验过程中实现结温、通态压降和热阻的在线测量。结果表明,在两种模式下失效方式均为键合线老化,但是老化后的电热反馈机制不同,造成其退化规律和寿命不同,相同热力条件下体二极管模式下的寿命约为正向MOSFET模式下的两倍。

关键词:SiC MOSFET 功率循环试验 导通模式 阈值电压漂移 结温测量 失效机理

近年来,随着碳化硅(Silicon Carbide, SiC)在材料生长和器件加工方面取得长足的进步,基于SiC材料的功率半导体器件在众多领域展现出越来越多的应用,例如金属-氧化物-半导体场效应晶体管(Metal-Oxide-Semiconductor Field Effect Transi- stor, MOSFET)[1]。SiC MOSFET以其高临界击穿场强、高开关频率、耐高温等突出优点,更加适合高压、高频、高温等应用场合[2-3]。随着SiC MOSFET的逐步商业应用,其长期运行可靠性问题开始受到了学术界和工业界的重视。

尽管SiC材料能够耐受高温,理论上可以达到500℃,但是受限于封装技术等方面的制约,目前SiC器件的封装仍采用传统Si器件的封装,无法发挥其高温工作的特性,市面上SiC MOSFET产品的最高工作温度均没有超过200℃[4],因此可以认为,封装技术是限制SiC器件在高温下应用的主要原 因[5]。同时由于制造成本高,SiC芯片面积较小,这将意味着相对较高的功率密度和工作温度。而且较之于Si芯片,SiC芯片的杨氏模量更大,大约是前者的3倍[6]。这些问题将导致SiC器件在工作过程中更容易出现因热应力产生的封装材料老化问题,可靠性问题更加严峻[7]。

功率循环试验是研究热应力加速老化试验条件下可靠性的有效方法,是进行器件失效机理分析和寿命评估最有效的手段[8]。通过给被测器件施加相应的负载电流使得器件结温升高达到指定结温,然后切断负载电流使其降温,如此反复升温和降温过程以达到使器件老化的目的,也称为主动温度循环。目前主流功率循环试验主要让器件工作在导通模式,依靠导通损耗来产生结温波动。对于绝缘栅双极型晶体管(Insulated Gate Bipolar Transistor, IGBT)和二极管这种单一导通模式的器件,功率循环试验方法是确定的。MOSFET由于元胞结构的特点,存在正向MOSFET模式、反向MOSFET模式和体二极管模式[9]三种导通模式。不同导通模式下器件的特性不同,导致功率循环试验方法不同,由此产生的失效机理和寿命可能会存在差异[10]。文献[11]中对MOSFET器件的功率循环试验方法也没有明确规定,并且提到可以使用体二极管模式,由此造成不同试验方法之间具有等效性的错觉,然而目前并没有相关文献对此进行研究分析。

另外,传统的基于Si器件的功率循环试验方法和失效标准可能不适用于新型的SiC MOSFET器件。众所周知,SiC MOSFET区别于Si MOSFET的一个重要特征是SiC/SiO2界面存在着大量的界面陷阱[12]。界面陷阱能够捕获沟道载流子,造成阈值电压漂移,漂移程度很大程度上取决于施加的栅极电压。在正向栅极偏压下,界面缺陷捕获沟道中的电子造成阈值电压正向漂移,而在反向栅极偏压下,界面缺陷捕获沟道中的空穴造成阈值电压反向漂 移[13]。阈值电压漂移最直接的影响就是造成芯片通态电阻的变化,进而影响通态压降和结温,给SiC MOSFET功率循环试验增加了难度[14]。

本文对SiC MOSFET在不同导通模式下进行功率循环试验,探究和对比其在不同老化试验方法下的失效机理和失效表征参数的变化规律。首先,基于器件在不同导通模式下的特性分析,重点对比正向MOSFET模式和体二极管模式,其中体二极管模式下的功率循环方法简单且容易实现,而正向MOSFET模式下,为了将阈值电压漂移的影响最小化,提出一种判断准则以及相应的功率循环试验方法,并在老化试验过程中实现结温、通态压降和热阻的在线测量。最后,基于实验结果,分析了不同功率循环试验方法对器件的老化规律、失效机理及寿命的影响,为SiC MOSFET的功率循环试验老化方法提供理论指导,并揭示影响SiC MOSFET封装可靠性的主要因素。

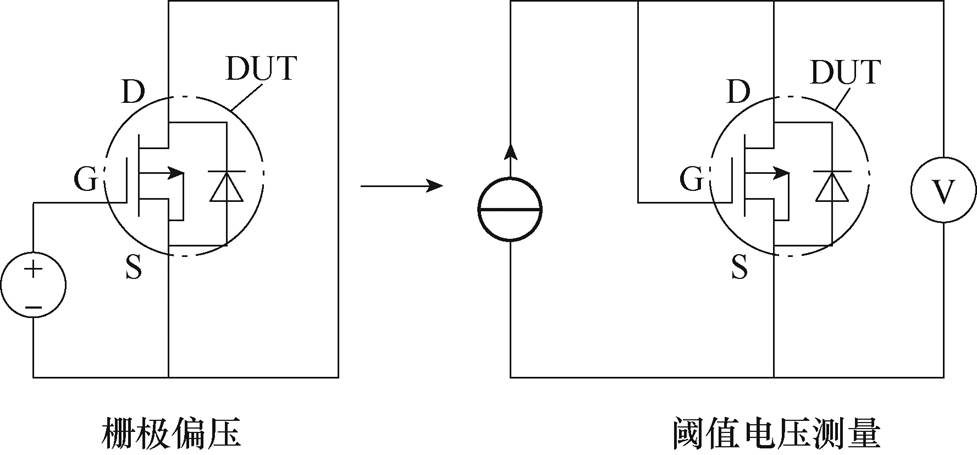

相比IGBT正向导通的单一导通模式,MOSFET由于其元胞结构的特点,拥有正向MOSFET模式、反向MOSFET模式和体二极管模式三种不同的导通模式,三种模式下电流流通路径如图1所示。一般情况下,功率MOSFET器件工作在正向MOSFET模式,此时正向电压加在漏极上,当栅极电压增加到超过阈值电压时,反型层逐渐形成,沟道开始流过电流,电流的流向从漏极到源极;在DC-DC的Buck变换器中,功率MOSFET器件有时也会工作在反向MOSFET模式,此时正向电压加在源极上,电流的流向从源极到漏极;体二极管是功率MOSFET器件的寄生结构,当MOSFET从导通状态切换到关断状态时,体二极管可以作为续流二极管使用,此时功率MOSFET器件处于体二极管导通模式。值得注意的是,当电流较小时,正向MOSFET模式和反向MOSFET模式是完全对称和等效的,仅仅是电流流向不同,但是当电流较大时,负载电流有可能从源极经过PN结J2到漏极,如图1b中虚线所示,此时处于等效正向MOSFET模式和体二极管模式的混合模式。

图1 MOSFET的三种不同导通模式

Fig.1 Three different conduction modes for MOSFET

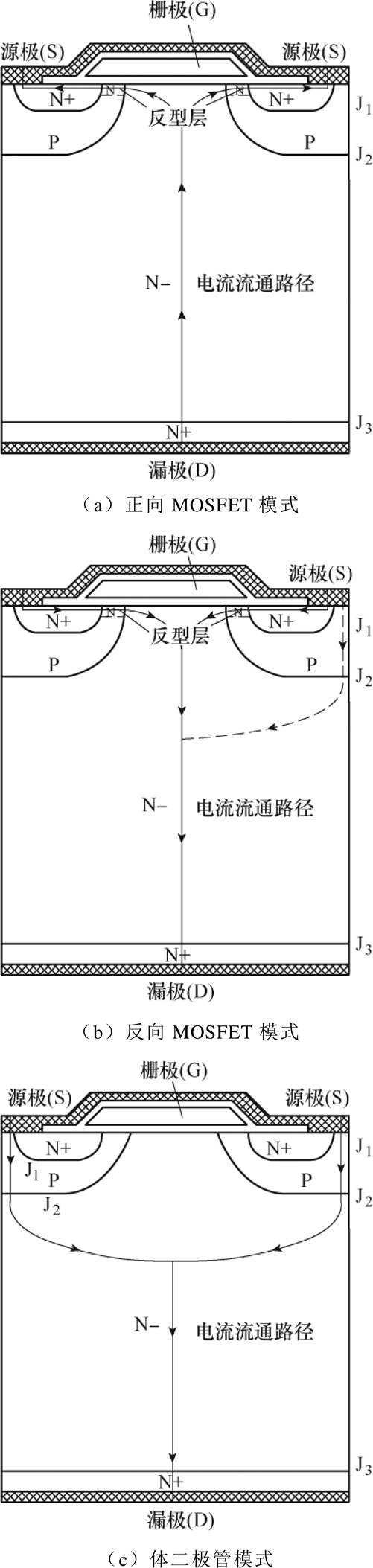

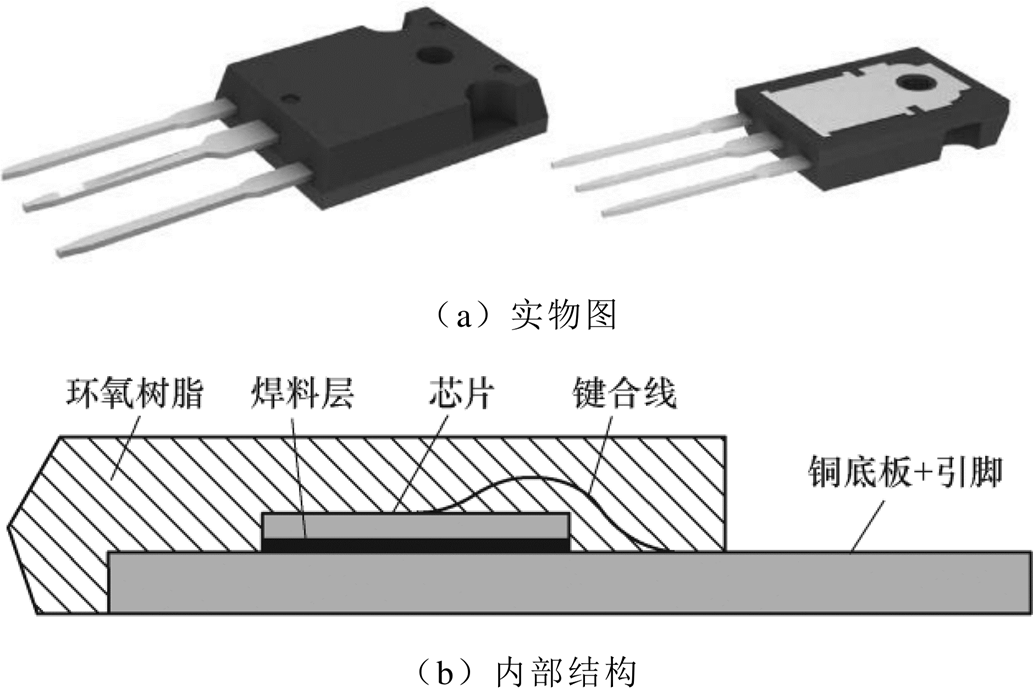

本文选择CREE公司的C3M0120090D SiC MOSFET器件作为实验研究对象,其实物图和内部结构如图2所示。该器件为TO-247封装形式,额定电压900V,导通电阻120mW,额定电流23A(@Tc=25℃)。采用Agilent B1505A测量器件在30℃和150℃下的三种导通模式下I-V特性,正向MOSFET模式和反向MOSFET模式下测量时的栅极电压均为15V,体二极管模式下测量时的栅极电压为-5V,由于三种模式对应不同工作象限(第一象限和第三象限),为了直观对比绘制在同一象限,结果如图3所示。从图中可以看出,当电流较小时,反向MOSFET模式和正向MOSFET模式的I-V特性完全相同;当电流较大时,由于导通电压的上升,负载电流被体二极管分流,此时可以看作是等效正向MOSFET和体二极管的组合。由于SiC MOSFET的体二极管通态压降较大,整体来看,反向MOSFET 模式下的I-V特性和正向MOSFET模式下的特性比较接近,呈现正温度特性,体二极管模式则呈现负温度特性。

图2 待测SiC MOSFET的结构示意图

Fig.2 Schematic diagram of the SiC MOSFET under test

图3 SiC MOSFET在不同模式下的I-V特性

Fig.3 I-V characteristics of SiC MOSFET in different conduction modes

对于MOSFET器件的功率循环试验,可以采用体二极管导通模式用于加热器件,进而达到加速老化的目的。根据对三种导通模式的分析发现,正向MOSFET模式和体二极管模式是两种完全不同的模式,反向MOSFET模式可以看作是这两种模式的混合。因此,本节对SiC MOSFET器件分别在正向MOSFET和体二极管模式两种模式下进行功率循环老化试验,研究不同试验方法对老化规律、失效机理以及寿命的影响。

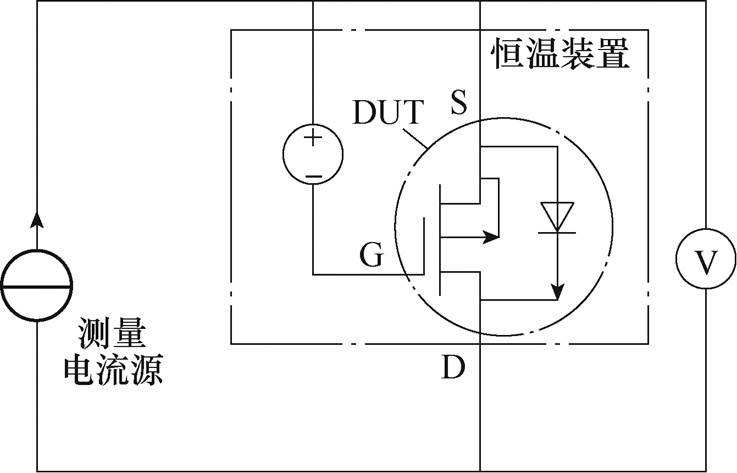

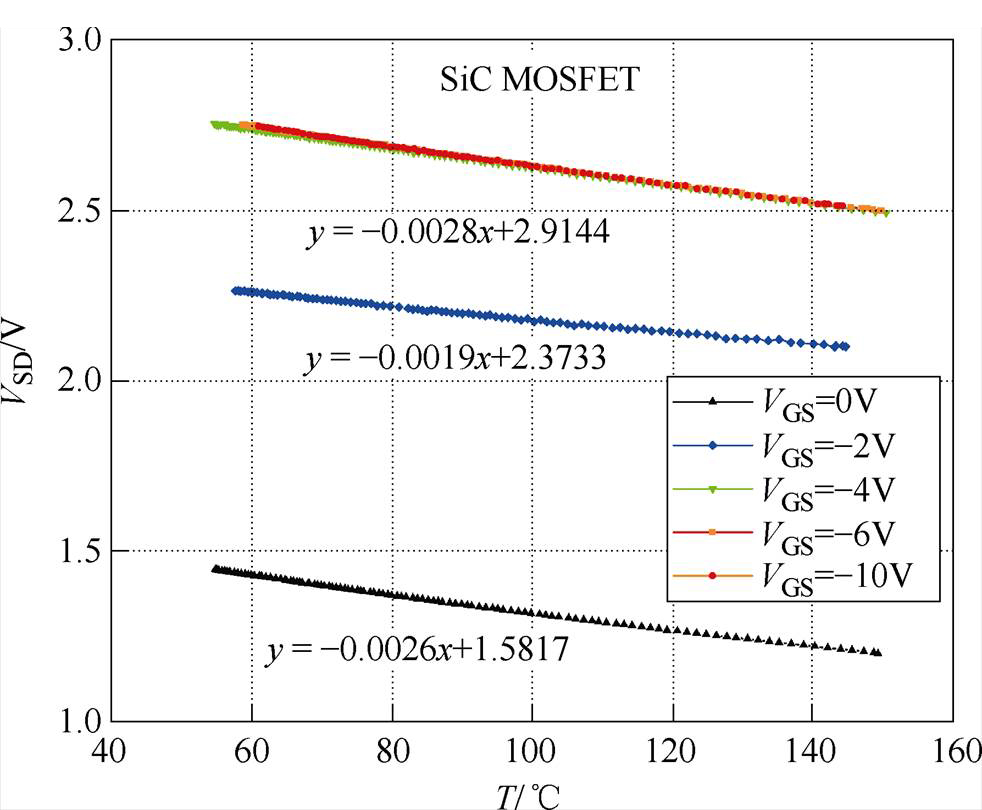

结温是影响功率循环试验结果最重要的一个参数,因此准确的结温测量对于功率循环试验尤为重要[15]。芯片被封装在器件内部,使得结温难以直接测量,一般采用温敏电参数方法进行结温的间接测量,合适的温敏电参数应该不随器件老化而发生变化[16]。在Si MOSFET功率循环试验中常使用三种温敏电参数进行结温测量,分别是通态电阻、阈值电压和小电流下体二极管压降[9]。然而,由于SiC MOSFET的SiC/SiO2界面处存在着大量的界面陷阱,捕获沟道中的载流子,造成阈值电压漂移,进而导致通态电阻的变化。因此,目前适合SiC MOSFET功率循环试验中结温测量的温敏电参数只有小电流下体二极管压降,这种方法也被称为VSD(T)法[17]。如图1c所示,MOSFET元胞结构中有一个寄生体二极管,当栅极沟道彻底关闭时,施加一个小的测量电流从源极(S)经过一个PN结J2后从漏极(D)流出,此时测量SD之间的通态压降即可利用校准关系得到器件的结温。对于Si MOSFET,当栅极电压为0V时,沟道可以完全关断,而SiC MOSFET在0V的栅极电压下沟道并不能完全关断,这也是其有别于Si MOSFET的又一个重要特性之一。因此,需要在不同栅极电压下进行温度系数校准,以确定应用VSD(T)法时选择合适的栅极电压。温度校准实验的电路原理如图4所示,通过恒温装置将待测器件(Device Under Test, DUT)加热至指定温度后停止加热,待温度稳定后开始自然缓慢下降,此时可以认为整个器件的温度处处相同,芯片的结温和外部壳温相等,这时测量得到的壳温将被认为是器件的结温。在寄生体二极管上施加一个恒定的50mA测量电流,记录器件两端的通态压降VSD和壳温T即可。实验得到的校准曲线如图5所示,可以看出,当栅极电压从-4~0V之间变化时,温度校准曲线是不同的,相同的温度下,栅极电压越小,通态压降越大,当栅极电压从-4V到-10V变化时,温度校准曲线不发生变化。其根本原因在于当栅极电压处于-4~0V之间时,SiC MOSFET的沟道区并没有被彻底关断,一部分测量电流被反向MOSFET分流,处于反向MOSFET模式和体二极管模式的混合态。因此,SiC MOSFET应用VSD(T)法进行结温测量时,栅极需要施加一定的负压来关断沟道区,对于本实验所用的器件,栅极电压至少需要-4V。

图4 温度校准实验电路原理

Fig.4 Circuit diagram of the calibration experiment

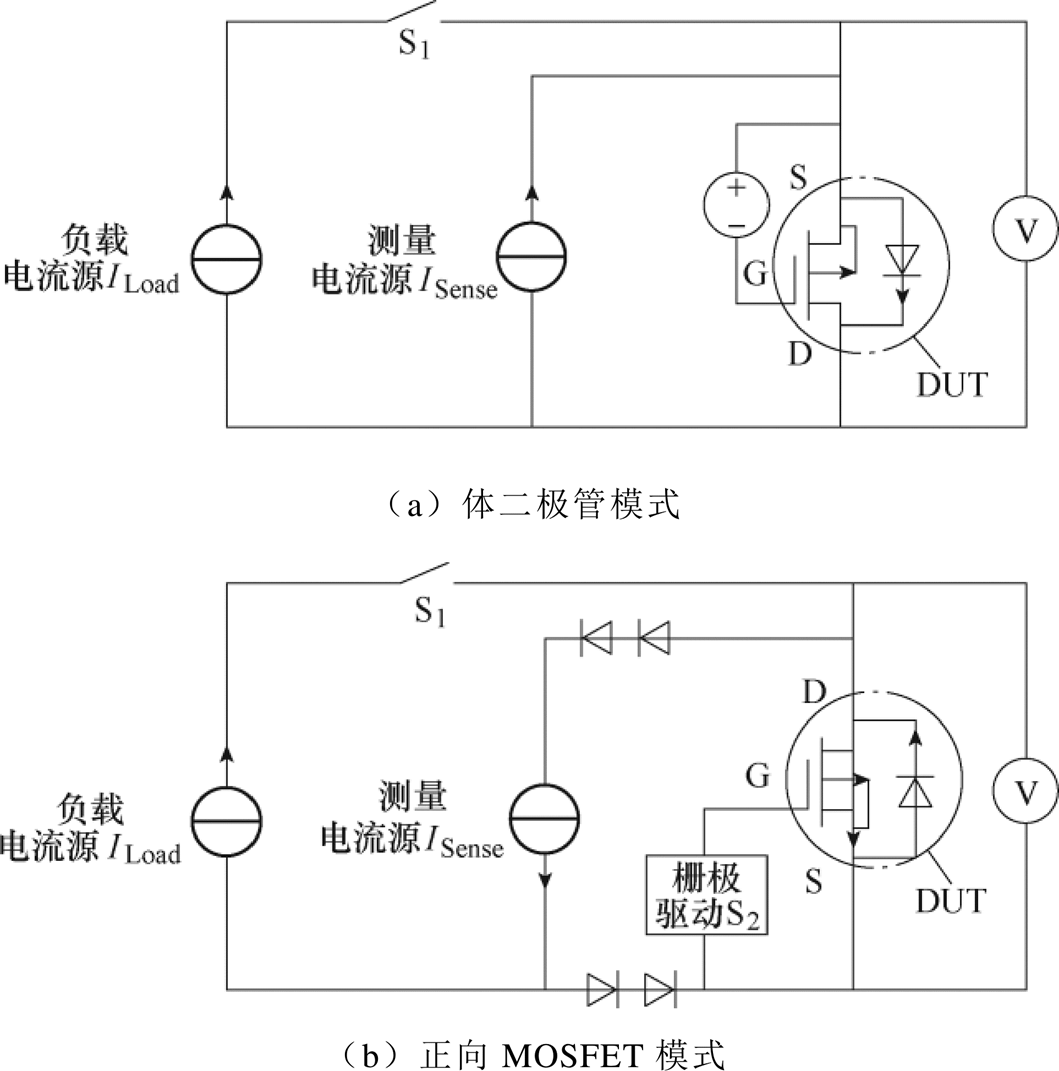

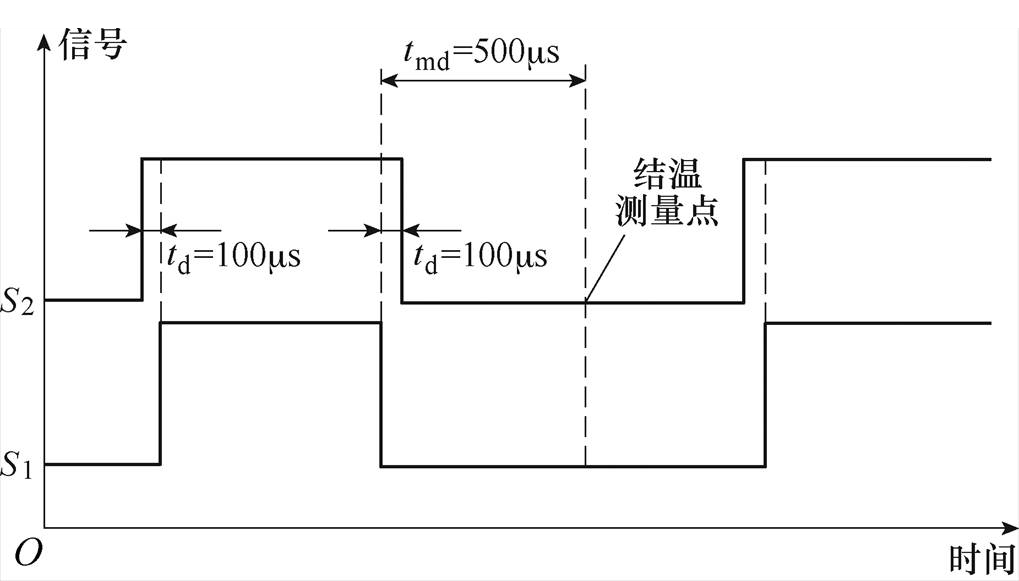

体二极管模式和正向MOSFET模式下的功率循环试验电路原理如图6所示。体二极管模式下,在MOSFET栅极一直施加负压,使得沟道区能彻底关闭,至少需要-4V的栅极电压才符合要求,此时负载电流和测量电流同向,均通过体二极管,和常规IGBT以及二极管的功率循环试验方法类似,电路结构简单容易实现。正向MOSFET模式下,负载电流和测量电流反向,在加热阶段,MOSFET的栅极需要施加15V使其开通,负载电流流经MOSFET,在冷却阶段,MOSFET的栅极施加至少-4V的电压使其关断,测量电流流经体二极管用于测量结温。测试支路的开关S1和栅极驱动S2的信号的时序如图7所示,为了避免控制系统信号传输过程中的延迟造成逻辑冲突,S1和S2之间设置100μs的延迟时间。同时,结温测量会在负载电流被关断后的500μs后测量,避免载流子复合效应导致结温测量误差[18]。因为负载电流和测量电流反向,在MOSFET导通时,负载电流可能会流经测量电流源,导致测量电流源的损坏。为了保护测量电流源,在测量电流和待测器件之间串联多个二极管,使得测量电流源支路的开启电压大于被测器件的通态压降,保证负载电流只从被测器件上流过。一般硅二极管的开启电压在0.5V左右,串联数量需要根据待测器件的通态压降的大小来决定。

图5 不同栅极电压下的温度校准曲线

Fig.5 Calibration curves at different gate voltages

图6 MOSFET两种不同模式下功率循环试验原理

Fig.6 Power cycling test schematic diagram of MOSFET under two different modes

图7 正向MOSFET模式下开关的控制时序

Fig.7 Control timing of the switch in forward MOSFET mode

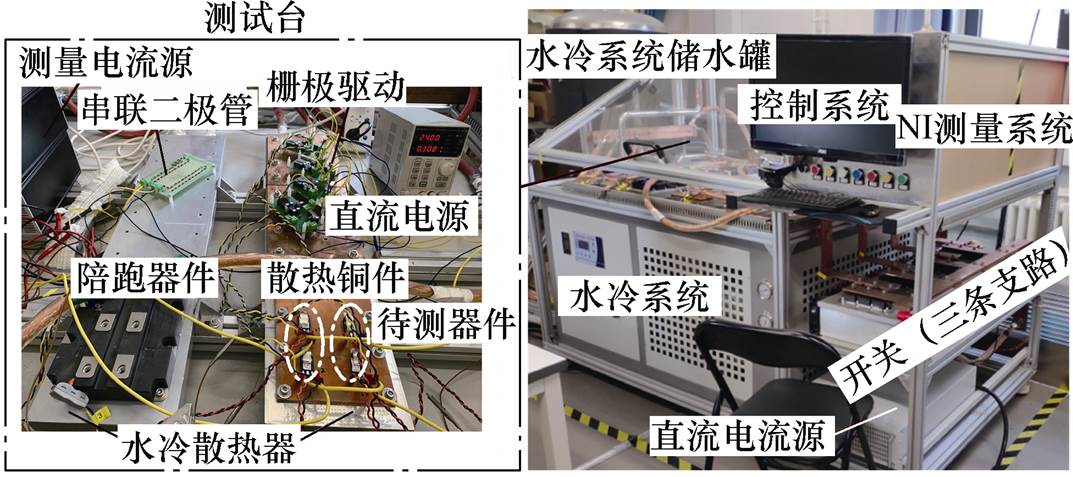

图6和图7是一条测试支路的电路原理,为了提高测试效率,同时也是避免负载电流源不断的启停而造成自身的老化,试验时设置了三条并联的测试支路[19]。三条支路交替工作,当负载电流对某一条支路上的器件进行加热时,其他两条支路的器件处于冷却阶段,因此待测器件的冷却时间是加热时间的两倍。试验装置实物如图8所示,主要包括电源系统、测量系统、水冷系统和控制系统,其中,测量系统可完成试验中电流、电压和温度的数据采集,而控制系统则基于Labview编程的上位机完成数据处理。

图8 试验装置实物

Fig.8 Experimental setup

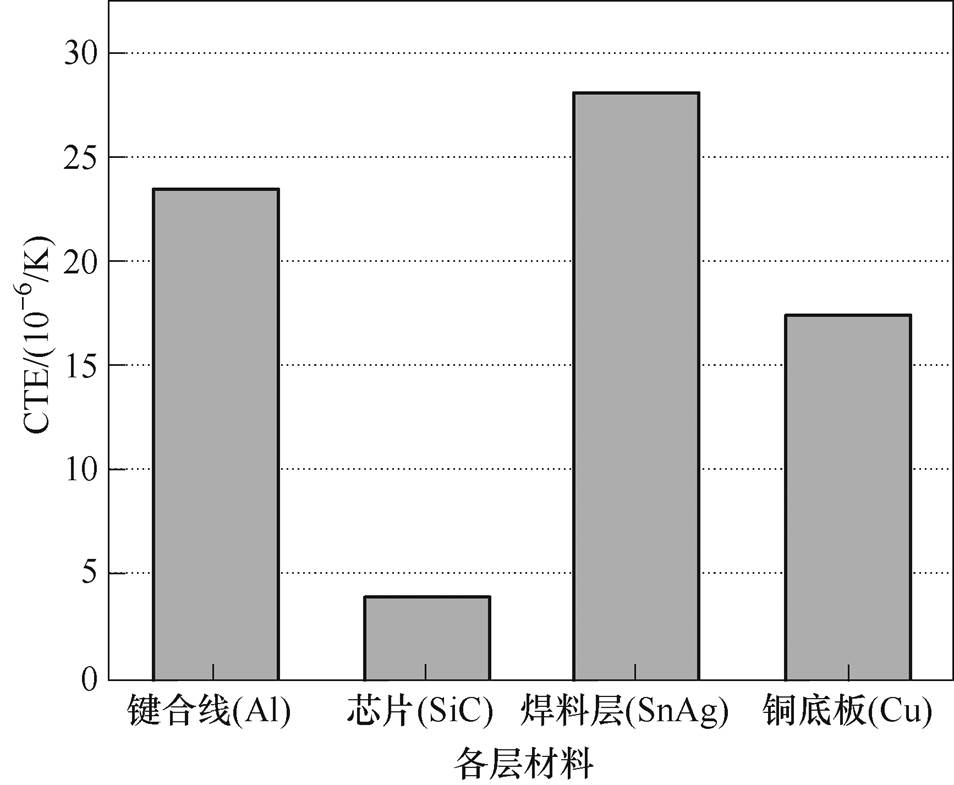

器件在功率循环过程中,由于材料膨胀系数(Coefficient of Thermal Expansion, CTE)不匹配在材料之间产生热应力,进而导致材料疲劳和老化。SiC MOSFET器件内部垂直结构如图2所示,自上而下分别是键合线、芯片、焊料层和铜底板,每层结构的材料及其CTE如图9所示。可以看出,键合线和芯片、芯片和焊料层之间的CTE不匹配最为严重,因此,键合线和焊料层成为最容易发生失效的部分。

图9 SiC MOSFET中各层材料的CTE

Fig.9 CTE of each layer in SiC MOSFET

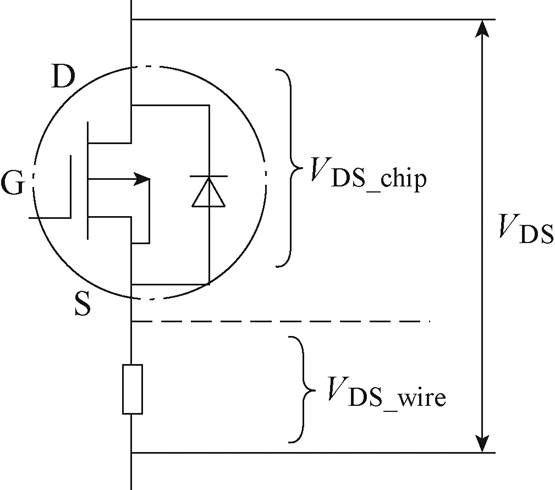

键合线是器件电流传导路径中最关键的一环,其老化会引起整体通态压降的增加,因此可以通过实时监测SiC MOSFET在最低结温处的通态压降VDS作为键合线的失效表征。器件测得通态压降由两部分组成,如图10所示,其中,VDS_chip是芯片上的通态压降,VDS_wire是键合线上的通态压降。

图10 测得通态压降的组成

Fig.10 The composition of the on-state voltage drop

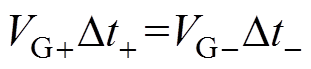

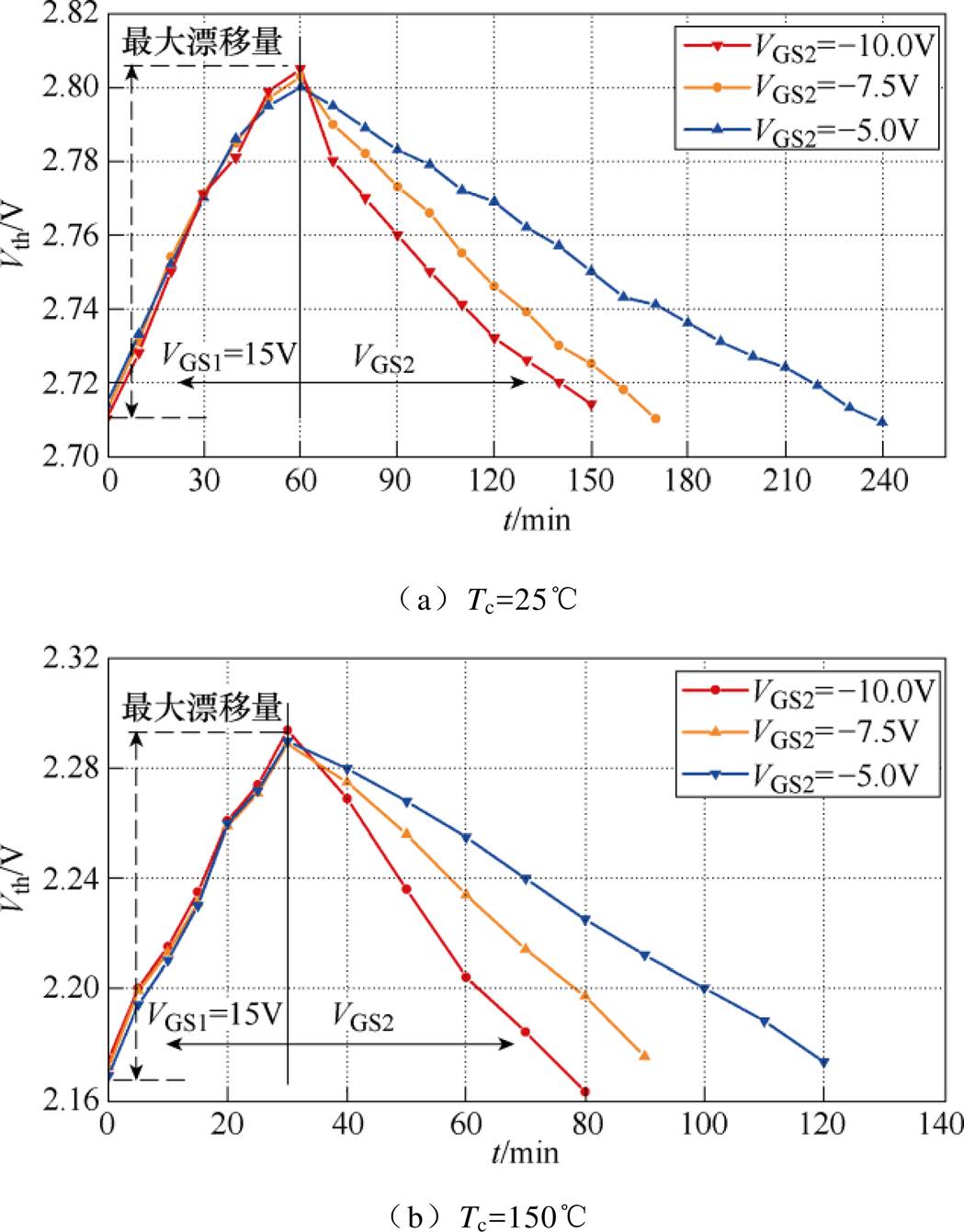

由于SiC MOSFET阈值电压的漂移效应,导致相同电流和相同温度下芯片的通态压降也会发生漂移,无法判断VDS的增加到底是由于阈值电压漂移造成的还是键合线老化造成的。为此,研究待测SiC MOSFET阈值电压漂移的影响因素和变化规律。对其在25℃室温和150℃高温下进行栅偏试验,每间隔一段时间(25℃时为10min,150℃时为5min)后,转而在对应温度下迅速测量其阈值电压,试验电路原理如图11所示。在两种不同温度下,对同一个器件重复进行三组不同栅压组合试验,每组试验中正向偏压均为15V且持续时间相同,反向偏压依次为5V、7.5V和10V,每组反向偏压持续到使得阈值电压与初始值接近(偏差在0.01V以内),然后马上进行下一组组合试验,最后测得阈值电压结果如图12所示。可以看出,第三代SiC芯片在栅极氧化层的制造工艺方面已经得到了极大提升,在VGS= 15V, Tc=25℃的条件下60min,阈值电压漂移量(某时刻测量值-初始测量值)在0.1V以内,而在VGS= 15V, Tc=150℃的条件下30min,阈值电压漂移也仅约为0.12V,如此小的阈值电压漂移对芯片通态压降的影响并不显著。另外,SiC MOSFET的阈值电压在正向偏压下发生正向漂移,而在反向偏压下发生反向漂移,并且几乎随时间呈线性变化。最重要的是,线性变化率和施加的偏压成正比,即阈值电压随时间的漂移量与栅极偏压的大小成正比,在室温和高温下均表现出类似的规律。此结果和文献[20]中的研究结果相似,表明阈值电压漂移和栅极电压

应力的极性、强度和持续时间有关。因此,为了将阈值电压漂移最小化,基于试验结果,提出一种判断准则为

(1)

(1)式中, 、

、 分别为正向和反向栅极电压大小;

分别为正向和反向栅极电压大小; 、

、 分别为正向偏压和反向偏压持续时间。

分别为正向偏压和反向偏压持续时间。

图11 阈值电压受栅极偏压影响的实验原理

Fig.11 Circuit diagram of threshold voltage affected by gate bias test

图12 不同栅极偏压组合下的阈值电压随时间变化

Fig.12 Threshold voltage changes with time under different gate bias combinations

当栅极电压的大小和持续时间满足式(1)时,SiC MOSFET的阈值电压漂移能够最小化,从而减小对功率循环试验结果的影响。在正向MOSFET模式下的功率循环试验中,冷却时间是加热时间的两倍,即反向栅压持续时间是正向栅压的两倍,因此试验中反向栅压选择-7.5V,既能够使得沟道区被彻底关断,又能使得阈值电压漂移最小化。虽然栅偏试验和功率循环试验条件不尽相同,在功率循环试验中温度是变化的而不是恒定的,但是由于该准则在常温和高温下均成立,温度只是影响漂移速度,并且在功率循环试验中,升温和降温过程中温度变化规律几乎是相同的[21]。因此,可以认为该准则在功率循环试验中是适用的。

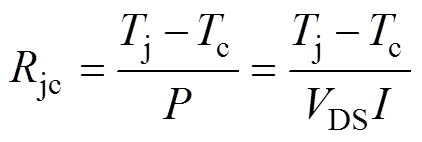

焊料层是器件传热路径中非常关键的一环,其老化将会引起整体热阻的增加,因此可以实时监测SiC MOSFET的结到壳热阻Rjc作为焊料层的失效表征。结到壳热阻Rjc的计算公式为

(2)

(2)式中,Tj为通过VSD(T)法测得的虚拟结温;Tc为壳温,由热电偶测得;P为功率损耗;VDS为最高温度处的通态压降;I为负载电流。

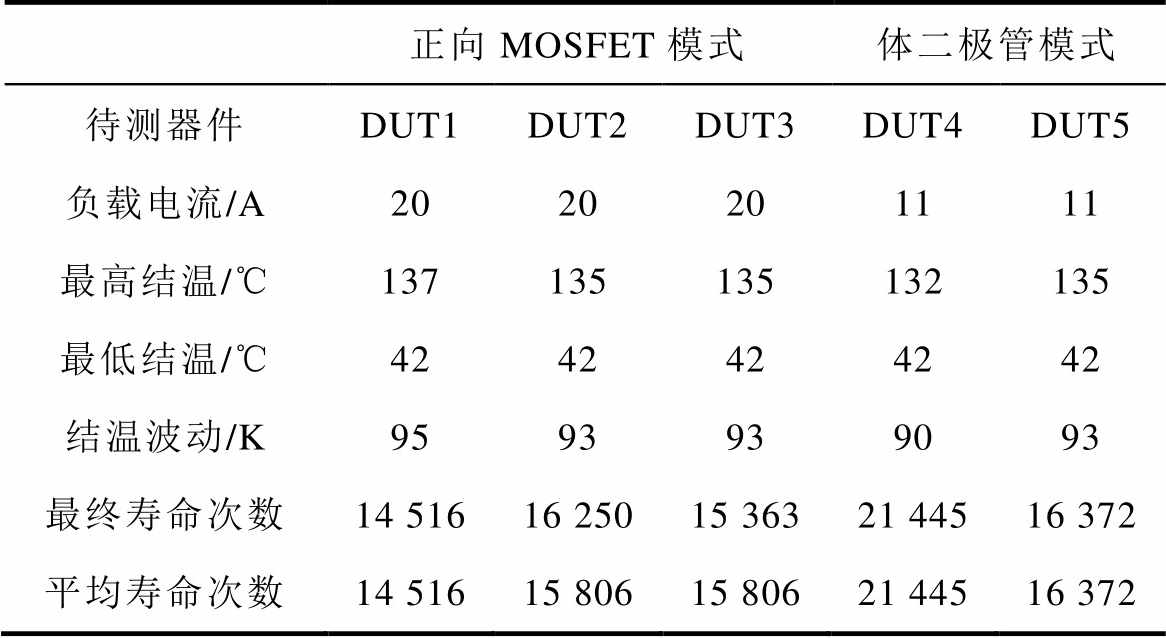

现有标准中对于器件失效的定义是通态压降增加5%或热阻增加20%,或者是器件失去既有功能。

影响功率循环能力最重要的因素是结温和结温波动[22],试验考核器件在不同导通模式下的功率循环能力需要在相同热力条件下进行,即尽量保证各待测器件的结温波动和最高结温相同。试验预设结温波动95K,最高结温为135℃,该试验条件可在安全结温范围内加速器件老化进程,有效缩短试验时间。实际测试中由于器件之间安装的差异性,导致热阻不同,使得个别待测器件的实际结温波动和最高结温距离预设值可能存在一定的偏差。设置三条测试支路,器件加热时间均为2s,冷却时间为4s。由于不同导通模式下的I-V特性不同,相同电流下的通态压降相差太大,如图3所示,因此不同模式下的负载电流不同。正向MOSFET模式下负载电流为20A,待测器件样本数量为3个,体二极管模式下负载电流为11A,待测器件样本数量为3个,其中1个器件在试验过程中由于人为失误造成损坏,因此有效样本数为2个。当试验条件确定之后,就会作为固定条件,在整个功率循环试验过程中不再改变。值得注意的是,延迟时间内结温会有所下降,根据文献[23]的仿真结果,当延迟时间为500μs时,结温变化量与功率密度成正比,约为1.1K每1W/mm2。本试验中,器件在两种模式下需要达到相同的结温和结温波动,因此功率损耗是相近的,即延迟时间内温度变化量也是近似相同的,对于本文的研究内容和结论不会产生影响。本试验过程中在线监测结温、通态压降和热阻等关键参数的变化规律。最终当通态压降或热阻出现急剧上升时,意味着器件因老化彻底失效,试验停止。

由于试验中待测器件较多,且通过试验数据分析发现,每种模式下不同器件的退化规律大致相同,因此在本节试验结果分析中,每种模式下仅展示一个器件的试验结果。

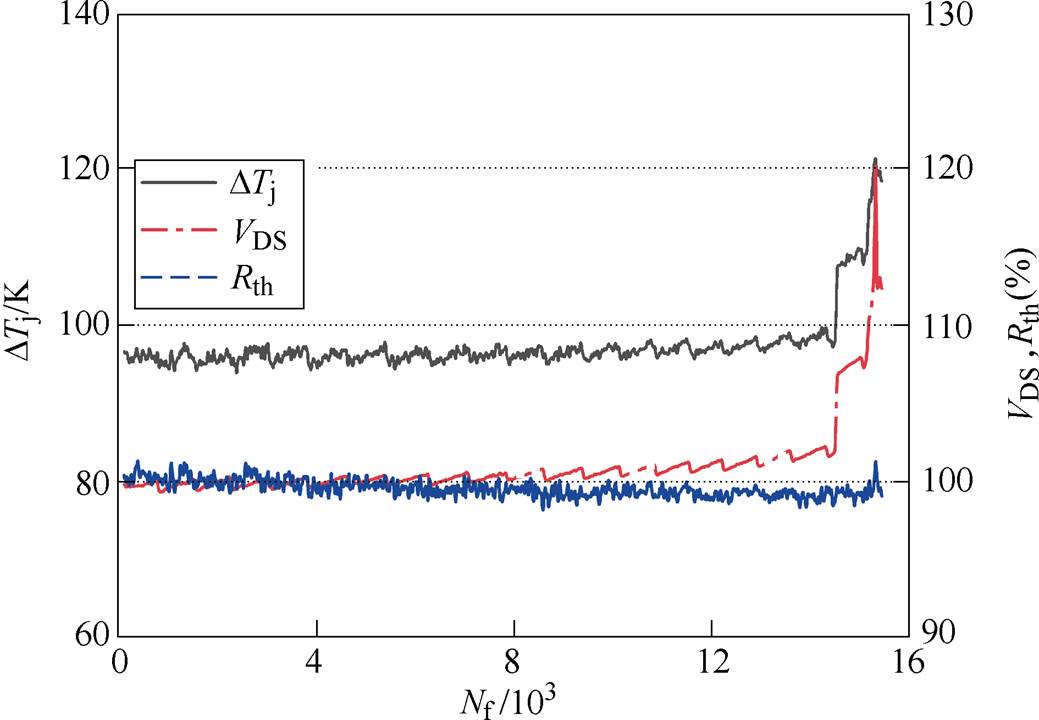

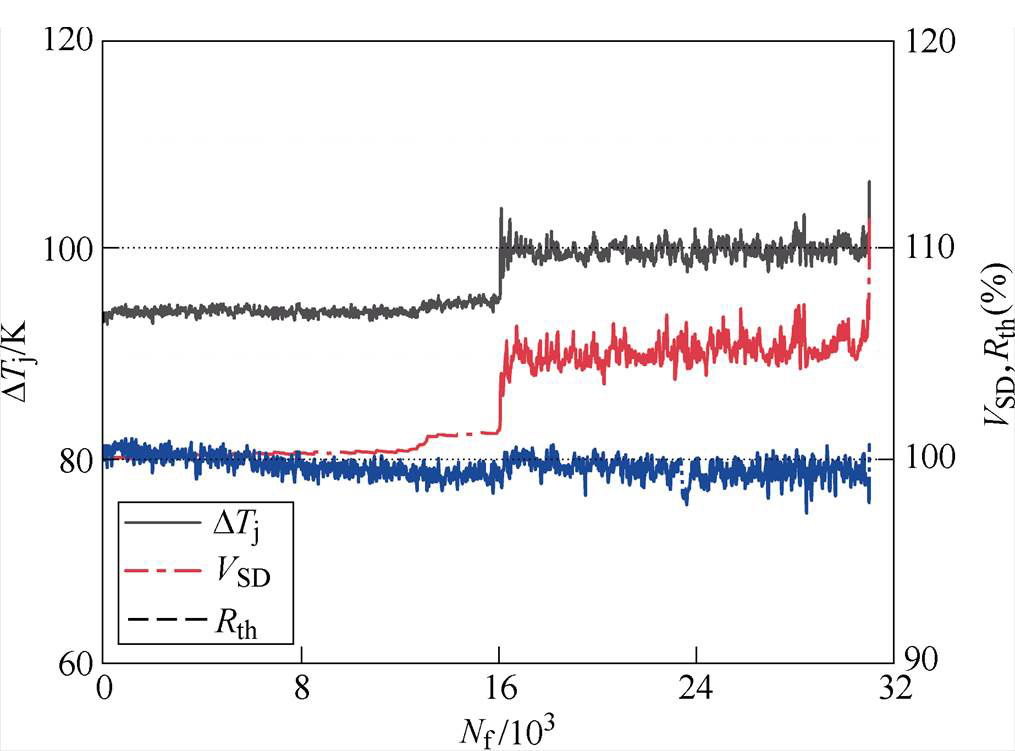

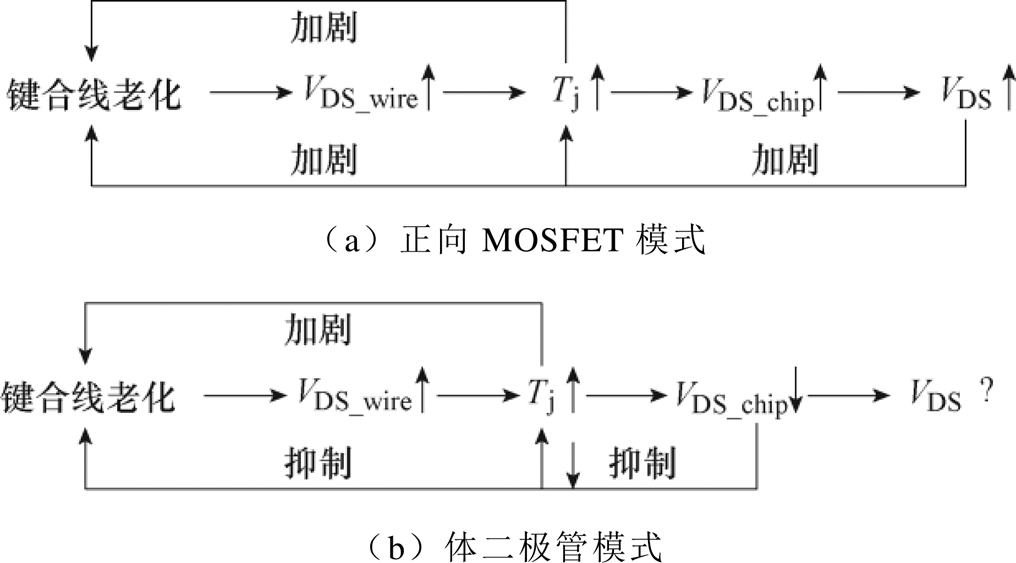

SiC MOSFET器件在正向MOSFET和体二极管模式下各参数在功率循环试验过程中的变化如图13和图14所示,其中,通态压降(VDS、VSD)和热阻(Rth)均已相对初始值进行了归一化。从两图中可以看出,热阻在功率循环试验过程中整体较为稳定,说明焊料层没有老化,只是试验初期存在一定的缓慢下降,这是由于试验时,在器件和散热铜板之间添加了一层导热硅胶片用于绝缘,在功率循环试验中,器件、导热硅胶片和散热铜板之间的接触在变好,使得它们之间的接触热阻在减小。两种模式下的失效均表现为通态压降的上升,通态压降的上升引起结温的升高,从两图中也可以看出,结温和通态压降的变化趋势几乎吻合,可以判断是键合线老化导致。虽然通态压降还和温度相关,但最低结温一般不随器件老化而升高,在整个功率循环过程中几乎保持恒定,此通态压降在每个循环周期中结温最低时测得,因此通态压降值仅受键合线健康状态的影响[19],当键合线发生老化,通态压降会增加;反之亦然。在正向MOSFET模式下,通态压降在前期缓慢线性增长,在试验后期开始指数增长;而在体二极管模式下,通态压降在16 000次循环左右阶跃上升后,存在一个较为稳定的阶段,但是这个阶段内通态压降开始出现波动,然后在试验后期急剧升高。究其原因,与两种模式下通态压降的温度特性有关,导致了键合线老化后引起的电热反馈机制不同,如图15所示。正向MOSFET模式下,通态压降具有正温度特性,当键合线老化引起通态压降上升时,导致结温升高,结温升高又会造成通态压降增加,进而功率损耗增加,导致结温进一步升高,键合线承受的热应力增大,如此正反馈的过程导致了试验后期通态压降呈指数上升,这也是标准认为当通态压降超过5%即可认为失效的根本原因,因为在指数上升的变化规律中,通态压降升高5%时对应的寿命和键合线完全脱落导致通态压降急剧上升时对应的寿命相差甚微。体二极管模式下,通态压降具有负温度特性,在负温度特性下,通态压降和结温是负反馈调节,即当键合线老化造成通态压降上升,进而导致结温的升高,而结温升高会造成芯片通态压降下降,从而抑制结温的升高,这对于器件键合线老化起到一定的补偿作用。从图13和图14中可以看出,当试验停止时,正向MOSFET模式下通态压降上升约20%,结温波动增加了约20K;而在体二极管模式下通态压降上升约10%,结温波动只增加了8K,充分说明了不同反馈机制对老化规律的影响不同。另外,从图14中还可以看出,试验在12 000次循环左右,通态压降VSD有微小的上升,但是结温波动却保持不变,这就是得益于负温度特性的结果。

图13 正向MOSFET模式下各参数在功率循环试验中的变化趋势

Fig.13 Evolution of parameters during power cycling test in forward MOSFET mode

图14 体二极管模式下各参数在功率循环试验中的变化趋势

Fig.14 Evolution of parameters during power cycling test in body diode mode

图15 两种模式下键合线老化后的电热反馈机制

Fig.15 Electrothermal feedback mechanism after bond wire aging under two modes

本次试验中所有待测SiC MOSFET器件在两种模式下最终的稳定的试验条件和功率循环寿命见表1,其中最终寿命根据标准定义为通态压降超过初始值5%时对应的循环数[11]。最高结温和最低结温以及结温波动以稳定后的数值为准。从表1可以看出,当最高结温为135℃,结温波动为93K时,正向MOSFET模式下的平均寿命为15 806次,体二极管模式平均寿命为16 372次,两者非常接近。实际上,体二极管模式下当通态压降超过初始值5%,即达到失效标准后,并没有出现急剧升高的现象,而是在很长一段时间内保持稳定,这同样属于有效寿命。如果考虑这部分的循环寿命,体二极管模式下的寿命平均可以达到31 170次,大约是正向MOSFET模式下的两倍。体二极管模式下的寿命偏高,一方面是体二极管模式下的负载电流较小;另一方面则是因为通态压降的负温度特性对老化起到较强的补偿作用。

表1 待测器件的测试条件及寿命

Tab.1 Test conditions and lifetime of the DUT

正向MOSFET模式体二极管模式 待测器件DUT1DUT2DUT3DUT4DUT5 负载电流/A2020201111 最高结温/℃137135135132135 最低结温/℃4242424242 结温波动/K9593939093 最终寿命次数14 51616 25015 36321 44516 372 平均寿命次数14 51615 80615 80621 44516 372

本文对SiC MOSFET在正向MOSFET模式和体二极管模式下进行功率循环试验,对比分析不同试验方法对器件的老化规律、失效机理及寿命的影响,从实验结果中可以得到如下结论:

1)小电流下体二极管压降可以作为温敏电参数用于SiC MOSFET的结温测量,应用该方法时栅极需要加一定的负压使沟道区被彻底关断。

2)阈值电压漂移几乎与栅极电压的大小和持续时间成正比,当正向偏压的大小和持续时间的乘积与反向偏压的大小和持续时间的乘积相同时,可以使得阈值电压漂移最小化,隔离其对键合线失效表征参数通态压降的影响。

3)正向MOSFET模式下通态压降具有正温度特性,当键合线出现老化之后,电热正反馈机制会加速老化过程,而二极管模式下通态压降具有负温度特性,由此产生的负反馈机制能够抑制老化进程,对老化起到一定的补偿作用。

4)对于具有电热负反馈机制的二极管模式,传统标准中通态压降超过初始值5%即定义为失效,会低估器件的功率循环寿命,当考虑有效循环寿命,在相同热力条件下,二极管模式下的寿命约为正向MOSFET模式下的两倍。

参考文献

[1] 柯俊吉, 赵志斌, 谢宗奎, 等. 考虑寄生参数影响的碳化硅MOSFET开关暂态分析模型[J]. 电工技术学报, 2018, 33(8): 1762-1774.

Ke Junji, Zhao Zhibin, Xie Zongkui, et al. Analytical switching transient model for silicon carbide MOSFET under the influence of parasitic para- meters[J]. Transactions of China Electrotechnical Society, 2018, 33(8): 1762-1774.

[2] 王莉娜, 邓洁, 杨军一, 等. Si和SiC功率器件结温提取技术现状及展望[J]. 电工技术学报, 2019, 34(4): 703-716.

Wang Lina, Deng Jie, Yang Junyi, et al. Junction temperature extraction methods for Si and SiC power devices-a review and possible alternatives[J]. Transactions of China Electrotechnical Society, 2019, 34(4): 703-716.

[3] 周林, 李寒江, 解宝, 等. SiC MOSFET的Saber建模及其在光伏并网逆变器中的应用和分析[J]. 电工技术学报, 2019, 34(20): 4251-4263.

Zhou Lin, Li Hanjiang, Xie Bao, et al. Saber modeling of SiC MOSFET and its application and analysis in photovoltaic grid-connected inverter[J]. Transactions of China Electrotechnical Society, 2019, 34(20): 4251-4263.

[4] Sheng Kuang. Maximum junction temperatures of SiC power devices[J]. IEEE Transactions on Elec- tronic Devices, 2009, 56(2): 337-342.

[5] Qi Feng, Wang Miao, Xu Longya. Investigation and review of challenges in a high temperature 30kVA 3-phase inverter using SiC MOSFETs[J]. IEEE Transactions on Industry Applications, 2018, 54(3): 2483-2491.

[6] Herold C, Schaefer M, Sauerland F, et al. Power cycling capability of modules with SiC-diodes[C]// International Conference on Integrated Power Systems, Nuremberg, Germany, 2014.

[7] Hu Borong, Gonzalez J O, Li Ran, et al. Failure and reliability analysis of a SiC power module based on stress comparison to a Si device[J]. IEEE Transa- ctions on Device and Materials Reliability, 2017, 17(4): 727-737.

[8] 张经纬, 邓二平, 赵志斌, 等. 压接型IGBT器件单芯片子模组疲劳失效的仿真[J]. 电工技术学报, 2018, 33(18): 4277-4285.

Zhang Jingwei, Deng Erping, Zhao Zhibin, et al. Simulation on fatigue failure of single IGBT chip module of press-pack IGBTs[J]. Transactions of China Electrotechnical Society, 2018, 33(18): 4277- 4285.

[9] Herold C, Sun Jian, Seidel P, et al. Power cycling methods for SiC MOSFETs[C]//29th International Symposium on Power Semiconductor Devices and IC's (ISPSD), Sapporo, Japan, 2017: 367-370.

[10] Schwabe C, Seidel P, Lutz J. Power cycling capability of silicon low-voltage MOSFETs under different operation conditions[C]//31th International Symposium on Power Semiconductor Devices and IC's (ISPSD), Shanghai, China, 2019.

[11] European Center for Power Electronics. AQG 324 qualification of power modules for use in power electronics converter units (PCUs) in motor vehicles[S]. Nuremberg, Germany: ECPE Working Group, 2018.

[12] 周郁明, 蒋保国, 刘航志, 等. 包含SiC/SiO2界面电荷的SiC MOSFET的SPICE模型[J]. 中国电机工程学报, 2019, 39(19): 5604-5612.

Zhou Yuming, Jiang Baoguo, Liu Hangzhi, et al. SPICE model of SiC MOSFET including the trapped charge at SiC/SiO2 interface[J]. Proceedings of the CSEE, 2019, 39(19): 5604-5612.

[13] 李辉, 黄樟坚, 廖兴林, 等. 一种抑制SiC MOSFET桥臂串扰的改进门极驱动设计[J]. 电工技术学报, 2019, 34(2): 275-285.

Li Hui, Huang Zhangjian, Liao Xinglin, et al. An improved SiC MOSFET gate driver design for crosstalk suppression in a phase-leg configuration[J]. Transactions of China Electrotechnical Society, 2019, 34(2): 275-285.

[14] Luo Haoze, Baker N, Iannuzzo F, et al. Die degradation effect on aging rate in accelerated cycling tests of SiC power MOSFET modules[J]. Microelectronics Reliability, 2017, 76-77: 415-419.

[15] Herold C, Franke J, Bhojani R, et al. Requirements in power cycling for precise lifetime estimation[J]. Microelectronics Reliability, 2016, 58: 82-89.

[16] Zeng Guang, Cao Haiyang, Chen Weinan, et al. Difference in device temperature determination using pn-junction forward voltage and gate threshold voltage[J]. IEEE Transactions on Power Electronics, 2019, 34(3): 2781-2793.

[17] Schmidt R, Werner R, Casady J, et al. Power cycle testing of sintered SiC-MOSFETs[C]//Power Conver- sion and Intelligent Motion (PCIM) Europe, Nuremberg, Germany, 2017: 694-701.

[18] Herold C, Franke J, Bhojani R, et al. Methods for virtual junction temperature measurement respecting internal semiconductor processes[C]//27th Inter- national Symposium on Power Semiconductor Devices & IC's (ISPSD), Hong Kong, China, 2015: 325-328.

[19] 邓二平, 陈杰, 赵雨山, 等. 90kW/3000A高压大功率IGBT器件功率循环测试装备研制[J]. 半导体技术, 2019, 44(3):70-78.

Deng Erping, Chen Jie, Zhao Yushan, et al. 90kW/ 3000A power cycling equipment for high voltage and high power IGBT modules[J]. Semiconductor Tech- nology, 2019, 44(3): 70-78.

[20] Lelis A J, Green R, Habersat D B, et al. Basic mechanisms of threshold-voltage instability and implications for reliability testing of SiC MOSFETs[J]. IEEE Transactions on Electron Devices, 2015, 62(2): 316-323.

[21] Blackburn D L, Oettinger F F. Transient thermal response measurements of power transistors[J]. IEEE Transactions on Industrial Electronics and Control Instrumentation, 1975, 22(2): 134-141.

[22] 黄涛, 陈民铀, 赖伟, 等. 计及疲劳累积及健康状态的风电变流器可靠性评估模型[J]. 电工技术学报, 2018, 33(20): 4845-4854.

Huang Tao, Chen Minyou, Lai Wei, et al. Reliability evaluation model of wind power converter con- sidering fatigue accumulation and health status[J]. Transactions of China Electrotechnical Society, 2018, 33(20): 4845-4854.

[23] Zeng Guang, Borucki L, Wenzel O, et al. First results of development of a lifetime model for transfer molded discrete power devices[C]//Power Conversion and Intelligent Motion (PCIM) Europe 2018, Nuremberg, Germany, 2018: 706-713.

Failure Mechanism Analysis of SiC MOSFET under Different Aging Test Methods

Abstract SiC MOSFETs are gradually entering the market due to their excellent electrothermal characteristics, and their long-term reliability has become the focus of attention. The power cycling test is the most important aging test for device reliability assessment. MOSFET has three conduction modes corresponding to three different power cycling test methods. To study and compare the failure mechanism and failure parameters evolution of SiC MOSFET under different aging test methods, the power cycling tests were carried out under different modes, focusing on forward MOSFET mode and body diode mode. Since the interface trap in the SiC MOSFET can cause the threshold voltage drift, a judgment criterion and a corresponding power cycling test method were proposed to minimize the influence of the threshold voltage drift on the test result. The on-line measurement of junction temperature, on-state voltage drop and thermal resistance during the test were achieved. The results show that the main failure mode in both modes is bond wire fatigue, but the electrothermal feedback mechanism after bonding wire fatigue is different, resulting in different degradation laws and lifespan. The life in diode mode is about twice that in the forward MOSFET mode under the same thermal conditions.

keywords:SiC MOSFET, power cycling test, conduction mode, threshold voltage drift, junction temperature measurement, failure mechanism

DOI: 10.19595/j.cnki.1000-6753.tces.191409

中图分类号:TM46

陈 杰 男,1994年生,博士研究生,研究方向为功率半导体器件结温准确测量及可靠性评估。E-mail: huadianchenjie@163.com

邓二平 男,1989年生,博士,讲师,研究方向为高压大功率IGBT器件封装及可靠性,包括失效机理、测试技术和方法。E-mail: dengerpinghit@163.com(通信作者)

收稿日期2019-10-28

改稿日期 2020-05-26

国家自然科学基金资助项目(52007061)。

(编辑 崔文静)