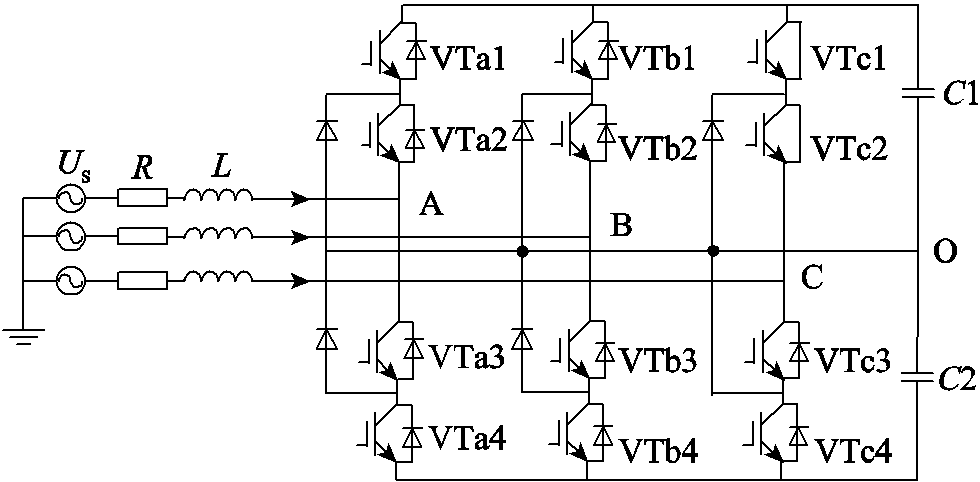

图1 三电平NPC整流器拓扑结构

Fig.1 Three-level NPC rectifier topology diagram

摘要 大功率三电平中点钳位(NPC)整流器在满足网侧谐波电流限值、直流侧中点电压平衡和避免相电压两电平跳变(TLJ)的前提下,要尽可能降低开关频率。基于以上功能需求,首先分析了空间矢量脉冲宽度调制(SVPWM)和不连续脉冲宽度调制(DPWM)的基本原理,介绍了传统的四种SVPWM开关序列和八种DPWM开关序列并对比了各自作用下的相电压波形。针对传统SVPWM相电压存在的TLJ和开关频率较高缺陷,提出两种改进型SVPWM开关序列;针对传统DPWM相电压存在的TLJ,提出两种改进型DPWM开关序列。在此基础上,该文从TLJ、开关频率、中点电压自平衡能力、谐波总畸变率(THD)和各次谐波电流含量等方面对SVPWM和DPWM的性能进行了详细分析,总结了适用于大功率三电平NPC整流器的三种SVPWM开关序列。最后搭建三电平NPC变流器样机,通过实验验证了所提出改进型开关序列的有效性。

关键词:三电平中点钳位整流器 空间矢量调制 不连续调制 两电平跳变 降低开关频率

在轨道牵引、光伏并网、电网无功补偿等领域,三电平中点钳位(Neutral Point Clamped, NPC)拓扑因其结构简单、器件电压应力低,输出电压和电流质量高的优点得到了广泛应用[1-3]。

当采用背靠背三电平NPC拓扑实现能量双向流动时,直流侧中点电压的平衡一般依靠整流侧控制[4]。另外,整流侧直接连接电网,其网侧各次谐波电流含量也必须严格限定在电网标准内,而公用电网谐波指标对偶次谐波电流的限定更为严格[5]。除此之外,大功率三电平NPC整流器要严格避免相电压两电平跳变(Two-Level Jump, TLJ),而且为减少开关损耗,大功率三电平NPC整流器还需降低各功率器件的开关频率[6-7]。因此,在满足网侧谐波电流限值、保持直流侧中点电压平衡和避免TLJ的前提下尽量降低开关频率,是选取大功率三电平NPC整流器调制策略的重要考虑点。

针对三电平NPC拓扑,常用的脉宽调制(Pulse Width Modulation, PWM)方法有四种:载波脉冲宽度调制(Carrier-Based PWM, CBPWM)、空间矢量脉宽调制(Space Vector PWM, SVPWM)、不连续脉宽调制(Discontinuous PWM, DPWM)和特定谐波消除脉宽调制(Specific Harmonic Elimination PWM, SHEPWM)。其中,SHEPWM在相同开关频率下,谐波性能最优,但其动态性能较差且难以对其施加中点平衡控制来维持直流侧中点电压的稳定;当向CBPWM的参考波信号中注入特定零序分量后,CBPWM和SVPWM、DPWM具有一致性[8-9],三者动态响应能力较强且均易实现中点电压平衡控制。但相比CBPWM,SVPWM和DPWM可以更加直观地通过设计各扇区内的矢量作用序列来得到偶次谐波含量更少的谐波分布性能和更低的开关频率。故针对大功率三电平NPC整流器,本文选取SVPWM和DPWM策略进行研究。

现有文献较少将SVPWM和DPWM与谐波分布、中点电压平衡、避免TLJ和降低开关频率同时结合在一起进行分析。针对SVPWM,文献[10]提出了在各扇区统一采用P型小矢量或N型小矢量首发的SVPWM开关序列,其可以在3的奇数倍载波比下消除偶次谐波、避免TLJ,并具备一定的中点电压自平衡能力,但其开关频率较高;文献[11]提出了在相邻60°区域分别采用P型小矢量和N型小矢量首发的SVPWM开关序列,其可以在3的偶数倍载波比下消除偶次谐波,但在非对称规则采样下可能出现TLJ;文献[12]在文献[11]的基础上提出了适合非对称规则采样的SVPWM开关序列,其可以消除偶次谐波并避免TLJ,缺点是增加了开关频率。

针对DPWM,文献[13-14]提出了四种满足半波对称和三相对称的DPWM开关序列,分别为DPWM 0/1/2/3。四种开关序列均可在降低三分之一开关频率的基础上消除偶次谐波,但DPWM 0/3可能出现TLJ;文献[15]另外提出了四种DPWM开关序列,分别为DPWM max/min/4/5,但DPWM max/min会导致中点电压不平衡,DPWM 4/5则存在TLJ;文献[16-17]分别以平均误差电流矢量幅值最小和开关损耗与磁链波动量有效值乘积最小为原则,通过选取最优开关序列,改善了DPWM作用下的输出电流质量,但均未考虑TLJ;文献[18]提出一种能够同时降低开关损耗和控制中点电压平衡的混合DPWM策略,但谐波分布中含有较多偶次谐波。

在满足网侧谐波电流限值、保持中点电压平衡和避免TLJ的基础上,为了降低开关频率,本文首先针对传统SVPWM开关序列存在的TLJ和开关频率较高的缺陷,提出了两种改进型SVPWM开关序列,并针对传统DPWM开关序列存在的TLJ,提出了两种改进型DPWM开关序列。在此基础上,本文从TLJ、开关频率、中点电压自平衡能力、总谐波畸变率(Total Harmonic Distortion, THD)和各次谐波电流含量等方面对六种SVPWM开关序列和十种DPWM开关序列进行了详细分析,总结了适用于大功率三电平NPC整流器的三种SVPWM开关序列。最后搭建了三电平NPC变流器样机,通过实验验证了所设计改进型开关序列的有效性。

三电平NPC整流器的拓扑结构如图1所示。通过控制每相由上到下四个功率器件VT1、VT2、VT3、VT4的通断,三电平NPC整流器可输出P、N、O三种不同的电平状态。其中,P电平对应VT1、VT2导通,VT3、VT4关断;N电平对应VT3、VT4导通,VT1、VT2关断;O电平对应VT2、VT3导通,VT1、VT4关断。三电平NPC整流器的电压空间矢量分布如图2所示。

图1 三电平NPC整流器拓扑结构

Fig.1 Three-level NPC rectifier topology diagram

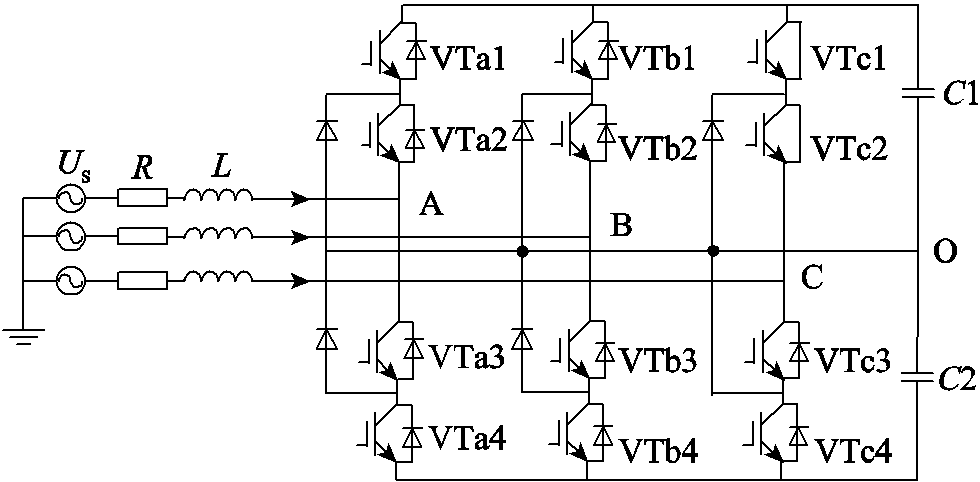

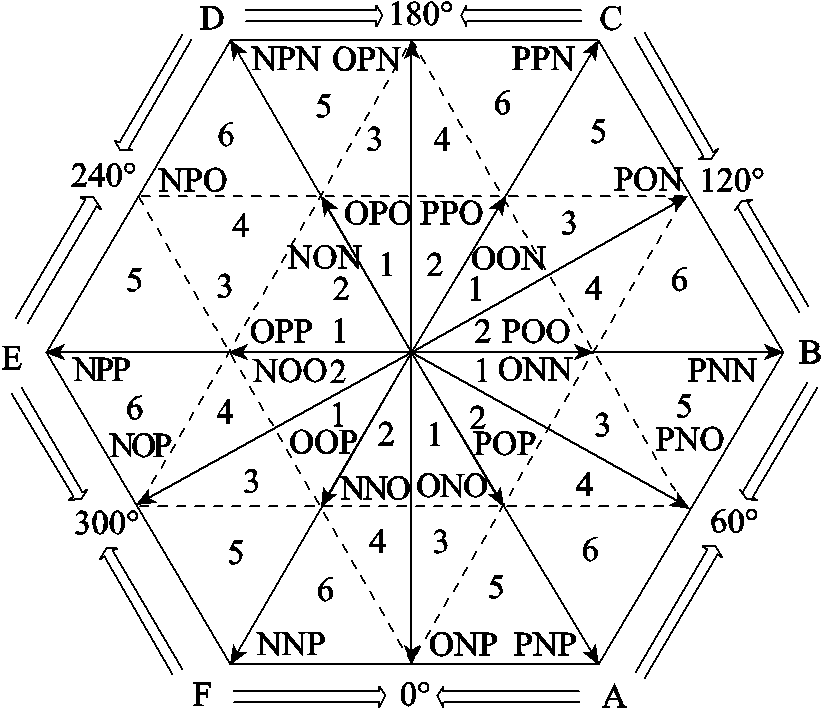

图2 三电平NPC整流器空间矢量图

Fig.2 Space vector diagram for three-level NPC rectifier

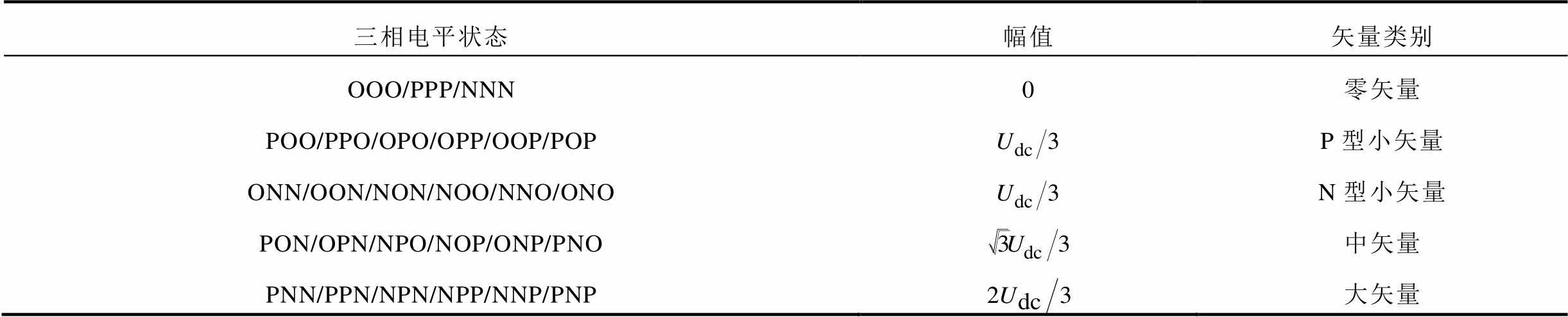

定义Udc为三电平NPC整流器直流侧电压,图2中各电压空间矢量见表1。其中幅值为Udc/3的同一位置处的冗余空间矢量可根据其三相电平状态分类为P型小矢量和N型小矢量。

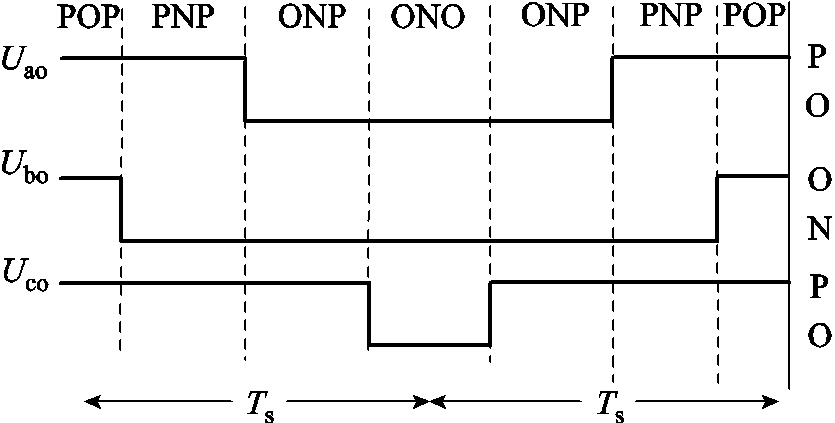

定义Vref为参考电压,传统SVPWM首先依据最近三矢量原则将Vref分解为三个空间矢量,然后利用伏秒等效原则求解各空间矢量的作用时间[19]。令Ts代表采样周期,当Vref位于图2区域A5时,SVPWM在连续两个Ts内的序列为POP↔PNP↔ ONP↔ONO↔ONP↔PNP↔POP,具体如图3所示。

表1 SVPWM各电压空间矢量幅值及对应的电平状态

Tab.1 The amplitude of each space vector of SVPWM and its corresponding level state

三相电平状态幅值矢量类别 OOO/PPP/NNN0零矢量 POO/PPO/OPO/OPP/OOP/POPP型小矢量 ONN/OON/NON/NOO/NNO/ONON型小矢量 PON/OPN/NPO/NOP/ONP/PNO中矢量 PNN/PPN/NPN/NPP/NNP/PNP大矢量

图3 SVPWM作用下的开关序列

Fig.3 Switching sequences under SVPWM

分析图3,由于SVPWM在一个Ts内同时使用了同一位置处的两个冗余小矢量,故SVPWM在每个Ts内存在四个空间矢量,对应开关序列为七段式。

DPWM是一种在每个Ts内总有一相功率器件不动作的调制策略[15]。通过在每个Ts内只使用特定的冗余矢量,DPWM可将相电压的电平状态钳位到特定电平,从而与SVPWM相比降低了开关频率。

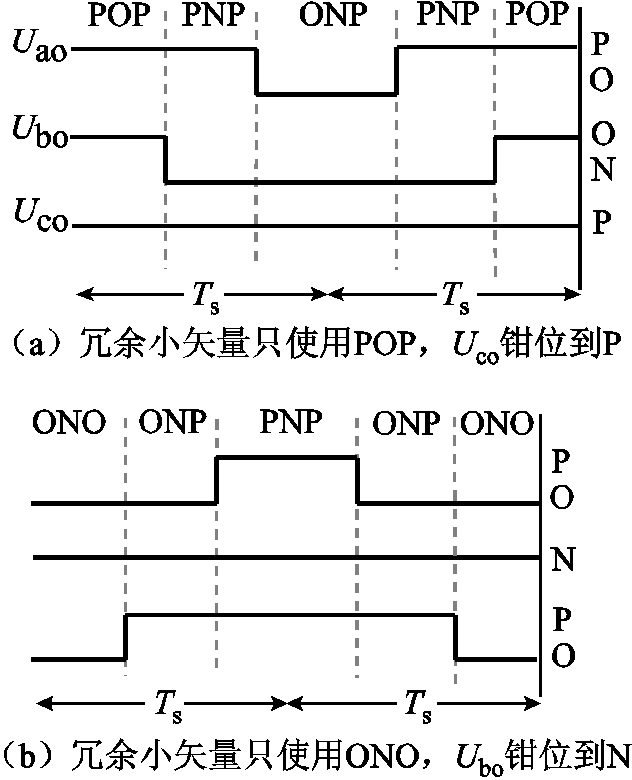

当Vref位于区域A5时,DPWM作用下的开关序列如图4所示。其中,只使用P型小矢量的DPWM开关序列为POP↔PNP↔ONP↔PNP↔POP,其可将C相电压钳位到P;只使用N型小矢量的DPWM开关序列为ONO↔ONP↔PNP↔ONP↔ONO,其可将B相电压钳位到N。DPWM在每个Ts内只存在三个空间矢量,对应开关序列为五段式。

图4 DPWM作用下的开关序列

Fig.4 Switching sequences under DPWM

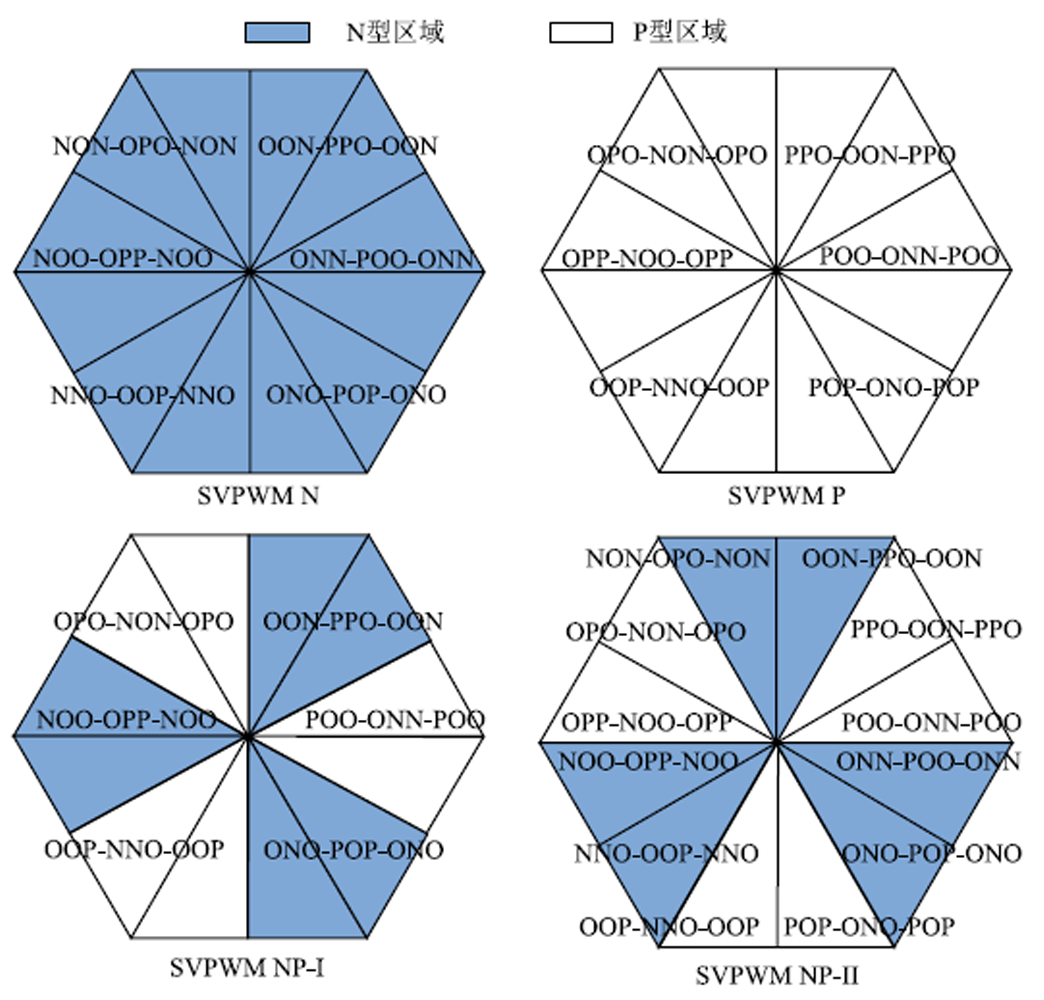

文献[10-12]根据每个60°扇区内首发小矢量类别的不同,提出了如图5所示四种不同的SVPWM开关序列,分别定义为SVPWM N、SVPWM P、SVPWM NP-I和SVPWM NP-II。

图5 SVPWM的四种传统开关序列

Fig.5 Four traditional switching sequences of SVPWM

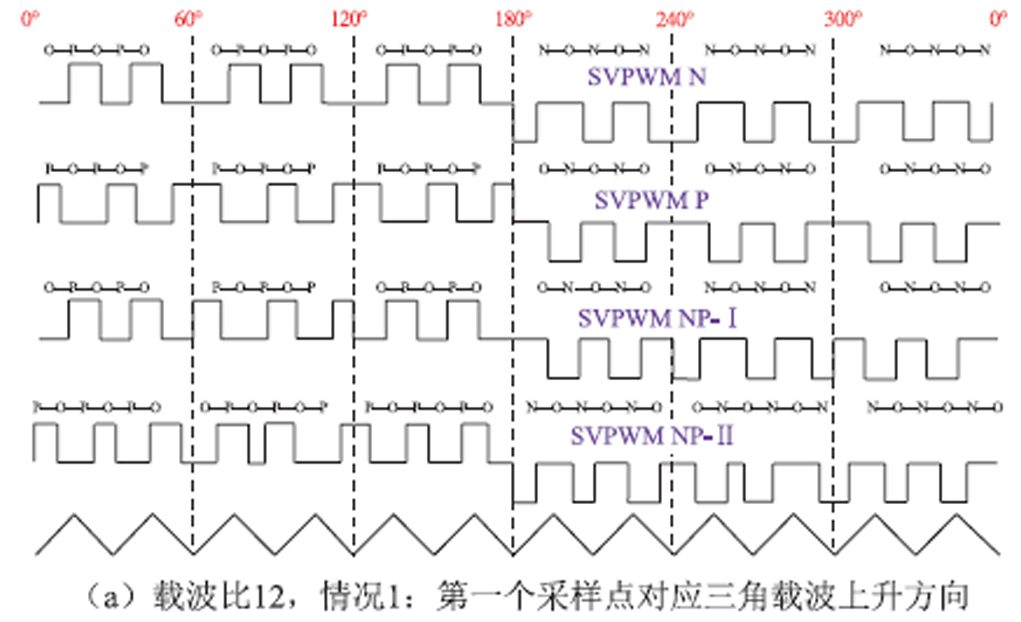

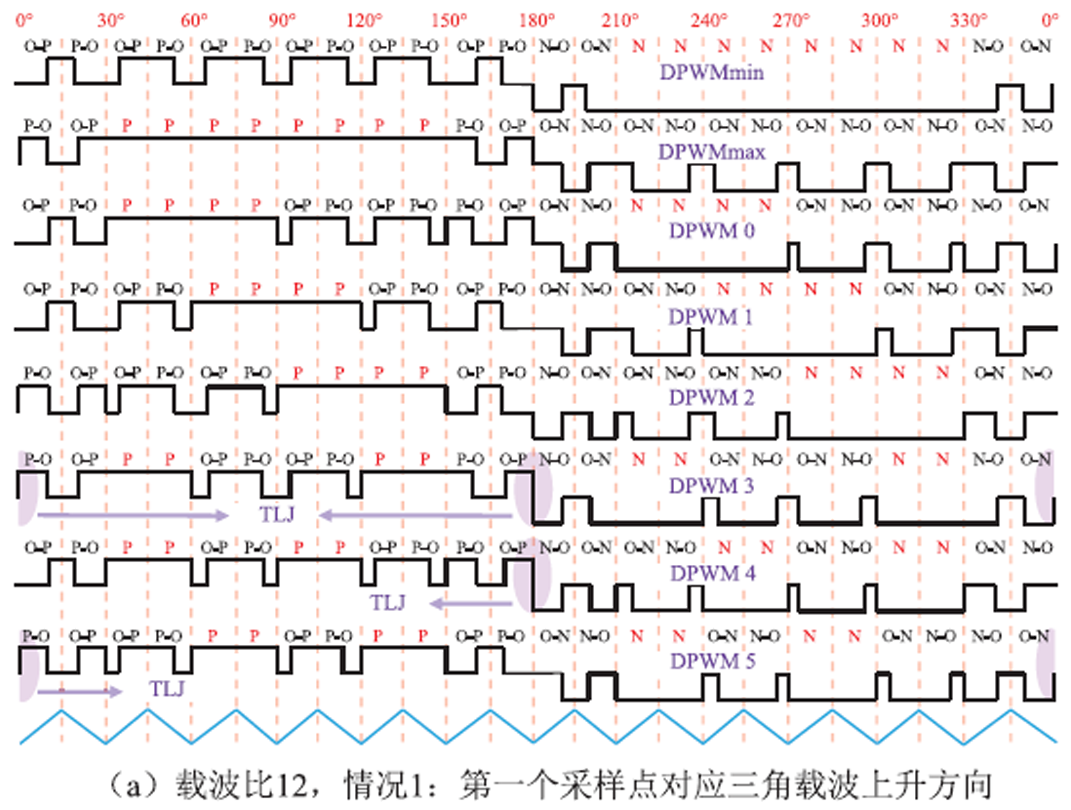

对于SVPWM,为保证大功率三电平NPC整流器各功率器件最高开关频率不超过500Hz[6],调制的载波比一般设置为12或15。同时为了提高采样精度,采用非对称规则采样方式。以A相为例,假定Vref位于图2区域5或区域6,在以上载波比和采样方式下,四种SVPWM作用下的相电压波形总结于图6。

图6 四种SVPWM开关序列对应的相电压

Fig.6 Phase voltage corresponding to four SVPWM switching sequences

图6中,第一个采样点对应三角载波上升方向,代表Vref进入P/N型区域后,第一个采样点处调用的开关序列为P/N型小矢量首发的开关序列;对应三角载波下降方向则代表Vref进入P/N型区域后,第一个采样点处调用的开关序列为N/P型小矢量首发的开关序列。定义载波频率和基波频率分别为fc和fb,对比图6,可得出以下结论:

1)SVPWM N和SVPWM P在载波比为15时可使相电压波形满足半波对称,从而可消除偶次谐波,且在其作用下相电压不会出现TLJ。但两者对应的开关频率较高,为(fc+fb)/2=8fb。

2)SVPWM NP-Ⅱ在载波比为12时可使相电压满足半波对称且不会出现TLJ,但其对应的开关频率较高,为fc/2+2fb=8fb。

3)SVPWM NP-Ⅰ在载波比为12时可使相电压满足半波对称。当为情况1时,在其作用下相电压不会出现TLJ且开关频率较低,为fc/2+fb=7fb;当为情况2时,在其作用下相电压会出现TLJ且开关频率较高,为fc/2+2fb=8fb。

对于SVPWM NP-Ⅰ,当Vref跨越P型和N型区域交界处时,若第一个采样点对应下降方向三角载波,相电压会出现TLJ且开关频率会增加。

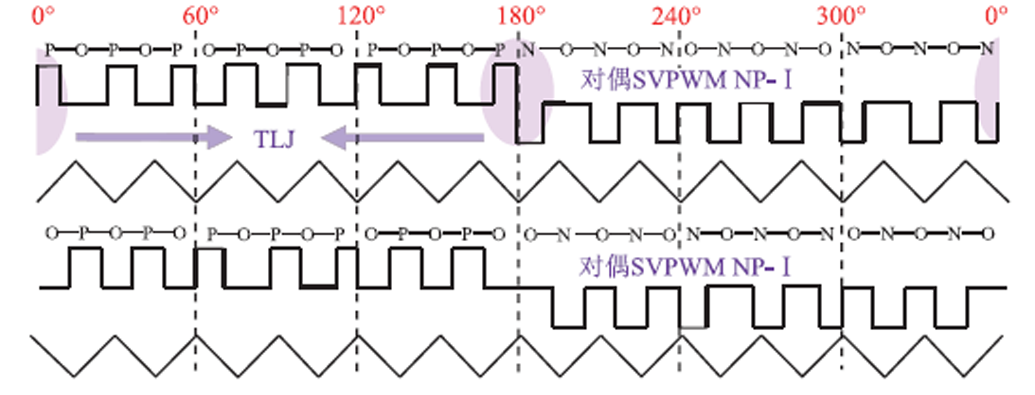

为解决SVPWM NP-Ⅰ存在的TLJ问题,首先分析载波比12下,SVPWM NP-Ⅰ的对偶模式对应的相电压波形,如图7所示。

图7 对偶SVPWM NP-Ⅰ对应的相电压

Fig.7 Phase voltage corresponding to dual SVPWM NP-Ⅰ

分析图7,对于对偶SVPWM NP-Ⅰ,当Vref跨越P型和N型区域交界处时,若第一个采样点对应上升方向三角载波,相电压会出现TLJ;若第一个采样点对应下降方向三角载波,相电压不会出现TLJ。对偶SVPWM NP-Ⅰ出现TLJ的情况与SVPWM NP-Ⅰ相反。

基于以上分析,提出针对SVPWM NP-Ⅰ的改进型开关序列,定义为SVPWM NP-Ⅲ,其原理为:当Vref跨越P型和N型区域交界处时,检测第一个采样点处对应的三角载波方向,若对应三角载波上升方向,选择使用SVPWM NP-Ⅰ;若对应三角载波下降方向,选择使用对偶SVPWM NP-Ⅰ。

经过上述处理的SVPWM NP-Ⅲ可在载波比12下避免TLJ,此外,其使得三相开关频率固定为7fb。

SVPWM N、SVPWM P和SVPWM NP-Ⅱ可分别在载波比15和12下使相电压满足半波对称并避免TLJ,但三者对应的开关频率均较高,达到8fb。

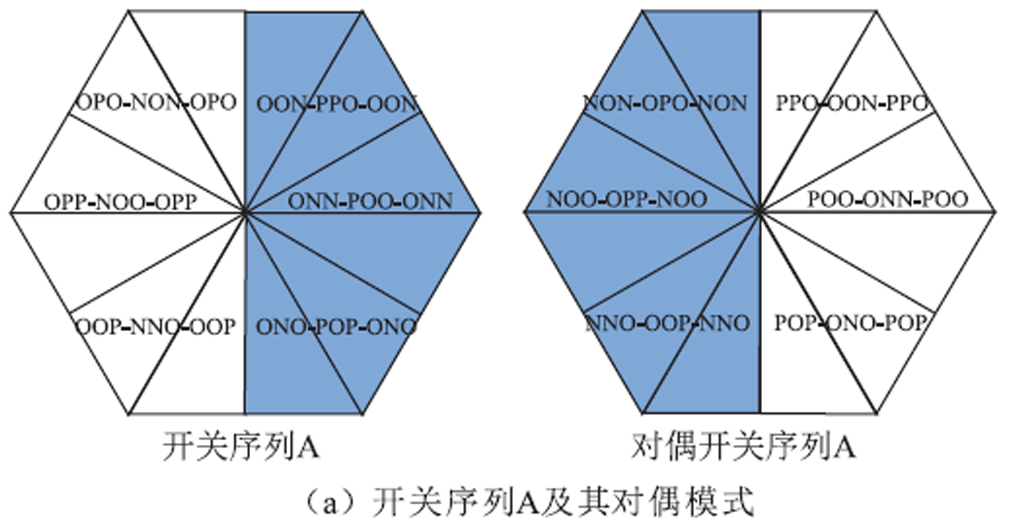

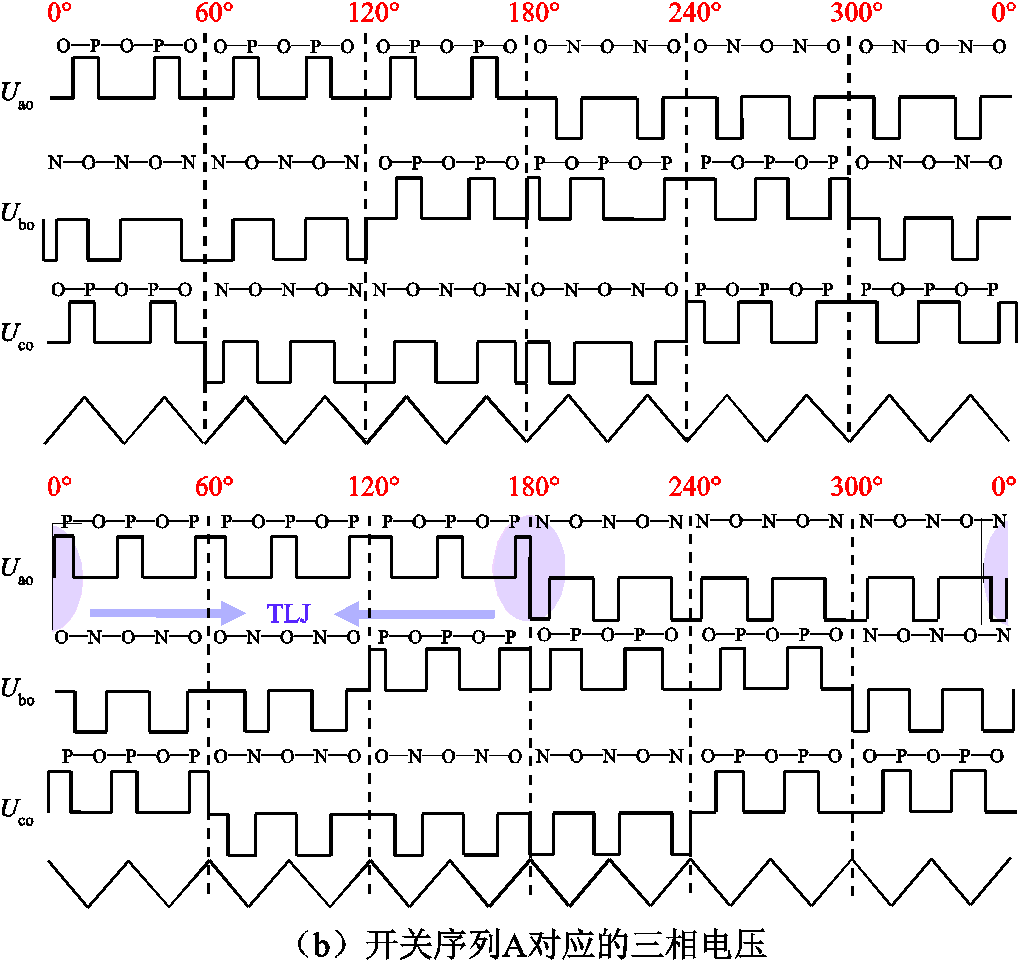

为在相电压满足半波对称的前提下降低开关频率,首先对比图6中SVPWM N和SVPWM P在载波比12下的相电压波形,从中可知:当进入各60°扇区后的第一个采样点对应上升方向三角载波时,在0°~180°区域,SVPWM N作用下的A相功率器件VTa1开关频率为fc,VTa2一直保持开通;在180°~360°区域,SVPWM P作用下的A相功率器件VTa2开关频率为fc,VTa1一直保持关断。则若在0°~180°区域使用SVPWM N,在180°~360°区域使用SVPWM P,可以在保证半波对称的前提下使A相内外管开关频率均保持为fc/2=6fb。相比传统SVPWM开关序列,该方法降低了A相的开关频率,定义为开关序列A。

开关序列A及其对应的三相电压状态如图8所示。观察图8,当进入各60°扇区后的第一个采样点对应上升方向三角载波时,开关序列A作用下的A相开关频率为6fb,B相和C相开关频率为7fb,相电压满足半波对称;当对应下降方向三角载波时,三相开关频率均为7fb,相电压满足半波对称,但A相电压会在N型区域和P型区域交界处出现TLJ。

图8 开关序列A及其对应的三相电压

Fig.8 Switching sequence A and its corresponding three-phase voltage

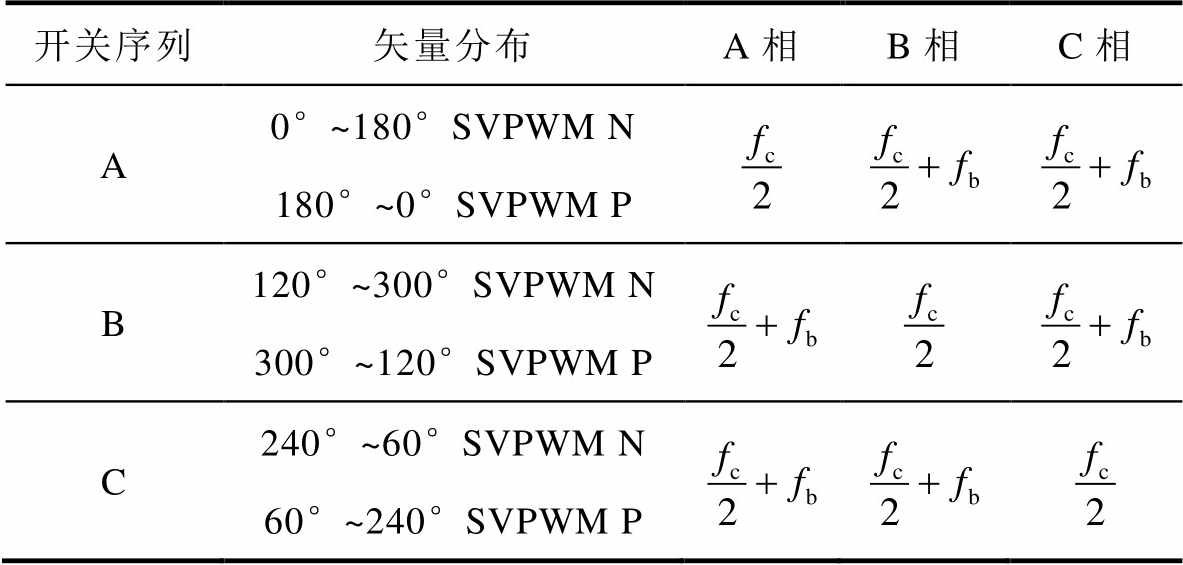

可同样利用对偶模式预防开关序列A作用下的相电压TLJ,具体方法如下:在Vref跨越0°和180°相角时进行判断,若跨越角度后的第一个采样点对应上升方向三角载波,调用开关序列A;若对应下降方向三角载波,则调用对偶开关序列A。将开关序列A分别移相120°和240°可得到降低B相开关频率的开关序列B和降低C相开关频率的开关序列C。开关序列A、开关序列B和开关序列C各自对应的三相开关频率见表2。

表2 开关序列A/B/C对应的开关频率

Tab.2 Switching frequency corresponding to switching sequences A, B and C

开关序列矢量分布A相B相C相 A0°~180°SVPWM N180°~0°SVPWM P B120°~300°SVPWM N300°~120°SVPWM P C240°~60°SVPWM N60°~240°SVPWM P

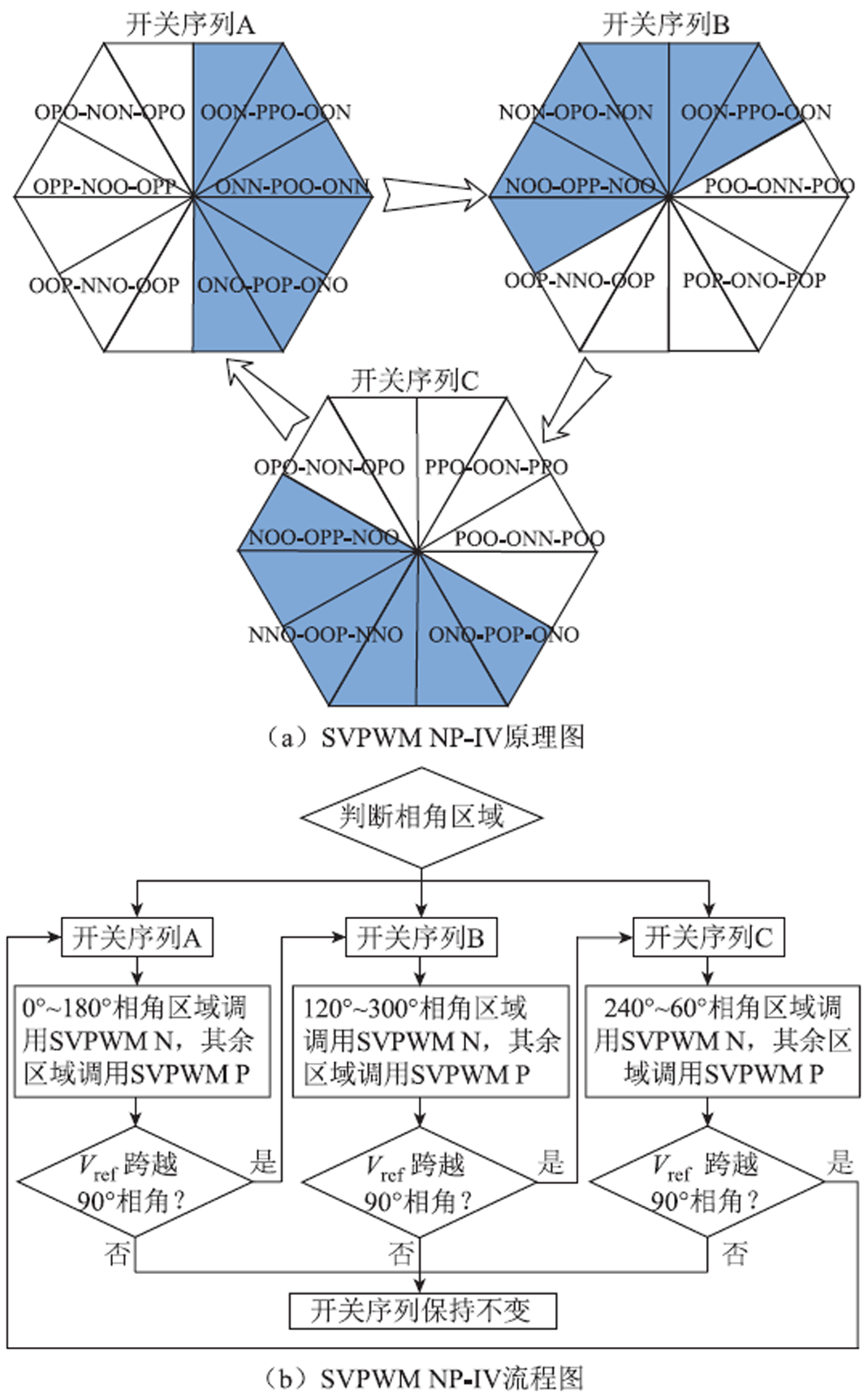

由表2可知,三种开关序列各自对应的三相开关频率并不相同,这不利于大功率三电平整流器的长期安全运行。为使三相平均开关频率一致,提出如图9所示的SVPWM NP-Ⅳ,其原理为:以整数倍基波周期作为时间单位,在90°相角处循环切换使用开关序列A、开关序列B和开关序列C,从而在相电压满足半波对称的前提下,将三相功率器件的平均开关频率降低至fc/2+2fb/3。

图9 SVPWM NP-IV原理及流程图

Fig.9 Principle and flow chart of SVPWM NP-IV

在90°处切换使用三种开关序列,需注意在切换前后是否出现TLJ。由图9推导三种开关序列在切换前后的相电压状态变化,其分别为:由开关序列A切换至B,对应相电压状态变化为ONN→POO;由开关序列B切换至C,对应相电压状态变化为POO→POO;由开关序列C切换至A,对应相电压状态变化为POO→ONN。故在90°相角处对三种开关序列进行切换,不会出现相电压TLJ,从而保证了SVPWM NP-IV的安全性。

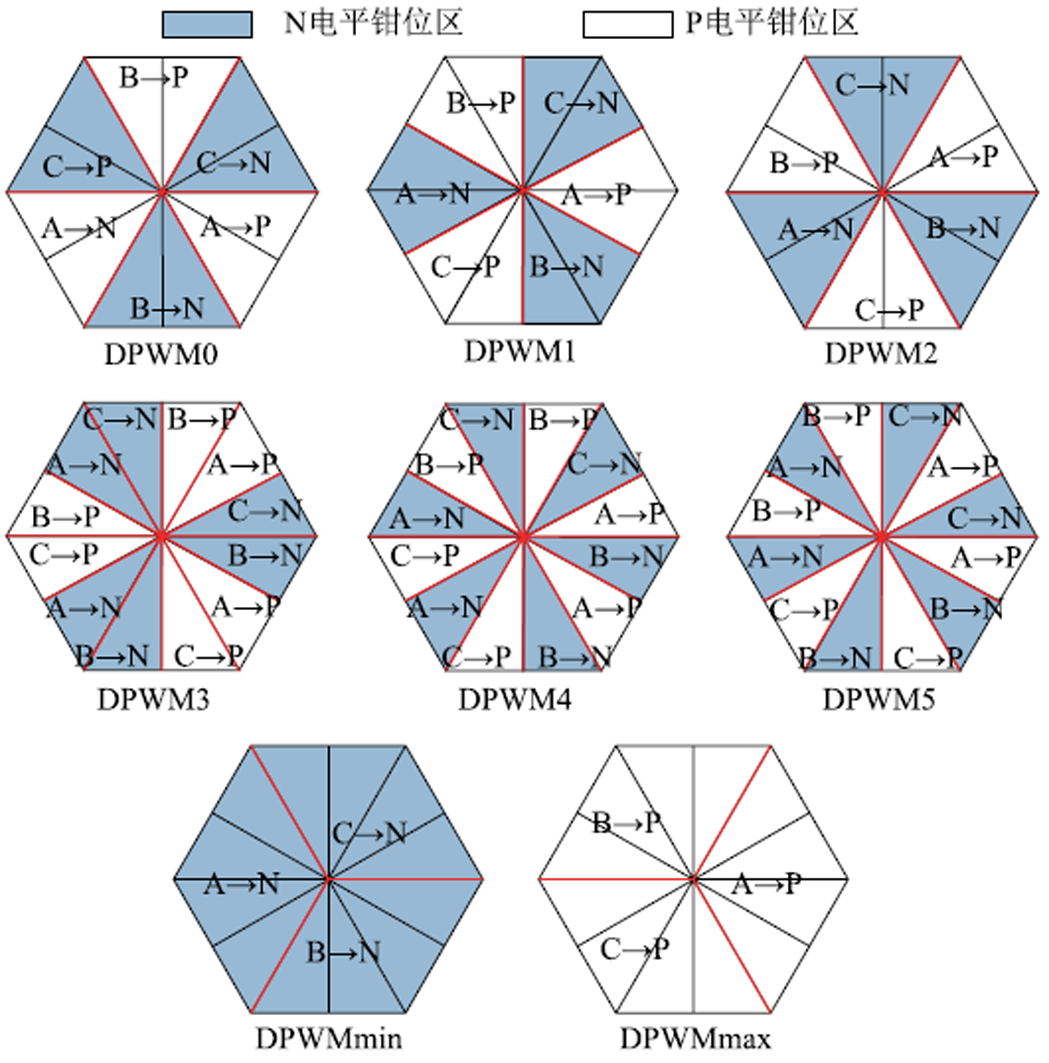

文献[13-15]根据每个Ts内使用特定冗余矢量类别的不同,提出了如图10所示八种不同的DPWM开关序列,分别定义为DPWM max/min/0/1/ 2/3/4/5。

图10 DPWM的八种传统开关序列

Fig.10 Eight traditional switching sequences of DPWM

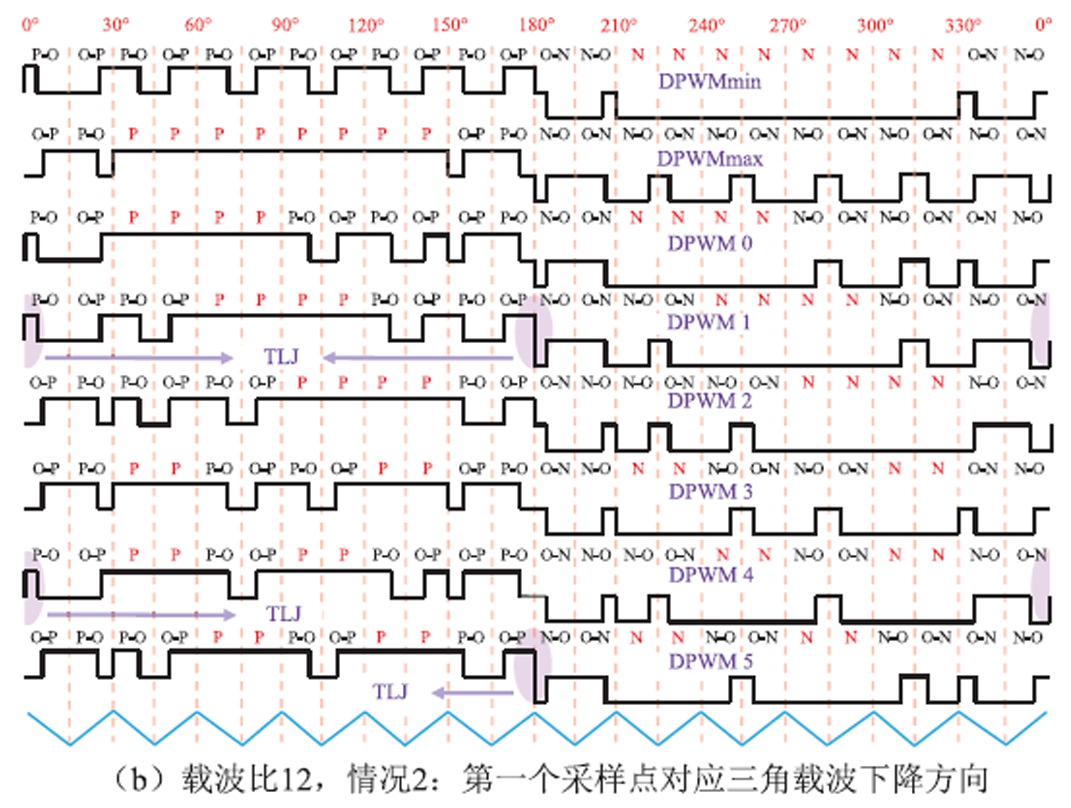

使用DPWM的主要目的是降低开关频率,故只分析DPWM在载波比12下的相电压波形。假定Vref位于图2区域5或区域6,八种DPWM开关序列对应的A相电压波形可总结于图11。

图11 八种DPWM开关序列对应的相电压

Fig.11 Phase voltage corresponding to eight DPWM switching sequences

对比图11,可得出以下结论:

1)DPWM min可将基波负半周120°的相电压钳位到N,DPWM max则可将基波正半周120°的相电压钳位到P,两者均可有效降低开关频率。但两者作用下的相电压波形均不满足半波对称,从而无法消除偶次谐波,不利于中点电压平衡。

2)DPWM 0和DPWM 2均可使相电压满足半波对称且不出现TLJ。当为情况1时,两者开关频率为6fb;当为情况2时,两者开关频率为5fb。

3)DPWM 1和DPWM 3均可使相电压满足半波对称并降低开关频率,但在两者作用下可能出现TLJ。其中,DPWM 3在情况1下会出现TLJ,DPWM 1则在情况2下出现TLJ。

4)DPWM 4和DPWM 5对应的相电压不满足半波对称且一定会出现TLJ。此外,在情况1下,两者的开关频率达到7fb。故相比其余DPWM开关序列,DPWM 4和DPWM 5无法有效降低开关频率。

综合以上分析可知,对于传统DPWM开关序列,只有DPWM 0和DPWM 2可在相电压满足半波对称和不出现TLJ的前提下有效降低开关频率。其余开关序列,只有DPWM 1和DPWM 3满足半波对称,但两者可能出现TLJ。针对DPWM 1和DPWM 3存在的缺陷,设计相应的改进型开关序列。

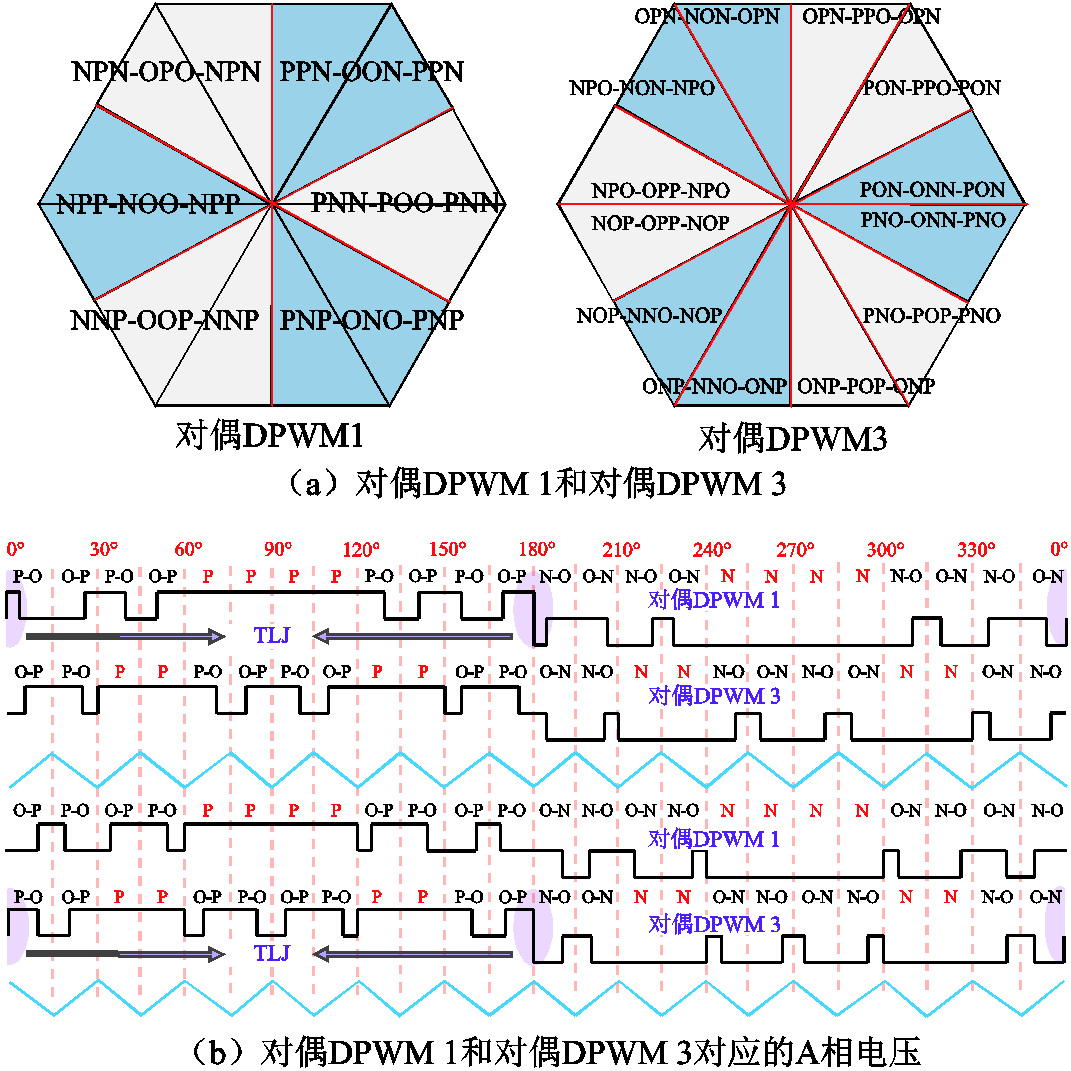

可利用DPWM 1和DPWM 3的对偶模式来预防TLJ。两种开关序列的对偶模式及其在载波比12下对应的A相电压如图12所示。

图12 对偶DPWM 1和对偶DPWM 3及其对应相电压

Fig.12 Dual DPWM 1 and dual DPWM 3 and their corresponding phase voltages

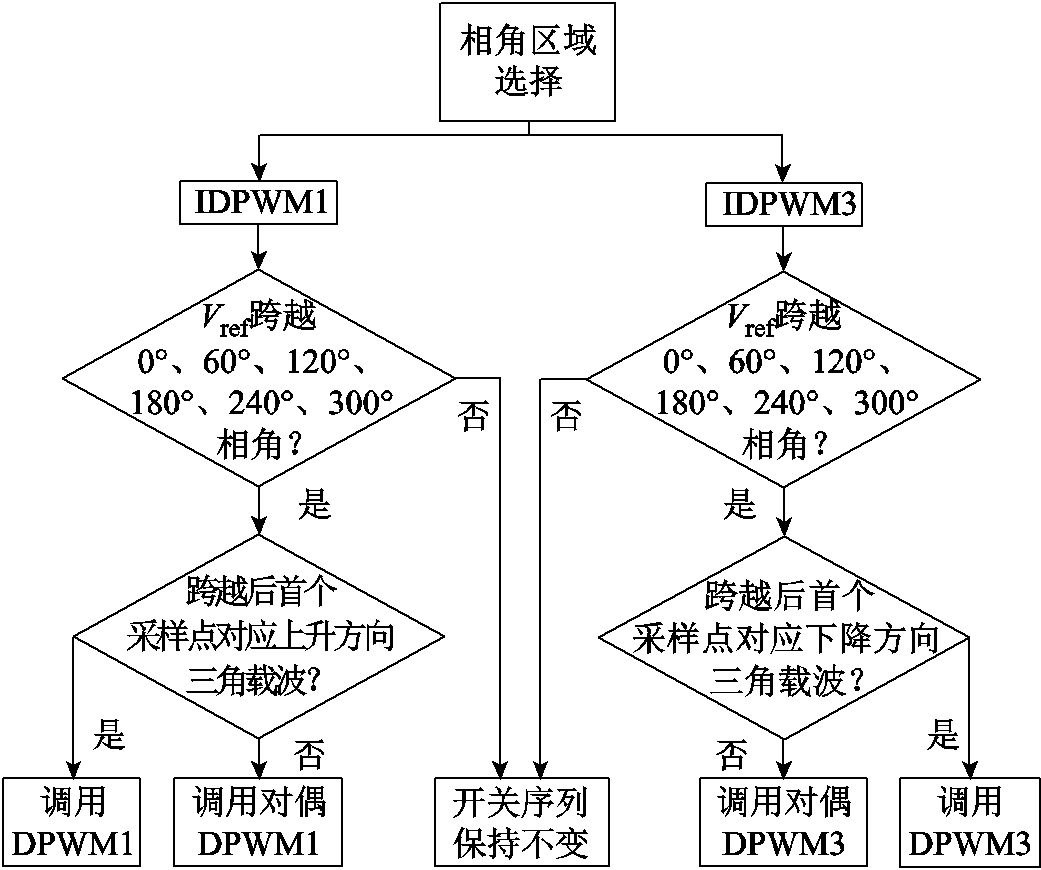

对比图11和图12可知,对偶DPWM 1、对偶DPWM 3的相电压出现TLJ的情况分别和DPWM 1、DPWM 3相反。利用这一特性,提出如图13所示DPWM 1和DPWM 3的改进型开关序列,分别定义为IDPWM 1和IDPWM 3。两者的具体原理为:当Vref跨越P电平钳位区和N电平钳位区交界处时,检测第一个采样点对应的三角载波方向。对于IDPWM 1,若对应上升方向三角载波,选择使用DPWM 1,若对应下降方向三角载波,选择使用对偶DPWM 1;对于IDPWM 3,若对应上升方向三角载波,选择使用对偶DPWM 3,若对应下降方向三角载波,选择使用DPWM 3。

图13 IDPWM 1和IDPWM 3流程

Fig.13 Flow chart of IDPWM 1 and IDPWM 3

经过第2节和第3节的总结与设计,共可得到六种SVPWM开关序列和十种DPWM开关序列。在此基础上,分别从TLJ、开关频率、中点电压自平衡能力、THD和网侧各次谐波电流含量等方面进一步分析各开关序列是否适用于大功率三电平NPC整流器。

第2节和第3节已从理论上对各开关序列的TLJ情况和开关频率进行了研究,在本节通过仿真进一步验证上述理论。利用PSIM软件搭建三电平NPC整流器模型,直流电压固定为5kV,调制比固定为1,基波频率50Hz,载波比设置为12或15。各开关序列作用下的相电压仿真结果如图14所示。

图14 各开关序列作用下的相电压仿真结果

Fig.14 Simulation results of phase voltage under each switching sequence

针对各开关序列的相电压TLJ情况,对比图14可知,只在SVPWM NP-I和DPWM 1/3/4/5作用下会出现TLJ,故此五种开关序列不能应用于大功率三电平NPC整流器。此外,所设计的SVPWM NP- III、IDPWM 1/3可有效解决SVPWM NP-I和DPWM 1/3存在的TLJ问题。

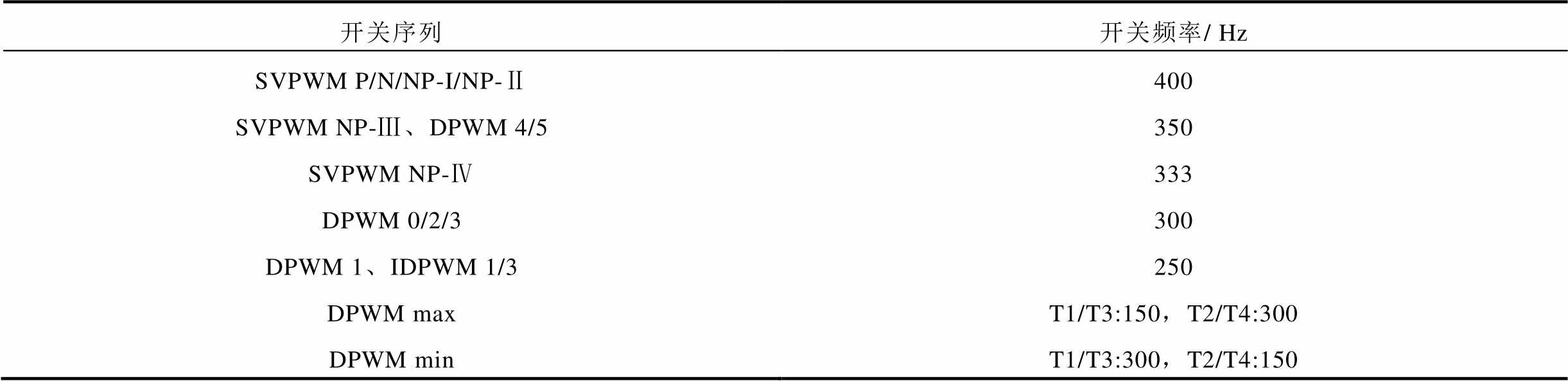

各开关序列对应的开关频率仿真结果见表4。由表4可知,相比SVPWM,各DPWM中只有IDPWM 1/3和DPWM 0/2/max/min可以在相电压无TLJ的前提下有效降低开关频率。此外,所设计的SVPWM NP-III/NP-IV相比SVPWM P/N/NP-II,可分别将开关频率由400Hz降至350Hz和333Hz。

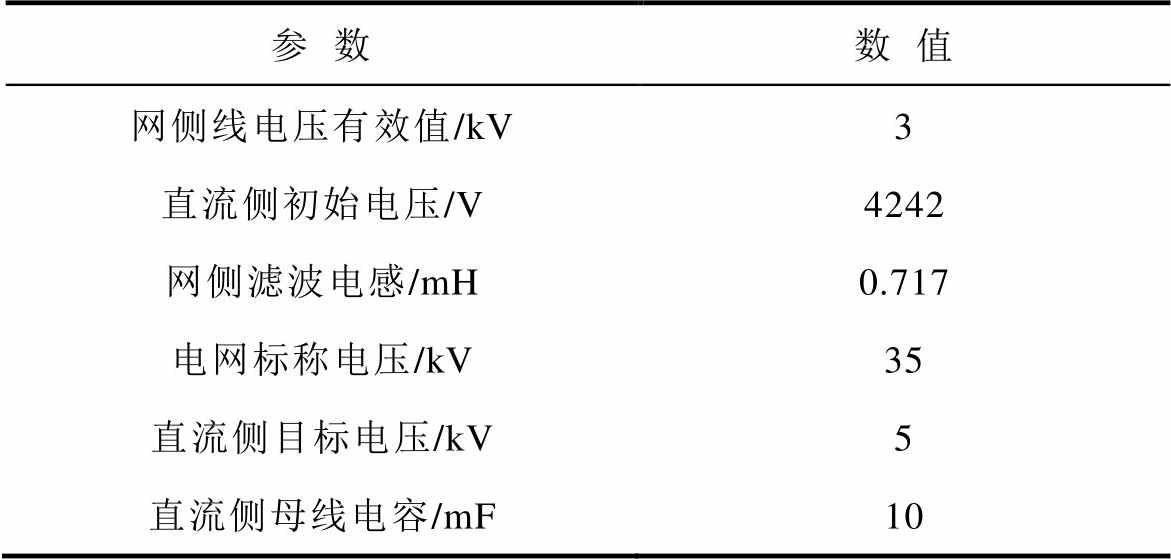

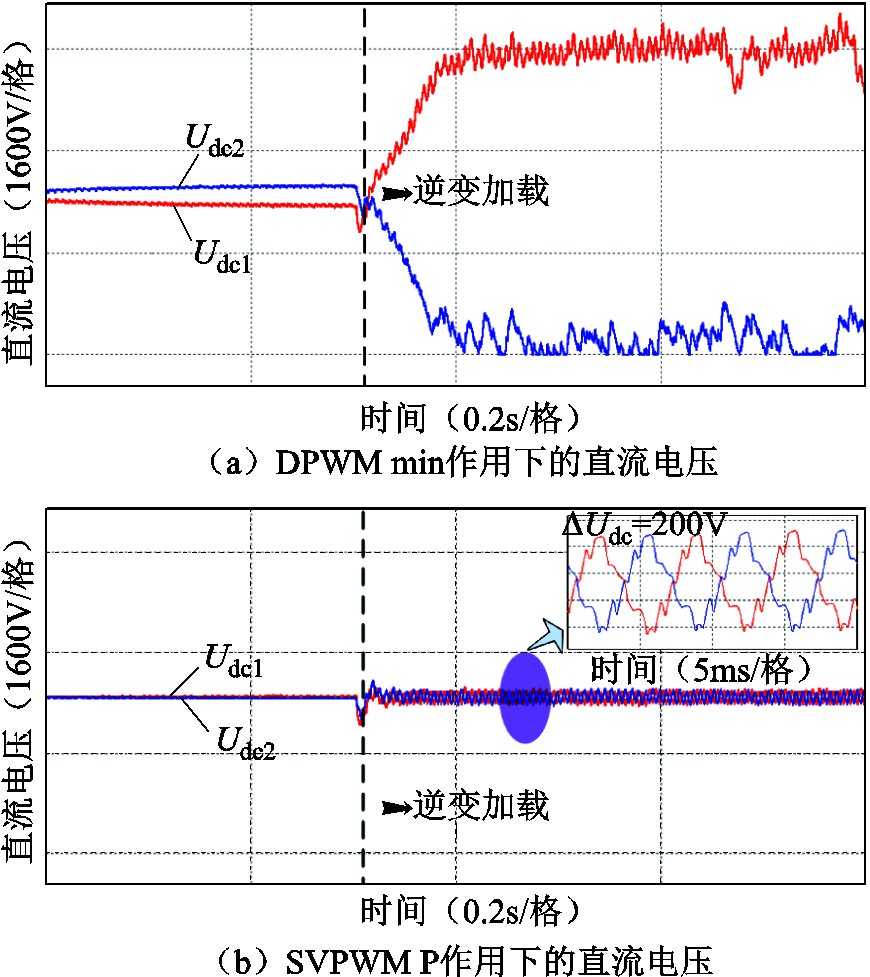

在DPWM 0/2/max/min、IDPWM 1/3、SVPWM P/N/NP-II/NP-III/NP-IV作用下,相电压不会出现TLJ。为进一步分析以上开关序列的中点电压自平衡能力,对以上开关序列分别进行闭环仿真。仿真在直流侧电压上升到5kV后,逆变突加10MW有功负载,整个过程不添加任何主动中点电压平衡控制方法,即完全依靠调制策略本身性能来维持中点电压的平衡。具体仿真条件见表5。

表4 各开关序列对应的开关频率仿真结果

Tab.4 Simulation results of switching frequency corresponding to each switching sequences

开关序列开关频率/ Hz SVPWM P/N/NP-I/NP-Ⅱ400 SVPWM NP-Ⅲ、DPWM 4/5350 SVPWM NP-Ⅳ333 DPWM 0/2/3300 DPWM 1、IDPWM 1/3250 DPWM maxT1/T3:150,T2/T4:300 DPWM minT1/T3:300,T2/T4:150

表5 三电平NPC整流器仿真条件

Tab.5 Three-level NPC rectifier simulation conditions

参数数值 网侧线电压有效值/kV3 直流侧初始电压/V4242 网侧滤波电感/mH0.717 电网标称电压/kV35 直流侧目标电压/kV5 直流侧母线电容/mF10

图15a和图15b分别为DPWM min和SVPWM P作用下的中点电压变化情况。相比DPWM min,相电压满足半波对称的SVPWM P具有更强的中点电压自平衡能力,其在逆变突加负载后仍可将中点电压偏差值控制在直流总电压的4%内。故为保持中点电压的平衡,大功率三电平NPC整流器应选用可使相电压满足半波对称的调制策略,而DPWM max/min并不适用于大功率三电平NPC整流器。

图15 DPWM min和SVPWM P作用下的直流电压

Fig.15 DC voltage corresponding to DPWM min and SVPWM P

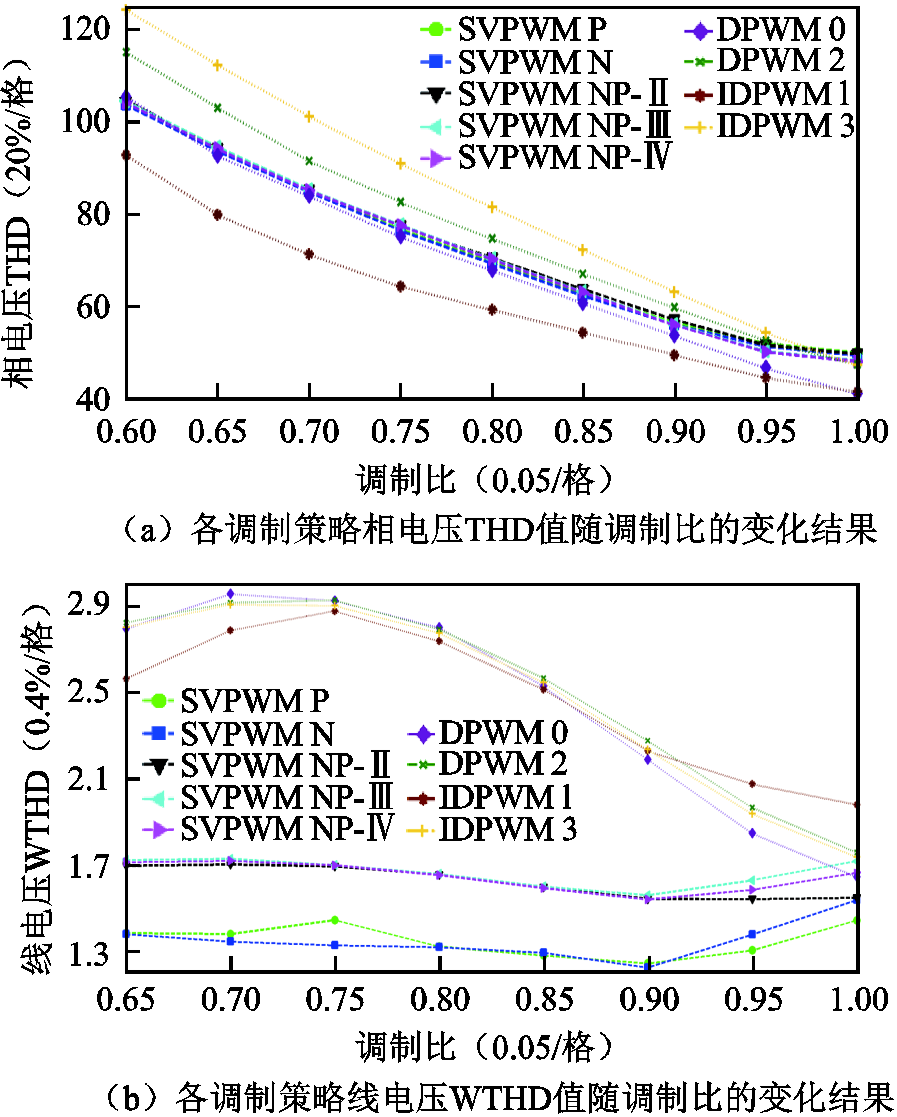

令调制比由0.6增加到1,对相电压无TLJ且满足半波对称的DPWM 0/2、IDPWM 1/3、SVPWM P/N/NP-II/NP-III/NP-IV的加权THD(Weighted THD,WTHD)和THD值进行仿真计算,结果如图16所示。

图16 各开关序列的谐波性能分析

Fig.16 Analysis of harmonic performance of each switching sequences

对比图16可知,在低载波比下,SVPWM的相电压THD值并未优于DPWM,DPWM 0、IDPWM 1的相电压THD值,甚至低于SVPWM。但在线电压WTHD比较上,SVPWM相比DPWM具有较大优势。这表明SVPWM相比DPWM,其主要谐波为高次谐波,对系统的不良影响更小。此外,载波比15下的SVPWM P/N线电压WTHD值最低。

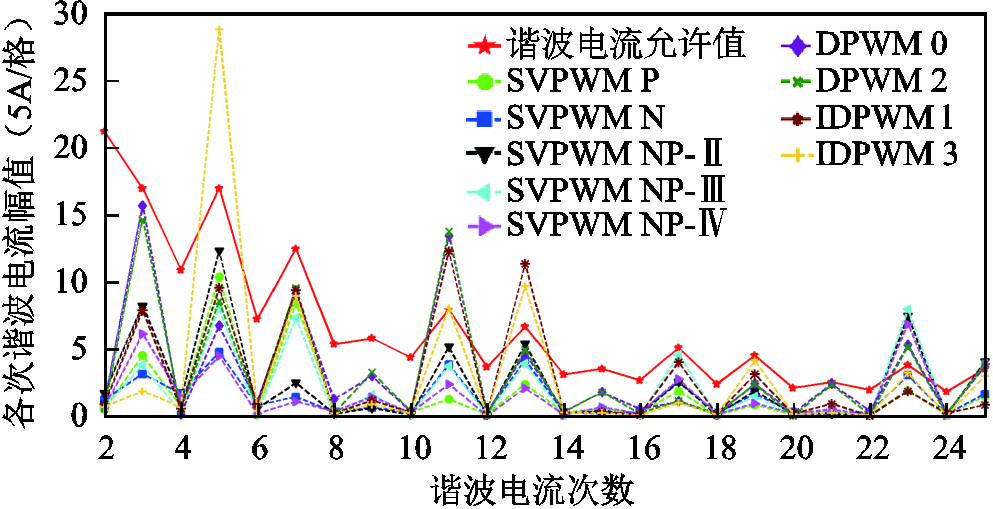

为进一步分析SVPWM P/N/NP-Ⅱ/NP-Ⅲ/NP-Ⅳ、DPWM 0/2、IDPWM 1/3对应的网侧各次谐波电流是否满足电网标准,依据表5仿真条件计算各开关序列的网侧谐波电流,结果如图17所示。

由于各开关序列均满足半波对称,故各次谐波电流值只可能在奇次谐波处超过允许值。分析图17,只有SVPWM P/N的25次以下谐波电流值均低于谐波电流允许值;SVPWM NP-Ⅱ/Ⅲ/Ⅳ的23次、25次谐波电流超过允许值,但其对应高次谐波电流,可通过适当增加网侧滤波电感值消除;DPWM 0/2和IDPWM 1/3均存在超过允许值的谐波电流,且次数集中在5次、11次、13次,其对应低次谐波电流,对系统的影响较大且不易消除。故DPWM 0/2和IDPWM 1/3不适用于大功率三电平NPC整流器。

图17 各开关序列的谐波电流分析

Fig.17 Analysis of harmonic current of each switching sequences

综合以上对SVPWM和DPWM各开关序列的TLJ、开关频率、中点电压自平衡能力、THD和各次谐波电流值的分析,研究适用于大功率三电平NPC整流器的调制策略,可得出以下结论:

1)针对SVPWM,当网侧滤波电感值较小时,为满足网侧谐波电流限值,优先使用载波比15下的SVPWM P/N,其对应开关频率为400Hz;当网侧滤波电感值较大时,23、25次等高次谐波电流可被消减,此时为尽可能降低开关频率,优先使用载波比12下的SVPWM NP-Ⅳ,其对应开关频率为333Hz。

2)针对DPWM,各DPWM的线电压WTHD值较大且均存在超过网侧谐波电流允许值的低次谐波电流,故DPWM不适用于大功率三电平整流器。

为验证所设计开关序列SVPWM NP-III/NP-Ⅳ和IDPWM 1/3的有效性,搭建了如图18所示基于IGBT的背靠背三电平NPC变流器样机。该样机通过VME机箱进行控制,机箱内包含AD采样板、时钟同步板、PWM脉冲板、CPU板等。样机的功率器件选用英飞凌公司的FZ300R12KE3G。

图18 三电平NPC变流器样机

Fig.18 Three-level NPC converter prototype

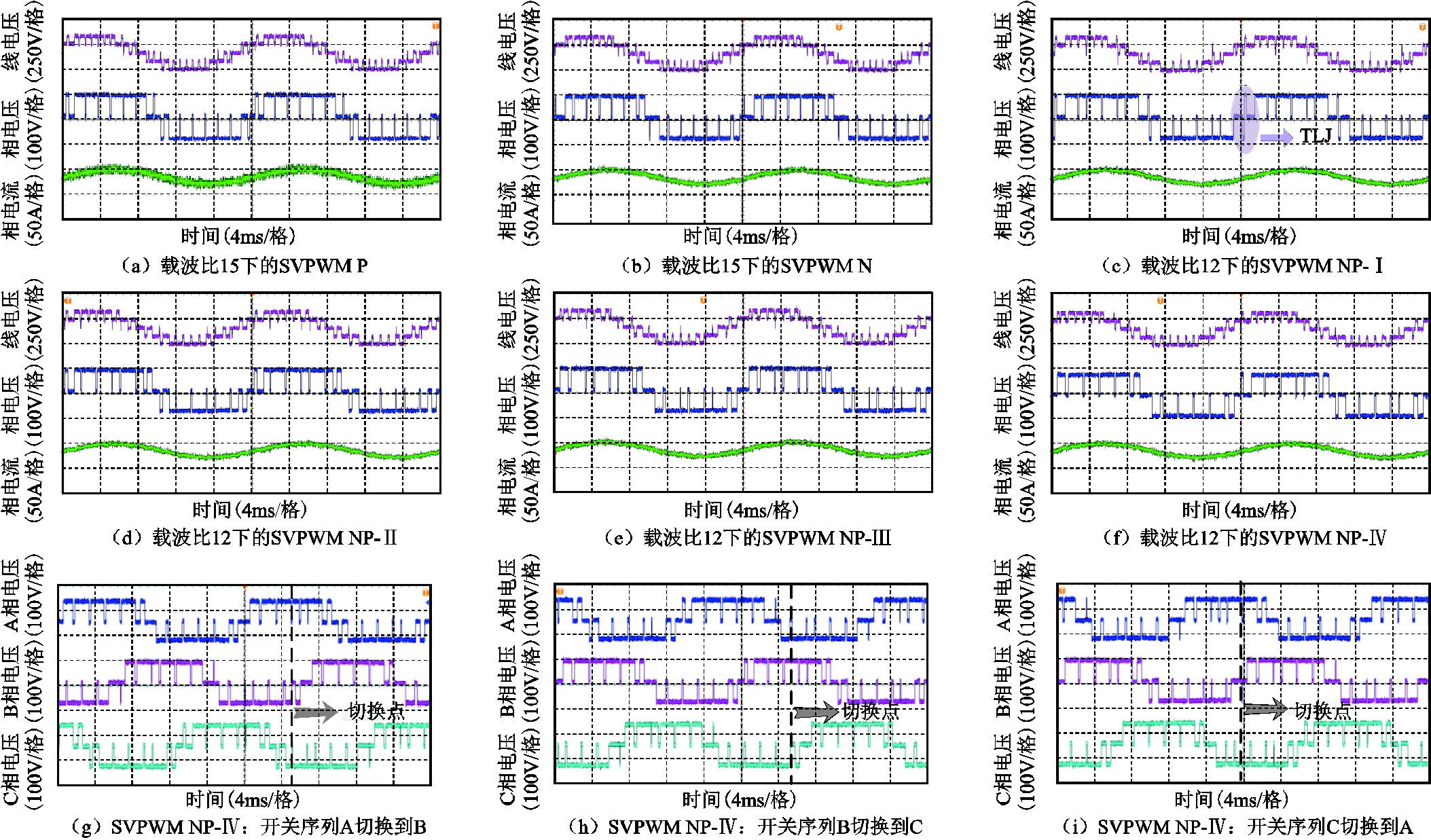

实验条件如下:采样方式为非对称规则采样,载波比设置为12或15。直流侧电压200V,逆变输出负载为4mH电感串联6.6Ω电阻。频率固定为50Hz,调制比固定为1。实验结果如图19所示。

图19 SVPWM和DPWM各开关序列的实验结果

Fig.19 Experimental results of SVPWM and DPWM switching sequences

图19a~图19d为SVPWM四种传统开关序列的实验结果。对比可知,SVPWM四种传统开关序列作用下的相电压均满足半波对称,但SVPWM N/P/NP-Ⅱ对应的开关频率较高,达到400Hz,SVPWM NP-Ⅰ则存在TLJ的缺陷。

图19e为SVPWM NP-III的实验结果。从中可知,SVPWM NP-III可解决SVPWM NP-I存在的TLJ并可将三相开关频率降低至350Hz。

图19f~图19i为SVPWM NP-IV的实验结果图。其中,图19g~图19i证明了开关序列A、B、C互相切换时不会出现TLJ。由图19f~图19i可知,SVPWM NP-IV作用下的相电压满足半波对称且三相平均开关频率仅为333Hz,其相比SVPWM N/P/NP-II降低了开关频率。

图19j~图19l为DPWM max/min的实验结果图。由于DPWM max/min的相电压不满足半波对称,导致两者并不具备中点电压自平衡能力,易出现如图19l所示的中点电压不平衡问题。

图19m~图19p分别为DPWM 0/2/4/5作用下的线电压、相电压和相电流波形。从中分析可知,DPWM 0/2作用下的相电压满足半波对称且无TLJ,其对应开关频率为300Hz,可相比SVPWM降低开关频率;DPWM 4/5作用下的相电压则不满足半波对称并且会出现TLJ。此外,DPWM 4/5对应的开关频率为350Hz,相比SVPWM并未明显降低。

图19q~图19t通过实验验证了本文所提IDPWM 1/3的有效性。传统DPWM 1/3作用下的相电压虽然满足半波对称但存在TLJ,IDPWM 1/3可分别解决DPWM 1/3存在的TLJ并可将三相开关频率固定至300Hz,从而有效降低了开关频率。

为研究适用于大功率三电平NPC整流器的SVPWM和DPWM策略,本文首先分析了SVPWM N/P/NP-I/NP-II和DPWM 0/1/2/3/4/5/max/min对应的相电压波形。针对SVPWM NP-I和DPWM 1/3存在的TLJ问题,分别提出了可预防TLJ的SVPWM NP-III和IDPWM 1/3;针对SVPWM N/P/NP-II存在的开关频率较高缺陷,提出了可降低开关频率的SVPWM NP-IV。基于以上各SVPWM和DPWM开关序列,本文分别从TLJ、开关频率、中点电压自平衡能力、THD和谐波电流含量来分析其性能,并以此总结了适用于大功率三电平NPC整流器的三种SVPWM开关序列:SVPWM N/P/NP-IV。最后,搭建了三电平NPC变流器样机,对所设计SVPWM NP-III/NP-IV和IDPWM 1/3的有效性进行了验证。

参考文献

[1] Rodriguez J, Bernet S, Steimer P K, et al. A survey on neutral-point-clamped inverters[J]. IEEE Transactions on Industrial Electronics, 2010, 57(7): 2219-2230.

[2] Abu-Rub H, Holtz J, Rodriguez J, et al. Medium- voltage multilevel converters-state of the art, chall- enges, and requirements in industrial applications[J]. IEEE Transactions on Industrial Electronics, 2010, 57(8): 2590-2596.

[3] 姜卫东, 赵德勇, 胡杨, 等. 基于载波实现的二极管钳位型三电平逆变器虚拟空间矢量脉宽调制方法[J]. 电工技术学报, 2016, 31(12): 153-160. Jiang Weidong, Zhao Deyong, Hu yang, et al. Carrier- based virtual space vector pulse width modulation for diode clamped three-level inverter[J]. Transactions of China Electrotechnical Society, 2016, 31(12): 153-160.

[4] Grigoletto F B, Pinheiro H. A space vector PWM modulation scheme for back-to-back three-level diode-clamped converters[C]//Proceedings of Power Electronics Conference, Bonito-Mato Grosso do Sul, 2009: 1058-1065.

[5] GB/T 14549-93 电能质量公用电网谐波[S]. 北京: 中国标准出版社, 1994.

[6] 殷正刚. 大功率三电平逆变器脉宽调制及磁场定向控制的研究[D]. 北京: 中国科学院大学, 2012.

[7] Chaturvedi P, Jain S, Agarwal P. Carrier-based neutral point potential regulator with reduced switching losses for three-level diode-clamped inverter[J]. IEEE Transactions on Industrial Electronics, 2014, 61(2): 613-624.

[8] Zhou Keliang, Wang Danwei. Relationship between space-vector modulation and three-phase carrier-based PWM a comprehensive analysis three-phase inverters[J]. IEEE Transactions on Industry Applications, 2002, 49(1): 186-196.

[9] Zhang Z, Thomsen O C, Andersen M A E, et al. Discontinuous PWM modulation strategy with circuit- level decoupling concept of three-level neutral- point- clamped (NPC) inverter[J]. IEEE Transactions on Industrial Electronics, 2013, 60(5): 1897-1906.

[10] Holmes D G, Lipo T A. Pulse width modulation for power converters: principles and practice[M]. BeiJing: Posts & Telecom Press, 2010.

[11] Feng D, Wu B, Liu C, et al. Space vector modulation for high-power three-level NPC rectifier without even order harmonics[C]//Power Electronics Specialists Conference, Recife, 2005:1986-1991.

[12] Yin Zhenggang, Tan Kai, Liu Congwei, et al. Three level space vector pulse width modulation without even order harmonics fit for asymmetrical uniform sampling[C]//2010 IEEE International Conference on Industrial Technology, Vinadel Mar, Chile, 2010, DOI: 10.1109/ICIT.2010.5472599.

[13] McGrath B P, Holmes D G, Lipo T. Optimized space vector switching sequences for multilevel inverters[J]. IEEE Transactions on Power Electronics, 2003, 18(6): 1293-1301.

[14] Beig A R, Kanukollu S, Hosani K A, et al. Space- vector-based synchronized three-level discontinuous PWM for medium-voltage high-power VSI[J]. IEEE Transactions on Industrial Electronics, 2014, 61(8): 3891-3901.

[15] 魏旻. 基于载波实现的DPWM统一化实现方法及其应用研究[D]. 成都: 电子科技大学, 2018.

[16] 谷鑫, 刘潮, 张国政, 等. 三电平逆变器同步不连续空间矢量调制输出电流优化策略[J]. 电工技术学报, 2019, 34(5): 924-933. Gu Xin, Liu Chao, Zhang Guozheng, et al. Space- vector based synchronous discontinuous PWM for three-level inverter with output current optimization[J]. Transactions of China Electrotechnical Society, 2019, 34(5): 924-933.

[17] 史婷娜, 刘潮, 张国政, 等. 三电平逆变器综合性能优化不连续空间矢量调制策略[J]. 电工技术学报, 2018, 33(24): 5874-5833. Shi Tingna, Liu Chao, Zhang Guozheng, et al. Discontinuous space vector PWM for three-level inverter with comprehensive performance optimization[J]. Transactions of China Electrotechnical Society, 2018, 33(24): 5874-5833.

[18] 罗锐, 何英杰, 陈晖等. 三电平变流器中点电压平衡及低开关损耗SVPWM调制策略[J]. 电工技术学报, 2018, 33(8): 1-10. Luo Rui, He Yingjie, Chen Hui, et al. SVPWM scheme for three-level converters with neutral point potential balancing and switching loss reduction[J]. Transactions of China Electrotechnical Society, 2018, 33(8): 1-10.

[19] 赵辉, 胡仁杰. SVPWM 的基本原理与应用仿真[J]. 电工技术学报, 2015, 30(14): 350-353. Zhao Hui, Hu Renjie. Space-vector pulse width modulation and it’s simulation based on simulink [J]. Transactions of China Electrotechnical Society, 2015, 30(14): 350-353.

Research on SVPWM and DPWM Strategies Suitable for High Power Three-Level Neutral Point Clamped Rectifier

Abstract The high power three-level neutral point clamped (NPC) rectifier should reduce the switching frequency as much as possible while satisfying the harmonic current limit of the grid side, the neutral-point voltage balancing of the DC side and avoiding the phase voltage two-level jump (TLJ). Based on the above requirements, this paper firstly analyzes the basic principles of space vector pulse width modulation (SVPWM) and discontinuous PWM (DPWM), and then introduces four SVPWM switching sequences and eight DPWM switching sequences and compares their respective phase voltage waveforms. Aiming at the defects of TLJ and high switching frequency of traditional SVPWM, two improved SVPWM switching sequences are designed. And to solve the TLJ of DPWM, two improved DPWM switching sequences are proposed. On this basis, this paper studies SVPWM and DPWM from the aspects of TLJ, switching frequency, neutral-point voltage self-balancing ability, total harmonic distortion (THD) and harmonic current content, and summarizes three SVPWM switching sequences suitable for high power three-level NPC rectifier. Finally, a three-level NPC converter prototype is established, and the effectiveness of the designed improved switching sequences are verified by experiments.

keywords:Three-level neutral point clamped rectifier, SVPWM, DPWM, two-level jump, reduce switching frequency

中图分类号:TM461

DOI:DOI:10.19595/j.cnki.1000-6753.tces.191599

国家重点研发计划高速磁浮交通系统关键技术研究课题资助项目(2016YFB1200602-20)、国家重点研发计划电力电子变压器及其控制策略研究与应用课题资助项目(2017YFB1200901-14)和国家自然科学基金(51907188)资助。

收稿日期2019-11-22

改稿日期 2020-01-09

高 瞻 男,1993年生,博士研究生, 研究方向为大功率电力电子变流器控制技术。E-mail:gz1993@mail.iee.ac.cn

赵 鲁 男,1984年生,副研究员, 硕士生导师, 研究方向为大功率变流器及高性能电机牵引控制技术。E-mail:zhaolu@mail.iee.ac.cn(通信作者)

(编辑 赫蕾)