图1 全桥及改进全桥子模块拓扑

Fig.1 FBSM and improved FBSM topologies

摘要 基于模块化多电平换流器的高压直流输电需应对直流线路可能短路故障和子模块数量过多带来的电容电压均衡问题。为保证模块之间独立工作为约束条件,该文首先分析全桥拓扑故障抑制机理。然后基于故障钳位电路和开关电容多电平思想,设计一种具有直流故障电流阻断和内部电容电压均衡能力的自阻自均压型子模块拓扑,不仅能满足直流故障电流阻断要求,还将参与排序均衡的电容数量减少一倍。同时研究自阻、自均压拓扑两种不同闭锁模式下直流故障抑制特性、电平输出优先的自均压控制策略以及非闭锁直流故障抑制策略。最后通过PSCAD- EMTDC仿真模型验证该文所提自阻自均压拓扑直流故障抑制及控制策略的有效性。

关键词:模块化多电平换流器 直流故障抑制 自阻自均压子模块拓扑 非闭锁抑制

模块化多电平换流器(Modular Multilevel Con- verter, MMC)采用子模块级联结构,具有开关器件应力小,电压、电流波形质量高,输出电压调节灵活等特点,因此在高压直流输电和电能变换领域得到广泛应用[1-2]。当MMC应用于高压直流输电时,有如下两个问题必须考虑。

(1)如何处理直流侧线路短路故障。直流系统一旦发生故障,较低的阻尼导致电流上升率较高,且不同于交流故障,没有电流过零点,从而电流清除难度要大于交流系统。当前主要有以下几种方法切断故障电流:首先依靠换流站交流断路器,但交流断路器故障切除时间通常在45~150ms之间,不利于故障快速切除和系统恢复。其次安装直流断路器对直流侧故障进行隔离,目前国内外仅有为数不多的几个公司完成了直流断路器样机研制,这些样机还没有广泛的工程成功应用案例,成本高且技术仍然不成熟[1-3]。最后,换流器采用具有故障抑制能力改进型子模块代替半桥子模块实现短路故障清除,例如,具有并联抑制功能的钳位二极管子模块(Clamp Diode Sub Module, CDSM)及其改进拓 扑[4-6];实现串联抑制功能的串联双子模块(Serial Double Sub Module, SDSM)和跨接三电平和五电平拓扑[7-8],为减少功率器件数量的闭锁后储能电容非对称充电的混合拓扑[9-11],利用双向阻断能力绝缘栅双极型晶体管(Insulated Gate Bipolar Transistor, IGBT)构成的阻断型拓扑[11-13]。上述改进型拓扑无一例外都是通过采用单一闭锁模式实现直流故障抑制。全桥拓扑具有直流故障电流非闭锁抑制功能,但是相对于半桥子模块拓扑所需功率器件较多。而全桥子模块+半桥子模块构成的混合拓扑虽然可以实现直流故障非闭锁抑制,但故障抑制期间,半桥子模块处于旁路状态。总之,无论是改进型拓扑直流故障闭锁抑制,还是全桥+半桥拓扑直流故障非闭锁抑制,都存在全部或部分子模块处于闭锁或旁路状态,而由于子模块取能电路影响,可能会导致电容电压发散[14]。

(2)电容电压均衡问题。MMC中子模块电容相互独立,电容电压均衡依赖于均压控制,而均压控制复杂程度又直接取决于MMC子模块数目。随着子模块数目增加,均压控制对计算量和数据采集速度要求日趋严苛,由此带来一系列子模块电容均压问题。文献[15]研究了电容电压排序均衡控制策略,该策略具有原理清晰、实现简单的特点。但排序均衡需要对所有模块电容电压进行实时排序和选择,占用运算资源较多,可能会在控制环节引入较大延迟,降低MMC电流动态跟踪特性。文献[16]针对载波移相调制策略,为每个子模块附加独立电容电压控制环节,实现了无需排序的电压均衡控制,但控制环节增加了均压控制复杂度。文献[17-18]提出一种减少传感器的电容电压分组均衡控制策略以提高均压效率,但不能应对组内部电容参数差异引起的误差。为实现模块间电容能量交换,解决电容电压均衡问题,文献[19]在相邻子模块电容上串接钳位二极管,提供能量通道,设计了一种MMC新拓扑,但是需要借助辅助变压器才能实现相内电压平衡。文献[20]提出一种具备自均压能力MMC拓扑,在保留MMC模块化特性的同时,采用二极管钳位方法,将各个子模块电容电压钳位在最底端子模块和最顶端子模块电容电压之间,使得MMC在子模块投切过程中自发实现电容电压均衡。这种方法控制简单,但是保持最底端和最顶端子模块电容电压平衡电路可能需要承受较高的绝缘电压。

针对上述问题,本文首先利用钳位电路和开关电容网络设计一种多电平子模块拓扑,研究其电平输出特性,实现闭锁和非闭锁直流故障抑制。然后为减少电容电压排序均衡所耗费控制系统计算资源,提高系统动态响应速度,在多电平子模块拓扑基础上根据并联电路电压相等原理,设计子模块内部均压电路,形成自阻自均压复合型子模块拓扑,并研究其均压控制策略。最后通过PSCAD/EMTDC仿真模型验证本文所提拓扑的直流故障抑制特性及均压控制策略的有效性。

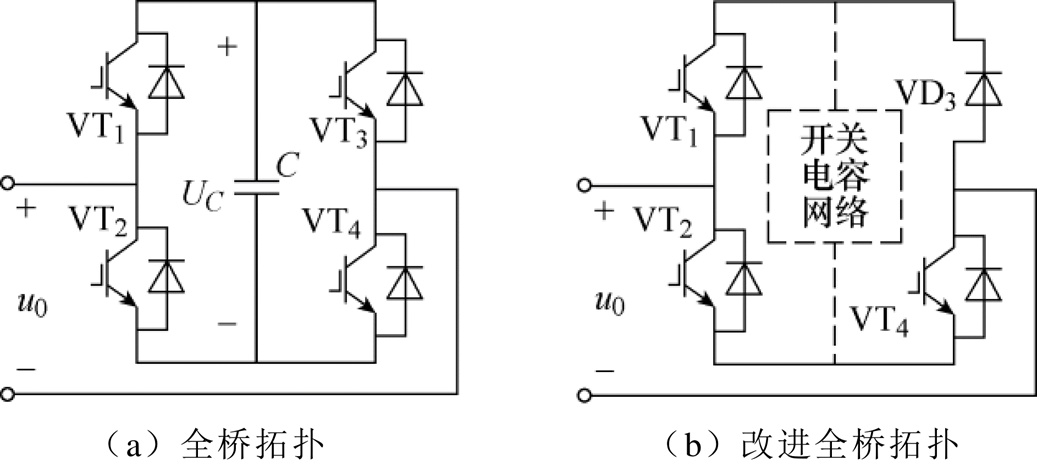

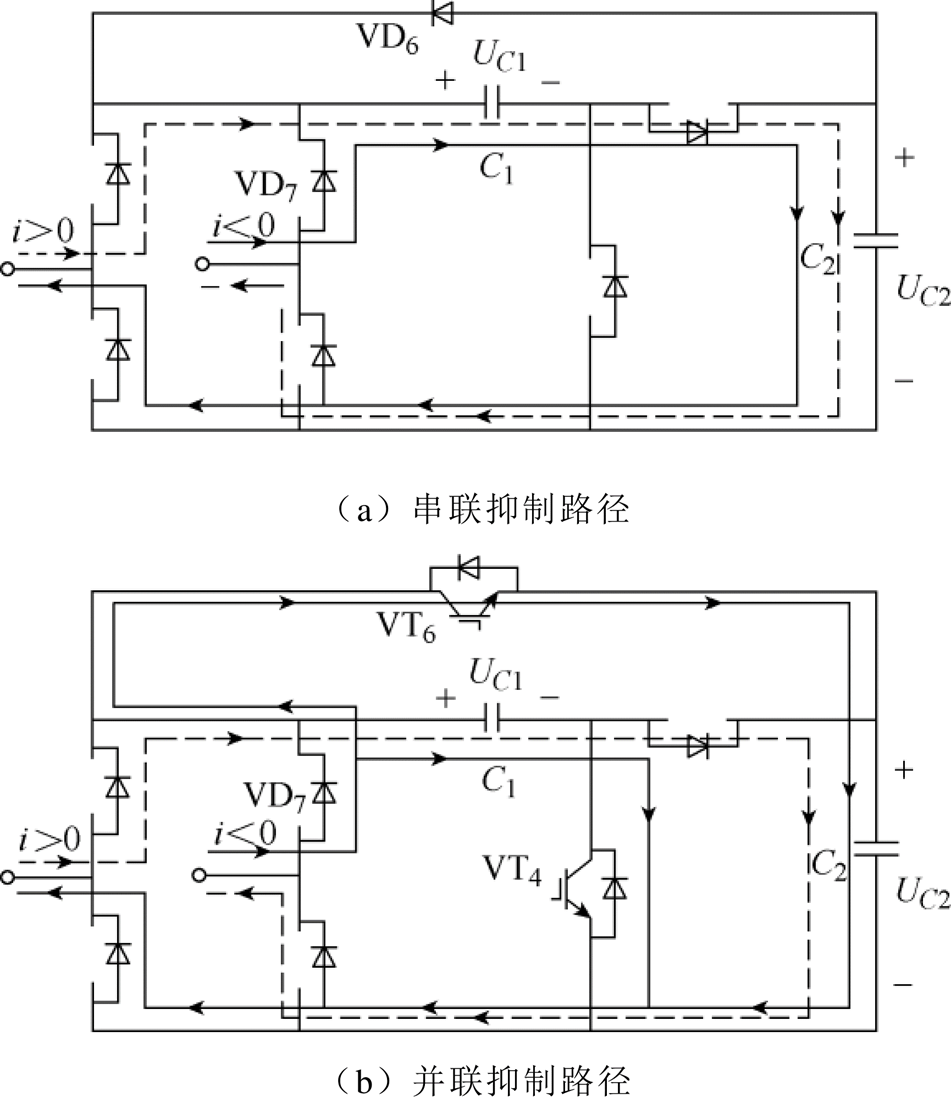

全桥及改进全桥子模块拓扑如图1所示。图1a所示全桥子模块(Full Bridge Sub Module, FBSM)拓扑能保证闭锁后桥臂电流双向流动下电容充电,吸收短路能量,并提供二极管反向偏置电压,实现故障抑制。相比半桥拓扑,图1a中右半部分构成了负电平输出电路,即反向电流充电路径。在不影响正电平输出和直流故障闭锁抑制前提下,将图1中IGBT VT3替换为二极管VD3,如图1b所示,以降低功率器件个数,形成改进全桥子模块拓扑,其中VT4和VD3构成钳位电路。

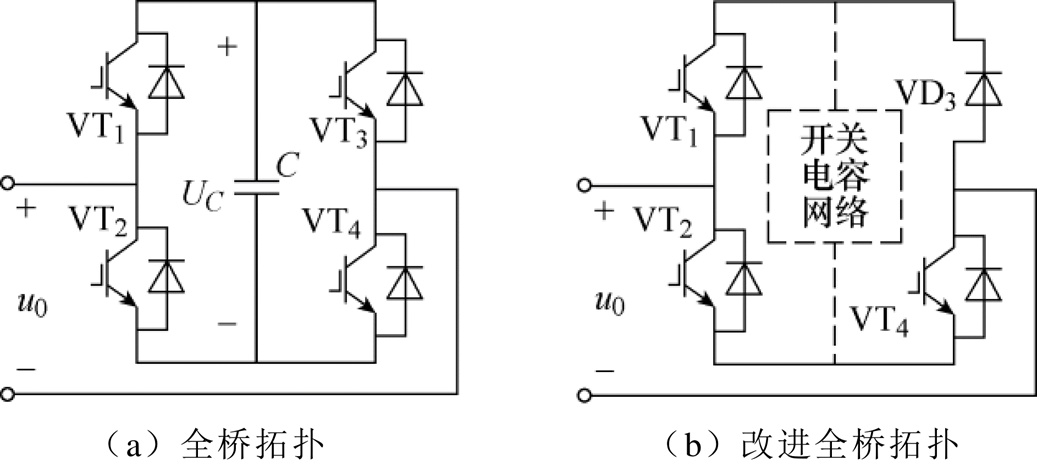

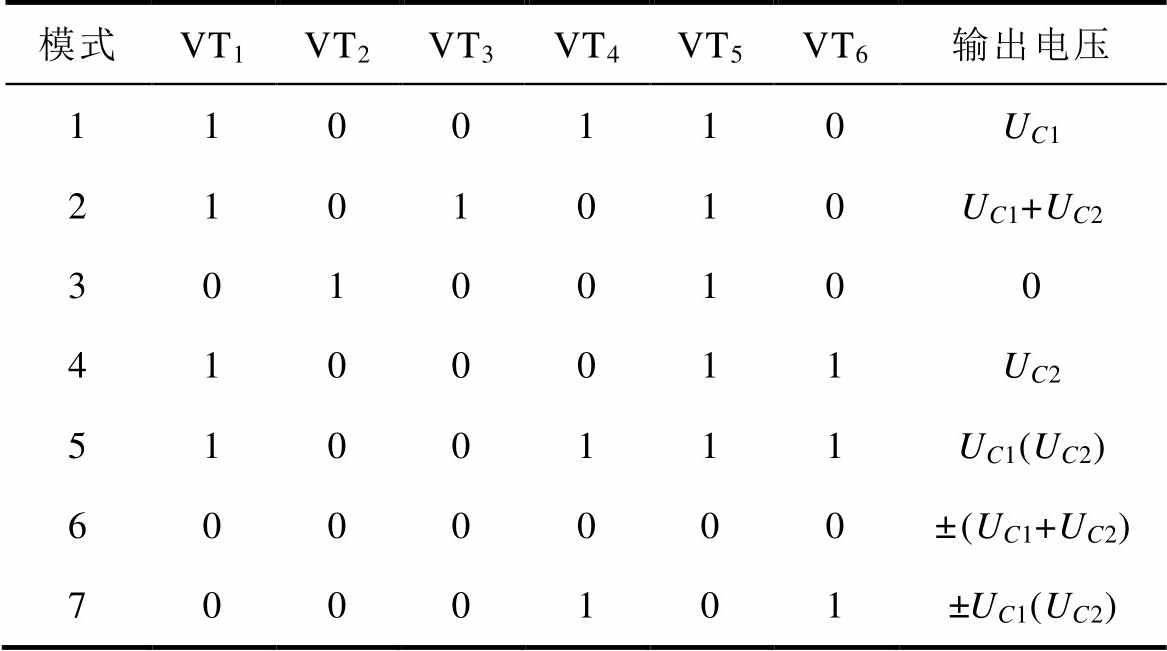

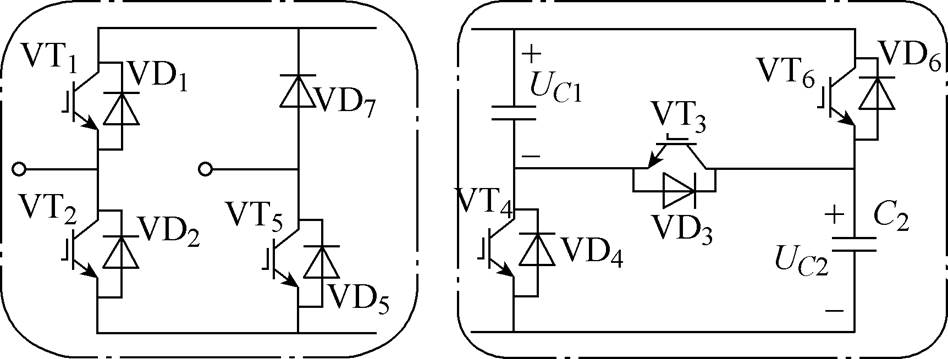

自阻自均压复合子模块拓扑如图2所示。为进一步降低单位电平功率器件数量,将图1a储能电容C替换为开关电容网络,设计出如图2a所示多电平拓扑,其开关逻辑见表1。由于钳位电路VT5和VD7作用,闭锁后新拓扑能够实现双向电流电容充电,因而具有直流故障阻断能力。但是不同于CDSM或SDSM双子模块拓扑,电容电压UC2不能单独输出,这一方面降低了模块工作灵活性;另一方面由于两个电容充放电时间长短差异,会带来电容电压内部不均衡问题,影响双一电平输出特性。如果能够实现C2电压单独输出,或保证其电压在合理波动范围内,便不会影响到模块内部电压均衡,从而保证子模块正常工作。

图1 全桥及改进全桥子模块拓扑

Fig.1 FBSM and improved FBSM topologies

图2 自阻自均压复合子模块拓扑

Fig.2 Self-block and balance composite SM topology

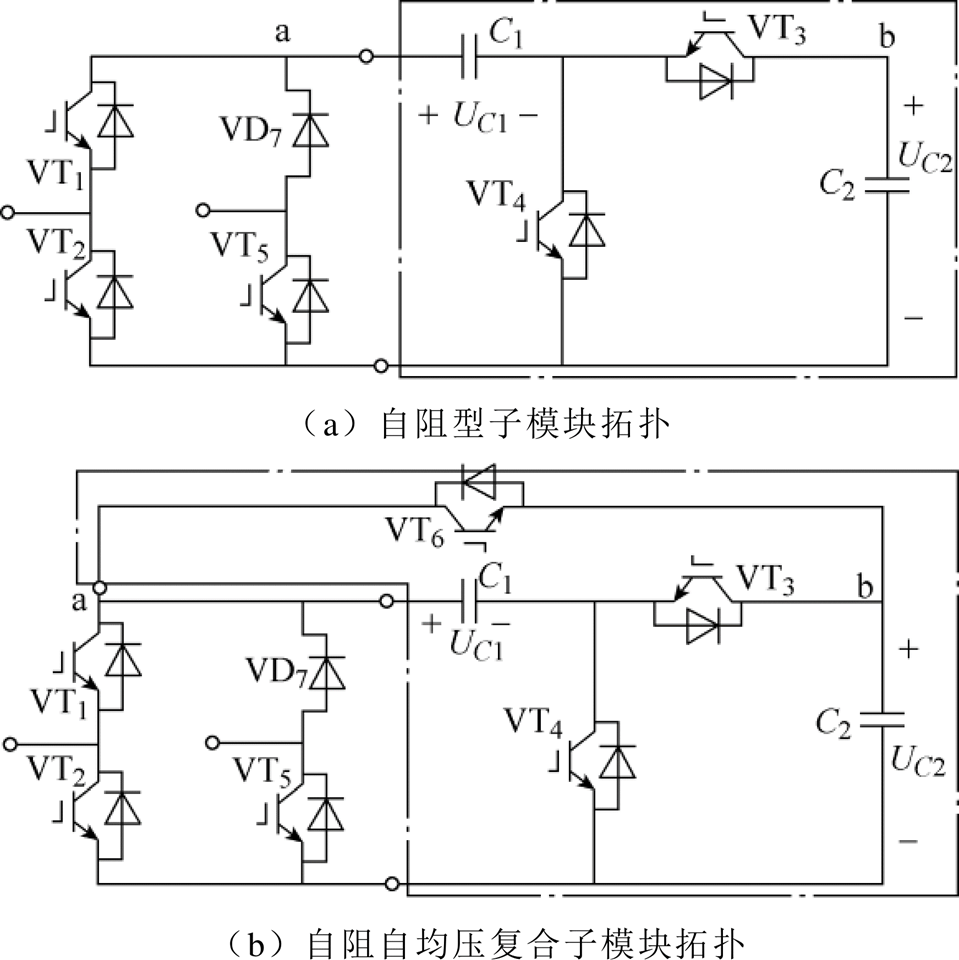

表1 自阻自均压复合子模块拓扑开关

Tab.1 Switch states of SBBCSM

模式VT1VT2VT3VT4VT5VT6输出电压 1100110UC1 2101010UC1+UC2 30100100 4100011UC2 5100111UC1(UC2) 6000000±(UC1+UC2) 7000101±UC1(UC2)

从电路角度,如果在工作触发脉冲配合下,通过附加电路使电容C1和C2处于并联状态,则电容储存能量能够在电容电压差下实现转移,从而达到电压均衡效果。根据图2a,在VT4导通,VT3截止时,C1和C2负极相连等电位。根据并联电路端电压相等的特点,只需a、b两端存在一条额外路径,使电容C1、C2正极相连,就能够实现两个电容物理上的并联连接。考虑到附加电路不应影响到子模块正常输出,则由附加全控器件VT6,构造了如图2b所示的具有内部自均压功能的复合拓扑,即自阻自均压复合子模块(Self-Block and Balance Composite SM, SBBCSM)拓扑,解决了UC2电平输出问题。其开关逻辑见表1,其中工作模式6、7分别属于直流故障下不同闭锁逻辑。

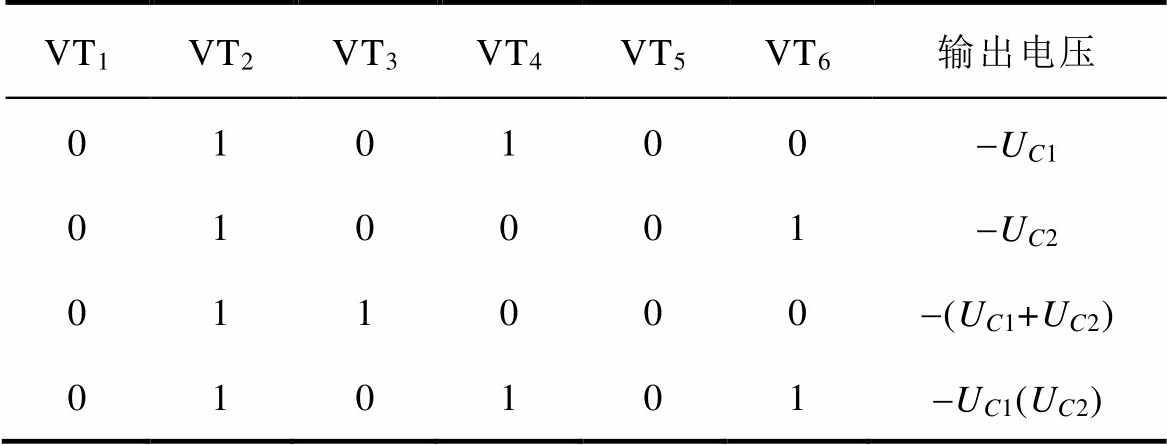

自阻型拓扑对直流故障电流抑制能力的大小取决于闭锁后桥臂中充电电容数量,数量越多则能够提供的二极管反向截止电压越大,从故障回路中吸收的能量也越多,从而加速故障电流抑制。自阻自均压复合子模块拓扑闭锁电路如图3所示。直流侧故障闭锁后,子模块等效电路如图3a所示。对于双向桥臂电流,电容C1和C2串联充电,输出UC1+UC2,满足直流故障电流抑制条件。根据工作开关表1,如果故障期间只保留VT6和VT4导通,而闭锁其余IGBT,则得到两条如图3b所示的并联故障抑制路径。此时电容C1和C2并联充电,且功率器件VT4和VT6只承担了短路电流的1/2。如果考虑电流裕度,理论上故障期间可以不闭锁VT4和VT6,达到并联抑制效果。虽然子模块数量N相同,由于SBBCSM串联闭锁电容数量大于并联闭锁模式,所以并联故障电流衰减时间要长于串联闭锁。

通过对SBBCSM正常工作时输出电平路径分析可知,当两个电容C1和C2处于串联输出状态时,VT2两端电压为UC1+UC2;而当桥臂电流小于零,直流故障子模块闭锁抑制时,VT1和VT5两端电压为UC1+UC2。虽然从功率器件电压裕度考虑,理论上能够短时承受2倍额定反向电压,但考虑到可靠性,仍需解决其过电压问题。根据电路各部分功能,SBBCSM拓扑可等效为改进全桥和开关电容网络两部分,自阻自均压复合子模块拓扑如图4所示,开关电容网络中功率器件不存在过电压问题。为解决改进全桥过电压问题,一种思路是功率器件额定电压选取为开关电容网络功率器件电压的2倍,此时SBBCSM能够提供最大桥臂反向偏置电压,同时在零电平输出时,导通路径中功率器件数量较少(2个,而对于CDSM或SDSM为3个),但这会带来器件成本增加的问题;由于VT1和VT5过电压问题是闭锁后电容C1、C2串联充电导致,因此另外一种思路是利用并联抑制模式或本文后面研究的非闭锁抑制策略解决其过电压问题。而对于VT2,则可采用两个低压功率器件串联代替,此时所需功率器件数量较少,但零电平输出时导通路径中功率器件数量与CDSM和SDSM相同,同时所提供的桥臂反向偏置电压也相应降低一半。

图3 自阻自均压复合子模块拓扑闭锁电路

Fig.3 Blocking circuit of SBBCSM

图4 自阻自均压复合子模块拓扑

Fig.4 Structure diagram of SBBCSM

直流侧短路故障将引起电流快速上升和直流母线电压急剧下降,因此系统需实时采集直流侧电压、电流信号,当监测到直流电流上升到一定限值且电压降低到一定程度后,则可判断是否发生直流短路故障。此时有两种抑制模式可选:模式一串联抑制,如果桥臂电流大于两倍的IGBT电流裕度,为防止VT4、VT6遭受过电流损害,全部闭锁,采用工作逻辑模式6,电流路径如图3a所示,为串联抑制模式;模式二并联抑制,如果故障电流未超出IGBT电流裕度,则采取工作逻辑模式7,此时闭锁后电路如图3b所示,C1和C2处于并联充电状态,即并联抑制模式。

对于模式二,由于电容并联连接,所以流过电流为短路电流的1/2,直流母线间反向电压较低,但电容电压略高。由于串联抑制储能单元等效数量大于并联抑制,模式一抑制速度和电容电压变化幅度都优于模式二,但故障抑制期直流侧反向电压也较大。

系统闭锁是最简单、快速的直流故障抑制策略,但系统长时间闭锁可能会造成电容电压发散,导致交流断路器动作[14]。如果利用控制作用将输出直流电压、电流降低为零,同样可实现直流故障抑制。通过调整VT5开关状态,子模块在桥臂电流小于零时具有负电平输出能力,而其正电平输出则不受电流方向约束,桥臂电流为负时,自阻自均压复合子模块拓扑开关见表2。

表2 自阻自均压复合子模块拓扑开关

Tab.2 Switch states of SBBCSM

VT1VT2VT3VT4VT5VT6输出电压 010100-UC1 010001-UC2 011000-(UC1+UC2) 010101-UC1(UC2)

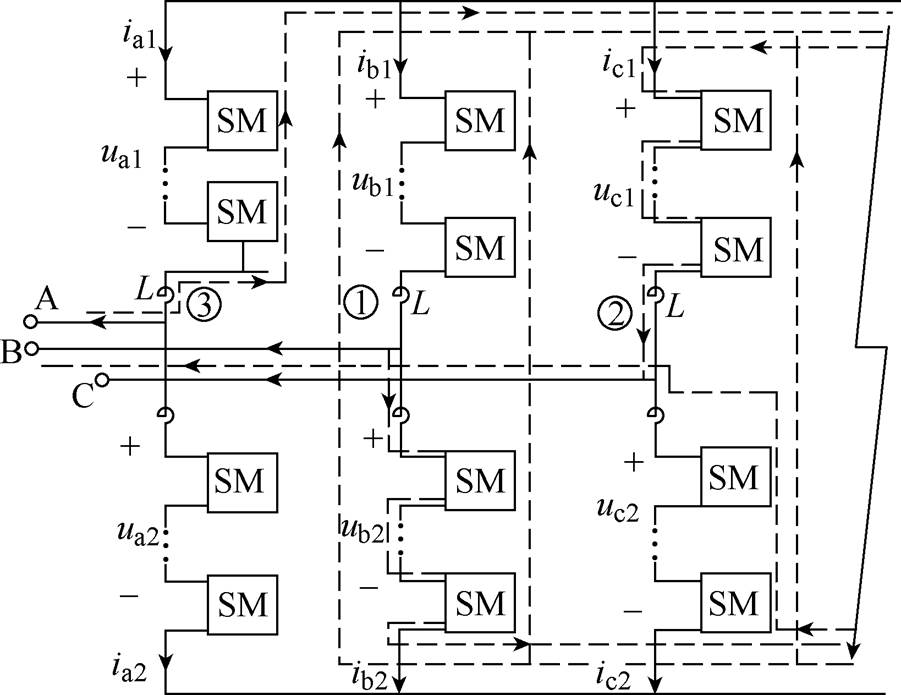

当直流侧发生两极短路故障时,按照桥臂电流方向将短路路径分为如图5所示的SBBCSM-MMC直流故障三种路径。故障期间以抑制故障电流为主要控制目标,控制系统有功功率、无功功率指令为零,此时交流侧馈入电流为零,上、下桥臂电流相同且流向直流侧短路点,形成图5所示路径①。桥臂电流小于零,具有正、负电平输出条件,改变VT5开关状态,调节上、下桥臂输出电平,使其满足大小相等、极性相反,则可以实现故障电流抑制效果。此种抑制虽然类似文献[22]中旁路抑制,桥臂电流以指数规律自然衰减,但却能避免旁路抑制所导致的交流侧三相短路。如果考虑无功支撑,则存在②和③两种路径,交流电流被上、下桥臂均分。忽略桥臂环流,上、下桥臂电流大小相等相位相反。对于路径②,桥臂电压方程为

图5 SBBCSM-MMC直流故障

Fig.5 DC fault circuit of SBBCSM-MMC

(1)

(1)式中,j∈(a, b, c)。由于上、下桥臂电抗电压相互抵消,所以为实现直流侧输出电压为零,上、下桥臂子模块输出电压极性相反。但由于桥臂电流大于零,桥臂子模块只能输出正电平,电压、电流同相位,则此种情况不能输出无功功率,只能闭锁子模块将正向电流抑制为零。而对于路径③,上、下桥臂电流都小于零,此时桥臂子模块可以输出正、负电平,具有全桥子模块工作特性,因而可以输出无功功率。由于直流电流为三相桥臂电流之和,而桥臂电流具有半波特性,因此不同于全桥抑制特性,故障抑制期间直流电流不为零,大小与输出无功功率有关。

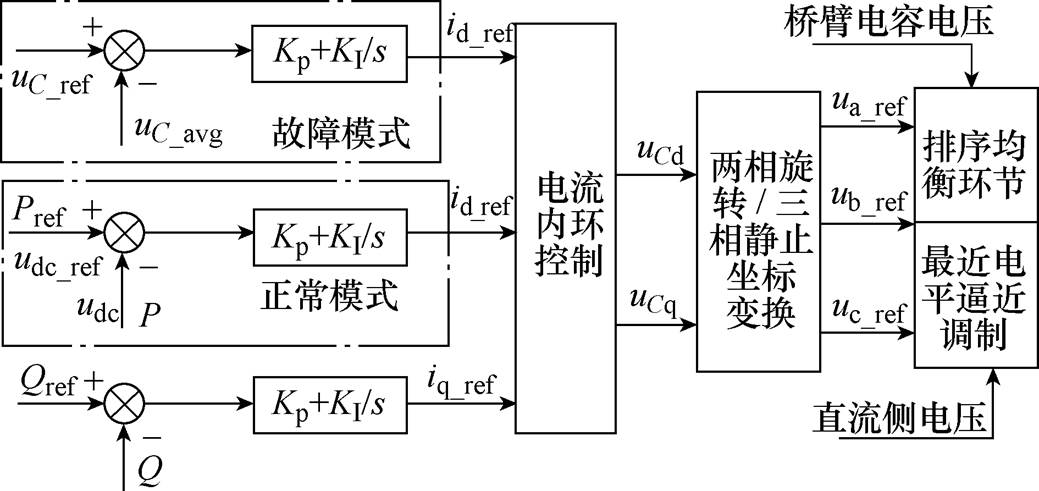

借鉴全桥拓扑直流故障控制思想,本文设计直流故障控制逻辑如图6所示[21]。其中uC_ref 、uC_avg分别为电容电压参考值和三相桥臂电容电压平均值。在故障期间可设置无功指令为零,或根据系统要求运行于STATCOM模式,给交流电网提供无功支持。

图6 SBBCSM-MMC控制逻辑

Fig.6 Control circuit of SBBCSM-MMC

由于SBBCSM内部电容C1和C2可以利用模式5实现均压效果,因此只需对一半电容电压排序即可,即参与排序的电容电压数量正好是复合子模块数量,从而降低排序算法压力。在确定开通电平数量后,利用电压均衡算法实现开通模块选择。首先定义子模块双一电平输出、单一电平输出和零电平输出三种状态分别为双触发工作状态、单触发工作状态和零电平触发工作状态。

为实现电容电压内部均衡,将SBBCSM等效为一个单电平子模块,即单一电平输出优先模式。这时需要考虑输出电平数量与子模块数量关系。当投入电平数量k<N(N为SBBCSM数量)时,每个SBBCSM单电平输出即可满足总电平要求,则投入k个C1电容,工作于单触发状态,并启动均压电路。而其余N-k个子模块处于旁路。

当投入子模块数量k>N时,SBBCSM单电平输出不能满足总电平输出要求。此时需要k-N个SBBCSM工作于双触发工作状态,应闭锁均压电路,此时输出电平为2(k-N)。而2N-k个SBBCSM保持一电平输出即单触发工作状态,输出2N-k个电平并启动均压电路,从而保证k个电平输出。

根据图2b所示电路,当采用单触发工作状态时,此时子模块内部两个电容并联输出,电容主要与外电路进行能量交换,两者之间环流比较小。而当采用零电平触发时,由于子模块处于旁路,两个电容与外电路之间没有能量交换。如果彼此之间电压差较大,可能会导致均压回路电流较大,此时可以考虑加入限流元件进行限流。

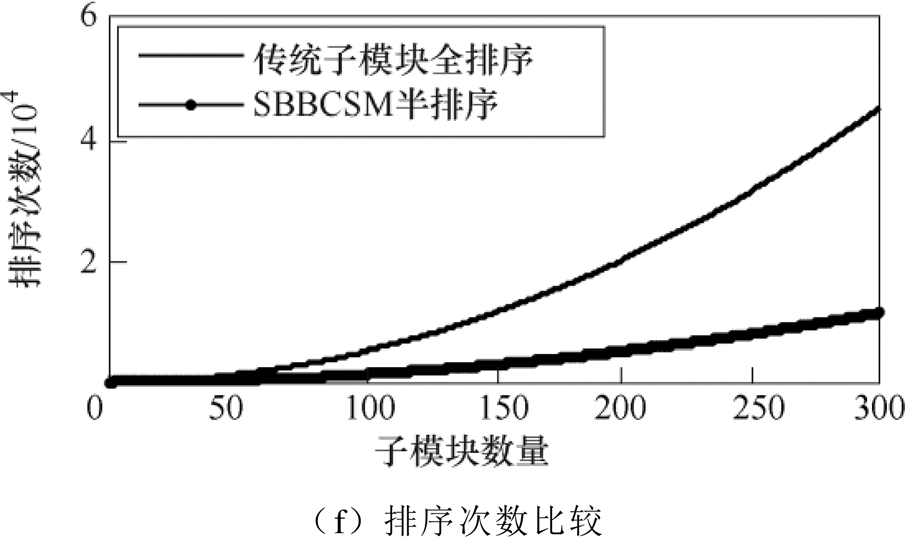

电容电压均衡需要对电容电压实时排序,采用冒泡排序算法。算法包括两层循环,外层循环执行M-1次,内层循环最多时执行M次,最少时执行1次,平均执行(M+1)/2次,其中M为电容个数。循环体内的比较、交换操作约执行(M-1)(M+1)/2= (M2-1)/2次。按照计算复杂度原则,其复杂度为O(M2)。而对于SBBCSM而言,由于只需对一半电容电压排序,所以执行次数为(0.5M-1)(0.5M+1)/2= (0.25M2-1)/2,其复杂度为O((0.5M)2),可将计算量近似降低至原来的0.25。

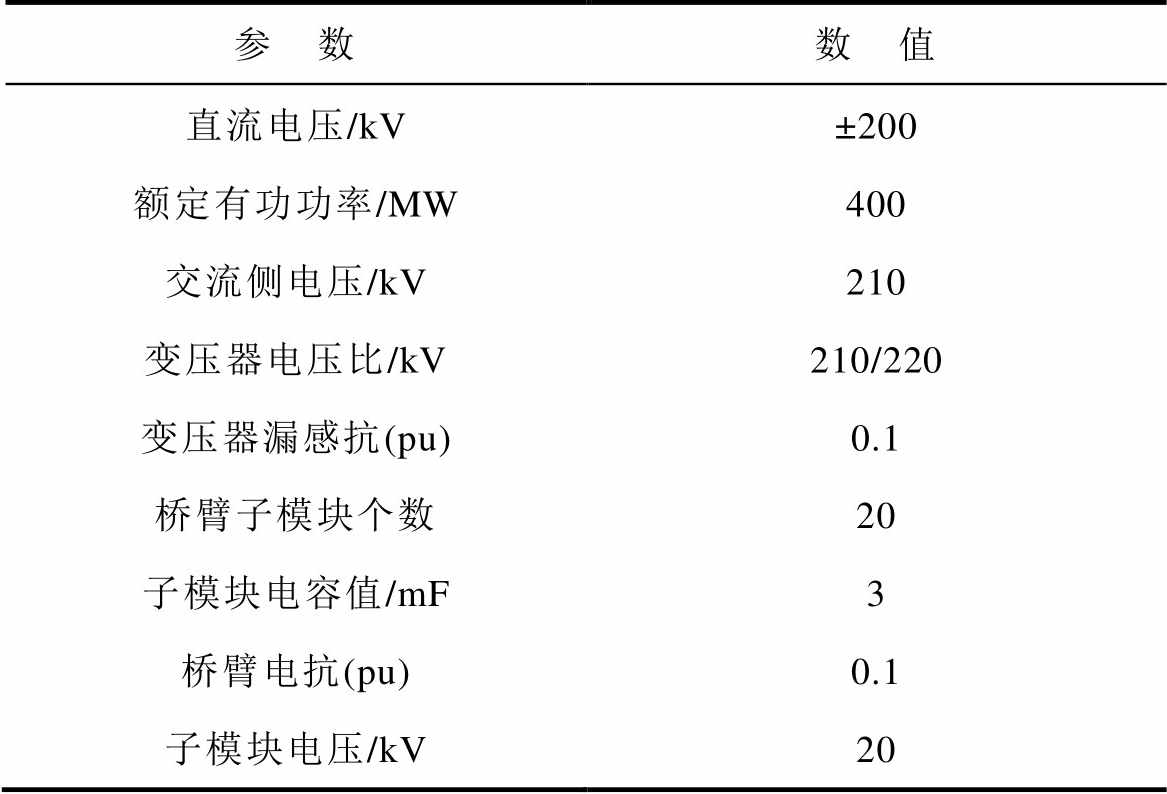

本文在PSCAD/EMTDC搭建了如图7所示的MMC-HVDC仿真模型,对控制策略和SBBCSM拓扑故障抑制特性进行仿真验证,系统参数见表3。1s时系统在距离两端换流站50km处发生两极永久短路故障。

图7 两端仿真模型

Fig.7 Two terminal simulating mode

表3 电路参数

Tab.3 Main circuit parameters

参 数数 值 直流电压/kV±200 额定有功功率/MW400 交流侧电压/kV210 变压器电压比/kV210/220 变压器漏感抗(pu)0.1 桥臂子模块个数20 子模块电容值/mF3 桥臂电抗(pu)0.1 子模块电压/kV20

图8为SBBCSM均压效果。从图8a可以看出,利用电容并联关系,实现了SBBCSM内部电容C1、C2电压的均衡。图8b、图8c是电容参数差异对电容电压的影响(±30%变化)波形。在不具有自均压功能时,电容电压之间存在差异(由于排序均衡算法在一定程度上也可降低差异影响,因而差异不是很明显);而均压功能可以消除电容参数变化对电压的影响,达到均衡效果。图8c中,之所以三条电压曲线没有完全重合主要是因为在C1、C2串联充电时,电流相同而参数不一致导致,而在其他输出状态时则能保证C1、C2并联,消除二者的电压差异。

图8 SBBCSM均压效果

Fig.8 Voltage balance effect of SBBCSM

从图8d、图8e可以看出,由于在零电平和一电平输出时,两个电容处于并联均压状态,所以VT6和VT4电流基本重合。而在双电平输出时,均压功能闭锁,VT6和VT4电流为零。虽然电容参数发生变化会导致串联输出期间电容电压出现差异,但由于零电平和一电平均压效果,对电容电压差异影响较小,因而流过VT6和VT4的电流差异不大。

图8f是每相桥臂排序次数随子模块数量变化曲线,随着子模块数量增加,SBBCSM可以大幅度降低排序次数,从而缓解子模块数量过多导致的电容电压排序均衡算法排序压力。

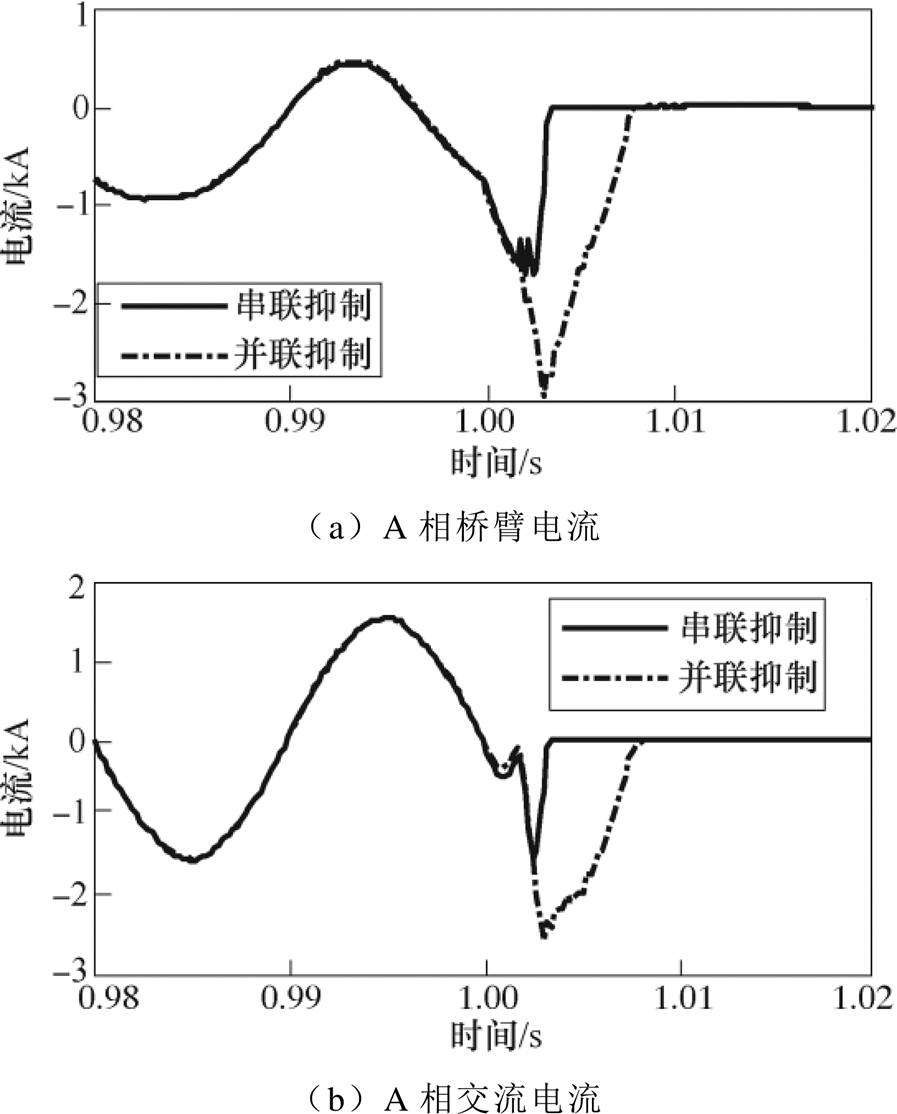

图9是串联和并联直流侧故障抑制效果比较仿真。由于串联抑制模式下每个SBBCSM中两个电容类似SDSM处于串联充电状态,而并联抑制模式中两个电容类似CDSM处于并联充电状态,所以桥臂中等效电容数量存在差异,串联抑制故障电流衰减到零所需时间少,如图9a~图9c所示。同时从图9d、图9e所示上桥臂电容电压可以看出,由于充电时间长短不同,电容电压也有所不同。虽然串联抑制效果要好,但是从图9f所示直流母线电压来看,故障抑制期间,串联抑制的反向电压是并联抑制的两倍,可能会存在暂时过电压问题,因此在抑制时间满足要求的前提下,可以考虑采用并联抑制。

图9 串联、并联直流故障抑制效果比较

Fig.9 DC link fault suppression with series and shunt blocking effect comparison

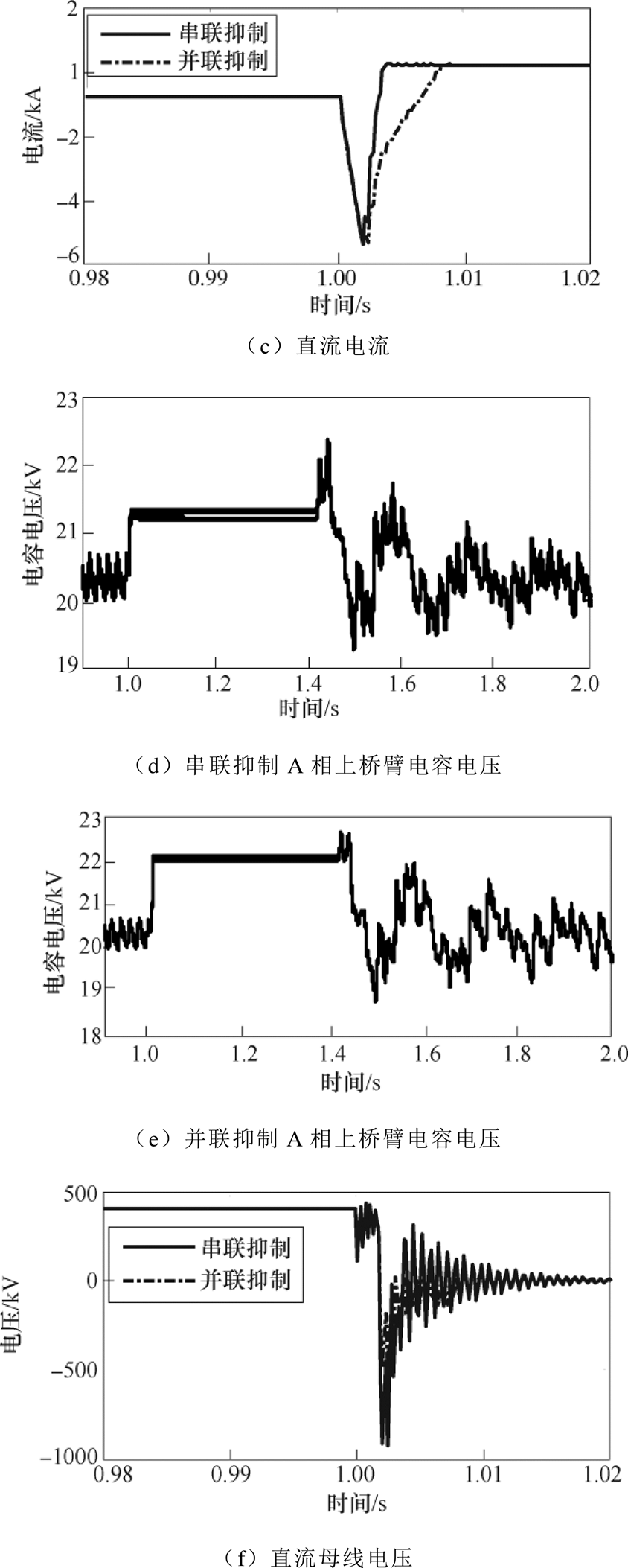

图10和图11分别是故障期间不考虑无功支持和STATCOM运行模式时仿真波形。故障抑制期间,上、下桥臂交替输出大小相等、极性相反电压,则直流电压、电流为零。故障期间换流器输出有功功率为零,但换流器会与交流电网交换少量有功功率以维持电容电压均衡,在无功功率指令为零时,交流侧电流基本为零。

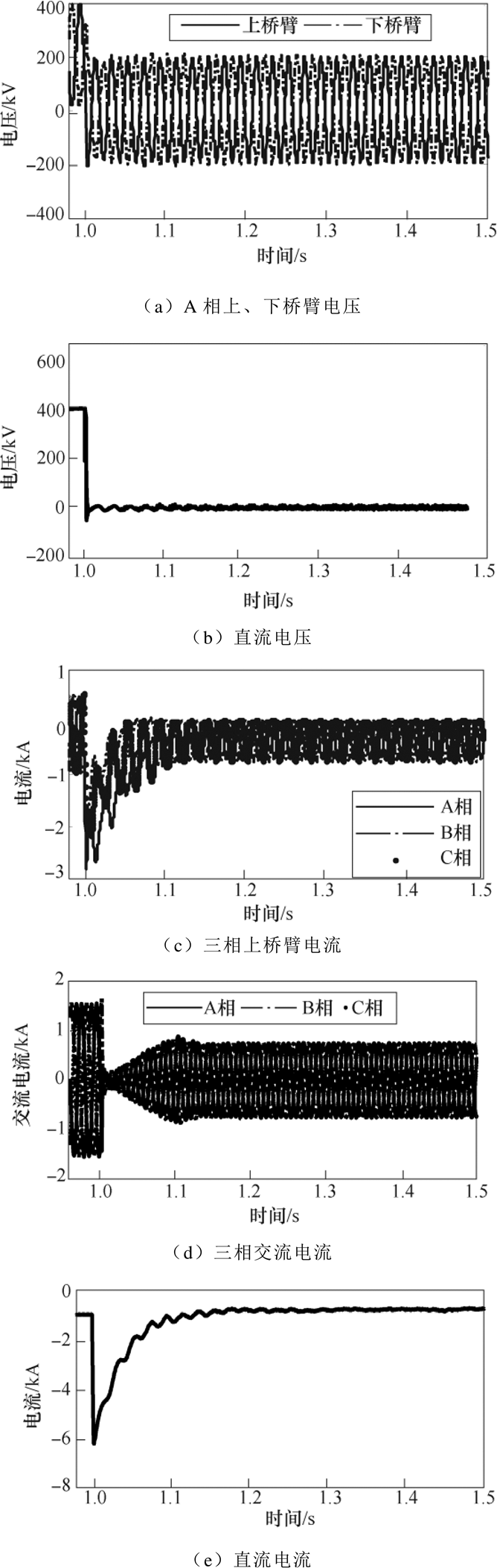

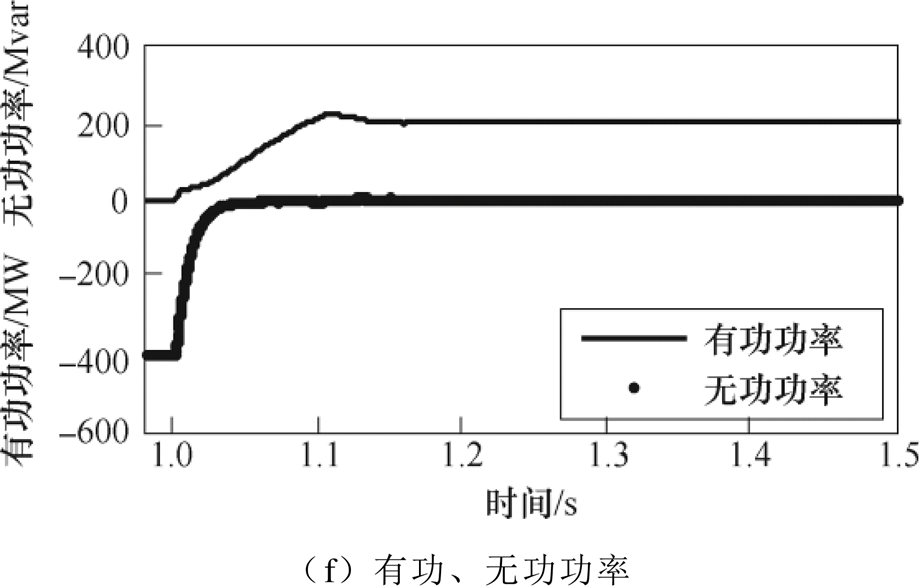

STATCOM模式直流故障非闭锁抑制效果如图11所示,当桥臂电流正向时,投入桥臂中所有子模块,且电容处于充电状态,因而类似闭锁抑制,桥臂电流基本为零,则三相桥臂电流只存在于桥臂电流小于零期间,呈现半波特性,如图11c所示。直流电流为三相桥臂电流之和,从而不对称三相桥臂电流导致故障期间直流电流不为零,如图11e所示,但从图11d、图11e可以看出,非闭锁抑制降低了故障期间交流和直流侧的过电流程度,起到了限制故障电流的作用。

图10 非STATCOM模式直流故障非闭锁抑制效果

Fig.10 DC link fault unlock blocking effect without STATCOM

图11 STATCOM模式直流故障非闭锁抑制效果

Fig.11 DC link fault unlock blocking effect with STATCOM

针对模块化多电平换流器应用于直流输电领域时双极短路故障电流抑制和子模块电容均压问题,本文提出了一种具有直流故障阻断和内部电容自均压能力的自阻自均压子模块拓扑。在不改变现有控制策略的基础上,该拓扑利用钳位电路和开关电容网络实现了多电平输出和直流故障抑制。通过内部并联自均压电路实现了均压功能,将参与排序均衡控制的子模块数量降低为一半,缓解了子模块数量过多计算量和数据采集压力较大的问题。同时该拓扑还可以根据直流故障导致的过电流程度,选择不同抑制模式,以获得不同抑制效果。

参考文献

[1] 徐政, 薛英林, 张哲任. 大容量架空线柔性直流输电关键技术及前景展望[J]. 中国电机工程学报, 2014, 34(19): 5051-5063.

Xu Zheng, Xue Yinglin, Zhang Zheren. VSC-HVDC technology suitable for bulk power overhead line transmission[J]. Proceedings of the CSEE, 2014, 34(19): 5051-5063.

[2] 苏见燊, 郭敬东, 金涛. 柔性直流电网中直流故障特性分析及线路故障重启策略[J]. 电工技术学报, 2019, 34(1): 352-359.

Su Jianshen, Guo Jingdong, Jin Tao. DC fault characteristics and line fault recovery strategy in flexible DC power network[J]. Transactions of China Electrotechnical Society, 2019, 34(1): 352-359.

[3] 魏晓光, 高冲, 罗湘, 等. 柔性直流输电网用新型高压直流断路器设计方案[J]. 电力系统自动化, 2013, 37(15): 95-102.

Wei Xiaoguang, Gao Chong, Luo Xiang, et al. A novel design of high-voltage DC circuit breaker in HVDC flexible transmission grid[J]. Automation of Electric Power System, 2013, 37(15): 95-102.

[4] Marquardt R. Modular multilevel converter topo- logies with DC-short circuit current limitation[C]// IEEE 8th International Conference on Power Electro- nics and ECCE Asia (ICPE & ECCE), Jeju, South, Korea, 2011: 1425-1431.

[5] 薛英林, 徐政. C-MMC直流故障穿越机理及改进拓扑方案[J]. 中国电机工程学报, 2013, 33(21): 63-70.

Xue Yinglin, Xu Zheng. DC fault ride through mechanism and improved topology scheme of C- MMC[J]. Proceedings of the CSEE, 2013, 33(21): 63- 70.

[6] 李建国, 刘文华, 王久和. 基于LCC和双钳位MMC混联高压直流输电的实验[J]. 电工技术学报, 2018, 33(16): 3678-3687.

Li Jianguo, Liu Wenhua, Wang Jiuhe. Experiment of hybrid high voltage direct current transmission based on LCC and clamp double sub module MMC[J]. Transactions of China Electrotechnical Society, 2018, 33(16): 3678-3687.

[7] 张建坡, 赵成勇. 模块化多电平换流器改进拓扑结构及其应用[J]. 电工技术学报, 2014, 29(8): 173-180.

Zhang Jianpo, Zhao Chengyong. The improved topology of modular multilevel converter and appli- cation[J]. Transactions of China Electrotechnical Society, 2014, 29(8): 173-180.

[8] Qin Jiangchao, Maryam Saeedifard. Hybrid design of modular multilevel converters for HVDC systems based on various sub module circuits[J]. IEEE Transactions on Power Delivery, 2015, 32(3): 1-10.

[9] 向往, 林卫星, 文劲宇. 一种能够阻断直流故障电流的新型子模块拓扑及混合型模块化多电平换流器[J]. 中国电机工程学报, 2014, 34(29): 5171-5180.

Xiang Wang, Lin Weixing, Wen Jinyu. A new topology of sub-modules with DC fault current blocking capability and a new type of hybrid MMC converter[J]. Proceedings of the CSEE, 2014, 34(29): 5171-5180.

[10] 孔明, 汤广福, 贺之渊. 子模块混合型MMC-HVDC直流故障穿越控制策略[J]. 中国电机工程学报, 2014, 34(30): 5343-5351.

Kong Ming, Tang Guangfu, He Zhiyuan. A DC fault ride-through strategy for cell-hybrid modular multi- level converter based HVDC transmission systems[J]. Proceedings of the CSEE, 2014, 34(30): 5343-5351.

[11] 张建坡, 颜湘武, 田新成. MMC-HVDC混合阻断拓扑直流故障抑制[J]. 电工技术学报, 2017, 32(10): 61-68.

Zhang Jianpo, Yan Xiangwu, Tian Xincheng. MMC- HVDC hybrid blocking topologies for suppressing DC fault[J]. Transactions of China Electrotechnical Society, 2017, 32(10): 61-68.

[12] 杨晓峰, 李泽杰, 薛尧. 增强型柔性逆阻模块化多电平换流器的故障阻断特性分析[J]. 电工技术学报, 2019, 34(10): 1-9.

Yang Xiaofeng, Li Zejie, Xue Yao. Fault blocking performance analysis of enhanced flexible reverse blocking multilevel modular converter[J]. Transa- ctions of China Electrotechnical Society, 2019, 34(10): 1-9.

[13] Zhang Jianpo, Cui Diqiong, Tian Xincheng. Hybrid double direction blocking sub-module for MMC- HVDC design and control[J]. Journal of Power Electronics, 2019, 19(6): 1486-1495.

[14] 罗永捷, 李耀华, 李子欣. 采用全桥型MMC-HVDC直流短路故障穿越控制保护策略[J]. 中国电机工程学报, 2016, 36(7): 1993-2003.

Luo Yongjie, Li Yaohua, Li Zixin. DC short-circuit fault ride-through control strategy of full-bridge MMC-HVDC systems[J]. Proceedings of the CSEE, 2016, 36(7): 1993-2003.

[15] 管敏渊, 徐政. MMC型VSC-HVDC 系统电容电压的优化平衡控制[J]. 中国电机工程学报, 2011, 31(12): 9-14.

Guan Minyuan, Xu Zheng. Optimized capacitor voltage balancing control for modular multilevel converter based VSC-HVDC system[J]. Proceedings of the CSEE, 2011, 31(12): 9-14.

[16] 荣飞, 陈盼庆, 黄守道. 一种减少电压互感器的模块化多电平换流器分组控制策略[J]. 电工技术学报, 2017, 32(18): 186-195.

Rong Fei, Chen Panqing, Huang Shoudao. Sub- module grouping strategy for reducing the number of voltage sensors in modular multilevel converters[J]. Transactions of China Electrotechnical Society, 2017, 32(18): 186-195.

[17] 岳雨霏, 徐千鸣, 罗安. 模块化多电平换流器单传感器电容电压平衡控制策略[J]. 电工技术学报, 2018, 33(16): 3663-3675.

Yue Yufei, Xu Qianming, Luo An. Capacitor voltages balancing control strategy with single sensor measurement for modular multilevel converter[J]. Transactions of China Electrotechnical Society, 2018, 33(16): 3663-3675.

[18] 罗德荣, 贺锐智, 黄守道. 模块化多电平变流器子模块电压分组检测中过电压防护策略[J]. 电工技术学报, 2019, 34(14): 2957-2969.

Luo Derong, He Ruizhi, Huang Shoudao. Over- voltage protection strategy for sub-module of modular multilevel converter with reduced sensors[J]. Transactions of China Electrotechnical Society, 2019, 34(14): 2957-2969.

[19] Gao Congzhe, Jiang Xinjian, Li Yongdong, et al. A DC-link voltage self-balance method for a diode- clamped modular multilevel converter with minimum number of voltage sensors[J]. IEEE Transactions on Power Electronics, 2013, 28(5): 2125-2139.

[20] 刘航, 赵成勇, 周家培, 等. 具备自均压能力的模块化多电平换流器拓扑[J]. 中国电机工程学报, 2017, 37(10): 1-10.

Liu Hang, Zhao Chengyong, Zhou Jiapei, et al. Novel topology of modular multilevel converter with voltage self-balancing ability[J]. Proceedings of the CSEE, 2017, 37(10): 1-10.

[21] 尹太元, 王跃, 段国朝. 基于零直流电压控制的混合型MMC-HVDC直流短路故障穿越策略[J]. 电工技术学报, 2019, 34(1): 343-351.

Yin Taiyuan, Wang Yue, Duan Guozhao. Zero DC voltage control based DC fault ride-through strategy for hybrid modular multilevel converter in HVDC[J]. Transactions of China Electrotechnical Society, 2019, 34(1): 343-351.

[22] Li Xiaoqian, Song Qiang, Liu Wenhua. Protection of nonpermanent faults on DC overhead lines in MMC- based HVDC systems[J]. IEEE Transactions on Power Delivery, 2013, 28(1): 483-490.

Self-Block and Voltage Balance Modular Multilevel Converter Sub Module Topology and Control

Abstract High-voltage DC transmission based on modular multilevel converters (MMC) needs to deal with possible short-circuit faults on the DC line and the capacitor voltage balance problem caused by too many sub modules. To ensure sub modules working independently as a constraint, the paper first analyzes the full bridge topology fault suppression mechanism. Then a sub module topology with DC link fault blocking and internal capacitor balance ability is designed based on the fault clamp circuit and switch capacitor multilevel ideas. Thus, it will not only meet the self-suppression requirement but also reduce the number of capacitors participating in the sort balancing algorithm to half. What is more, for the self blocking and voltage balance topology, the DC link fault suppression characteristics under two different blocking modes, i.e. self-balancing control strategy based on the voltage level output priority and the unblocking DC link fault suppression strategy, are also studied. Finally, a PSCAD-EMTDC simulation model is used to verify the effectiveness of the proposed topology of DC link fault suppression and control strategy.

keywords:Modular multilevel converter, DC fault suppression, self-block and balance sub module topology, unblocking suppression

中图分类号:TM46

DOI: 10.19595/j.cnki.1000-6753.tces.190751

河北省自然科学基金资助项目(E2019502123)。

收稿日期 2019-06-21

改稿日期 2019-10-28

张建坡 男,1973年生,博士,讲师,主要研究方向为高压直流输电与柔性输配电技术。E-mail: zhangjianpo@126.com(通信作者)

崔涤穹 男,1997年生,硕士研究生,研究方向为高压直流输电与柔性输配电技术。E-mail: 18730293867@163.com

(编辑 陈 诚)