图1 输入、输出功率的理论波形

Fig.1 Theoretical waveforms of input power and output power

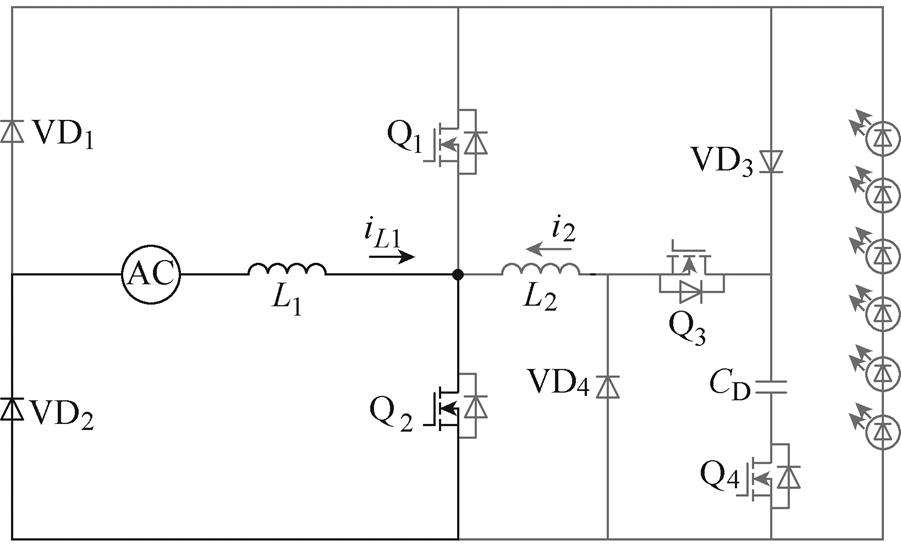

摘要 为消除电解电容对高亮度发光二极管(HB-LEDs)寿命的影响,并迎合轻量化设计理念,提出一种具有功率解耦能力的单级无桥式虚拟三端口整流器。该拓扑采用路径优化的方式缩短能量传输路径,并通过功率器件共享的方式实现多级整合,极大地提升了器件利用率与电路功率密度;虚拟第三端口专用于功率解耦,从而有效缓解系统对大电容的依赖,为薄膜电容替代电解电容提供可能。此外,所提整流器可实现功率因数校正(PFC),控制单元简单、易行。该文分析该整流器的工作原理,详述关键电路的参数设计,并通过额定输出功率为90W的实验样机验证了该整流器的优越性。

关键词:电解电容 功率因数校正(PFC) 功率解耦 三端口整流器

目前,全球照明损耗约占能源损耗的五分之一[1]。开发高效、节能、低成本的照明灯具依然是解决世界能源问题的重要途径。高亮度发光二极管(High- Brightness Light-Emitting Diodes, HB-LEDs)具有光效高、性能好、寿命长、环保和体积小等优点,近年来已逐渐成为照明领域的主流产品。因发光二极管(LED)本身不能直接与交流源相连接,常采用整流器作为中间环节[2-3]。

现有整流器按能量传递方式可大致分为单级、两级和多级三大类[4],前级常用于功率因数校正(PowerFactor Correction, PFC),以满足IEC 61000-3-2、EnergyStar[5]等标准,后级为DC-DC变换器以提供负载所需的驱动电流。两/多级整流器具有功率因数高、输出控制简单等优点,但成本高、效率低。鉴于此,文献[6-7]提出一种基于Fly-Buck的主电路拓扑,但其必须工作在断续导通模式(Discontinuous Conduction Mode, DCM)下才可实现PFC,且存在较大的输出纹波,因此只能应用于低功率场所。文献[8]提出一种Boost型整流器,大大降低了纹波电流,同时解决了开关管电压应力过高等问题;但大量磁性器件的存在降低了电路整体功率密度。文献[9]提出一种级联桥式整流器,即前级Boost和后级LLC谐振变换器,实现了高功率因数(Power Factor, PF)和零电压软开关(Zero Voltage Switching, ZVS)。但现有的高频桥式整流器转换效率优化困难,并且PFC工作在连续导通模式(Con- tinuous Conduction Mode, CCM)下,极大地增加了整流二极管的损耗。鉴于此,文献[10]提出一种基于Buck-Boost变换器的两相交错级联型拓扑,以满足单级能量传输需求。另外,文献[11]提出一种基于Buck-Flyback的单级无桥式拓扑,由于减少了整流器件,使得导通损耗降低;且无需电流反馈,控制较为简单。但上述整流器将负载LED与电解电容相匹配,势必导致系统寿命缩短为原先的1/5~1/3[4]。

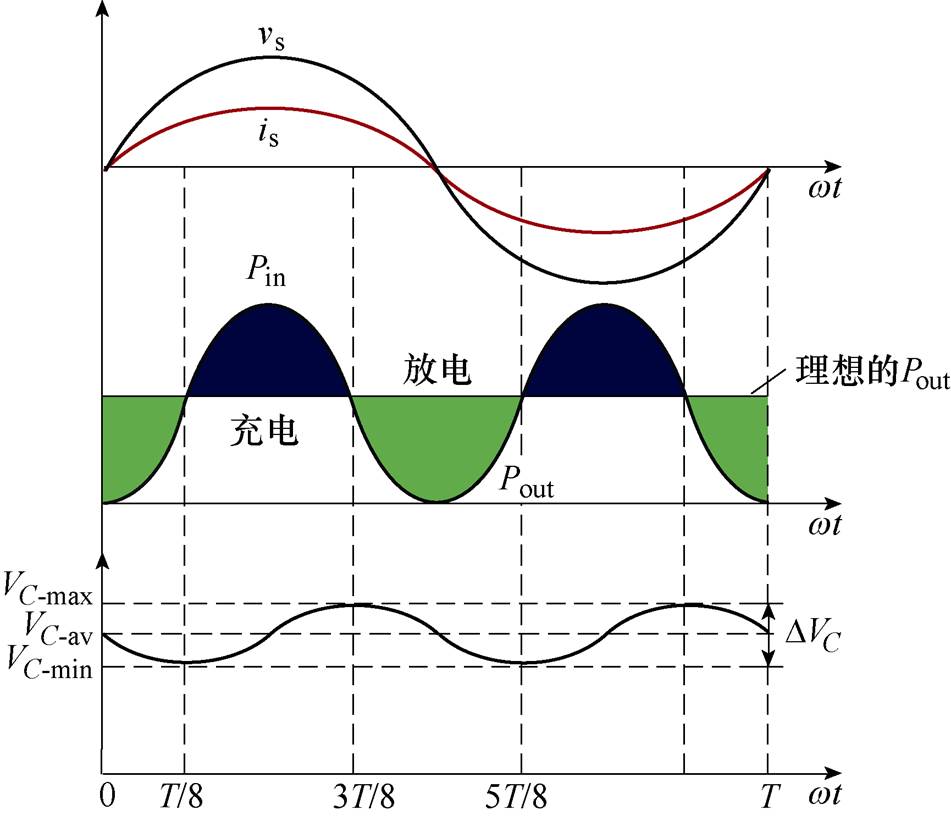

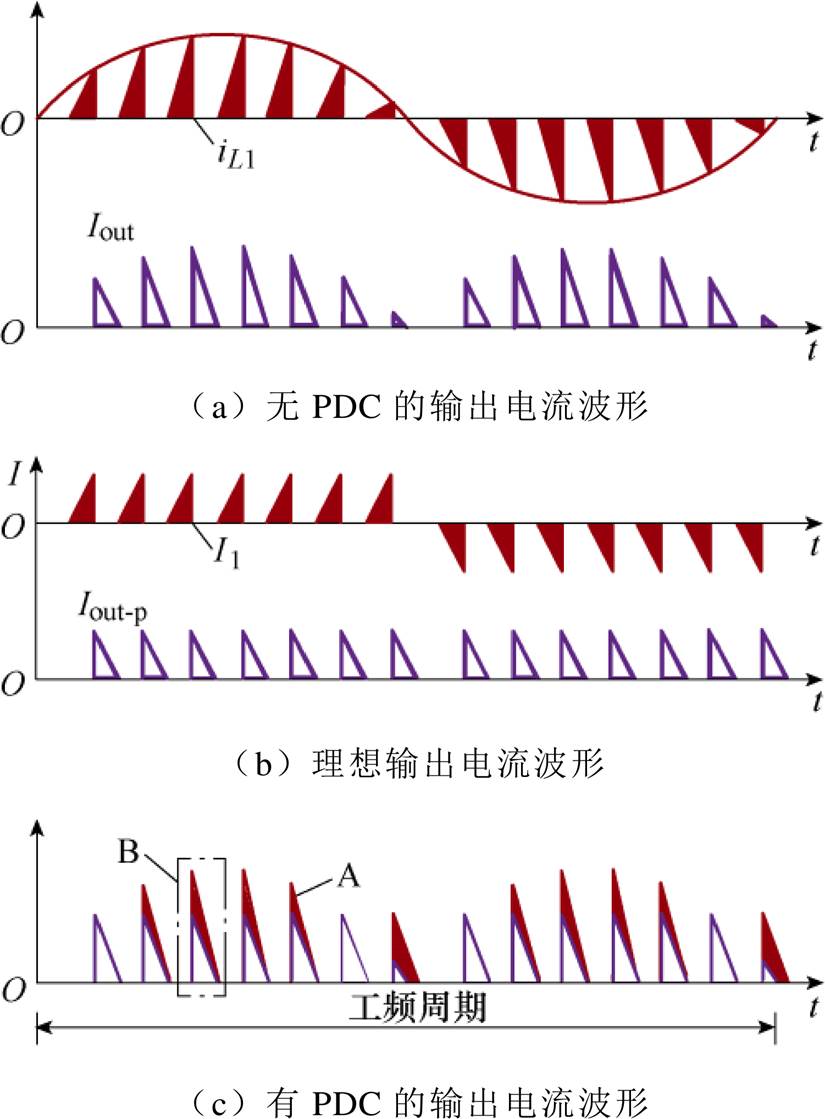

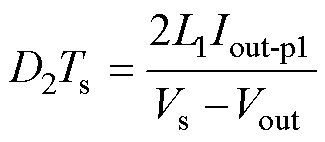

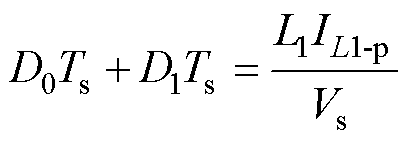

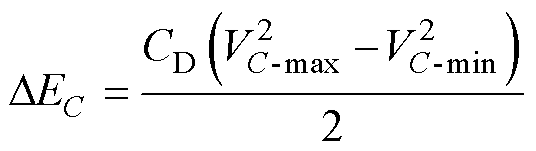

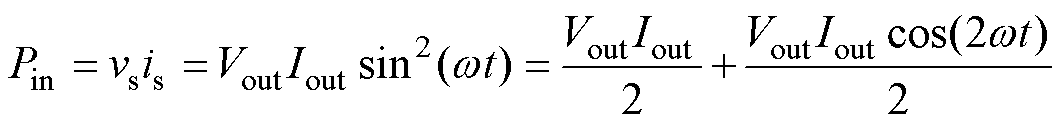

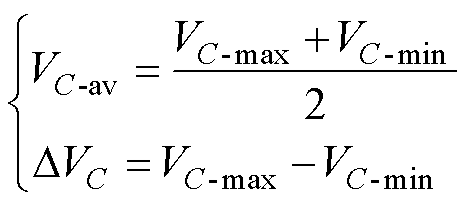

因此,如何消除电解电容是当前研究的另一个热点[12]。但若无电解电容消纳二倍工频的脉动功率,负载势必存在频闪现象,输入、输出功率的理论波形如图1所示。图中,vs、is、Pin和Pout分别为输入电压、输入电流、输入功率和输出功率;VC-av、VC-max和VC-min分别为电容CD两端的平均电压、峰值电压和谷值电压。因此变换器是否采用电解电容已经成为衡量其稳定性的重要标准[13]。

图1 输入、输出功率的理论波形

Fig.1 Theoretical waveforms of input power and output power

根据现阶段学者研究内容,可将消除电解电容的方法分为两类[14-33],即改进控制策略和优化电路拓扑。文献[14-16]从控制策略的角度出发,通过向变换器注入3次和5次谐波,达到对输入电流进行重新塑形的目的,无需引入额外器件。但该方案以牺牲功率因数为代价,仅限于低功率场合应用。此外,国内、外学者已在拓扑的优化上做了大量工作。文献[17-18]提出一种填谷电路和Boost型变换器集成式拓扑。文献[19-20]提出一种利用串联谐振变换器(Series Resonant Converter, SRC)吸收部分脉动纹波的电路结构。但上述方案缺陷为并未完全消除电解电容,电路仍需较大电容平衡输入、输出功率。

为消除对电解电容的依赖,文献[21]提出一种三端口变换器,其核心是将一双向变换器作为第三端口与主变换器串联以消除脉动功率。但相较于传统串联解耦方案,并联解耦处理功率等级较低[22],因此,并联三端口网络传递效率更高。在此基础上演化形成Buck变换器[23-26]、双向Buck-Boost电 路[27-28]、三绕组变压器[29-31]和辅助电路[32-33]用以构建脉动功率流通路径,达到恒定功率输出。此外,文献[34]利用主电路和解耦电路分别使用一个存在较大电压纹波的电容作为主端口和辅助端口,但两电容电压相位相反;最终串联输出,以消除彼此峰值;所需元件少、拓扑结构简单。但上述方案中,文献[27-28]提出的双向Buck-Boost解耦电路工作于升压状态,使得解耦电路输出电压高出输入电压数倍,进而使解耦电路开关器件耐压要求较高,增加了电路成本。文献[31, 33]提出的拓扑不仅造成调制策略更为复杂,而且并未给漏感能量提供吸收回路[22-25, 29-30]。

鉴于已有方案的不足,本文提出了一种虚拟三端口拓扑结构,其中虚拟端口特定用于功率解耦。该拓扑具有元件数少、功率密度高、成本低、效率高等优点。与上述结构相比,所提整流器优点在于:①通过多单元整合和器件共享,消除冗余元件,实现了能量单级变换;②控制上采用高频脉动电流驱动,消除了承受高电压应力的输出电容;③大多情况下,仅两个开关管工作于高频状态,有效降低了导通损耗;④解耦电感可同时用作输出滤波,大大削减了磁损和铁耗。本文理论分析了该整流器的工作原理和调制方式,并通过样机实验验证了理论分析的正确性。

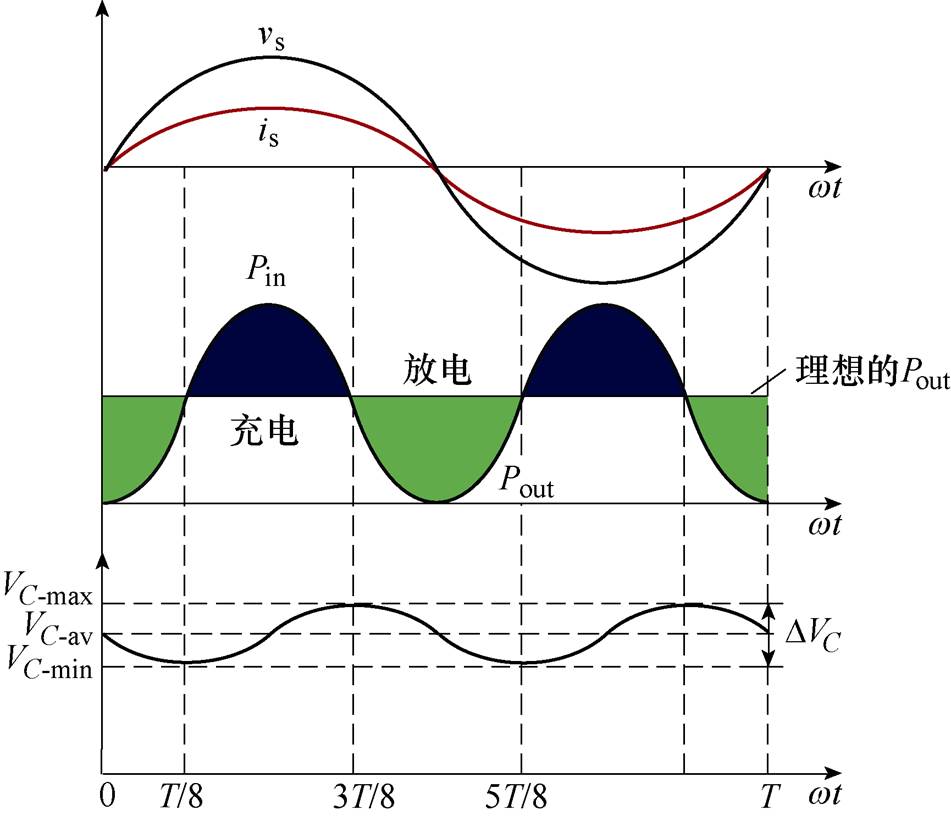

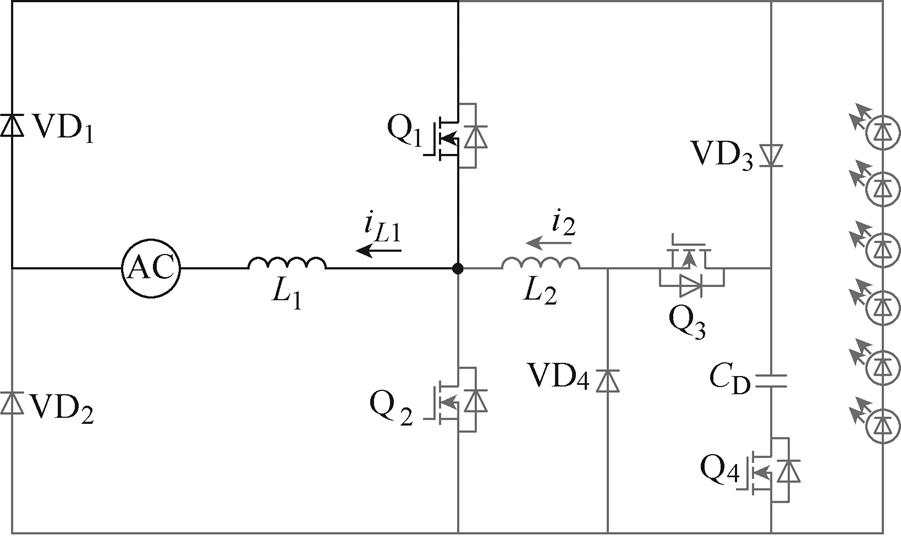

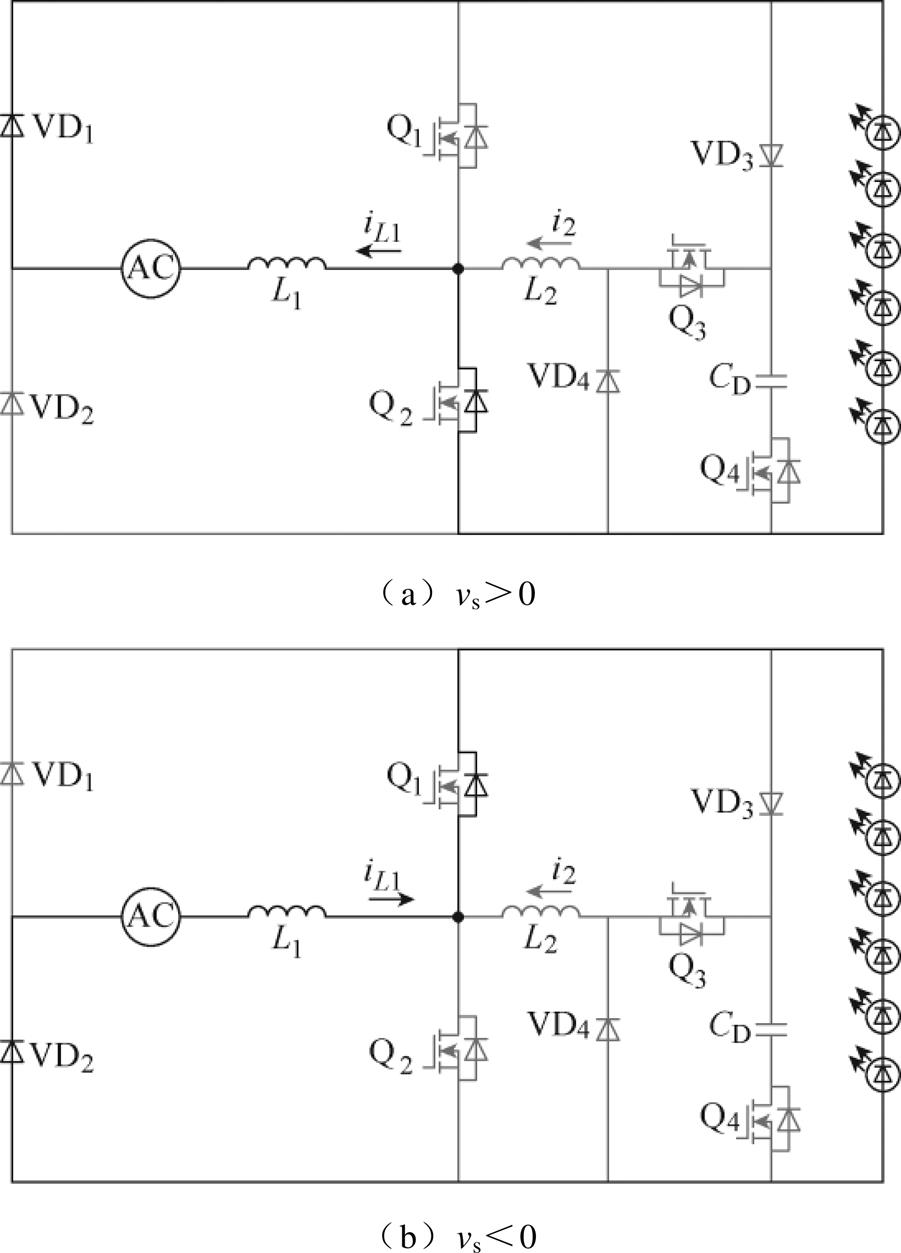

图2所示为本文提出的具有功率解耦能力的单级无桥式虚拟三端口整流器拓扑,由功率因数校正电路(PFC Circuit, PFCC)和功率解耦电路(Power Decoupling Circuit, PDC)构成。图中,Lf和Cf为输入滤波电感和电容;L1、VD1、VD2、Q1和Q2为PFCC的升压电感、二极管和开关管,用来实现高功率因数以满足IEC 61000-3-2标准;CD和L2为第三虚拟端口PDC(见图2中阴影部分)的解耦电容和电感,Q2、Q3、Q4、VD3和VD4分别为其开关管和二极管。iL1为升压电感电流,i3为流经CD的电流。

图2 本文提出的电路拓扑

Fig.2 Proposed energy buffering circuit

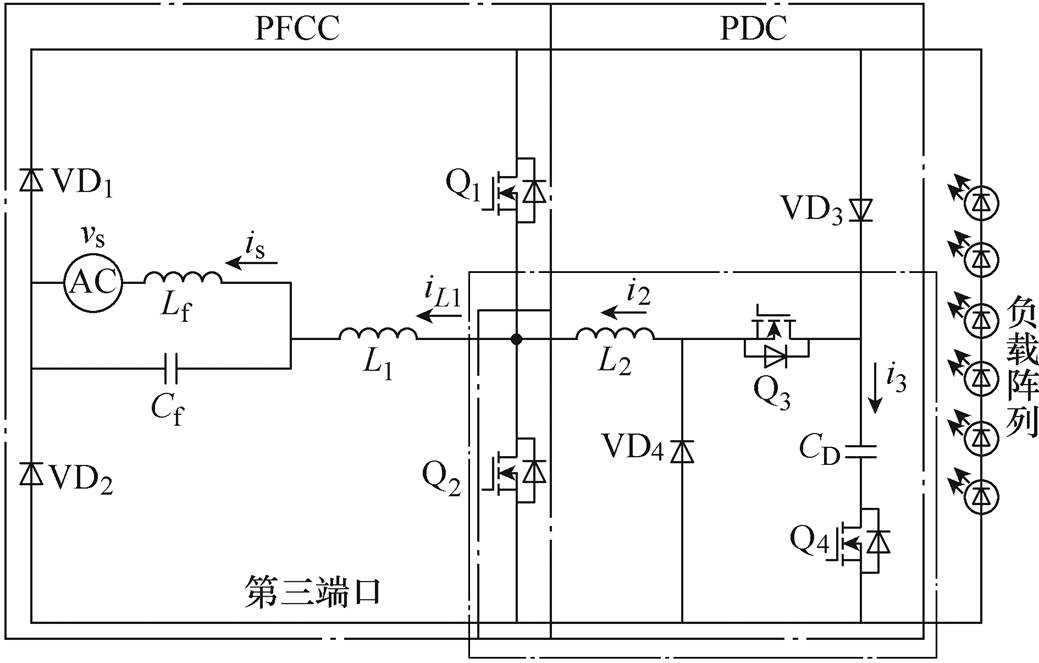

图3为工频下各开关管的驱动波形,为方便分析,将工作原理分为充电阶段和放电阶段。详言之,当输入功率Pin高于输出功率Pout时,冗余能量(即Pin-Pout)存储在解耦电容CD中;当输入功率Pin低于输出功率Pout时,解耦电容CD通过谐振方式将能量释放至解耦电感L2。此时,解耦电感L2与升压电感L1共同为负载馈电,以消除输出功率赤字。众所周知,Boost型PFC单元可实现高功率因数,但也致使多个器件承受高电压应力,损耗增大,成本增加。然而,本文仅解耦电容CD处于高电压应力下,因此并未对整体效率产生较大影响。

图3 图2的关键波形

Fig.3 Key waveforms for Fig.2

输入、输出电流波形如图4所示。图4a和图4b分别为有、无PDC参与的输出电流波形。图中,Iout为输出电流波形,Iout-p为输出的峰值电流。本方案预通过引入第三虚拟端口实现在图4c区域B中解耦出阴影区域A,进而得到恒定的输出电流。为便于分析,在本文做出以下假设:开关周期Ts远小于工频周期T;因此每个开关周期中,vs可以视为常量。

图4 输入、输出电流波形

Fig.4 Input and output current waveforms

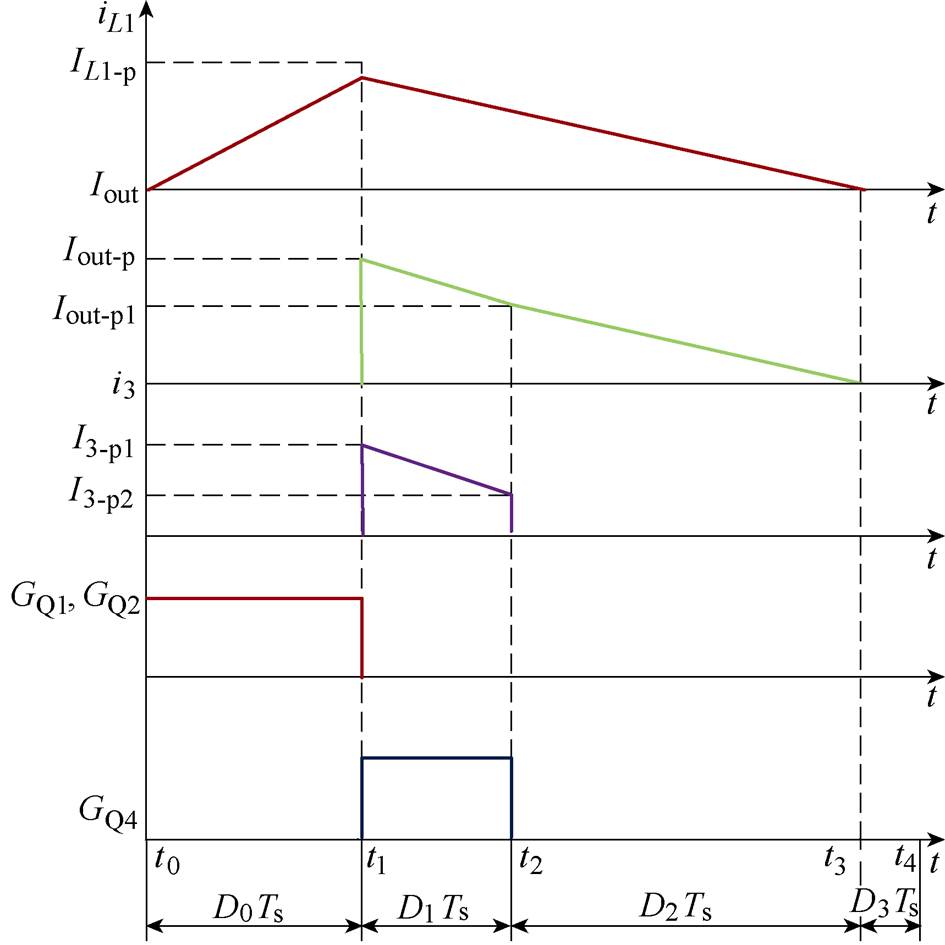

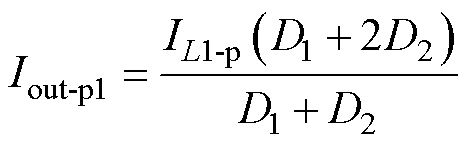

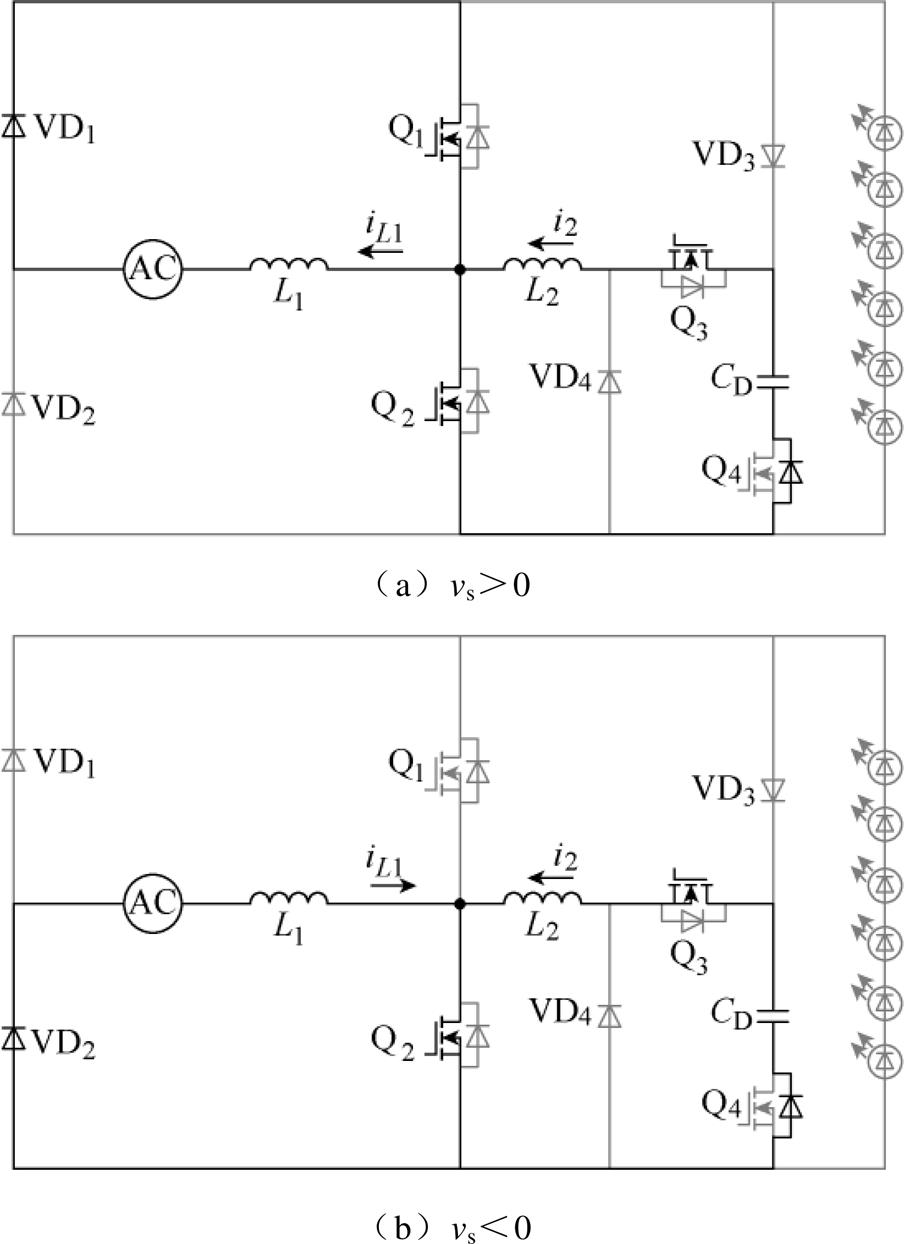

阶段Ⅰ根据开关状态分为四个工作模态,如图5所示。图中,I3-p为电流i3的峰值,GQ1、GQ2和GQ4分别为开关管Q1、Q2和Q4的驱动信号。简言之,其过程为:①能量从输入端口转移至升压电感L1;②L1释放多余能量至解耦电容CD;③所需能量转移至负载侧;④由于DCM运行,等待下一个开关周期。在此阶段下,Q3始终处于关闭状态。

图5 阶段Ⅰ的电流波形及驱动信号

Fig.5 Current waveforms and driving signs under Period Ⅰ

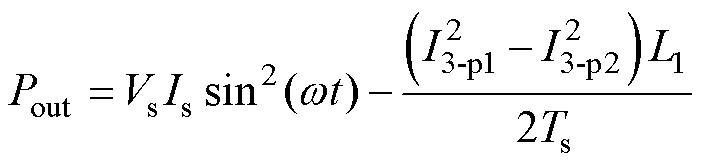

模态1 [t0, t1 :由于输入电压vs的极性,该状态可分为两种情况,等效电路如图6所示。当t =t0时,触发开关管Q1、Q2,交流源vs、电感L1、二极管VD1、VD2形成电流回路;此时电源给电感L1充电,电流iL1线性上升。当开关Q1、Q2断开时,电感器电流达到峰值IL1-p,可表示为

:由于输入电压vs的极性,该状态可分为两种情况,等效电路如图6所示。当t =t0时,触发开关管Q1、Q2,交流源vs、电感L1、二极管VD1、VD2形成电流回路;此时电源给电感L1充电,电流iL1线性上升。当开关Q1、Q2断开时,电感器电流达到峰值IL1-p,可表示为

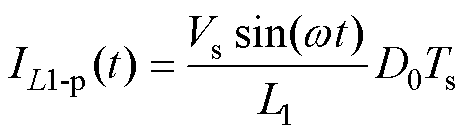

(1)

(1)

式中,Vs为输入电流峰值;D0为开关管Q1、Q2的占空比。

(a)vs>0

(b)vs<0

图6 阶段Ⅰ中工作模态1的等效电路

Fig.6 Equivalent circuit for mode 1 in Period Ⅰ

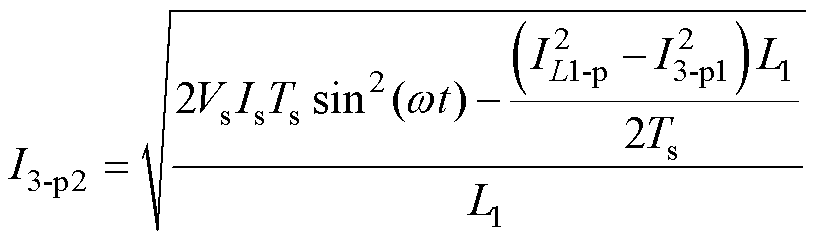

模态2 [t1, t2 :当t =t1时,Q1、Q2断开,Q4导通,等效电路如图7所示。此阶段,L1向解耦电容CD和LED负载供电,电流i3达到峰值I3-p2。假设:PF= 1,且L1的能量完全释放给负载,可得电流I3-p2为

:当t =t1时,Q1、Q2断开,Q4导通,等效电路如图7所示。此阶段,L1向解耦电容CD和LED负载供电,电流i3达到峰值I3-p2。假设:PF= 1,且L1的能量完全释放给负载,可得电流I3-p2为

(2)

(2)

式中,I3-p1=IL1-p-Iout-p;w=2pf,f为输入电压的角频率。此时,输出功率可表示为

(3)

(3)

图7 阶段Ⅰ中工作模态2的等效电路

Fig.7 Equivalent circuit for mode 2 in Period Ⅰ

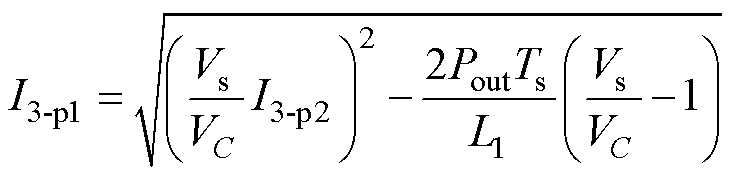

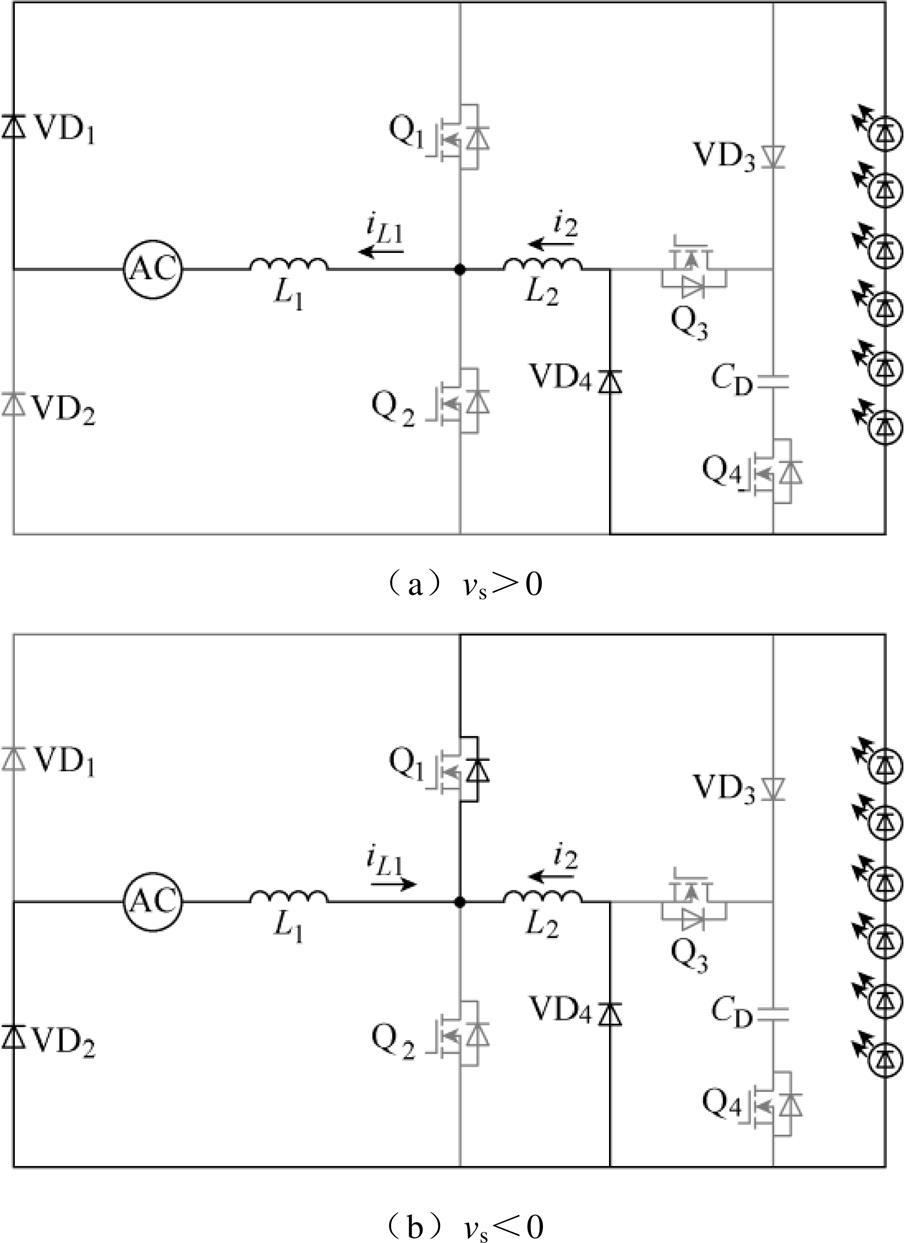

由式(3)可知,为保持恒定的输出功率,电流I3-p1需随I3-p2的变化而变化。为描述其关系,首先占空比D0和D1可分别表示为

(4)

(4)

(5)

(5)

式中,VC为CD两端的电压。将式(4)和式(5)代入式(3),可以得出电流I3-p1与I3-p2的关系为

(6)

(6)

模态3 [t2, t3 :所有开关管均处于关断状态,工作电路如图8所示。此阶段,能量不再向解耦电容释放,并全部流入输出端口。当电流Iout减小至零,该模态结束。

:所有开关管均处于关断状态,工作电路如图8所示。此阶段,能量不再向解耦电容释放,并全部流入输出端口。当电流Iout减小至零,该模态结束。

图8 阶段Ⅰ中工作模态3的等效电路

Fig.8 Equivalent circuit for mode 3 in Period Ⅰ

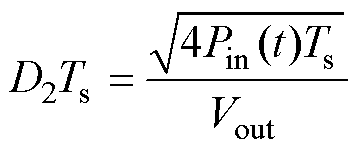

由于L1为CD和LEDs提供的能量等于两个模态(D1Ts和D2Ts)的总和。那么,D2Ts可表示为

(7)

(7)

式中,Vout为负载输出电压;Iout-p1为工作在模态3时输出电流峰值。根据基尔霍夫电流定律(Kirchhoff Current Law, KCL),Iout-p1可表示为

(8)

(8)

将式(1)、式(8)代入式(7),可得D2Ts为

(9)

(9)

由式(9)可知,Pin仅与D2Ts有关。因此,在每个开关周期内,D2Ts总会随着输入功率的变化而变化,以满足恒功率输出。

模态4 [t3, t4]:此阶段,无电流回路,因此不再给出等效电路。

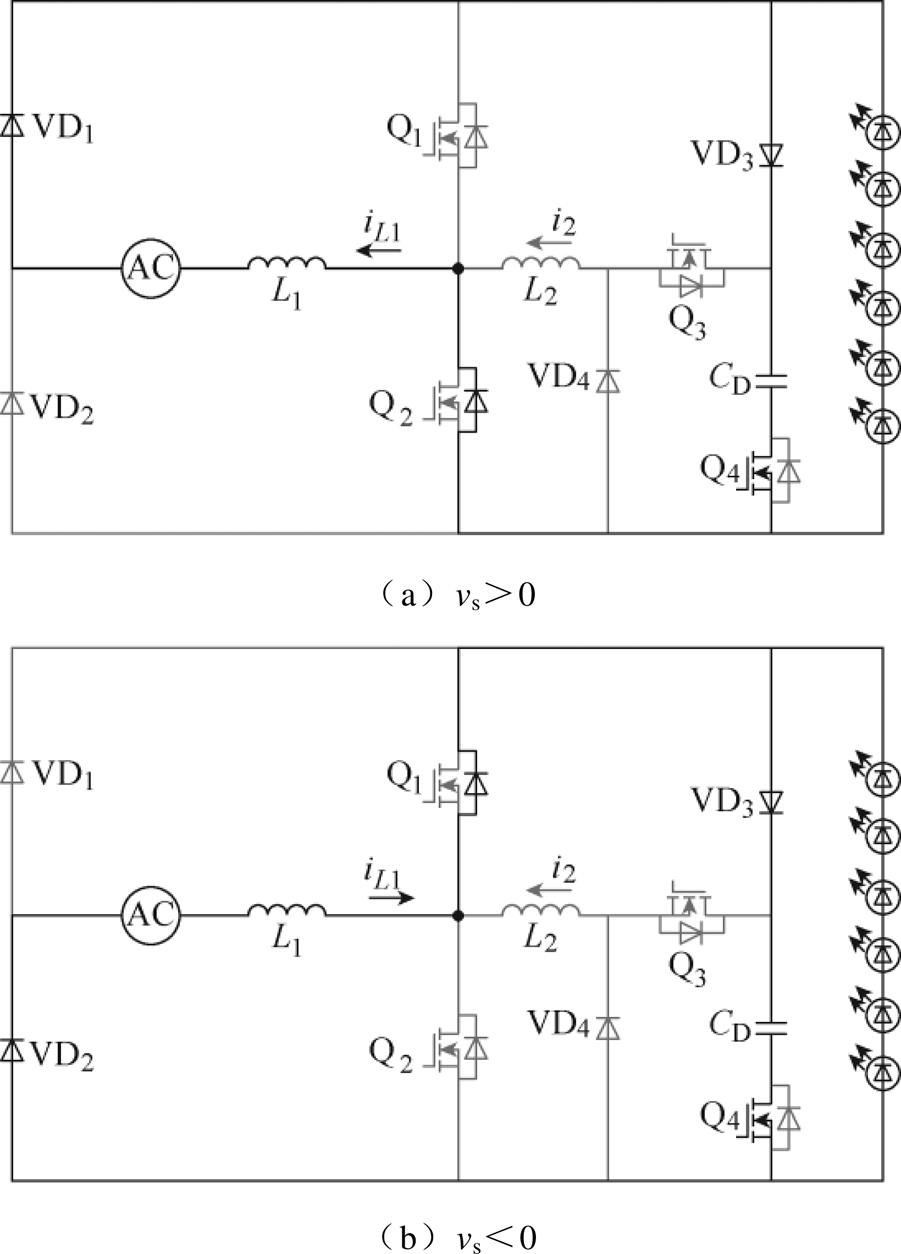

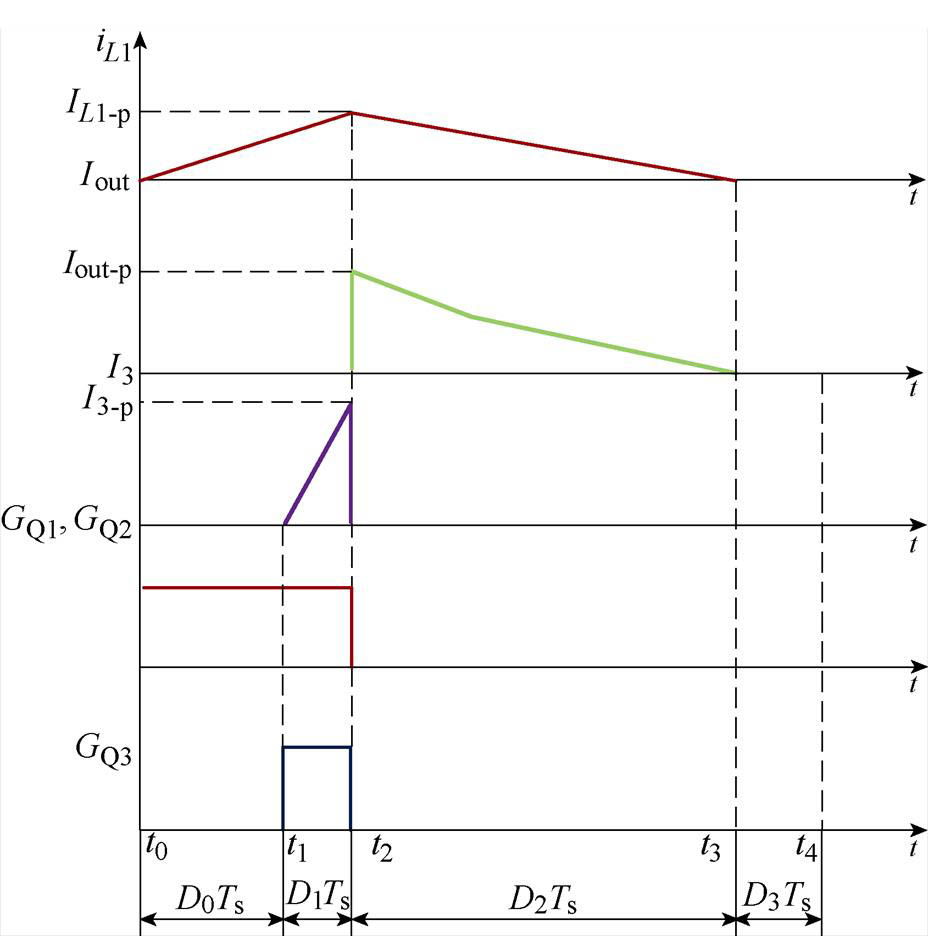

图9为整流器在阶段Ⅱ下的开关状态,与阶段Ⅰ类似。阶段Ⅱ中Q4始终保持关断状态。为满足Pout=Pin,此阶段需从解耦电容CD释放能量到电感L2,同时与L1共同为负载供电。

图9 阶段Ⅱ的电流波形及驱动信号

Fig.9 Current waveforms and driving signs under Period Ⅱ

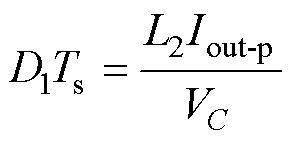

阶段Ⅱ中的模态1和模态4与阶段Ⅰ相似,此处不再赘述。因此仅分析模态2和模态3,其等效电路如图10和图11所示。

模态2 [t1, t2 :此阶段,L1仍在充电。Q3导通,CD开始向L2放电,等效电路如图10所示。若负载亮度不变,那么D0Ts与D1Ts之和不变。因此,D0Ts和D1Ts分别为

:此阶段,L1仍在充电。Q3导通,CD开始向L2放电,等效电路如图10所示。若负载亮度不变,那么D0Ts与D1Ts之和不变。因此,D0Ts和D1Ts分别为

(10)

(10)

图10 阶段Ⅱ中工作模态2的等效电路

Fig.10 Equivalent circuit for mode 2 in Period Ⅱ

图11 阶段Ⅱ中工作模态3的等效电路

Fig.11 Equivalent circuit for mode 3 in Period Ⅱ

(11)

(11)

模态3 [t2, t3 :开关管均处于关断状态。此时,电感L1和L2维持输出,消除输出功率赤字,如图11所示。D2Ts的推导与式(9)相同,不再赘述。

:开关管均处于关断状态。此时,电感L1和L2维持输出,消除输出功率赤字,如图11所示。D2Ts的推导与式(9)相同,不再赘述。

本文所提方案具有普遍性,可满足不同功率等级的设备对电源需求。因此,为不失一般性,本文以功率等级90W为例来设计关键参数、元器件选型和控制策略。

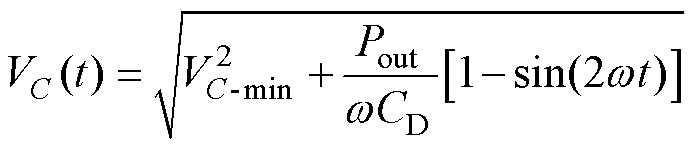

CD两端的电压VC以两倍工频脉动[34],如图1所示。VC-max为其峰值电压,由电容值和电压纹波DVC决定。根据模态分析可知,Q3、Q4和VD3、VD4的电压应力为VC-max,Q1、Q2的电压应力为VC-max-Vs。VD1、VD2的电压应力在输入电压峰值时达到极值。此外,与普通整流二极管不同,VD1~VD4的选取应满足反向恢复时间短和正向压降低的条件,如碳化硅肖特基二极管或快速恢复二极管。

解耦电容在半个工频周期内完成充电或放电过程。设解耦电容的能量变化值为DEC,根据积分运算可得

(12)

(12)

此外,DEC也可表示为

(13)

(13)

瞬时输入功率Pin(t)包括两倍工频的脉动功率,通过分解,可得

(14)

(14)

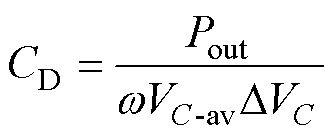

因此,解耦电容值及其电压应力通过联立式(12)~式(14)可以得出

(15)

(15)

(16)

(16)

其中

(17)

(17)

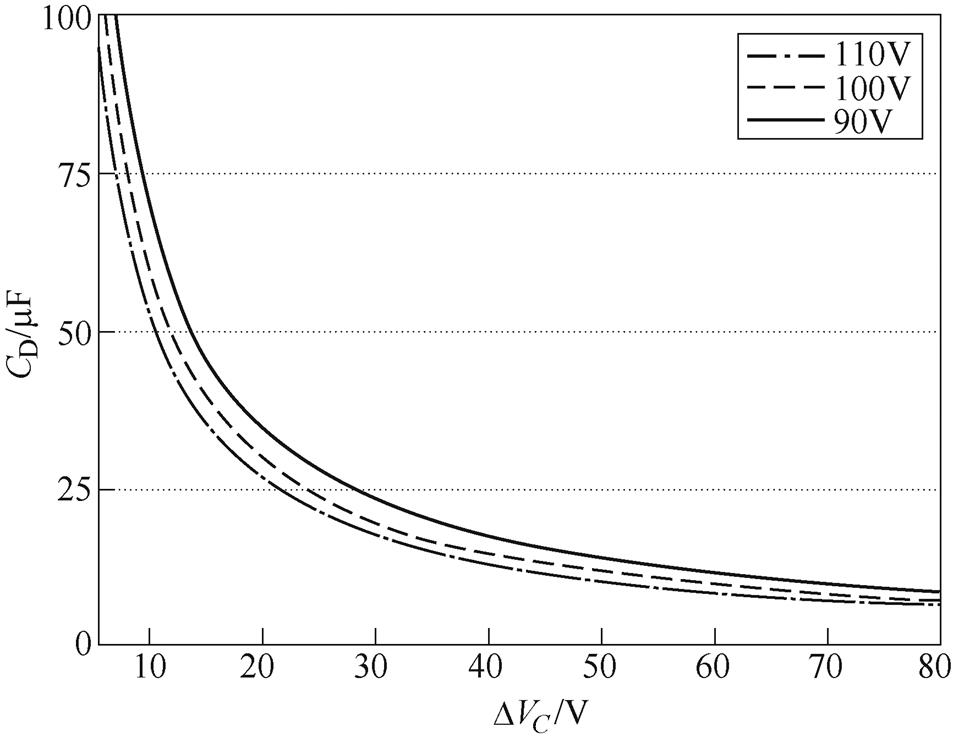

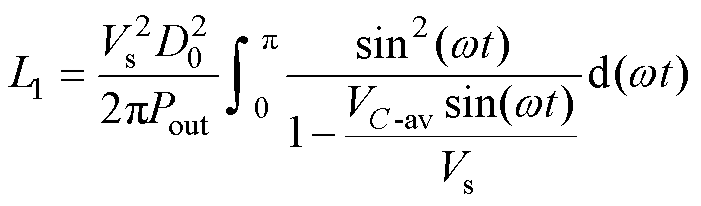

根据式(15),将w 和Pout视作定量,可绘制出不同输入电压等级下,解耦电容与电压纹波DVC的关系,如图12所示。观察图12可知,解耦电容值CD与VC-av和DVC成反比,因此,增大电容两端电压和纹波幅值能够减小解耦电容,从而允许使用寿命较长的薄膜电容代替电解电容。考虑到制造成本和传递效率,本文最终要求110V输入电压下,VC幅值不超过350V。

图12 解耦电容与纹波电压的关系

Fig.12 Decoupling capacitance versus ripple voltage

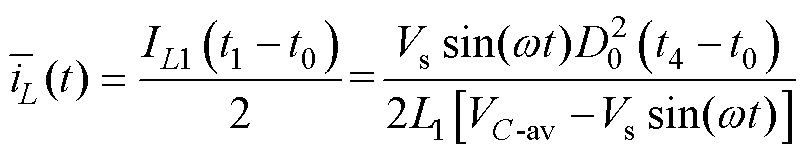

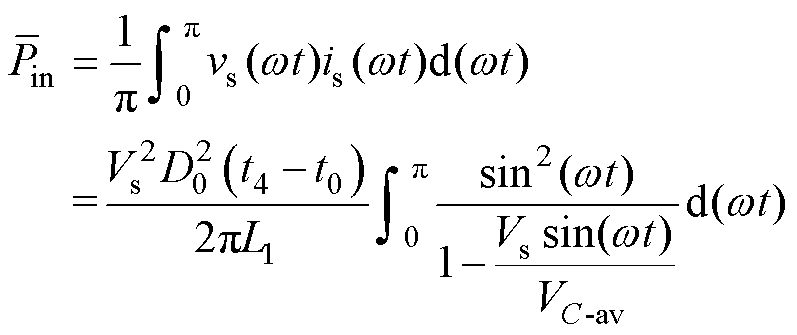

由于PFC在一个工频周期内的工作原理相同,因此本文仅分析vs>0的情况。首先,电流iL(t)的平均值可定义为

(18)

(18)

联立式(14)与式(18)可得,输入功率Pin的平均值为

(19)

(19)

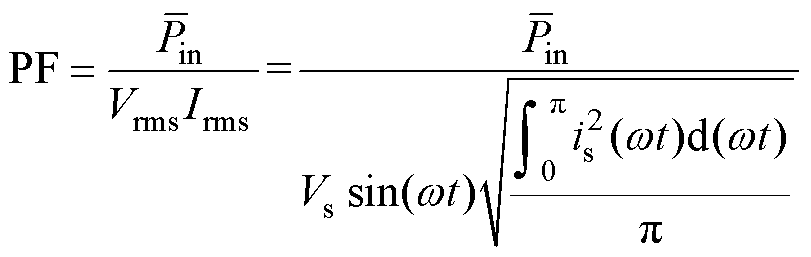

由式(19)得电路功率因数PF为

(20)

(20)

式中,Irms为输入电路is的方均根值;Vrms为电压vs的方均根值。假设 =Pout,可得

=Pout,可得

(21)

(21)

假定D0=0.5,输出功率Pout=90W,输入电压Vs= 110V,可得Lb=570mH。为满足DCM的运行模式,并保证在最小输入电压下仍可正常运行,最终取L1= 550mH。

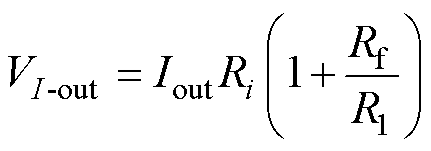

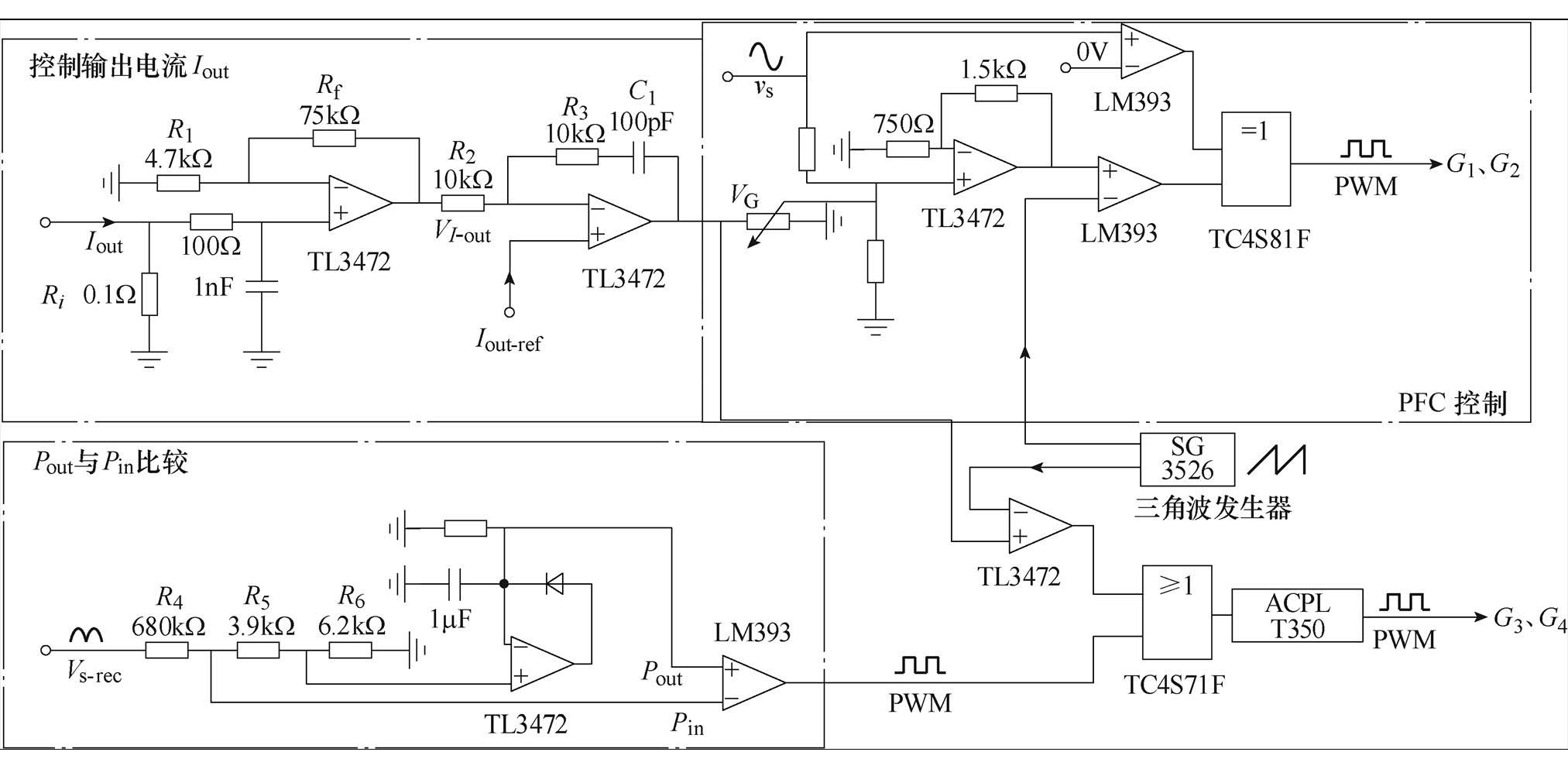

图13为本文所提整流器的控制单元,由于采用了PWM驱动LED,输出端口无需滤波电容。为简化控制策略,Q1和Q2不仅用于PFC,同时用于调节负载亮度。详言之,输出电流Iout由0.1W 的电阻Ri检测,并将检测信号与参考值Iout-ref进行比较后,通过放大器进行放大。输出电流Iout需转换为0~3V的电压信号VI-out,其表达式为

(22)

(22)

图13 控制电路结构

Fig.13 Structure of control circuit

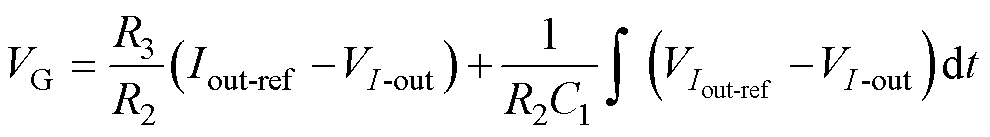

根据式(22)可知,Rf=75kW,R1=4.7kW。紧接着,VI-out和Iout-ref的误差值传递至PI调节器,PI调节器的输出信号可表示为

(23)

(23)

式中,Iout-ref为输出电流参考信号。根据式(23)可知,R2=R3=10kW,C1=100pF。

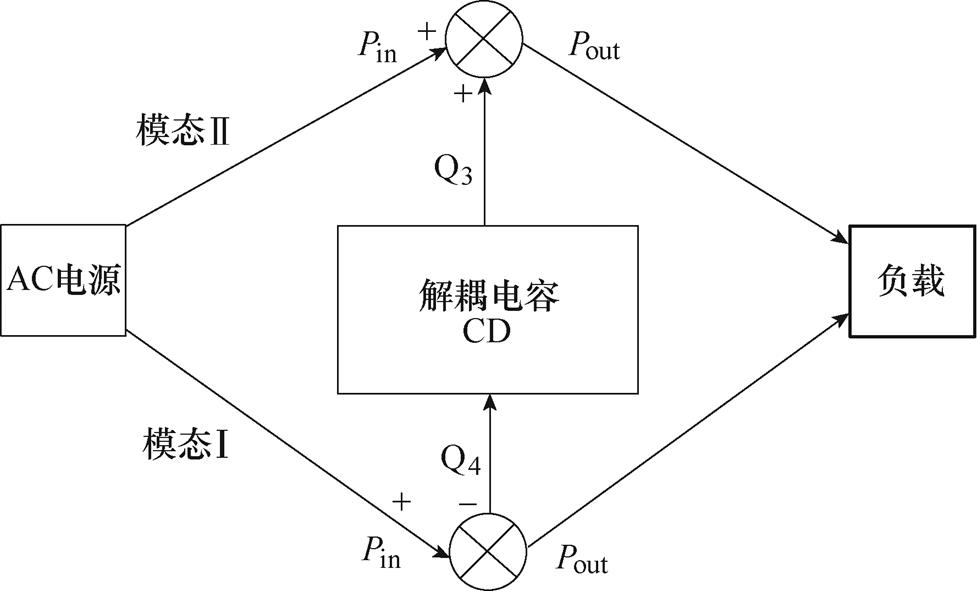

PI调节器输出信号VG与输入电压vs用作PFC控制器输入,并经过载波信号比较后生成PWM信号G1和G2。Vs-ref作为功率比较模块的输入量,根据式(3)和式(19)可得,R4=680kW、R5=3.9kW、R6= 6.2kW。通过运算得到Pin和Pout,并将其比较后得到低频方波信号;随后将载波信号与其比较后生成PWM信号G3和G4。详细的功率流动路径如图14所示。

图14 功率路径

Fig.14 Power flow of the proposed scheme

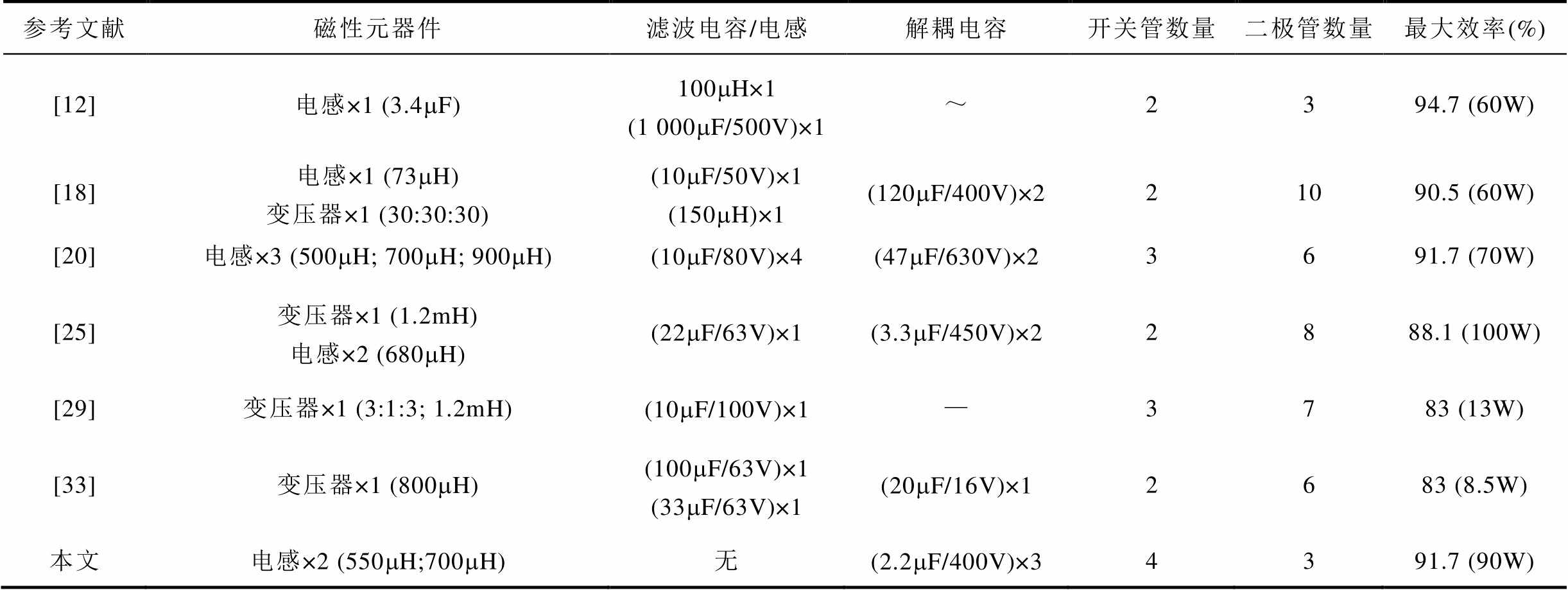

为了说明所提整流器在元器件使用和转换效率等方面的优势,本文与其他单相变换器进行了比较,详见表1。

表1 功率元件数比较分析

Tab.1 Comparative analysis of the number of power elements

参考文献磁性元器件滤波电容/电感解耦电容开关管数量二极管数量最大效率(%) [12]电感×1 (3.4mF)100mH×1 (1 000mF/500V)×1~2394.7 (60W) [18]电感×1 (73mH)变压器×1 (30:30:30)(10mF/50V)×1 (150mH)×1(120mF/400V)×221090.5 (60W) [20]电感×3 (500mH; 700mH; 900mH) (10mF/80V)×4(47mF/630V)×23691.7 (70W) [25]变压器×1 (1.2mH)电感×2 (680mH)(22mF/63V)×1(3.3mF/450V)×22888.1 (100W) [29]变压器×1 (3:1:3; 1.2mH)(10mF/100V)×1—3783 (13W) [33]变压器×1 (800mH)(100mF/63V)×1 (33mF/63V)×1(20mF/16V)×12683 (8.5W) 本文电感×2 (550mH;700mH)无(2.2mF/400V)×34391.7 (90W)

注:“—”表示文章中并未示出;“~”表示并无功率解耦功能。

从表1中可明显看出,相较于现有工作,本文主要有两个特点:①功率元器件和磁性元器件较少;②脉冲驱动的方式无需输出滤波电容,致使功率密度进一步提升。

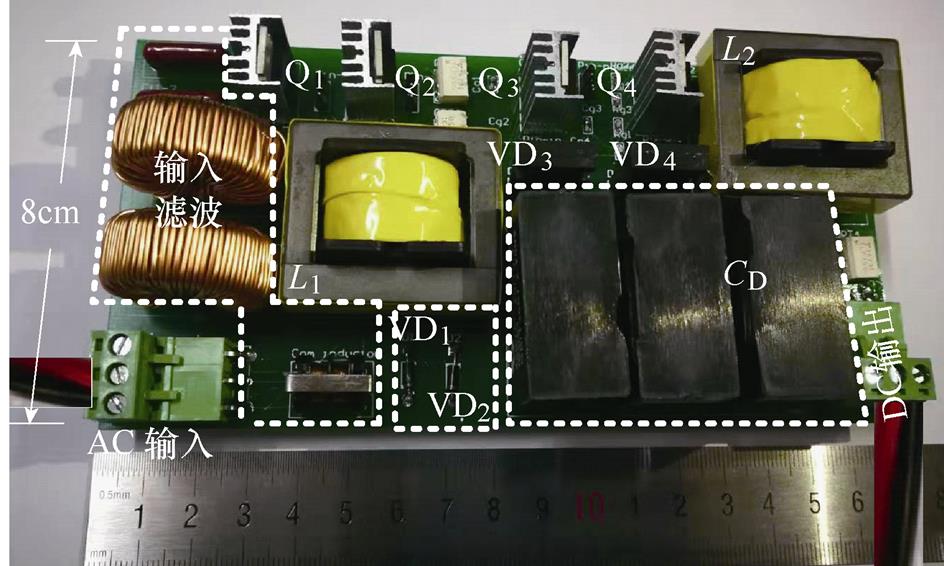

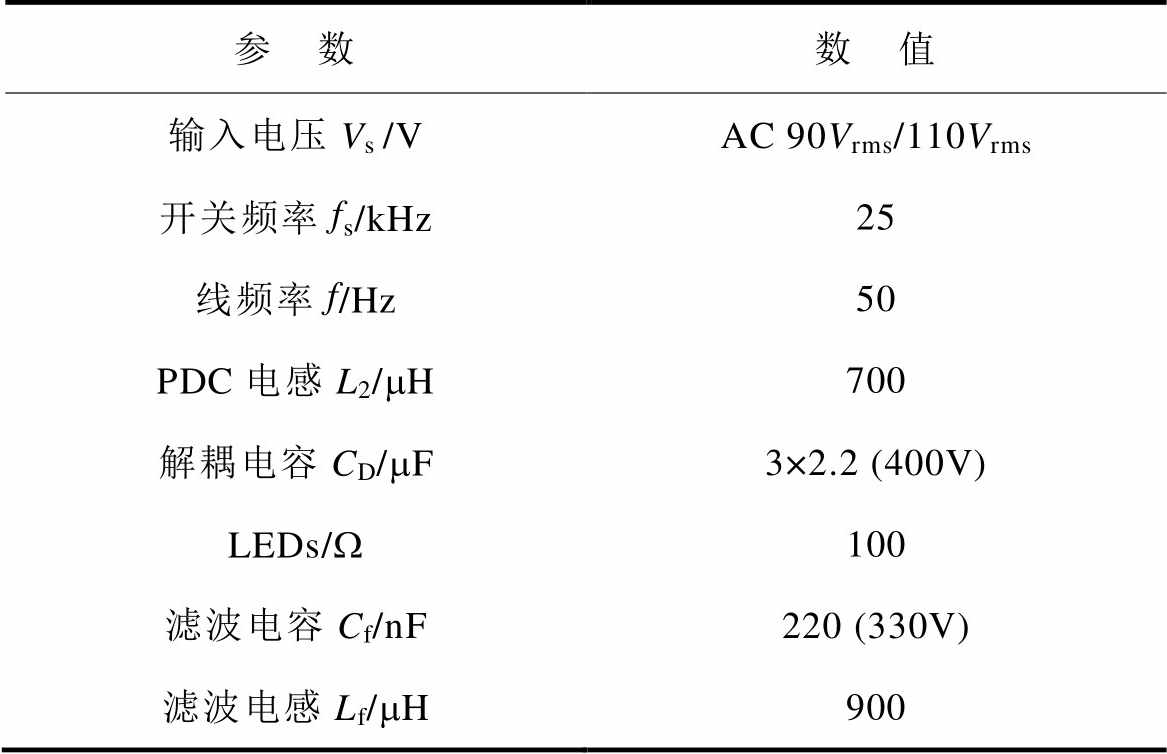

为验证所提电路及控制策略的可行性和正确性,本文搭建了90W实验样机,如图15所示。表2为本次实验的样机详细的电路参数。图16~图18为本次样机的实验波形。

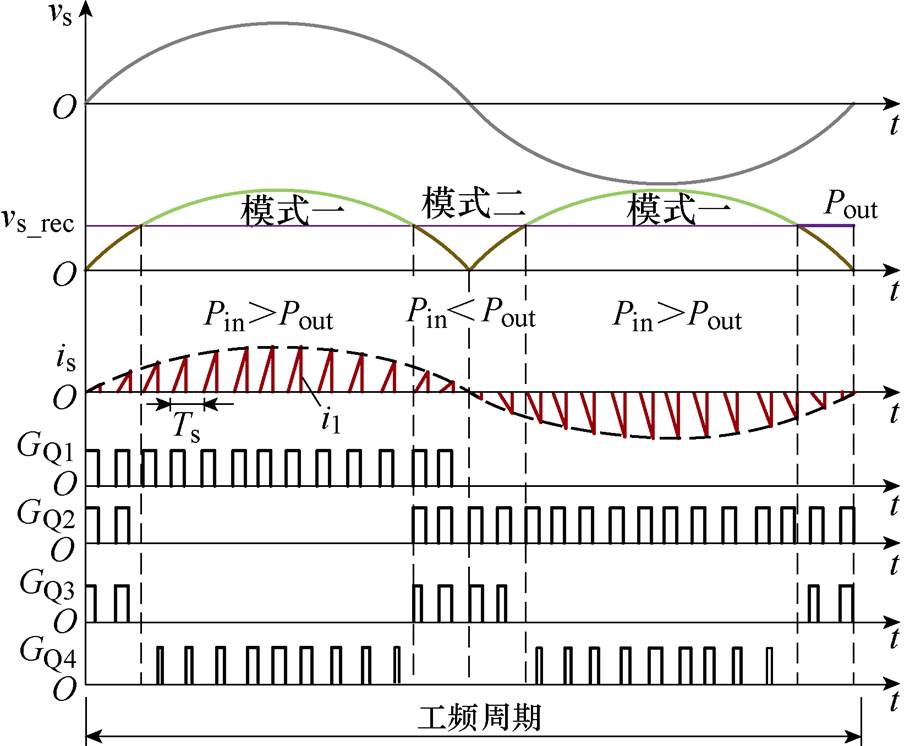

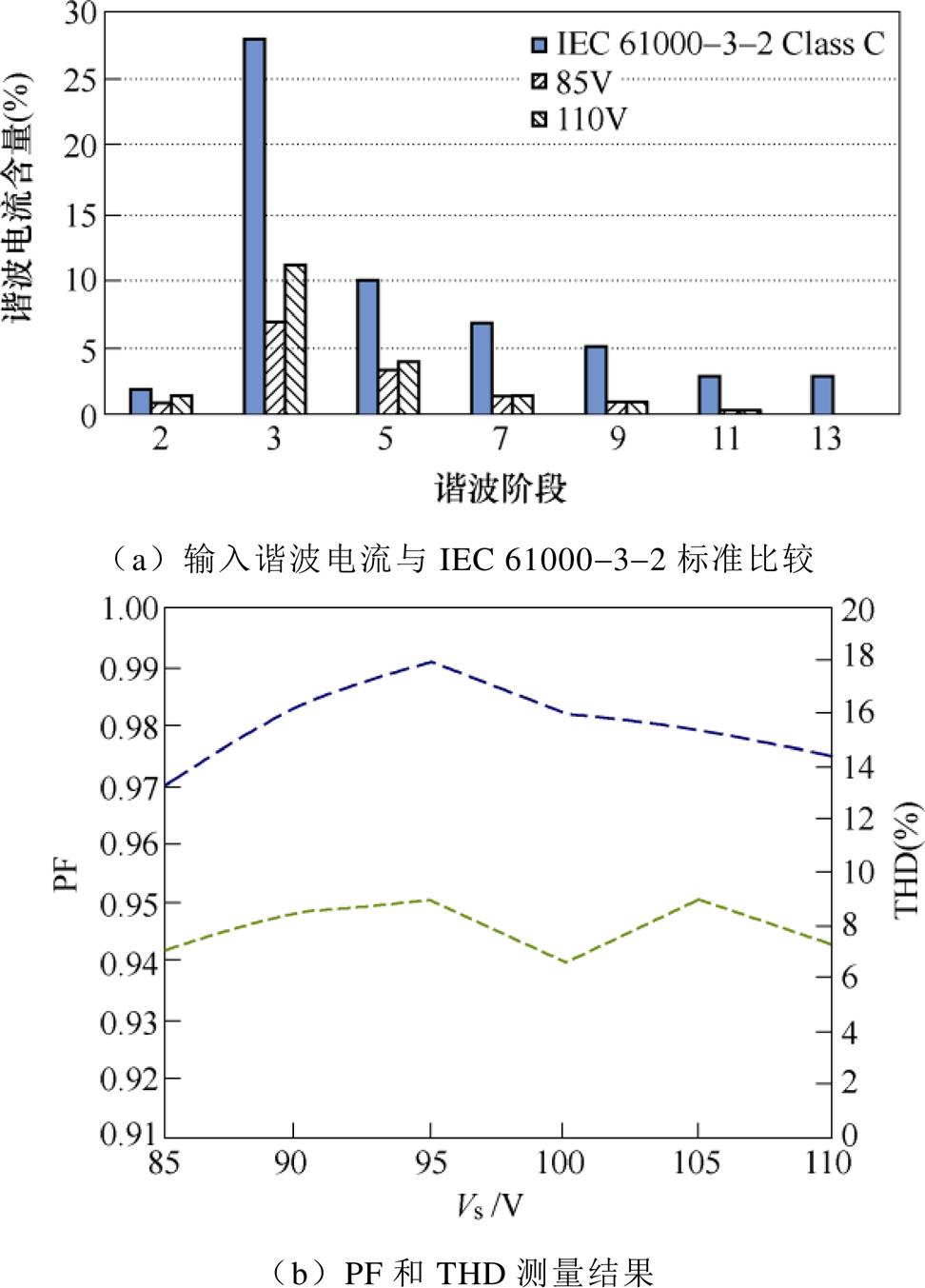

图16为不同输入电压等级90Vrms和110Vrms下,输入电流i1的实验波形。实测功率因数分别为0.989和0.984,且输入电流包络线近似为正弦波。此外,最大的电流谐波失真发生在90Vrms输入电压下,其数值为7.3%。图16b示出了DCM运行模式,有效地降低了二极管VD1和VD2的关断损耗。此外,不同输入电压下的功率因数PF和THD的测量结果将在下文详述。

图15 实验样机

Fig.15 Experimental prototype

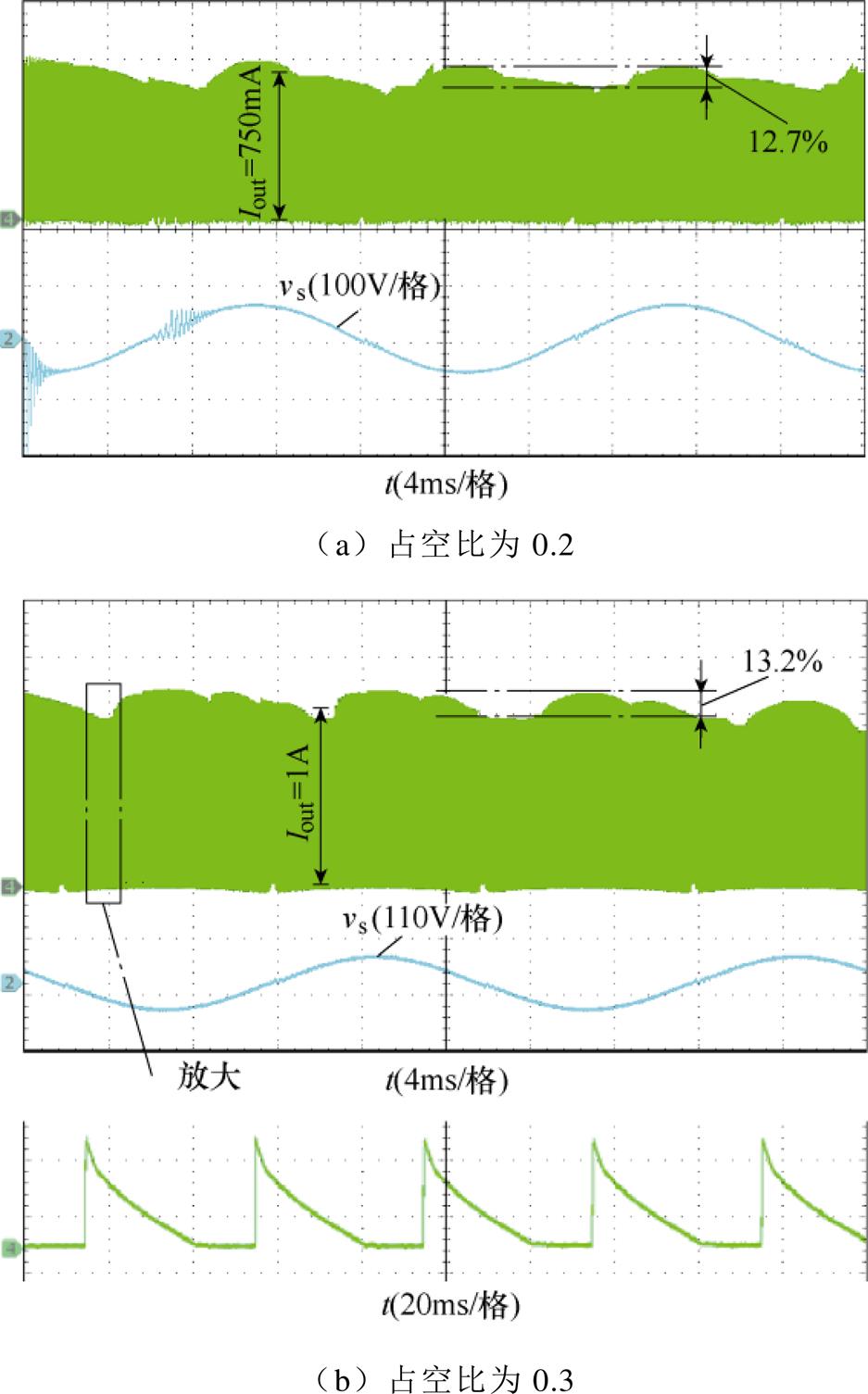

表2 所提驱动器电路参数

Tab.2 Component parameters of the proposed driver

参 数数 值 输入电压Vs /VAC 90Vrms/110Vrms 开关频率fs/kHz25 线频率f/Hz50 PDC电感L2/mH700 解耦电容CD/mF3×2.2 (400V) LEDs/W100 滤波电容Cf/nF220 (330V) 滤波电感Lf/mH900

图16 关键输入电流波形

Fig.16 Key input current waveforms

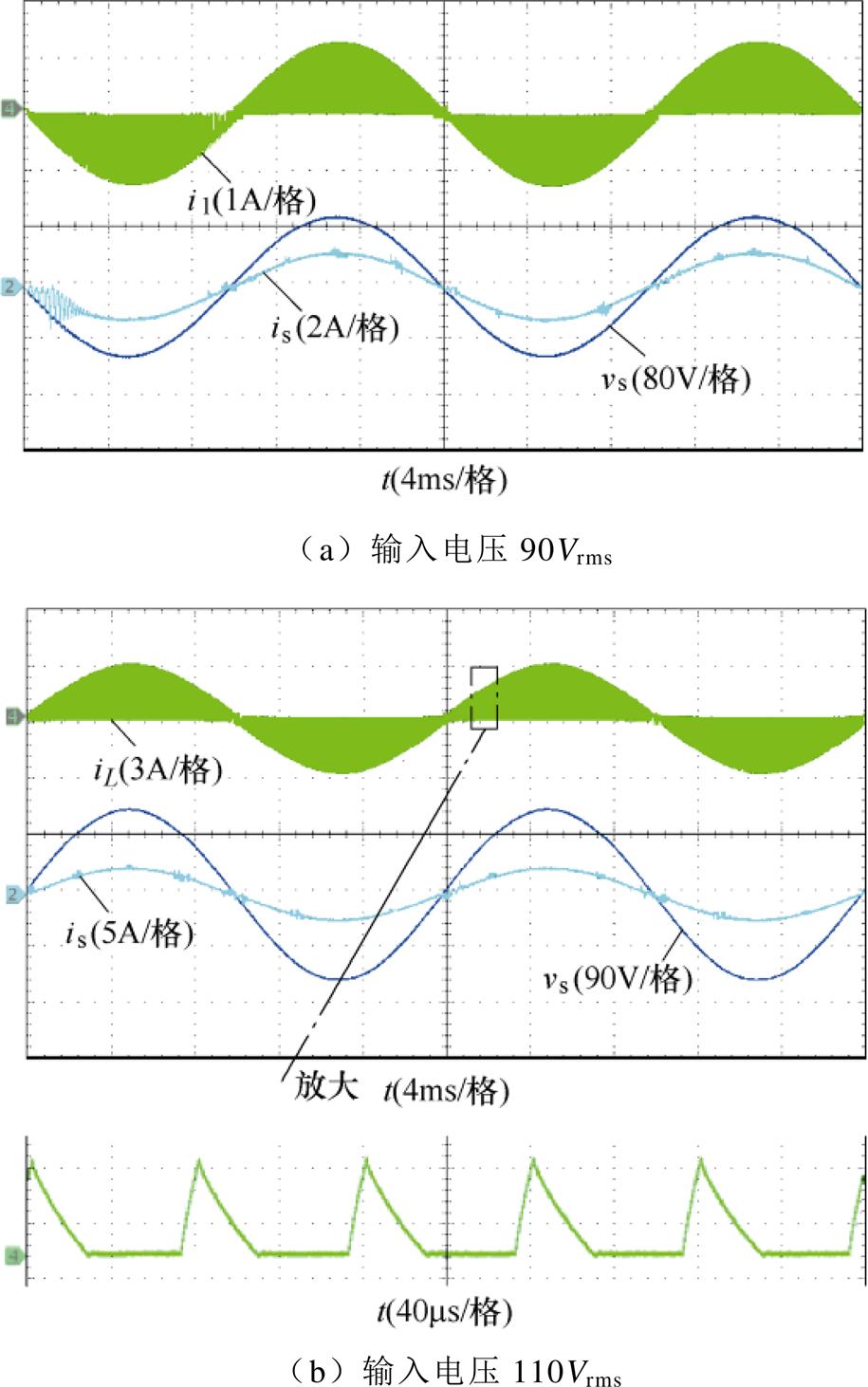

图17 输出电流波形

Fig.17 Waveforms of output currents

图18 实验波形

Fig.18 Experimental waveforms

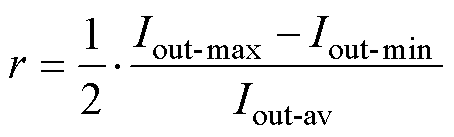

为满足节能要求,大范围调节负载亮度是必要的。图17a给出了Q1、Q2占空比为0.2和输入电压为85Vrms时,输出电流的实验波形。结果表明,最大输出电路纹波约为94mA,纹波率r可表示为

(24)

(24)

式中,Iout-max、Iout-min和Iout-av分别为输出电流峰值、谷值和平均值。

根据式(24),可得r=6.35%。当Q1、Q2占空比为0.3时,如图17b所示,其纹波率为6.6%。较于相似工作7.05%的纹波率[31],本文电路输出电流质量更佳。图17b为开关频率下输出脉动电流Iout,其平均值近似相等,与理论分析一致,因此可证明控制单元的可行性和正确性。同时,电路处于DCM运行模式,VD3、VD4无反向恢复电流。此外,输出电流质量的详细分析将在下文给出。

图18给出了输入电压为110Vrms时,电压VC和开关管的驱动信号波形。从图18a可以看出,DVC的频率为100Hz;其较高的幅值(约80V)有助于减小解耦电容值,因此本文仅需3×2.2mF的薄膜电容即可;观察图18b,Q2分时复用于PFC和PDC;此外,当Pin>Pout时,CD充电,Q3导通,VC增加;反之亦然,与理论分析一致。

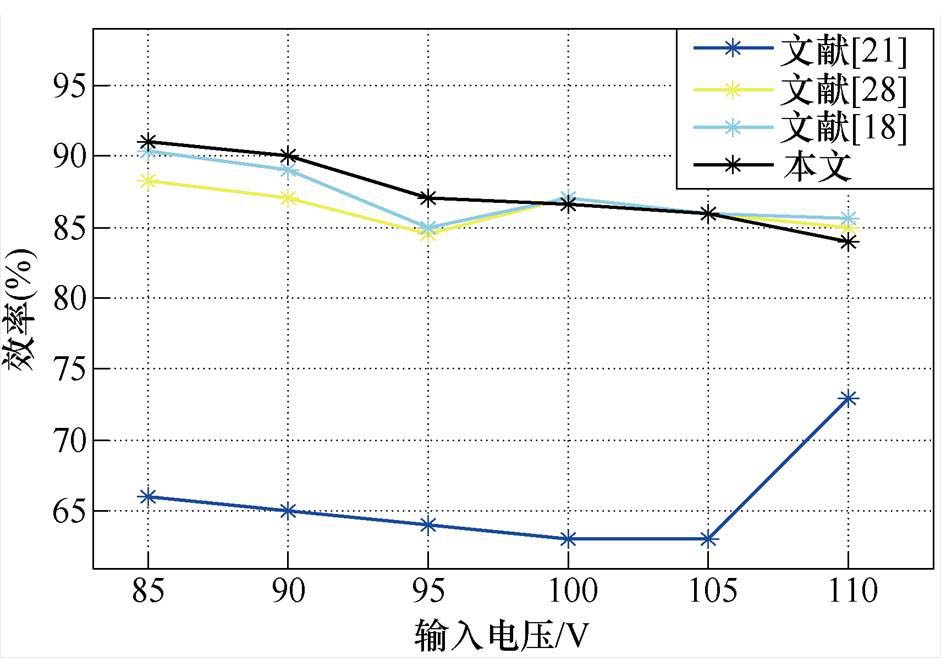

图19为效率曲线,结果表明,本文所提整流器的效率随着输入电压的增加而降低,但整体高于传统变换器系统。

图19 驱动器在输入电压变化下的效率变化

Fig.19 Efficiency variation of proposed driver under the variation of input voltage

图20给出了满载情况下输入谐波电流、功率因数以及总谐波畸变率(Total Harmonics Distortion, THD)的性能分析结果。由图可知,所有谐波电流均满足IEC 61000-3-2要求;同时0.991的功率因数也远远满足了EnergyStar的要求。此外,在85~110V的输入电压范围内,输入电流的THD值均小于9.3%。由此表明,LED负载可与本文所提整流器实现较好的结合。

图20 性能分析

Fig.20 Performance analysis

对于传统整流器而言,通常需要较大的电解电容平衡功率脉动,因此限制了系统的整体寿命,同时也影响了其轻量化设计。然而,现有解决方案的解耦电路和控制策略较为复杂。此外,尽管Boost电路在PFC中具有良好的性能,但它会使大部分器件承受高电压应力,从而导致较大导通损耗。鉴于此,本文提出了一种新型虚拟三端口网络整流器,通过仿真和实验验证,得到以下结论:

1)采用3×2.2mF/400V的薄膜电容替代了电解电容,且功率因数均高于0.971。

2)通过改变驱动模式,消除了传统电路中承受高压应力的输出电容,效率得到了进一步提高。

3)通过多单元整合,有效消除了功率器件和磁性器件的数量;器件分时复用,简化了解耦单元。Q1、Q2不仅用于功率因数校正,还可实现大范围亮度调节,且无需多路反馈通道,控制单元简单、易行。

此外,当输出电流约为1A时,纹波率最大,其数值为6.6%,满足LED无频闪要求。实验结果表明,本文介绍的整流器拥有良好的输出电流质量。

参考文献

[1] Farzam N, Li Yunwei, Sun Kai, et al. Active power oscillation cancellation with peak current sharing in parallel interfacing converters under unbalanced voltage[J]. IEEE Transactions on Power Electronics, 2019, 46(6): 3424-3435.

[2] Liu Junfeng, Tian Hanlei, Zeng Jun. Multi-channel LED driver based on switched-controlled capacitor with constant frequency control[J]. IET Power Electronics, 2018, 11(12): 1991-1999.

[3] Fang Peng, Qiu Yajie, Wang Hongliang, et al. A single-stage primary-side-controlled off-line fly-back LED driver with ripple cancellation[J]. IEEE Transa- ctions on Power Electronics, 2017, 32(6): 4700-4715.

[4] 梁国壮, 田涵雷, 王子园, 等. 一种单级无桥式高功率因数无电解电容AC-DC LED驱动器[J]. 电工技术学报, 2019, 34(16): 3396-3407.

Liang Guozhuang, Tian Hanlei, Wang Ziyuan, et al. A single-stage AC-DC LED driver without bridge and high power factor and electrolytic capacitor[J]. Transactions of China Electrotechnical Society, 2019, 34(16): 3396-3407.

[5] 田涵雷, 刘俊峰, 曾君, 等. 基于可控开关电容的定频谐振式多路LED均流驱动器[J]. 电工技术学报, 2019, 34(2): 88-97.

Tian Hanlei, Liu Junfeng, Zeng Jun, et al. Fixed frequency resonant multi-channel LED current sharing driver based on controllable switched capacitor[J]. Transactions of China Electrotechnical Society, 2019, 34(2): 88-97.

[6] Diego G L, Manuel A, Alberto R, et al. Designed- oriented analysis and performance evaluation of a low-cost high-brightness led driver based on flyback power factor corrector[J]. IEEE Transactions on Power Electronics, 2013, 60(7): 2614-2626.

[7] Jung Min K, Woo Young C, Bong Hwan K. Single- stage quasi-resonant flyback converter for a cost- effective PDP sustain power module[J]. IEEE Transa- ctions on Industrial Electronics, 2011, 58(6): 2372-2377.

[8] Qiao C, Smedley K M. A topology survey of single-stage power factor corrector with a boost type input-current-shaper[J]. IEEE Transactions on Power Electronics, 2001, 16(3): 354-368.

[9] Ma Hongbo, Lai J S, Zheng Cong, et al. A high- efficiency quasi-single-stage bridgeless electrolytic capacitor-free high-power AC-DC driver for supplying multiple LED strings in parallel[J]. IEEE Transa- ctions on Power Electronics, 2016, 31(8): 5825-5836.

[10] Chang Yeol O, Dong Hee K, Dong Gyun W, et al. A high-efficient non-isolated single-stage on-board battery charger for electric vehicles[J]. IEEE Transa- ctions on Power Electronics, 2015, 28(12): 5746-5757.

[11] 阎铁生, 李明洪, 周国华, 等. 一种一次侧控制的Buck-Flyback单级功率因数校正变换器LED驱动电路[J]. 电工技术学报, 2019, 34(16): 57-67.

Yan Tiesheng, Li Minghong, Zhou Guohua, et al. A Buck-Flyback single-stage power factor correction converter with primary side control[J]. Transactions of China Electrotechnical Society, 2019, 34(16): 57-67.

[12] Ignacio G, Aitor V, Manuel A, et al. A review on flicker-free AC/DC led drivers for single-phase and three-phase AC power grids[J]. IEEE Transactions on Industrial Electronics, 2019, 34(10): 10035-10057.

[13] Huai W, Marco L, Frede B. Toward reliable power electronics: challenges, design tools, and opportuni- ties[J]. IEEE Industrial Electronics Magazine, 2013, 7(2): 17-26.

[14] Ruan Xinbo, Wang Beibei, Yao Kai, et al. Optimum injected current harmonics to minimize peak-to- average ratio of LED current for electrolytic capacitor-less AC-DC drivers[J]. IEEE Transactions on Power Electronics, 2011, 26(7): 1820-1825.

[15] Ali S, Moallem M. Filter capacitor minimization in a flyback LED driver considering input current harmonics and light flicker characteristics[J]. IEEE Transactions on Power Electronics, 2015, 30(8): 4467-4476.

[16] Wang Beibei, Ruan Xinbo, Yao Kai, et al. A method of reducing the peak-to-average ratio of LED current for electrolytic capacitor-less AC-DC drivers[J]. IEEE Transactions on Power Electronics, 2010, 25(3): 592-601.

[17] Wang Lei, Zhang Bo, Qiu Dongyuan. A novel valley- fill single-stage Boost-forward converter with opti- mized performance in universal-line range for dimmable LED lighting[J]. IEEE Transactions on Industrial Electronics, 2017, 64(4): 2770-2778.

[18] Ma Hongbo, Zheng Cong, Yu Wensong, et al. Bridge- less electrolytic capacitor-less valley-fill AC/DC converter for offline Twin-Bus light-emitting diode lighting application[J]. IET Power Electronics, 2013, 6(6): 1132-1141.

[19] Liu Junfeng, Tian Hanlei, Liang Guozhuang, et al. A bridgeless electrolytic-free LED driver based on series resonant converter with constant frequency control[J]. IEEE Transactions on Power Electronics, 2019, 34(3): 2712-2725.

[20] Wang Fei, Li Lin, Zhong Yuanxu, et al. Flyback- based three-port topologies for electrolytic capacitor- less LED drivers[J]. IEEE Transactions on Industrial Electronics, 2017, 64(7): 5818-5827.

[21] Qiu Yajie, Wang Hongliang, Wang Laili, et al. Current-ripple-based control strategy to achieve low- frequency ripple cancellation in single-stage high- power LED driver[C]//IEEE Energy Conversion Con- gress and Exposition (ECCE), Montreal, 2015: 1-7.

[22] Hyun Chang K, Moon Chul C, Sungwoo K, et al. An AC-DC LED driver with a two-parallel inverted buck topology for reducing the light flicker in lighting applications to low-risk levels[J]. IEEE Transactions on Power Electronics, 2017, 32(5): 3879-3891.

[23] Hamed V, Ghasem R, Mohammad R Z. Flicker-free electrolytic capacitor-less universal input offline LED driver with PFC[J]. IEEE Transactions on Power Electronics, 2016, 31(9): 6553-6561.

[24] Dong Hanjing, Xie Xiaogao, Jiang Lei, et al. An electrolytic capacitor-less high power factor LED driver based on a “one-and-a-half stage” forward- flyback topology[J]. IEEE Transactions on Power Electronics, 2018, 33(2): 1572-1584.

[25] Diego G L, Marcos F, Marta M H, et al. Tapped- inductor Buck HB-LED AC/DC driver operating in boundary conduction mode for replacing incandescent bulb lamps[J]. IEEE Transactions on Power Elec- tronics, 2012, 27(10): 4329-4337.

[26] Fang Peng, Liu Yanfei, Paresh C Sen. A flicker-free single-stage offline LED driver with high power factor[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2015, 3(3): 654-665.

[27] 王立乔, 李占一, 刘乐, 等. 一种无电解电容单级Buck-Boost逆变器[J]. 电工技术学报, 2019, 34(20): 129-139.

Wang Liqiao, Li Zhanyi, Liu Le, et al. A single-stage Buck-Boost inverter without electrolytic capacitor[J]. Transactions of China Electrotechnical Society, 2019, 34 (20): 129-139.

[28] Fang Peng, Sheng Bo, Samuel W, et al. LED driver achieves electrolytic capacitor-less and flicker-free operation with an energy buffer unit[J]. IEEE Transa- ctions on Power Electronics, 2019, 34(7): 6777-6793.

[29] John C W L, Praveen K J. Isolated AC/DC offline high power factor single-switch LED drivers without electrolytic capacitors[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2015, 3(3): 679-690.

[30] John C W L, Praveen K J. A high power factor, electrolytic capacitor-less AC-input LED driver topology with high frequency pulsating output current[J]. IEEE Transactions on Power Electronics, 2015, 30(2): 943-955.

[31] Hu Haibing, Souhib H, Fang Xiang, et al. A three-port flyback for PV microinverter applications with power pulsation decoupling capability[J]. IEEE Transactions on Power Electronics, 2012, 27(9): 3953-3964.

[32] Shimizu T, Wada K, Nakamura N. Flyback-type single-phase utility interactive inverter with power pulsation decoupling on the DC input for an AC photovoltaic module system[J]. IEEE Transactions on Power Electronics, 2006, 21(5): 1264-1272.

[33] Qiu Yajie, Wang Laili, Wang Hongliang, et al. Bipolar ripple cancellation method to achieve single- stage electrolytic-capacitor-less high-power LED driver[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2015, 3(3): 698-713.

[34] 张超, 胡鑫, 朱孝勇, 等. 基于微升压功率解耦电路的无电解电容驱动系统研究[J]. 电工技术学报, 2019, 34(16): 3322-3332.

Zhang Chao, Hu Xin, Zhu Xiaoyong, et al. Research on non electrolytic capacitor drive system based on micro Boost power decoupling circuit[J]. Transactions ofChina Electrotechnical Society, 2019, 34(16): 3322-3332.

Virtual Three-Port Network for Single-Stage Bridgeless Rectifier with Power Decoupling Capability

Abstract In order to eliminate the influence of electrolytic capacitors on the life of high-brightness light-emitting diodes (HB-LEDs) and cater to the lightweight design concept, a single-stage bridgeless virtual three-port rectifier with power decoupling capability is proposed. This topology uses path optimization to shorten the energy transmission path, and achieves multi-level integration through power device sharing, which greatly improves device utilization and circuit power density. The virtual third port is dedicated to power decoupling, which effectively alleviates the system's dependence on large capacitance and provides the possibility for film capacitors to replace electrolytic capacitors. In addition, the proposed converter can realize power factor correction (PFC), and the control unit is simple and easy to implement. The paper analyzes the working principle of the converter and details the parameter design of the key circuit. Finally, the superiority of the rectifier is verified by an experimental prototype with a rated output power of 90W.

keywords:Electrolytic capacitor, power factor correction (PFC), power decoupling, three-port rectifier

DOI: 10.19595/j.cnki.1000-6753.tces.210410

中图分类号:TM46

田涵雷 男 1993年生,博士研究生,研究方向为电能变换和电能质量控制。E-mail: thledu@stu.scu.edu.cn

梁国壮 男,1968 年生,硕士,副教授,研究方向为电机电器及其控制、电气参数检测与信息处理技术。E-mail: Guozhuangliang@hebust.edu.cn(通信作者)

国家自然科学基金(61876059)和中央高校基础科研业务费专项资金(YJ201909)资助项目。

收稿日期 2021-03-24

改稿日期 2021-05-20

(编辑 陈 诚)