图1 图腾柱无桥PFC拓扑

Fig.1 Topology of totem-pole PFC recticier

摘要 该文提出基于低高度平面电感的GaN-Si混合型图腾柱无桥功率因数校正器(PFC),利用工频Si二极管的慢恢复特性为高频GaN开关桥臂提供反向电流通路,实现临界电流导通模式无桥PFC和高频GaN开关桥臂的软开关运行。为了实现低高度和高功率密度,提出低高度平面电感结构及其优化设计方法,通过将临界电流导通模式下的电感电流进行分解,给出高频电感磁心和绕组损耗分析模型,并据此对电感结构尺寸进行优化设计。最后制作一台开关频率为200~700kHz、400W的实验样机,验证了所提出的解决方案的可行性和有效性。

关键词:图腾柱无桥功率因数校正器 氮化镓 平面电感 优化设计

功率因数校正器(Power Factor Corrector, PFC)是实现交流网侧高功率因数、低谐波电流的关键,被广泛应用于电源适配器、LED驱动、服务器电源等各类AC-DC电源系统中[1-5]。消费类电子的快速发展,对高效率、小型化/便携式、低成本AC-DC电源的需求愈加强烈。

在众多的PFC电路结构中,图腾柱无桥PFC具有结构简单、导通损耗低、效率高的突出优势[6-7]。多年来,Si-MOSFET体二极管严重的反向恢复、开关损耗等问题,极大地限制了图腾柱无桥PFC的性能和规模化推广应用[8]。第三代半导体器件氮化镓高电子迁移率晶体管(Gallium Nitride High Electro Mobility Transistor, GaN-HEMT)从根本上避免了体二极管的反向恢复问题,并能够大幅提升变换器的开关频率、降低电路损耗,使得图腾柱无桥PFC重新获得学术界和工业界的重视[9-10]。由于GaN器件的关断损耗小,利用临界导通模式(Boundary Conduction Mode, BCM)实现GaN器件的零电压开通,变换器的开关频率可以实现数量级提升,从而为AC-DC电源的小型化/便携式设计创造条件。为了实现GaN-HEMT的软开关,图腾柱无桥PFC的低频开关桥臂通常采用Si-MOSFET实现,同时采用高频电流检测电路以判断电感电流的过零点,与之相应的还需要配置驱动、控制和辅助电源等电路,增加了PFC的复杂程度、体积和成本。

宽禁带器件技术的发展使得有源开关器件不再是制约变换器体积、质量的主要因素,但高频滤波电感依然是决定电源尺寸、质量和效率的关键[11]。基于印制电路板(Printed Circuit Board, PCB)绕组的平面电感是实现高频滤波电感低高度、小型化的有效途径,如何进一步降低平面电感的高度已经成为超薄电源模块设计和实现的关键。降低平面磁件高度的关键在于降低磁件上下盖板的厚度,而上下盖板的厚度又受限于其磁通密度。为了应对功率磁件薄平化的需求,文献[12-13]提出了矩阵磁解决方案,通过分散磁件然后进行阵列化集成,能够显著降低磁盖厚度,但是会带来磁心总体积的大幅增加和绕组长度及其损耗的大幅上升。文献[14-15]给出了低温共烧陶瓷(Low Temperature Co-fired Ceramic, LTCC)钳入式电感解决方案,将电源中的磁性器件集成在陶瓷基板中,使得电源模块的体积和高度大幅降低,但对制作工艺要求较高。针对超高频应用,文献[16]提出了空心变压器和空心电感方案,磁件高度进一步降低。

本文提出基于低高度平面电感的GaN-Si混合型图腾柱无桥PFC,高频开关桥臂采用GaN-HEMT,低频桥臂采用Si二极管,利用二极管的慢恢复特性为高频GaN开关桥臂提供反向电流通路,实现开关管的零电压开关,采用优化的磁心结构,能显著降低磁心高度,并对磁心尺寸进行优化,实现了电感结构的高度为7.2mm。

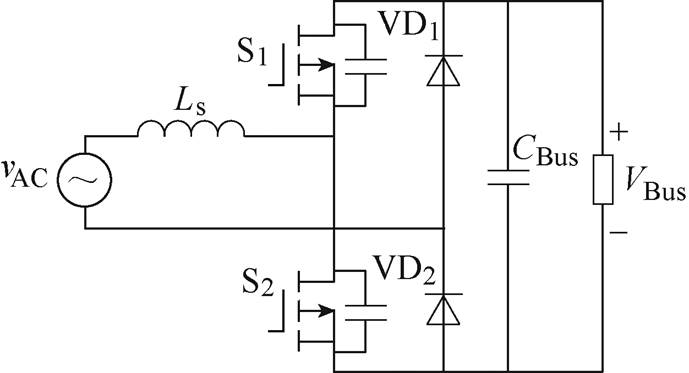

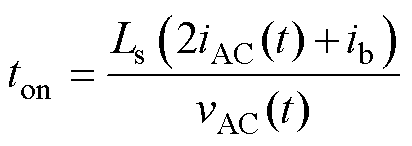

图1为图腾柱无桥PFC拓扑,S1和S2为GaN开关管,两开关高频互补导通;VD1和VD2为工频慢恢复Si二极管,利用工频二极管的慢恢复特性为高频开关桥臂的软开关提供电流通路。相比于Si MOSFET,二极管的尺寸更小,且无需隔离驱动、隔离辅助电源和相应的控制逻辑。此外,Si二极管相比于MOSFET可靠性更高、成本更低。

图1 图腾柱无桥PFC拓扑

Fig.1 Topology of totem-pole PFC recticier

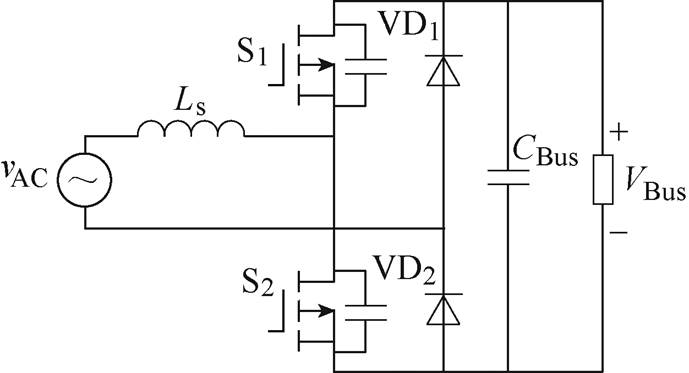

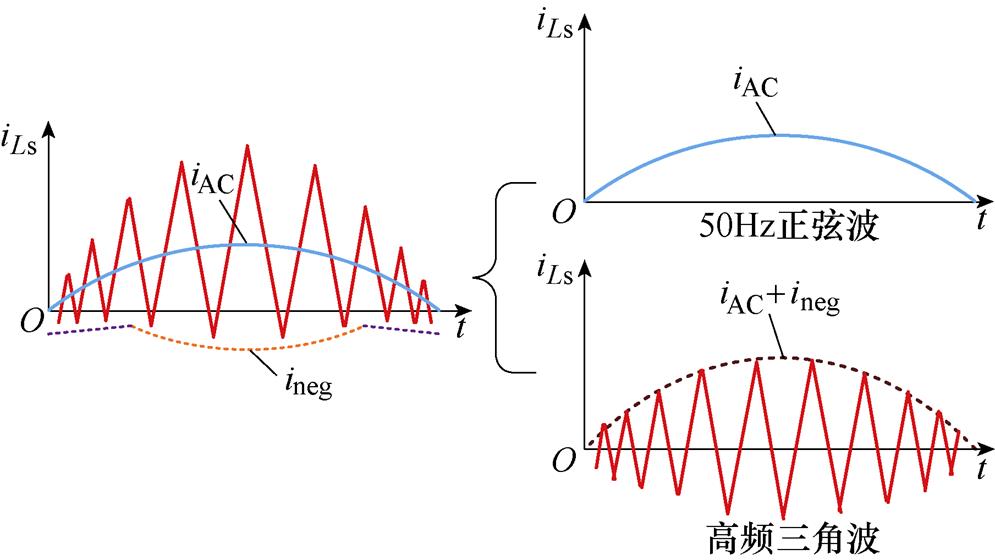

以输入电压正半周为例分析电路工作原理。变换器工作于BCM,电感电流理论波形如图2所示。需要注意的是,高频开关周期内,电感电流存在负电流以实现高频开关GaN器件软开关。变换器共有四种工作模态,图腾柱PFC开关状态如图3所示。

图2 电感电流理论波形

Fig.2 Theoretical waveforms of inductor current

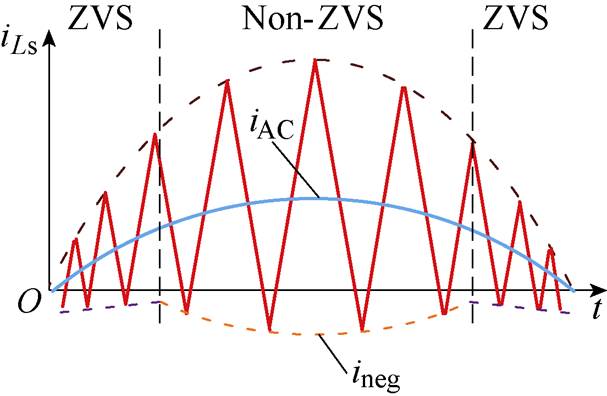

图3 图腾柱PFC开关状态

Fig.3 Switching stages of totem-pole PFC rectifier

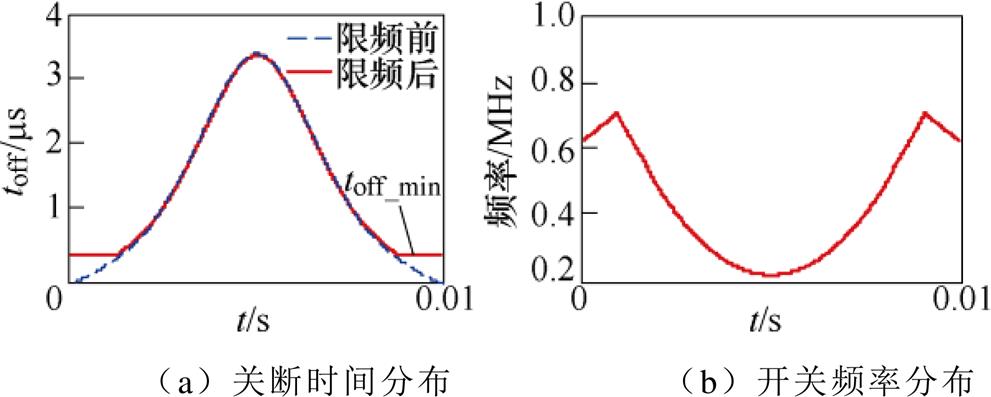

模态一:如图3a所示,S2、VD2导通,S1、VD1关断,交流输入侧将能量传递给电感,电感电流线性增加。开关管S2的导通时间为

(1)

(1)式中,Ls为电感;iAC(t)为输入电流峰值;ib为反向电流边界;vAC(t)为输入电压。

模态二:如图3b所示,当电感电流达到峰值时,开关管S2关断,电感Ls和开关管寄生电容谐振,给S1的寄生电容放电、S2的寄生电容充电,最终使得S1的寄生电容电压为0,S2的寄生电容电压为VBus,此时开关管S1自然实现零电压开通。

模态三:如图3c所示,开关管S1零电压开通,交流输入侧和电感传递能量给直流输出侧,电感电流线性下降,开关管S2关断时间表示为

(2)

(2)模态四:如图3d所示,开关管S1关断,电感Ls和开关管寄生电容谐振,给S1的寄生电容充电,S2的寄生电容放电,若S2的寄生电容电压谐振到零,则开关管S2自然实现零电压开通。

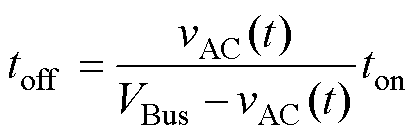

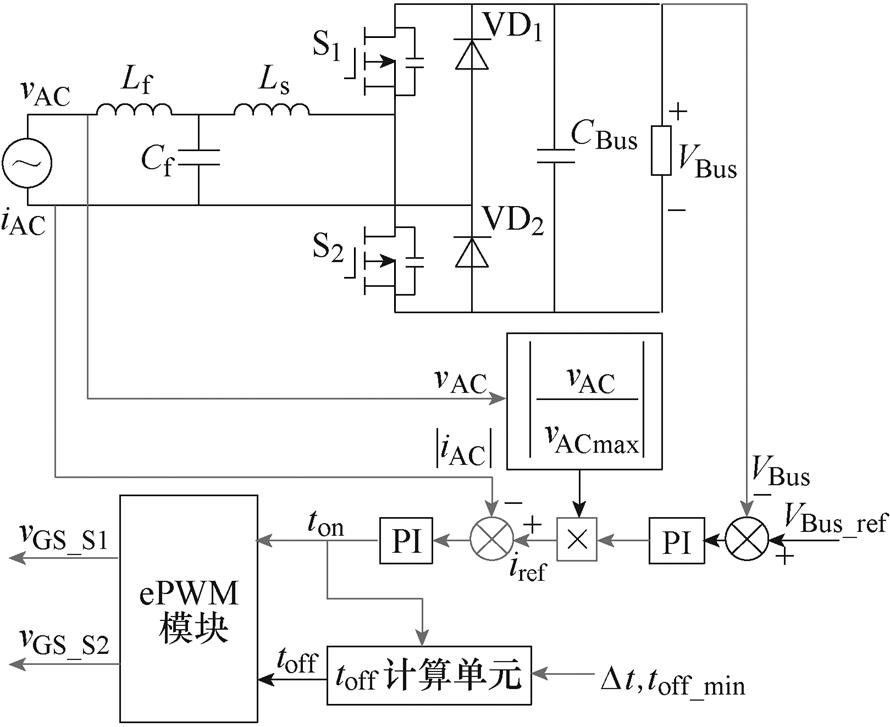

图4为PFC控制框图。当电感电流下降到零时,通过补偿一段开关管关断时间Dt,使其自然产生负电流,开关管结电容电压能谐振到零,实现软开关。关断时间和开关频率分布如图5所示,由式(1)和式(2)可知,轻载时开关频率很高,为了减小开关损耗、提升效率,在输入电压过零点附近限制了关断时间的最小值,如图5a所示,实际开关频率分布如图5b所示。

图4 PFC控制框图

Fig.4 Control block diagram of PFC

图5 关断时间和开关频率分布

Fig.5 toff and frequency distribution

平面电感因其可复制性,加工方便,且功率密度高、散热性好,得到广泛应用。对于高频PFC来说,电感损耗是变换器的主要损耗,电感高度决定变换器的高度,因此高效率、高功率密度、低高度平面电感对整个变换器具有重要意义。

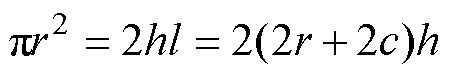

平面磁件由上、下两块磁板和中间的磁柱组成,磁柱高度由PCB厚度、气隙高度、绕组与气隙的避让距离决定,不易调整,上下两块磁板的高度直接决定磁心整体高度。

常见平面电感结构有E型、罐型结构,图6给出了ER型磁心的结构尺寸参数,图中,r为磁心半径,c为绕组宽度,l为磁心宽度,h为磁板厚度。设计时使磁板的磁心有效截面积Ae等于磁柱的Ae,则磁板和磁柱的最大磁通密度相同,磁心的利用率较高,即满足

(3)

(3)

图6 ER磁心尺寸参数

Fig.6 Structure parameters of ER core

从式(3)中可以得到,当磁心的半径r和绕组宽度c确定时,磁板的高度h也相应确定。如果只是减小磁板的高度h,则会导致磁板Ae降低,磁板上的磁通密度增加,工作时产生的磁心损耗大幅上升,甚至产生局部饱和,从而导致整机效率的大幅下降。所以传统E型或罐型平面磁件,其结构限制了磁心进一步薄化的可能。

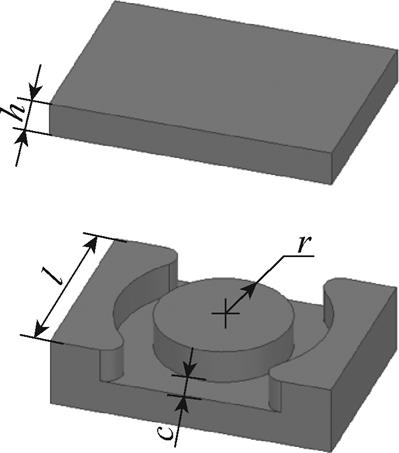

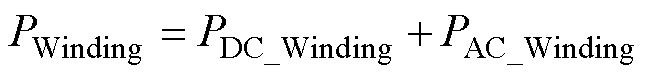

注意到,如果保持磁柱的Ae不变,将磁心沿纵向拉伸,增大磁心宽度l,则磁板的Ae得到有效扩展,此时磁板高度h可以降低,图7为磁心拉伸示意图。

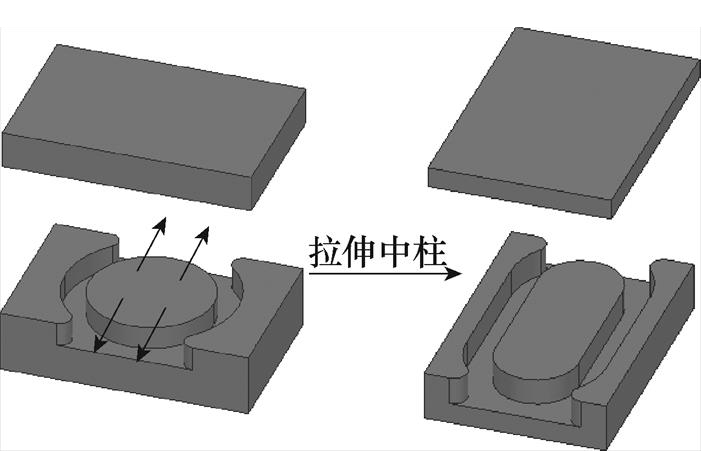

为了验证拉伸磁心方案的有效性,利用Ansys Maxwell 3D有限元软件进行仿真验证。建立图7所示的磁心模型,设置仿真条件为涡流场,激励为频率为300kHz、最大值为2.5A的正弦电流。图8为不同拉伸长度的磁心磁通密度分布,每个磁心的Ae均相同,表1给出了对应的有限元仿真数据。

图7 磁心拉伸示意图

Fig.7 Diagram of stretching core

图8 不同拉伸长度的磁心磁通密度分布

Fig.8 Flux density distribution with different stretching length

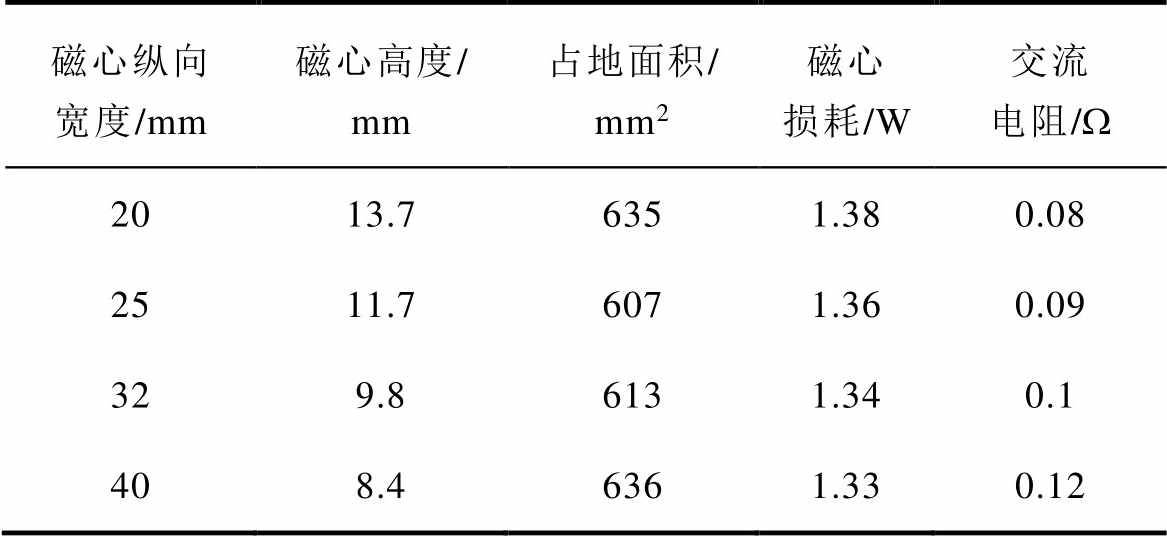

表1 有限元仿真数据

Tab.1 Finite element simulation data

磁心纵向宽度/mm磁心高度/ mm占地面积/ mm2磁心损耗/W交流电阻/W 2013.76351.380.08 2511.76071.360.09 329.86131.340.1 408.46361.330.12

从仿真结果中可以看出,拉伸后磁心高度得到有效降低。由于磁心体积的降低,且磁板上的磁通密度基本不变,磁心损耗也会略微降低。但是在拉伸过程中,由于绕线长度的增加,其交流电阻也会显著增加。因此在拉伸过程中,需要在磁心高度和损耗之间折中。

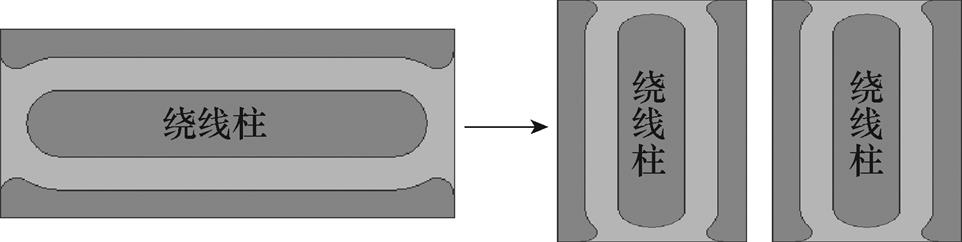

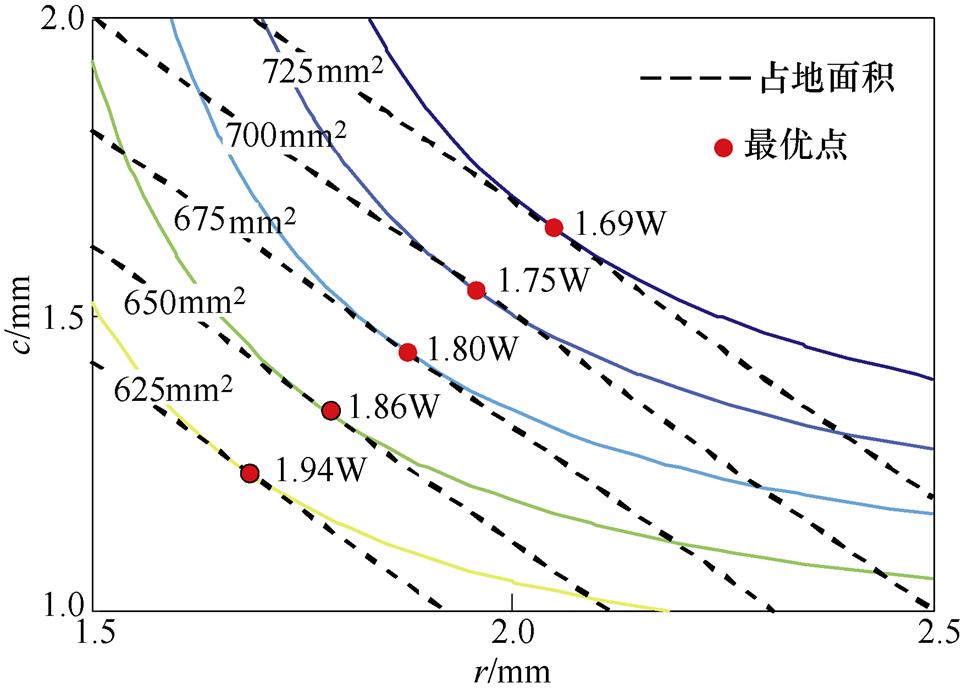

由2.1小节所述,随着拉伸长度的增加,电感高度可以不断降低。但若拉伸长度太大,不利于磁心及PCB绕组在整机中的布局,为了解决该问题,可以将单个电感拆分为两个,如图9所示。

图9 磁心的拆分

Fig.9 Separation of magnetic core

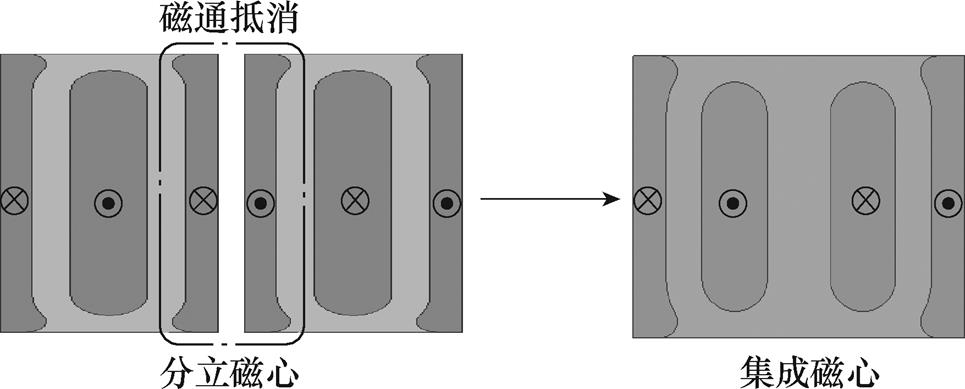

对于上述两个分立磁心,若控制两个磁心内绕组电流方向相反,则两个磁心相邻边柱的磁通方向也相反,从而进行磁通抵消,将两个分立磁心集成到一起,如图10所示。

图10 磁心的集成

Fig.10 Integration of magnetic core

集成后磁心省去了两个边柱,占地面积减小,体积也相应减小,在不影响磁心损耗密度的情况下,磁心集成会带来功率密度的提升。除此之外,在分立磁心中,需要对两个电感进行串联连接,所以会造成额外的端接损耗,而在集成磁心中,两个电感中柱之间没有原先边柱的阻挡,端接损耗可以忽略不计,进一步降低了绕组损耗,提高了效率。

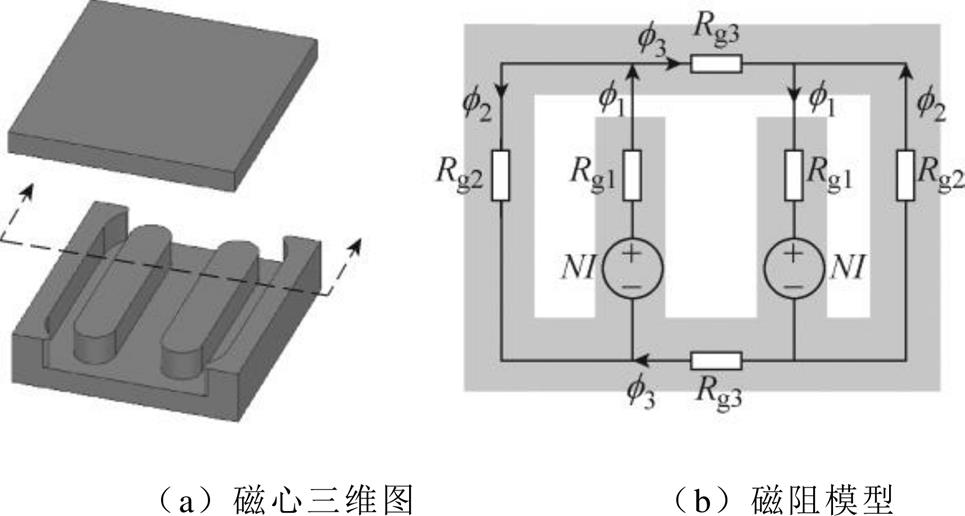

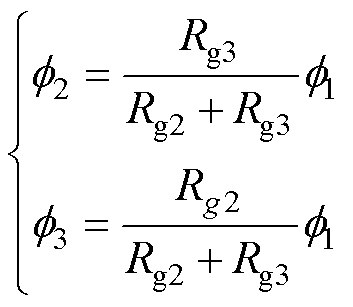

基于图10中的集成双磁柱拉伸结构,图11给出了相应的磁阻模型。其中,NI为绕组电流产生的磁动势,两个绕线柱的磁动势方向相反,Rg1为中柱磁阻和中柱气隙磁阻之和,Rg2为中柱中心和磁盖两个交点处到边柱的磁阻,Rg3为磁盖上两个中柱中心点连线上的磁阻,f1、f2、f3 分别为中柱、边柱和磁板上的磁通。

对图11b所示的磁阻模型进行求解,可得

图11 集成磁心磁阻模型

Fig.11 Reluctance model of integrated core

(4)

(4)由于Rg2与Rg3均是无气隙高磁导率材料的磁阻,其大小比值约为磁通路径长度之比,在实际的集成结构中,Rg3略小于Rg2,因此f3 会略大于f2。

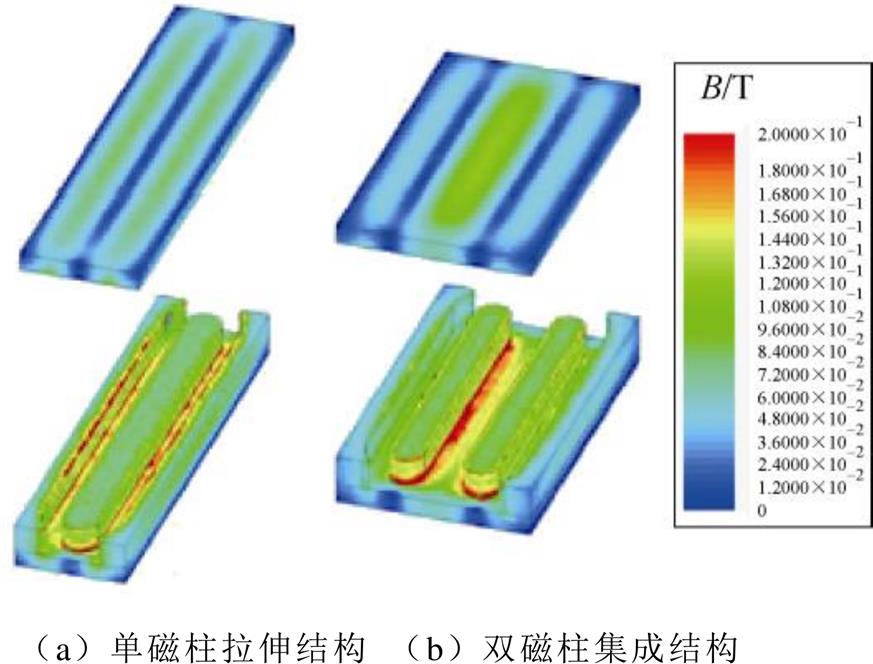

为了验证集成磁心方案的有效性,利用Maxwell 3D软件进行有限元仿真。建立单磁柱拉伸和双磁柱集成磁心模型,设置仿真条件为涡流场,激励是频率为300kHz、最大值为2.5A的正弦电流。不同磁心结构的磁通密度分布如图12所示,磁心集成后,由于磁阻分布的影响,磁盖中部的磁通密度会略微变大,这也与理论分析相一致。

图12 磁心有限元仿真磁通密度分布

Fig.12 Flux density distribution of magnetic cores with finite element simulation

基于图1的图腾柱无桥PFC拓扑及第2节提出的磁心结构,对电感磁件进行相关优化设计。

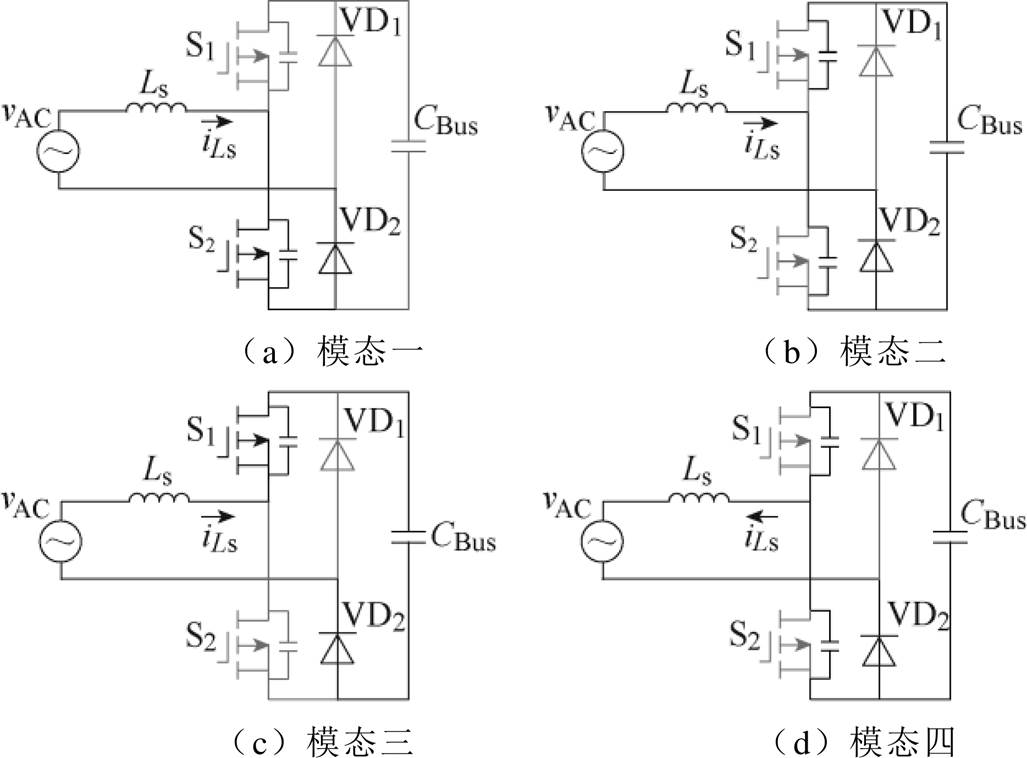

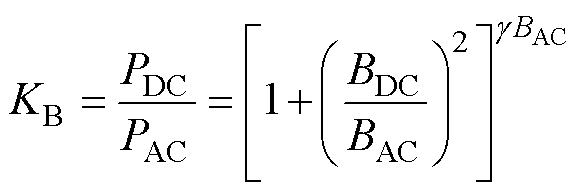

由于电路工作在BCM软开关模式,电感电流为50Hz正弦波和高频三角波的叠加,求解磁心损耗时,在正弦波激励下的传统斯坦梅茨公式在这种情况下并不适用。且电感电流在一个工频周期内不断变化,难以用有限元软件仿真得到磁心损耗。

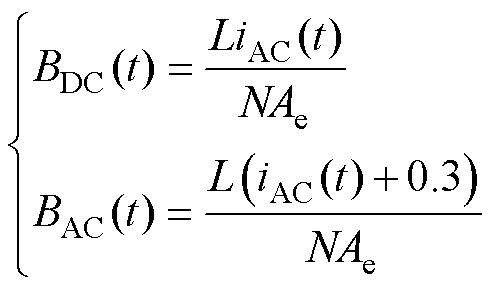

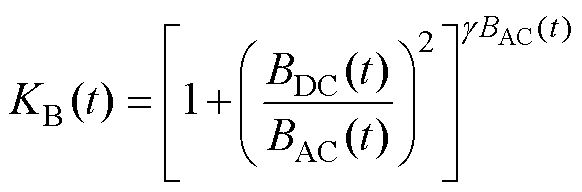

将电感电流波形进行分解,拆分为一个工频正弦波和一个高频三角波,电感电流分解如图13所示。电感负电流ineg在一个工频周期内随时间变化,为了简化计算,将其全部设为-0.3A。工频正弦波定义为iAC(t),高频三角波的最大值包络线为iAC(t)+ 0.3A。工频正弦波产生直流偏磁,高频三角波产生交流磁心损耗,文献[17]给出了一种直流偏磁下的磁心损耗计算方法,引入系数KB,表示在直流偏磁下的磁心损耗和无直流偏磁下的磁心损耗之比,表达式为

(5)

(5)式中,BDC为直流偏置作用下的最大磁通密度;BAC为交流分量作用下的最大磁通密度;g 为修正系数,g =6.894。

图13 电感电流分解

Fig.13 Decomposition of inductor current

针对图13的电流波形,在任意时刻t,直流磁通密度BDC(t)与交流磁通密度BAC(t)可以表示为

(6)

(6)式中,L为电感值;N为电感匝数;Ae为磁心有效截面积。此时系数KB的表达式为

(7)

(7)

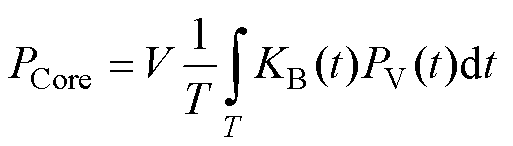

图5b给出了开关频率随时间变化的曲线,据此可以得到开关频率随时间变化的函数表达式。采用斯坦梅茨公式计算高频三角波激励下每个开关周期的单位体积磁心损耗为

(8)

(8)式中,Cm、x、y为磁心材料手册所提供的系数,为了得到一个工频周期内的磁心总损耗,则需要对表达式进行积分得

(9)

(9)

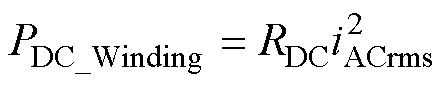

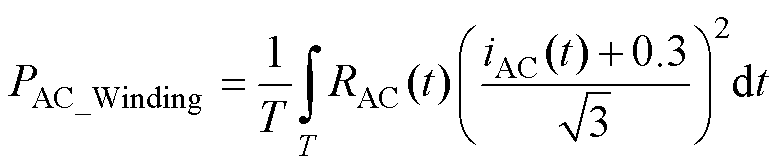

对于绕组损耗部分,可分为直流绕组损耗和交流绕组损耗,工频正弦波产生直流绕组损耗,高频三角波产生交流绕组损耗,直流绕组损耗为

(10)

(10)式中,iACrms为50Hz正弦波电流的有效值;RDC为直流电阻,可以通过计算得到。

交流绕组损耗的求解需要用到交流电阻值,但交流电阻值受到趋肤效应、临近效应及气隙边缘效应的影响,且频率越高,交流电阻值越大。于是采用有限元软件仿真得到不同频率下的交流电阻,从而得到交流电阻随频率的变化关系。且开关频率随时间的变化关系已知,则交流电阻随时间的变化关系也可得到。通过在半个工频周期内进行积分,可得到绕组的交流损耗为

(11)

(11)总的绕组损耗为

(12)

(12)

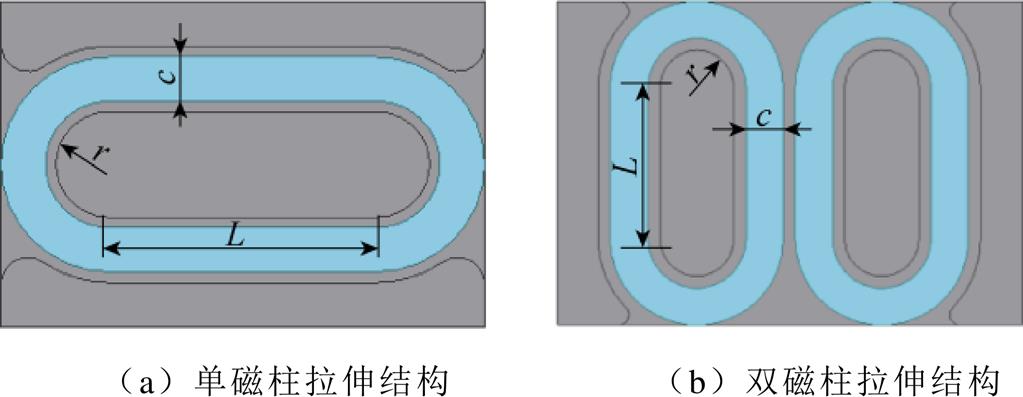

图14给出了单磁柱拉伸结构和双磁柱拉伸结构磁心结构。考虑PCB绕组板厚、气隙高度及绕组和气隙的避让距离,磁柱高度定为3.2mm,考虑磁板加工能力,磁板高度定为2mm,因此磁心总高度给定为7.2mm。要确定最终电感的尺寸,关键参数为绕线柱半圆半径r、长L及绕组宽度c。以单磁柱设计为例,下面给出设计过程。

图14 磁心结构

Fig.14 Diagram of magnetic core

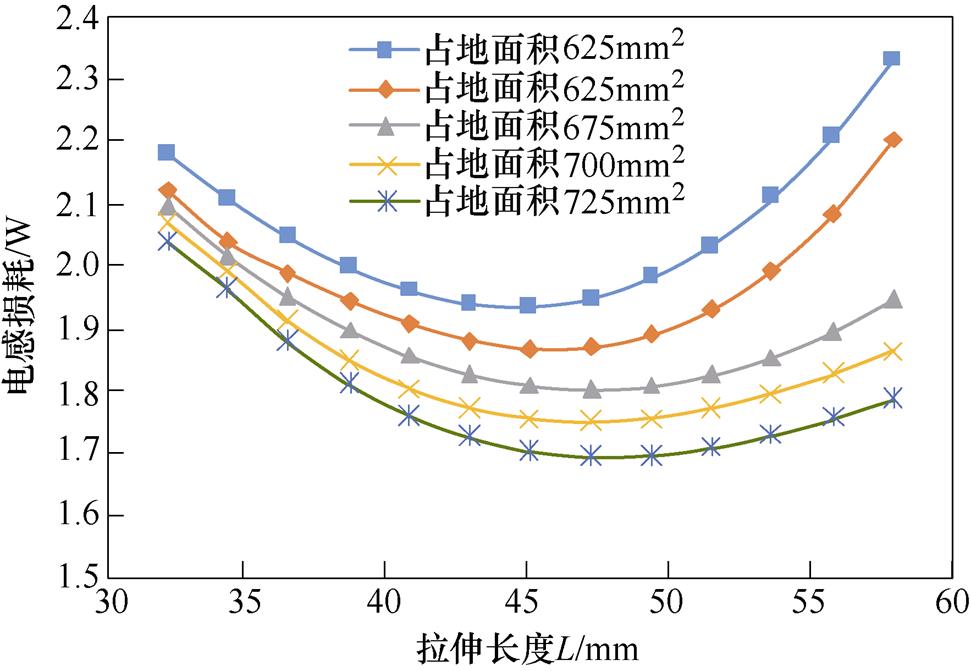

首先固定L,例如,当L=45mm时,扫描不同r、c,根据上述损耗模型,得到不同占地面积下的损耗等高线,如图15所示。实曲线为电感损耗的等高线,虚直线为等占地面积线,两簇曲线的切点则代表在该占地面积下损耗最小的尺寸点,即最优设计点。将这些最优设计点记录下来,然后改变L,得到不同L、不同占地面积下的最优设计点,并绘制在一张图中,如图16所示。

图15 电感损耗-占地面积曲线

Fig.15 Curves of inductor loss-footprint

图16 不同占地面积下电感损耗-拉伸长度曲线

Fig.16 Curves of inductor loss-tensile length under different footprint

从图16中可以看出,在确定占地面积和磁心高度的前提下,随着拉伸长度的增加,电感总损耗先减小后增加,即存在一个拉伸长度使电感损耗最低,该点即为电感的最优设计点。

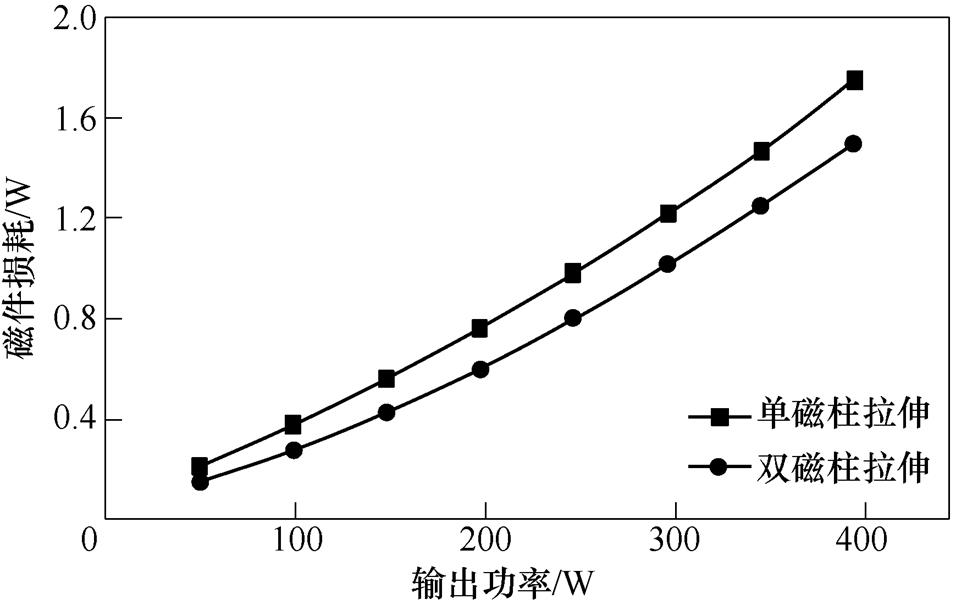

以相同方法对双磁柱拉伸结构进行设计。考虑样机布局,选择占地面积700mm2为设计点,单磁柱拉伸结构的最优尺寸为:r=2.2mm,L=44mm,c= 1.2mm。双磁柱拉伸结构的最优尺寸为:r=1.8mm,L=26.8mm,c=1.2mm。图17给出了两种电感结构在相同高度、相同占地面积下,理论损耗随输出功率变化曲线。仿真结果表明,双磁柱拉伸结构在全负载范围内具有更小的损耗,更利于磁件的低高度设计。

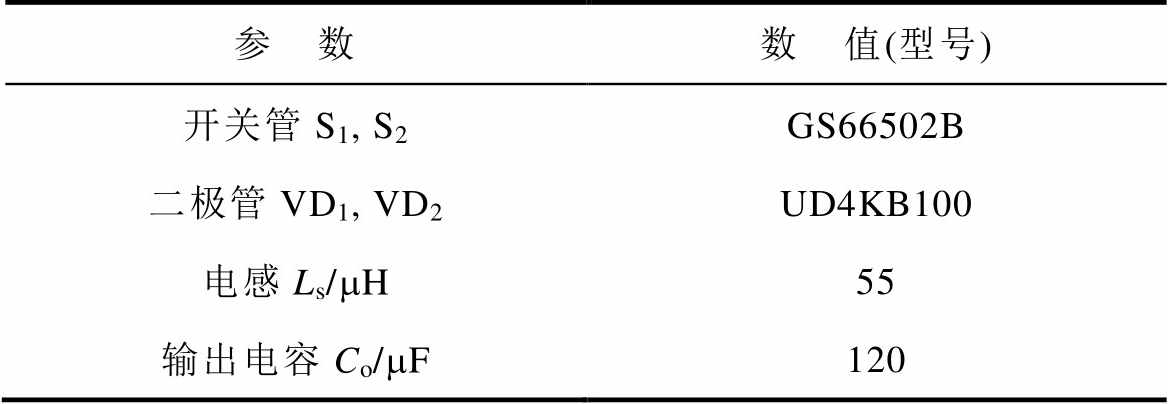

搭建了一台AC 220V输入、DC 400V输出、功率400W的GaN-Si混合型图腾柱无桥PFC变换器。样机关键参数见表2。系统对交流侧输入电压、输入电流及直流侧电压进行采样,经过信号转换、处理电路后送至控制单元,处理器采用TI公司的DSP芯片DSP28075。

图17 电感损耗随功率的变化关系

Fig.17 Relationship between inductor loss and power

表2 样机关键参数

Tab.2 Key parameters of the prototype

参 数数 值(型号) 开关管S1, S2GS66502B 二极管VD1, VD2UD4KB100 电感Ls/mH55 输出电容Co/mF120

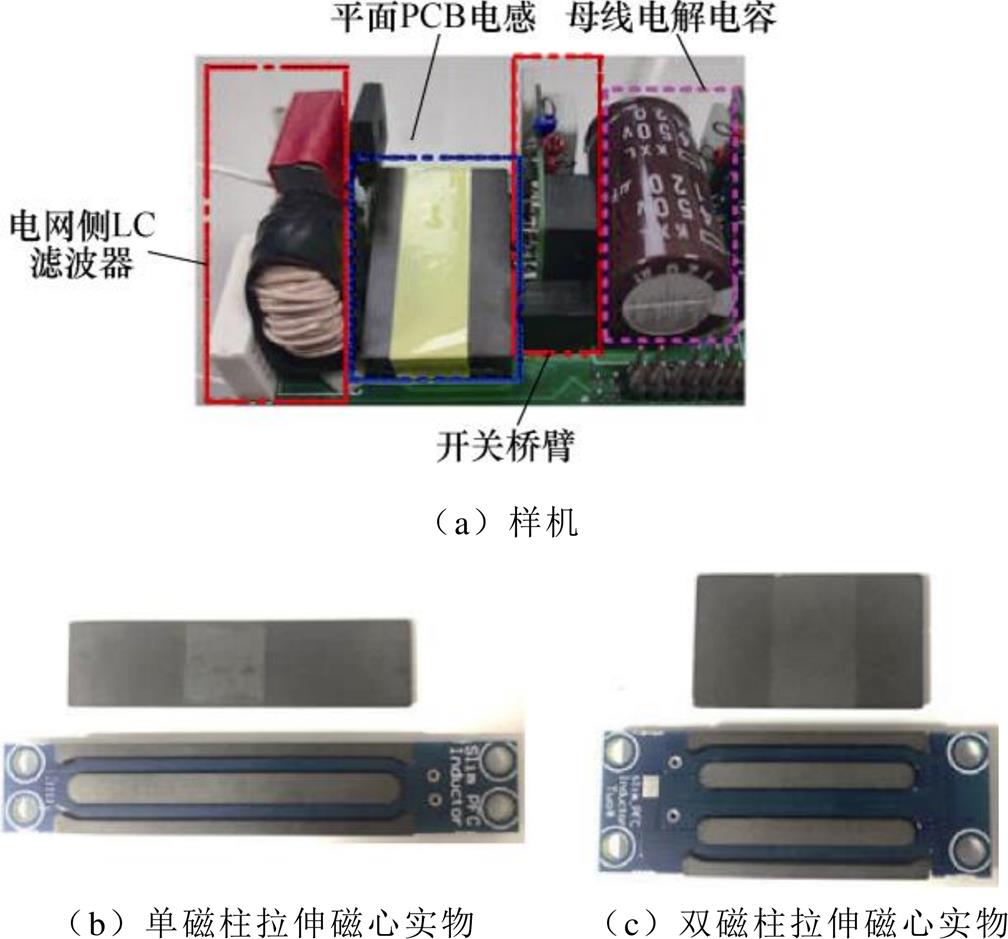

为了验证理论分析的正确性,分别在最优设计点下制作两种电感磁心,样机及磁心如图18所示。图18a为实验样机,图18b为单磁柱拉伸结构电感磁心实物,图18c为双磁柱拉伸结构电感磁心实 物。两种磁心的占地面积均为700mm2,高度均为7.2mm。

图18 样机及磁心

Fig.18 Picture of prototype and core

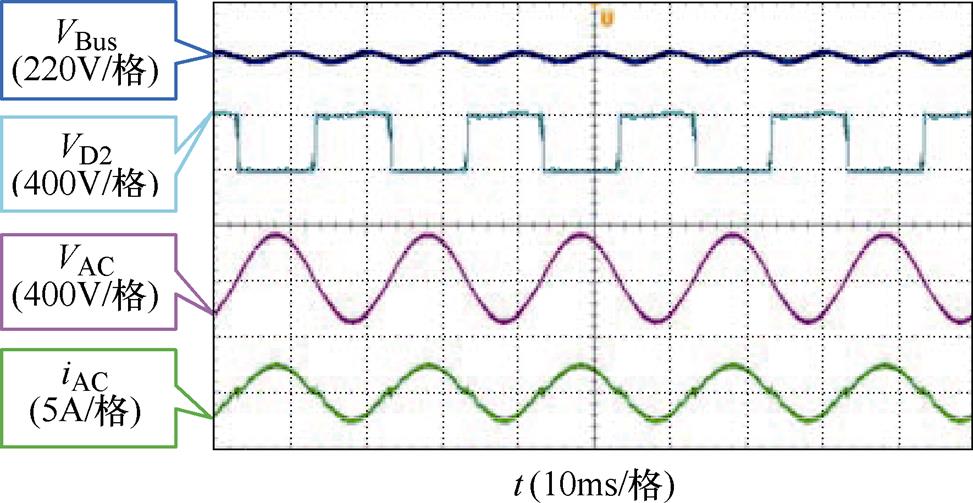

母线电压、二极管VD2电压、电网电压和电流波形如图19所示。可以看出,在电网电压正半周,二极管VD2常通,并且在过零点附近没有高频开关。输入电流跟踪电网电压的效果良好,实现了功率因数校正的功能。

图19 母线电压、二极管VD2电压、电网电压和电流波形

Fig.19 The experimental waveforms of VBus, vD2, vAC and iAC

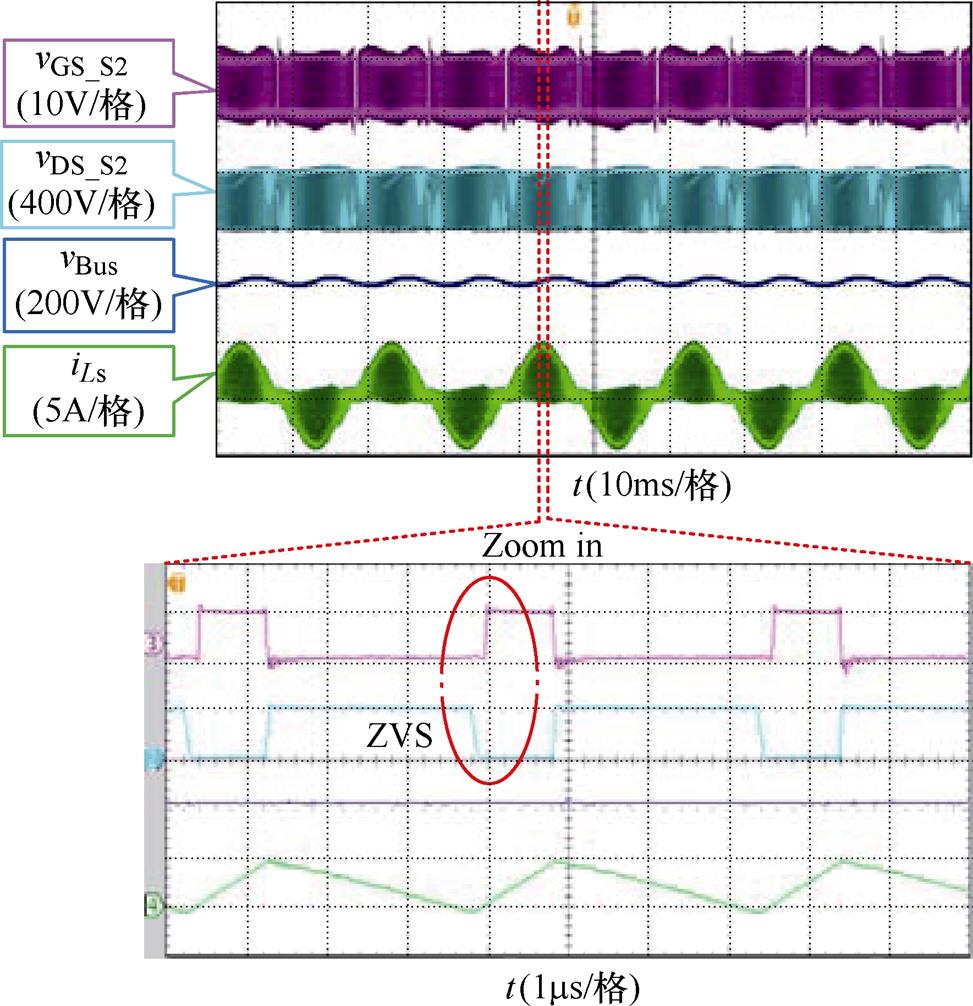

图20为输出功率300W时的实验波形。VBus为母线电压,vGS_S2和vDS_S2分别为开关管S2的驱动电压和漏源极电压,iLs为电感电流。母线电压稳定在400V,在电网电压峰值附近,电感电流工作在BCM,开关管实现了零电压开通。

图20 输入300W时实验波形

Fig.20 The experimental waveforms at 300W

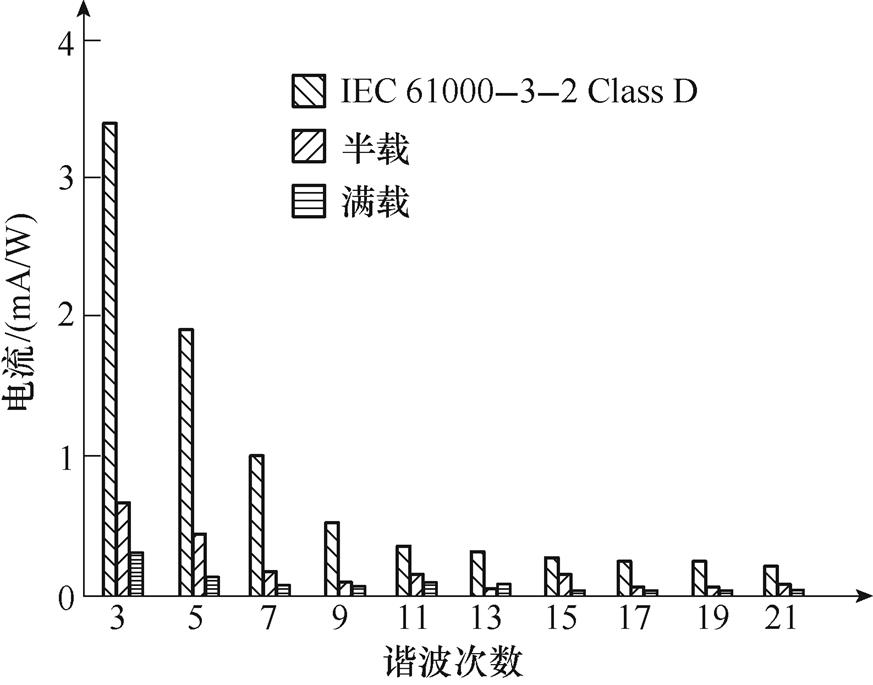

图21为满载和半载情况下输入电流的谐波含量,每次谐波电流均满足IEC 61000-3-2 Class D的标准,实验测试满载功率因数为99.7%。

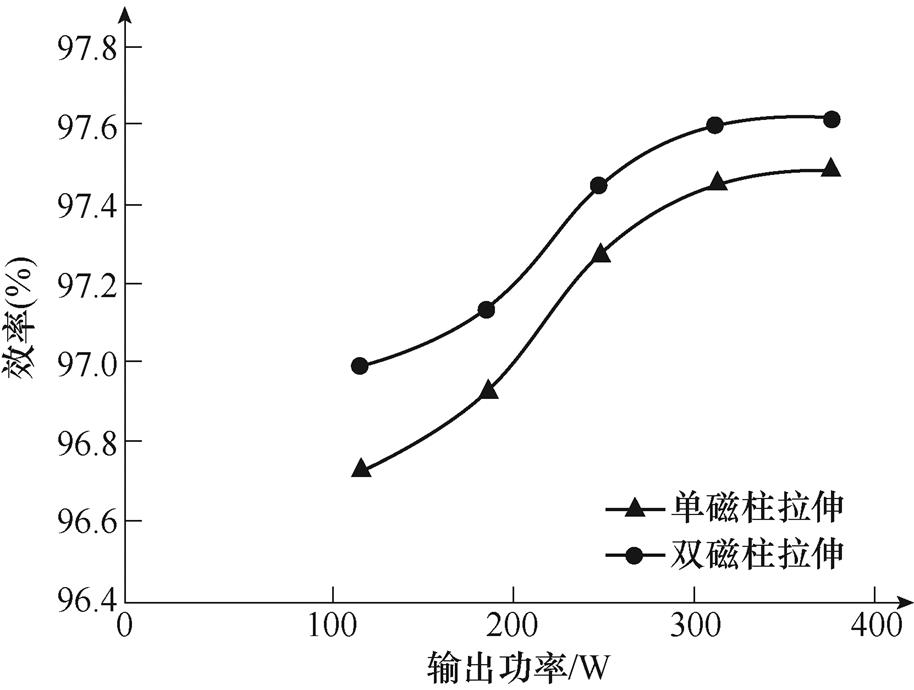

图22为变换器效率曲线,两组效率曲线的差别仅在于更换了电感。使用双磁柱拉伸结构平面电感的满载效率为97.61%,使用单磁柱拉伸结构平面电感的满载效率为97.48%,在全负载范围内,第一种电感的效率比第二种电感大0.1%以上。实验结果显示了双磁柱拉伸磁心结构的优越性。

图21 输入电流的谐波含量

Fig.21 The harmonic content in the input current

图22 效率曲线

Fig.22 Efficiency curves

本文针对高效率、小型化/便携式、低成本AC-DC电源需求,提出了一种基于低高度平面电感的GaN-Si混合型图腾柱无桥PFC。

1)提出了GaN-Si混合型图腾柱无桥PFC,利用工频Si二极管的慢恢复特性,为高频GaN开关桥臂提供反向电流通路,从而实现软开关。

2)提出了优化的磁心结构,能够减小平面电感的高度,并建立了BCM下PFC电感的损耗计算模型。

3)给出了电感优化设计流程,搭建了一台400W图腾柱PFC样机,验证了所提出的拓扑结构与磁心结构。相比于单磁柱拉伸磁心结构,双磁柱拉伸磁心结构在全负载范围内效率提升了0.1%~0.25%。本文所提出的低高度电感磁心结构及电感尺寸优化过程,对于进一步提高PFC变换器的效率和功率密度具有一定参考价值。

致谢:感谢横店集团东磁股份有限公司为本文研究提供高频磁心。

参考文献

[1] 阎铁生, 李明洪, 周国华, 等. 一种一次侧控制的Buck-Flyback单级功率因数校正变换器LED驱动电路[J]. 电工技术学报, 2019, 34(16): 3355-3365.

Yan Tiesheng, Li Minghong, Zhou Guohua, et al. A Buck-Flyback single-stage power factor correction converter for LED driving circuit with primary-side control[J]. Transactions of China Electrotechnical Society, 2019, 34(16): 3355-3365.

[2] 曹勇, 杨飞, 李春晖, 等. 不同耦合系数下的交错并联电流连续模式Boost功率因数校正变换器的传导电磁干扰[J]. 电工技术学报, 2019, 34(10): 2176- 2186.

Cao Yong, Yang Fei, Li Chunhui, et al. Conducted electromagnetic interference of interleaved conti- nuous current mode Boost power factor correction converter with different coupling coefficients[J]. Transactions of China Electrotechnical Society, 2019, 34(10): 2176-2186.

[3] 孟宪增, 孟涛, 贲洪奇. 基于无源钳位方式的三相单级全桥功率因数校正变换器电压尖峰抑制策略[J]. 电工技术学报, 2019, 34(6): 3373-3385.

Meng Xianzeng, Meng Tao, Ben Hongqi, et al. A voltage spike suppression strategy based on passive clamp circuit for the three-phase single-stage full- bridge power factor correction converter[J]. Transa- ctions of China Electrotechnical Society, 2019, 34(6): 3373-3385.

[4] 梁国壮, 田涵雷, 王子园, 等. 一种单级无桥式高功率因数无电解电容AC-DC LED驱动器[J]. 电工技术学报, 2019, 34(16): 3396-3407.

Liang Guozhuang, Tian Hanlei, Wang Ziyuan, et al. A single-stage bridgeless, electrolytic capacitor-free AC-DC LED driver with high power factor[J]. Transactions of China Electrotechnical Society, 2019, 34(16): 3396-3407.

[5] 陈文博, 程红, 王聪. 三相无桥功率因数矫正器开路故障的快速诊断与定位策略[J]. 电工技术学报, 2019, 34(18): 3873-3883.

Chen Wenbo, Cheng Hong, Wang Cong. A fast open circuit fault diagnosis and location strategy for three- phase bridgeless power factor corrector[J]. Transa- ctions of China Electrotechnical Society, 2019, 34(18): 3873-3883.

[6] Huang Qingyun. Review of GaN totem-pole brid- geless PFC[J]. CPSS Transactions on Power Elec- tronics and Applications, 2015, 2(3): 124-125.

[7] Huang Qingyun, Ma Qingxuan, Yu Ruiyang, et al. Improved analysis, design and control for interleaved dual-phase ZVS GaN-based totem-pole PFC rectifier with coupled inductor[C]//IEEE Applied Power Electronics Conference and Exposition, San Antonio, 2018: 2077-2083.

[8] Zhao Chenkai, Wu Xinke. ZVS accurate operating analysis of boundary mode totem-pole Boost PFC converter considering the reverse recovery of MOSFET[J]. IEEE Transactions on Power Elec- tronics, 2018, 33(12): 10038-10043.

[9] Zhang Rongchi, Liu Shaobo, Li Binxing, et al. Totem- pole bridgeless Boost PFC converter based on GaN HEMT for air conditioning applications[C]//2nd IEEE Conference on Energy Internet and Energy System Integration, Beijing, 2018: 1-9.

[10] Huang Qingyun, Yu Ruiyang, Ma Qingxuan, et al. Predictive ZVS control with improved ZVS time margin and limited variable frequency range for a 99% efficient, 130W/in3MHz GaN totem-pole PFC rectifier[J]. IEEE Transactions on Power Electronics, 2019, 34(7): 7079-7091.

[11] Fu Minfan, Fei Chao, Yang Yuchen, et al. Optimal design of planar magnetic components for a two-stage GaN-based DC-DC converter[J]. IEEE Transactions on Power Electronics, 2019, 34(4): 3329-3338.

[12] Fei Chao, Lee F C, Li Qiang. High-efficiency high- power-density LLC converter with an integrated planar matrix transformer for high-output current applications[J]. IEEE Transactions on Industrial Electronics, 2017, 64(11): 9072-9082.

[13] Wang Shuo, Wu Hongfei, Lee F C, et al. Integrated matrix transformer with optimized PCB winding for high-efficiency high-power-density LLC resonant converter[C]//IEEE Energy Conversion Congress and Exposition, Baltimore, 2019: 6621-6627.

[14] Wang Laili, Hu Zhiyuan, Liu Yanfei, et al. A horizontal- winding multipermeability LTCC inductor for a low- profile hybrid DC/DC converter[J]. IEEE Transactions on Power Electronics, 2013, 28(9): 4365-4375.

[15] Li Qiang, Dong Yan, Lee F C, et al. High-density low-profile coupled inductor design for integrated point-of-load converters[J]. IEEE Transactions on Power Electronics, 2013, 28(1): 547-554.

[16] Guan Yueshi, Hu Xihong, Zhang Shu, et al. A low profile high frequency LED driving system based on aircore planar inductor[C]//International Power Elec- tronics Conference, Niigata, 2018: 614-618.

[17] 孔剑虹, 何湘宁, 钱照明. 功率变换器电感在直流偏置或矩形波激励时磁损问题研究[J]. 电工技术学报, 2005, 20(5): 13-19.

Kong Jianhong, He Xiangning, Qian Zhaoming. Core losses of magnetic components in power converter topologies[J]. Transactions of China Electrotechnical Society, 2005, 20(5): 13-19.

Hybrid Totem-Pole Bridgeless Power Factor Corrector Converter with GaN HEMT and Si Diode Based on Low Profile Planar Inductor

Abstract A GaN-Si hybrid totem-pole bridgeless PFC converter based on low profile planar inductor is presented in this paper. With the slow reverse recovery characteristics of the low frequency diode, a reverse current path is provided for high frequency GaN switching leg, so that the critical mode operation and the soft-switching can be achieved. In order to achieve lower height and higher power density, a low-profile planar inductor structure and an optimal design method are presented. The calculation method of inductor core loss and winding loss is presented by decomposing the inductor current in CRM mode, and the inductor dimension is optimized. Finally, a 200~700kHz, 400W PFC converter prototype is built to verify the feasibility and effectiveness of the presented scheme.

keywords:Totem-pole power factor corrector, GaN, planar inductor, optimal design

DOI: 10.19595/j.cnki.1000-6753.tces.201428

中图分类号:TM46

邹 军 男,1996年生,硕士,研究方向为电力电子高频磁技术。E-mail: zoujun@nuaa.edu.cn

吴红飞 男,1985年生,教授,博士生导师,研究方向为电力电子高频磁技术、高能效电力变换技术、新能源发电等。E-mail: wuhongfei@nuaa.edu.cn(通信作者)

收稿日期 2020-10-28

改稿日期 2021-01-05

国家自然科学基金(51977105)、江苏省自然科学基金(BK20200017)和江苏省青蓝工程资助项目。

(编辑 陈 诚)