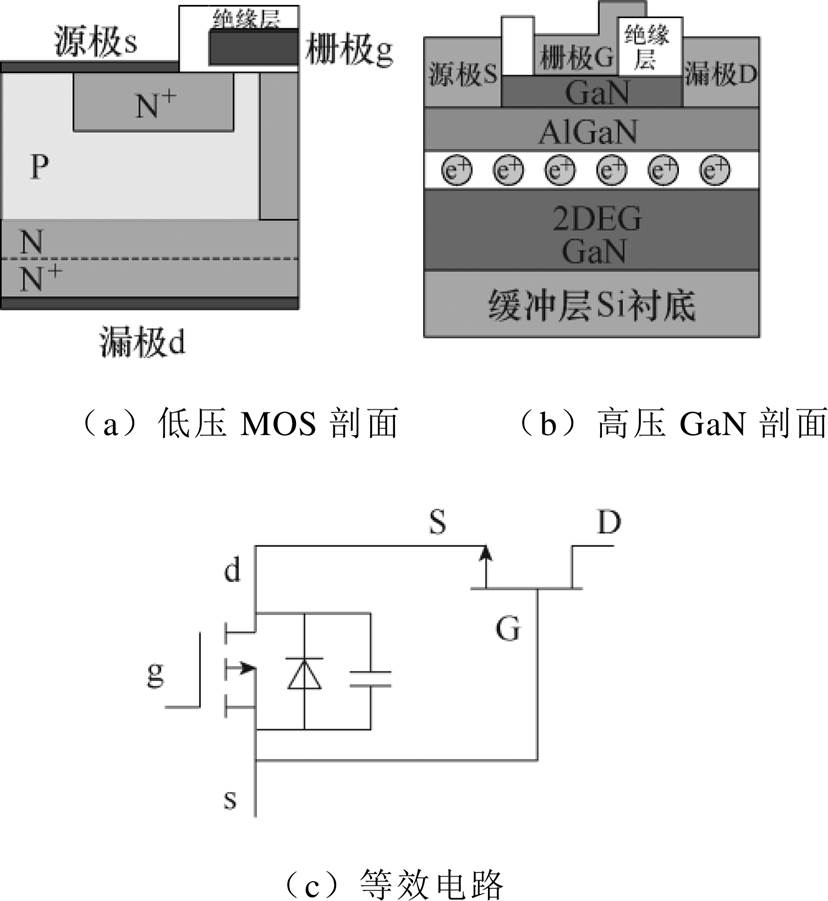

图1 Cascode GaN剖面图及等效电路

Fig.1 Cascode GaN cross-section diagram and equivalent circuit

摘要 为了减小氮化镓驱动电路高频工作时的损耗,针对共栅共源氮化镓高电子迁移率晶体管(Cascode GaN HEMT)提出一种高频谐振驱动电路,采用储能元件替代传统驱动电路中的耗能元件,电感电流为GaN器件栅极电容充/放电,有源密勒钳位电路抑制桥臂串扰。该文重点研究高频谐振驱动电路的工作模态,对电路损耗进行详细分析,给出电感取值的选取原则,并利用PSIM软件对电路进行仿真。最终搭建实验平台对电路的性能进行测试。结果表明,电感为电容充/放电提供低阻抗通路,能有效减小GaN器件驱动电路的电压振荡,明显降低驱动电路的损耗。仿真和实验同时证明了所提出的电路具有较好的性能。

关键词:Cascode GaN高电子迁移率晶体管 高频谐振 驱动电路 串扰抑制 低损耗

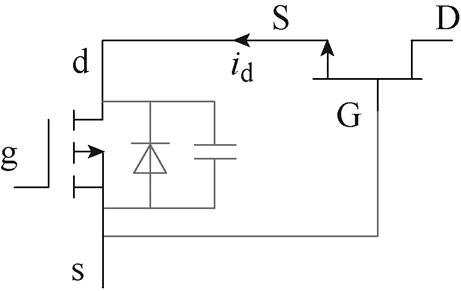

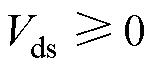

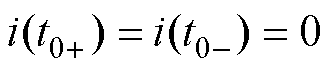

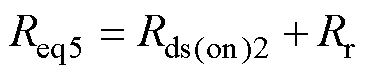

为了减小开关电源设备的体积,提高电源转换效率,电源逐步向高功率密度、低损耗、高频化方向发展,其中,高频化对功率器件的驱动电路提出了新要求。传统硅(Si)器件栅极驱动电路中包含耗能元件,高频工作时,驱动损耗显著增加,已成为限制开关电源发展的关键因数之一[1-2]。宽禁带功率半导体器件的应用,极大地促进了驱动电路技术的发展[3-5]。宽禁带器件具有导通电阻小、寄生参数小、工作频率高的优点,在减小电源体积和提高效率方面具有显著优势[6-8]。目前,共栅共源氮化镓高电子迁移率晶体管(Cascode Gallium Nitride High Electron Mobility Transistor, Cascode GaN HEMT)是由低压MOS管和高压常通GaN组成,其剖面图及等效电路如图1所示。

图1 Cascode GaN剖面图及等效电路

Fig.1 Cascode GaN cross-section diagram and equivalent circuit

GaN器件开关频率可达到数十MHz,若延用传统耗能型驱动电路,会导致电源效率降低。因此,在高频应用中,GaN驱动电路设计尤为重要,它将会直接影响器件的可靠性和稳定性。自GaN器件商用以来,研究者们就着手探寻低功耗、高可靠性的驱动电路。文献[9-10]提出了常通型GaN HEMT器件栅极谐振驱动电路,该类型器件正常情况下为常通状态,极易造成短路故障。文献[11-13]提出了全桥型谐振驱动电路,可以实现能量回馈,部分开关管能实现软开关,具有较高的效率,但所需开关管数量较多,控制相对复杂。文献[14-15]研究了一种抑制串扰的改进驱动电路,通过增加辅助支路抑制串扰,改进的驱动电路可降低时延和损耗。文献[16]详细地研究了SiC器件的静态和动态特性,并基于Saber仿真环境,提出了一种应用于光伏逆变器仿真的建模方法。文献[17]提出了一种脉冲变压器隔离IGBT驱动电路,电路响应速度快,同时具备保护功能,但该电路不适用于高频变换电路。文献[18]研究了一种MHz隔离谐振驱动电路,该电路中的开关管能实现软开关,可有效降低损耗,但驱动电压振铃较大。文献[19]提出了高频变换器的栅极多谐振驱动电路,该振驱动电路不仅节能,还可以缩短电源启动时间,但多谐振驱动波形为准方波,幅值波动大,而增强型GaN器件驱动电压范围窄(通常最大电压为6V),不利于谐振元件参数选取。文献[20]提出了一种GaN HEMT预充电式驱动电路,该电路由4只辅助开关管、电感L和电容C组成,实现了能量回馈,降低了驱动功耗;高/低电平钳位,保证了开关管可靠开通和关断,但该电路开关管数量多、驱动时序繁琐、硬件电路设计复杂。因此,GaN器件的高频驱动电路仍具有研究价值。

为了满足GaN器件高频驱动要求,本文针对Cascode GaN HEMT提出一种高频谐振驱动电路,该电路由开关电路和串扰抑制电路组成。电感为GaN栅极电容充/放电提供一条低阻抗通路,可有效降低功耗,有源密勒钳位电路能有效抑制桥臂串扰。本文分析了Cascode GaN器件的稳态工作特性,重点研究了所提出的高频驱动电路的工作模态;并对各模态的损耗进行了详细分析;还为电路搭建了仿真模型和实验平台,分析了实验结果;最后结合全文得出结论。

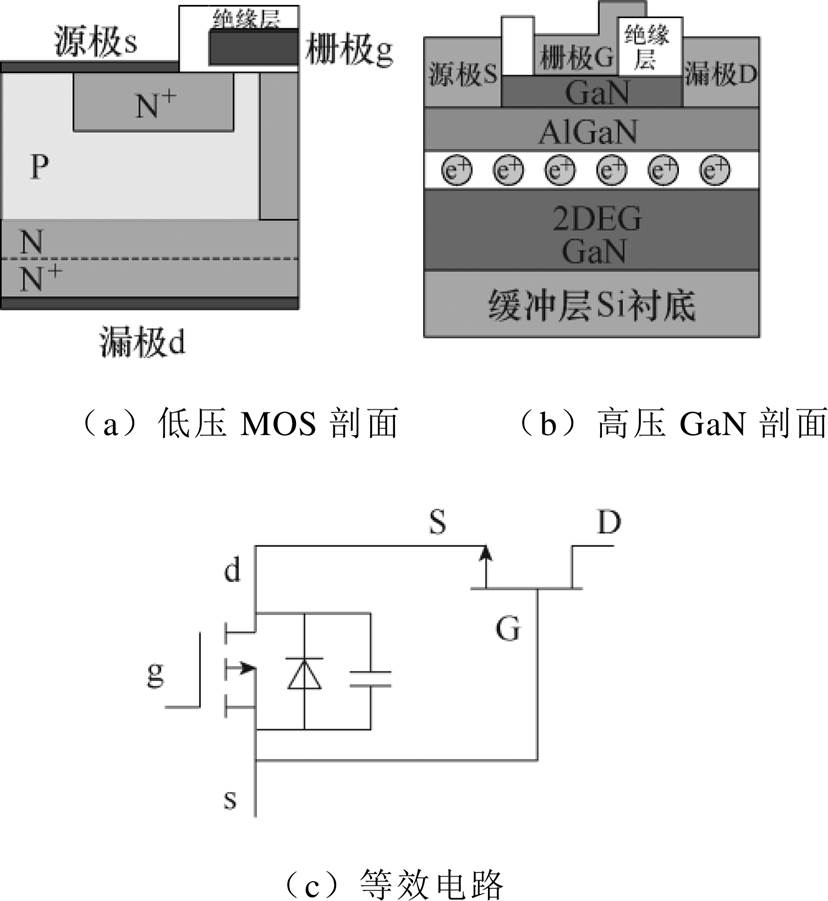

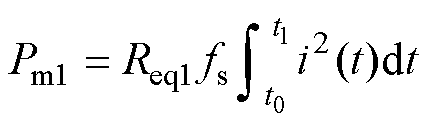

GaN是横向器件,漏极和源极穿过AlGaN层与下层二维电子气(Two-Dimensional Electron Gas,2DEG)形成欧姆接触,并形成电流通路,当2DEG被耗尽时,半绝缘GaN缓冲层阻碍电流流通。GaN器件关断时,需在栅极和源极之间施加负压将2DEG耗尽。GaN为常通器件,漏极与源极之间反向耐压低,不适用于功率变换电路。为了解决这一问题,已有公司采用Cascode结构开发出了适用于高压的GaN器件。Transphorm公司650V高压GaN器件就采用了低压MOS与高压常通GaN级联的结构制备GaN器件。本文以TP65H300G4LSG器件为例,研究一种适用于Cascode GaN的高频驱动电路。该器件输出特性曲线如图2所示。

图2 Cascode GaN输出特性曲线

Fig.2 Cascode GaN output characteristics

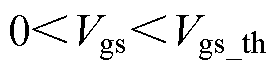

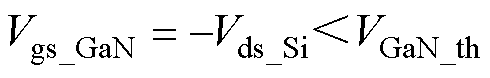

稳态工作时,根据低压MOS管栅源电压 和漏源电压

和漏源电压 的值,可将TP65H300G4LSG分为四种模态:

的值,可将TP65H300G4LSG分为四种模态:

(1)正向导通( ,

, )。当Cascode GaN栅极驱动电压大于阈值电压

)。当Cascode GaN栅极驱动电压大于阈值电压 时,低压MOS管开通,沟道流过的电流为

时,低压MOS管开通,沟道流过的电流为 ,正向导通模态如图3所示。低压MOS管漏源电压

,正向导通模态如图3所示。低压MOS管漏源电压 ,

, 为低压MOS管导通电阻。

为低压MOS管导通电阻。

图3 正向导通模态

Fig.3 Forward conduction mode

由基尔霍夫电压定律(KVL)可得,常通GaN栅源电压

,此时,高压常通GaN处于导通状态,流过沟道电流为id,GaN器件漏源两端的电压为

,此时,高压常通GaN处于导通状态,流过沟道电流为id,GaN器件漏源两端的电压为

,

, 为常通GaN晶体管导通电阻。

为常通GaN晶体管导通电阻。

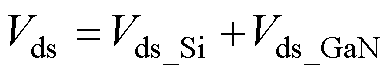

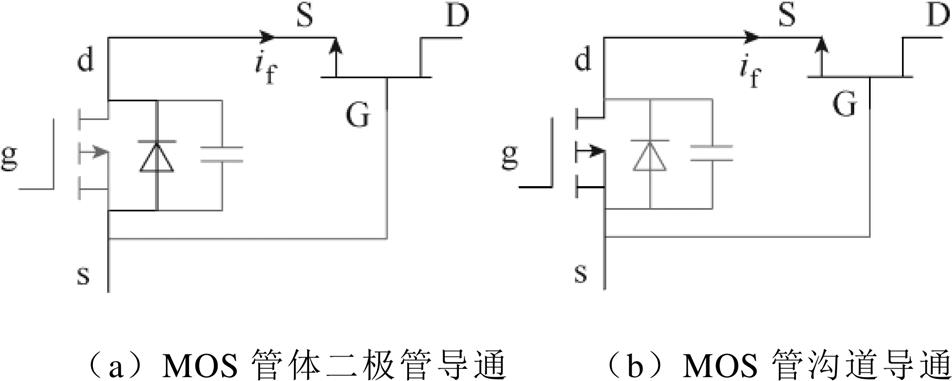

(2)反向恢复( ,

, ,

, )。低压MOS管导通阶段会储存少数载流子,漏源电压

)。低压MOS管导通阶段会储存少数载流子,漏源电压 时,器件关断过程会产生反向恢复电流。此时,电流流经高压常通GaN和低压MOS管的体二极管,反向恢复模态如图4所示。反向恢复结束,流经高压常通型GaN的电流id给低压MOS管寄生电容Cds_Si充电,当-Vds_Si小于常通GaN栅极开启电压VGaN_th时,GaN器件完全截止。

时,器件关断过程会产生反向恢复电流。此时,电流流经高压常通GaN和低压MOS管的体二极管,反向恢复模态如图4所示。反向恢复结束,流经高压常通型GaN的电流id给低压MOS管寄生电容Cds_Si充电,当-Vds_Si小于常通GaN栅极开启电压VGaN_th时,GaN器件完全截止。

图4 反向恢复模态

Fig.4 Reverse recovery mode

(3)正向截止( ,

, )。当

)。当 时,MOS管关断,GaN器件中无电流流通。

时,MOS管关断,GaN器件中无电流流通。

因为

,所以高压常通GaN处于导通状态,GaN器件漏源电压

,所以高压常通GaN处于导通状态,GaN器件漏源电压 ,随着GaN器件漏源电压

,随着GaN器件漏源电压 的逐渐增加,直至

的逐渐增加,直至 时,高压常通GaN处于完全截止状态,GaN器件漏源电压

时,高压常通GaN处于完全截止状态,GaN器件漏源电压 ,

, 为常通GaN的漏源电压。

为常通GaN的漏源电压。

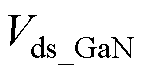

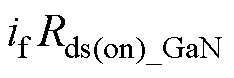

(4)反向导通( )。当Cascode GaN器件栅极电压

)。当Cascode GaN器件栅极电压 时,低压MOS管处于截止状态。GaN器件漏源电压

时,低压MOS管处于截止状态。GaN器件漏源电压 ,故MOS管体二极管导通,其电流为

,故MOS管体二极管导通,其电流为 ,压降为

,压降为 ,常通GaN栅源电压

,常通GaN栅源电压

,GaN器件反向导通,如图5a所示,此时,GaN器件漏源电压

,GaN器件反向导通,如图5a所示,此时,GaN器件漏源电压

。

。

图5 反向导通模态

Fig.5 Reverse conduction mode

当Cascode GaN器件栅极电压 时,MOS管处于导通状态。由于GaN器件漏源电压

时,MOS管处于导通状态。由于GaN器件漏源电压 ,反向电流

,反向电流 由低压MOS管和常通型GaN器件的沟道流通,如图5b所示。此时,GaN器件反向导通,漏源电压

由低压MOS管和常通型GaN器件的沟道流通,如图5b所示。此时,GaN器件反向导通,漏源电压 。

。

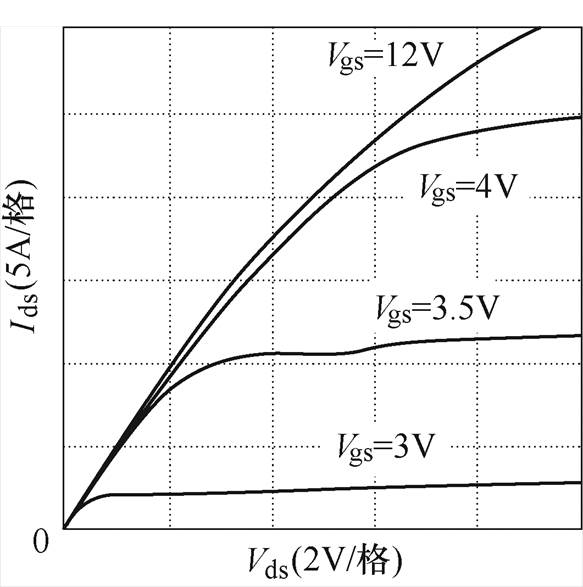

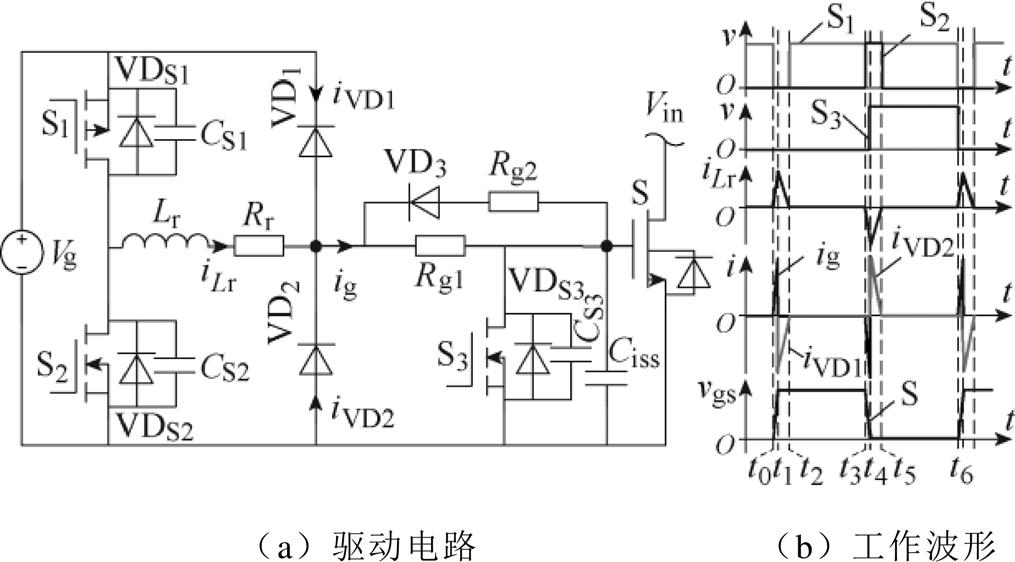

本文所提出的高频驱动电路及工作波形如图6所示。驱动电路由2只MOS管S1、S2,2只二极管VD1、VD2,谐振电感Lr和串扰抑制电路S3组成。其中,图腾柱电路上管为PMOS,下管为NMOS,Rr为电感Lr的等效电阻,Rg1、Rg2为栅极驱动电阻,Ciss为GaN栅极等效电容,VD3、Rg1和Rg2分别提供两条不同电流路径,二极管VD1和VD2提供能量回馈路径,iLr为流过谐振电感电流,ig为驱动电流,iVD1和iVD2分别为流过二极管VD1、VD2的电流。

图6所提出的驱动电路中,开关管S3构成串扰抑制电路,当开关管S开通时,S3截止,寄生电容CS3 Ciss,故开通过程中可忽略CS3的影响;当开关管S关断时,S3开通,S栅极电压被钳位,能有效抑制开关管串扰。

Ciss,故开通过程中可忽略CS3的影响;当开关管S关断时,S3开通,S栅极电压被钳位,能有效抑制开关管串扰。

图6 所提出的驱动电路及工作波形

Fig.6 The proposed drive circuit and working waveforms

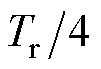

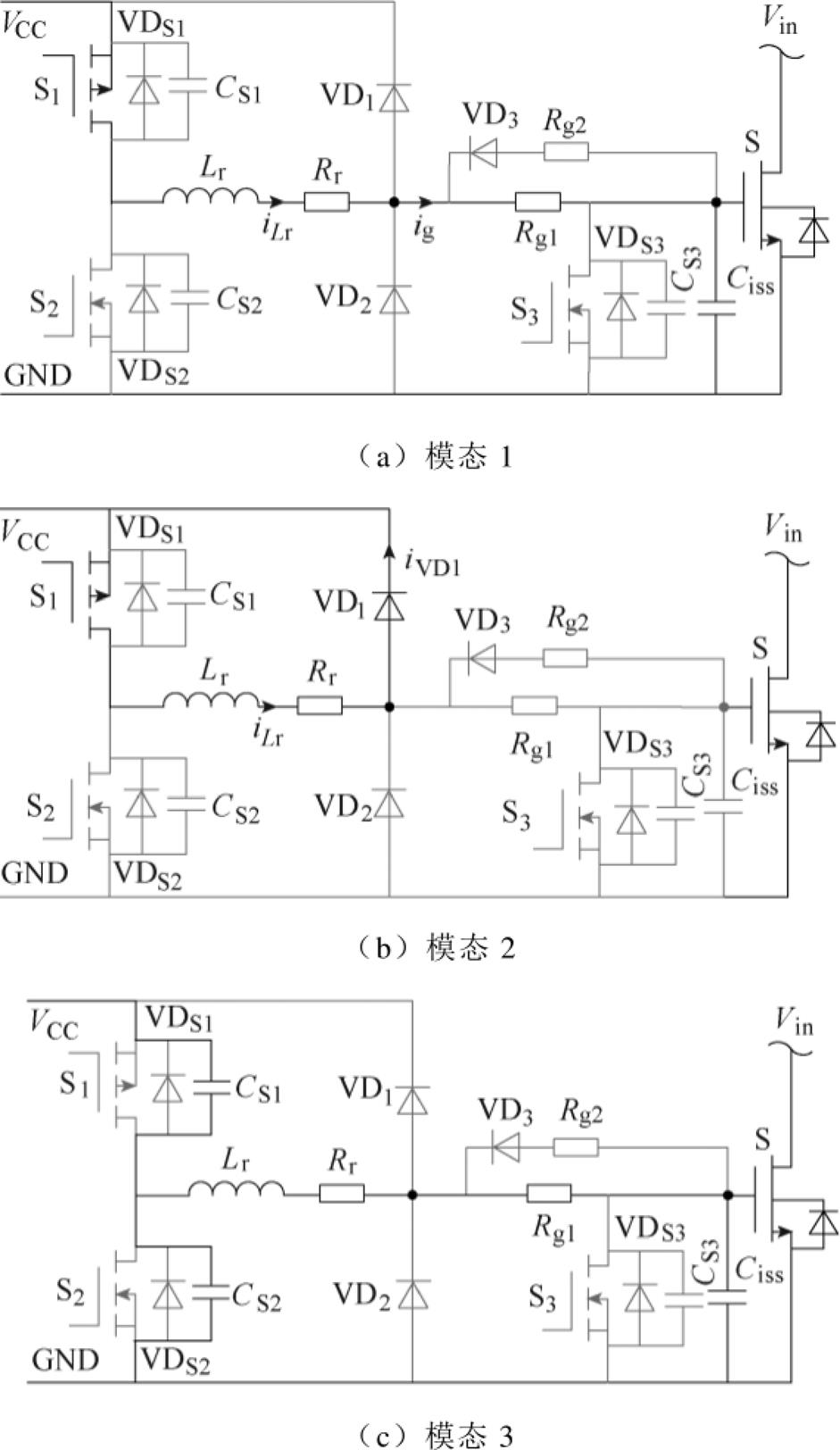

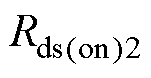

工作模态分析如图7所示。根据电路驱动时序对原理工作模态分析如下:

模态1[t0, t1 :如图7a所示。

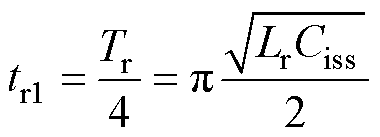

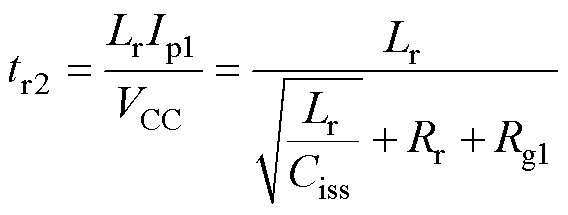

:如图7a所示。 时刻,开关管S1导通、S2截止,谐振电感Lr和电容Ciss开始谐振,电感Lr电流从零逐渐增大,为电容Ciss充电,充电电流路径为S1→Lr→Rr→Rg1,经过

时刻,开关管S1导通、S2截止,谐振电感Lr和电容Ciss开始谐振,电感Lr电流从零逐渐增大,为电容Ciss充电,充电电流路径为S1→Lr→Rr→Rg1,经过 谐振周期

谐振周期 ,电容Ciss两端电压达到VCC,电流iLr达到峰值Ip1,此时,二极管VD1导通。

,电容Ciss两端电压达到VCC,电流iLr达到峰值Ip1,此时,二极管VD1导通。

图7 工作模态分析

Fig.7 Operational modal analysis

(1)

(1)式中,Ciss=Cgd+Cgs,Cgd、Cgs分别为Cascode GaN栅漏极间寄生电容、栅源极间寄生电容。

模态2[t1, t2 :如图7b所示。开关管S1导通、S2截止,

:如图7b所示。开关管S1导通、S2截止, 时刻,电感Lr和电容Ciss谐振结束,电感Lr电流从峰值Ip1逐渐减小,此阶段电感电流由二极管VD1流通,电容Ciss被驱动电源的电压钳位,电流路径为S1→Lr→Rr→VD1,经过

时刻,电感Lr和电容Ciss谐振结束,电感Lr电流从峰值Ip1逐渐减小,此阶段电感电流由二极管VD1流通,电容Ciss被驱动电源的电压钳位,电流路径为S1→Lr→Rr→VD1,经过 时间,电感Lr中电流降为零,二极管VD1截止。

时间,电感Lr中电流降为零,二极管VD1截止。

(2)

(2)式中,Rr为电感Lr的等效电阻;Rg1为开关管S的门极驱动电阻; 为驱动电压。

为驱动电压。

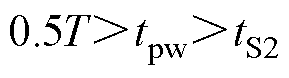

分析模态1和模态2发现,开关管S1导通时间需满足 。

。

模态3[t2, t3 :如图7c所示。开关管S1、S2均截止,t2时刻,电感Lr电流近似为零,[t2, t3

:如图7c所示。开关管S1、S2均截止,t2时刻,电感Lr电流近似为零,[t2, t3 时间段内,电感Lr、电容Ciss和MOS管S1、S2的寄生电容CS1、CS2谐振,电容Ciss存储的电荷量得以保持,用于支撑开关管S持续导通。电阻Rg1可抑制电压振荡幅值。

时间段内,电感Lr、电容Ciss和MOS管S1、S2的寄生电容CS1、CS2谐振,电容Ciss存储的电荷量得以保持,用于支撑开关管S持续导通。电阻Rg1可抑制电压振荡幅值。

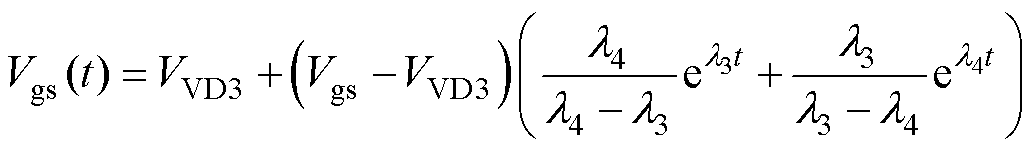

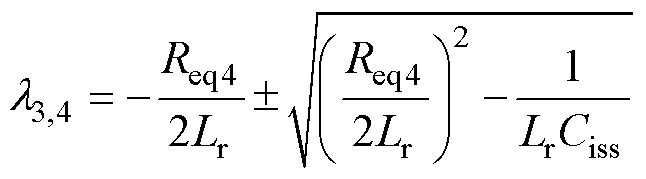

模态4[t3, t4 :如图7d所示。

:如图7d所示。 时刻,开关管S1截止、S2导通,电感Lr和电容Ciss开始谐振,电感Lr电流从零逐渐反向增大,为电容Ciss放电,放电电流路径为Rg2→VD3→Rr→Lr→S2,经过

时刻,开关管S1截止、S2导通,电感Lr和电容Ciss开始谐振,电感Lr电流从零逐渐反向增大,为电容Ciss放电,放电电流路径为Rg2→VD3→Rr→Lr→S2,经过 谐振周期

谐振周期 ,电流iLr达到峰值Ip2,S栅极电位被拉至-VVD2,此时,二极管VD2导通,S栅极电压被二极管电压钳位。

,电流iLr达到峰值Ip2,S栅极电位被拉至-VVD2,此时,二极管VD2导通,S栅极电压被二极管电压钳位。

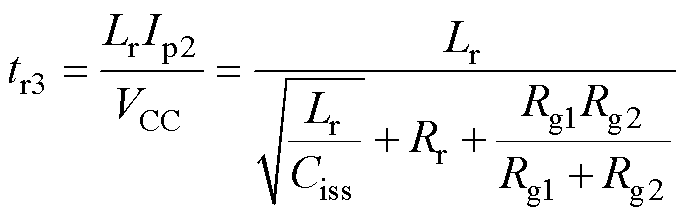

模态5[t4, t5 :如图7e所示。开关管S1截止、S2导通,

:如图7e所示。开关管S1截止、S2导通, 时刻,电感Lr和电容Ciss谐振结束,电感Lr电流从峰值Ip2逐渐减小,此阶段电感电流由二极管VD2流通,电容Ciss被二极管电压钳位,电流路径为Lr→S2→VD2→Rr。当开关管S栅极电压Vgs小于密勒台阶电压时,S3开通,S栅极电压被钳位。经过

时刻,电感Lr和电容Ciss谐振结束,电感Lr电流从峰值Ip2逐渐减小,此阶段电感电流由二极管VD2流通,电容Ciss被二极管电压钳位,电流路径为Lr→S2→VD2→Rr。当开关管S栅极电压Vgs小于密勒台阶电压时,S3开通,S栅极电压被钳位。经过 时间,电感Lr中电流降至零,二极管VD2截止。

时间,电感Lr中电流降至零,二极管VD2截止。

(3)

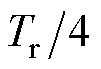

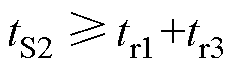

(3)分析模态4和模态5发现,开关管S2导通时间需满足 ,且

,且 。

。

模态6[t5, t6]:如图7f所示。开关管S1、S2均截止,t5时刻,电感Lr电流近似为零,[t5, t6]时间段内,S截止,S3导通,S栅极电压被钳位,防止du/dt经Cgd产生位移电流,使得栅极电压Vgs超过开通阈值电压Vgs(th),导致S误导通。

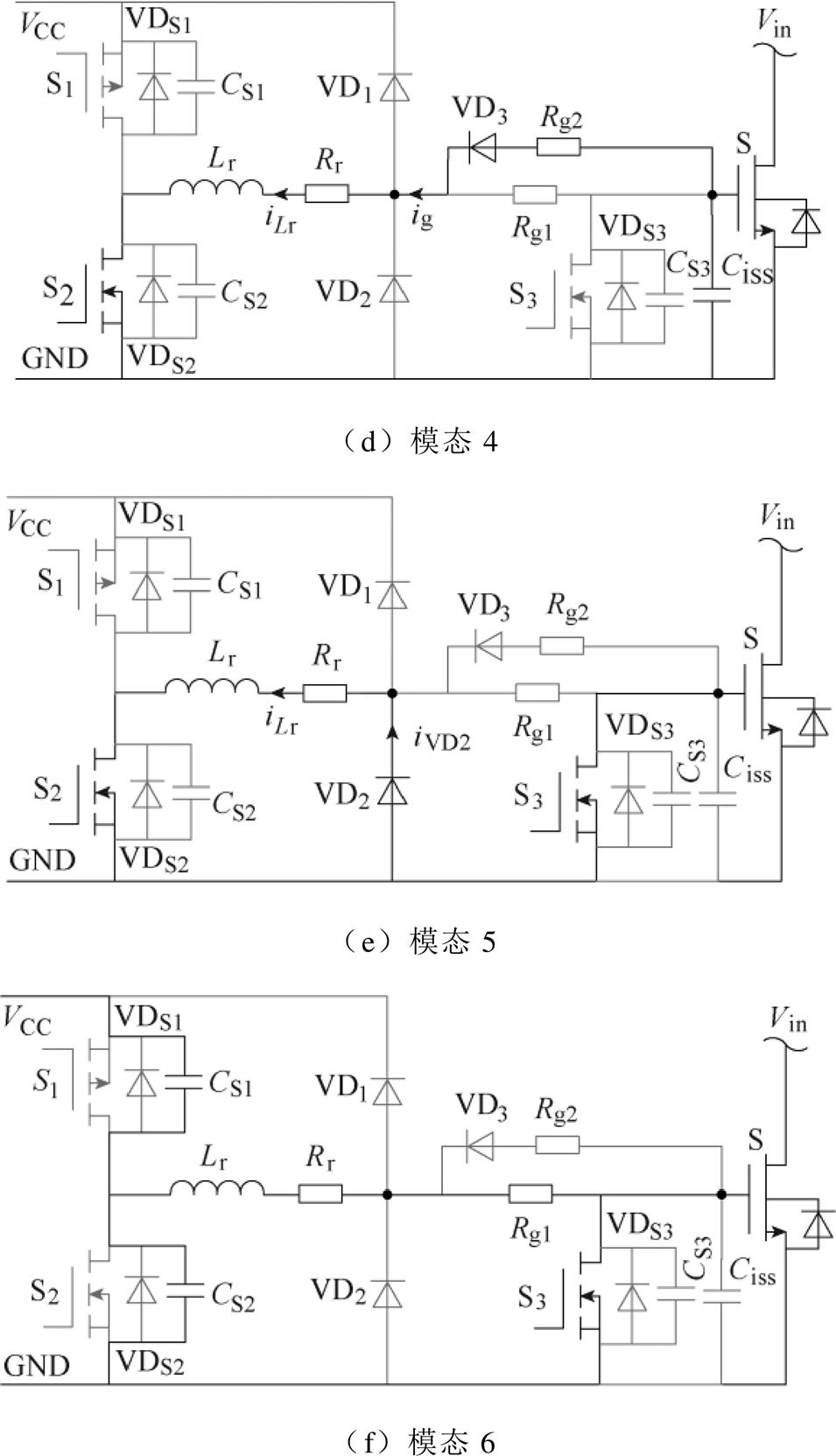

高频驱动电路各工作模态等效电路如图8所示。 、

、 分别为S1、S2的导通电阻,

分别为S1、S2的导通电阻, 为回路电流,

为回路电流, 为电容Ciss两端电压。

为电容Ciss两端电压。

图8 工作模态等效电路

Fig.8 Working mode equivalent circuit

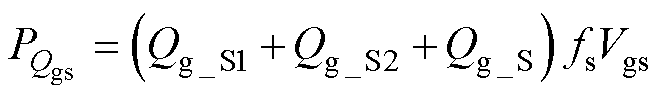

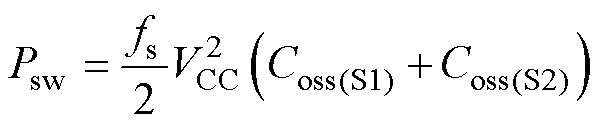

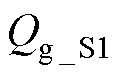

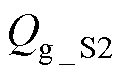

开关管S1、S2和S的驱动损耗 和开关损耗

和开关损耗 分别为

分别为

(4)

(4) (5)

(5)

式中, 、

、 和

和 分别为PMOS、NMOS和GaN栅极电荷量;

分别为PMOS、NMOS和GaN栅极电荷量; 为开关频率;Coss(S1)为S1输出电容;Coss(S2)为S2输出电容。

为开关频率;Coss(S1)为S1输出电容;Coss(S2)为S2输出电容。

谐振电感的损耗包括铜损耗和磁心损耗,铜损耗等效为电阻 的损耗,包含在各模态损耗分析中。电感磁心损耗为

的损耗,包含在各模态损耗分析中。电感磁心损耗为

(6)

(6)式中, 为磁心有效体积;

为磁心有效体积; 为磁心常数;

为磁心常数; 为频率指数;

为频率指数; 为磁通密度;

为磁通密度; 为磁通指数。

为磁通指数。

模态损耗分析如下,以图6中 时刻为起始时刻。

时刻为起始时刻。

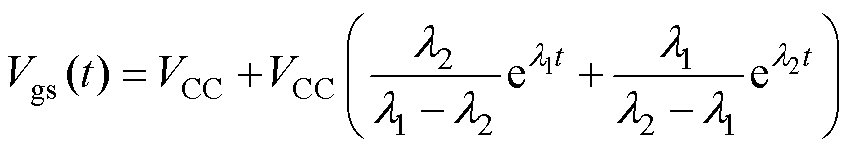

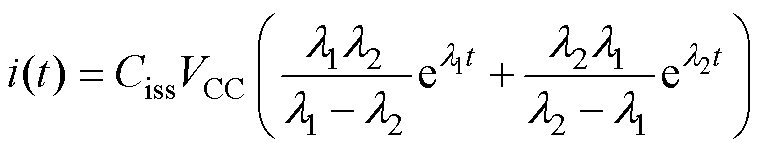

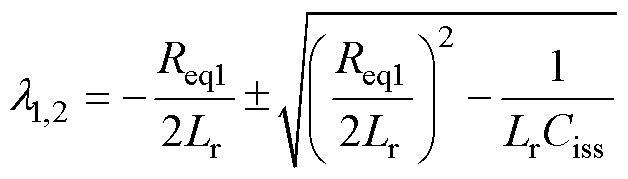

模态1等效电路如图8a所示。回路中等效电阻 ,初始值

,初始值 ,

, ,则GaN器件等效电容Ciss两端电压表达式为

,则GaN器件等效电容Ciss两端电压表达式为

(7)

(7)充电电流为

(8)

(8)

式中,系数 。

。

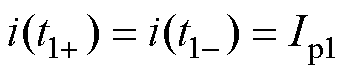

在 时间段内,回路中的损耗为

时间段内,回路中的损耗为

(9)

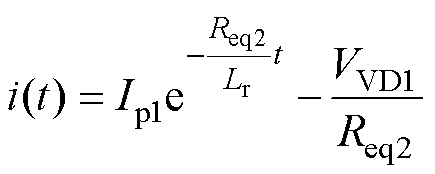

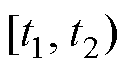

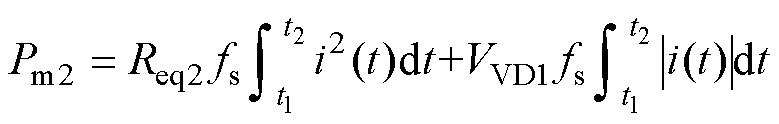

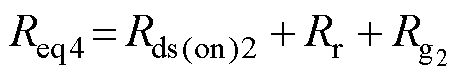

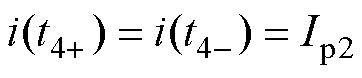

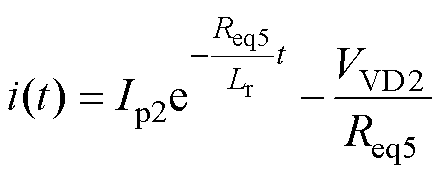

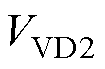

(9)模态2等效电路如图8b所示。回路中等效电阻 ,初始值

,初始值 ,则回路电流为

,则回路电流为

(10)

(10)

式中, 为二极管VD1的导通压降。

为二极管VD1的导通压降。

在 时间段内,回路中的损耗为

时间段内,回路中的损耗为

(11)

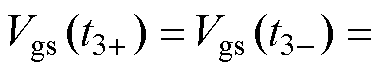

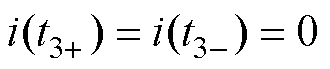

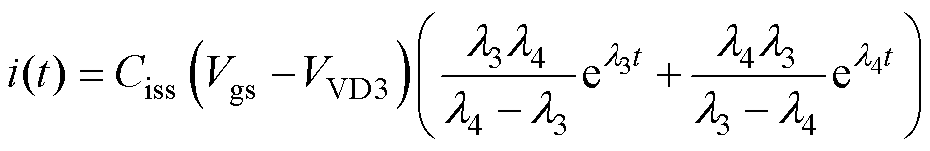

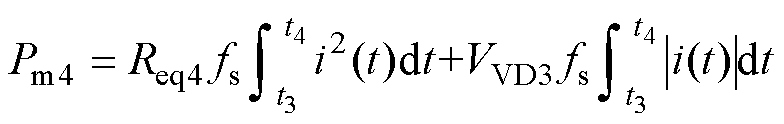

(11)模态4等效电路如图8d所示。回路等效电阻 ,初始值

,初始值

,

, ,则Cascode GaN器件等效电容Ciss两端电压表达式为

,则Cascode GaN器件等效电容Ciss两端电压表达式为

(12)

(12)

式中,系数 ;

; 为二极管VD3的导通压降。

为二极管VD3的导通压降。

放电电流为

(13)

(13)在 时间段内,回路中的损耗为

时间段内,回路中的损耗为

(14)

(14)

模态5等效电路如图8e所示。回路中等效电阻 ,初始条件

,初始条件 ,则回路电流为

,则回路电流为

(15)

(15)式中, 为二极管VD2的导通压降。

为二极管VD2的导通压降。

在 时间段内,回路中的损耗为

时间段内,回路中的损耗为

(16)

(16)模态3、模态6等效电路如图8c、图8f所示。电路中电流近似为零,由电感Lr和寄生电容CS1、CS2产生谐振,此时间段内损耗忽略不计。

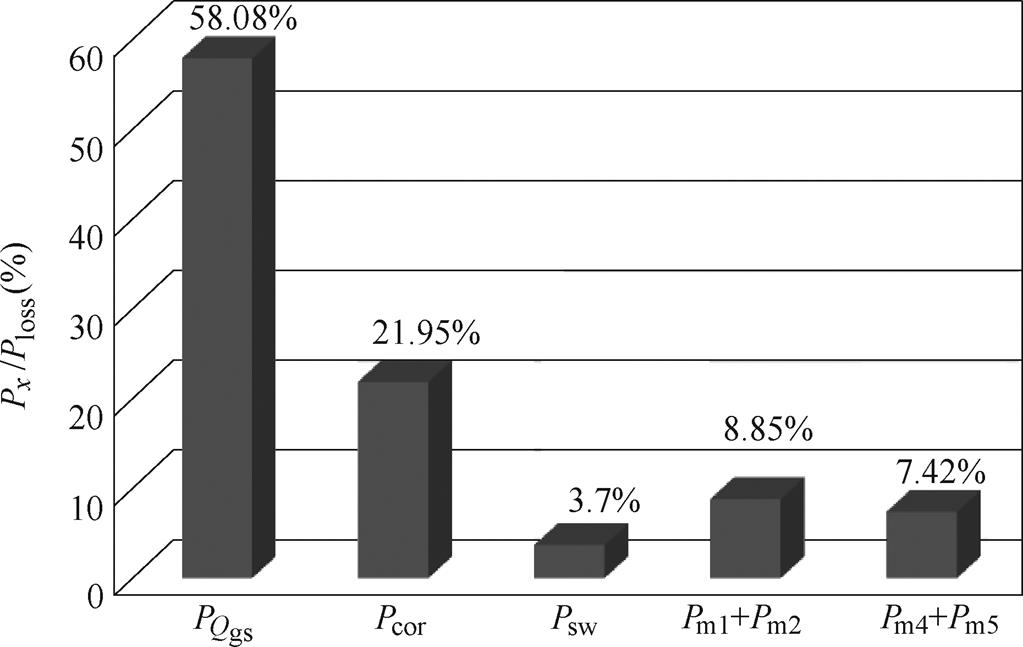

综上分析,驱动电路的总损耗为

(17)

(17) 根据分析过程,结合已选型的器件参数得出开关频率为1.5MHz时的损耗分布如图9所示。

图9 驱动电路损耗分布

Fig.9 Drive circuit loss distribution

根据驱动电路模态分析可知,谐振电容为GaN器件寄生电容和PCB的寄生参数之和,若器件选型和PCB布局确定,电容参数确定不变。调节谐振电感Lr值,可改变谐振驱动电路特性。研究发现,图腾柱驱动信号脉冲宽度与谐振电感取值密切相关,为了确保GaN可靠开通和关断,一个周期T内,电感中能量必须归零。如果开关管开通期间能量没有归零,在模态3时间段内,电路中电感Lr、电容Ciss与MOS管寄生电容产生电压振荡,可能导致GaN器件误导通。为了保证GaN器件可靠驱动,最小脉冲宽度tpw需大于谐振电感Lr为电容Ciss放电时间tS2,为了避免两只MOS同时导通,PWM占空比必须小于0.5,即

(18)

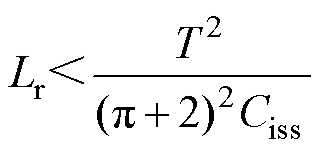

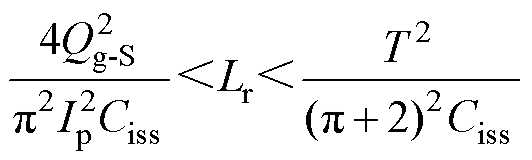

(18)由式(1)、式(3)和式(18)得到电感Lr的取值需满足

(19)

(19)

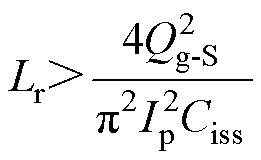

若电感取值太小,充/放电过程会产生较大的di/dt,导致驱动波形产生电压尖峰;同时,也会导致驱动能力不足。为了使GaN器件可靠工作,需确定电感Lr的最小取值。根据电荷守恒原理,S1导通时间段内,电感Lr所储存的电荷量QLr需大于S开通所需的电荷量Qg-S,即QLr>Qg-S。

(20)

(20)式中,Ip为电感峰值电流。

综上分析,电感Lr的取值范围为

(21)

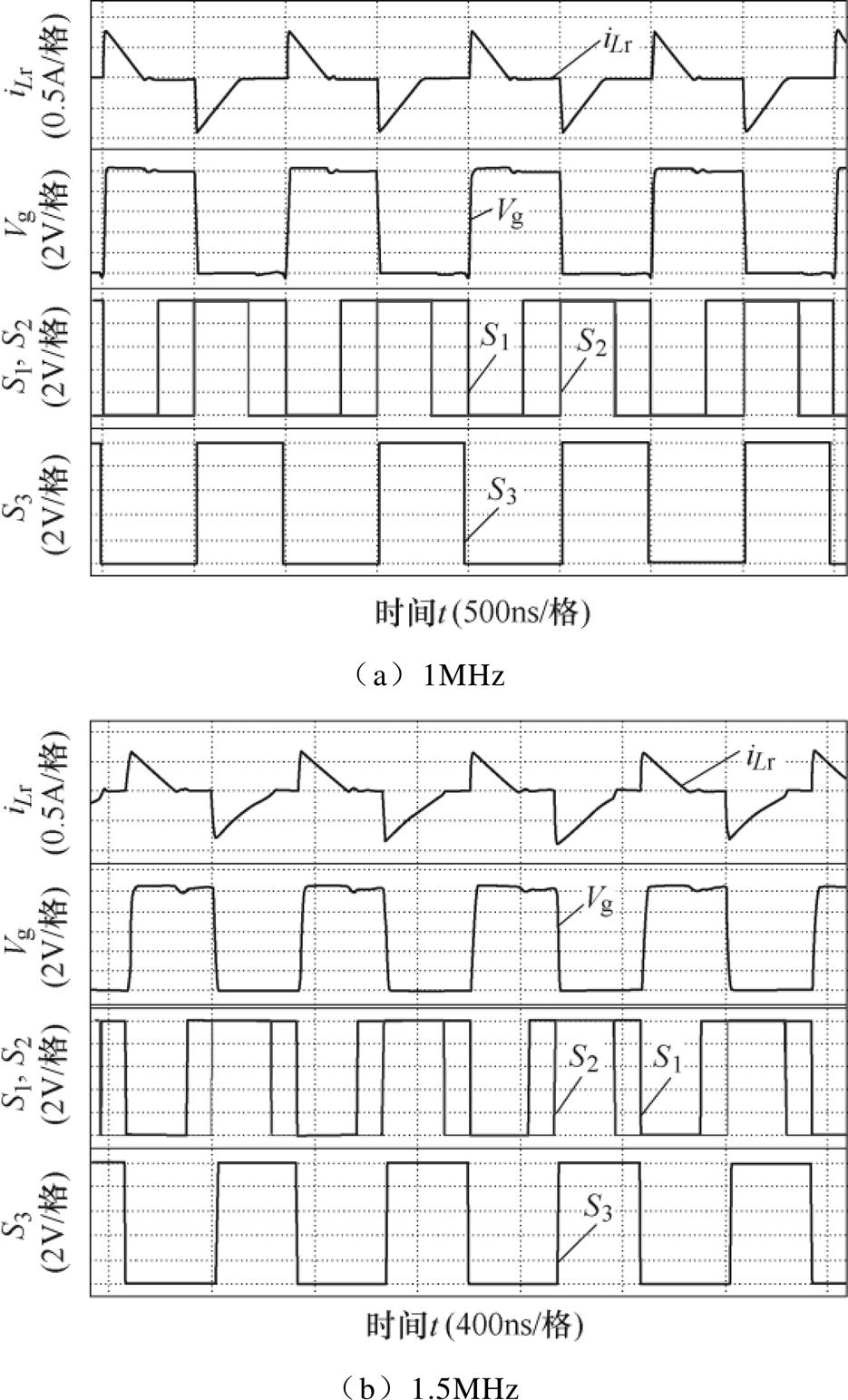

(21)为了进一步验证所提出的高频驱动电路原理的正确性,本文利用PSIM软件搭建了驱动电路模型,分别给出了1MHz和1.5MHz工作时的仿真结果,驱动电路仿真波形如图10所示。由TP65H300G4LSG数据手册查得,等效电容值Ciss=760pF,驱动电路仿真参数见表1。

图10 驱动电路仿真波形

Fig.10 Driving circuit simulation waveforms

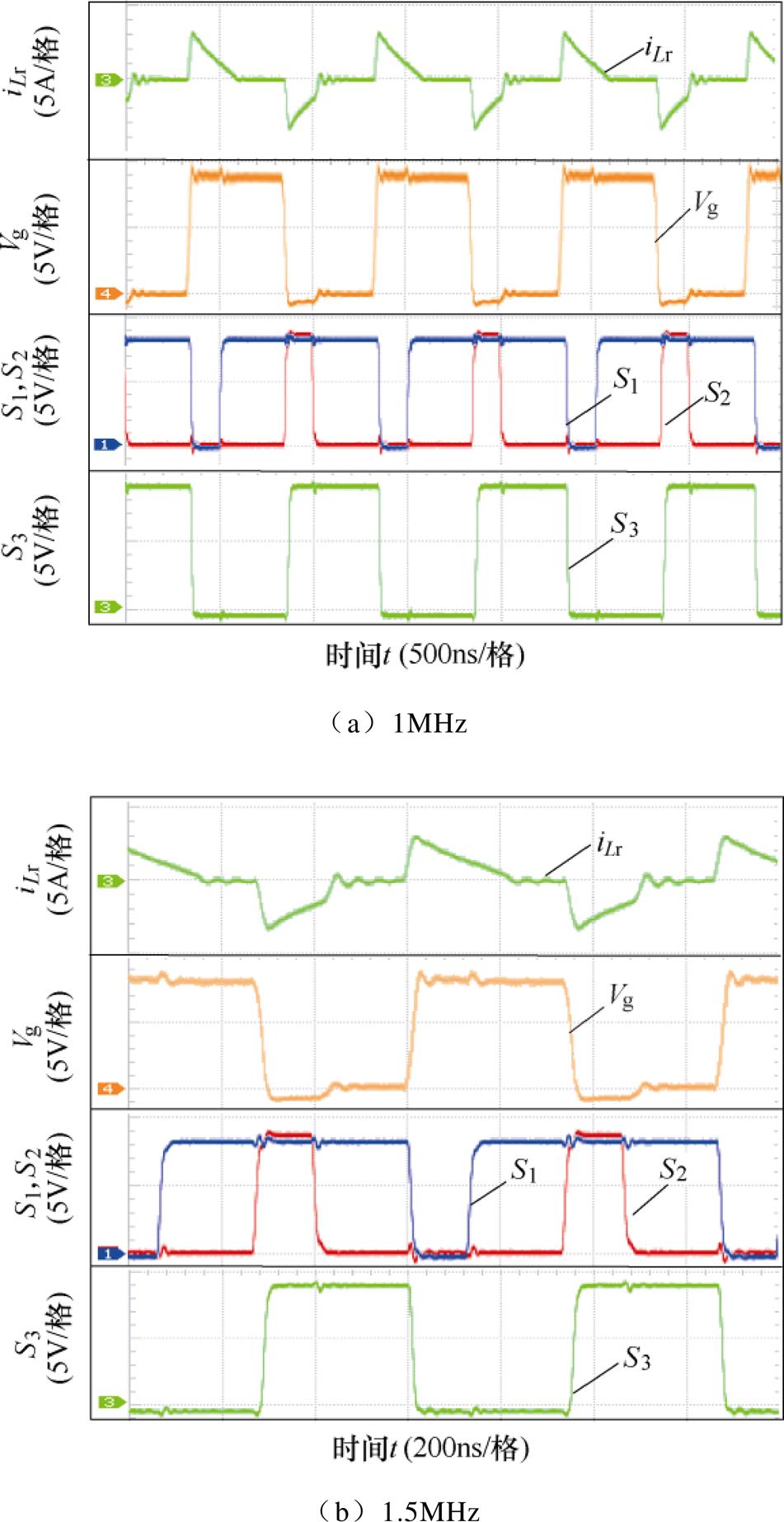

图10中,iLr为电感的电流波形,Vg为GaN器件栅极电压波形,S1、S2、S3分别为MOS管S1、S2、S3的驱动波形。

表1 驱动电路仿真参数

Tab.1 Drive circuit simulation parameters

频率fs/MHz电感Lr/nHMOS管导通时间t/ns电阻Rg1/Ω电阻Rg2/Ω 11003003.31 1.51003503.31

分析仿真结果可得,谐振回路具有阻抗小的优点,可以减小开关管开通和关断的电压振荡。调节电阻Rg1、Rg2可抑制GaN栅极驱动电压振荡,电阻需要根据实际情况选取,若取值较大,高频工作时,du/dt经过电容Cgd产生位移电流,使S栅极电压增加,当电压值大于阈值电压时,会导致GaN器件误导通。设计中必须保证电容Ciss放电时间小于MOS管导通时间,否则电容中电荷无法完全释放,导致GaN关断时,栅极电压无法拉至低电平。

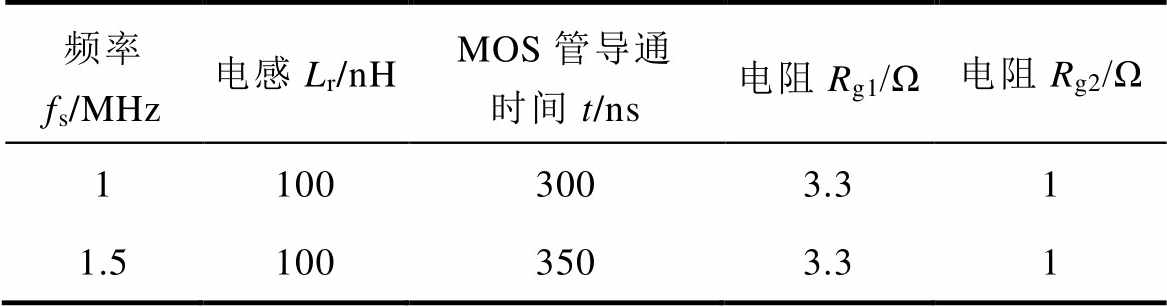

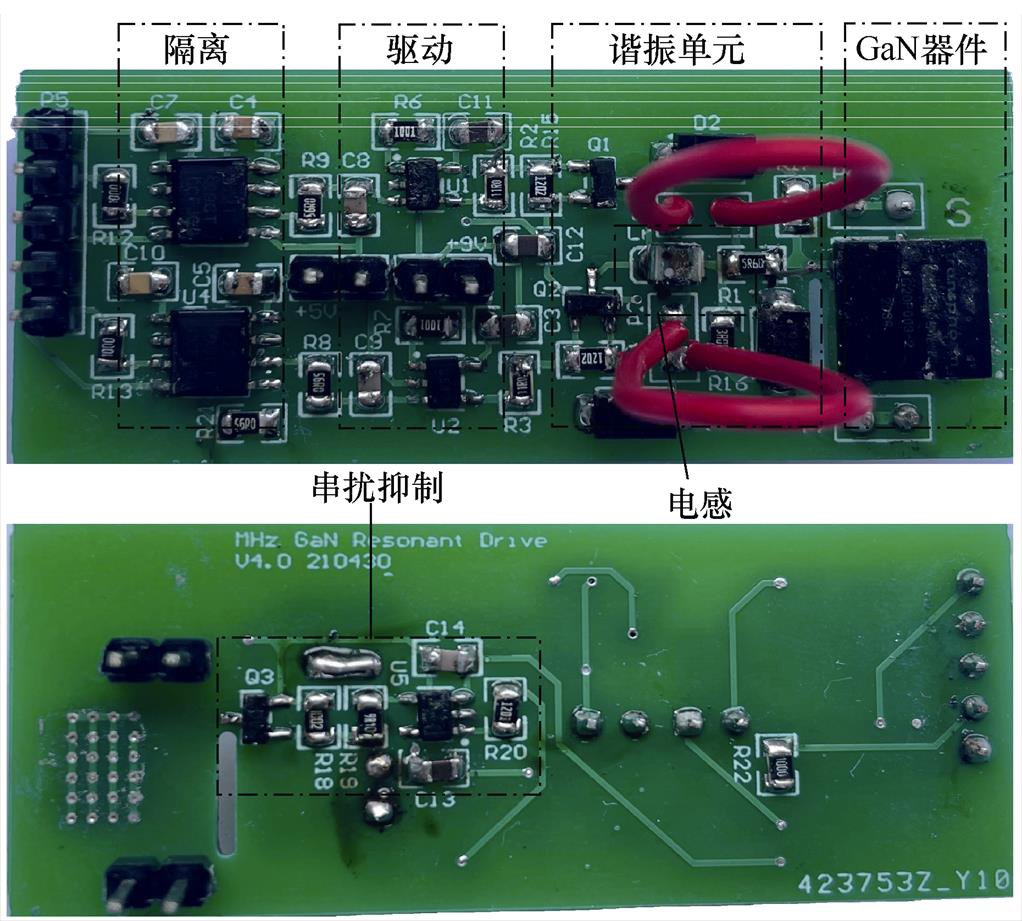

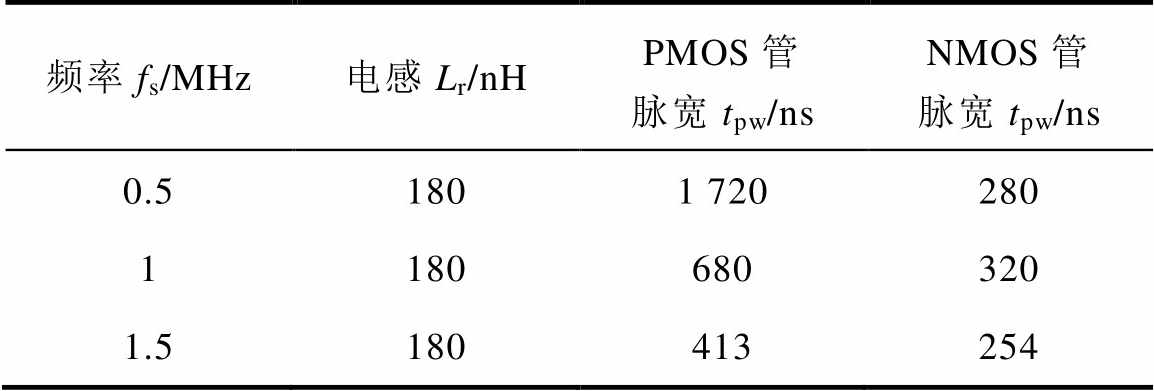

本文搭建了Cascode GaN HEMT器件的高频谐振驱动电路实验平台,硬件驱动电路如图11所示。电路包括隔离电路、MOS管驱动电路、谐振电路和串扰抑制电路四部分。由控制器产生图6中MOS管S1、S2和S3所示时序的PWM波,经高速隔离芯片后,由驱动芯片将功率放大,以满足PMOS管和NMOS管的驱动要求,实现对GaN栅极电容Ciss进行充/放电,确保GaN器件能被可靠驱动。硬件驱动电路的器件选型见表2,MOS管的驱动时间设置见表3。驱动电路工作在不同频率时,GaN栅极驱动电压测试波形如图12所示。

图11 Cascode GaN高频驱动电路

Fig.11 Cascode GaN high-frequency drive circuit

对比图12和图10发现,实验测试波形与仿真波形结果一致,证明了设计的正确性。通过实验得出,当频率增大时,需调节电感参数或MOS导通时间,使电感中能量被完全释放,确保在任何情况下,GaN器件都能被可靠开通和关断。

表2 驱动电路主要器件

Tab.2 Main components of the drive circuit

器 件型 号 隔离芯片ISO7721DR 驱动芯片UCC27519D MOS管BLM3401/BLM3400 肖特基二极管B240A Cascode GaN HEMTTP65H300G4LSG

表3 驱动电路时序设置

Tab.3 Drive circuit timing setting

频率fs/MHz电感Lr/nHPMOS管脉宽tpw/nsNMOS管脉宽tpw/ns 0.51801 720280 1180680320 1.5180413254

图12 驱动电路测试波形

Fig.12 Drive circuit test waveforms

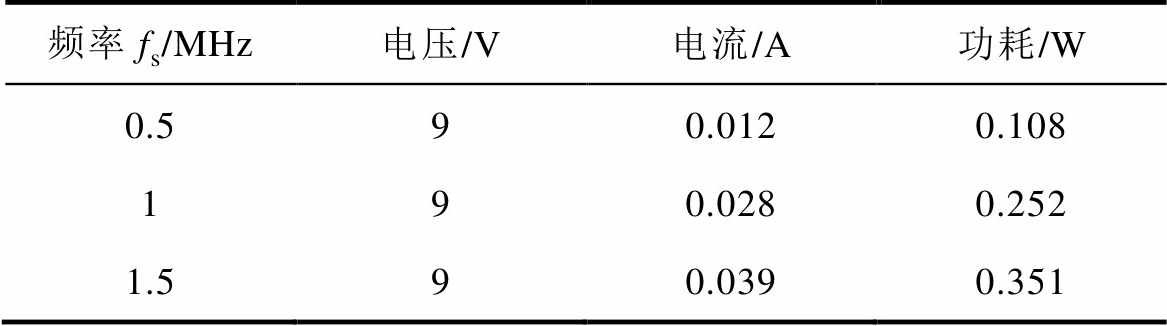

不同工作频率条件下,驱动电路的功耗测试结果见表4。

表4 驱动电路功耗测试结果

Tab.4 Drive circuit power consumption test results

频率fs/MHz电压/V电流/A功耗/W 0.590.0120.108 190.0280.252 1.590.0390.351

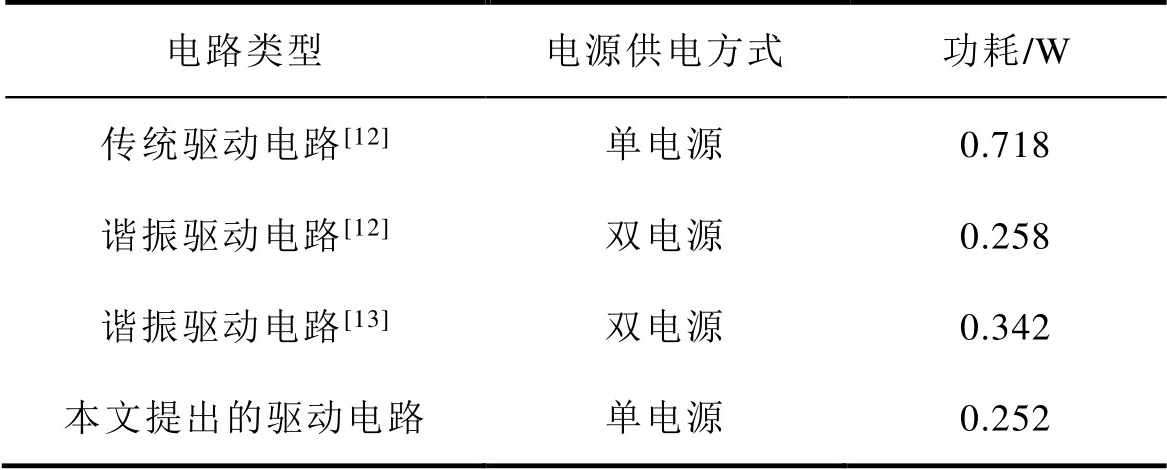

工作频率为1MHz时,不同类型驱动电路的损耗见表5。

表5 驱动电路损耗对照

Tab.5 Drive circuit loss comparison

电路类型电源供电方式功耗/W 传统驱动电路[12]单电源0.718 谐振驱动电路[12]双电源0.258 谐振驱动电路[13]双电源0.342 本文提出的驱动电路单电源0.252

从表4中数据可以看出,随着开关频率增加,GaN器件的驱动损耗也显著增加。对比表5中数据可得,本文所提出的高频驱动电路损耗最小。虽然文献[12]中提出的驱动电路损耗为0.258W,与本文电路损耗相近,但文献[12]中没有考虑驱动电路的桥臂串扰抑制问题。文献[13]所提出的SiC驱动电路损耗为0.342W,文献中所述电路采用双电源供电,需要4只开关管,控制时序复杂,硬件设计困难。本文提出的驱动电路只需3只MOS管,具有驱动功耗低和抑制桥臂串扰的优势。

本文针对在高频驱动电路应用中,传统耗能型驱动电路无法使GaN器件完全发挥自身性能的问题,提出了一种Cascode GaN HEMT高频谐振驱动电路,利用电感电流为GaN栅极电容Ciss充/放电,通过有源密勒钳位电路抑制桥臂串扰。实验结果表明,由电感Lr构成的驱动电路具备回路阻抗低的特点,抑制了GaN器件栅极驱动波形的振荡,同时降低了驱动损耗。工作频率为1.5MHz时,驱动损耗为0.351W,该电路结构简单、控制易实现。与耗能型驱动电路和其他类型谐振驱动电路相比,本文所提出的高频驱动电路具有功耗低、电路结构简单的优点,并能有效抑制桥臂串扰,改善了GaN器件高频驱动电路的工作性能。

参考文献

[1] Mashhadi I A, Rahimzadeh Khorasani R, Adib E, et al. A discontinuous current-source gate driver with gate voltage boosting capability[J]. IEEE Transactions on Industrial Electronics, 2017, 64(7): 5333-5341.

[2] 赵清林, 郭娟伟, 袁精, 等. MOSFET谐振门极驱动电路研究综述[J]. 电力自动化设备, 2018, 38(10): 66-73, 107.

Zhao Qinglin, Guo Juanwei, Yuan Jing, et al. Review of MOSFET resonant gate drive circuit research[J]. Electric Power Automation Equipment, 2018, 38(10): 66-73, 107.

[3] Sun Bainan, Zhang Zhe, Michael A E, et al. A comparison review of the resonant gate driver in the silicon MOSFET and the GaN transistor appli- cation[J]. IEEE Transactions on Industry Applications, 2019, 55(6): 7776-7786.

[4] Ding Xiaofeng, Zhou Yang, Cheng Jiawei. A review of gallium nitride power device and its applications in motor drive[J]. CES Transactions on Electrical Machines and Systems, 2019, 3(1): 54-64.

[5] 吴海富, 张建忠, 赵进, 等. SiC MOSFET短路检测与保护研究综述[J]. 电工技术学报, 2019, 34(21): 4519-4528.

Wu Haifu, Zhang Jianzhong, Zhao Jin, et al. Review of short-circuit detection and protection of silicon carbide MOSFET[J]. Transactions of China Electro- technical Society, 2019, 34(21): 4519-4528.

[6] 闫琪, 李艳, 王路. 基于GaN器件的双Buck逆变器共模与损耗[J]. 电工技术学报, 2017, 32(20): 133- 141.

Yan Qi, Li Yan, Wang Lu. The common-mode characteristics and loss of dual Buck grid-connected inverter based on GaN devices[J]. Transactions of China Electrotechnical Society, 2017, 32(20): 133-141.

[7] 刘佳斌, 肖曦, 梅红伟. 基于GaN-HEMT器件的双有源桥DC-DC变换器的软开关分析[J]. 电工技术学报, 2019, 34(增刊2): 534-542.

Liu Jiabin, Xiao Xi, Mei Hongwei. Soft switching analysis of dual active bridge DC-DC converter based on GaN-HEMT device[J]. Transactions of China Electrotechnical Society, 2019, 34(S2): 534-542.

[8] 刘瑞煌, 杨景刚, 贾勇勇, 等. 中压直流配电网中直流变压器工程化应用[J]. 电力系统自动化, 2019, 43(23): 131-140.

Liu Ruihuang, Yang Jinggang, Jia Yongyong, et al. Engineering applications of DC transformer in medium-voltage DC distribution network[J]. Auto- mation of Electric Power Systems, 2019, 43(23): 131-140.

[9] Yue Yan, Antonio Martinez-Perez, Alberto Castellazzi. High-frequency resonant gate driver for GaN HEMTs[C]//IEEE 16th Workshop on Control and Modeling for Power Electronics (COMPEL), Vancouver, BC, 2015: 1-6.

[10] Masayuki Okamoto, Takaharu Ishibashi, Hiroaki Yamada, et al. Resonant gate driver for a normally on GaN HEMT[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2016, 4(3): 926-934.

[11] 赵清林, 陈磊, 袁精, 等. 一种适用于GaN器件的谐振驱动电路[J]. 电力自动化设备, 2019, 39(4): 114-118.

Zhao Qinglin, Chen Lei, Yuan Jing, et al. A resonant gate driver circuit for GaN device[J]. Electric Power Automation Equipment, 2019, 39(4): 114-118.

[12] 张建忠, 吴海富, 张雅倩, 等. 一种SiC MOSFET谐振门极驱动电路[J]. 电工技术学报, 2020, 35(16): 3453-3459.

Zhang Jianzhong, Wu Haifu, Zhang Yaqian, et al. A resonant gate driver for SiC MOSFET[J]. Transa- ctions of China Electrotechnical Society, 2020, 35(16): 3453-3459.

[13] Zhang Jianzhong, Wu Haifu, Zhao Jin, et al. A resonant gate driver for silicon carbide MOSFETs[J]. IEEE Access, 2018(6): 78394-78401.

[14] 李辉, 黄樟坚, 廖兴林, 等. 一种抑制SiC MOSFET桥臂串扰的改进门极驱动设计[J]. 电工技术学报, 2019, 34(2): 275-285.

Li Hui, Huang Zhangjian, Liao Xinglin, et al. An improved SiC MOSFET gate driver design for crosstalk suppression in a phase-leg configuration[J]. Transactions of China Electrotechnical Society, 2019, 34(2): 275-285.

[15] Plinio Bau, Marc Cousineau, Bernardo Cougo, et al. CMOS active gate driver for closed-loop dv/dt control of GaN transistors[J]. IEEE Transactions on Power Electronics, 2020, 35(12): 13322-13332.

[16] 周林, 李寒江, 解宝, 等. SiC MOSFET的Saber建模及其在光伏并网逆变器中的应用和分析[J]. 电工技术学报, 2019, 34(20): 4251-4263.

Zhou Lin, Li Hanjiang, Xie Bao, et al. Saber modeling of SiC MOSFET and its application and analysis in photovoltaic grid-connected inverter[J]. Transactions of China Electrotechnical Society, 2019, 34(20): 4251-4263.

[17] 刘虹伶, 刘明宇. 一种脉冲变压器隔离的IGBT驱动电路的设计研究[J]. 电气技术, 2017, 18(3): 94- 96.

Liu Hongling, Liu Mingyu. Research and design of an IGBT drive circuit for pulse transformer isolation[J]. Electrical Engineering, 2017, 18(3): 94-96.

[18] Fumiya Hattori, Hirokatsu Umegami, Masayoshi Yamamoto. Multi-resonant gate drive circuit of isolating-gate GaN HEMTs for tens of MHz[J]. IET Circuits Devices and Systems, 2017, 11(3): 261-266.

[19] Lei Gu, Wei Liang, Juan Rivasdavila. A multi- resonant gate driver for very-high-frequency (VHF) resonant converters[C]//IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL), Stanford, CA, 2017: 1-7.

[20] 高圣伟, 段尧文, 刘晓明, 等. GaN HEMT预充电式驱动电路设计[J]. 天津工业大学学报, 2020, 39(1): 69-76.

Gao Shengwei, Duan Yaowen, Liu Xiaoming, et al. Design of precharge drive circuit for GaN HEMT[J]. Journal of Tiangong University, 2020, 39(1): 69-76.

High-Frequency Drive Circuit and Its Loss Analysis of Cascode GaN High Electron Mobility Transistor

Abstract In order to reduce the loss of the GaN driving circuit during high-frequency operation, a high-frequency resonant drive circuit for the Cascode GaN high electron mobility transistor is proposed in this paper. In the circuit, the traditional power-dissipation device is replaced by the power-storage device, and the GaN device gate capacitor is charged or discharged through the inductance current. At the same time, the crosstalk of bridge arm is suppressed by the active Mueller clamp circuit. In this paper, the working mode of the high-frequency resonant driving circuit was studied, the circuit loss was analyzed in detail, the selection principle of the inductance value was given, and the simulation of the circuit was verified by PSIM software. Finally, an experimental platform was built to test the performance of the circuit. The results show that the inductor provides a low impedance path for capacitor charging or discharging, the voltage oscillation of GaN device drive circuit is effectively reduced, and the loss is obviously reduced. The simulation and experiment show that the proposed circuit has better performance.

keywords:Cascode GaN high electron mobility transistor, high-frequency resonance, drive circuit, crosstalk suppression, low loss

DOI: 10.19595/j.cnki.1000-6753.tces.210243

中图分类号:TM46

岳改丽 女,1967年生,副教授,硕士生导师,研究方向为高频功率变换和电力电子技术。E-mail: Yuegl@xust.edu.cn(通信作者)

向付伟 男,1996年生,硕士研究生,研究方向为高频功率变换器技术。E-mail: xfwpowerdesign@163.com

收稿日期2021-03-01

改稿日期 2021-05-19

国家自然科学基金资助项目(51777167)。

(编辑 陈 诚)