0 引言

LLC谐振变换器能够实现变压器前级器件的零电压开通(Zero Voltage Switch, ZVS)和变压器后级器件的零电流关断(Zero Current Switch, ZCS),所以非常适合工作在高开关频率下,以获得较高的工作效率和功率密度[1-3]。近年来,随着通信和计算等需求的不断增大,对LLC变换器的效率和功率密度提出的要求越来越高。传统的绕线式变压器不仅绕制困难,而且体积较大,正逐渐被以印制电路板(Printed Circuit Board, PCB)导线为绕组的平面磁集成变压器所替代[4-7]。而且随着供电电压的降低,供电电流不断增大,变换器中的器件承受的电流应力、导通损耗和热应力也越来越大。

在这种低压大电流应用场合,通常采用并联技术来解决器件承受的导通损耗和热应力问题。第一种并联方案是器件直接并联,但是存在器件不均流和 PCB局部过热的问题[6-7];另外一种方案是变换器交错并联,但是需要加入额外的均流控制,降低了变换器的功率密度和可靠性[8-9]。相比于以上两种并联方案,变压器前级绕组串联后级绕组并联的矩阵变压器不仅可以实现自动均流,避免变换器局部过热而且可以进一步提高集成度,得到越来越多的应用[7-13]。文献[10-11]采用分离磁心的矩阵变压器实现了高功率密度LLC直流变压器(LLC-DCX),但是文中重点论述变换器电参数的优化设计,而对于矩阵变压器的设计细节却很少论述。但实际上矩阵变压器中的绕线结构、PCB厚度和线圈端接方式均对线圈损耗和漏感存在较大影响[7,12-13]。而且根据文献[12-14]可以知道,基于磁通抵消原理,矩阵变压器中分离的磁心还可以进一步集成到单个磁心中,以进一步减小磁心损耗并提高变换器的功率密度。所以,矩阵变压器还存在很多优化设计的空间。此外,文献[15]建立一种适用于平面结构变压器线圈损耗和磁心损耗的计算模型,从而可以在绕组交流损耗最小的条件下优化设计变压器绕组结构;同时也为实现变压器损耗和尺寸的优化设计提供了可能。

本文在上述文献的基础上,给出一种应用于高功率密度LLC变换器(LLC-D2D)的平面矩阵变压器优化设计方法。首先基于磁通抵消原理,将两个分离的磁心集成到单个磁心中,给出变压器磁心结构;其次在变压器磁心结构基础上,基于绕组漏感和交流损耗最小的原则,设计了变压器绕组结构,并确定了绕组PCB厚度;接着给出了绕组和磁心损耗计算模型,并在此基础上给出变压器总损耗和变压器尺寸折中优化设计方法,最后通过实验样机验证了矩阵变压器设计方法的正确性和有效性。

1 矩阵变压器磁心优化设计

LLC谐振变换器可工作在 LLC-DCX和 LLCD2D两种工作模式。其中前者按照变压器电压比对输入直流电压进行隔离传输,但是不具有稳压能力,变换器谐振参数依据总损耗最小的原则进行优化设计[11,16];而后者可以通过闭环控制维持输出电压的稳定。图 1所示是典型的全桥 LLC-D2D变换器拓扑。按照设计要求,本文设计的LLC变换器谐振频率fr设定为1.5MHz,输入电压Vin波动范围为36~72V,输出电压Vo=12V。

图1 全桥LLC-D2D变换器拓扑

Fig.1 Diagram of full-bridge LLC-D2D

为了减小整流管关断损耗,同时尽量减小关断时由于漏感造成的关断过电压和振铃,设计中将谐振频率设置在最大输入电压下,以保证同步整流器件实现ZCS。所以,当输入电压Vin=72V时,变换器增益等于 1,由此确定出变压器电压比 N=6。关于LLC变换器谐振参数的设计,很多文献已经给出详细设计步骤[1-3],这里不再赘述。这里直接给出本文设计的LLC变换器谐振参数,见表1。

根据设计要求可以计算出变换器输出电流平均值 接近34A,当工作在谐振频率点,LLC谐振变换器输出电流波形接近正弦波,流过变压器后级同步整流管的电流峰值Ipk为

接近34A,当工作在谐振频率点,LLC谐振变换器输出电流波形接近正弦波,流过变压器后级同步整流管的电流峰值Ipk为

表1 LLC 变换器主要谐振参数

Tab.1 Resonant parameters of LLC converter

参 数 数 值谐振电感 Lr/μH 0.153谐振电容Cr/nF 72励磁电感 Lm/μH 1.53谐振频率fr/MHz 1.5死区时间Tdt/ns 37

根据式(1)计算出工作在谐振频率点时流过同步整流管的整流电流峰值高达54A。而且,通过闭环仿真得到当输入电压等于36V时,同步整流管电流峰值高达130A。这种导通时间短,但是峰值电流较高的整流电流的有效值较大,增大了器件的损耗和散热压力。通过采用如图2所示的矩阵变压器,可以将流过后级同步整流管的电流分配到两个子变压器模块的同步整流器件中,减小了同步整流管中的电流峰值和电流有效值,减小了同步整流管损耗,同时也避免了PCB局部发热。

图2 基于矩阵变压器的LLC-D2D拓扑

Fig.2 Diagram of LLC-D2D based on matrix transformer

根据图2所示的采用矩阵变压器的全桥LLC变换器拓扑和表1中给出的谐振参数,可以仿真得到工作在谐振频率点处 LLC变换器的励磁电流峰值Im、谐振电流有效值Ipri、中分抽头变压器中每一路同步整流回路的电流有效值 Isec和励磁磁链峰值Ψm见表2,表 2给出的数据将用于后文矩阵变压器的优化设计。

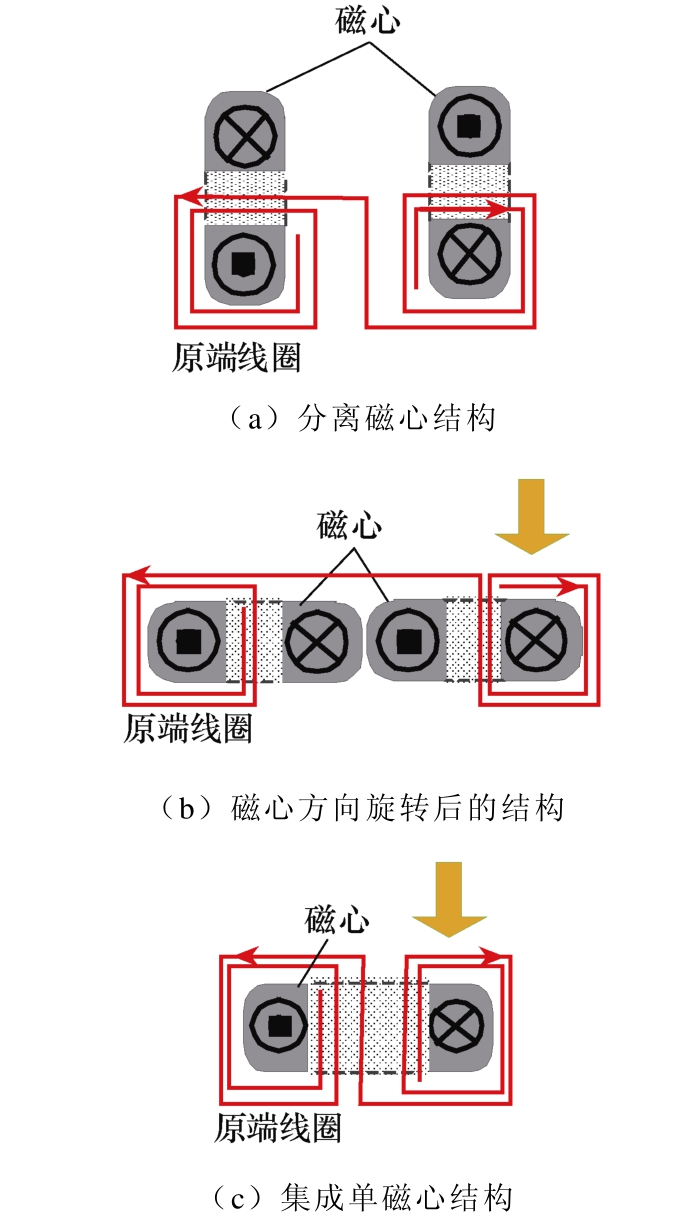

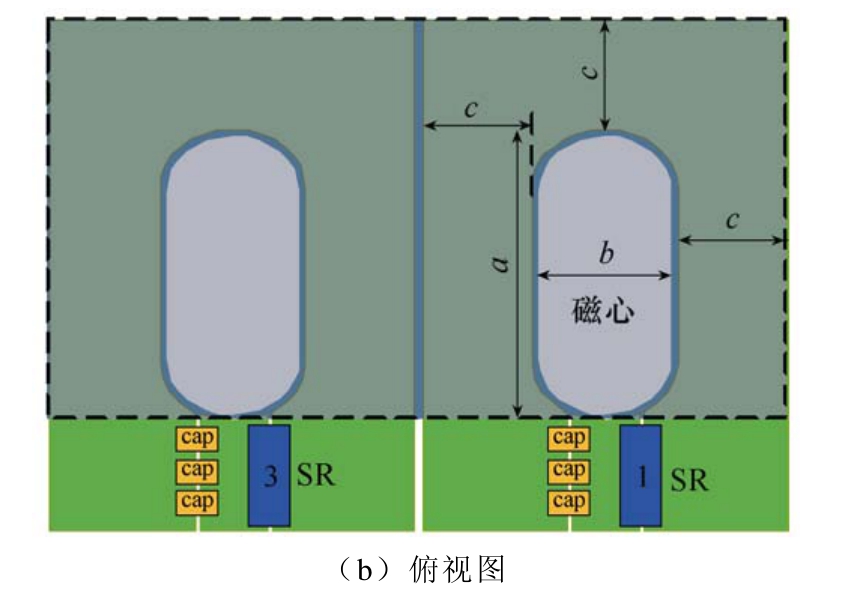

文献[10-11]采用如图 3a所示的两个分离磁心构成矩阵变压器以降低同步整流器件电流应力,但是两个分离磁心在变换器中占据的体积较大。将图3a所示的两个分离磁心分别旋转90°,得到如图3b所示的磁心结构。可以看到,由于两个分离磁心的绕组匝数相同,流过的电流也相等,所以图3b中的两个分离磁心相互靠近的两个磁柱中的磁通、磁链大小相等、方向相反,可以相互抵消。所以,可以省去图3b中的中心磁柱,将两个分离磁心集成到图3c所示的单个磁心中,以进一步减小磁心体积和磁心损耗,提高变换器功率密度。

表2 谐振频率点处的部分关键电气参数

Tab.2 Key electrical parameters working at resonant frequency

参 数 数 值励磁电流峰值Im/A 8.3谐振电流有效值Ipri/A 8.2同步整流电流有效值Isec/A 13.5励磁磁链峰值Ψm/(μV·s) 12.8

图3 矩阵变压器

Fig.3 Matrix transformer

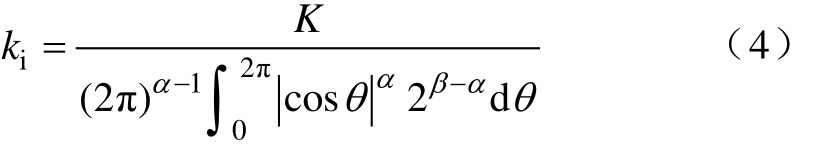

LLC变换器一般工作在谐振频率点处的损耗较小,变换器的优化设计一般也是在谐振频率点进行,所以本文也是在谐振频率点展开变压器的优化设计。在计算磁心损耗时,广泛采用如式(2)所示的Steinmetz公式[15],该公式是正弦激励下用于拟合磁心损耗的经验公式。

式中,Pv为磁心损耗密度;K、α 和β 为拟合系数;fsw为开关频率;ΔB为磁心中磁感应强度的峰峰值。对于本设计中采用的磁心,采用Steinmetz公式拟合的结果如图 4所示,通过曲线拟合得到系数 K=0.000 2,α =1.993,β =3.5。

图4 正弦激励下磁心损耗变化曲线及其拟合结果

Fig.4 Curves of magnetic core loss vs. magnetic flux density and fitting output

上述 Steinmetz计算公式适用于正弦激励下的磁心损耗计算,在非正弦激励下,采用如式(3)所示的改进Steinmetz公式更加准确[15]。

其中

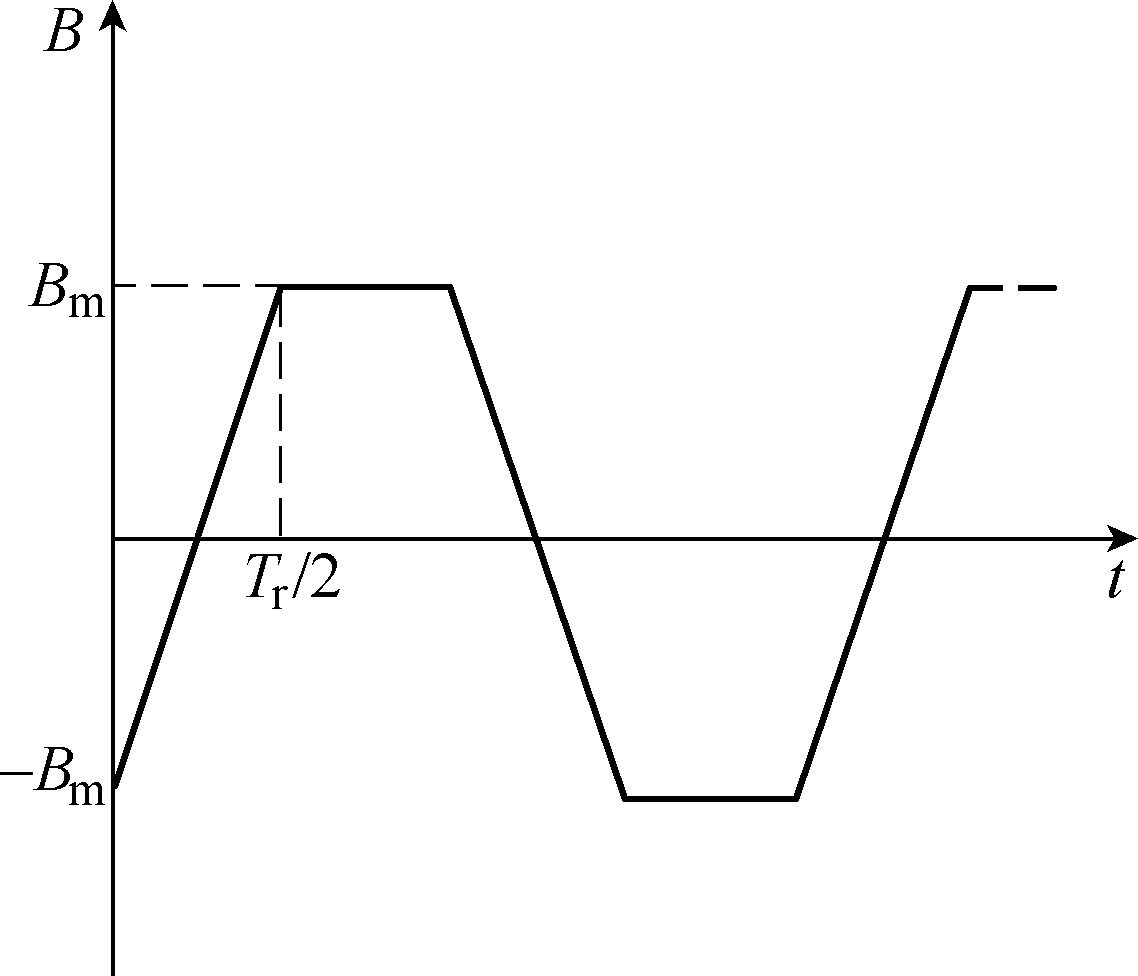

在LLC变换器中,磁心中磁通密度的典型波形如图5所示。

图5 LLC变换器变压器磁心中的磁感应强度典型波形

Fig.5 Typical waveform of magnetic flux density in the magnetic core of LLC converter

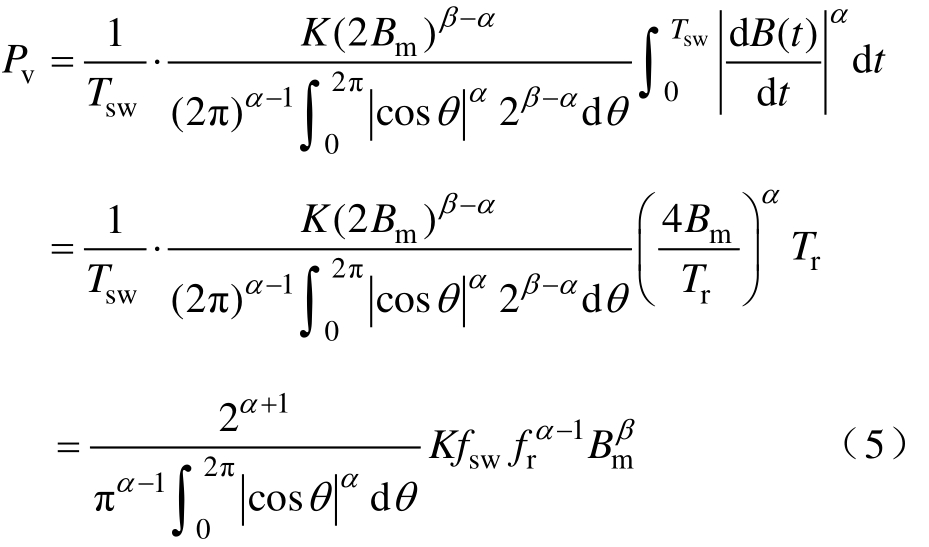

根据图5所示磁通密度波形,式(3)可以化简为

式中,Tsw为开关周期,参数α 和β 已通过图4给出的损耗曲线拟合得到,代入式(5)并采用数值积分得到

为了减小磁心损耗,将谐振频率点变压器磁心损耗密度设置为1 000mW/cm3,根据表1给出的谐振频率和死区时间,可以得到工作在谐振频率点处的开关频率 fsw=1.35MHz,代入式(6),得到此时的磁感应强度最大值Bm=71mT。谐振频率点,励磁磁链幅值Ψm与磁感应强度峰值 Bm,变压器匝数 N和磁通有效面积Ae之间的关系为

根据表2给出的励磁磁链峰值和式(7),可以计算出磁通有效面积Ae=30mm2。

2 矩阵变压器优化设计

2.1 矩阵变压器绕组设计

变压器绕组中 PCB线圈的分布决定了线圈中磁动势的分布,进而决定了变压器漏感的大小、线圈涡流效应强弱和绕组交流损耗的大小[15, 17]。本文采用图6所示的变压器一次和二次绕组交错放置的绕组结构,以尽量减小绕组间磁动势,从而尽量减小漏感、涡流效应和涡流损耗。其中前级有6匝线圈串联,均分在两个磁柱;每一个磁柱上有三套并联的单匝中心抽头后级绕组,同一中心抽头的两个后级绕组分别放置在原端绕组所在PCB层的上、下层。为了进一步减小后级绕组引线造成的漏感和交流损耗,并减小线圈占用的PCB空间以提高功率密度,本文将同步整流管直接放置在后级绕组上,如图6b所示。

图6 矩阵变压器绕组结构

Fig.6 Structure of matrix transformer

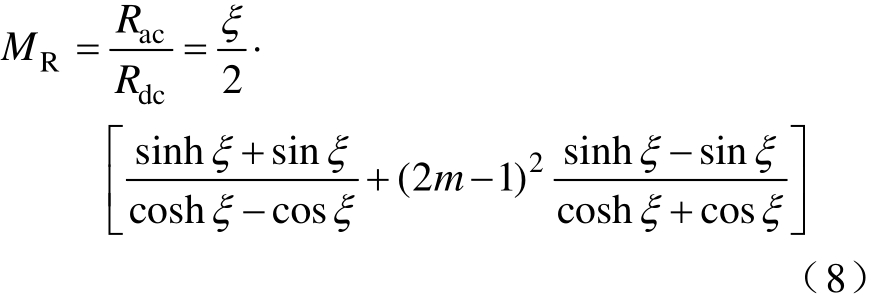

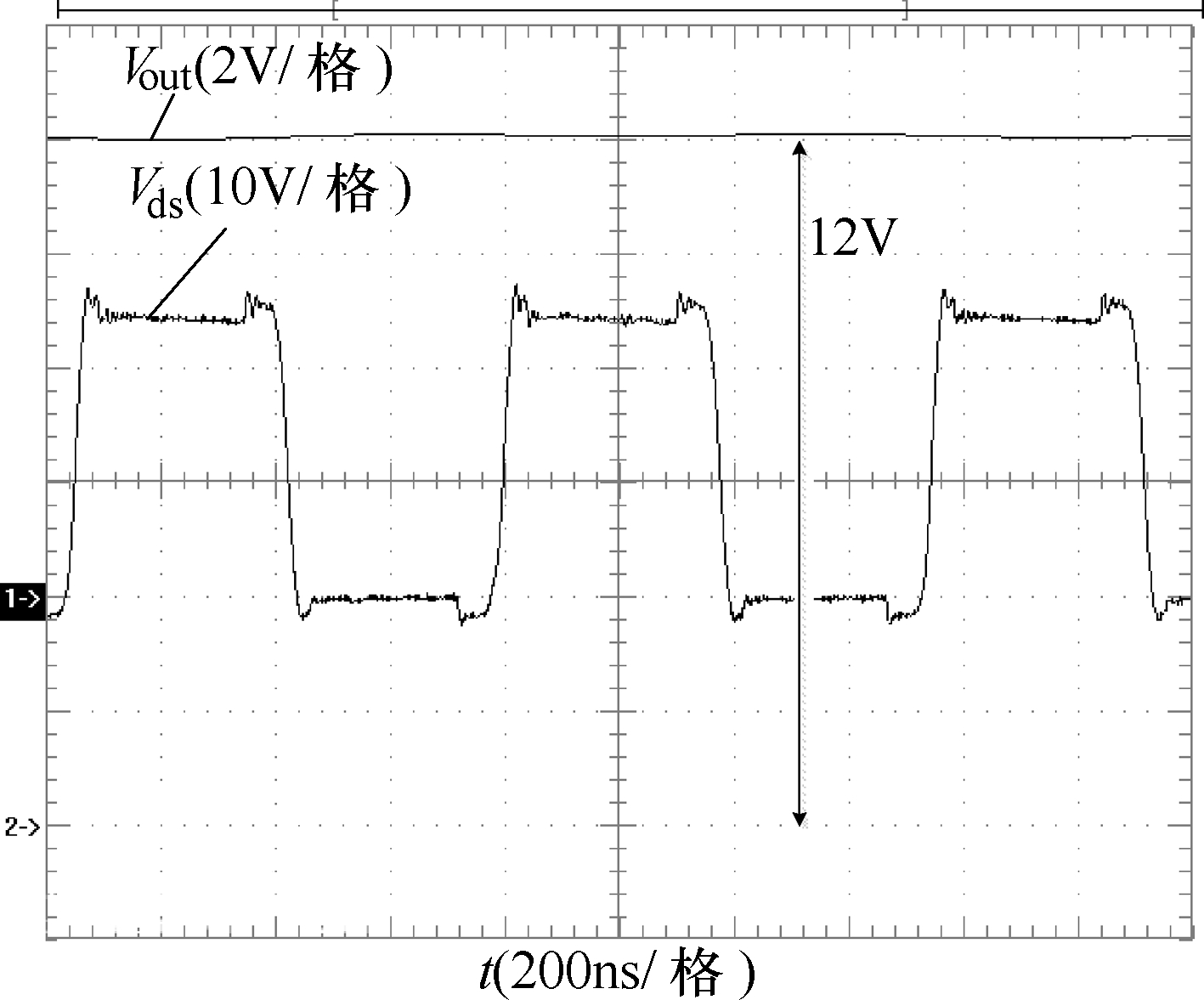

根据文献[18]可知,图 6所示的交错放置的绕组结构中,其第m层PCB线圈的交流电流Rac和直流电阻Rdc的比值MR为

式中,ξ 为PCB绕组厚度h与绕组中电流趋肤深度δ 的比值,在 fsw=1.35MHz下,可以计算出铜导线的趋肤深度等于57μm;m计算公式为

式中,F(h)和F(0)分别为当前绕组所在PCB层上、下边界上的磁动势,对于图6a所示的前后级绕组交错放置绕组结构,可以得到所有绕组的m值均等于1。由于式(8)分母中的直流电阻也随参数ξ 的变化而变化,因此无法选择交流电阻最优值对应的参数ξ。所以式(10)中给出交流电阻 Rac与ξ =1时的直流电阻 Rdc|ξ =1比值 MR|ξ =1,以选择合理的导线厚度。

根据式(10)可以得到 m=1时 PCB线圈交流电阻Rac和ξ =1下直流电阻Rdc|ξ =1比值随导线厚度h变化曲线,如图7所示。

图7 线圈交流电阻与ξ =1时直流电阻之比随铜箔导线厚度h的变化关系

Fig.7 Values of coil AC resistance vs. DC resistance at parameter ξ =1 with different copper thickness h

从图7可以看出,2oz(1oz=28.35g)厚的铜箔下绕组的交流电阻已经较小,虽然3oz厚铜箔的交流电阻更小,但是交流电阻的减小量并不明显,却增大了PCB的加工难度和加工费用,所以选用2oz的铜箔作为PCB绕组。根据图6b所示的变压器绕组结构,可以根据式(11)计算出单匝线圈的直流电阻为

式中,ρ 为导体电阻率。

根据式(8)可以得到2oz铜厚下,单匝绕组的交流损耗Rac等于MR和式(10)中Rdc的乘积。

2.2 变压器损耗计算及优化设计

依据2.1节给出的变压器绕组结构和交流电阻,可以计算得到线圈的总损耗Pwinding为

式中,Ipri和Isec的意义和数值已经在表2中给出。根据图6所示的磁心结构,可以得到变压器磁心体积为

式中,hPCB为 PCB板的厚度;hcore为图 6b阴影部分所示磁心上表面的厚度,有

依据式(13)给出的变压器磁心体积,可以计算出变压器磁心损耗为

变压器总损耗 Pall等于式(12)中绕组损耗和式(15)中磁心损耗之和,有

根据图6b可以知道,磁心上下表面在PCB板上占用的尺寸Sf为

根据图6b所示的磁心结构,可以得出,磁通有效面积Ae和磁心尺寸参数a和b之间的关系为

根据式(18)和变压器总损耗式(16),可以得到变压器总损耗随变压器尺寸参数b和c变化的等值线,如图8中实线所示。

图8 变压器总损耗随几何尺寸变化等值线

Fig.8 Total loss of transformer under different geometry parameters

在谐振变换器的设计中,为了同时实现高功率密度和高效率,不能片面地追求变压器的总损耗最小或变压器占用的PCB面积最小,需要在两者之间进行折中优化。图8中,同一损耗等值线对应有很多种变压器尺寸结构,为了实现同一损耗下变压器占据的PCB面积最小,可以根据式(17)计算出同一损耗等值线上的点对应的尺寸所决定的 PCB面积,从中选择占用PCB面积最小的一组变压器尺寸参数,从而实现在保证变压器总损耗不变的条件下,最小化变压器占用的PCB面积。图8中虚线所示是由式(17)决定的不同尺寸下变压器占用的PCB面积,图中等占用面积等值线与变压器总损耗等值线相切点处的尺寸就是该变压器总损耗下的最优尺寸。

从图8可以看出,变压器总损耗随着变压器占用PCB面积的减小而增大。通过仿真和损耗分解计算得到,为满足后文实验设计的变换器的效率要求,需要变压器总损耗小于3.5W。同时,根据后文给出的LLC变换器的尺寸要求,变压器占用的PCB面积需要小于 400mm2。综合变压器的总损耗和面积指标,并留取一定的裕量,这里选择变压器总损耗等于2.7W。从图8中可以读出2.7W总损耗等值线和 353mm2等 PCB占用面积等值线切点处尺寸为b=4mm, c=3.6mm。

2.3 励磁电感和漏感设计

依据 2.2节设计的原端线圈匝数 N,磁通有效截面积 Ae和励磁电感 Lm,根据安培环路定理可以得到变压器气隙长度Δg的计算公式为

式中,μo为空气中磁导率。通过Ansys有限元仿真得到矩阵变压器漏感Llk=56nH。从表1可知,变压器漏感小于谐振电感,所以需要外接0.1μH的成品电感作为谐振电感。

3 矩阵变压器实验验证

为了验证以上提出的矩阵变压器优化设计方法的有效性,设计了一款基于氮化镓(Gallium Nitride,GaN)器件的 LLC变换器,其输入电压变化范围36~72V,输出电压12V,满载功率400W,体积为标准1/8砖,满载效率96%。本文设计的变换器是一个两级变换器,LLC变换器作为前级实现隔离且稳压,四相同步整流变换器位于后级,实现12V到1V变换,变换器实物如图9所示。

图10所示是在72V输入电压、1.5MHz谐振频率和37ns死区时间下,测量得到的LLC样机电源满载工作时变压器前级 GaN器件的漏源电压和谐振电流波形。

从图10可以看出,变压器原端H桥器件的漏源电压在导通初期的电压降等于-2.4V,这是由于GaN器件反向导通压降较大的缘故,同时该反向电压也说明变换器前级 H桥中的 GaN器件实现了ZVS。本文通过死区时间优化,已经将GaN器件反向续流的导通时间减小到12ns左右。同时,从图10可以看出,励磁电流峰值等于7.2A,代入式(20)可以计算出,励磁电感等于1.65μH,相对于设计值的偏差小于8%,验证了励磁电感设计的正确性。

图9 采用单磁心矩阵变压器的LLC样机电源

Fig.9 LLC converter prototype with single core matrix transformer

图10 LLC样机电源变压器前级器件漏源电压和谐振电流波形

Fig.10 Drain-source voltage of LLC H-bridge GaN HEMT and resonant current

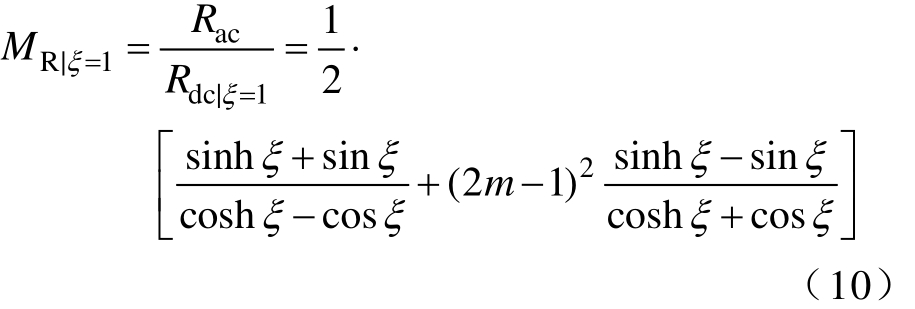

图11所示是在72V输入电压和谐振频率点下,满载工作时测量到的变压器后级同步整流管的漏源电压和输出电压波形。

从图11可以看出,同步整流器件关断时基本不存在电压过冲和振铃。同时可以看出,在该输入电压和谐振频率下,输出电压等于12V,LLC谐振网络的增益等于 1,所以此时变换器工作在谐振频率点,验证了谐振电感设计的正确性。

图11 变压器后级同步整流器件漏源电压和输出电压

Fig.11 Drain-source voltage of LLC synchronous GaN HEMT and output voltage

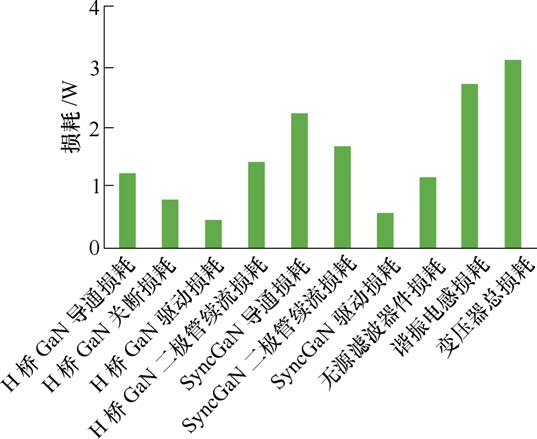

目前测量变压器总损耗的主流方法是损耗分解的方法,就是根据测量到的一定负载下变换器的工作波形和效率,对变换器各部分损耗进行分解计算,最终折算出变压器的总损耗。实验测量LLC变换器效率随负载的变化曲线如图12所示。从图12可以看出,LLC变换器满载时的效率为96.2%,根据测量到的工作波形和满载时效率,对变换器满载工作时的损耗分解计算结果如图13所示。

图12 在72V输入电压下,LLC变换器的效率随负载的变化曲线

Fig.12 Curve of LLC converter efficiency changing with the load under 72V input voltage

图13 满载下的损耗分解

Fig.13 Loss breakdown under full load

根据图 13所示的损耗分解结果可以得到变压器的总损耗等于 3.1W,相对于优化设计值2.7W,偏差在15%以内,偏差范围在工程应用允许的范围内,验证了损耗计算模型的正确性和有效性。

4 结论

本文根据磁通抵消原理,将分离磁心实现的矩阵变压器集成到单个磁心中实现,进一步减小了矩阵变压器的磁心损耗,并提高了LLC变换器的功率密度。在矩阵变压器绕组损耗模型和磁心损耗模型的基础上,提出了变压器总损耗和变压器占用PCB面积的优化折中设计方法。本文提出的磁集成矩阵变压器设计方法的正确性得到了样机电源测量数据的验证,对于实际指导平面磁集成矩阵变压器设计,进一步提高 LLC变换器的效率和功率密度具有一定的参考价值。

[1] Yang Bo, Lee F C, Zhang A J, et al. LLC resonant converter for front end DC/DC conversion[C]//Seventeenth IEEE Applied Power Electronics Conference and Exposition, Dallas, Texas, USA,2002: 1108-1112.

[2] Fang Yu, Xu Dehong, Zhang Yanjun, et al. Design of high power density LLC resonant converter with extra wide input range[C]//Applied Power Electronics Conference (APEC), Anaheim, CA, USA, 2007: 976-981.

[3] Park H P, Jung J H. Power stage and feedback loop design for LLC resonant converter in high switching frequency operation[J]. IEEE Transactions on Power Electronics, 2017, 32(10): 7770-7782.

[4] Ouyang Ziwei, Andersen M A E. Overview of planar magnetic technology-fundamental properties[J]. IEEE Transactions on Power Electron, 2014, 29(9): 4888-4900.

[5] Cui Meiting, You Xiaojie, Li Yan, et al. Planar transformer design in GaN based LLC resonant converter[C]//IEEE 2014 International Power Electronics and Application Conference and Exposition(PEAC), Shanghai, China, 2014: 1353-1357.

[6] Wang Hongfang, Wang Fred. Power MOSFETs paralleling operation for high power high density converters[C]//Conference Record of the 2006 IEEE Industry Applications Conference Forty-First IAS Annual Meeting, Tampa, FL, USA, 2006, 5: 2284-2289.

[7] Fu Dianbo, Lee F C, Wang S. Investigation on transformer design of high frequency high efficiency DC-DC converters[C]//2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), California, USA, 2010: 940-947.

[8] Yi K H, Moon G W. Novel two-phase interleaved LLC series-resonant converter using a phase of the resonant capacitor[J]. IEEE Transactions on Industrial Electronics, 2009, 56(5): 1815-1819.

[9] 赵清林, 刘会峰, 袁精, 等. 基于移相补偿的全桥LLC谐振变换器交错并联技术[J]. 电工技术学报,2018, 33(12): 2777-2787.Zhao Qinglin, Liu Huifeng, Yuan Jing, et al. An interleaved full-bridge LLC resonant converter with phase shift compensation[J]. Transactions of China Electrotechnical Society, 2018, 33(12): 2777-2787.

[10] 刘鑫, 郑祥杰, 侯庆会, 等. 变压器串并联 LLC+Buck级联DC-DC变换器的均流特性[J]. 浙江大学学报: 工学版, 2018, 52(4): 806-818.Liu Xin, Zheng Xiangjie, Hou Qinghui, et al.Current-sharing characteristic of converter composed of LLC with series-parallel transformer and interleaved Buck[J]. Journal of Zhejiang University:Engineering Science, 2018, 52(4): 806-818.

[11] 任仁, 刘硕, 张方华. 基于氮化镓器件和矩阵变压器的高频 LLC直流变压器[J]. 中国电机工程学报,2015, 35(13): 3373-3380.Ren Ren, Liu Shuo, Zhang Fanghua. High frequency LLC DC-DC transformers with a GaN transistor and a matrix transformer[J]. Proceedings of the CSEE,2015, 35(13): 3373-3380.

[12] Reusch D, Lee F C. High frequency bus converter with low loss integrated matrix transformer[C]//2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC),Orlando, Florida, USA, 2012: 1392-1397.

[13] Huang Daocheng, Ji S, Lee F C. LLC resonant converter with matrix transformer[J]. IEEE Transactions on Power Electronics, 2014, 29(8): 4339-4347.

[14] Fei Chao, Lee F C, Li Q. High-efficiency high-power-density LLC converter with an integrated planar matrix transformer for high-output current applications[J]. IEEE Transactions on Industrial Electronics, 2017, 64(11): 9072-9082.

[15] Ouyang Ziwei, Thomsen O C, Andersen M A E.Optimal design and tradeoff analysis of planar transformer in high-power DC-DC converters[J].IEEE Transactions on Industrial Electronics, 2012,59(7): 2800-2810.

[16] 任仁, 张方华, 刘硕. 基于 LLC直流变压器(LLCDCT)效率优化的死区时间与励磁电感设计[J]. 电工技术学报, 2014, 29(10): 141-146.Ren Ren, Zhang Fanghua, Liu Shuo. Optimal design for efficiency based on the dead time and magnetizing inductance of LLC DC transformer[J].Transactions of China Electrotechnical Society, 2014,29(10): 141-146.

[17] Ouyang Ziwei, Ole C Thomsen, Michael AE Andersen.The analysis and comparison of leakage inductance in different winding arrangements for planar transformer[C]//IEEE International Conference on. Power Electronics and Drive Systems (PEDS), Taipei, China,2009: 1143-1148.

[18] Ferreira J A. Improved analytical modeling of conductive losses in magnetic components[J]. IEEE Transactions on Power Electronics, 1994, 9(1): 127-131.